# Automated Design of Application-Specific Smart Camera Architectures

Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen op maandag 4 februari 2008 om 15:00 uur

$\operatorname{door}$

WOUTER CAARLS

doctorandus in de Kunstmatige Intelligentie geboren te Amsterdam

Dit proefschrift is goedgekeurd door de promotoren: Prof.dr.ir. L.J. van Vliet Prof.dr.ir. P.P. Jonker

Samenstelling promotiecommissie:

| Rector Magnificus,          | voorzitter                                |

|-----------------------------|-------------------------------------------|

| Prof.dr.ir. L.J. van Vliet, | Technische Universiteit Delft, promotor   |

| Prof.dr.ir. P.P. Jonker,    | Technische Universiteit Eindhoven         |

|                             | Technische Universiteit Delft, promotor   |

| Prof.dr.ir. H.J. Sips,      | Technische Universiteit Delft             |

| Prof.dr. H. Corporaal,      | Technische Universiteit Eindhoven         |

| Prof.dr.ir. H. Bal,         | Vrije Universiteit Amsterdam              |

| Dr. E. Visser,              | Technische Universiteit Delft             |

| Dr.ir. R. Kleihorst,        | NXP Semiconductors                        |

| Prof.dr. I.T. Young,        | Technische Universiteit Delft, reservelid |

This work was supported by the Dutch government in their PROGRESS research program under project EES.5411, and carried out in the Quantitative Imaging group of the Imaging Science and Technology department in the faculty of Applied Sciences of the Delft University of Technology.

Copyright © 2007, Wouter Caarls, Delft. This work is licensed under a Creative Commons Attribution 3.0 License. Reproduction, distribution, and derivation, in whole or in part, is explicitly allowed, provided that the work is properly attributed. ISBN 978-90-9022688-0

# Contents

| 1 | Intr           | roduction                                              | 1  |

|---|----------------|--------------------------------------------------------|----|

|   | 1.1            | Smart cameras                                          | 2  |

|   | 1.2            | Algorithm-specific languages                           | 2  |

|   | 1.3            | Automated design space exploration                     | 3  |

|   | 1.4            | Design flow                                            | 3  |

|   | 1.5            | Contributions and thesis outline                       | 4  |

| 2 | Em             | bedded image processing                                | 7  |

|   | 2.1            | Application domain                                     | 8  |

|   | 2.2            | Processor architectures                                | 8  |

|   | 2.3            | Algorithms                                             | 14 |

|   | 2.4            | Languages                                              | 21 |

|   | 2.5            | Constructing applications                              | 30 |

|   | 2.6            | Discussion                                             | 31 |

| 3 | $\mathbf{Des}$ | igning architecture-independent applications           | 33 |

|   | 3.1            | Architecture independence through algorithm dependence | 34 |

|   | 3.2            | Algorithmic skeletons                                  | 35 |

|   | 3.3            | Stream programming                                     | 38 |

|   | 3.4            | Stream kernels as skeleton inputs                      | 44 |

|   | 3.5            | Discussion                                             | 46 |

| 4 | Imr            | plementing skeletons using meta-programming            | 49 |

| _ | 4.1            | Functional requirements                                | 49 |

|   | 4.2            | Meta-programming                                       | 53 |

|   | 4.3            | A meta-programming language for skeleton instantiation | 58 |

|   | 4.4            | Rewriting                                              | 61 |

|   | 4.5            | Partial evaluation                                     | 65 |

|   | 4.6            | Skeleton merging                                       | 70 |

|   | 4.7            | Results                                                | 75 |

|   | 4.8            | Discussion                                             | 77 |

| 5 | Imr            | plementing stream programming using RPC                | 81 |

| Ŭ | 5.1            | Remote procedure call                                  | 81 |

|   | 5.2            | Run-time environment                                   | 85 |

|   | 5.3            | Mapping                                                | 87 |

|              | 5.4            | Performance prediction           | 93  |

|--------------|----------------|----------------------------------|-----|

|              | 5.5            | Buffer management                | 99  |

|              | 5.6            | Results                          | 101 |

|              | 5.7            | Discussion                       | 105 |

| 6            | $\mathbf{Exp}$ | loring the SmartCam design space | 107 |

|              | 6.1            | Architecture template            | 108 |

|              | 6.2            | Benchmarking                     | 111 |

|              | 6.3            | Application simulation           | 113 |

|              | 6.4            | Pareto optimization              | 116 |

|              | 6.5            | Results                          | 120 |

|              | 6.6            | Discussion                       | 125 |

| 7            | Con            | clusions                         | 127 |

|              | 7.1            | Discussion                       | 128 |

| G            | ossa           | ry                               | 131 |

| Bi           | bliog          | graphy                           | 135 |

| ۸            | Мо             | deling language                  | 147 |

| A            | A.1            | Data structure                   | 147 |

|              | A.2            | Semantics                        | 147 |

|              |                | Syntax                           | 150 |

| в            | Lon            | guage syntax                     | 155 |

| D            | B.1            |                                  | 155 |

|              |                | PEPCI                            | 155 |

| $\mathbf{C}$ | Exa            | mples                            | 159 |

|              | C.1            | Stream program                   | 159 |

|              | C.2            | Skeleton                         | 165 |

|              | C.3            | Meta-skeleton                    | 166 |

| Su           | ımma           | ary                              | 175 |

| Sa           | men            | vatting                          | 177 |

| A            | cknov          | wledgements                      | 179 |

| Cı           | urric          | ulum Vitae                       | 181 |

# Chapter 1

# Introduction

Common wisdom dictates that having the right tool is half the job. The trouble is finding the right tool – or even being aware that it exists! – and learning how to use it. This holds double in computer science, where the number of tools practically exceeds the number of uses. However, often we stick to what we know, and use a programming language and processor architecture that we are familiar with. Only when it becomes apparent that our favorite tools are not sufficient do we start looking for other solutions, leading to costly redesign efforts.

Fortunately, the tools in computer science are much more flexible than those used in crafts. In computer science, if you know how to hammer in a nail, you only need an appropriate *compiler* to use the same algorithm for screwing in a screw. In the past, it has therefore been enough to know just one or a few general-purpose programming languages. But the increasing demands of high data throughput applications such as computer-assisted camera surveillance require radically different, parallel processing architectures. The large semantic gap between language and architecture makes programming akin to actually hammering in the screw.

The common approach to closing this gap is learning a new, architecturespecific language. However, this is not portable and therefore does not solve the redesign problem when the chosen architecture proves insufficient, nor does it help us finding the right architecture in the first place. We need to structurally expand a programmer's toolbox to include many current and future architectures, and – since we cannot expect the programmer to have the knowledge necessary to choose between architectures he does not know – automate the architecture selection.

Instead of bringing the language closer to the architecture, we propose to bring it closer to the *algorithm*, as the programmer certainly is intimately familiar with that. Such an *algorithm-specific language* (ASL) is easy to use because it caters to the specific needs of the algorithm, and it allows the program to run on any processor which implements its interface. Instead of choosing an architecture, the programmer now chooses an ASL to use, which can be done in a much more defined and informed manner.

As the program is now architecture-independent, we can automatically select an appropriate architecture *after* developing the application. The result is a processing architecture tailored to the application: the right tool for the job.

# 1.1 Smart cameras

The drive for our research is the field of embedded image processing. Even though the miniaturization and associated performance increase of microprocessors has been phenomenal, analyzing images delivered by current sensors at video speed (thirty frames per second) is still a daunting task. Specialized parallel architectures, such as single-instruction multiple-data (SIMD) processors, are necessary to maintain the required performance at an acceptable level of power consumption.

It is important to note that we are not targeting multimedia tasks such as video compression and image enhancement, which are static and often implemented in application-specific integrated circuits (ASICs) or vendor-supplied libraries. We are interested in the extraction and analysis of information from the images, which can then be used to make control decisions.

A device which integrates an image sensor with a processing architecture for analyzing the images is called a Smart Camera (SMARTCAM). The output of the processing is often not an image but image features, measurements, or control decisions. Such a device must be able to handle low-level pixel processing (noise removal, edge detection, segmentation) as well as feature extraction and high-level decision making. These tasks place vastly different requirements on the processor architectures implementing them. Consequently, there is no single architecture that is best in all situations, and an efficient SmartCam solution will have to be a heterogeneous multiprocessor.

Parallel programming is notoriously hard, even more so if the processors are heterogeneous. Heterogeneous multiprocessors are therefore usually not part of a programmer's toolbox, even if they offer the most efficient solution to the problem at hand. Algorithm-specific languages allow us to add any such architecture to the toolbox, and to automatically determine the optimal configuration.

# **1.2** Algorithm-specific languages

Architecture-independent programming is not a new concept; general-purpose languages such as C and Java can be compiled and executed on a large number of processors. Unmodified, however, their use is limited to sequential processors. Although there have been many attempts to automatically translate a C program to a parallel architecture, they are invariably inefficient, or efficient only for a small subset of C programs.

Once we realize that there is no reliably efficient way to translate a generalpurpose sequential language to a parallel implementation, it makes sense to look at special-purpose sequential languages. By specializing a language to just those concepts necessary for the implementation of a particular class of algorithms, we accomplish two things: the language becomes easier to use, and can be efficiently translated to more (parallel) architectures.

The efficiency of the translation depends on the size of the language subset that a particular algorithm requires. Simple algorithms which use only a small subset can be translated very efficiently and can run on very simple processors. Complex algorithms using large subsets will generally be able to exploit less parallelism and can only run on more flexible processors. We must therefore provide a range of algorithm-specific languages, each for a different class of algorithms, and each providing a different trade-off between generality and efficiency. If the user then chooses the most restrictive language in which his algorithm can be specified, it will execute the most efficiently and on the largest range of processors.

Of course, an application consists not of a single algorithm, but of many different algorithms connected together. Each algorithm may use its own language; this provides the ultimate freedom and flexibility to *map* the application onto an architecture, as it imposes the least number of requirements on the individual architecture components. In turn, this leads to efficient execution on heterogeneous multiprocessor systems.

# **1.3** Automated design space exploration

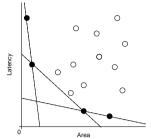

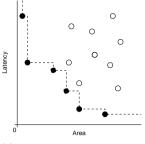

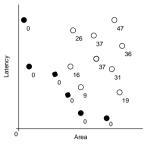

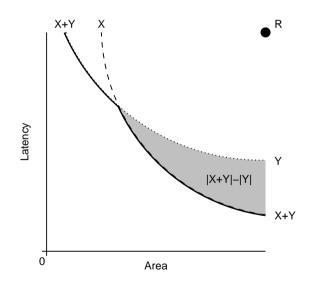

Choosing the right heterogeneous multiprocessor architecture for an application is not an easy task. Apart from choosing the characteristics of the individual processors, we need to determine how many of each processor type to take and how they are to be connected. Each architecture constitutes a trade-off between the objective variables: performance (speed/latency), power consumption and chip area.

Again, there is no single best architecture, even for a single application. Which architecture is more desirable depends on the relative priorities of the objective variables. Since these are hard to specify beforehand, we need to present the user with a set of *optimal trade-offs* (Pareto points) among which he can make the final decision himself.

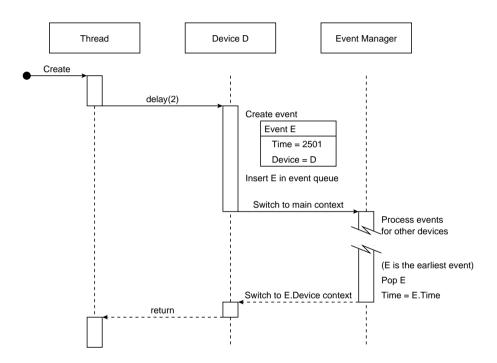

It is of course impossible to actually execute the program on all architectures in the design space. In the first place, we will need to *simulate* the application, as the hardware is not available during the design phase. To reduce simulation time, we use the fact that our model of computation splits the program into separate algorithms which can be simulated individually.

Secondly, the design space is too big to explore using a brute-force method. We use a multivariate heuristic technique to limit the search space while still providing a reasonable approximation of the optimal trade-offs. By repeatedly choosing an architecture, simulating it, and refining the choice, we move towards successively better approximations. Because the design space is highly irregular, the heuristic that we use is based on *genetic algorithms*, since they do not assume a smooth objective space.

The design space is further limited by the use of an *architectural template*. The template contains the modes in which the architecture is allowed to change, such as word size, type and number of execution units, memory organization, interconnection, etc. Each architecture is an instantiation of this template.

# 1.4 Design flow

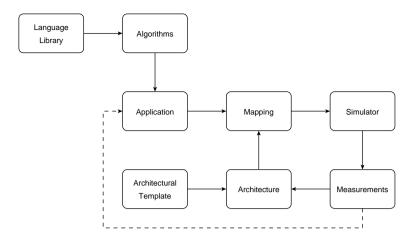

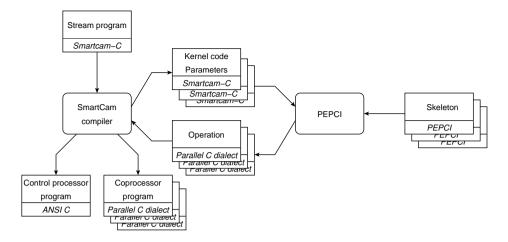

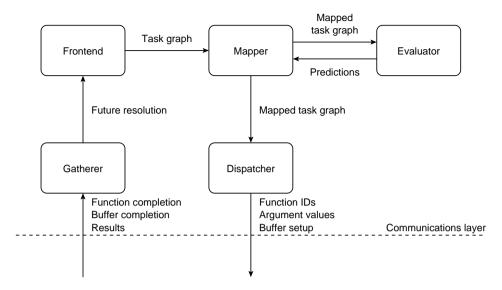

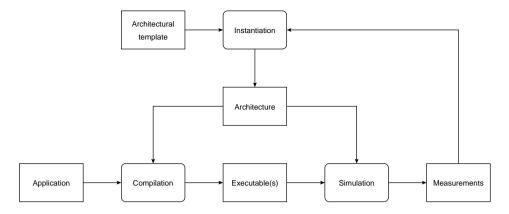

We can now construct the central design flow of our framework, illustrated in figure 1.1. A programmer starts by selecting the appropriate languages and us-

Figure 1.1: Design flow for the development of SmartCam applications. The dotted line denotes the manual restructuring of code if none of the presented architectures are sufficient.

ing these to construct his algorithms. The algorithms are connected to create an application, which is then mapped onto an instantiation of the architectural template. Simulating the application provides performance measures that can be used to refine the architecture.

It is possible to *incrementally* restructure an existing application to use our framework. In this case, the programmer starts by only rewriting the most computationally intensive inner loops of the application. If the trade-offs found by the design space exploration are not to his liking, he can rewrite more parts of the application.

# 1.5 Contributions and thesis outline

Chapter 2 of this thesis gives an introduction to the field of embedded image processing, its typical applications, processor architectures, algorithms and programming languages. We present a set of algorithm classes and match those to architectural features using a processor taxonomy. This supports the conclusion that there is no single best processing architecture, and that we need architectureindependent programs to be able to efficiently exploit all the options.

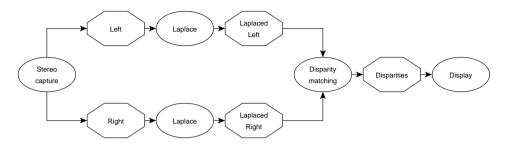

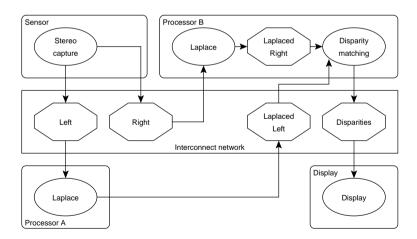

Chapter 3 presents the novel concept of algorithm-specific languages by relating them to functional programming and algorithmic skeletons. It then introduces stream programming as a way of connecting the algorithms, and explains how algorithm-specific languages can be seen as a generalization of the kernel languages used in stream programming.

Chapter 4 contains details about our implementation of algorithm-specific languages. We have created a new meta-programming language especially designed for the source-to-source translation of C-like languages into (parallel) C derivatives. This allows advanced programmers to add support for new algorithm classes or processor architectures. The language uses a novel technique which we call *pseudo*- *dynamic meta-programming* to blur the distinction between the meta-level and source-level parts of the code.

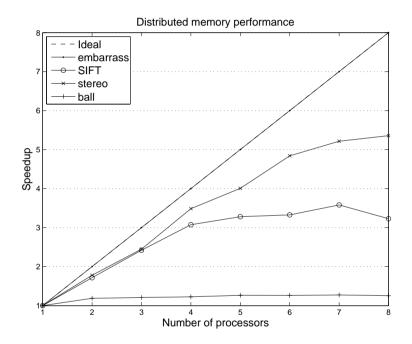

In chapter 5 we discuss the execution of an architecture-independent program on a multiprocessor architecture, especially the problem of mapping operations to processors under dynamically changing conditions. We introduce a new performance prediction technique that incorporates both task cooperation and task dependencies, and present results on the efficiency of our approach.

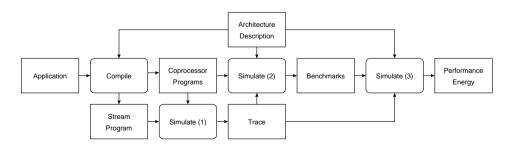

Chapter 6 details how the architecture independence of an application program and properties of the streaming model of computation can be used to efficiently explore the design space of possible processing architectures using Pareto optimization of performance, energy and area. To our knowledge, such a complete integration of the trajectory from source code to a suitable parallel heterogeneous architecture has not been shown before. Results are presented on the convergence and coverage of the exploration, using simulated robotic soccer and augmented reality case studies.

Finally, in chapter 7 we summarize our work and discuss the results.

# Chapter 2 Embedded image processing

Embedded systems are special-purpose computer systems designed to perform a dedicated function. Often, this function includes measuring a property of the environment and acting upon it. For example, a home thermostat measures the air temperature in a room and controls the gas valve and water flow in a central heating system. Such control functions have *real-time constraints*, meaning that an action has to be taken within a certain period after the change in the environment.

In embedded image processing applications, this period is often in the order of 10-100 milliseconds (though it depends on the properties of the dynamic system that is being controlled). In this time frame, many algorithms dealing with noise reduction, segmentation, feature extraction and decision making have to be performed. Since video sequences contain vast amounts of data, processing all the information takes a lot of computing power, often more than is available in regular microprocessors.

In terms of power consumption and speed, an application-specific integrated circuit (ASIC) solution will always be the most efficient. However, the non-recurring engineering (NRE) cost is very high, because on the one hand the design is time-consuming, and on the other the cost of making a leading-edge lithographic mask set already exceeds a million US dollars [125]<sup>1</sup>. Both of these problems are only likely to grow in the future, as designs are getting larger and features sizes smaller [67].

The high NRE costs make ASICs unsuitable for small production runs. Furthermore, they make it uneconomical to modify the implementation based on new conditions or algorithmic insights. Finally, if an application consists of many different possible operations, only a few of which are active at one time, an ASIC requires hardware to be available for all operations, leading to high area overhead.

We are interested in applications for which a single general-purpose CPU is not fast enough – or too inefficient in terms of power consumption –, and which are too specialized, unstable, or dynamic for ASIC implementation. We will describe common image processing algorithms used in such applications, analyze what requirements they put on the processor architecture implementing them, and discuss

$<sup>^{1}</sup>$ Multi-project wafers or limited-custom masks such as sea-of-gates designs can bring this figure down, at the expense of per-unit cost.

the languages that may be used to program those architectures.

# 2.1 Application domain

Many current image processing applications, especially those in machine vision tasks such as industrial inspection, operate in a well-controlled, static environment. Because the environment does not change (except for the properties that have to be measured), they can manage with a static succession of algorithms. These applications are most suitable for an ASIC implementation.

In other situations, the task of the vision system depends on the environment. A photocopier might select different algorithms depending on whether the input is color or black-and-white, text or graphics. A digital video recorder needs to either compress or decompress video depending on whether it is recording or playing back. Still, such *use cases* are themselves static, and switching between them is sporadic. However, performance demands may still require the use of multiple processing devices, each specialized for a certain use case.

The most interesting application domain, and the one we will focus on, requires dynamic reactions to the environment on a frame-by-frame basis. This can be limited to just the front-end vision (such as adjusting noise reduction algorithms based on the signal to noise ratio and scene content), but can also change the entire control behavior of the system [11, 91]. Often, the dynamic environment also leads to many algorithmic changes over the lifetime of the system, thereby requiring a programmable solution.

It may be clear that dealing with this dynamic behavior is mostly a matter of being able to quickly change the way in which the algorithms inside an application are configured and interconnected. Apart from that, however, the fact that the environment is dynamic also has an impact on the types of algorithms that are used. Most importantly, the algorithms should be robust against variable lighting conditions, occlusions, motion, and other factors not under the control of the system.

Note that guaranteeing a reaction within a certain timeframe is hampered by the dynamic task connections. We will not address such guarantees in this study, and use the performance constraints as a guideline only. Because devices that operate in a dynamic environment are often untethered, energy consumption is typically constrained to hundreds of milliwatts to a few watts.

# 2.2 **Processor architectures**

Having restricted our scope to applications requiring programmable solutions and robust algorithms, there is still a very large range of processors to choose from. The main factors that exert an influence on the decision (apart from cost) are the speed at which the device can execute the algorithms, and the amount of energy it needs for the execution.

Speed and efficiency are largely a function of the amount of parallelism that can be exploited, as increasing the clock speed of a single processor is limited by heat production and power dissipation [51]. This parallelism comes in many different flavors, such as bit-level (doing an addition on 8 bits at a time), instruction-level (executing an addition and a multiplication simultaneously), data-level (multiplying many different values at the same time) and task-level (convolving one image while segmenting another). All these need to be exploited for optimally efficient execution.

Section 2.3 will analyze the requirements of common image processing algorithms for efficient execution on a parallel processor architecture. Because we are investigating single algorithms, we will ignore task-level parallelism (that is the subject of section 2.5). We will also ignore bit-level parallelism, because we will assume all architectures allow the concurrent processing of entire bytes or words. This leaves us with instruction and data-level parallelism, for which we will need a consistent description of architectural support in the form of a taxonomy.

## 2.2.1 Taxonomy of parallel computing

The most common taxonomy for (parallel) computation is that by Flynn [50]. Flynn distinguishes four classes of computers:

- Single instruction stream single data stream (SISD, sequential computation)

- Single instruction stream multiple data stream (SIMD, vector computing)

- Multiple instruction stream single data stream (MISD, not generally used)

- Multiple instruction stream multiple data stream (MIMD, cluster computing)

This taxonomy makes essentially two distinctions: whether there are one or more instruction sequencers, and whether an instruction addresses multiple memories or only one. The main problem of this system is that it is not detailed enough for our purposes – having only two classes for parallel computers (SIMD and MIMD).

Whether an algorithm can be efficiently executed in parallel depends on many more factors. One important aspect is the degree of local autonomy in the processors, which can take a number of different forms [54, 83]. Essentially, these constitute different dimensions, spanning a space that encompasses everything from truly centralized (SIMD) to truly distributed (MIMD) autonomy. The most efficient execution architecture for a certain algorithm, then, is the one which distributes only as many resources as is necessary to exploit the parallelism inherent to the algorithm, while centralizing the rest. We will consider the following dimensions:

- Number of processing elements (PEs). This determines how many instructions may be executed in parallel.

- *Homogeneous or heterogeneous processing elements.* This specifies whether all processing elements are the same or not. There may be differences in instruction set, frequency, memory, access to external resources, etc.

- Local or global instruction sequencing. This specifies whether each processing element may branch independently; local instruction sequencing means there are multiple instruction streams.

- Instruction synchronization. Even with only one instruction stream (global instruction sequencing), processing elements may execute different parts of the stream at different times (buffered execution). Conversely, locally sequenced processing elements will include "barrier" instructions which are executed concurrently by all elements.

- *Shared or distributed memory.* If each processing element has its own memory, the memory bandwidth is higher. On the other hand, accessing non-local memory becomes more difficult.

- Local or global memory address generation (per-processor indirect memory addressing). Local memory address generation with global instruction sequencing means that, while every processor executes the same *load*, they may read from *different* parts of memory. Shared memory always implies local memory address generation.

- Interconnect organization. This describes how the processing elements are connected. It has a large impact on the communications bandwidth. Popular choices are rings, meshes, and crossbars. Often, a separate broadcast capability is also included.

- Local or global communication address generation. Analogous to memory address generation, a communication operation may require each processor to communicate with the same relative address (such as their left neighbor in a ring interconnect), or it may compute the address locally.

- Communication latency. Tightly coupled systems can communicate with single cycle latency. Shared memory coupled systems typically require tens to hundreds of cycles. Finally, networked systems need many tens of thousands of cycles.

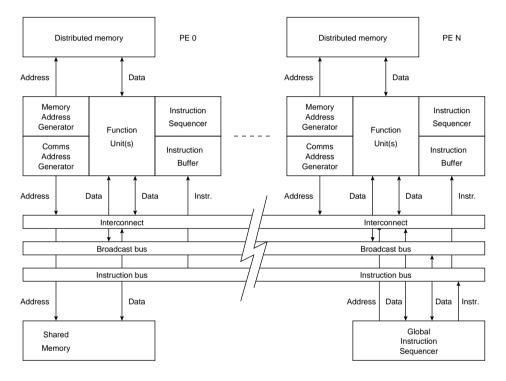

Figure 2.1 illustrates how these components interact in a generalized parallel system.

# 2.2.2 Examples

Table 2.1 categorizes a number of contemporary processing architectures in terms of our taxonomy. While superscalar processors such as the Intel Core 2 microarchitecture (Intel Corporation, USA) are not generally considered to be a parallel system, they exploit a considerable amount of instruction-level parallelism through wide execution paths.

Furthermore, the nodes of the DAS2-TUD (Advanced School for Computing and Imaging, The Netherlands) cluster themselves consist of Intel Pentium processors, while the IMAP-CE (NEC Corporation, Japan) processing elements contain multiple (heterogeneous) function units. The TriMedia (Philips Semiconductors, The Netherlands) contains instructions which allow the bytes in a 32-bit data

Figure 2.1: Generalized view of a parallel system. Many components can be either present or absent (such as the local address generators) or may have different properties (such as the interconnect or the function units).

word to be treated as single values, offering a limited form of data parallelism. The taxonomy could therefore apply to multiple levels of abstraction. For each architecture, we will only consider the level that exposes the largest degree of parallelism.

#### Intel Core 2 microarchitecture

The Core 2 [135] is Intel's latest microarchitecture to implement the x86 instruction set. It is a 5-issue out-of-order superscalar processor. This means that while the instruction stream is one dimensional, different parts of it are executed by different execution units, not necessarily in the order in which they appear in the stream; each execution unit has its own instruction queue. The execution units are heterogeneous (for example, one can only do loads from memory), and can forward results using a fully connected bypass network.

Intel produces chips with multiple of these cores on a single die, in a shared memory configuration. The number of cores per die is expected to grow in the future.

#### Philips TriMedia

The TriMedia [118] is a 5-issue VLIW processor. This is a different approach from superscalars but achieves the same result: a number of heterogeneous execution units is fed from a single instruction stream. In VLIWs, however, the instructions are scheduled by the compiler instead of the processor: each instruction in the stream contains a sub instruction for every execution unit, and these are executed in lock-step, reducing hardware complexity and power dissipation.

The main drawbacks of this approach are the large code side and the inefficiency of branching instructions.

#### Philips XeTaL

XETAL (Philips Research Laboratories, The Netherlands [1]) is an SIMD processor specifically targeted to near-sensor processing such as fixed pattern noise correction and color reconstruction, but due to its fully programmable nature it can also be used for tasks like segmentation and stereo vision (through block matching between a left and a right camera image). It contains 320 10-bit fixed-point PEs with little local autonomy and small memories (16 image lines at a horizontal resolution of 640 pixels). Notably, the PEs have no indirect addressing capability, and only one of the operands of a multiplication may be local. The PEs are connected in a line (broken ring), and have access to a broadcast bus.

The control processor has a 12-bit integer ALU and 30 registers. The program memory is limited to 1024 instructions.

#### NEC IMAP-CE

The IMAP-CE [85] SIMD processor is similar to the XETAL but has less, more powerful, PEs. Each of its 128 8-bit PEs is a 4-way VLIW with 24 registers and 2KB of local memory. The control processor is 16 bit, with 26 registers, 2KB local

data memory and 32KB program memory. An external 256MB SDRAM can be used if more memory is required. Data from this memory can be copied under DMA.

The IMAP-CE's PEs are interconnected using a ring. For binary operations, it supports *neighborhood parallelism* by gathering the data of the 8-connected neighborhood of a pixel in a single cycle. Each PE may generate its own memory address, but not the communication address.

A redesign of the IMAP-CE, called the IMAPCAR, uses 16-bit instead of 8-bit PEs.

#### TU/e DC-SIMD

The DC-SIMD [49] architecture is a prototype linear SIMD array that brings instruction buffering to SIMD processors with local communication address generation. Instruction buffering was introduced to avoid the long delays associated with dynamic communication in other architectures [68, 16]. In this case, execution is not fully synchronous, as each processor may wait a different amount of time depending on communication distance. If these distances are evenly distributed (so that a processor waiting for a long-distance communication is later likely to require only a short waiting time), DC-SIMD is faster than repeated shifting.

#### NVidia G80

Graphics Processing Units (GPUs) used for 3D visualization have become progressively more capable of scientific computing. Their processing elements started as configurable fixed-function units specifically for pixel (*fragment*) and triangle (*vertex*) operations. Later, they became programmable, and the G80 (NVidia Corporation, USA [40]) is the first such architecture to provide homogeneous scalar processing elements, unifying the fragment and vertex processors.

The G80 actually consists of 16 SIMD processors with 8 processing elements each. Instead of memory local to the PEs each processor has 16KB of *shared* memory, divided in 16 banks. As long as there are no bank conflicts, memory access is as fast as using registers. This is not the case for access to *global* memory, which has a 200-300 clock cycle latency. To hide this latency, a *thread scheduler* can switch to a different task while waiting for the transaction to complete. Using global memory is the only way for the processors to communicate.

#### ASCI DAS2-TUD

MIMD systems created by connecting commercial off-the-shelf components (*Beowulf* clusters, [121]) have become very popular in the last decade. The Distributed ASCI Supercomputer 2 (DAS2) consists of five such clusters, of which DAS2-TUD is one. Each of its 32 nodes contains 2 1 GHz Intel Pentium III processors with 1GB shared memory, and they are connected using Myrinet-2000 (Myricom, Inc., USA). Myrinet-2000 allows any permutation of connections between nodes to communicate bidirectionally at full 2Gb/s bandwidth using a Clos network. The minimum communication latency is around 10.000 clock cycles.

An new cluster, called DAS3, has now been installed. The TUD site contains 68 2.4 GHz AMD Opteron (Advanced Micro Devices, USA) processors connected by 1Gbps Ethernet.

# 2.3 Algorithms<sup>2</sup>

Image processing is a very large field, even if we restrict ourselves to embedded and real-time applications. It is therefore impossible to analyze all algorithms. We will, however, present a number of popular algorithms in this sub domain. Of course, what is possible in real-time is a shifting target as processors become faster.

In our analyses, we will always assume an optimal distribution of the image(s) over the available processors, and enough memory to store all relevant information. The following notation is used:

- X, Y and Z are digital images, treated as partial functions which map a pixel location to some value:  $X : \mathbb{N}^2 \to \mathcal{R}(X)$ . The domain of X, that is, all pixel locations for which X is defined, is denoted by  $\mathcal{D}(X)$ . Images are assumed to be square, having  $|\mathcal{D}(X)|$  pixels, where  $2\log\sqrt{|\mathcal{D}(X)|} \in \mathbb{N}$ . The range (possible pixel values) is denoted by  $\mathcal{R}(X)$ , and can be an intensity, a Cartesian product of intensities (in the case of *tensor* images), or any other value.

- p, q and r are pixel locations. X<sub>p</sub> is the value of the pixel in X at location p.

- S and T are sets of relative pixel locations, used as a neighborhood or *structuring element* around a pixel.

- *R* is a set of absolute pixel locations.

- f and g are functions.

- C is an array of constants.

## 2.3.1 Parallelism

We will classify the considered algorithms into categories which offer the same amount of parallelism. On an algorithmic level, we are only interested in the *inherent* parallelism of the algorithm, that is, the (average) amount of primitive operations that may be executed in parallel assuming infinite resources. This can be determined by counting the number of computational steps in the algorithm, and dividing it by the number of steps a hypothetical infinitely parallel machine would need to execute it.

Two operations may not be executed in parallel if, under transitive closure, there exists a dependency between them. There are three kinds of dependencies which affect the inherent parallelism of an algorithm [14]:

$<sup>^2\</sup>mathrm{The}$  basis of this section was formed during an internship at NEC, Japan in May 2005

| Characteristic                    | cteristic Core 2 TriMedia XeTaL-1 IMAP-CE DC-SIMD G80 DAS2- | TriMedia | XeTaL-1     | IMAP-CE     | DC-SIMD     | G80                              | DAS2-TUD         |

|-----------------------------------|-------------------------------------------------------------|----------|-------------|-------------|-------------|----------------------------------|------------------|

| PEs                               | 5                                                           | 5        | 320         | 128         | 320         | 128                              | 24               |

| Heterogeneous                     | ~                                                           | X        | z           | z           | z           | z                                | z                |

| Instruction<br>sequencing         | Global                                                      | Global   | Global      | Global      | Global      | Clustered per<br>8 PEs           | Local            |

| Synchronization                   | Buffered                                                    | Lockstep | Lockstep    | Lockstep    | Buffered    | Clustered per<br>8 PEs           | Free             |

| Memory<br>organization            | Shared                                                      | Shared   | Distributed | Distributed | Distributed | Shared per<br>cluster            | Distributed      |

| Memory address<br>generation      | Global                                                      | Global   | Global      | Local       | Local       | Local                            | Local            |

| Interconnect<br>organization      | Full                                                        | Full     | Ring        | Ring        | Ring        | Using global<br>shared<br>memory | (8, 8, 8)-Clos   |

| Comm address<br>generation        | Global                                                      | Global   | Global      | Global      | Local       | Local                            | Local            |

| Communication<br>latency (cycles) | 1                                                           | 1        | 1           | 1           | 1           | $\approx 100$                    | $\approx 10.000$ |

\_\_\_\_

\_\_\_\_

- *Flow dependencies* arise when an operation writes a variable which is read by an operation occurring later in the algorithm description.

- Anti dependencies are those where an operation writes a variable which is read by an operation *preceding* it in the algorithm description.

- Output dependencies occur when two operations write to the same variable.

Often, the algorithm can be rewritten to avoid anti and output dependencies, but flow dependencies are really inherent. Whether the inherent parallelism is *exploitable* depends on the amount of available processing elements, their capabilities and interconnections. In short, it depends on whether the pattern in which the algorithm accesses the pixels is supported by the hardware. We will therefore define our categories based on these access patterns.

#### 2.3.2 Low-level operations

Low-level operations work on entire images. They take images as input and produce images as output. This means that essentially all pixels in the input image will be visited by the algorithm.

#### Pixel to pixel operations

$$\forall \mathbf{p} \in \mathcal{D}(Y) : Y_{\mathbf{p}} \leftarrow f(X_{\mathbf{p}}) \tag{2.1}$$

Pixel operations, such as binarization and addition, contain trivial parallelism. Each pixel may be processed completely in isolation, resulting in parallelism  $|\mathcal{D}(Y)|$ . Depending on f, it may be possible to exploit instruction-level parallelism within each pixel. For example, computing an arctangent is often implemented as a multi-linear approximation, some parts of which may be executed in parallel.

#### Anisotropic pixel operations

$$\forall \mathbf{p} \in \mathcal{D}(Y) : Y_{\mathbf{p}} \leftarrow f(\mathbf{p}) \tag{2.2}$$

Anisotropic operations have access to the pixel coordinates. These are often used to generate images for use in later operations, such as ramps and subsampling maps. Apart from requiring each processing element to know which pixel locations it is processing, this does not affect the available parallelism.

#### Pixel lookup operations

$$\forall \mathbf{p} \in \mathcal{D}(Y) : Y_{\mathbf{p}} \leftarrow f(X_{\mathbf{p}}, Z) \tag{2.3}$$

Lookup operations can access a lookup table (Z) to determine the value of a pixel. This category includes such operations as color mapping and segmentation, but if X is a displacement map and Z an image, it may also be used for lens distortion correction. The inherent parallelism is still  $|\mathcal{D}(Y)|$ , but implementations may suffer from read contention on Z. If the added latency due to such accesses can not be sufficiently amortized through duplication, pipelining, or instruction buffering, this may severely limit the exploitable parallelism.

Lookup operations require local memory address generation for efficient implementation. Additionally, 2D lookups (such as displacement maps) require local communication address generation.

#### Pixel to global operations

$$\forall \mathbf{p} \in \mathcal{D}(X) \forall \mathbf{q} \in g(X_{\mathbf{p}}) : Y_{\mathbf{q}} \leftarrow f(X_{\mathbf{p}}, \mathbf{q})$$

(2.4)

This is the dual of the pixel lookup class, generating multiple output pixels per input pixel. Clearly, this suffers from output dependencies if the sets of output pixels generated by g are not disjoint. Even if the sets are disjoint, write contention on Y limits exploitable parallelism; efficient implementations therefore require the memory to be distributed according to g. In addition, pixel to global operations have the same address generation requirements as pixel lookup operations. An example is the Hough transform, where each pixel of an image generates a curve in Hough space.

#### Neighborhood to pixel operations

$$\forall \mathbf{p} \in \mathcal{D}(Y) : Y_{\mathbf{p}} \leftarrow f(\{X_{\mathbf{p}+\mathbf{q}} | q \in S\}) \tag{2.5}$$

Any neighborhood operation, from mathematical morphology to convolution. Again, without further knowledge of f, inherent parallelism is still  $|\mathcal{D}(Y)|$ . However, if S is not contiguous (for example, because the convolution kernel contains many zeroes), exploiting this parallelism requires a denser interconnect than rings or meshes.

#### **Recursive neighborhood to pixel operations**

$$\forall p \in \mathcal{D}(Y) : Y_{\mathbf{p}} \leftarrow f(\{X_{\mathbf{p}+\mathbf{q}} | q \in S\}, \{Y_{\mathbf{p}+\mathbf{r}} | r \in T\})$$

(2.6)

A recursive operation allows access to certain parts T of the *output* image. This introduces flow dependencies, and therefore an ordering and limitations on parallelism. T might even be chosen such that no legal order can be found. In the most popular recursive neighborhood operations, such as distance transforms [18], T is the neighborhood that would be available assuming row-major iteration (iterating over columns in the inner loop). Parallelism is limited to  $\frac{\sqrt{|\mathcal{D}(Y)|}}{2}$ , because at every step only a diagonal line of the output image can be calculated. Full exploitation requires at least a tightly coupled ring connected system with local memory address generation. Loosely coupled systems will lose too much time waiting for the processed boundary values on which f depends.

#### **Bucket** processing

$$Y \leftarrow X$$

$$Bucket \leftarrow R$$

while  $\exists \mathbf{p} \in Bucket$

$$Bucket \leftarrow (Bucket \setminus \mathbf{p}) \cup g(Y_{\mathbf{p}})$$

$$Y_{\mathbf{p}} \leftarrow f(Y_{\mathbf{p}})$$

(2.7)

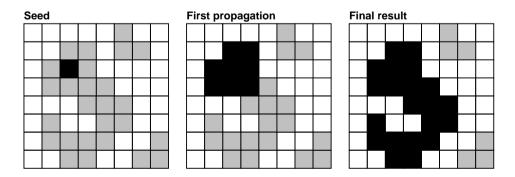

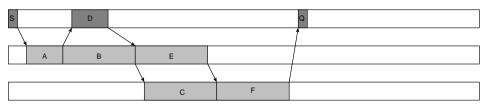

A bucket is initialized with a number of seed points (R). For each seed point, the output is updated using f, while new points can be added using g. There is no explicit ordering on the treatment of the bucket elements. It may be implemented as a *stack*, in which case the order is depth-first. An example operation which can be implemented using bucket processing is the binary propagation of a seed over a mask image, shown in figure 2.2.

By distributing the bucket over the available processing elements [100], each PE reading from the bucket that contains the pixels it has in local memory, we attain a parallel implementation. The inherent parallelism is limited by the size of the bucket, which itself depends on g, and is thus data-dependent. Exploitable parallelism is further limited by the process of writing remote buckets. For buckets sizes larger than one, local memory address generation is necessary.

#### Ordered-iteration bucket processing

$$Y \leftarrow X$$

$$Stack \leftarrow R$$

while  $Stack \neq \emptyset$ :

$\forall p \in Stack$ :

$Y_{\mathbf{p}} \leftarrow f(\{X_{\mathbf{p}+\mathbf{q}} | q \in S\})$

$$NewStack \leftarrow Stack \cup g(\{X_{\mathbf{p}+\mathbf{q}} | q \in S\})$$

$$Stack \leftarrow NewStack$$

$X \leftarrow Y$

$$(2.8)$$

Many wavefront propagation algorithms, such as skeletonization, require the neighborhood of a pixel in order to determine the output value and update the bucket. Anti-dependencies (where an updated value is erroneously read as part of the neighborhood) must therefore be resolved by creating a temporary output image and placing a partial ordering on which pixels may be processed: all pixels in one iteration must be completed before starting the next.

Figure 2.2: Successive stages of the binary propagation of a seed over a mask. The first figure is the seed R; the middle figure illustrates the pixels that may be reached by the first application of g, while the right figure is the final image.

Iteration ordering further limits parallelism (although, again, data-dependently), while neighborhood addressing has the same requirements as in eq. 2.5.

#### 2.3.3 Intermediate-level operations

Intermediate-level operations reduce the amount of data in an image, either by selecting pixels or objects from an image, or by accumulating the pixels into a scalar or vector by some statistical operation.

#### Scalar reduction

$$\forall \mathbf{p} \in \mathcal{D}(X) : y \leftarrow f(X_{\mathbf{p}}, y) \tag{2.9}$$

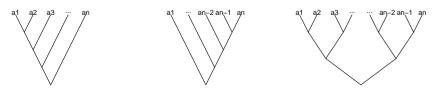

Reduces an entire stream to a scalar value. As we have not defined an *order* on X, f must be both associative and commutative. Many reduction operations, such as maximum, minimum and addition, satisfy these conditions. From commutativity also follows that  $\mathcal{R}(X) = \mathcal{R}(y)$ . Such operations may be performed in  $2 \log |\mathcal{D}(X)|$  steps using a *reduction tree*, leading to inherent parallelism  $\frac{|\mathcal{D}(X)|-1}{2\log|\mathcal{D}(X)|}$ .

Full exploitation of this parallelism requires a tightly coupled interconnect which can emulate a tree (such as full or hypercube interconnect). More restricted forms, such as rings or meshes, have to spend time shifting the intermediate values. A broadcast bus is then needed to avoid too many shifts at the upper levels of the tree. In that case, ring parallelism is in the order of  $\frac{1}{3}|\mathcal{D}(X)|^{\frac{2}{3}}$  (see footnote<sup>3</sup>).

#### Vector reduction

$$\forall \mathbf{p} \in \mathcal{D}(X) : Y_{X_{\mathbf{p}}} \leftarrow f(Z_{\mathbf{p}}, Y_{X_{\mathbf{p}}}) \tag{2.10}$$

Vector reductions are used to aggregate values for a number of different items simultaneously, the most well-known being histogramming, with f = (+) and Z = 1; in other cases, X is often an image of *object indices*. The amount of work, and the inherent parallelism, is the same as scalar reduction. Full exploitation is still possible, but now requires  $|\mathcal{D}(Y)| (= |\mathcal{R}(X)|)$  parallel reductions.

A naive ring implementation using the same method as for scalar reduction requires  $|\mathcal{D}(Y)|$  times more work, since all elements of Y have to be combined at each node of the reduction tree. From a certain size of  $|\mathcal{D}(Y)|$  onwards, it becomes advantageous to distribute Y over the available processors (with each processor creating a local version and combining them afterwards), leading to parallelism  $\frac{1}{2}|\mathcal{D}(X)|^{\frac{1}{2}}$  for  $|\mathcal{D}(Y)| \leq \sqrt{|\mathcal{D}(X)|}$ .

#### Filtering

$$Y = \{X_{\mathbf{p}} | Z_{\mathbf{p}} = \mathsf{true}\}$$

(2.11)

<sup>&</sup>lt;sup>3</sup>This may be achieved in three phases: first, reducing the values local to each processor. Next, doing parallel reductions by shifting the data over increasing distances. Finally, a sequential reduction by gathering the remaining data over the broadcast bus. Each phase takes  $|\mathcal{D}(X)|^{\frac{1}{3}}$  steps.

Generates an output containing fewer elements than the input, such as in subsampling. There are no dependencies, and inherent parallelism is  $|\mathcal{D}(X)|$ . Exploitation efficiency depends on the time it takes to redistribute Y.

#### Contour following

$$\forall \mathbf{r} \in R : Y_{\mathbf{r}} \leftarrow (0, \mathbf{r})$$

while  $R \neq \emptyset :$

$$\forall \mathbf{r} \in R :$$

$$\mathbf{p} \leftarrow \operatorname{Snd}(Y_{\mathbf{r}})$$

$$Y_{\mathbf{r}} \leftarrow (Y_{\mathbf{r}}, \mathbf{p} + f(\{X_{\mathbf{p}+\mathbf{s}} | \mathbf{s} \in S\})$$

$$(2.12)$$

This is similar to bucket processing, except that instead of updating the image, for each seed a list of visited points is kept. In 2.12, this list is constructed as a left-recursive tuple (Snd returns the right member of the tuple). Each contour has to be followed sequentially, but different contours may be followed in parallel. Inherent parallelism is therefore |R|.

#### 2.3.4 High-level operations

High-level operations work on the features extracted from images by intermediatelevel operations, and generate new features, or *decisions* based on those features. The data structures involved in these calculations are often not arrays, but lists or trees. In many cases, efficient parallelization requires a different algorithm than the sequential case.

Often, high-level algorithms are not specific to image processing, but rather draw from fields such as linear algebra, optimization, pattern recognition, and symbolic reasoning. We therefore only discuss two examples.

#### Sorting

The fastest sequential sorting algorithm in the average case is *quick sort*, requiring O(NlogN) steps. For linear SIMD arrays, the theoretically optimal worst case is O(N), because a value may have to be shifted from one end of the array to the other. This theoretical optimum is reached by *odd-even transposition sort* (which is a parallel version of *bubble sort*). On meshes, *shear sort* [113] can reach  $O(\sqrt{NlogN})$  by alternatively sorting rows and columns (although this requires limited local communication address generation), and *bitonic sort* [13] reaches  $O(log^2N)$  on hypercubes.

Machines with large communication latencies (such as MIMD clusters) will require N >> P for efficiency. In that case, each processor usually keeps a sorted list. An algorithm that is often used in this case is *sample sort* [60], with time complexity  $O(\frac{N}{P}log\frac{N}{P})$ .

#### Branch and bound search

Branch and bound search is common in optimization problems such as path finding and machine learning. The concept is to start with a partial solution and move towards the final goal, expanding upon that partial solution which minimizes a certain *cost function*. Examples are depth-first search (evaluate first expanded solution first), uniform cost search (expand solution with minimum cost) and  $A^*$  (expand solution with minimum incurred + predicted cost).

Because of its formulation, B&B search is sequential: only one partial solution is expanded at a time. However, we may expand more than one in parallel, provided that the final solution is the same as in sequential expansion. Each processor keeps its own priority queue of expanded but unevaluated partial solutions, and the tops of these queues are regularly exchanged. Note that this means that nonessential partial solutions are expanded, making it difficult to asses the inherent parallelism.

The exchange of partial solutions can be done locally between neighbors [41, 140], and updating a local priority queue only requires local memory address generation. However, how a partial solution is to be expanded depends on the solution, as does the number of children it generates. This makes B&B algorithms less suitable for implementation on machines without local instruction sequencing [79]. In addition, the size of the priority queues will generally exceed the local memory of SIMD processing elements.

#### 2.3.5 Discussion

Image processing uses a wide variety of algorithms, displaying a large diversity in the memory access patterns and inherent parallelism. How this parallelism may be exploited depends on the architecture on which the algorithm is executed; each architecture will require its own implementation in order to achieve the best speedup.

Furthermore, which architecture is most suited to exploit the parallelism depends on the algorithm in question. While an architecture with a large amount of local autonomy and dense interconnect will support all the modes presented in this section, the cost of these features will dramatically reduce the number of processing elements that can be implemented, leading to a loss of exploitable parallelism for less complex operations.

There is therefore no single optimal image processing architecture, but rather a continuum of architectures, each of which is optimal for only a certain *class* of algorithms.

# 2.4 Languages

We will now present a number of APIs and languages that can be used to program parallel devices. In order to restrict our scope somewhat, we only describe Cbased languages, and have selected one representative from each of four categories targeted at different architectures and applications. As in section 2.3, we will focus on the execution of single algorithms.

#### 2.4.1 Shared memory: OpenMP

OpenMP [45] is a multi-platform application program interface (API) for sharedmemory parallel programming in C/C++ and Fortran. It consists of a set of compiler directives (*pragmas*) for expressing fork-join parallelism and a library of utility functions. Fork-join parallelism is characterized by a *master thread* which executes the sequential parts of the program, and splits off *worker threads* in the parallel sections. Once the parallel section is finished, the worker threads are destroyed or suspended until the next parallel section.

#### **Program 2.1** Example of the OpenMP parallel for directive.

```

int y, x;

double out[height][width], in[height][width];

#pragma omp parallel for private(x)

for (y=1; y < height-1; y++)

for (x=0; x < width; x++)

out[y][x] = in[y-1][x] - in[y+1][x];

```

The most common form of parallelism is the data parallelism encoded in forloops. In program 2.1, a vertical gradient is calculated in parallel for all rows in an image. Depending on the number of available processors, OpenMP spawns a thread for each block of y values. Unless stated otherwise, all variables are shared. Since each thread should have its own copy of x, it is declared **private**.

Other forms of parallelism are also possible, such as master-slave data parallelism or task parallelism. Program 2.2 illustrates how task parallelism is expressed: all the code in the block following the omp parallel directive is usually replicated over the threads, but the sections directive restricts this by only spawning a thread to execute each section. Therefore, gauss\_dx and gauss\_dy are executed in parallel.

**Program 2.2** Task parallel gradient magnitude in OpenMP. The Gaussian derivatives gauss\_dx and gauss\_dy are executed in parallel.

```

void gradmag(image_t *in, image_t *out)

{

image_t dx, dy

#pragma omp parallel sections

{

#pragma omp section

gauss_dx(in, & dx);

#pragma omp section

gauss_dy(in, & dy);

}

norm(& dx, & dy, out);

}

```

Additional directives exist to express reductions, and to define *critical sections*, which may only be executed by one thread at a time. Library functions allow interaction with the OpenMP run-time system, such as adjusting the number of worker threads, and querying the current thread identifier.

A key aspect of shared memory parallel programming systems is the absence of a *data distribution* mechanism. As each processor may access any part of the memory with the same latency, the location is unimportant except for caching. While efforts have been made to implement OpenMP for distributed-memory systems [47], the lack of control over the data distribution can lead to a performance loss compared to true distributed-memory programming environments.

OpenMP may be used for *incremental parallelization*. Because OpenMP is a strict superset of the host language, any normal sequential program is a valid OpenMP program. Furthermore, OpenMP directives may be added one at a time, locally, without restructuring the rest of the program. This enables the programmer to direct his parallelization efforts to only those parts of the program where the benefit is largest.

#### 2.4.2 MIMD clusters: MPI

The Message Passing Interface (MPI, [53]) is the industry standard for parallel scientific computing. It is based on the single-program multiple-data (SPMD) paradigm, where the same program runs on all processors of an MIMD cluster, but each processor operates on different data elements and may follow a different execution path. MPI is available for both C/C++ and Fortran.

MPI provides a library of communication routines that implement *message* passing. This is an inherently distributed-memory approach, where no variables are shared unless explicitly communicated by sending messages. The communication primitives include both point-to-point and collective operations.

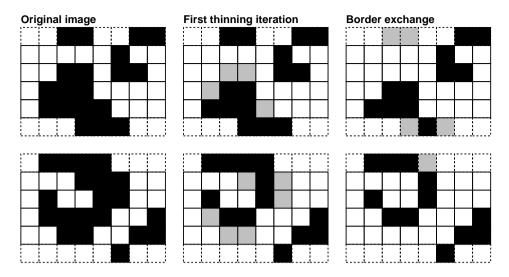

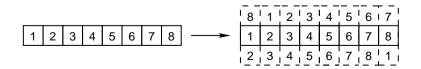

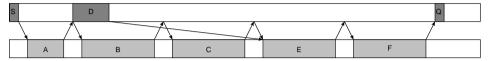

Program 2.3 illustrates this programming paradigm. The same program is run on each processor, but they receive different values for **rank** (third line). These are then used to process different parts of the image; each processor is allocated lines image lines, plus one line of border both above and below (see figure 2.3). After the local computation, a collective communication operation (MPI\_Allreduce) is used to determine whether any pixels changed. Finally, the borders are exchanged, first shifting up, and then down (MPI\_Sendrecv).

Unlike in OpenMP, it is not possible to incrementally parallelize a sequential application. Data distribution is under explicit imperative program control, and must be carefully thought out before writing a parallel program. While this creates a significant hurdle to writing parallel code, the level of control that is possible allows for efficient implementations.

Because MPI is so low-level, and because it is available for so many architectures, it is often used to implement higher-level parallel languages or libraries. It can be seen as the "assembly language" of parallel programming, abstracting over different cluster interconnects. **Program 2.3** MPI program for iterating a neighborhood operation until idempotence. Each processor is allocated a series of image lines to process, and the image borders are exchanged during each iteration.

```

MPI_Init(&arqc, &arqv);

MPI_Comm_size(MPI_COMM_WORLD, & nprocs);

MPI_Comm_rank(MPI_COMM_WORLD, & rank);

lines = \text{HEIGHT}/nprocs;

while (1)

ł

int res, changed=0;

for (y=1; y < lines+1; y++)

/* Code to process local image stripe */

/* Set changed to 1 if any pixel changed */

}

MPI_Allreduce(& changed, & res, 1, MPI_INT, MPI_SUM,

MPI_COMM_WORLD);

if (!res) break;

MPI_Sendrecv(&img[1][0], WIDTH, MPI_INT, prev(rank, nprocs), 0,

& img[lines+1][0], WIDTH, MPI_INT, next(rank, nprocs), 0,

MPI_COMM_WORLD, & status);

MPI_Sendrecv(&img[lines][0], WIDTH, MPI_INT, next(rank, nprocs), 0,

& img[0][0], WIDTH, MPI_INT, prev(rank, nprocs), 0,

MPI_COMM_WORLD, & status);

```

Figure 2.3: Border exchange for 2 processors during an iterative thinning algorithm. We assume a *cyclic* vertical dimension, so that the upper neighbor of the top image line is the bottom image line. Grey values indicate changed pixels; the overlapping borders (dotted lines) are not updated until the communication step.

## 2.4.3 SIMD arrays: 1DC

Both MPI and OpenMP are intended for use on MIMD machines; MPI for distributed-memory systems, and OpenMP for shared-memory ones. They are essentially control-oriented: the system (or programmer) distributes loop iterations. SIMD languages, on the other hand, are data oriented. By introducing *parallel data types*, they expose parallelism while still maintaining a single thread of control.

1DC [86] is an extension of the C language that was designed for use with the NEC IMAP-Vision SIMD processor [55] (the predecessor of the IMAP-CE). It adds a new keyword "separate" to declare that a variable should be distributed over all processors; calculations involving such a variable are done by all processors at the same time. There are also a number of new operations on these variables for accessing neighboring values.

Program 2.4 illustrates some of these operations. It implements bucket processing in the spirit of eq 2.7 using stacks. The : || global or operator is used to check whether any of the stacks are nonzero (this requires a broadcast bus), and the :< and :> operators access the right and left neighbor respectively. 1DC also provides an : [i:] indexing operator to access the value of a single processing element.

New control constructs are introduced to conditionally enable or disable PEs: the code following **mif** is only executed by those PEs for which the condition is true. This may sometimes require a rethinking of the intended algorithm. For example, in program 2.4 it would be natural to add the left neighbor of a processed pixel to the stack. However, in 1DC it is not possible to write something to a **Program 2.4** 1DC code for the stack-based 4-connected propagation of 255 (the seed) over 1 (the mask). Each processor keeps a separate stack, and iteration continues until all stacks are empty. Note the use of indirect addressing to deal with differing stack sizes. This code assumes the border to be zero.

```

#define push(img, y, stk, sp)\

mif (img[y] == 1) { img[y] = 255; stk[sp++] = y; }

void propagate(separate uchar *img)

ł

separate uchar stk[HEIGHT];

separate int sp = 0;

int i;

for (i=0; i < \text{HEIGHT}; i++)

mif (img[i] == 255) stk[sp++] = i;

while (:||sp) /* Any stack is nonempty */

separate int y = 0;

mif (sp)

{

y = stk[--sp];

push(img, y-1, stk, sp); /* Pixels above and below */

push(img, y+1, stk, sp);

}

push(img, y:<1, stk, sp); /* Pixels left and right */</pre>

push(img, y:>1, stk, sp);

}

```

neighboring pixel. Instead, each PE adds the pixel left to the one processed by his right neighbor to his own stack.

1DC (and other SIMD languages, such as XTC [98] and HPF [52]) combine the power of distributed data types with the familiarity of a single thread of control, although care must be taken as to the proper distribution. They vary mainly in the generality of the added operations, and the strictness with which they enforce the distribution. For example, XTC does not allow indirect addressing, while HPF allows non-local access as though the data were local (remote memory accesses will simply incur a penalty).

## 2.4.4 Hardware compilation: Handel-C

Handel-C was developed to provide a familiar environment for creating synchronous FPGA hardware designs. Instead of using a hardware description language such as VHDL [9] or Verilog [63], the programmer writes a C-like program, which is then compiled to the logic gate level. Handel-C is a derivative of the Occam [70] language, which was itself heavily influenced by Hoare's CSP [69].

All expressions in Handel-C are created using combinatorial logic, and may not have side effects; the cycle time of the design therefore depends on the most complex expression in the program. Assignments to variables take one cycle. Parallelism is introduced using the **par** construct, which executes all its statements at the same time. Variables in such constructs may not be written by more than one statement. As assignment takes one cycle, reading a variable in the same **par** construct as it is written to refers to its *previous* value.

Different parallel processes may communicate using FIFO *channels* (chan keyword). This is the only reliable way of communications for statements in different **par** constructs. "!" is the write operator, while "?" reads a value from the channel.

Handel-C also adds a host of features dealing with the bit-widths of integer variables, the placement of arrays (in RAMs or registers), RAM accesses, hardware interfaces, clocking, signals and general issues of targeting a program to a specific device.

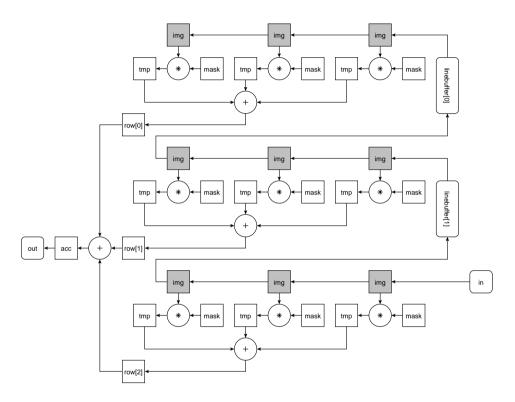

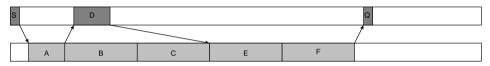

Program 2.5 implements a streaming 3x3 convolution. Each cycle a pixel is read from in, and a result is written to out. The code is pipelined to avoid too many gate delays, so the output value is delayed for a number of cycles. The line buffers are WIDTH-3 bytes long. An illustrative diagram of the resulting hardware can be found in figure 2.4.

It can be seen from this example that Handel-C, although having a C-like syntax, requires a clear vision of what the generated hardware is going to be and a thorough understanding of the parallel semantics to be able to write efficient programs. Especially the explicit pipelining needed to create a fast design calls for a change of perspective.

#### 2.4.5 Discussion

While all the languages we discussed are based on C syntax and imperative semantics, they differ in the kind of parallelism that may be exploited. Even though **Program 2.5** Pipelined 3x3 convolution in Handel-C. The do loop produces one result every cycle, but the convolution of a particular pixel is only available 4 cycles after the bottom-right pixel of its neighborhood is read.

```

macro proc convolve (chan int in, chan int out, int mask[3][3],

chan int linebuffer[2][2])

{

int img[3][3], tmp[3][3], row[3], acc;

do

{

par

ł

img[0][0]

= img[0][1];

img[0][1]

= img[0][2];

linebuffer[0][1]? img[0][2];

linebuffer[0][0] ! img[1][0];

img[1][0]

= img[1][1];

img[1][1]

= img[1][2];

linebuffer[1][1]? img[1][2];

linebuffer[1][0] ! img[2][0];

img[2][0]

= img[2][1];

img[2][1]

= img[2][2];

? img[2][2];

in

par (ii=0; ii < 3; ii++)

par (jj=0; jj < 3; jj++)

tmp[ii][jj] = img[ii][jj] * mask[ii][jj];

row[ii] = tmp[ii][0] + tmp[ii][1] + tmp[ii][2];

}

acc = row[0] + row[1] + row[2];

out ! acc;

}

} while (1);

```

Figure 2.4: Hardware structure generated from the Handel-C code in program 2.5. Each square box is a register, and each circle is an expression. The registers make sure that the execution is pipelined. The gray registers contain the image.

many are retargetable (even 1DC has been implemented for the MMX and SSE SIMD extensions used in desktop processors), each has a specific type of architecture for which it is most suited, and also places firm restrictions on which hardware features must be present. Apart from this, we must deal with the fact that processor vendors generally support only one or at most a few languages.

Analogous to the discussion in section 2.3.5, it is difficult to choose a single language for implementing image processing algorithms. The choice is dependent on the architecture, which in turn depends on the specific algorithm.

# 2.5 Constructing applications

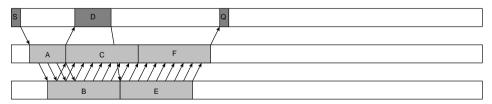

A typical application consists of many of the algorithms described in section 2.3, connected in various ways. Often, the basic access patterns are first combined to yield composite operations. For example, creating a run-length encoding (RLE) of a binary image may be achieved by first replacing the pixels that are different from their left neighbor by their linear index, filtering them out, and finally replacing all elements with the difference to their left neighbor, creating a list of run lengths. See figure 2.5.

As described in section 2.3.5, there is no single processor architecture on which all of these algorithms can be optimally implemented. This means that if the application is diverse enough (which is nearly always the case), it is beneficial to look at architectures containing more than one type of processor. From section 2.4.5 we may infer that this also requires the use of multiple languages.

#### 2.5.1 Heterogeneous multiprocessing

In order to make efficient use of a multiprocessor system, all the processors must be kept busy with meaningful work (as opposed to waiting for data, or bookkeeping). In a heterogeneous system, where each processor has different strengths and weaknesses, this implies the exploitation of task parallelism. Note, however, that in typical image processing applications, the amount of exploitable data parallelism far outweighs the gains reachable by task parallelism. In our view, task parallelism is therefore purely a way to make efficient use of a heterogeneous system, and does not scale to more than a few (data-parallel) processors.

The main issue with the construction of task parallel heterogeneous systems is one of interfacing. These interfaces may be arbitrarily complex. For example, we might envision an SIMD and superscalar cooperating using shared memory and locking, as is the case with the IMAP-CE PCI board. This allows intricate cooperation but is therefore also difficult to code for and debug, especially if different languages are involved.

In signal processing systems, it is common to abstract these interfaces into a *process network*. Each sub algorithm is considered a black-box process, and communicates with other processes over *channels*. The properties of the channels and the rules to which the processes must adhere depend on the particular model of computation (MoC) that is being used. The application developer is now only concerned with a *software interface* that may be implemented in any number of ways. Original imaga

| Ori | Original Image |  |  |  |  |  |  |  |  |  |

|-----|----------------|--|--|--|--|--|--|--|--|--|

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

|     |                |  |  |  |  |  |  |  |  |  |

#### Differing pixel coordinates

|   |   |   |   |   | 5 | 6 |   |

|---|---|---|---|---|---|---|---|

|   |   | 2 |   | 4 | 5 |   | 7 |

|   | 1 |   |   | 4 |   |   |   |

|   | 1 |   |   |   | 5 |   |   |

|   |   |   | 3 |   |   | 6 |   |

|   | 1 | 2 |   | 4 |   | 6 |   |

|   | 1 |   |   |   | 5 |   | 7 |

| 0 |   | 2 |   | 4 |   | 6 |   |

#### Filtered

| 5 | 6 | 2 | 4 | 5 | 7 | 1 | 4 |  |  |  |  |

|---|---|---|---|---|---|---|---|--|--|--|--|

| 1 | 5 | 3 | 6 | 1 | 2 | 4 | 6 |  |  |  |  |

| 1 | 5 | 7 | 0 | 2 | 4 | 6 |   |  |  |  |  |

#### Difference

| 5 | 1 | 4 | 2 | 1 | 2 | 2 | 3 |

|---|---|---|---|---|---|---|---|

| 5 | 4 | 6 | 3 | 3 | 1 | 2 | 2 |

| 3 | 4 | 2 | 1 | 2 | 2 | 2 |   |

Figure 2.5: Run-length encoding as a combination of an anisotropic pixel operation (finding the index), neighborhood to pixel operation (placing the index in the pixels which are different from their left neighbor), filtering, and another neighborhood to pixel operation (replacing the X coordinates with differences). Indices are shown in X coordinates for simplicity.

We have already stated in section 2.1 that our application domain requires fast dynamic reconfiguration based on changes in the environment. In the context of a process network, this means being able to change the sources and destinations of the channels. Typically, such changes do not affect the entire process network, and in order to maintain sufficient task parallelism we would like to continue the execution during reconfigurations.

# 2.6 Discussion

We have shown that there are many processing architectures available for embedded image processing applications. However, not all of these architectures are equally suited for all applications. Depending on which classes of algorithms are used, and which requirements are put on factors such as performance, power consumption and cost, different processors – or combinations of processors – are most appropriate.

It may be clear that it is not always possible to choose the correct architecture beforehand. However, we have seen that the language in which an application is written already restricts the class of architectures which may be efficiently used. Therefore, if we wish to make an unbiased decision about the most suitable architecture, the application cannot be written in any of the languages we discussed.

In this entire chapter we have deliberately made a distinction between algorithms (which exploit data parallelism) and applications (which treat algorithms as black boxes that need to be connected). The reason being that it allowed us to discuss the different properties of each class of algorithms separately. From this point of view, it is not a huge leap to think about using languages which are dependent on the properties of the *algorithm* we wish to implement instead of the *architecture* on which it will be executed, thereby achieving architecture independence.

The next chapter will further detail this concept, and the rest of the thesis

discusses an implementation and how it can be used to make an unbiased decision about the most appropriate architecture for executing a certain application.

## Chapter 3

# Designing architecture-independent applications

There is a wide diversity of embedded image processing architectures. As was discussed in chapter 2, none of these architectures is superior to all the others. Which architecture is the most desirable is highly dependent on the application. In current practice, therefore, the choice of architecture is generally based on an estimate of the performance needed by the application.

However, a large bias is introduced against multiprocessor architectures and processors that are not programmed in a general-purpose language, because of the specialized knowledge that is necessary to effectively exploit their power. Furthermore, if the performance estimate proves incorrect, porting the application to a new architecture (especially if it consists of multiple processors) can be very time-consuming.

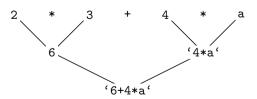

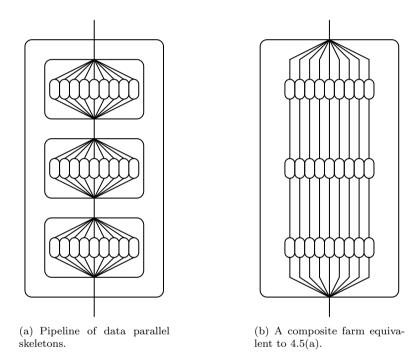

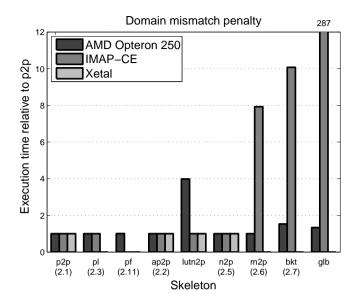

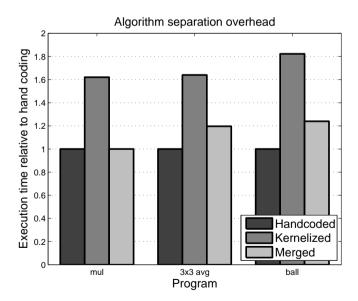

In order to overcome the latter problem, we aim to automatically determine the optimal architecture *after* the program has been written. As such, the application needs to be written in an architecture-independent way, since the architecture is unknown at design-time. As an additional benefit, the programmer does not need specialized architectural knowledge, because this would break the architecture independence. This removes the bias against multiprocessor systems.