### Automated Space/Time Scaling of Streaming Task Graphs on Field-Programmable Gate Arrays

by

Hossein Omidian Savarbaghi

B.Sc. in Computer Engineering, Isfahan University of Technology, 2007M.Sc. in Computer Engineering, Science and Research Branch of IAU, 2011

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **Doctor of Philosophy**

in

### THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES (Electrical and Computer Engineering)

The University of British Columbia (Vancouver)

October 2018

© Hossein Omidian Savarbaghi, 2018

The following individuals certify that they have read, and recommend to the Faculty of Graduate and Postdoctoral Studies for acceptance, the dissertation entitled:

| Automated Space/Time Scaling of Streaming Task Graphs on                       |

|--------------------------------------------------------------------------------|

| Field-Programmable Gate Arrays                                                 |

| submitted by Hossein Omidian Savarbaghi in partial fulfillment of the require- |

| ments for the degree of Doctor of Philosophy                                   |

| in Electrical and Computer Engineering                                         |

#### **Examining Committee:**

#### Guy Lemieux, Electrical and Computer Engineering Supervisor

Prof. Mieszko Lis, Electrical and Computer Engineering Supervisory Committee Member

Prof. Andre Ivanov, Electrical and Computer Engineering University Examiner

> Prof. Alan Hu, Computer Science University Examiner

Prof. Russell Tessier, Electrical and Computer Engineering External Examiner

## Abstract

Parallel computing platforms provide good performance for streaming applications within a limited power budget. However, these platforms can be difficult to program. Moreover, when the size of the computing platform target changes, users must manually reallocate resources and parallelism. This thesis provides a framework to retarget applications described by a Streaming Task Graph (STG) for implementation on different platforms, where the framework can automatically scale the solution size to fit available resource or performance targets.

First, we explore automated space/time scaling for STGs targeting a pipelined coarse-grained architecture. We produce a tool that analyzes the degrees of parallelism in a general stream application and finds possible bottlenecks. We introduce possible optimization strategies for STGs, and two algorithmic approaches: a classical approach based upon Integer Linear Programming (ILP), and a novel heuristic approach which introduces a new optimization and produces better results (using 30% less area) with a shorter run-time.

Second, we explore automated space/time scaling for STGs targeting a finegrained architecture (Field-Programmable Gate Array (FPGA)). We propose a framework on top of a commercial High-Level Synthesis (HLS) tool which adds the ability to automatically meet a defined area budget or target throughput. Within the framework, we use similar ILP and heuristic approaches. The heuristic automatically achieves over 95% of the target area budget on average while improving throughput over the ILP. It can also meet the same throughput targets as the ILP while saving 19% area.

Third, we investigate automated space/time scaling of STGs in a hybrid architecture consisting of a Soft Vector Processor (SVP) and select custom instructions. To achieve higher performance, we investigate using dynamic Partial Reconfiguration (PR) by time-sharing the FPGA resources. The performance results achieve speedups far beyond what a plain SVP can accomplish: an 8-lane SVP achieves a speedup of 5.3 on the Canny-blur application, whereas the PR version is another 3.5 times faster, with a net speedup of 18.5 over the ARM Cortex A9 processor. By increasing the dynamic PR rate beyond what is available today, we also show that a further 5.7 times speedup can be achieved (105.9x speedup versus the Cortex A9).

## Lay Summary

Software applications are often computationally intensive. To maximize the use of resources on a range of hardware platforms with a differing amount of parallel resources and minimize the runtime of software applications as much as possible, engineers need to manually modify and optimize each application for each platform with different resource restrictions or desired performance targets. This process is time consuming and can be prone to error. We propose an approach to automatically explore different ways of implementing an application for a performance target or a resource restriction defined by users.

## Preface

The following publications have been adapted for inclusion in the dissertation:

• Automated Space/Time Scaling of Streaming Task Graph [66]

Published in the 2016 International Workshop on Overlay Architectures for FPGA (OLAF 2016). Authored by Hossein Omidian and Guy Lemieux. Appears in chapter 3.

For this paper, I performed all of the deign methodology and implementation of compiler and simulator. I also did the benchmarking, simulating and evaluation. I also formulated the ILP optimization and proposed and implemented the heuristic optimization approach presented in this paper. Guy Lemieux served in an advisory fashion.

• Exploring Automated Space/Time Tradeoffs for OpenVX Compute Graphs [67].

Published in the 2017 International Conference on Field-Programmable Technology (FPT 2017). Authored by Hossein Omidian and Guy Lemieux. Appears in chapter 4.

I performed all the design methodology, implementation and benchmarking as well as all the simulation and evaluation for this paper. Guy Lemieux served in an advisory fashion.

• JANUS: A Compilation System for Balancing Parallelism and Performance in OpenVX [65].

Presented in the 2018 International Conference on Machine Vision and Information Technology (CMVIT 2018) and published in Journal of Physics: Conference Series. Authored by Hossein Omidian and Guy Lemieux. Appears in chapter 3 and chapter 4.

I performed all the implementation and benchmarking for this paper. Guy Lemieux served in an advisory fashion.

#### • An Accelerated OpenVX Overlay for Pure Software Programmers

Published as a shot paper (poster) in the 2018 International Conference on Field-Programmable Technology (FPT 2018). Authored by Hossein Omidian, Nick Ivanov and Guy Lemieux. Appears in chapter 5.

I performed all the design methodology, implementation and benchmarking as well as all the simulation and evaluation for this paper. Nick Ivanov helped implementing runtime results for SVP and ARM. Guy Lemieux served in an advisory fashion.

# **Table of Contents**

| Ab      | strac                                    | tiii                                                                                                                               |

|---------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| La      | y Sun                                    | nmary v                                                                                                                            |

| Pro     | eface                                    | vi                                                                                                                                 |

| Ta      | ble of                                   | Contents                                                                                                                           |

| Lis     | st of <b>T</b>                           | Tables                                                                                                                             |

| Lis     | st of F                                  | Tigures                                                                                                                            |

| Gl      | ossar                                    | y                                                                                                                                  |

|         |                                          |                                                                                                                                    |

| Ac      | know                                     | ledgments                                                                                                                          |

| Ac<br>1 |                                          | ledgments                                                                                                                          |

|         |                                          |                                                                                                                                    |

|         | Intro                                    | oduction 1                                                                                                                         |

|         | <b>Intro</b><br>1.1                      | Deduction         1           Motivation         1                                                                                 |

|         | <b>Intro</b><br>1.1                      | Deduction       1         Motivation       1         Approach       4                                                              |

|         | <b>Intro</b><br>1.1                      | Deduction       1         Motivation       1         Approach       4         1.2.1       Experimental Architecture Models       5 |

|         | <b>Intro</b><br>1.1<br>1.2               | Deduction1Motivation1Approach11.2.1Experimental Architecture Models1.2.2Experimental Methodology                                   |

|         | <b>Intro</b><br>1.1<br>1.2<br>1.3<br>1.4 | Deduction1Motivation1Approach1Approach41.2.1Experimental Architecture Models51.2.2Experimental Methodology6Contributions8          |

|   | 2.2 | Programming Models                                      |

|---|-----|---------------------------------------------------------|

|   | 2.3 | Reconfigurable Computing Platforms 15                   |

|   |     | 2.3.1 FPGA                                              |

|   |     | 2.3.2 Massively Parallel Processor Array                |

|   | 2.4 | OpenVX                                                  |

|   | 2.5 | Partial Reconfiguration                                 |

| 3 | MPI | PA Space/Time Scaling                                   |

|   | 3.1 | Introduction                                            |

|   | 3.2 | Finding Different Implementations                       |

|   |     | 3.2.1 Intra-Node Optimizer                              |

|   |     | 3.2.2 Inter-Node Optimizer                              |

|   |     | 3.2.3 Example: N-Body Problem 32                        |

|   | 3.3 | Trade-off Finding Formulation and Solutions             |

|   |     | 3.3.1 Integer Linear Programming Algorithm              |

|   |     | 3.3.2 Heuristic Algorithm                               |

|   | 3.4 | Experimental Results                                    |

|   |     | 3.4.1 StreamIt                                          |

|   |     | 3.4.2 JPEG 47                                           |

|   | 3.5 | Summary                                                 |

| 4 | FPG | A Space/Time Scaling 49                                 |

|   | 4.1 | Introduction                                            |

|   | 4.2 | Approach                                                |

|   | 4.3 | Tool Flow for OpenVX-based HLS                          |

|   |     | 4.3.1 OpenVX Programming Model                          |

|   |     | 4.3.2 Finding Different Implementations                 |

|   |     | 4.3.3 CV Accelerator on FPGA                            |

|   |     | 4.3.4 Heavily Parameterized C++-based OpenVX Kernels 59 |

|   |     | 4.3.5 Intra-node Optimizer                              |

|   |     | 4.3.6 Inter-node Optimizer                              |

|   |     | 4.3.7 Trade-off Finding Formulation and Solutions 64    |

|   | 4.4 | Experimental Results                                    |

|   |     |                                                         |

|    | 4.5   | Summa    | у         |        |       | •••   |      |      |     | •   |      | • • | •  |     | •  | • | • | • | • | 71  |

|----|-------|----------|-----------|--------|-------|-------|------|------|-----|-----|------|-----|----|-----|----|---|---|---|---|-----|

| 5  | FPG   | A Over   | ay Space  | /Tim   | e Sca | aling | wit  | h C  | ust | om  | ı Ir | str | uc | tio | ns | • | • | • | • | 73  |

|    | 5.1   | Introdu  | tion      |        |       | •••   |      |      |     |     |      |     |    |     |    |   | • | • |   | 74  |

|    | 5.2   | System   | Overviev  | v      |       |       |      |      |     |     |      |     |    |     |    |   |   | • | • | 78  |

|    | 5.3   | Mappir   | g OpenV   | X Ap   | plica | tions | to I | FPG  | A ( | Ove | erla | ıy. |    |     |    |   |   | • | • | 80  |

|    |       | 5.3.1    | Finding 1 | Differ | ent I | mple  | mer  | tati | ons |     |      |     |    |     |    |   |   | • |   | 80  |

|    |       | 5.3.2    | Executio  | n Tim  | e An  | alys  | is . |      |     |     |      |     |    |     |    |   |   | • |   | 81  |

|    |       | 5.3.3    | Solving ( | he Sp  | ace/  | Гime  | Tra  | deo  | ff  |     |      |     |    |     |    |   |   | • |   | 86  |

|    | 5.4   | Experir  | ental Re  | sults  |       | •••   |      |      |     |     |      |     |    |     |    |   | • |   | • | 87  |

|    | 5.5   | Summa    | у         |        |       | •••   |      |      |     |     |      |     | •  |     | •  |   | • | • | • | 97  |

| 6  | Con   | clusions |           | •••    | •••   | •••   | ••   | ••   | ••• | •   |      | ••• | •  | ••• | •  | • | • | • | • | 98  |

| Bi | bliog | raphy .  |           | • • •  | •••   | ••    | ••   | ••   | ••  | •   | •••  | ••  | •  | ••  | •  | • | • | • | • | 101 |

# **List of Tables**

| Table 3.1 | Different operations with their initiation intervals                | 33 |

|-----------|---------------------------------------------------------------------|----|

| Table 3.2 | Number of different implementations found by the tool for StreamIt  |    |

|           | benchmarks                                                          | 46 |

| Table 3.3 | Implementation library for JPEG encoder                             | 47 |

| Table 3.4 | Heuristic vs ILP for many-core system                               | 47 |

|           |                                                                     |    |

| Table 5.1 | <i>vxMagnitude</i> kernel throughput running on different platforms | 74 |

| Table 5.2 | Some of common patterns used for pre-synthesized node fusion        | 86 |

| Table 5.3 | List of CV kernels                                                  | 89 |

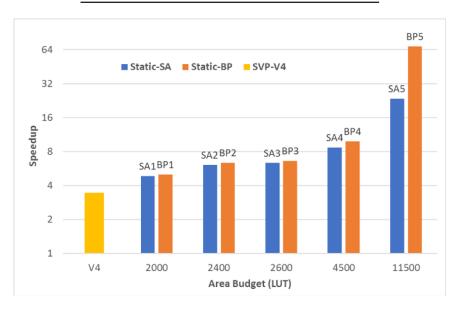

| Table 5.4 | List of CV kernels implemented as VCIs in Figure 5.8                | 91 |

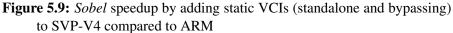

| Table 5.5 | List of CV kernels implemented as VCIs on SVP-V4 in Figure 5.9      | 93 |

# **List of Figures**

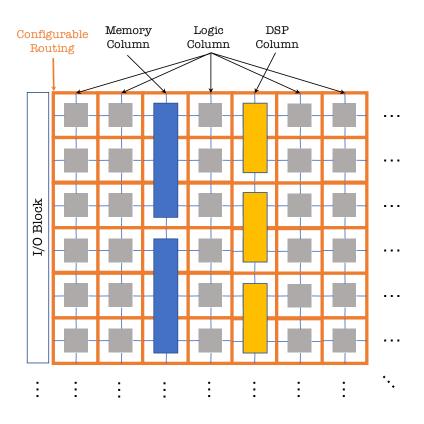

| Figure 2.1  | Example FPGA architecure                                         | 18 |

|-------------|------------------------------------------------------------------|----|

| Figure 2.2  | Ambric <i>bric</i> organization [12]                             | 20 |

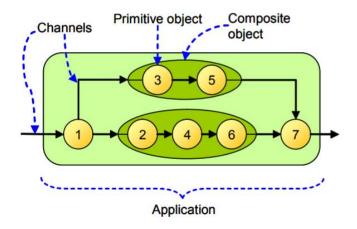

| Figure 2.3  | Structural object programming model [12]                         | 22 |

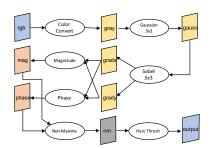

| Figure 2.4  | OpenVX source code for Canny                                     | 23 |

| Figure 2.5  | OpenVX graph for Canny                                           | 23 |

| Figure 2.6  | Area saving by reconfiguring only the currently required accel-  |    |

|             | erator module to the FPGA. Configurations are fetched from       |    |

|             | the module repository at runtime.                                | 24 |

| Figure 2.7  | System acceleration due to partial reconfiguration. By spend-    |    |

|             | ing temporarily more area for each function, the overall latency |    |

|             | is reduced[47]                                                   | 25 |

| Figure 3.1  | Tool flow                                                        | 30 |

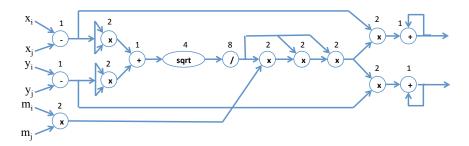

| Figure 3.2  | Pipelined force calculation                                      | 33 |

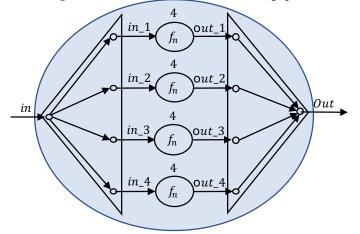

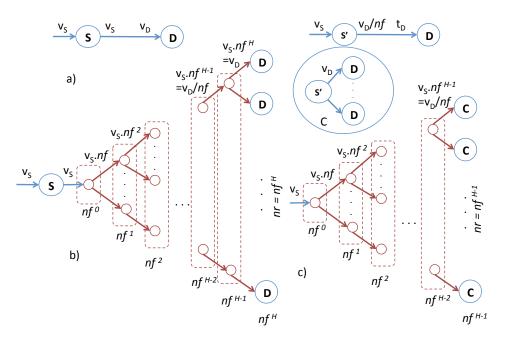

| Figure 3.3  | A node with inverse-throughput=4                                 | 34 |

| Figure 3.4  | Expanding node using replication to improve throughput           | 34 |

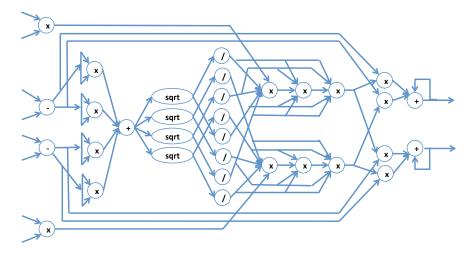

| Figure 3.5  | Expanded force calculation                                       | 35 |

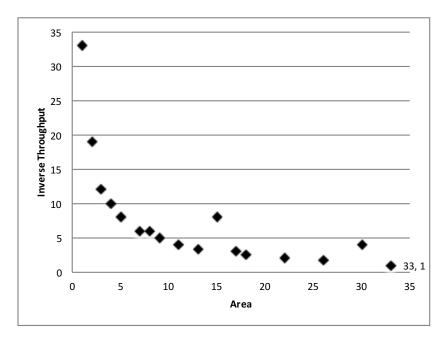

| Figure 3.6  | Inverse-throughput/area relation for different implementations   |    |

|             | of force calculation                                             | 36 |

| Figure 3.7  | Minimum and expected inverse-throughput                          | 38 |

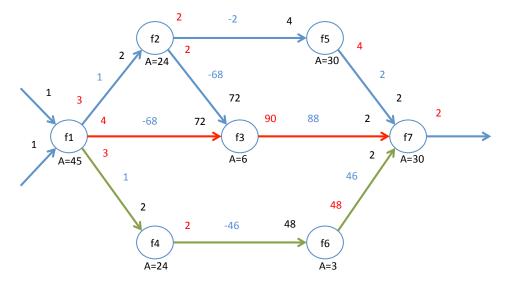

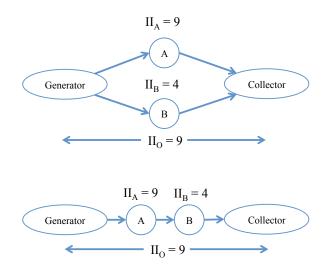

| Figure 3.8  | Throughput analysis example                                      | 39 |

| Figure 3.9  | Throughput propagation and balancing                             | 40 |

| Figure 3.10 | Node combining in Bottleneck Optimizer                           | 42 |

| Figure 3.11 | Node combining in Bottleneck Optimizer                           | 47 |

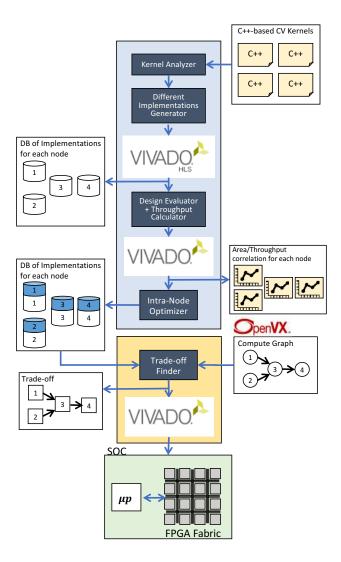

| Figure 4.1  | Tool flow                                                       | 53 |

|-------------|-----------------------------------------------------------------|----|

| Figure 4.2  | OpenVX source code                                              | 54 |

| Figure 4.3  | Sobel graph                                                     | 54 |

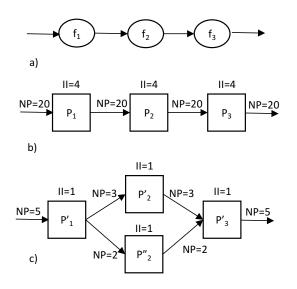

| Figure 4.4  | Two different approaches for satisfying $\Theta = 5$            | 56 |

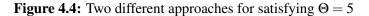

| Figure 4.5  | System view implemented on Xilinx FPGA                          | 57 |

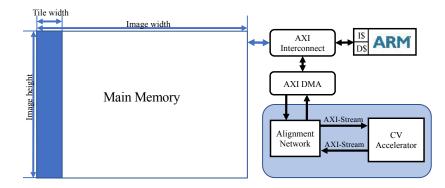

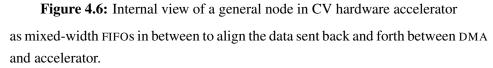

| Figure 4.6  | Internal view of a general node in CV hardware accelerator      | 57 |

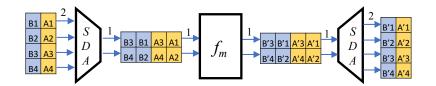

| Figure 4.7  | Pixel2Pixel kernel example, $W_T = 4, W_F = 2$                  | 59 |

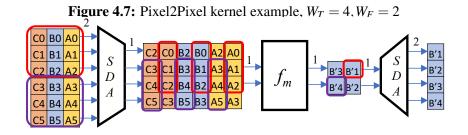

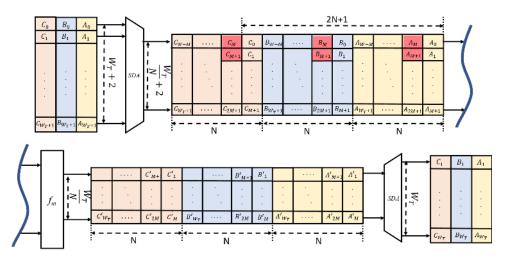

| Figure 4.8  | Window2Pixel kernel example, $W_T = 4, W_F = 2 \dots \dots$     | 59 |

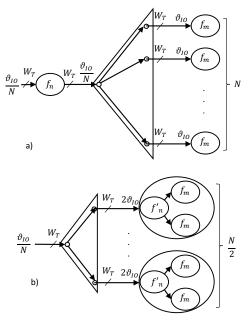

| Figure 4.9  | Window2Pixel kernel                                             | 60 |

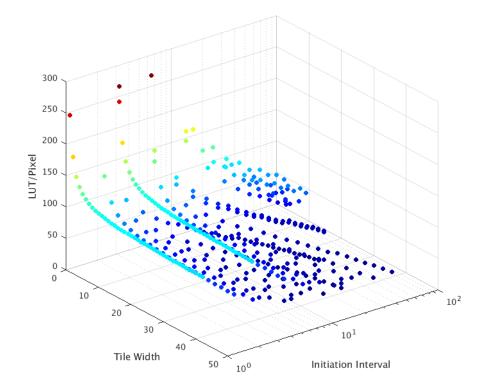

| Figure 4.10 | Area, throughput and tile-width correlation for Gaussian3x3     |    |

|             | kernel                                                          | 61 |

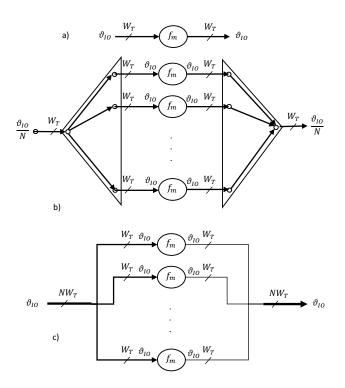

| Figure 4.11 | Pixel2Pixel replication                                         | 62 |

| Figure 4.12 | Window2Pixel replication                                        | 63 |

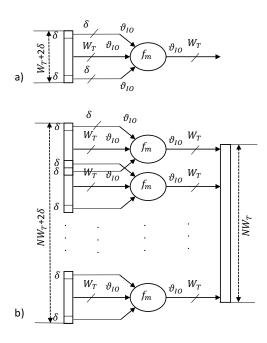

| Figure 4.13 | Node combining                                                  | 63 |

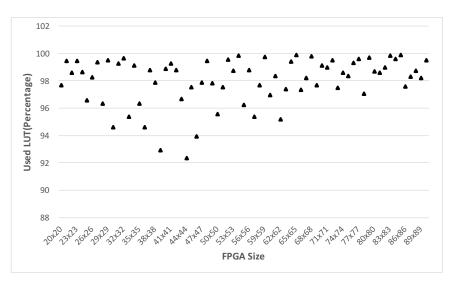

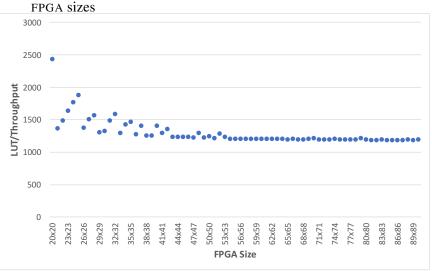

| Figure 4.14 | LUT usage percentage for Sobel implementations on different     |    |

|             | FPGA sizes                                                      | 67 |

| Figure 4.15 | Throughput achieved for Sobel on different FPGA sizes           | 67 |

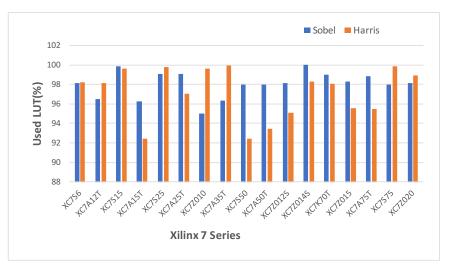

| Figure 4.16 | Percentage of LUT usage for different Xilinx FPGAs              | 68 |

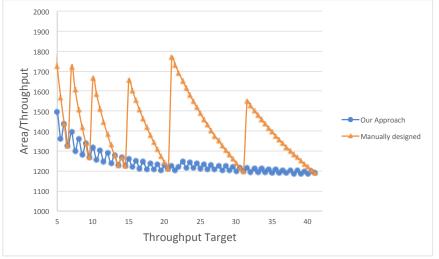

| Figure 4.17 | vxMagnitude Area/Throughput results for different throughput    |    |

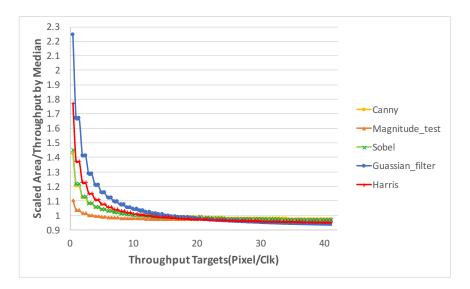

|             | targets                                                         | 68 |

| Figure 4.18 | Area cost results for different throughput targets              | 69 |

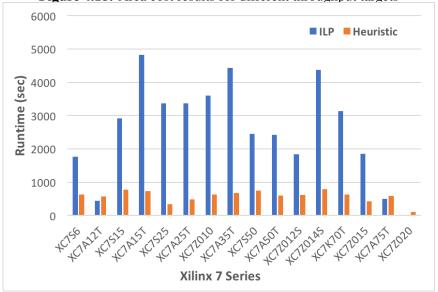

| Figure 4.19 | Heuristic vs ILP runtime speedup for Harris corner detection .  | 69 |

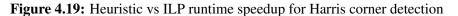

| Figure 4.20 | Area cost results for Harris using Heuristic and ILP approaches | 70 |

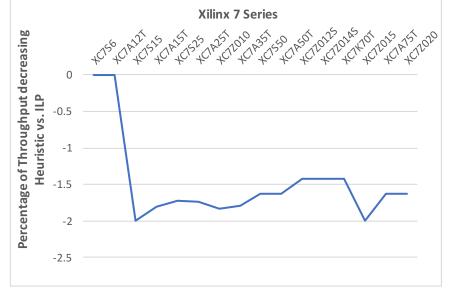

| Figure 4.21 | Heuristic vs ILP throughput results for Harris corner detection | 70 |

| Figure 4.22 | Area/throughput results for implementing Sobel on Xilinx Zed-   |    |

|             | Board                                                           | 71 |

| Figure 5.1  | Running an application on the hybrid system                     | 76 |

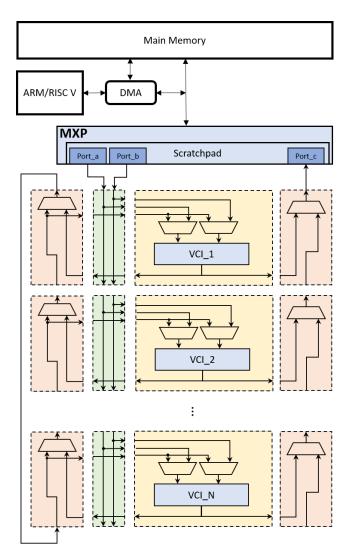

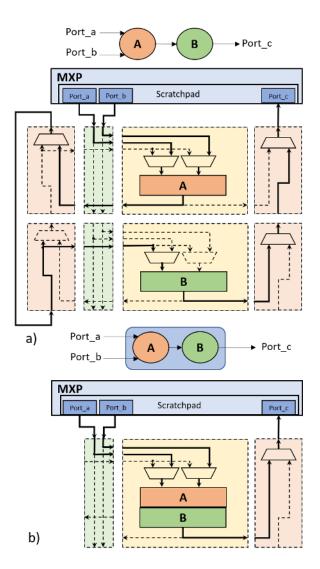

| Figure 5.2  | System overview                                                 | 79 |

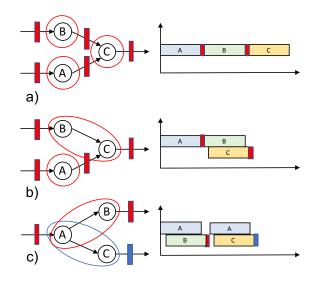

| Figure 5.3  | Node clustering and bypassing the scratchpad                    | 83 |

| Figure 5.4  | VCI chaining versus node fusion                                 | 85 |

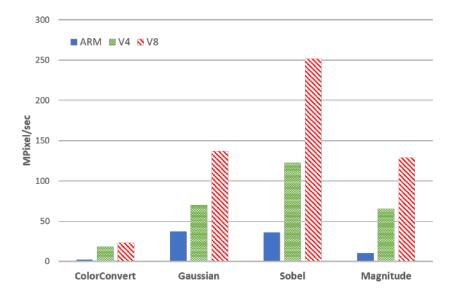

| Figure 5.5  | ARM Cortex-A9 (667MHz) vs SVP-V4 and SVP-V8 (100MHz)            | 88 |

| Figure 5.6  | Graph representation of <i>Sobel</i> application with 6 nodes   | 88 |

| Figure 5.7  | Graph representation of $Canny - Blur$ application with 10 nodes    | 90 |

|-------------|---------------------------------------------------------------------|----|

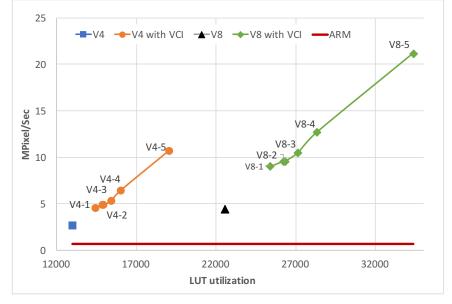

| Figure 5.8  | Throughput vs area for V4 and V8 with/without VCI (Canny-           |    |

|             | <i>Blur</i> Figure 5.7)                                             | 90 |

| Figure 5.9  | Sobel speedup by adding static VCIs (standalone and bypass-         |    |

|             | ing) to SVP-V4 compared to ARM                                      | 91 |

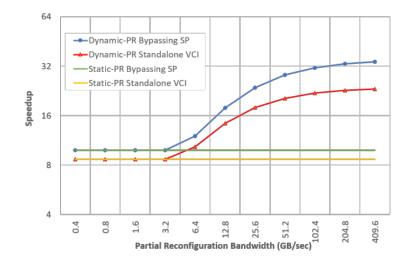

| Figure 5.10 | V4 Dynamic PR and Static PR speedup vs ARM for Sobel                |    |

|             | Application (4500 LUT budget, image size $1920 \times 1080$ )       | 94 |

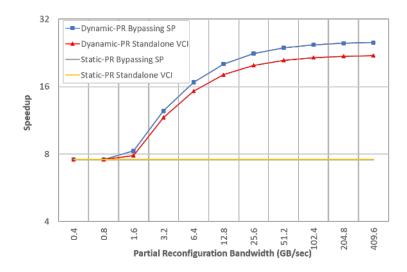

| Figure 5.11 | V4 Dynamic PR and Static PR speedup vs ARM for Canny-               |    |

|             | blur Application (4500 LUT budget, image size $1920 \times 1080$ )  | 95 |

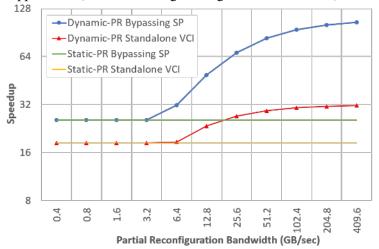

| Figure 5.12 | V8 Dynamic PR and Static PR speedup vs ARM for Canny-               |    |

|             | blur Application (14000 LUT budget, image size $1920 \times 1080$ ) | 95 |

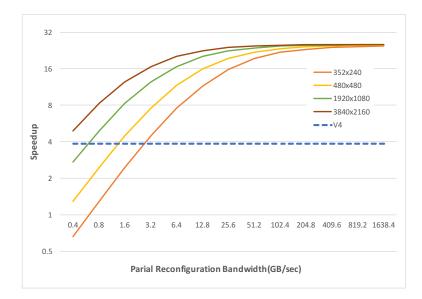

| Figure 5.13 | V4 Dynamic PR speedup vs ARM for Canny-Blur for different           |    |

|             | image sizes (4500 LUT budget)                                       | 96 |

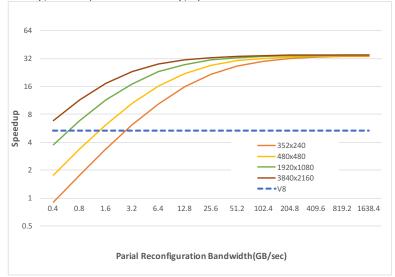

| Figure 5.14 | V8 Dynamic PR speedup vs ARM for Canny-Blur for different           |    |

|             | image sizes (4500 LUT budget)                                       | 96 |

## Glossary

| ALU | Arithmetic Logic Unit |

|-----|-----------------------|

|     |                       |

- Application-Specific Integrated Circuit ASIC

- BRAM Block RAM

- Computer Aided Design CAD

- CLB Configurable Logic Block

- Central Processing Unit CPU

- Computer Vision CV

- DAG Directed Acyclic Graph

- DIG Different Implementation Generator

- DMA Direct Memory Access

- DSP Digital Signal Processing

- First In, First Out FIFO

- FPGA Field-Programmable Gate Array

- GLPK GNU Linear Programming Kit

- Hardware Description Language HDL

- HLL High-Level Language

- HLS High-Level Synthesis

- **HPC** High Performance Computing

- IC Integrated Circuit

- ICAP Internal Configuration Access Port

- ILP Integer Linear Programming

- JPEG Joint Photographic Experts Group

- **KPN** Kahn Processing Network

- LUT Look-Up Table

- MIMD Multiple Instruction, Multiple Data

- MPPA Massively Parallel Processor Array

- MUX Multiplexer

- MXP Matrix Processor

- NOC Network on Chip

- **PE** Processing Element

- **PR** Partial Reconfiguration

- **PRR** Partial Reconfiguration Region

- **RAM** Random Access Memory

- **RTL** Register Transfer Level

- SDA Stream Data Adjuster

- **SDFG** Synchronous Data Flow Graphs

- SDK Software Development Kit

- SIMD Single Instruction, Multiple Data

- SRAM Static RAM

- STG Streaming Task Graph

- SVP Soft Vector Processor

- VCI Vector Custom Instruction

- VLIW Very Long Instruction Word

## Acknowledgments

Baba, thanks for all the support. You taught me how to think differently. Maman, thanks for your unconditional love and helping me through the tough times. Thanks grandpa for inspiring me even after you left us, you always wanted me to improve myself.

Guy, thank you for everything you've done for me. You literally changed my life. I cannot thank you enough. Thanks Kia Bazargan for all the support during my Masters. You are the reason I started my PhD, you are my hero. Thank you Jayme Carvey for everything. You helped me getting my speech confidence back. Aaron, Thanks for helping me starting my research.

Thanks SOC faculties and members. It was a pleasure working with everyone in the SOC lab.

Thanks to NSERC for funding.

## **Chapter 1**

## Introduction

#### **1.1 Motivation**

Applications that are structured around the notion of a "stream" are increasingly important and widespread. One study shows that streaming applications are already consuming most of the cycles on consumer machines, and their use is continuing to grow [71]. Many of these are media and vision applications, and most of them are computationally intensive. There is no doubt that increasingly more complex streaming applications will continue to be introduced, so the demand for higher performance will continue.

Increasing the clock frequency was the simple and traditional way to achieve high performance computing, however, since clock frequency scaling has essentially stopped due to power constraints, an issue known as Dennard scaling [25], computer designers and architects have focused on delivering increased levels of parallelism to improve both performance and performance-per-Watt [68]. Several different approaches have been introduced to address this issue. At one end is coarse-grained parallelism, often implemented through multi-core processors, usually through a high-level language. At the other end is fine-grained parallelism, often implemented through Field-Programmable Gate Array (FPGA) and Application-Specific Integrated Circuit (ASIC) devices by designing hardware-level solutions.

Unfortunately, both coarse-grained and fine-grained parallelism can be chal-

lenging to program. In software, it can be challenging to expose sufficient parallelism in common languages like C, and difficult to describe some types of computation in CUDA or OpenCL, for example. In hardware, Register Transfer Level (RTL) languages such as VHDL and Verilog achieve very good results, but it is not accessible to users without hardware design knowledge. RTL is also very tedious to program, as it requires describing everything on a cycle-by-cycle basis. This makes the above-mentioned approaches either inaccessible to general users or time consuming and hard to implement for more expert users.

In FPGAs, design is made easier through High-Level Synthesis (HLS) tools. These are tools that convert a High-Level Language (HLL) (e.g., Java or C) into RTL (e.g., an Hardware Description Language (HDL) such as Verilog or VHDL). However, they impose their own challenging constraints in writing the HLL and in what can be parallelized [23, 62]. Several industrial and academic HLS tools have been developed to provide an environment for users to describe their application in a HLL such as C/C++ to avoid the difficulty of HDL programming. However, current HLS tools require the user to explicitly manage resources at every stage in their algorithm in order to meet a specified area target or throughput target. This is done by manual control of things such as loop unrolling or pipelining by control pragmas to the code to change how it is synthesized. Moreover, in order to fit a design to different FPGA sizes or achieve a different throughput, users need to alter the design manually, which involves changing the pragmas at best, but in other cases may require more significant rewriting of the source code. Instead, users would benefit from an HLS tool that can automatically investigate different degrees of parallelism, explore space/time tradeoffs and find a suitable implementation for either a throughput target or an area budget.

As another example, coarse-grained streaming architectures such as Ambric's Massively Parallel Processor Array (MPPA) device [13] also require programmming in a HLL. In Ambric's case, Java is used to describe each thread and to explicitly allocate instances, where each thread has streaming input and output ports, and the Astruct custom language is used to connect these ports together [12]. The compiler creates a graph of communicating object-threads which must be placed and routed, much like an FPGA. This can be a great platform for low-power, highperformance computing [40]. However, the Astruct language design does not allow for the creation of dynamic connections; these must be known explicitly at compile-time. Although using object-oriented Java helps make this platform accessible to general users, to achieve high performance, users still need to manually do the resource management by partitioning the application into small atomic objects. This requires the user to learn the Ambric architecture and parallelism methods. Moreover, users need to go through the same process again if they want to increase performance, shrink the size, or target another MPPA with a different architecture and resources.

The approaches described above are specialized for getting high performance from specific hardware targets. In both cases, however, when the number of available resources changes, or the target changes, users need to change the source code of the implementation to satisfy the new constraints. For example, let us go through four different scenarios which need changing these targets. One scenario can be implementing an application on a different platform with different computing resources (from a small embedded device to a big data center). In this case, the user needs to fill up different chips (different area budgets) while maximizing the throughput. A second scenario is when the user has purchased a pre-made design, wants to change/customize one block within the whole design, and there is a limited amount of leftover area available. This needs an area budget. A third scenario can be with a big team of hardware and software developers, where the hardware developers assign a budget (throughput or area) to the software developers to implement their algorithm (e.g., part of a floorplanning process for a whole team). A fourth scenario is when a user wishes to put multiple applications onto a chip, and is trying to pack as many applications (or application instances) as possible; this needs setting throughput targets or area budgets for each instance, but the overall goal is to achieve maximum throughput for the entire chip. A final use-case is that a user may wish to develop several different products or solutions at different price (and performance) points; there is a need for a tools that allow them to more easily scale it to fit different chips or budgets.

This process of retargetting and scaling an application in all the scenarios mentioned above can be time consuming and expensive, and in many cases programmers need extensive skill as well as knowledge of the target platform. There is a need to have general, scalable and flexible approach which allows users to describe streaming applications in a retargetable way.

Streaming applications can be described by a Streaming Task Graph (STG) which are collections of tasks with dependencies between their inputs and outputs. This means they can leverage pipelined architectures. This work focuses on STGs with Directed Acyclic Graph (DAG) topologies. These type of graphs can easily be manipulated to adopt different methods such as pipelining, node replicating and node combining in order to find different degrees of parallelism. This makes an STG suitable model for exploring space/time implementation tradeoffs on pipelined architectures. The scope of automatically exploring space/time tradeoffs for STGs has motivated a considerable amount of research to improve the usability of parallel resources in different pipelined architectures.

The goal of this dissertation is to broaden the overall usability of parallel resources by providing an environment which allows users to automatically explore space/time tradeoffs and find suitable implementations regarding a throughput target or an area budget on a wide range of different pipelined architectures. This can be added to a HLL or to the HLS process to make them more flexible, scalable and more area efficient. Moreover this makes a broad range of pipelined architectures with different granularity and resources accessible to people with limited specialized knowledge. They can easily define an application as a STG in an HLL instead of dealing with using low level RTL or parallel programming languages such as OpenCL. At the same time, we wish to ensure that, by using this approach, the HLS approach is able to automatically find a broad range of different solutions which can each compete with manually optimized implementations. Moreover, the HLS tools need to automatically explore the different solutions and find a suitable implementation based on different defined restrictions or desired targets.

#### 1.2 Approach

As mentioned above, the main goal of this dissertation is to broaden the overall usability of parallel resources in different pipelined architectures by making scaling an implementation easier for general users. This can be done by providing an environment which allows users to define applications as STGs, explore the space/time design space, and find a suitable solution for a defined restriction or a desired target. In other words, we wish to address the automated space/time scaling problem for STGs on different pipelined architectures. We start with addressing this problem targeting a coarse-grained architecture (an MPPA), then target a fine-grained architecture (an FPGA), and finally use the experience learned to target a hybrid architecture with both coarse and fine components. Below, we discuss our approach in greater detail.

#### **1.2.1** Experimental Architecture Models

Our experiments into automated space/time scaling for STGs examine three different parallel architecture models.

First, we examine pipelined coarse-grained parallelism modelled after the Ambric MPPA. Like Ambric, we develop a Java-based compiler tool chain targeting the MPPA. The compiler attempts to find the maximum degrees of parallelism in the stream application, then performs throughput analysis, throughput propagation and looks for possible bottlenecks. We study different STG manipulations to find different implementations in the space/time tradeoff space. We show that a classical Integer Linear Programming (ILP) optimization strategy, based upon prior work, finds a locally optimal design point subject to the given area or throughput target. In addition, we introduce a heuristic approach that runs faster and achieves better results than the ILP approach because it has fewer restrictions. We discuss our solutions to this coarse-grained model in detail in chapter 3.

Second, we examine pipelined fine-grained parallelism available on a Xilinx FPGA. We investigate automating the ability to make space/time tradeoffs in the commercial HLS tool, Xilinx Vivado HLS [43, 96], targeting the FPGA fabric. Since we do not have access to the Xilinx Vivado HLS source code, we propose a framework on top of it which evaluates many ways pragmas can be used to parallelize a STG. To represent STGs, we restrict ourselves to the OpenVX standard which enables the creation of Computer Vision (CV) applications as compute graphs. Our OpenVX HLS system uses heavily parameterized CV kernels as well as multiple optimization approaches to automatically expand and explore the space/time design space. Ultimately, our system finds a suitable fine-grained implementation for a given area or throughput target. We compare both the classical ILP and novel

heuristic optimization approaches, and compare these to manually written implementations. We discuss this model in detail in chapter 4.

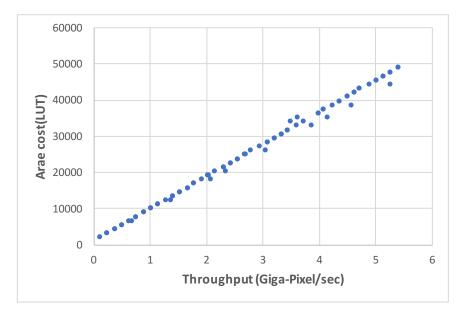

Third, we examine a hybrid approach that uses both coarse-grained and finegrained parallelism. For coarse-grained parallelism, we target a Soft Vector Processor (SVP) architecture implemented in the Xilinx FPGA fabric that streams data through a wide Single Instruction, Multiple Data (SIMD) datapath. For fine-grained parallelism, we target custom instructions implemented in the Xilinx FPGA fabric built using the HLS tool developed earlier. Each Vector Custom Instruction (VCI) offers horizontal parallelism up to the same SIMD width as the SVP, as well as vertical parallelism created with pipelining. Furthermore, additional coarse-grain pipeline parallelism can be created by cascading the output of one VCI to another, producing a chain of VCI operations. The entire VCI chain must respect the twoinput, one-output restriction of a single VCI, and must be of the same SIMD width. To assemble such a system, we rely upon a feature of FPGAs known as Partial Reconfiguration (PR), where a Partial Reconfiguration Region (PRR) can be reconfigured dynamically at run time. The VCI chain is connected to the SVP using a multiplexer network added to the PRR logic. Using this system, we examine the ability to implement OpenVX compute graphs with space/time tradeoffs on an FPGA device with limited resources. This means our approach decides which part of the graph runs on the SVP and which part runs as a VCI or VCI chain. Similar to previous approaches, we use a heuristic approach to leverage runtime optimization techniques which cannot be done as easily in the classical ILP approach. We discuss this model in detail in chapter 5.

#### **1.2.2 Experimental Methodology**

For each of the three experimental architectural models, we use a slightly different methodology for building our tools and collecting results.

In the first model, we develop a Java-based compiler platform similar to the Ambric system. This compiler performs optimization and code generation for our target device which is similar to the Ambric MPPA. However, we did not follow precise instruction encodings, and we did not attempt to run the code on a real Ambric device. Instead, we developed a cycle-accurate simulator which measures execu-

tion time. Benchmarks are written in Java and run on this simulator. Although real Ambric devices are no longer available, similar coarse-grained overlays are being developed on FPGAs such as the GRVI Phalanx [34] as well as an Ambric clone. <sup>1</sup>

In the second model, we use the actual Xilinx tools and devices to produce a real bitstream. In particular, the Vivado HLS tool is used to synthesize C for the FPGA. Benchmarks are written in C using the OpenVX API. We develop a front-end tool which synthesizes an FPGA implementation of an entire OpenVX compute graph. This tool is given an overall area or throughput target; it analyzes the full graph, optionally transforms it, and determines the best space/time tradeoff to meet the target. Each node is an OpenVX compute kernel which is written in C and fully annotated with pragmas for maximum parallelism with Vivado HLS. Our tool determines which pragmas are needed for each kernel instance in the graph to meet the overall target. The final output is a C program which is compiled by the Vivado tools into an FPGA bitstream, where the area usage, clock speed, and throughput metrics can be verified. These graphs use AXI-stream inputs and outputs, allowing them to be easily connected to a full system.

In the third model, we continue to use Xilinx tools and devices together with the VectorBlox Matrix Processor (MXP) SVP, but we produce final results using a performance equation. For each OpenVX compute kernel, we use three implementations: scalar ARM Cortex-A9 code produced using regular C with gcc, vectorized code for the ARM and VectorBlox MXP, and a VCI. The scalar code is only used to produce a performance baseline. The VCI implementations are produced by compiling the OpenVX kernels (from the previous model) for varying SIMD widths, up to the width of the SVP, and compiled into the smallest area required. To save time in this work, we did not implement the multiplexer network required to connect VCI chains into the MXP, nor did we implement the PR control logic. Instead, we model the time required to perform PR based upon performance specifications given by Xilinx for their Internal Configuration Access Port (ICAP) on-chip configuration controller. We are particularly interested making the ICAP controller faster, so we model this speed as a variable, and use performance equations to model the speed of the overall system. With this feasibility study, we have confidence that a

<sup>&</sup>lt;sup>1</sup>Michael Butts, private communication.

working system could be implemented to verify the estimated gains.

#### **1.3** Contributions

The contributions of this dissertation are summarized in the following paragraphs.

• **Chapter 3** is a demonstration of the benefits of automated space/time scaling for STGs mapped onto MPPA overlays rather than manually implementing, scaling and optimizing. We introduce an HLS tool that automatically allows exploring area/throughput tradeoffs for STGs. We improve upon the classical ILP approach by introducing a heuristic approach.

Our approach differs from existing approaches because:

- 1. It automatically investigates partitioning and finding different implementations.

- It combines module selection and replication methods with node combining and splitting in order to automatically find a better area/throughput tradeoff.

- 3. It presents a novel heuristic approach which is more flexible and can find design points not feasible to find with a classical ILP approach.

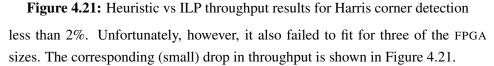

- Chapter 4 is a demonstration of our solution for automating the ability to make space/time tradeoffs in a commercial HLS tool. This leads to a C-to-RTL tool which can automatically explore the space/time problem space for implementing OpenVX applications defined as STGs on FPGAs. Based on our knowledge, this cannot be done with existing C-to-RTL tools. The experiment shows the proposed approach is able to achieve the same performance as manually written implementations and also it finds several more solutions for a variety of different throughput targets which leads to a 30% area reduction. The tool is able to achieve over 95% of the target area budget on average while improving the throughput. The Inter-node Optimizer step of our heuristic is able to hit the same throughput targets while reducing the area cost by 19% on average compared to the ILP approach. In terms of efficient use of parallel resources on the chip, the experiment shows the

tool manages to satisfy different throughput targets while using parallel resources efficiently. For example, it achieves up to 5.5 GigaPixel/sec for the Sobel application on a small Xilinx 7Z020 device.

• Chapter 5 is a demonstration of run-time acceleration using dynamic partial reconfiguration. More specifically, a SVP software system with coarsegrained parallelism is further accelerated using rapid reconfiguration of VCI chains. The experiment shows speedups far beyond what a plain SVP can accomplish. For example, an 8-lane SVP achieves a net speedup of 18 versus the scalar ARM processor for running the *Canny – blur* application. This was achieved by using automated space/time scaling, node clustering and dynamic PR. However, if FPGA vendors can provide a much faster PR rate, a net speedup of 106 is possible.

Our approach differs from existing approaches because:

- 1. It is the first work to explore PR and time-sharing of VCI for speeding up SVP.

- 2. It further improves performance by adding scratchpad bypass with VCI chaining.

- 3. It uses pre-synthesized node fusion of common VCI chains to save area.

#### **1.4 Dissertation Organization**

Chapter 2 presents the background of this dissertation, including the general approach to find different degrees of parallelism in an application and programming models to describe the application. Moreover, it presents the background of different reconfigurable computing platforms we used in this dissertation. Chapter 3 details our implementation of automated space/time scaling of STG on a coarse-grained architecture (MPPA). Chapter 4 details our approach of exploring automated space/time tradeoffs for CV application described as an OpenVX compute graph on a fine-grained architecture (FPGA). Chapter 5 details our implementation of a compilation system which uses run-time reconfiguration to accelerate applications on a hybrid SVP/FPGA architecture.

### **Chapter 2**

## Background

This chapter provides the necessary background information for this dissertation. First, it presents an overview of finding parallelism in a general program to show different transformations that find different degrees of parallelism in a general program. Next, it describes different programming models and their pros and cons. To give the necessary background to understand different reconfigurable computing platforms used in this dissertation, FPGA, MPPA and SVP are introduced. This leads to discussing OpenVX applications on reconfigurable computing platforms. Finally, it discusses the advantages and limitations of partial reconfiguration.

#### 2.1 Finding Parallelism in a General Program

Regardless of what programming model we will use for describing a computational problem, the first step to get better throughput and use parallel resources efficiently is analyzing the program and finding the potential parallelism in it. Getting high performance on a platform with parallel resources requires not only finding parallelism in the program but also minimizing the synchronization overhead because the synchronization process may stall the system; a processing element may have to wait for another processing element to reach the corresponding synchronization point and make data ready. High synchronization frequency generally comes with high levels of data communication between processing elements, which might reduce the performance of the system. As a result, a program with fine-grain syn-

chronization can run on a multi-core system even slower than one processor [56]. It is therefore important to find parallelism that requires minimal synchronization. In other words the final goal is identifying the coarsest granularity of parallelism in a program by finding the largest set of independent computations that can be run by different processing elements in a synchronization-free manner. As mentioned above, it is important to find parallelism before implementing a design. A parallelism finder algorithm analyzes and transforms the program to find all the degrees of parallelism in it.

There have been several studies on program transformation to achieve parallelism and data locality for a program. These transformations are generally limited to loops that use affine functions for representing bounds and array accesses [6].

Below we describe an algorithm that finds the maximum degree of parallelism in a general program with nested loops and affine index expressions for array accesses proposed by Lim et al. [56]. Index expressions are affine if it involves multiplying the loop index variables by constants and adding constants. All the instructions in a program are identified by the loop index values of their surrounding loops, and affine expressions are used to map these loop index values to a partition number. Partition numbers are used for two different purposes, space partitioning and time partitioning. Operations belonging to the same space partition are mapped to the same processing element. On the other hand operations belonging to time partition *i* should execute before those in partition i + 1. We try to find a combination of affine space and time partition mappings that maximizes the degree of parallelism with successively greater degree of synchronization. Several transformations are described in [5, 7, 8, 14, 44, 74, 92]. We can achieve all of the loop-level parallelism with a combination of these transformations such as:

- Fusion

- Fission

- Re-indexing

- Scaling

- Reversal

- Permutation

- Skewing

First we should explain the different forms of parallelism and present our problem statement. A program has k degrees (number of dimensions) of parallelism if  $O(n^k)$  units of computations can be executed in parallel, where n is the number of iterations in a loop. Also we say that different degrees of parallelism in a loop nest exist at the same nesting level if and only if they require the same amount of synchronization. The algorithm described in this section locates all the degrees of parallelism in a program. In other words it finds the maximum degree of parallelism at each level of granularity, starting from coarsest to finest. It also finds opportunities for pipelining. This algorithm assumes there is an infinite number of virtual processors, which means for each independent thread of computation there is a processor. To generate code for a specific number of processing elements in a target architecture we can simply combine multiple of these parallel threads and assign them to the same processing element.

We can describe the overall problem of finding the maximum degree of parallelism into subproblems such as: how to maximize the degree of parallelism that requires 0, O(1), and O(n) amount of synchronization, where *n* is the number of iterations in a loop. By solving each of these problems in turn, the algorithm finds successively more degrees of parallelism at a higher cost of synchronization. The above-mentioned algorithm repeats these steps to find parallelism requiring  $O(n^2), O(n^3), \dots$  synchronization until it finds sufficient parallelism to occupy all of the available hardware. Below we describe these subproblems with more detail.

The subproblem of maximizing synchronization-free parallelism studies the problem of parallelizing an application without allowing any communication or synchronization between processors at all. In other words it is formulated as partitioning the dynamic operations, into the largest number of independent partitions. More specifically, it finds an affine partition mapping for each instruction that maximizes the degree of parallelism. By using a set of space-partition constraints in the affine partition mapping process, we ensure that the processing elements executing operations in different partitions need no synchronization with each other.

The next subproblem is to find parallelism with O(1) synchronization which

means the number of synchronizations must be independent of the number of iterations in a loop. This algorithm divides instructions into a sequence of stages (strongly connected components) and locates synchronization-free parallelism within each stage, then it inserts barrier synchronization before and after each parallelized stage.

Finally, to find parallelism with O(n) synchronization, the algorithm tries to find an affine time partition mapping for each instruction. By using a set of time-partition constraints in the affine mapping process, we ensure that data dependences can be satisfied by executing the partitions sequentially. The goal is to find affine mapping that yields the maximum parallelism among operations within each of the time partitions.

The time partitions and space partitions are similar in many ways and are amenable to the same kind of techniques. The affine form of the Farkas lemma [29] has been used to transform the constraints into linear inequalities. The problem of finding a partition mapping that gives the maximum degree of loop-level and pipelined parallelism while satisfying the space-partition or time-partition constraints reduces to finding the null space of a system of equations. This affine partition mapping can be found easily with a set of simple algorithms.

#### 2.2 **Programming Models**

In this section we go through some programming models and their pros and cons. For more information see the Tessier et al. survey paper [80]. In the early days of reconfigurable computing, there was no overlap between programming general purpose computers and FPGAs or other reconfigurable computing platforms. While procedural languages such as C were generally used to target microprocessors, most FPGAs application designers were still drawing schematics or using HDLs such as Verilog or VHDL. In order to make the reconfigurable computing platforms more accessible for general users without any hardware knowledge, several different programming models have been introduced.

A key goal in the early days was making the programming environment for reconfigurable computing platforms as similar as possible to microprocessor-based systems to make it attractive to general users. Since C was primary language of the day, many C-based programming models were introduced. An initial C-tohardware compiler [89] could do source to source transformation for a simple chain of operations (e.g. add, shift) into HDL code. Wo et al. [91] extended this idea by adding a simple state machine to execute multiple sequential hardware operations (considering data dependencies). To express parallelism better, features were added to the language. Early compilers often relied on users to manually express parallelism and synchronization using "pragma" statements [32]. Modern systems are closer to extracting parallelism from C source code [87] and consider the interface between the synthesized hardware and memory [99]. Application code can also be profiled using software execution [15] to determine target code for hardware acceleration. An important aspect of C-to-FPGA compilers is the estimation of functional unit area and performance [21], an issue made easier by the recent inclusion of hard macro blocks in FPGAs. Moreover, specialized systems have also been introduced to target synthesis with floating-point data types [85]. The amount of research and number of commercial procedural language-to-hardware tools (including Xilinx's Vivado, Calypto Catapult C, and Cadence's C-to-silicon) in recent years, show the demand of targeting users without hardware knowledge.

The similarity between objects in object-oriented programming models and instantiated hardware modules has led to a number of attempts to represent reconfigurable computing as communicating objects. Predictable communication flow and limited communication dependencies are key aspects of these models. This is similar to pipelined implementations. Streaming applications typically have coarse-grain compute objects that communicate with adjacent blocks via buffers or synchronized communication channels. Moreover, results are often sent along predetermined communication paths at predictable rates. This model is suitable for defining a series of signal processing blocks that require minimal control flow or global synchronization. PamBlox focused on the ability to define hierarchies of C++ objects [63] and the use of embedded block memories. These blocks could then be organized into streams. The Streams-C model [31] introduced a series of communicating sequential processes that used small local memories. Streams-C tools were later commercialized into the Impulse-C compiler. Perhaps the most comprehensive stream-based, object-oriented environment to date was the commercial Ambric model [12]. In this model, a Processing Element (PE) can execute one or more user-defined objects that communicate with objects running on other PEs via self-synchronizing, dataflow channels. The commercial Bluespec SystemVerilog [64] hardware synthesis system is also based on the manipulation of objects.

The ability to abstract away details of implementing reconfigurable platforms from the users makes stream-based environments attractive to general users. Several projects have considered the possibility of combining stream-oriented computation with run-time reconfiguration. JHDL [10] allows defining objects whose functionality can be dynamically changed. Development tools allow for evaluation of system performance using both simulation and in-circuit execution. The SCORE project [16] explores swapping stream-based objects on-demand at run-time. Objects can be swapped if the number of objects in an application is too large to fit in the hardware. As a result, the same application could be mapped to hardware platforms of many different sizes.

Data flow models are often used for specifying the behaviour of signal processing and streaming applications as a set of tasks, actors or processes with data and control dependencies. The differences between various dataflow models can be characterized by their expressive power and the availability of techniques for analyzing correctness and performance properties like absence of deadlock and throughput. The Kahn Processing Network (KPN) [30], for example, can capture many of the dynamic aspects of these systems, but evaluating their correctness and performance is in general undecidable. On the other hand, Synchronous Data Flow (SDF) [53] models do allow analysis of many correctness and performance properties but they lack support for expressing any form of dynamism.

#### 2.3 **Reconfigurable Computing Platforms**

#### 2.3.1 FPGA

FPGAs are Integrated Circuits (IC) that are used to implement digital logic functions. In contrast to an ASIC, an FPGA is field-programmable. This means that logic functions must be programmed after the device has been manufactured. On the other hand, an ASIC implements digital logic functions by placing and connecting transistors (layout), which cannot be changed once the chip is fabricated. An FPGA implements digital logic functions with Configurable Logic Block (CLB) modules (typically containing Look-Up Table (LUT)s and flip-flops (FF)) and configurable interconnect between them. Most modern FPGAs can be programmed by loading data into Static RAM (SRAM) cells, which can be reconfigured practically an unlimited number of times [51]. Since normal Integrated Circuit (IC) technology has been used to fabricate SRAM cells, CLBs and routing components on FPGAs, it's reasonable to describe an FPGA as a type of ASIC than emulates other ASICs. Traditionally FPGAs are used for applications such as ASIC prototyping, telecommunications equipment (where low volumes and changing standards make ASICs less attractive), and as interfaces between other ICs ("glue-logic"). In recent years, modern FPGAs have been introduced which provide more performance by adding different hard-core components such as memory blocks and multipliers. This makes them more desirable to run computationally-intensive applications such as computer vision.

#### **Architecture and Design Flow**

A common model of an FPGA is a two-dimensional grid of blocks which are connected by a mesh routing network. The blocks may consist of CLBs or different hard blocks. The hard blocks are frequently used functions that are too expensive to implement as soft logic using CLBs. The most common hard blocks implemented by FPGA vendors are memories (Block RAM (BRAM) modules) and multipliers or other expensive arithmetic and logical functions (Digital Signal Processing (DSP) blocks). FPGA blocks communicate through a configurable routing network, usually using horizontal and routing wires meeting though reconfigurable switch blocks. Additionally, the wires within a routing channel to which a block input or output connect is configurable. The input/output blocks with pins that connect the FPGA to the outside world are also configurable, supporting multiple voltage levels and signalling styles.

FPGA architecture is relatively generic so user logic can be implemented in any set of CLBs. This means there are many possible ways to implement a general digital circuit on an FPGA. This process is not straightforward: the size of modern FPGAs are large, so mapping a large design to a large FPGA is an optimal way is computationally intensive. To appreciate the problem size, consider that the largest Xilinx Virtex UltraScale+ FPGA has 3.8 million programmable logic cells, 94 Mb BRAM and 12,288 DSP slices.

The Computer Aided Design (CAD) flow for translating a design to an FPGA configuration bitstream varies for different vendors. For more information refer to a survey paper by Chen et al [17]. The differences are not important for the purposes of this dissertation, but it is necessary to understand a CAD flow to understand the reasons the traditional FPGA design cycle is long compared to the design cycle for software. RTL synthesis is the process of translating the input circuit as specified by the user to a netlist of Boolean functions and macros such as hard blocks. The Boolean functions get technology-mapped to FPGA programmable logic blocks. Placement then selects locations for each of these units, and routing determines how to configure the communication network to connect logic block inputs and outputs. Finally, assembly creates the bitstream that is used to program the FPGA. Note the term synthesis is often used to refer to the entire process; it includes the time taken by all of the steps. For large FPGAs, synthesis can take hours or even days. This fact makes automatically exploring the space/time tradeoffs and using a library of pre-synthesized bitstream implementations desirable for users.

#### 2.3.2 Massively Parallel Processor Array

A Massively Parallel Processor Array (MPPA) is a type of embedded platform which has an array of hundreds or thousands of processing elements (processors) and memories (Random Access Memory (RAM)). Processors in the system pass work to one another through a reconfigurable interconnect of channels (e.g. First In, First Out (FIFO) buffers). A general MPPA is Multiple Instruction, Multiple Data (MIMD) architecture, often with local distributed memory. Communication between processors is realized in the configurable interconnect. Each processor can often run independently at its own speed. Several different architectures for MPPAs have been introduced by both industry and academia. Companies such as Aspex (Ericsson), Ambric, PicoChip, Intel, IntellaSys, GreenArrays, ASOCS, Tilera, Kalray, Coherent Logix, Tabula, and Adapteva have introduced their MPPAs

Figure 2.1: Example FPGA architecure

in recent years. Academia has introduced some architectures as well such as AsAP [100]. Below we discuss some popular MPPAs.

PicoChip (acquired by Intel) developed a multi-core digital signal processor, the picoArray [27]. This integrates 250-300 individual DSP cores onto a single die (depending on the specific product) and as such it can be described as an MPPA. Each of these cores is a 16-bit processor with Harvard architecture, local memory and 3-way Very Long Instruction Word (VLIW). The picoArray is programmed using a mixture of VHDL [2], ANSI/ISO C and assembly language. The VHDL is used to describe the structure of the overall system, including the relationship between processes, and the signals which connect them together. Each individual process is programmed in conventional C (albeit with additional communication functions), or in assembly language.

The Epiphany architecture consists of a low power, multi-core, scalable, parallel, distributed shared memory embedded system created by Adapteva [1]. The Epiphany IV Network on Chip (NOC) co-processor contains 64 cores (referred to as eCores) organized in a 2D mesh with future versions expected to house up to 4096 eCores. The Epiphany chip can be programmed using C, and has a Software Development Kit (SDK) but users need to manually find and express parallelism.

The Kalray MPPA was introduced as a single-chip many-core processor that integrates 256 user cores and 32 system cores in 28nm CMOS technology [24]. These cores are distributed across 16 compute clusters of 16+1 cores, and 4 quad-core I/O subsystems. Each compute cluster and I/O subsystem owns a private address space, while communication and synchronization between them uses a NOC. This processor targets embedded applications whose programming models fall within the following classes: KPN, as motivated by media processing; single program multiple data (SPMD), traditionally used for numerical kernels; and time-triggered control systems.

University of California, Davis, introduced Asynchronous Array of Simple Processors (AsAP) [100] which contains an array of simple RISC processors with a nine-stage pipeline with small instruction and data memories. Processors communicate only with adjacent processors to permit full-rate communication with low energy. Each processor can receive data from any two neighbors and send data to any combination of its four neighbors. The first generation was introduced with 36 processors. The second generation has 167 processors [86] for DSP, communication, and multimedia workloads. It contains 164 programmable processors with dynamic supply voltage and dynamic clock frequency circuits, three algorithm-specific processors, and three 16 KB shared memories, all clocked by independent oscillators and connected by configurable long-distance-capable links.

#### Ambric

Ambric Inc. was a high performance computing company founded in 2003 in Oregon state, United State of America. Their Am2045 MPPA chips have 336 32-bit RISC-DSP fixed-point processors and run up to 300 MHz. They were designed for high-performance embedded systems such as medical imaging, video, and signal-

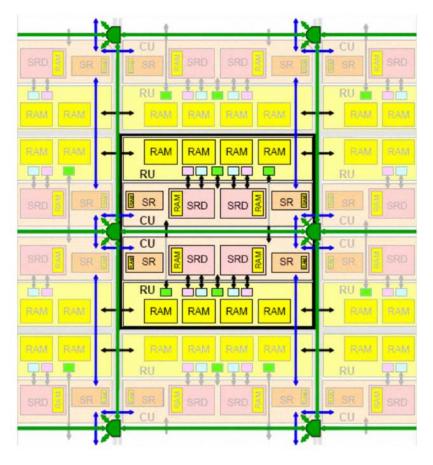

Figure 2.2: Ambric bric organization [12]

processing. The Am2045 is internally organized into a  $5 \times 9$  array of *bric* modules. Figure 2.2 shows one *bric* and its neighbouring *brics*. Each *bric* contains two kinds of 32-bit Central Processing Unit (CPU)s. SRD processors contain 3 Arithmetic Logic Unit (ALU)s and provide math-intensive instructions to support DSP operations. Each SRD processor contains a dedicated 256-word RAM for instructions and data. This memory can be augmented though direct connections to *bric* memory objects. SR processors are lighter weight with only 1 ALU. They contain a dedicated 128-word memory for programs and data but do not have direct connections to memory objects. Each of the two memory objects (RU) in a *bric* is organized as 4 independent RAM banks. Ambric introduced the Am2045 and its software tools in 2007, but fell victim to the 2008 worldwide financial crises [90].

Microprocessor Report gave a 2006 MPR Analysts' Choice Award for innovation for the Ambric architecture "for the design concept and architecture of its massively parallel processor, the AM2045". Although Ambric Inc. is defunct, in 2013 the Ambric architecture received the Top 20 award from the IEEE International Symposium on Field-Programmable Custom Computing Machines, recognizing it as one of the 20 most significant publications in the 20-year history of the conference.

Software written for Ambric devices is based on the Structural Object Programming Model [12]. Each processor is programmed in conventional Java (a strict subset) and/or assembly code (Figure 2.3). A programmed processor or memory is called a primitive object. Objects run independently at their own speeds. They are strictly encapsulated, execute with no side effects on one other, and have no implicitly shared memory. Objects intercommunicate through channels (FIFO-buffers) in hardware. Channels carry both data and control tokens. Channel hardware synchronizes its elements at each end, not at compile time but dynamically as needed at run time. Inter-processor communication and synchronization are combined in these channels. The transfer of a word on a channel is also a synchronization event. Processors, memories, and channel hardware handle their own synchronization transparently, dynamically, and locally, so it doesn't have to be done by the developer or the tools. Channels provide a common hardware-level interface for all objects. This makes it simple for nodes to be assembled into higher-level composite nodes. Because nodes are encapsulated and interact only through channels, composite nodes work the same way as primitive node objects. The developers express object-level parallelism using a block diagram. First the hierarchical structure of primitive and composite objects is defined, connected by channels. Then ordinary sequential software is written to implement the primitive objects. We have used an architecture and programming similar to Ambric in chapter 3.

Figure 2.3: Structural object programming model [12]

# 2.4 OpenVX

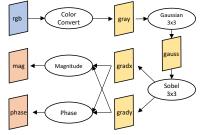

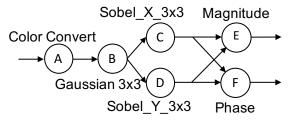

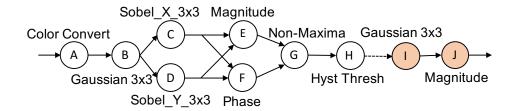

OpenVX is a cross-platform, C-based API standard for Computer Vision applications. OpenVX is a good programming model for embedded systems because it enables performance and power-optimized CV processing to be written in a way that is independent of the target architecture. At the lowest level are OpenVX kernel functions; these are implemented as a library by developers with detailed knowledge of the target accelerator. In OpenVX, CV applications are implemented as a set of these vision kernel functions which communicate through streaming channels. An OpenVX application assembles these kernels, or nodes, into a graph, where edges convey an image passed between kernels. For example, Figure 2.4 shows the OpenVX code for Canny edge detection and Figure 2.5 shows the corresponding graph.

The OpenVX run-time system can break a large image into smaller image tiles, allowing each small tile to pass through the entire graph to completion before writing back to external memory. This provides excellent memory locality and improves both performance and power keeping the tile and its transformations on-chip for as long as possible. Most kernel functions can work with tiles because they need only local information. The few kernel functions that need global information cannot be executed until the full image output of the preceding kernel functions is computed; this can be achieved by cutting the graph at this point and

```

//Canny example

vx_node nodes[] = {

vxColorConvertNode(graph,rgb, gray),

vxGaussian3x3Node(graph,gray,gauss),

vxSobel3x3Node(graph,gauss,gradx,grady),

vxMagnitudeNode(graph,gradx,grady,mag),

vxPhaseNode(graph,gradx,grady,phase),

vxNonMaxima(graph,mag,phase,nm),

vxThreshold(grpah,nm,output)

};

```

Figure 2.4: OpenVX source code for Canny

Figure 2.5: OpenVX graph for Canny

only operating on full images at these cut points.

OpenVX applications can be defined as streaming applications: each stage receives stream of image pixels, rows or frames, processes them, and sends the results as stream of data to the next stage. This means we can describe a computation as compute graphs or Synchronous Data Flow Graphs (SDFG) [53]. Previous studies have shown that custom hardware implementations on FPGAs as well as MPPAs have the potential to dramatically increase the performance/Watt for computationally intensive SDFGs [4, 40].

# 2.5 Partial Reconfiguration

The functionality of an FPGA is created by loading its configuration with a set of bits called a bitstream. In most applications, the entire FPGA is configured at once with a single bitstream. The Partial Reconfiguration (PR) feature available in most SRAM-based FPGAs allow only a portion of the FPGA to be reconfigured, with the rest of the bits staying intact. PR allows changing behaviour of partitions in the FPGA architecture while the remaining logic is still running.

There are two main uses for PR: to save parallel resources and power [42, 69], or to increase performance. There have been several studies on the use of PR. For example [19, 50] demonstrate using partial FPGA reconfiguration for image processing, [20, 83] propose self-adaptive control systems, and [28, 72] investigate the use of PR for High Performance Computing (HPC).

**Figure 2.6:** Area saving by reconfiguring only the currently required accelerator module to the FPGA. Configurations are fetched from the module repository at runtime.

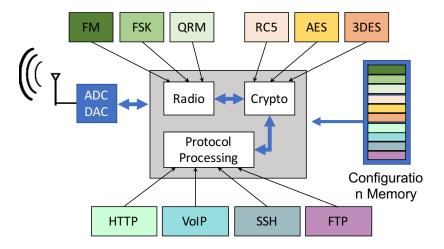

Below we will go through two examples to illustrate the benefits of PR [47]. First, Figure 2.6 shows an adaptive communications device where each of three stages (the front-end radio, the cryptographic accelerator, and the protocol processing engine) can be loaded with three or four different 'algorithms'. The algorithms within each stage are never needed at the same time, i.e., they are mutually exclusive. In a traditional hardware system, all of these algorithms would be implemented at the same time and use considerable area. In a PR system, only enough area for the largest algorithm in each stage needs to be reserved, leading to considerable savings.

There are more potential benefits than only power and area savings. If we can implement a system with a smaller FPGA, we might be able to use a smaller package, which is especially important for mobile applications. In the case of more complex systems that demand multiple FPGAs, PR may reduce the total FPGA count, thereby simplifying PCB and system design. Due to higher integration, we may be able to perform more data processing on-chip, thereby reducing energy for chip-to-chip communications and/or memory writes.

Second, partial reconfiguration can help increase system performance. For example, in Figure 2.7, the PR system on the right can perform more work to achieve

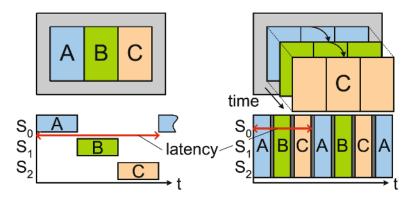

**Figure 2.7:** System acceleration due to partial reconfiguration. By spending temporarily more area for each function, the overall latency is reduced[47].

lower latency and higher throughput than the one on the left (without PR). If we assume that modules A, B and C are executed one after another, the system on the left requires 3 time steps to operate on a single block of data. In contrast, the system on the right can dedicate all resources to step A before using PR to move to step B.

A practical example for this is a hardware accelerated secure SSL connection. In this protocol, we first exchange a session key using asymmetric key exchange. After this, the session key is used by a symmetric cipher for the actual data transfer. Consequently, both steps are executed strictly sequentially and we can dedicate more resources for each step and reduce latency by using PR.

Partial run-time reconfiguration has been an active research field for more than two decades. Much research has been done on increasing the reconfiguration speed and reducing the reconfiguration time. Many different approaches and ideas have been proposed. Hauck introduced the concept of configuration prefetching to swap modules in the background to hide latency and improve the reconfiguration time [36]. Dittmann et al. used reconfiguration port scheduling as well as configuration preemption to improve the efficiency of the reconfiguration interface and to decrease the reconfiguration time [26]. Lange et al. introduced a hyper-reconfigurable architecture to reduce the amount of configuration data needed to perform reconfiguration, which results in lower reconfiguration time and faster reconfiguration speed [52]. Different studies have investigated bitstream (de)compression to reduce the required bandwidth of configuration storage and to reduce the reconfiguration time [39, 48, 54]. Moreover, several different types of reconfiguration controllers, with or without Direct Memory Access (DMA) capabilities, have been investigated to improve the reconfiguration speed and reduce the reconfiguration time [18, 58, 61].

Although FPGA PR rates are relatively low, it is possible to obtain increased performance. For example, Xilinx FPGAs provides 400MByte/sec configuration speed with its on-chip ICAP controller ICAP. Hansen et al. showed it possible to achieve 2.2GByte/sec with existing Xilinx FPGAs [35] by overclocking the ICAP controller. In addition, other studies have suggested different architectures to improve PR time. For example, Trimberger et al. proposed a time-multiplexed FPGA architecture with a 33GByte/sec reconfiguration rate [84]. While faster reconfiguration times are possible, FPGA vendors have not yet seen sufficient need or demand to provide this feature.

# **Chapter 3**

# **MPPA Space/Time Scaling**

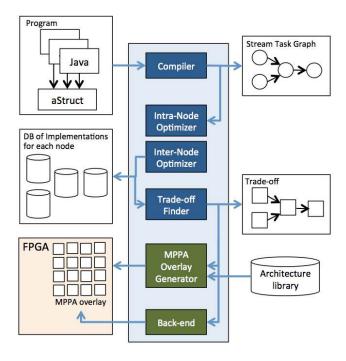

In this chapter, we automate space/time scaling for STGs by developing a Javabased compilation tool chain targeting a pipelined coarse-grained architecture that is very similar to the Ambric MPPA chip architecture. Similar to the Ambric tools, our compiler accepts input written in a subset of Java. Unlike the Ambric tools, our compiler analyzes the parallelism internal to each node and evaluates the throughput and area of several possible implementations. After finding different implementations for each node, it then analyzes the full graph for bottlenecks or excess compute capacity, and selects an implementation for each node while either minimizing area (for a fixed throughput target), or maximizing throughput (for a fixed area target). To find a better area/throughput tradeoff, we use node combining and splitting in the graph. We present two optimization approaches, a formal ILP formulation based on prior work and a novel heuristic solution. Results show that the heuristic is more flexible and can find design points that are computationally infeasible to find using the ILP, thereby achieving superior results with a faster runtime.

# 3.1 Introduction

In this chapter, we will investigate whether an array of ALUs or very lightweight processors, described best as a massively parallel processor array or MPPA, can achieve sufficient levels of performance, and make design entry sufficiently easy, to make them an interesting alternative to more traditional design methods for running STGs. Moreover, we propose a novel approach to automatically explore space/time tradeoffs that can produce different optimized implementations for different throughput targets or different area budgets.

To explore the MPPA as an alternative target, we need a programming model and a tool flow that can compile algorithms into the target and use parallel resources efficiently. To make an MPPA a truly high performance platform, the programming model should support some of the strengths of FPGAs, especially pipelined parallelism. This led us to start with the explicit streaming model and architecture that was defined by Ambric [12, 13].