## Automatic Instrumentation of Embedded Software for High Level Hardware/Software Co-Simulation

## Aimen Bouchhima, Patrice Gerin and Frédéric Pétrot

System-Level Synthesis Group TIMA Laboratory 46, Av Félix Viallet, 38031 Grenoble, France

january 21st 2009

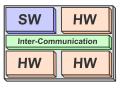

## The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

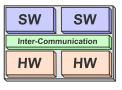

## The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

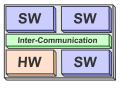

## The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

## The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

## The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

Achieve easily usable computational power

## Overriding challenges

- Validation and debug

- System level architecture exploration: SW deployment, communication implementation

## The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

Achieve easily usable computational power

## Overriding challenges

- Validation and debug

- System level architecture exploration: SW deployment, communication implementation

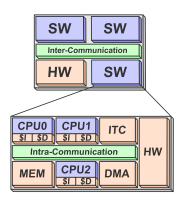

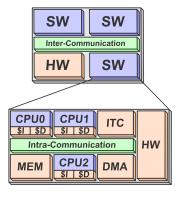

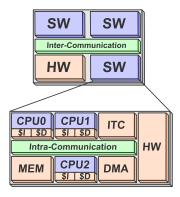

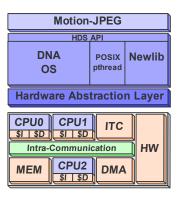

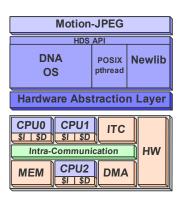

## Focus of this work: Software Node

• Hardware: The processor subsystem

### The Trends

Software-centric architectures

- Exploit parallelism at application task level

- Benefit from software flexibility

Multiple Processors per SW node

Achieve easily usable computational power

## Overriding challenges

- Validation and debug

- System level architecture exploration: SW deployment, communication implementation

## Focus of this work: Software Node

- Hardware: The processor subsystem

- Software: The layered software stack

## Classical approaches

Cycle Accurate co-simulation environment

- Cross compiled embedded software

- Interpreted and executed by ISSs

- Accurate but slow

TLM based co-simulation environment

- Abstraction of the hardware in TLM

- Software still interpreted by ISSs

## Classical approaches

Cycle Accurate co-simulation environment

- Cross compiled embedded software

- Interpreted and executed by ISSs

- Accurate but slow

TLM based co-simulation environment

- Abstraction of the hardware in TLM

- Software still interpreted by ISSs

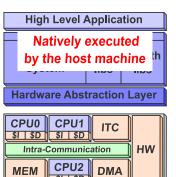

## Native HW/SW co-simulation approaches

- Software is executed:

- By the host machine:

i.e. the processor running the simulation

## Classical approaches

Cycle Accurate co-simulation environment

- Cross compiled embedded software

- Interpreted and executed by ISSs

- Accurate but slow

TLM based co-simulation environment

- Abstraction of the hardware in TLM

- Software still interpreted by ISSs

## Native HW/SW co-simulation approaches

- Software is executed:

- By the host machine:

i.e. the processor running the simulation

- 2 On a simulation model of the hardware dependant part

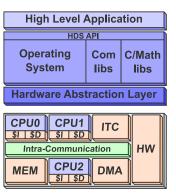

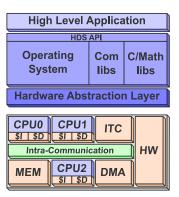

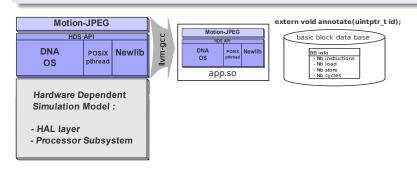

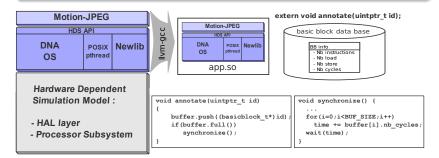

## Natively executed by the host machine

Hardware Dependent Simulation Model :

- HAL layer

- Processor Subsystem

## Classical approaches

Cycle Accurate co-simulation environment

- Cross compiled embedded software

- Interpreted and executed by ISSs

- Accurate but slow

TLM based co-simulation environment

- Abstraction of the hardware in TLM

- Software still interpreted by ISSs

## Native HW/SW co-simulation approaches

- Software is executed:

- By the host machine:

i.e. the processor running the simulation

- On a simulation model of the hardware dependant part

- Considerable speedup

- Functional validation of the whole system

## Natively executed by the host machine the Hardware Dependent

Simulation Model :

- HAL layer

- Processor Subsystem

## Few or no timing information

- Software executes atomically in zero time

- Allows only functional validation

- Annotations must be introduced in software code to enable time modeling

## Performance of software depends on two orthogonal factors

- The software itself depends on

- Sequence and type of executed instructions

- The executed control flow graph

- The underlying hardware depends on

- Caches, access latencies,

- Other processors, ...

- In this work we focus on the software source of dependency.

- The hardware aspects have been addressed in previous works [1,2]

<sup>[1]</sup> P. Gerin et al., "Flexible and executable HW/SW interface modeling for MPSOC design using SystemC", ASPDAC'07

<sup>[2]</sup> P. Gerin et al., "Efficient Implementation of Native Software Simulation for MPSoC", DATE'08

## Objectives & Contributions

## Objectives: Bring native execution closer to target execution

- Provide information of the executed target instructions in native execution

- That reflects closely:

- The execution flow on the target processor

- The performance of the instruction execution on the target processor

## Contributions: A compiler based annotation technique

- Specific to native simulation approaches

- Fully automated and accurate

## Outline

- Introduction

- Basic Concepts

- Proposed Approach

- Experimentations

- **6** Conclusions and Perspectives

## Outline

- Introduction

- Basic Concepts

- Proposed Approach

- Experimentations

- **6** Conclusions and Perspectives

## Execution time approach

- Follow the execution control flow of the target program

- Annotate at basic block level

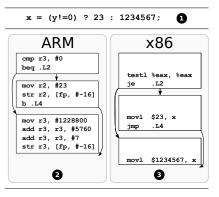

## Execution time approach

- Follow the execution control flow of the target program

- Annotate at basic block level

x = (y!=0) ? 23 : 1234567;

## Basic concepts

A software source code

## Execution time approach

- Follow the execution control flow of the target program

- Annotate at basic block level

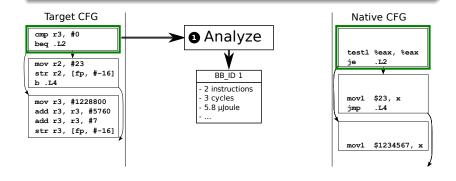

## Basic concepts

- A software source code

- The target object CFG (ARM)

x = (y!=0) ? 23 : 1234567;

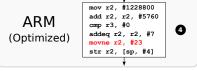

# ARM cmp r3, #0 beq .L2 mov r2, #23 str r2, [fp, #-16] b .L4 mov r3, #1228800 add r3, r3, #5760 add r3, r3, #7 str r3, [fp, #-16]

0

## Execution time approach

- Follow the execution control flow of the target program

- Annotate at basic block level

## Basic concepts

- A software source code

- The target object CFG (ARM)

- The host object CFG (x86) Not relevant for estimation,  $x86 \neq ARM$

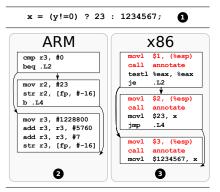

## Execution time approach

- Follow the execution control flow of the target program

- Annotate at basic block level

## Basic concepts

- A software source code

- The target object CFG (ARM)

- The host object CFG ( $\times$ 86) Not relevant for estimation,  $\times$ 86  $\neq$  *ARM*

- Annotation function call inserted in each basic blocks

- Function argument identifies a corresponding basic block in the target CFG

## Execution time approach

- Follow the execution control flow of the target program

- Annotate at basic block level

## Basic concepts

- A software source code

- The target object CFG (ARM)

- The host object CFG (x86) Not relevant for estimation, x86 ≠ ARM

- Annotation function call inserted in each basic blocks

- Function argument identifies a corresponding basic block in the target CFG

- Assumes a one-to-one mapping between the two CFGs: generally not the case

## Outline

- Introduction

- Basic Concepts

- Proposed Approach

- 4 Experimentations

- **6** Conclusions and Perspectives

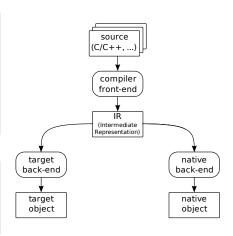

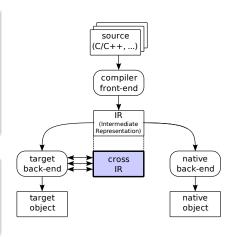

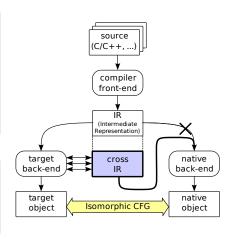

## Main idea: Use the compiler intermediate representation IR

- Host independent (before the host processor back-end)

- Independent from the high level language (C,C++,etc)

- The IR already contains the CFG related informations

- Extend the IR troughout the back-end

- Keep track of processor specific CFG transformations

## Main idea: Use the compiler intermediate representation IR

- Host independent (before the host processor back-end)

- Independent from the high level language (C,C++,etc)

- The IR already contains the CFG related informations

- Extend the IR troughout the back-end

- Keep track of processor specific CFG transformations

## Main idea: Use the compiler intermediate representation IR

- Host independent (before the host processor back-end)

- Independent from the high level language (C,C++,etc)

- The IR already contains the CFG related informations

- Extend the IR troughout the back-end

- Keep track of processor specific CFG transformations

## Main idea: Use the compiler intermediate representation IR

- Host independent (before the host processor back-end)

- Independent from the high level language (C,C++,etc)

- The IR already contains the CFG related informations

- Extend the IR troughout the back-end

- Keep track of processor specific CFG transformations

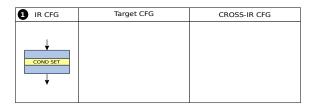

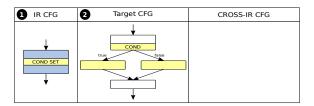

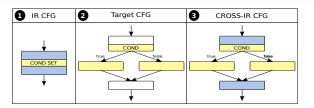

## Cross IR Construction

## Typical case of CFG transformation

- 4 A complex IR instruction e.g. Set On Condition

- Converted in a diamond-like structure for target processor with no support of such instructions

- 3 The Cross IR is modified to reflect the same diamond-like structure

## Native and Target CGF are isomorphic

## Typical case of CFG transformation

- 4 A complex IR instruction e.g. Set On Condition

- Converted in a diamond-like structure for target processor with no support of such instructions

- The Cross IR is modified to reflect the same diamond-like structure

## Native and Target CGF are isomorphic

## Typical case of CFG transformation

- 4 A complex IR instruction e.g. Set On Condition

- Converted in a diamond-like structure for target processor with no support of such instructions

- The Cross IR is modified to reflect the same diamond-like structure

Native and Target CGF are isomorphic

# Target CFG cmp r3, #0 beq .L2 mov r2, #23 str r2, [fp, #-16] b .L4 mov r3, #1228800 add r3, r3, #5760 add r3, r3, #7 str r3, [fp, #-16]

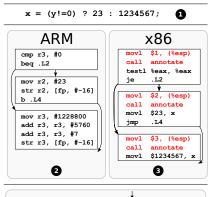

## For each cross-IR basic blocks:

## Target CFG

## Native CFG

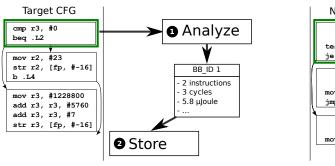

## For each cross-IR basic blocks:

Analyze statically the corresponding target basic block i.e. number/type of instructions, estimated number of cycles

## For each cross-IR basic blocks:

- Analyze statically the corresponding target basic block i.e. number/type of instructions, estimated number of cycles

- 2 Store informations (memory, file,...) and identify the basic block

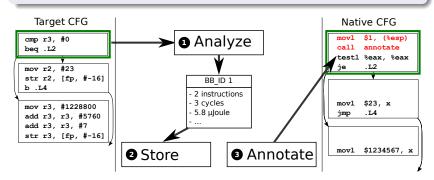

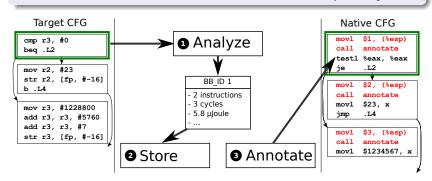

## For each cross-IR basic blocks:

- Analyze statically the corresponding target basic block i.e. number/type of instructions, estimated number of cycles

- 2 Store informations (memory, file,...) and identify the basic block

- 3 Annotation call insertion with basic block identifier as only one argument

## For each cross-IR basic blocks:

- Analyze statically the corresponding target basic block i.e. number/type of instructions, estimated number of cycles

- 2 Store informations (memory, file,...) and identify the basic block

- 3 Annotation call insertion with basic block identifier as only one argument

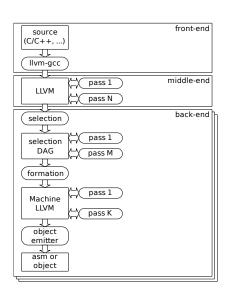

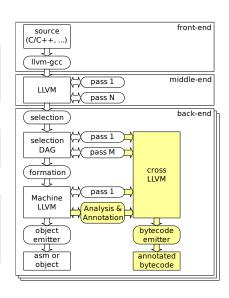

# Implementation In LLVM

#### The Low Level Virtual Machine is

- An open source compiler infrastructure

- An intermediate representation

# Architecture organization

- middle-end: transformation and optimization

- front-end: a port of GCC to the LLVM ISA

- back-end: processor specific

Machine-LLVM representation

## Implementation In LLVM

#### The Low Level Virtual Machine is

- An open source compiler infrastructure

- An intermediate representation

# source (C/C++,...) | Ilvm-gcc | middle-end

# Architecture organization

- middle-end: transformation and optimization

- front-end: a port of GCC to the LLVM ISA

- back-end: processor specific Machine-LLVM representation

#### The Low Level Virtual Machine is

- An open source compiler infrastructure

- An intermediate representation

# Architecture organization

- middle-end: transformation and optimization

- front-end: a port of GCC to the LLVM ISA

- back-end: processor specific

Machine-LLVM representation

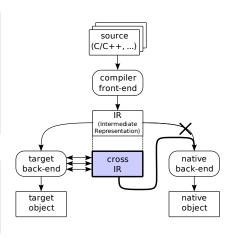

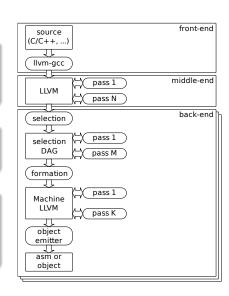

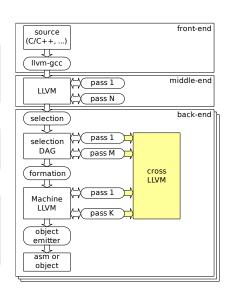

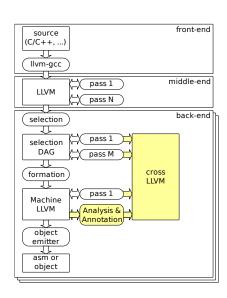

#### LLVM CFG maintained during back-end

Transformations in the target CFG are reflected to the LLVM CFG until the last pass.

#### Annotation pass

Analysis and annotation take place at the end of the back-end

## Output

#### LLVM CFG maintained during back-end

Transformations in the target CFG are reflected to the LLVM CFG until the last pass.

#### Annotation pass

Analysis and annotation take place at the end of the back-end

## Output

#### LLVM CFG maintained during back-end

Transformations in the target CFG are reflected to the LLVM CFG until the last pass.

#### Annotation pass

Analysis and annotation take place at the end of the back-end

## Output

#### LLVM CFG maintained during back-end

Transformations in the target CFG are reflected to the LLVM CFG until the last pass.

#### Annotation pass

Analysis and annotation take place at the end of the back-end

## Output

# Approach Limitations

#### Limitations

- Processor specific implementation in assembly language

- Hand optimized performance critical algorithms

- Compilers back-end builtin functions

- Binary object format libraries not handled by this approach

- Code provided by thrird-party

- Non Open-Source code

#### Possible solution

- Decompilation approaches

- Convert target assembly into compiler IR

- Annotate the obtained IR according to the target code

- Generate host machine code

# Outline

- Introduction

- Basic Concepts

- Proposed Approach

- 4 Experimentations

- **6** Conclusions and Perspectives

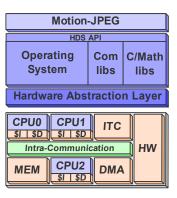

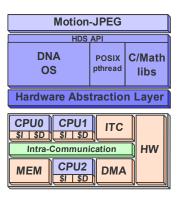

- Application: Multithread version of Motion-IPFG

- Operating System: DNA OS, with SMP support and POSIX pthread library

- C library: Newlib

- Application: Multithread version of Motion-IPFG

- Operating System: DNA OS, with SMP support and POSIX pthread library

- C library: Newlib

- Application: Multithread version of Motion-IPFG

- Operating System: DNA OS, with SMP support and POSIX pthread library

- C library: Newlib

- Application: Multithread version of Motion-IPFG

- Operating System: DNA OS, with SMP support and POSIX pthread library

- C library: Newlib

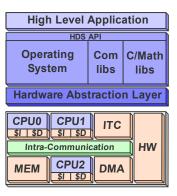

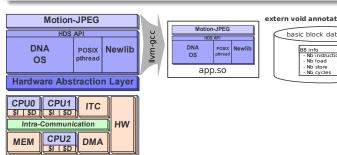

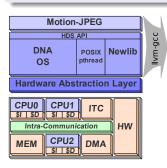

#### Software part

- Application: Multithread version of Motion-JPEG

- Operating System: DNA OS, with SMP support and POSIX pthread library

- C library: Newlib

## Hardware part

• Symmetric Multi-Processor architecture

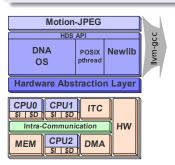

An MPSOC native co-simulation environment: Software part

#### An MPSOC native co-simulation environment: Software part

- Hardware independent part of the software is annotated using Ilvm-gcc

- For arm: Ilvm-gcc -g -Zmllvm"-annotate=arm" -c main.c -o main.o

- For sparc: Ilvm-gcc -g -Zmllvm"-annotate=sparc" -c main.c -o main.o

#### An MPSOC native co-simulation environment: Software part

- Hardware independent part of the software is annotated using Ilvm-gcc

- For arm: Ilvm-gcc -g -Zmllvm"-annotate=arm" -c main.c -o main.o

- For sparc: Ilvm-gcc -g -Zmllvm"-annotate=sparc" -c main.c -o main.o

- 2 Build a dynamic library of the software parts containing:

- Undefined annotate function calls, automatically inserted during compilation

- Basic blocks information directly stored in the library binary image

- ID argument corresponds to a basic block information structure address

extern void annotate(uintptr t id):

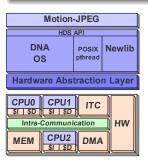

## An MPSOC native co-simulation environment: Hardware part

#### An MPSOC native co-simulation environment: Hardware part

- Processor Sub-System and HAL layer are modeled using SystemC

- Allow validation of the OS and middle ware implementation

- Reflect low level details of a real architecture

#### An MPSOC native co-simulation environment: Hardware part

- Processor Sub-System and HAL layer are modeled using SystemC

- Allow validation of the OS and middle ware implementation

- Reflect low level details of a real architecture

- The annotate function is implemented in the SystemC model

- Called at each basic block execution

- ID are buffered and computed only when needed to speed-up the simulation

- Basic block information is computed to consume simulation time

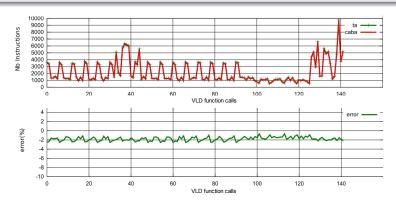

# Experimentation Results

#### Objective: Assess only the annotation accuracy

- Ability to reflect the CFG of the target software execution

- Should not take into account the underlying HW model

- ⇒ Use the number of instruction metric

#### Estimate the number of executed instructions

- On a relevant function:

- Need a function with a large dynamicity

- Variable Length Decoder (VLD) function of the jpeg decoder

#### Does not provide any performance estimation

Number of instruction ≠ execution time

#### Number of executed instruction for each VLD function call

- Cycle accurate bit accurate (caba) provide the reference count

- Less than 3% of error due to not annotated code

The SystemC model of the HAL software layer

- The error is negative or zero when the code is fully annotated

# Experimentation Results

## Simulation Speed-up compared to CABA execution model

- Very dependent on:

- Execution time computation trace dump, software profiling, ...

- The underlying HW model

- From x100 with timing estimation and execution time software profiling

- To x1000 speed-up factor with only execution time estimation.

#### Outline

- Introduction

- Basic Concepts

- Proposed Approach

- 4 Experimentations

- **6** Conclusions and Perspectives

#### A compiled-based approach

- Automatic annotation of embedded software

- Accurate in term of program control flow execution

- The annotation process is clearly separated from the performance estimation

- Performance estimation depend on

- Informations associated with the basic blocks

- The underlying hardware architecture

## Main benefits

- Adapted to high level hardware/software cosimulation approaches

- Not restricted to a particular compiler

# Perspectives & Futur Work

#### Improving analysis of basic blocks

- Increase accuracy

- Pipeline effect

- Instructions dependencies

- e.g. WCET at a BB granularity

- Different information

- Power consumption

#### Tools are needed

- To interprete simulation results

- Annotation technique used to profile target software executed on the host machine

- "Cross profiling"

# Perspectives & Futur Work

#### Improving analysis of basic blocks

- Increase accuracy

- Pipeline effect

- Instructions dependencies

- e.g. WCET at a BB granularity

- Different information

- Power consumption

#### Tools are needed

- To interprete simulation results

- Annotation technique used to profile target software executed on the host machine

- "Cross profiling"

# Perspectives & Futur Work

#### Improving analysis of basic blocks

- Increase accuracy

- Pipeline effect

- Instructions dependencies

- e.g. WCET at a BB granularity

- Different information

- Power consumption

#### Tools are needed

- To interprete simulation results

- Annotation technique used to profile target software executed on the host machine

"Cross profiling"

# Questions

# Patrice.Gerin@imag.fr

System-Level Synthesis Group TIMA Laboratory 46, Av Félix Viallet, 38031 Grenoble, France