## Automatic Task and Data Mapping in Shared Memory Architectures

vorgelegt von

Dipl.-Ing. Matthias Diener geb. in Berlin

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften - Dr.-Ing. -

genehmigte Dissertation

Promotionsausschuss:

| Vorsitzender:         | Prof. Dr. Sebastian Möller                    |

|-----------------------|-----------------------------------------------|

| Stellv. Vorsitzender: | Prof. Dr. Rodolfo Azevedo                     |

| Gutachter:            | Prof. Dr. Hans-Ulrich Heiß                    |

| Gutachter:            | Prof. Dr. Jan Richling                        |

| Gutachter:            | Prof. Dr. Antonio Carlos Schneider Beck Filho |

| Gutachter:            | Prof. Dr. Philippe O. A. Navaux               |

Tag der wissenschaftlichen Aussprache: 28. Oktober 2015

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisors, who have continuously guided and motivated me throughout my research. This thesis would not have been possible without their support.

My thanks also go to all my colleagues and collaborators at the GPPD and KBS research groups, for their comments, discussions and support for my research.

Finally, I am deeply grateful for the encouragement and support of my family during the PhD, as well as in my life in general.

#### ABSTRACT

Reducing the cost of memory accesses, both in terms of performance and energy consumption, is a major challenge in shared-memory architectures. Modern systems have deep and complex memory hierarchies with multiple cache levels and memory controllers, leading to a Non-Uniform Memory Access (NUMA) behavior. In such systems, there are two ways to improve the memory affinity: First, by mapping tasks that share data (communicate) to cores with a shared cache, cache usage and communication performance are improved. Second, by mapping memory pages to memory controllers that perform the most accesses to them and are not overloaded, the average cost of accesses is reduced. We call these two techniques task mapping and data mapping, respectively. For optimal results, task and data mapping need to be performed in an integrated way. Previous work in this area performs the mapping only separately, which limits the gains that can be achieved. Furthermore, most previous mechanisms require expensive operations, such as communication or memory access traces, to perform the mapping, require changes to the hardware or to the parallel application, or use a simple static mapping. These mechanisms can not be considered generic solutions for the mapping problem. In this thesis, we make two contributions to the mapping problem. First, we introduce a set of metrics and a methodology to analyze parallel applications in order to determine their suitability for an improved mapping and to evaluate the possible gains that can be achieved using an optimized mapping. Second, we propose two automatic mechanisms that perform task mapping and combined task/data mapping, respectively, during the execution of a parallel application. These mechanisms work on the operating system level and require no changes to the hardware, the applications themselves or their runtime libraries. An extensive evaluation with parallel applications from multiple benchmark suites as well as real scientific applications shows substantial performance and energy efficiency improvements that are significantly higher than simple mechanisms and previous work, while maintaining a low overhead.

Keywords: Task mapping. Data mapping. Shared memory. Multicore. NUMA.

#### Mapeamento automático de processos e dados em arquiteturas de memória compartilhada

#### RESUMO

Arquiteturas paralelas modernas têm hierarquias de memória complexas, que consistem de vários níveis de memórias cache privadas e compartilhadas, bem como Non-Uniform Memory Access (NUMA) devido a múltiplos controladores de memória por sistema. Um dos grandes desafios dessas arquiteturas é melhorar a localidade e o balanceamento de acessos à memória de tal forma que a latência média de acesso à memória é reduzida. Dessa forma, o desempenho e a eficiência energética de aplicações paralelas podem ser melhorados. Os acessos podem ser melhorados de duas maneiras: (1) processos que acessam dados compartilhados (comunicação entre processos) podem ser alocados em unidades de execução próximas na hierarquia de memória, a fim de melhorar o uso das caches. Esta técnica é chamada de mapeamento de processos. (2) Mapear as páginas de memória que cada processo acessa ao nó NUMA que ele está sendo executado, assim, pode-se reduzir o número de acessos a memórias remotas em arquiteturas NUMA. Essa técnica é conhecida como mapeamento de dados. Para melhores resultados, os mapeamentos de processos e dados precisam ser realizados de forma integrada. Trabalhos anteriores nesta área executam os mapeamentos separadamente, o que limita os ganhos que podem ser alcançados. Além disso, a maioria dos mecanismos anteriores exigem operações caras, como traços de acessos à memória, para realizar o mapeamento, além de exigirem mudanças no hardware ou na aplicação paralela. Estes mecanismos não podem ser considerados soluções genéricas para o problema de mapeamento. Nesta tese, fazemos duas contribuições principais para o problema de mapeamento. Em primeiro lugar, nós introduzimos um conjunto de métricas e uma metodologia para analisar aplicações paralelas, a fim de determinar a sua adequação para um melhor mapeamento e avaliar os possíveis ganhos que podem ser alcançados através desse mapeamento otimizado. Em segundo lugar, propomos um mecanismo que executa o mapeamento de processos e dados online. Este mecanismo funciona no nível do sistema operacional e não requer alterações no hardware, os códigos fonte ou bibliotecas. Uma extensa avaliação com múltiplos conjuntos de carga de trabalho paralelos mostram consideráveis melhorias em desempenho e eficiência energética.

**Palavras-chave:** Mapeamento de processos. Mapeamento de dados. Memória compartilhada. Multicore. NUMA.

#### Automatisches Mapping von Tasks und Daten in Shared Memory Architekturen

#### ZUSAMMENFASSUNG

Moderne parallele Architekturen haben komplexe Speicherhierarchien, die aus mehreren Ebenen von privaten und gemeinsam genutzten Caches, sowie einem Non-Uniform Memory Access (NUMA) Verhalten aufgrund mehrerer Speichercontroller bestehen. Eine der größten Herausforderungen in diesen Architekturen ist die Verbesserung der Lokalität und Balance von Speicherzugriffen, so dass die Latenz der Speicherzugriffe reduziert wird, da dies die Performance und Energieeffizienz von parallelen Anwendungen verbessern kann. Zwei Typen von Verbesserungen existieren: (1) Tasks die auf gemeinsame Daten zugreifen, sollen nah beieinander in der Speicherhierarchie ausgeführt werden, um die Nutzung der Caches zu verbessern. Wir bezeichnen diese Technik als Task Mapping. (2) Speicherseiten sollen den Speichercontrollern zugeordnet werden, von denen die meisten Zugriffe kommen und die nicht überlastet sind, um die durchschnittliche Speicherzugriffszeit zu reduzieren. Wir nennen diese Technik Data Mapping. Für optimale Ergebnisse müssen Task und Data Mapping in integrierter Form durchgeführt werden. Frühere Arbeiten in diesem Bereich führt das Mapping nur getrennt aus, wodurch die Vorteile, die erzielt werden können, begrenzt werden. Außerdem erfordern die meisten früheren Mechanismen teure Operationen um das Mapping durchzuführen, wie etwa Traces der Kommunikation oder von Speicherzugriffen. Andere Arbeiten erfordern Änderungen an der Hardware oder an der parallelen Anwendung, oder erzeugen nur ein einfaches statisches Mapping. Diese Mechanismen können nicht als generische Lösungen für das Mapping-Problem betrachtet werden. In dieser Arbeit präsentieren wir zwei Beiträge für das Mapping-Problem. Zuerst führen wir eine Reihe von Metriken und eine Methodologie zur Bestimmung der Eignung von parallelen Anwendungen für die verschiedenen Arten von Mapping. Das Ziel ist es, die möglichen Gewinne, die durch eine optimiertes Mapping erreicht werden können, vorherzusagen. Zweitens stellen wir zwei Mechanismen vor, die Task und Data Mapping automatisch während der Laufzeit der parallelen Applikation ausführen. Diese Mechanismen funktionieren auf der Betriebssystemebene und erfordern keine Änderungen an der Hardware, den Anwendungen oder deren Laufzeit-Bibliotheken. Eine umfangreiche Auswertung mit einer großen Auswahl paralleler Applikationen zeigen signifikante Verbesserungen der Performance und der Energieeffizienz.

Keywords: Task Mapping. Data Mapping. Shared Memory. Multicore. NUMA.

## LIST OF FIGURES

| Figure 1.1 Comparison of a shared memory architecture and a cluster system              | . 21 |

|-----------------------------------------------------------------------------------------|------|

| Figure 1.2 Scaling of the Intel Xeon processor between 1998 and 2014                    | . 22 |

| Figure 1.3 The impact of memory accesses on performance and energy consumption.         | .23  |

| Figure 1.4 Comparison of UMA and NUMA architectures                                     | . 25 |

| Figure 1.5 Example NUMA architecture with 4 NUMA nodes                                  | . 27 |

| Figure 1.6 Results of the producer/consumer benchmark.                                  | . 28 |

| Figure 1.7 Why task mapping is required for data mapping                                | .29  |

| Figure 1.8 Classification of the memory access behavior of parallel applications        | . 30 |

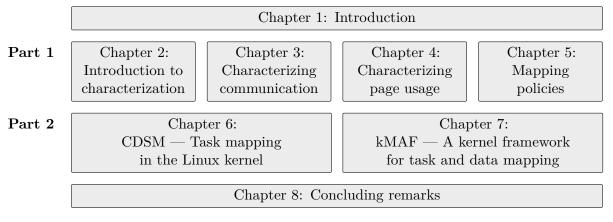

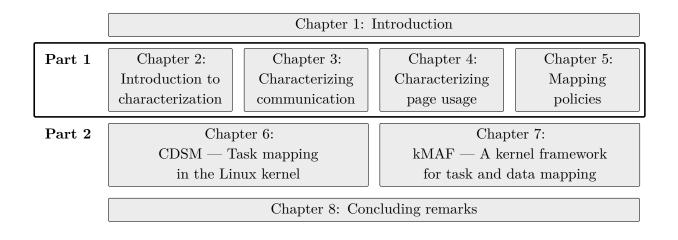

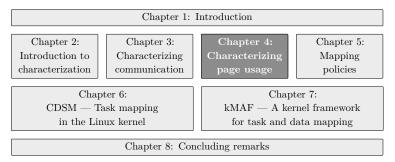

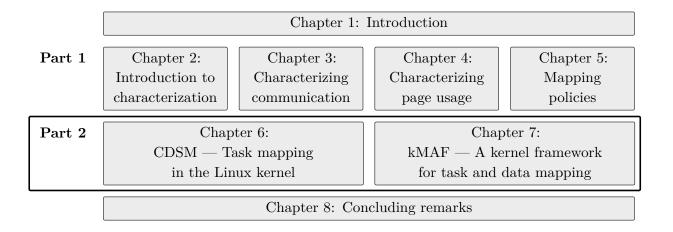

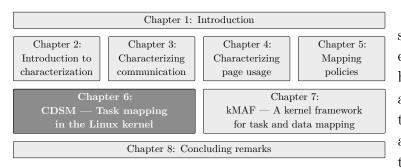

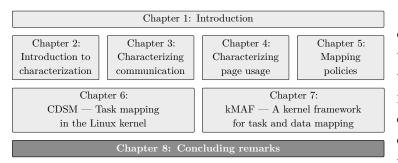

| Figure 1.9 Overview of the chapters of the thesis                                       | . 34 |

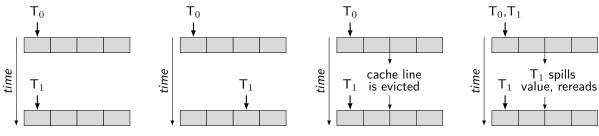

| Figure 3.1 Explicit and implicit communication between two tasks                        |      |

| Figure 3.2 Comparison between true and false communication                              | . 47 |

| Figure 3.3 Representations of undirected communication behavior                         | . 49 |

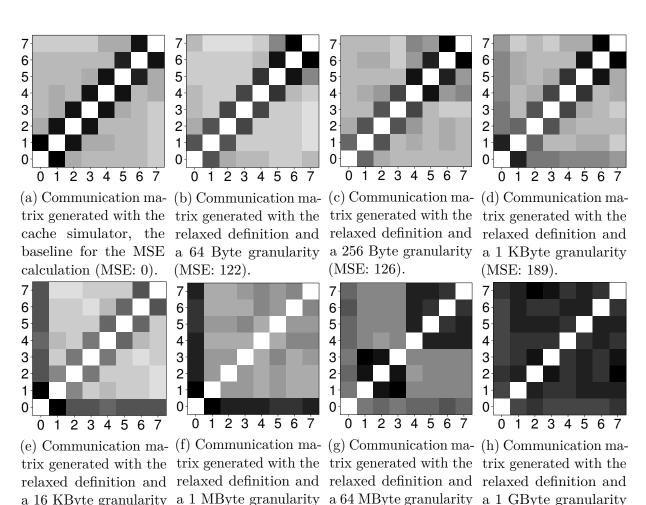

| Figure 3.4 Communication matrices of the accurate and relaxed definitions               | . 52 |

| Figure 3.5 Common types of communication patterns.                                      | . 54 |

| Figure 3.5 Common types of communication patterns (ctd.).                               | . 55 |

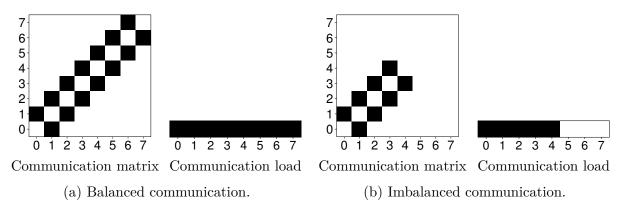

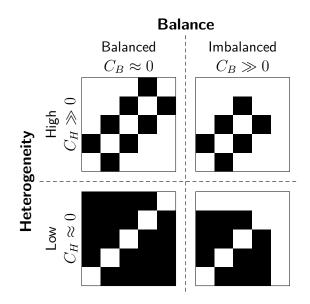

| Figure 3.6 Locality and balance of communication.                                       |      |

| Figure 3.7 Communication balance.                                                       |      |

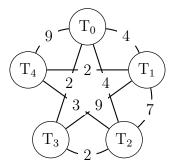

| Figure 3.8 Comparison of the structure of communication.                                |      |

| Figure 3.9 Inputs for the task mapping example                                          |      |

| Figure 3.10 Output of the task mapping example with various algorithms                  | .65  |

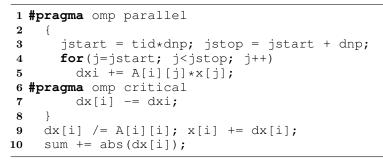

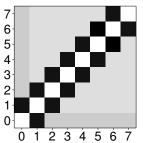

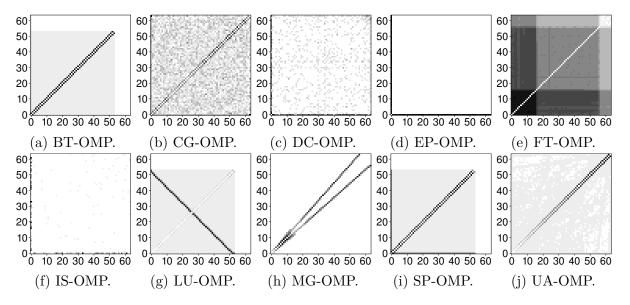

| Figure 3.11 Communication matrices of the NAS-OMP benchmarks                            |      |

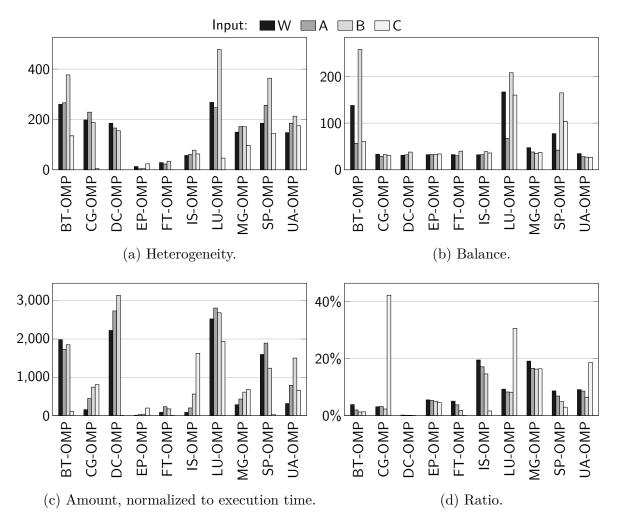

| Figure 3.12 Communication characteristics of the NAS-OMP benchmarks.                    | . 67 |

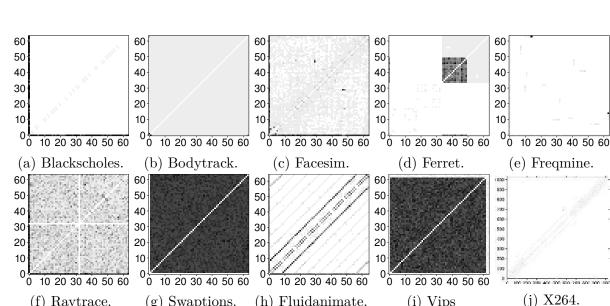

| Figure 3.13 Communication matrices of the PARSEC benchmarks                             |      |

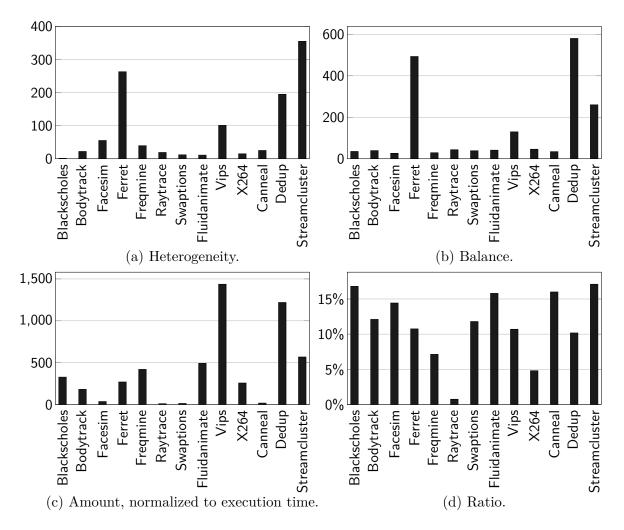

| Figure 3.14 Communication characteristics of the PARSEC benchmarks                      |      |

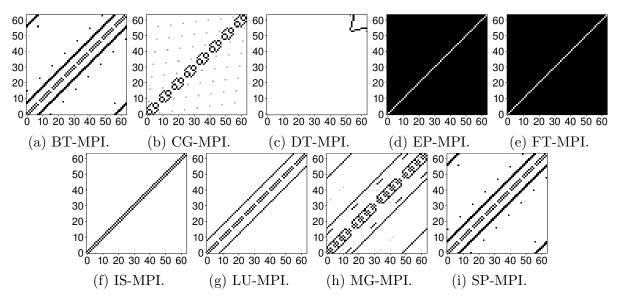

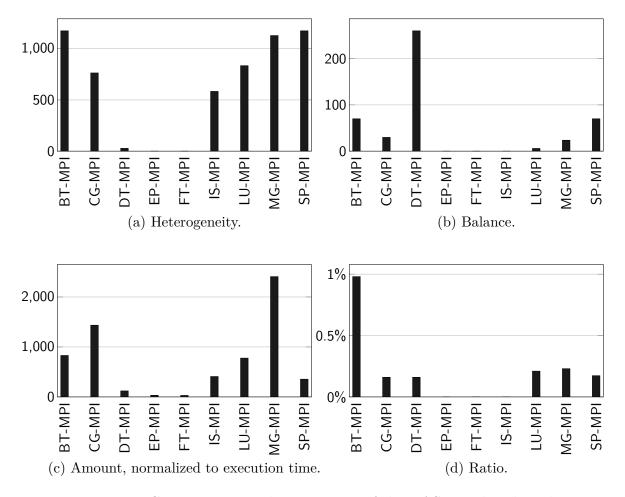

| Figure 3.15 Communication matrices of the NAS-MPI benchmarks                            | . 70 |

| Figure 3.16 Communication characteristics of the NAS-MPI benchmarks                     |      |

| Figure 3.17 Communication matrices of various phases of the HPCC benchmark              | . 71 |

| Figure 3.18 Communication characteristics of each phase of the HPCC benchmark           | .72  |

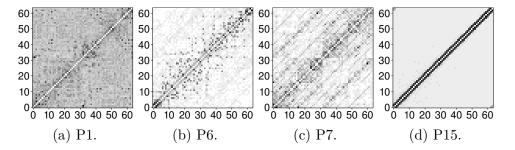

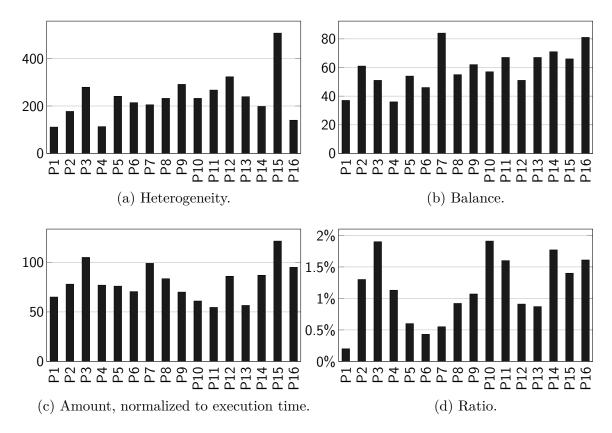

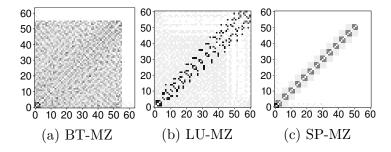

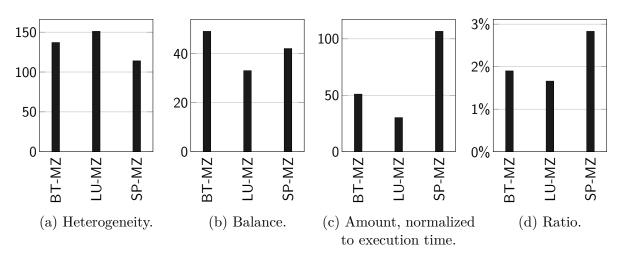

| Figure 3.19 Communication matrices of the NAS-MZ benchmarks                             | . 72 |

| Figure 3.20 Communication characteristics of the NAS-MZ benchmarks.                     |      |

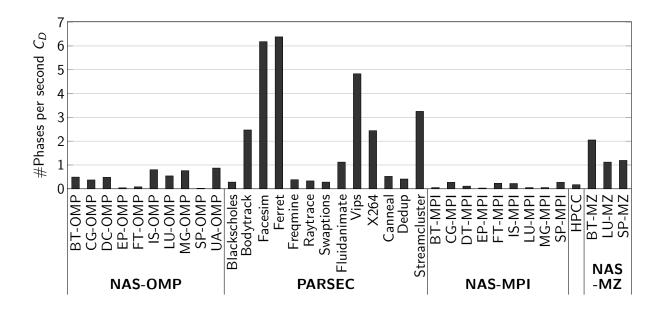

| Figure 3.21 Number of communication phases per second execution time $C_D$              | . 73 |

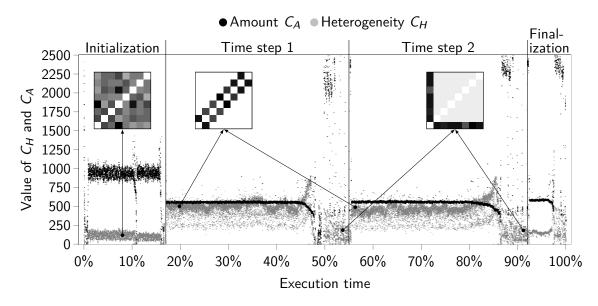

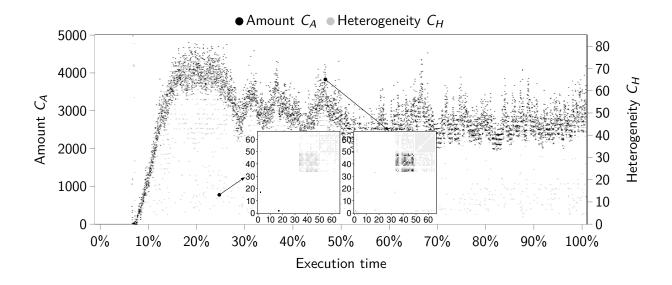

| Figure 3.22 Dynamic communication behavior of the SP-OMP benchmark                      |      |

| Figure 3.23 Dynamic communication behavior of the Ferret benchmark                      | .74  |

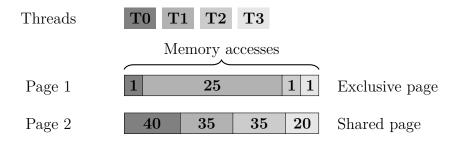

| Figure 4.1 Memory access exclusivity for an application that accesses two pages         | . 78 |

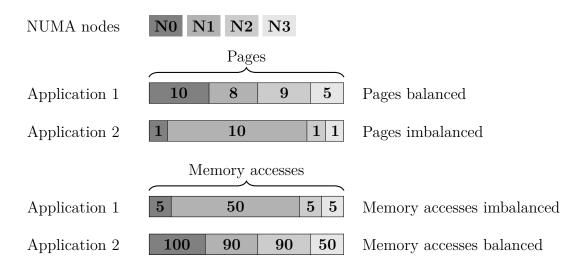

| Figure 4.2 Memory access balance for two applications and four NUMA nodes               | . 79 |

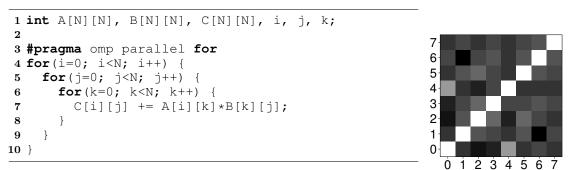

| Figure 4.3 Matrix multiplication code                                                   | . 79 |

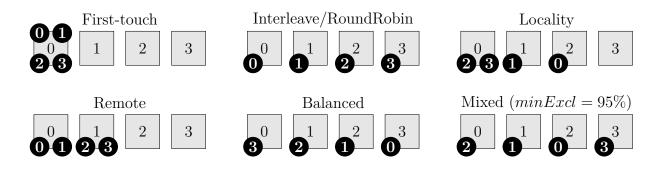

| Figure 4.4 Example of data mapping policy behavior                                      | . 91 |

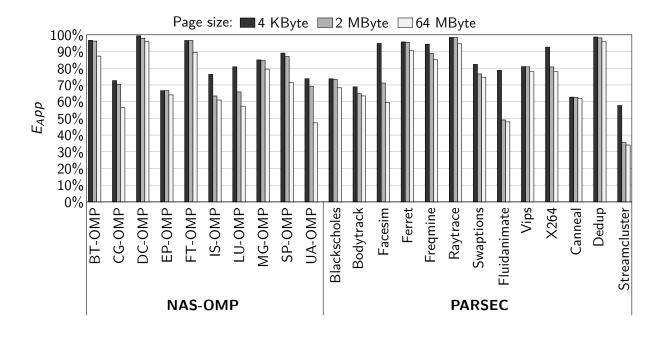

| Figure 4.5 Application exclusivity $E_{App}$ for 4 NUMA nodes and different page sizes  | . 92 |

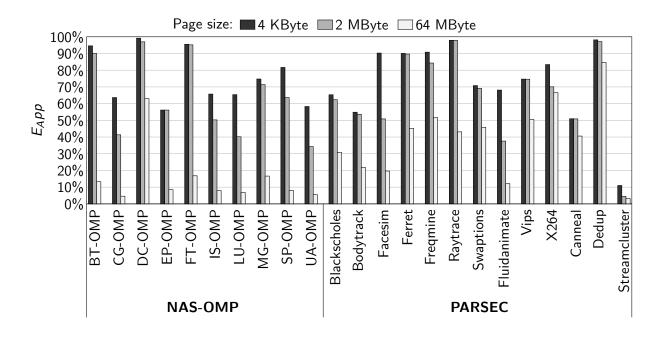

| Figure 4.6 Application exclusivity $E_{App}$ for 64 NUMA nodes and different page sizes |      |

| Figure 4.7 Page and memory access balance of the first-touch policy                     | .94  |

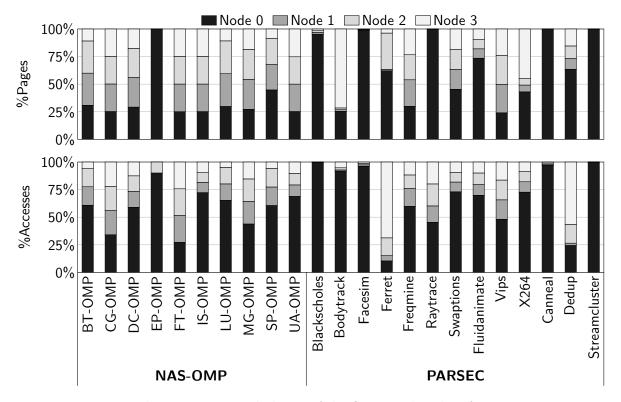

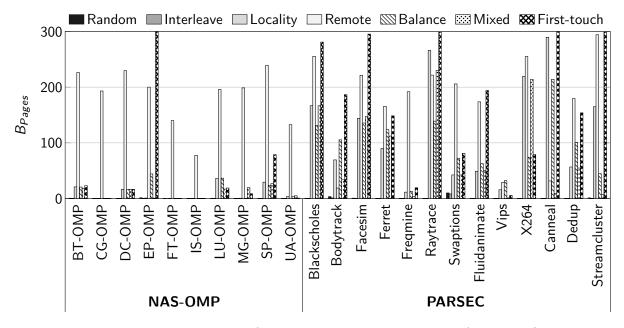

| Figure 4.8 Page balance $B_{Pages}$ of the data mapping policies                        |      |

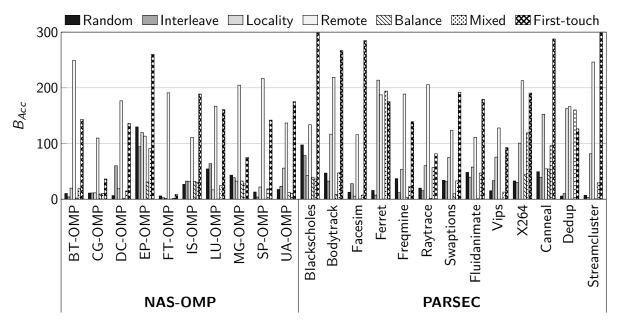

| Figure 4.9 Memory access balance $B_{Acc}$ of the data mapping policies                 |      |

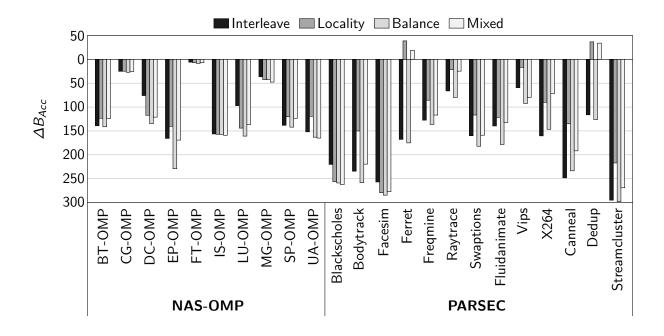

| Figure 4.10 Comparing memory access balance between the main mapping policies           |      |

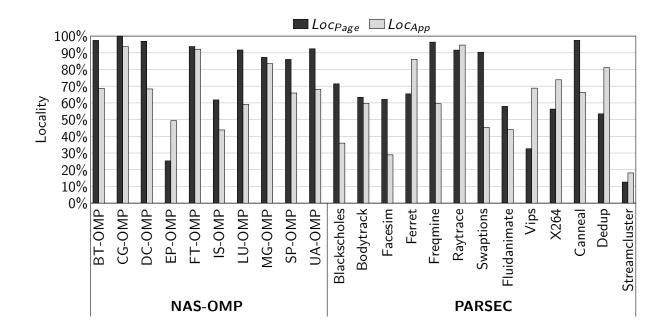

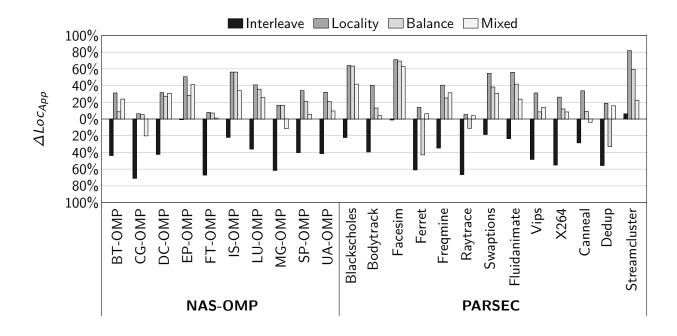

| Figure 4.11 Locality of the first-touch page mapping                                    | . 96 |

| Figure 4.12 Comparing memory access locality between the main mapping policies          | . 97 |

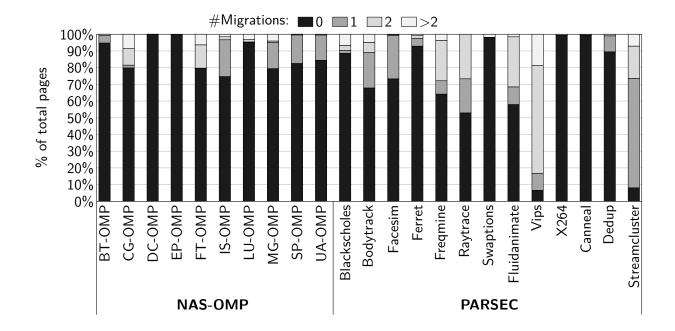

| Figure 4.13 Number of page migrations.                                                  | . 98 |

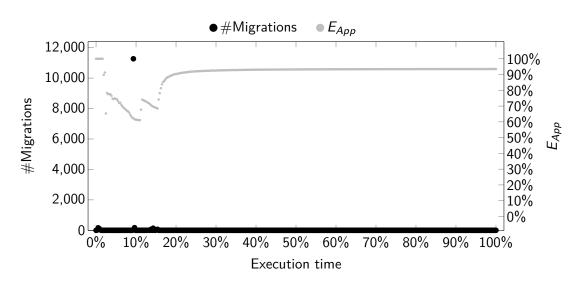

| Figure 4.14 Dynamic page usage behavior of SP-OMP.                                | 98    |

|-----------------------------------------------------------------------------------|-------|

| Figure 4.15 Dynamic page usage behavior of Vips                                   | 99    |

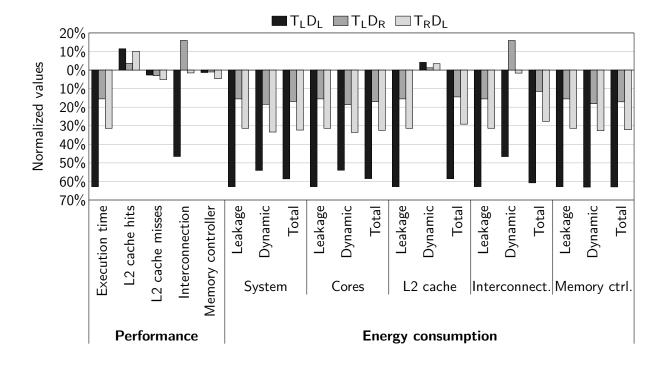

| Figure 5.1 Performance and energy consumption of SP-OMP in SiNUCA.                | 105   |

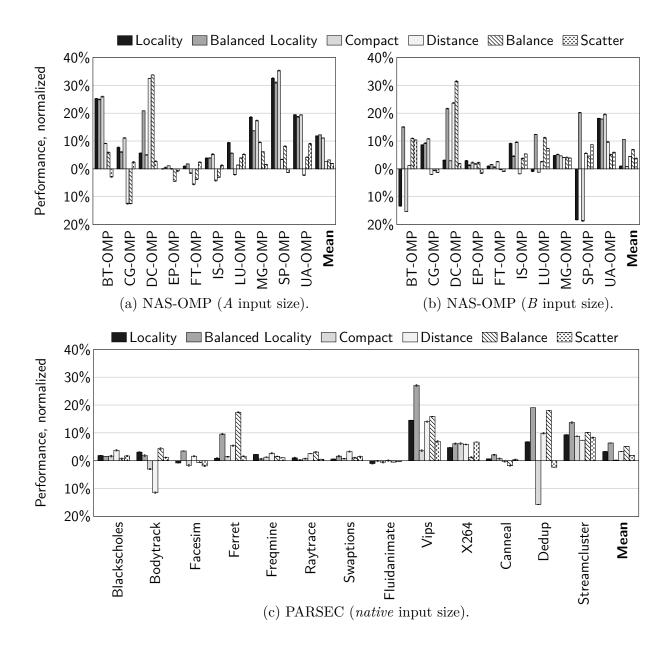

| Figure 5.2 Performance improvements of task mapping policies on <i>Xeon</i>       |       |

| Figure 5.3 Performance improvements of data mapping policies on <i>Itanium</i>    |       |

| Figure 5.4 Performance improvements of data mapping policies on <i>Xeon</i>       |       |

| Figure 5.5 Performance improvements of data mapping policies on <i>Opteron</i>    |       |

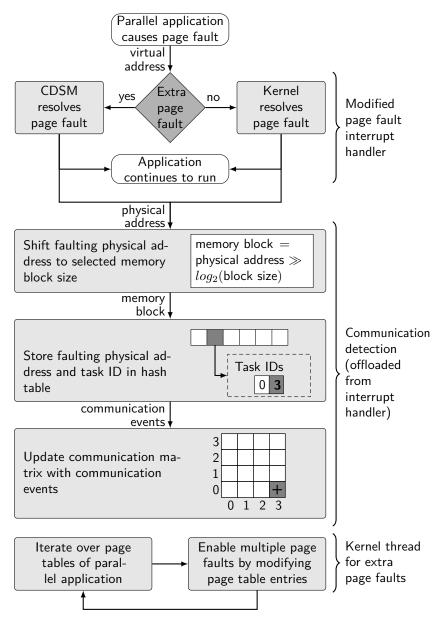

| Figure 6.1 The communication detection mechanism                                  | . 124 |

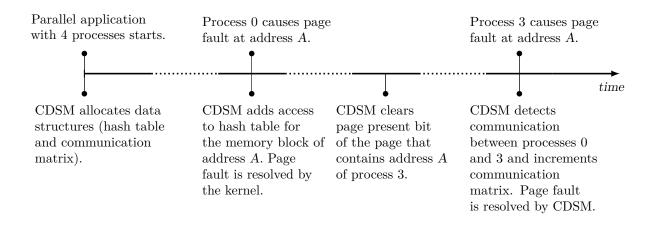

| Figure 6.2 Example of the operation of CDSM.                                      |       |

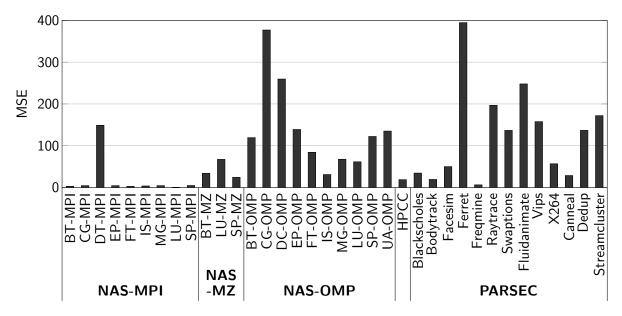

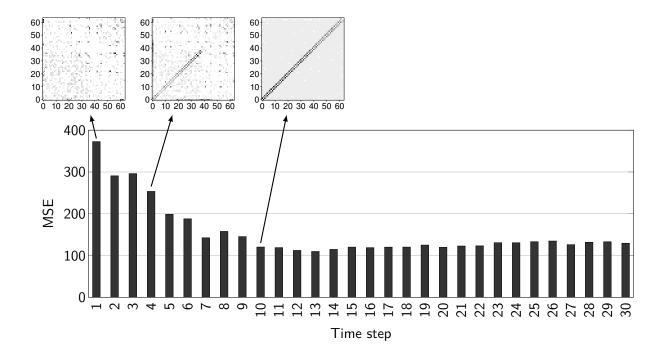

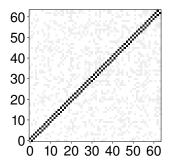

| Figure 6.3 Communication detection accuracy of CDSM                               | .129  |

| Figure 6.4 Dynamic detection behavior of the SP-OMP benchmark                     | .13(  |

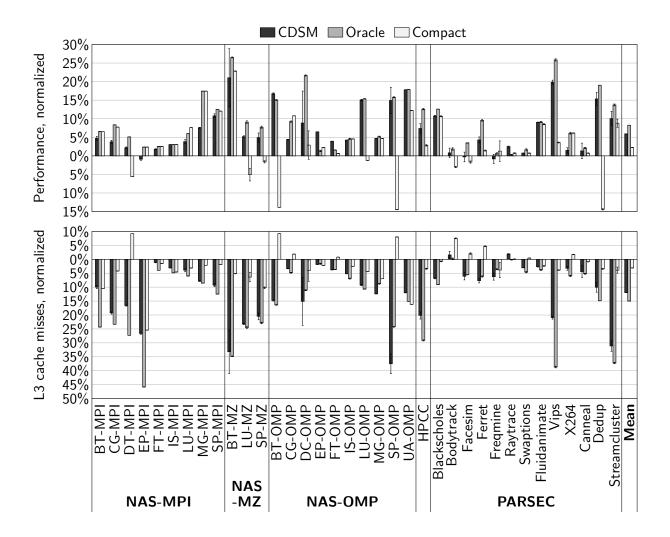

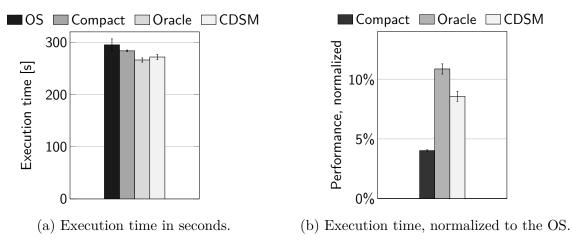

| Figure 6.5 Performance results of CDSM.                                           |       |

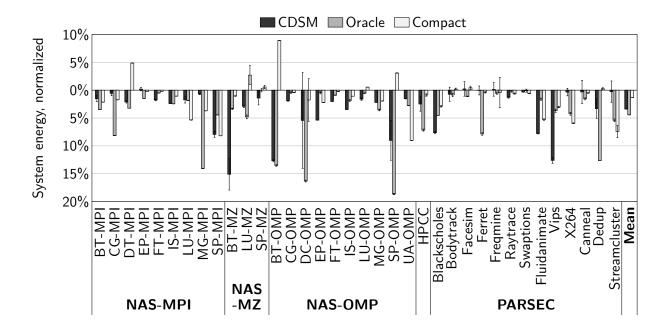

| Figure 6.6 Energy consumption results of CDSM                                     |       |

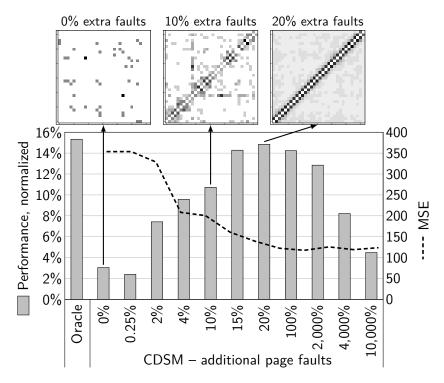

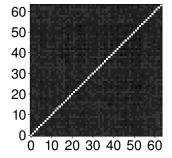

| Figure 6.7 Varying the number of extra page faults of the SP-OMP benchmark        |       |

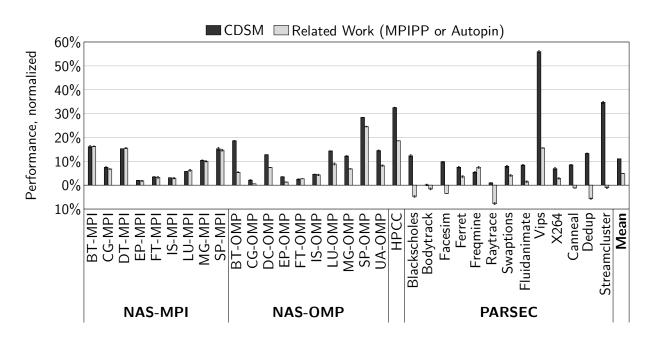

| Figure 6.8 Comparing CDSM to related work                                         |       |

| Figure 6.9 Communication behavior of the BRAMS application detected by CDSM.      |       |

| Figure 6.10 Performance results of BRAMS on <i>Xeon</i>                           |       |

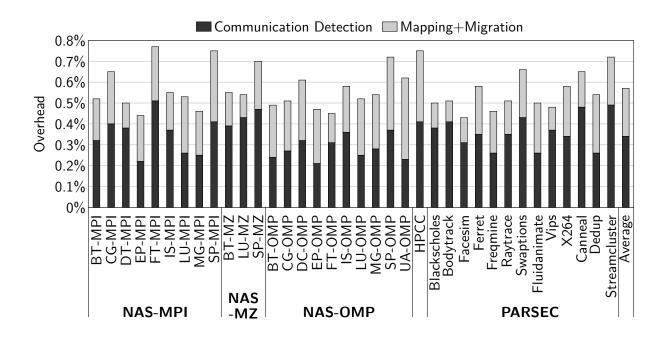

| Figure 6.11 Overhead of CDSM.                                                     | . 138 |

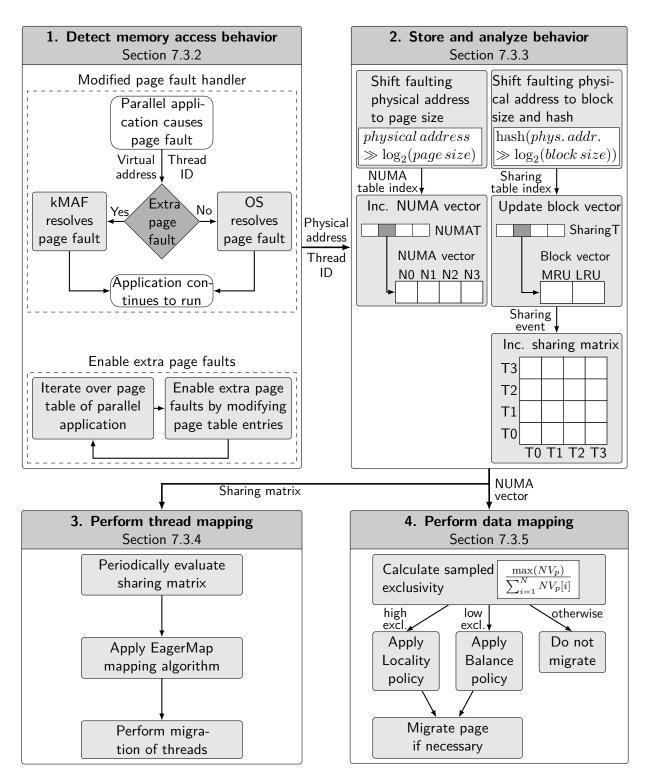

| Figure 7.1 Overview of kMAF                                                       | . 148 |

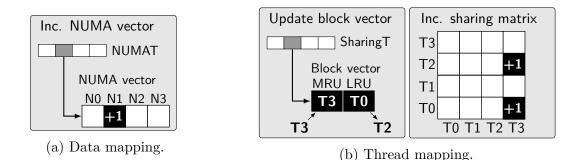

| Figure 7.2 Example of the update of kMAF's data structures                        | 15    |

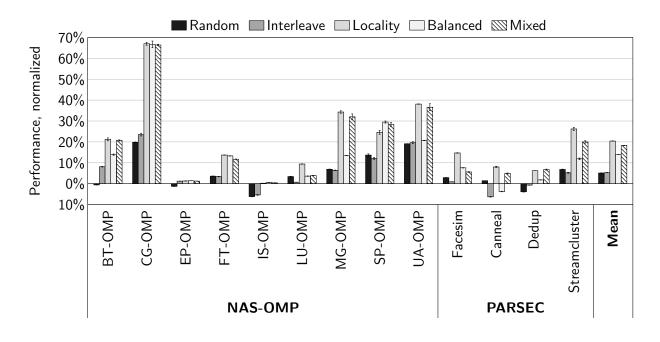

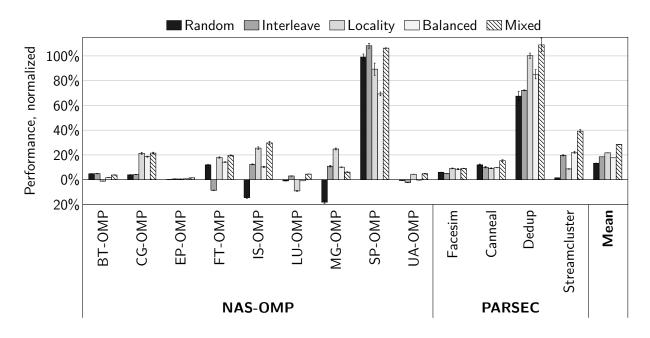

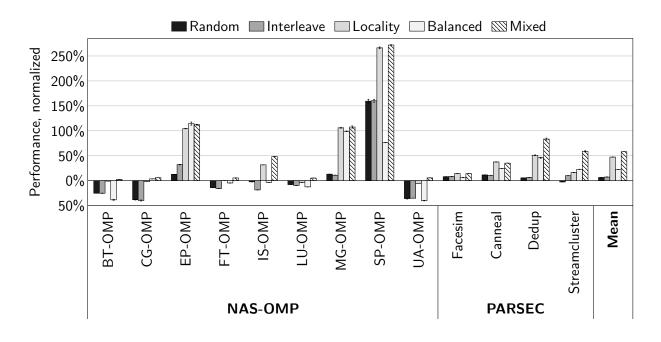

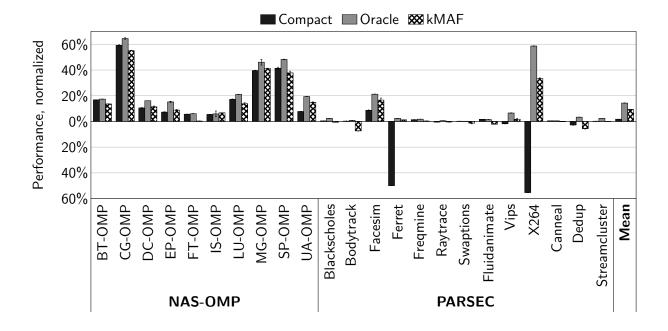

| Figure 7.3 Performance improvements on <i>Itanium</i>                             | 158   |

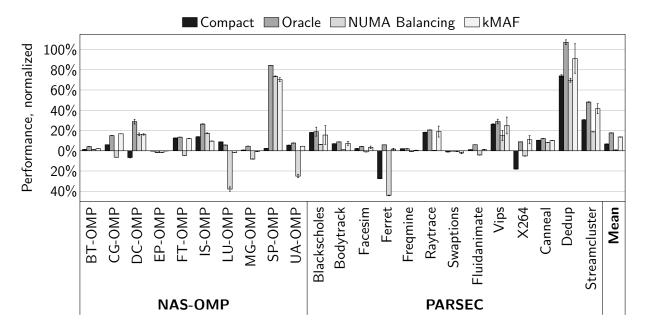

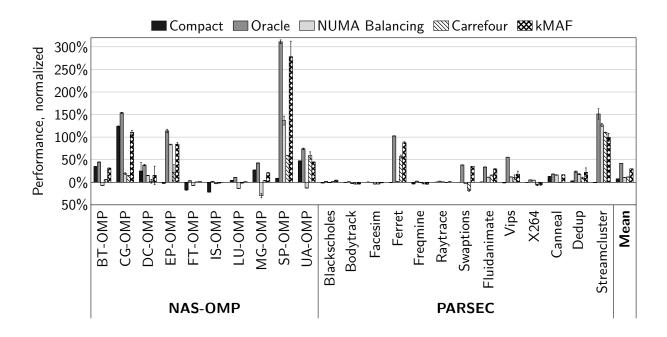

| Figure 7.4 Performance improvements on <i>Xeon.</i>                               | 158   |

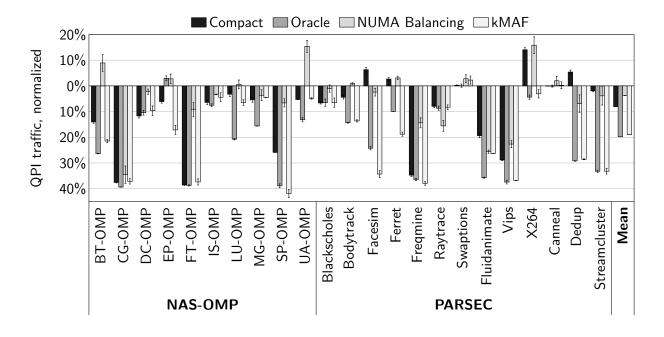

| Figure 7.5 QPI traffic reduction on <i>Xeon</i>                                   |       |

| Figure 7.6 Performance improvements on <i>Opteron</i>                             |       |

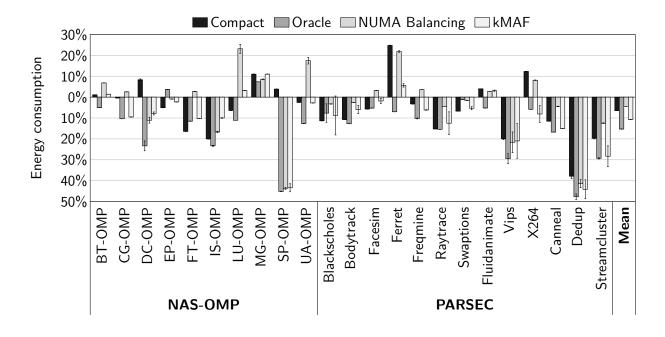

| Figure 7.7 Energy consumption results on <i>Xeon</i>                              |       |

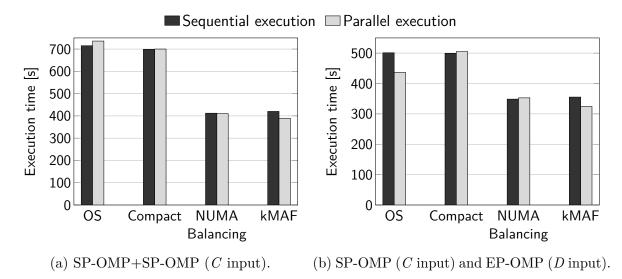

| Figure 7.8 Running multiple applications on the <i>Xeon</i> machine               |       |

| Figure 7.9 Communication pattern of both versions of Ondes3D                      |       |

| Figure 7.10 Communication pattern of HashSieve                                    |       |

| Figure 7.11 Varying the number of additional page faults of kMAF                  |       |

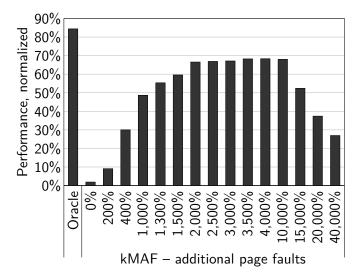

| Figure 7.12 Varying the <i>factor</i> of the locality formula                     | . 16' |

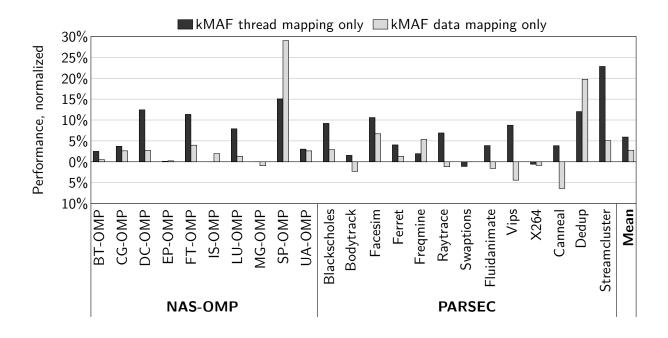

| Figure 7.13 Performance improvements of kMAF with only thread or data mapping     |       |

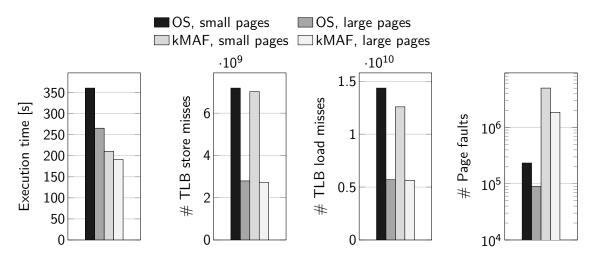

| Figure 7.14 Performance results of SP-OMP when running with small and large pages |       |

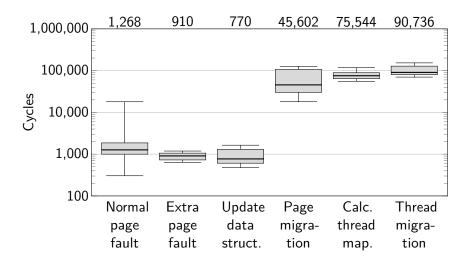

| Figure 7.15 Number of cycles of each kMAF operation on the <i>Xeon</i> machine    | 170   |

## LIST OF TABLES

| Table 2.1 | Overview of the parallel benchmark suites.                       | 38  |

|-----------|------------------------------------------------------------------|-----|

| Table 2.2 | Overview of the scientific applications                          | 39  |

| Table 2.3 | Overview of the systems used in the evaluation.                  | 41  |

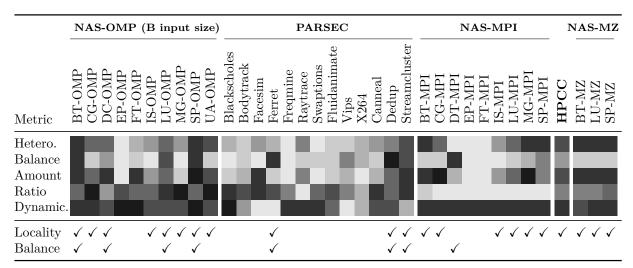

| Table 3.1 | Overview of the communication metrics introduced in this section | 61  |

| Table 3.2 | Overview of benchmark suitability for task mapping               | 75  |

| Table 4.1 | Page usage of the matrix multiplication                          | 81  |

| Table 4.2 | Overview of the page usage metrics introduced in this section    | 87  |

| Table 4.3 | Input for the data mapping example                               | 90  |

| Table 4.4 | Average values of the balance metrics of the mappings policies   | 94  |

|           | Dynamic page usage $Page_{dyn}$                                  |     |

| Table 4.6 | Overview of benchmark suitability for data mapping               | 100 |

| Table 5.1 | Configuration of the machine that was simulated in SiNUCA        | 105 |

| Table 6.1 | Summary of the main related task mapping mechanisms              | 122 |

| Table 6.2 | Experimental configuration of CDSM                               | 128 |

| Table 6.3 | Overhead of the FT-MPI benchmark.                                | 139 |

| Table 7.1 | Overview of the main related work in data mapping                | 146 |

| Table 7.2 | Behavior of kMAF's data mapping policy.                          | 154 |

| Table 7.3 | Default configuration of kMAF used in the experiments            | 155 |

| Table 7.4 | Page usage statistics of Ondes3D for 4 NUMA nodes                | 163 |

| Table 7.5 | Execution time of two versions of Ondes3D                        | 164 |

| Table 7.6 | Page usage statistics of HashSieve for 4 NUMA nodes              | 165 |

| Table 7.7 | Execution time of two versions of HashSieve                      | 165 |

| Table 7.8 | Overhead of the SP-OMP benchmark, measured on the Xeon machine   | 170 |

|           | Overhead of kMAF of the benchmarks                               |     |

### LIST OF ABBREVIATIONS AND ACRONYMS

- API Application Programming Interface

- ASLR Address Space Layout Randomization

- BMC Baseboard Management Controller

- BRAMS Brazilian developments on the Regional Atmospheric Modeling System

- BV Block Vector

- ccNUMA cache-coherent NUMA

- CDSM Communication Detection in Shared Memory

- CFD Computational Fluid Dynamics

- CFS Completely Fair Scheduler

- CMP Chip Multi-Processing

- DBI Dynamic Binary Instrumentation

- DRAM Dynamic Random Access Memory

- DSM Distributed Shared Memory

- FLOP Floating Point Operation

- FSB Front-Side Bus

- HPC High-Performance Computing

- HPCC High-Performance Computing Challenge

- IBS Instruction-Based Sampling

- ILP Instruction-Level Parallelism

- IPMI Intelligent Platform Management Interface

- kMAF kernel Memory Affinity Framework

- LLC Last Level Cache

- LRU Least Recently Used

- LWP Lightweight Profiling

- McPAT Multicore Power, Area, and Timing

- MPE MPI Parallel Environment

- MPI Message Passing Interface

- MPSS Multiple Page Size Support

- MRU Most Recently Used

- MSE Mean Squared Error

| NAS    | NASA Advanced Supercomputing                                 |

|--------|--------------------------------------------------------------|

| NPB    | NAS Parallel Benchmarks                                      |

| NUMA   | Non-Uniform Memory Access                                    |

| NV     | NUMA Vector                                                  |

| OMP    | OpenMP                                                       |

| 000    | Out-of-Order                                                 |

| OS     | Operating System                                             |

| PAE    | Physical Address Extension                                   |

| PARSEC | Princeton Application Repository for Shared-Memory Computers |

| PCM    | Performance Counter Monitor                                  |

| PEBS   | Precise Event Based Sampling                                 |

| PMU    | Performance Monitoring Unit                                  |

| PU     | Processing Unit                                              |

| QPI    | QuickPath Interconnect                                       |

| RAMS   | Regional Atmospheric Modeling System                         |

| RAPL   | Running Average Power Limits                                 |

| ROB    | Re-Order Buffer                                              |

| ROI    | Region Of Interest                                           |

| SMP    | Symmetric Multi-Processing                                   |

| SMT    | Simultaneous Multi-Threading                                 |

| SPCD   | Shared Pages Communication Detection                         |

| TIG    | Task Interaction Graph                                       |

| TLB    | Translation Lookaside Buffer                                 |

| TLP    | Thread-Level Parallelism                                     |

| TLS    | Thread-Local Storage                                         |

| TSC    | Time Stamp Counter                                           |

| UMA    | Uniform Memory Access                                        |

|        |                                                              |

## CONTENTS

| 1 INTRODUCTION                                                 | 21 |

|----------------------------------------------------------------|----|

| 1.1 Parallel Shared Memory Architectures                       | 24 |

| 1.1.1 State-of-the-Art Architectures                           | 24 |

| 1.1.2 Emerging Technologies                                    | 25 |

| 1.2 Measuring the Impact of Mapping                            | 26 |

| 1.2.1 Task and Data Mapping Example                            | 27 |

| 1.2.2 Benefits of Improved Mappings                            | 28 |

| 1.3 Mapping Approaches                                         | 30 |

| 1.3.1 Classification of Memory Access Behavior                 | 30 |

| 1.3.2 Classification of Mapping Mechanisms                     | 31 |

| 1.4 Contributions of this Thesis                               | 33 |

| 1.5 Document Organization                                      | 33 |

| 2 CHARACTERIZING PARALLEL APPLICATIONS: OVERVIEW               | 37 |

| 2.1 Benchmark Selection                                        |    |

| 2.1.1 Parallel Benchmark Suites                                |    |

| 2.1.1 Real Scientific Applications                             |    |

| 2.2 Hardware Architectures                                     |    |

| 2.3 Characterization Methodology                               |    |

| 2.4 Related Work on Characterization of Memory Access Behavior |    |

| ·                                                              |    |

| 3 CHARACTERIZING COMMUNICATION BEHAVIOR                        |    |

| 3.1 Qualitative Communication Behavior                         |    |

| 3.1.1 Explicit and Implicit Communication                      |    |

| 3.1.2 True/False Communication and Communication Events        |    |

| 3.1.3 Read and Write Memory Accesses                           |    |

| 3.1.4 Communication Direction and Communication Matrix         |    |

| 3.1.5 Relaxing the Definition of Communication                 |    |

| 3.1.6 Common Types of Communication Patterns                   |    |

| 3.1.7 Communication Balance                                    |    |

| 3.2 Quantitative Communication Behavior                        |    |

| 3.2.1 Communication Heterogeneity                              |    |

| 3.2.2 Communication Balance                                    |    |

| 3.2.3 Communication Amount                                     |    |

| 3.2.4 Communication Ratio                                      |    |

| 3.2.5 Temporal Communication Behavior and Phase Detection      |    |

| 3.2.6 Summary of Communication Metrics                         |    |

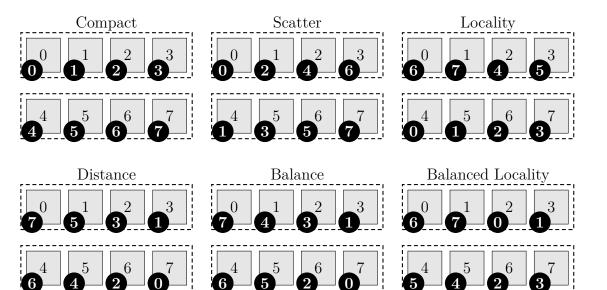

| 3.3 Task Mapping Policies                                      |    |

| 3.3.1 The Policies                                             |    |

| 3.3.2 Example of Policy Behavior                               |    |

| 3.4 Communication Behavior of the Benchmarks                   |    |

| 3.4.1 Global Communication Behavior                            |    |

| 3.4.2 Dynamic Behavior                                         |    |

| 3.5 Summary of Communication Behavior                          | 75 |

| 4 CHARACTERIZING PAGE USAGE                                    | 77 |

| 4.1 Qualitative Page Usage                                     |    |

| 4.1.1 Introduction to Page Usage                               |    |

|                                                                |    |

| 4.1.2 Example of Page Usage                                                  |     |

|------------------------------------------------------------------------------|-----|

| 4.1.3 Common Types of Page Usage                                             | 79  |

| 4.1.4 Data Mapping for MPI Applications?                                     |     |

| 4.2 Quantitative Page Usage                                                  |     |

| 4.2.1 Memory Access Exclusivity                                              |     |

| 4.2.2 Memory Access Balance                                                  |     |

| 4.2.3 Total Memory Usage                                                     |     |

| 4.2.4 Dynamic Behavior                                                       |     |

| 4.2.5 Locality of a Page Mapping                                             |     |

| 4.2.6 Summary of Page Usage Metrics                                          |     |

| 4.3 Data Mapping Policies                                                    |     |

| 4.3.1 The Policies                                                           |     |

| 4.3.2 Example of Policy Behavior                                             |     |

| 4.4 Page Usage of the Benchmarks                                             |     |

| 4.4.1 Global Behavior                                                        |     |

| 4.4.2 Dynamic Behavior                                                       |     |

| 4.5 Summary of Page Usage                                                    | 100 |

| MARY AND DAMA MADDING DOLICIES                                               | 109 |

| 5 TASK AND DATA MAPPING POLICIES                                             |     |

| 5.1 Evaluating Task and Data Mapping in a Simulator                          |     |

| 5.1.1 Simulation Methodology                                                 |     |

| 5.1.2 Simulation Results                                                     |     |

| <ul><li>5.1.3 Summary</li><li>5.2 Evaluating Task Mapping Policies</li></ul> |     |

|                                                                              |     |

| 5.2.1 Experimental Methodology<br>5.2.2 Results                              |     |

| 5.2.2 Tresuits                                                               |     |

| 5.2.4 Summary                                                                |     |

| 5.3 Evaluating Data Mapping Policies                                         |     |

| 5.3.1 Methodology                                                            |     |

| 5.3.2 Performance Results                                                    |     |

| 5.3.3 Comparison to Predicted Data Mapping Suitability                       |     |

| 5.3.4 Summary and Discussion                                                 |     |

| 5.4 An Oracle Mapping Mechanism                                              |     |

| 5.5 Summary                                                                  |     |

| сто <i>г</i> аннисцу                                                         |     |

| 6 CDSM: COMMUNICATION-AWARE TASK MAPPING                                     | 119 |

| 6.1 Introduction                                                             |     |

| 6.2 Related Work on Task and Process Mapping                                 |     |

| 6.2.1 Applications Based on Message Passing                                  |     |

| 6.2.2 Multithreaded Applications                                             |     |

| 6.2.3 Summary of Related Work on Task Mapping                                |     |

| 6.3 CDSM: Communication Detection in Shared Memory                           |     |

| 6.3.1 Fundamentals of CDSM                                                   |     |

| 6.3.2 Implementation                                                         |     |

| 6.3.3 Calculate the Task Mapping                                             |     |

| 6.3.4 Runtime Overhead of CDSM                                               |     |

| 6.3.5 Summary                                                                |     |

| 6.4 Methodology of the Experiments                                           |     |

| 6.5 Evaluation of CDSM                                                       |     |

| 6.5.1 Accuracy of Detected Communication Behavior                            |     |

| 6.5.2 Performance Results                                                                         | 130   |

|---------------------------------------------------------------------------------------------------|-------|

| 6.5.3 Energy Consumption                                                                          | 133   |

| 6.5.4 Varying the Number of Page Faults                                                           | 134   |

| 6.5.5 Comparing CDSM to Related Work                                                              | 135   |

| 6.5.6 Case Study: BRAMS                                                                           | 136   |

| 6.5.7 Overhead of CDSM                                                                            | 137   |

| 6.6 Summary                                                                                       | 139   |

| 7 KMAE INTECDATED TACK AND DATA MADDING                                                           | 1 4 1 |

| 7 KMAF: INTEGRATED TASK AND DATA MAPPING<br>7.1 Introduction                                      |       |

| 7.2 Related Work on Data Mapping                                                                  |       |

| 7.2.1 OS-Based Mapping                                                                            |       |

| 7.2.2 Compiler-Based and Runtime-Based Mapping                                                    |       |

| 7.2.3 Hardware-Based Mapping                                                                      |       |

| 7.2.4 Manual Mapping                                                                              |       |

| 7.2.5 Summary of Related Work                                                                     |       |

| 7.3 kMAF: The Kernel Memory Affinity Framework                                                    |       |

| 7.3.1 Overview of KMAF                                                                            |       |

| 7.3.2 Detecting Memory Access Behavior                                                            | 147   |

| 7.3.3 Storage and Analysis of the Detected Behavior                                               |       |

| 7.3.4 Thread Mapping                                                                              | 151   |

| 7.3.5 Data Mapping                                                                                | 151   |

| 7.3.6 Supporting Multiple Running Applications                                                    | 154   |

| 7.3.7 Implementation of KMAF                                                                      |       |

| 7.3.8 Overhead of KMAF                                                                            |       |

| 7.4 Methodology of the Experiments                                                                |       |

| 7.5 Results                                                                                       |       |

| 7.5.1 Single Applications                                                                         |       |

| 7.5.2 Energy Consumption                                                                          |       |

| 7.5.3 Multiple Applications                                                                       |       |

| 7.5.4 Case Study: Ondes3D                                                                         |       |

| 7.5.5 Case Study: HashSieve                                                                       |       |

| 7.5.6 Mechanism Sensitivity                                                                       |       |

| 7.5.7 Performing Thread and Data Mapping Separately                                               |       |

| <ul><li>7.5.8 Performance Improvements with Larger Pages</li><li>7.5.9 Overhead of KMAF</li></ul> | 160   |

| 7.6 Summary                                                                                       |       |

| 7.0 Summary                                                                                       | 170   |

| 8 CONCLUDING REMARKS                                                                              | 173   |

| 8.1 Summary of Main Results                                                                       | 173   |

| 8.2 Released Software                                                                             |       |

| 8.3 Research Perspectives                                                                         |       |

| 8.4 Publications                                                                                  | 176   |

| REFERENCES                                                                                        | 179   |

#### **1 INTRODUCTION**

Since reaching the limits of Instruction Level Parallelism (ILP), Thread Level Parallelism (TLP) has become important to continue increasing the performance of computer systems. Increases in the TLP are accompanied by more complex memory hierarchies, consisting of several private and shared cache levels, as well as multiple memory controllers that introduce Non-Uniform Memory Access (NUMA) characteristics, to provide data to memory-hungry applications. As a result, the performance of memory accesses started to depend also on the location of the data (WANG et al., 2012; COTEUS et al., 2011). Accesses to data that is located on local caches and NUMA nodes have a higher bandwidth and lower latency than accesses to remote caches or nodes (FELIU et al., 2012). Improving the *locality* of memory accesses is mostly important when the time to access remote caches and NUMA nodes is much higher than an access to local ones (RIBEIRO et al., 2010; LIU; MELLOR-CRUMMEY, 2014). However, when the difference between local and remote accesses is low, the influence of locality becomes lower. In these cases, another important factor to be considered is the load of the caches and memory controllers. The goal is to *balance* the memory accesses such that all caches and controllers handle a similar number of requests (WANG; MORRIS, 1985; BELLOSA; STECKERMEIER, 1996; AWASTHI et al., 2010; BLAGODUROV et al., 2010; DASHTI et al., 2013). Improving locality and balance are therefore important ways to optimize performance and energy consumption of parallel applications in modern architectures.

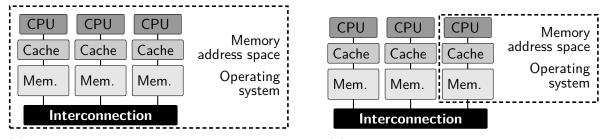

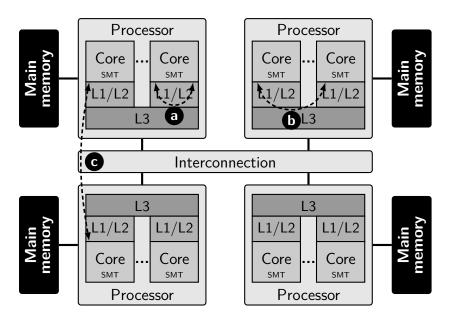

In this thesis, we focus on *shared memory architectures*, that is, parallel architectures that share a single global memory address space and execute a single instance of an operating system. Current shared memory architectures consist of several processors, cores, and NUMA nodes, as shown in Figure 1.1a. Interconnections in this type of architecture consist of traditional buses, or newer point-to-point systems, such as Intel's QuickPath Interconnect (QPI) (ZIAKAS et al., 2010) and AMD's HyperTransport (CONWAY, 2007). A special type of shared memory system is a *distributed shared memory (DSM) architecture* (NITZBERG; LO, 1991). In these systems, the main memories are physically separate but can be addressed as a single address space. Usually, each DSM platform has a custom interconnect, such as SGI's NUMAlink interconnect (WOODACRE et al., 2005), which is used in the Altix platform. In contrast to shared memory systems, cluster systems are *distributed memory architectures*, where each cluster node has its own memory address space, as shown in Figure 1.1b. Each cluster node runs its own copy of an operating

(a) Shared memory system with 3 NUMA nodes. (b) Cluster system with 3 cluster nodes.

Figure 1.1: Comparison of a shared memory architecture and a cluster system.

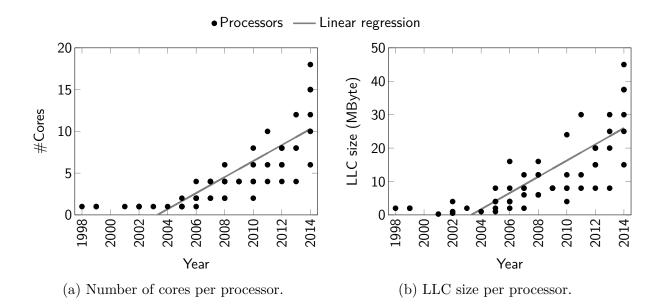

Figure 1.2: Scaling of the Intel Xeon processor between 1998 and 2014.

system and needs to communicate with other nodes through interconnections such as Ethernet or Infiniband. Although the mechanisms that will be presented in this thesis work in shared memory systems, they can be applied to cluster systems as well to optimize memory accesses in each cluster node.

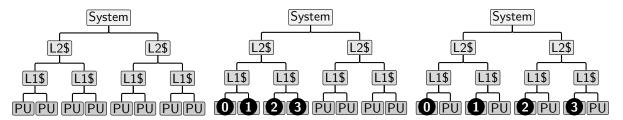

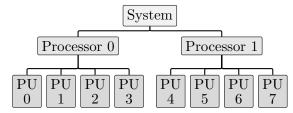

Historically, parallel shared memory architectures were introduced as a solution to the high power consumption and wire-delay problems (AGARWAL et al., 2000) of single-threaded cores. TLP was increased through multiple processors per systems (Symmetric Multi-Processing, SMP), multiple cores per processors (Multi-core, or Chip Multi-Processing, CMP) and execution of multiple tasks<sup>1</sup> on each core simultaneously (such as Symmetric Multi-Threading, SMT). We refer to an element of a shared memory system that can execute a task as a *processing unit (PU)*. We assume that all PUs are homogeneous, that is, they have the same computational power in terms of functional units, cache sizes and execution frequency, among others. As an example of the TLP increase, Figure 1.2 shows the number of cores and Last Level Cache (LLC) size of the Intel Xeon processors released between 1998 (first Xeon generation) and 2014. Every 4 to 5 years, the number of cores and LLC size has been doubling.

This increase of the TLP leads to a higher memory pressure and exacerbates the memory wall problem (WULF; MCKEE, 1995). For these reasons, traditional bus interconnections between processors and memories (such as the Front-Side Bus, FSB) were replaced by dedicated point-to-point interconnections, resulting in a NUMA behavior. Despite these improvements, memory accesses still represent a challenge for the performance and energy consumption of applications. For the performance, the gap between CPU and memory performance still keeps on increasing (Figure 1.3a). Analyzing the energy consumption for computation and data accesses presents similar challenges. Figure 1.3b shows the average energy consumption (in picojoules) of a floating point operation (FLOP),

<sup>&</sup>lt;sup>1</sup>In the context of this thesis, we use the word task to refer to the threads and processes of parallel applications. When it is necessary for the discussion, we will refer to threads and processes directly.

(a) The memory wall problem. Comparison (b) Energy consumption per operation, for comof relative processor and memory performance (1980=1). Adapted from (WULF; MCKEE, 1995; METER, 2009).

putation (FLOP) and data accesses (all others). Adapted from (SHALF; DOSANJH; MORRI-SON, 2010).

Figure 1.3: The impact of memory accesses on performance and energy consumption. Note that the y-axis in both graphs is in logarithmic scale.

a register access, an on-chip cache access, and an off-chip cache access/DRAM access. Values from 2010, as well as predictions for 2018 are depicted in the figure. The results show that memory accesses to local caches and memory have a far lower energy consumption than remote accesses and are projected to remain so for the foreseeable future (SHALF; DOSANJH; MORRISON, 2010). Furthermore, moving data between processors, caches, and the memory has an energy consumption that is generally much higher than the computation performed on the data (DALLY, 2010).

In distributed-memory environments, locality has been improved by placing processes that communicate on cluster nodes that are close to each other (SISTARE; VAN-DEVAART; LOH, 1999; RODRIGUES et al., 2009). For parallel applications running on shared memory architectures, memory access locality can be improved in two ways. First, by executing tasks that access shared data close to each other in the memory hierarchy, they can benefit from shared caches and faster intra-chip interconnections (CRUZ; DIENER; NAVAUX, 2012; DIENER; CRUZ; NAVAUX, 2013). We refer to accesses to shared data as *communication* in this thesis and call the resulting mapping of tasks to processing units a communication-aware task mapping. Most parallel programming APIs for shared memory, such as OpenMP and Pthreads, directly use memory accesses to communicate. Even many implementations of the Message Passing Interface (MPI) (which uses explicit functions to communicate) contain optimizations to communicate via shared memory. Second, the memory pages that a task accesses should be placed on NUMA nodes close to where it is executing, to reduce the inter-node traffic as well as to increase the performance of accesses to the main memory (RIBEIRO et al., 2009). We call this technique data *mapping.* For both types of mapping, balancing the communication and memory accesses can also become important in order to prevent an overload.

The state-of-the-art research in this area focuses on either task or data mapping, performing them only separately. We make the case that mapping should be performed in an integrated way in order to achieve the maximum gains. Some mechanisms rely on communication or memory access traces (RODRIGUES et al., 2009; MARATHE; THAKKAR; MUELLER, 2010; DIENER et al., 2010; CRUZ et al., 2011), which cause a high overhead (ZHAI; SHENG; HE, 2011; BARROW-WILLIAMS; FENSCH; MOORE, 2009) and generate incorrect data if the behavior of the application changes between executions. Mechanisms that use indirect information about the memory access behavior, such as cache statistics or IPC (AZIMI et al., 2009; KLUG et al., 2008; BROQUEDIS et al., 2010a; RADOJKOVIĆ et al., 2013), can result in less accurate mappings. Other approaches use architecture dependent features or require hardware changes or changes to the applications themselves to perform an optimized mapping (MARATHE; MUELLER, 2006; CRUZ; DIENER; NAVAUX, 2012; CRUZ et al., 2014a; TIKIR; HOLLINGSWORTH, 2008; OGASAWARA, 2009). These approaches can not be considered generic solutions for the mapping problem.

The goal of this thesis is to improve on the current state-of-the-art by introducing mechanisms that perform an integrated task and data mapping on the kernel level. The proposed techniques use sampling of memory accesses to determine the behavior of the parallel application during its execution, and use this information to perform the mapping. The mechanisms are compatible with a wide range of hardware architectures, requiring no changes to the hardware. Since they operate on the kernel level, they require no changes to the applications, are independent of the parallelization API and support several running applications at the same time. Extensive evaluation using a large set of parallel benchmarks show significant improvements of performance and energy efficiency.

The research described in this thesis was conducted in the context of a joint degree between the Federal University of Rio Grande do Sul (UFRGS) and the Technische Universität Berlin. Parts of the research were developed at the Parallel and Distributed Processing Group (GPPD) at UFRGS and the at the Communication and Operating Systems group (KBS) at TU Berlin.

#### 1.1 Parallel Shared Memory Architectures

Modern shared memory architectures are characterized by an increasing amount of parallelism in each system. We briefly discuss the current state-of-the-art of these architectures and give an overview of emerging technologies that affect the memory access behavior.

#### 1.1.1 State-of-the-Art Architectures

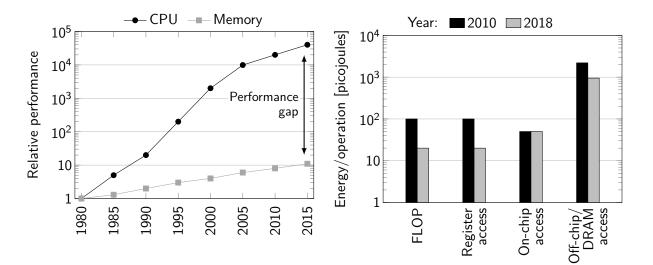

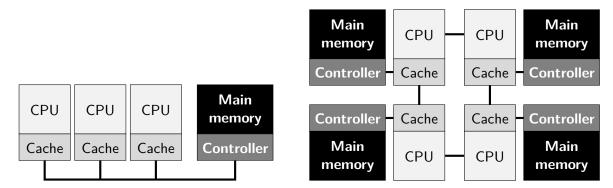

Traditional parallel shared memory architectures were built with Symmetric Multi Processing (SMP), that is, multiple single-core processors interconnected through a shared bus. Each processor can only execute a single thread at the same time, and has a cache that is private to the CPU. Such systems contain a single memory controller, which is usually connected to the same bus shared between the processors. Figure 1.4a depicts an example of such a Uniform Memory Access (UMA) architecture.

Since traffic on the shared bus and accesses to the main memory represent a significant bottleneck, these UMA systems are being replaced by architectures that feature a Non-Uniform Memory Access (NUMA) behavior. In NUMA systems, the bus has been replaced by high-speed point-to-point interconnections. To increase the efficiency of memory accesses, the physical memory is split between several memory controllers, such that multiple memory requests can be handled at the same time. In this thesis, we only discuss cache-coherent NUMA architectures (ccNUMA), where the cache coherence is maintained automatically by the hardware. An example of such a system is shown in Figure 1.4b. NUMA systems are characterized by an overhead to access memory on remote memory controllers, which is called the NUMA factor (PILLA et al., 2011).

In addition to NUMA behavior, the parallelism in each CPU has increased remarkably compared to SMP machines. To increase the utilization of functional units, techniques such as Simultaneous Multi-Threading (SMT) allow the execution of multiple tasks concurrently by sharing the same functional units. To reduce data movement between processors, the industry has been duplicating functional units on processors, creating multi-core or CMP chips. Most current architectures employ both SMT and CMP to maximize the parallelism on each processor, resulting in the introduction of complex cache hierarchies with private and shared cache levels.

#### 1.1.2 Emerging Technologies

Since NUMA architectures have reached the mainstream, several important developments have happened that affect the memory access efficiency and mapping policies. Most of the challenges introduced by these emerging technologies will be discussed in more detail throughout the thesis. First of all, manycore architectures will lead to a large increase of parallelism on a single chip, going from tens of cores in multi-core systems to

a shared bus.

(a) UMA system with multiple processors and (b) NUMA system with multiple processors and a single memory controller interconnected with memory controllers connected with point-topoint interconnections.

thousands of cores or more (ASANOVIC et al., 2006). This impacts especially the task mapping (SINGH et al., 2013), requiring the introduction of more efficient algorithms or limiting the mapping to only a part of the chip. Chapter 3 discusses some of these questions in more detail. On the other hand, the gains from task mapping are also expected to be higher due to the larger and more complex chip structure. Another technology that affects task mapping is the introduction of additional cache levels, such as L4 caches consisting of embedded Dynamic Random Access Memory (eDRAM) (WU et al., 2009) on the chip. This can impact the improvements from task mapping by further increasing the benefits of keeping data local.

For data mapping, two main trends are emerging. Due to the rising memory consumption of parallel applications, increasing the page size of modern systems is an attractive way to reduce the overhead of memory management. Larger pages reduce the number of page faults (GAUD et al., 2014), TLB misses (BASU et al., 2013), and TLB shootdowns (VILLAVIEJA et al., 2011), and require less memory to store the page table (CASCAVAL et al., 2005). For these reasons, many applications can benefit from significant performance improvements when using larger pages (WEISBERG; WISEMAN, 2009; BASU et al., 2013). Most current architectures have a default page size of a few KByte (such as 4 KByte in Intel x86 (INTEL, 2013b)) and optionally support much larger pages (256 MByte in Intel Itanium and 1 GByte in Intel x86 64, for example). Also, most modern operating systems include at least rudimentary support for larger pages, such as the Huge page mechanism for Linux (LU et al., 2006), Superpages in FreeBSD (NAVARRO, 2004), and the Multiple Page Size Support (MPSS) of Solaris (MCDOUGALL, 2004). Although larger pages increase memory management efficiency, it presents challenges for data mapping, as the larger granularity reduces opportunities for improvements (GAUD et al., 2014). This aspect will be discussed in more detail in Chapters 4 and 7.

The second trend that impacts data mapping is the increase of the number of memory controllers in shared memory systems. Most architectures currently in use contain a single memory controller per chip, such as most modern Intel Xeon processors. However, manufacturers are beginning to include multiple memory controllers on the same chip, leading to a NUMA behavior even within a single socket, as well as a hierarchy of memory controllers in a multi-socket system. This can increase the gains from an improved data mapping policy. Many current AMD processors feature multiple memory controllers (AMD, 2012), and we will evaluate the performance improvements of data mapping on such an architecture in Chapters 5 and 7.

#### 1.2 Measuring the Impact of Mapping

To evaluate how mapping affects parallel applications, we experiment with a small synthetic benchmark to discuss the benefits of improved task and data mappings.

#### 1.2.1 Task and Data Mapping Example

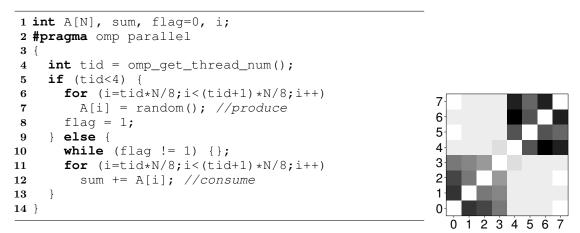

To illustrate the impact of mapping decisions on the performance and energy consumption of parallel applications, consider the NUMA system shown in Figure 1.5, which is based on the Intel Xeon Nehalem microarchitecture (INTEL, 2010b). This system consists of 4 multi-core processors with support for Simultaneous Multi-Threading (SMT). Each processor contains an L3 cache that is shared by all cores, as well as L1 and L2 caches that are private to each core. Since the processors have their own memory controllers, each one forms a NUMA node and is connected to its local main memory.

In this system, there are 3 different ways to execute a pair of tasks, labeled (a), (b) and (c) in the figure, which impact the access to shared data between the tasks. In case (a), the tasks execute on the same core, and can access shared data through the fast private caches as well as the local NUMA node. In case (b), tasks execute on different cores in the same processor and can still benefit from the shared L3 cache and fast on-chip interconnection. In case (c) however, tasks need to access shared data across the slow off-chip interconnection. Furthermore, since the shared data needs to be placed on one of the NUMA nodes, the task that runs on the other node has a further penalty to access the memory located on the remote node.

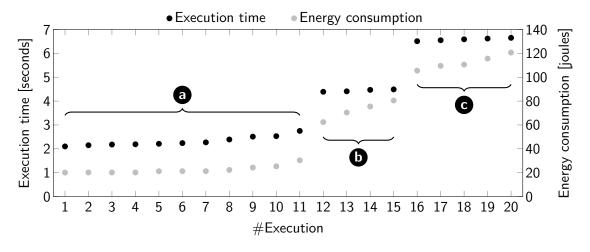

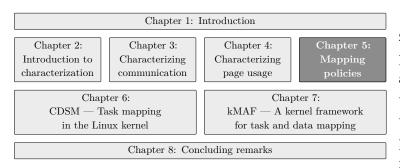

To evaluate the impact of mapping choices, we developed a producer/consumer benchmark that consists of two tasks. The producer task repeatedly writes data to a shared vector, which gets read by the consumer task. Neither task performs significant calculations apart from incrementing a loop counter, and the application is therefore highly memory-bound. We executed this benchmark 20 times on the machine described above, using the default task and data mapping policies of the Linux operating system (OS), and measured the execution time and energy consumption of each run.

The results of this experiment are shown in Figure 1.6. For each of the 20 executions,

Figure 1.5: Example NUMA architecture with 4 NUMA nodes. In this system, two tasks can access shared data in three different ways, labeled **a**, **b** and **c**.

Figure 1.6: Performance and energy consumption results of 20 executions of the producer/consumer benchmark running on the machine shown in Figure 1.5. The results are ordered according to the execution time of the benchmark. (a), (b), and (c) correspond to the three mapping decisions depicted in Figure 1.5, performed by the OS.

we show the execution time and energy consumption, and order the results according to the execution time. From the results, the three mapping possibilities described before, (a), (b), and (c), can be clearly determined. For about half of the executions, the OS chose the correct mapping for this particular benchmark, executing the two tasks on the same core, resulting in the lowest execution time and energy consumption. Since the OS uses the first-touch policy to allocate pages, the data mapping is also correct in this case. For the other half of the executions, the OS placed the tasks farther apart, reducing performance and energy efficiency due to the worse task mapping. Furthermore, when the tasks get mapped to different NUMA nodes (case (c)), they have to perform memory accesses to the remote NUMA nodes, which contributes to the further decreases in this case. Between the best and worst mapping, execution time more than tripled, and energy consumption was increased 5.5 times. These results show that mapping has a large impact on the application's efficiency.

#### 1.2.2 Benefits of Improved Mappings

Task and data mapping aim to improve the memory accesses to shared and private data in parallel applications. This section discusses how mapping can improve performance and energy efficiency.

#### 1.2.2.1 Performance Improvements

Task mapping improves the efficiency of the interconnections, reducing inter-chip traffic that has a higher latency and lower bandwidth than intra-chip interconnections. It also reduces the number of cache misses of parallel applications. In read-only situations, executing tasks on the same shared cache reduces data replication, thereby increasing the cache space available to the application (CHISHTI; POWELL; VIJAYKUMAR, 2005). In

tween NUMA nodes.

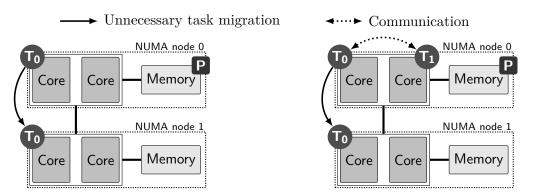

(a) Prevent unnecessary task migrations be- (b) Increase data mapping benefits when several tasks access the same page.

Figure 1.7: Two scenarios that show why task mapping is a requirement for data mapping. Consider that two tasks  $T_0$  and  $T_1$  access a page P.

read-write or write-write situations, an optimized task mapping also reduces cache line invalidations, reducing the traffic on the interconnections as well as preventing a cache miss on the next access to the cache line (ZHOU; CHEN; ZHENG, 2009). Data mapping improves the memory locality on NUMA machines by reducing the number of accesses to remote memory banks. As task mapping, it improves the efficiency of the interconnections by reducing the traffic between NUMA nodes. This increases the memory bandwidth available in the system and reduces the average memory access latency.

It is important to note that task mapping is a prerequisite for data mapping, for the two reasons depicted in Figure 1.7, where two tasks  $T_0$  and  $T_1$  access a page P. First, task mapping prevents unnecessary task migrations between NUMA nodes, such that tasks can benefit from the local data accesses (Figure 1.7a). In the figure, task  $T_0$  is migrated unnecessarily between NUMA nodes, such that accesses to page P are now accesses to a remote NUMA node, rendering the data mapping of the page ineffective. Second, data mapping alone is not able to improve locality when more than one task accesses the same page, since the tasks may be executing on different NUMA nodes. In this situation, only the tasks that are executing on the same node where the data is located can benefit from the increased locality (Figure 1.7b). By performing the task mapping, tasks that communicate a lot are executed on the same NUMA node, thereby improving the effectiveness and the gains of the data mapping. We will evaluate the interaction of the two types of mapping in more detail throughout this thesis.

#### 1.2.2.2 Energy Consumption Improvements

As shown in the experiment with the producer/consumer benchmark, improved task and data mappings can also reduce energy consumption of parallel applications. By reducing application execution time, static energy consumption (leakage) will be reduced proportionally in most circumstances. Reducing the number of cache misses and traffic on the interconnections reduces the dynamic energy consumption, leading to a more energy-efficient execution of parallel applications due to improved mappings. We therefore expect for most experiments a reduction of energy consumption that is similar to the

performance improvements and will evaluate our mapping mechanisms in this regard as well.

#### 1.3 Mapping Approaches

Task and data mappings can be generated and applied in different ways. The type of mapping determines the amount of benefits, the overhead, as well as the applicability to different classes of applications, depending on the dynamicity of their memory access behavior. This section briefly compares parallel applications in terms of this dynamicity and afterwards presents a classification of mapping approaches.

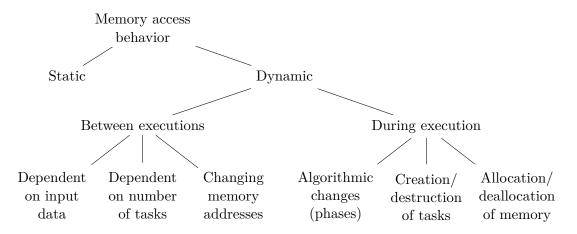

#### 1.3.1 Classification of Memory Access Behavior

On a high abstraction level, we classify the general memory access behavior of an application as *static* or *dynamic*, as shown in Figure 1.8. We further divide dynamic access behavior into two types. The first type is characterized by dynamic behavior *between executions*, where the behavior depends on specified parameters of the application, such as the input data or the number of tasks that will be created. Moreover, memory addresses can also change between executions, due to security techniques such as Address Space Layout Randomization (ASLR) (MARCO-GISBERT; RIPOLL, 2014) or a different order of dynamic memory allocations with functions such as malloc().

The second type of dynamic behavior occurs *during the execution* of the application, due to the way a parallel algorithm is implemented (such as using work-stealing (BLU-MOFE; LEISERSON, 1994) or pipeline programming models), or due to the creation and destruction of tasks or allocation/deallocation of memory. If none of these cases occur, we classify the applications' behavior as static. It is important to mention the influence of the granularity on the classification. If looking at a very small granularity, such as classifying every memory access, most applications will have a very dynamic behavior. Since we are mostly interested in the effects of mapping, we will use larger time frames for classifying the behavior.

Figure 1.8: Classification of the memory access behavior of parallel applications.

The memory access classification is important for the types of mapping that can be performed. If the memory access behavior is static, no runtime migrations of tasks and memory pages need to be performed. Moreover, the behavior can be classified and analyzed through communication or memory access traces, and only the global behavior throughout the complete execution needs to be taken into account. For applications that show a dynamic behavior only during the execution, traces can still be used to analyze their behavior. However, the changing behavior during execution needs to be taken into account when performing mapping, which can require task or data migrations during the execution to achieve optimal gains. For applications whose behavior changes between executions, trace-based mechanisms require the generation of a new trace for each set of input parameters, as the detected behavior would otherwise not be valid for future executions of the application. Care must also be taken to limit the impact of changes to memory addresses. Online mechanisms directly support all types of dynamic behavior.

#### 1.3.2 Classification of Mapping Mechanisms

Mapping mechanisms generally consist of two parts: they need to analyze and describe memory access behavior, which we call the *analysis* part. Important characteristics of the analysis are when the analysis is performed (whether information is available before execution starts), which metrics are used to describe behavior, on which level information is gathered (hardware, OS, application, ...), and if the hardware or software need to be modified. Based on the analyzed behavior, a mapping mechanism needs to apply a *policy* to determine where tasks and data should be placed and when they should be migrated. The policy can be characterized in terms of its goals (such as improving locality or balance), when it is applied (before or during execution), and if the application or runtime environment needs to be modified. Based on how the analysis and policy parts are performed in the context of the execution of a parallel application and their characteristics, we develop a classification of mapping mechanisms that consists of three groups: *manual, semi-automatic* and *automatic* mechanisms.

#### 1.3.2.1 Manual Mechanisms

Manual mapping mechanisms are defined as mechanisms where the mapping is performed by the developer through source code modifications or by the user through options in the runtime environment. Libraries such as hwloc (BROQUEDIS et al., 2010b) and libnuma (KLEEN, 2004) provide information about the hardware and memory hierarchy and can be used directly from the application. The numactl program (KLEEN, 2004) provides options for the user to modify the data mapping of an application, such as a forced allocation on a specific NUMA node or an interleaving policy.

To perform task mapping, application developers can use OS functions to execute tasks on a specified set of processing units. For application users, many runtime environments for OpenMP and MPI offer options to specify a task mapping. Many environments also provide more high-level task mapping options, such as a *compact* mapping, where neighboring tasks are mapped such that they execute on nearby processing units (INTEL, 2012b; ARGONNE NATIONAL LABORATORY, 2014b). The most common way to perform manual data mapping is by performing an explicit memory access at the beginning of execution such that each memory page is accessed first by the task that will access it, which can be beneficial in *first-touch* data mapping policies. In case the memory access behavior changes during execution, most operating systems include functions to migrate memory pages during execution. More sophisticated libraries such as MAi (RIBEIRO et al., 2009) and libnuma (KLEEN, 2004) provide support for data mapping in the application.

Manual mapping mechanisms put the burden of calculating and performing the mapping on the developer, and can therefore not be considered a general solution to the mapping problem. They are intrusive, as they require changes to the source code of every application and adaptation to different hardware architectures. Furthermore, manual mapping can present problems if multiple applications are executing at the same time, as the applications are unaware of each other and their mapping decisions might interfere. However, they can provide the highest improvements in case the developer or the user have perfect knowledge of the application's behavior.

#### 1.3.2.2 Semi-Automatic Mechanisms

Semi-automatic mapping mechanisms consist of two steps: First, the application is profiled to determine its memory access behavior, for example through memory or communication traces. Tools such as extrace (TRAHAY et al., 2011) and the Pin dynamic binary instrumentation tool (LUK et al., 2005) can be used for this purpose. The profile is analyzed to determine an optimized mapping. In the second step, the calculated mappings are then applied during the real execution of the application. The profiling phase is potentially time-consuming and is not applicable if the application changes its behavior between executions. Similar to the manual mapping, it can also present problems when multiple applications are executing at the same time. Furthermore, the data generated during profiling might be very large, necessitating a time-consuming analysis (ZHAI; SHENG; HE, 2011). However, it requires no changes to the applications are performed before the application starts.

#### 1.3.2.3 Automatic Mechanisms

Automatic mapping mechanisms perform the mapping online, during the execution of the parallel application, using information gathered only during execution. This has several consequences. The advantages are that automatic mapping presents a truly general solution to the mapping problem, as concurrently executing applications can be taken into account, as well as changing behavior between or during executions. Moreover, no expensive analysis before execution has to be performed. On the other hand, they have two important issues that need to be resolved. The main challenge for this type of mechanism is the runtime overhead, as the information gathering and migration may have a large impact on the application, reducing or even eliminating the improvements of mapping. Furthermore, since no prior information about the application behavior is available, future behavior needs to be predicted using past behavior. This also implies that improvements can be lower in comparison to mechanisms that already have this information before the application starts. We will focus on automatic mapping mechanisms in this thesis, and compare their improvements to semi-automatic and manual mechanisms.

#### 1.4 Contributions of this Thesis

The main objective of this thesis is to improve the performance and energy consumption of modern shared memory architectures by performing automatic task and data mapping. The primary contributions of this thesis are as follows:

**Characterization of Parallel Applications.** We develop metrics and a methodology to describe the memory access behavior of parallel applications, focusing on the communication and page usage of the tasks during the execution. The behavior is analyzed to determine their suitability for task and data mapping.

**Trace-Based Benchmark Analysis and Mapping Improvements.** We analyze several parallel benchmark suites that use different parallelization paradigms and evaluate their improvements using task and data mapping using a trace-based mechanism, which will serve as the baseline for our automatic mapping mechanisms.

Automatic Kernel-Based Mechanisms to Perform Mapping. We introduce two automatic, kernel-based mechanisms to perform task and data mapping, CDSM and kMAF, and implement them in the Linux kernel. CDSM performs task mapping of parallel applications, while kMAF performs an integrated task and data mapping. Both mechanisms gather information about the memory access behavior of applications during their execution through tracing and analyzing the applications' page faults, which causes only a small overhead.

#### **1.5 Document Organization**

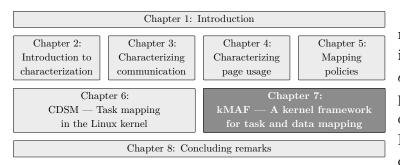

The remainder of this thesis is separated into two parts. The **first part** discusses which types of memory access behavior can be improved with different mapping policies and proposes a trace-based mechanisms to generate these policies. This first part consists of the following chapters. **Chapter 2** briefly presents the general methodology of the thesis, including the benchmark suites and parallel machines used for measurements, as well as the software tools used for the characterization. **Chapter 3** discusses qualitative and quantitative aspects of communication in parallel applications, introduces metrics and methodologies to describe communication behavior and presents task mapping policies that can improve different behaviors. The chapter **4** introduces a similarly-structured analysis of the page usage of parallel applications and discusses various data mapping policies for improving page usage on NUMA architectures. **Chapter 5** evaluates the performance and energy consumption impact of the various task and data mapping policies and presents an Oracle mapping mechanism based on memory access traces.

The second part contains the main contributions of this thesis, presenting two automatic mapping mechanisms, CDSM and kMAF, which are based on the concepts

Figure 1.9: Overview of the chapters of the thesis.

introduced in the first part. It consists of the following chapters. Chapter 6 introduces Communication Detection in Shared Memory (CDSM), an automatic task mapping mechanism for the Linux kernel. After a detailed description of CDSM, we evaluate it in terms of accuracy, as well as performance and energy consumption improvements, comparing CDSM to the Oracle and other mechanisms. Chapter 7 introduces the kernel Memory Affinity Framework (kMAF). kMAF is a generalization of CDSM, supporting data mapping in addition to task mapping and allowing the use of different types of policies.

Related work for each topic will be discussed in their respective chapters, in Section 2.4 regarding characterization of memory access behavior, Section 6.2 regarding task mapping and Section 7.2 regarding data mapping. Finally, **Chapter 8** summarizes our conclusions, gives an overview of the software produced as part of this research and outlines ideas for future work that can be based on this thesis. An overview of the structure of the thesis is shown in Figure 1.9.

## Part 1:

# The Memory Access Behavior of Parallel Applications

### **2 CHARACTERIZING PARALLEL APPLICATIONS: OVERVIEW**

In order to determine if applications can benefit from task or data mapping, two questions about their memory access behavior need to be addressed. Which type of behavior can be improved with mapping? How can the behavior be described

mathematically? This first part of this thesis aims to answer these questions for a large set of parallel benchmarks to determine their suitability for mapping improvements, focusing on the way that they communicate and how they access memory pages. This chapter contains a brief overview about related work regarding the memory access characterization of parallel applications, introduces the benchmarks that we evaluate, and presents an overview of the memory tracer that is used to perform the characterization. In Chapter 3, we introduce metrics for the communication behavior and evaluate the benchmarks with these metrics. Similarly, Chapter 4 presents the metrics and evaluation of the page usage.

# 2.1 Benchmark Selection

In this thesis, we evaluate a diverse set of parallel applications that use several parallelization models and have different memory access behaviors. Experiments were performed with multiple parallel benchmark suites, as well as larger scientific applications. This section gives an overview of these applications.

#### 2.1.1 Parallel Benchmark Suites

We selected the following parallel benchmark suites: NAS-OMP, PARSEC, NAS-MPI, HPCC and NAS-MZ. NAS-OMP and PARSEC represent typical parallel shared memory applications and are therefore the main focus in this thesis. The other benchmark suites are implemented with MPI. We use the MPICH2 framework (GROPP, 2002) MPI framework for compilation and execution of the MPI benchmarks. All benchmarks were compiled with gcc, version 4.6, with the default compilation options specified by each suite (which, in most cases, specify the -02 optimization level). Table 2.1 contains a summary of the parallel APIs, benchmark names, input sizes and average memory usage of the benchmarks in each suite. Memory usage is presented for benchmark configurations with 64 tasks and only includes memory that was actually accessed by the application (on the page size granularity).

NAS-OMP (JIN; FRUMKIN; YAN, 1999) is the OpenMP version of the NAS Parallel Benchmarks (NPB), which consists of 10 applications from the High Performance Computing (HPC) domain. Due to its good scaling behavior, we will execute these applications with various input sizes, W, A, B, C, and D, from smallest to largest, to

| Benchmark<br>suite  | Parallel<br>API     | Benchmark<br>names                                                                                                                                | Input<br>size                          | Memory<br>usage            |

|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|

| NAS-OMP<br>v3.3.1   | OpenMP              | BT-OMP, CG-OMP, DC-OMP,<br>EP-OMP, FT-OMP, IS-OMP,<br>LU-OMP, MG-OMP, SP-OMP,<br>UA-OMP (10)                                                      | <i>W–D</i><br>(DC-OMP:<br><i>W–B</i> ) | 70.1 MByte<br>– 24.8 GByte |

| PARSEC<br>v3.0 beta | Pthreads,<br>OpenMP | Blackscholes, Bodytrack, Facesim,<br>Ferret, Freqmine, Raytrace,<br>Swaptions, Fluidanimate, Vips,<br>X264, Canneal, Dedup,<br>Streamcluster (13) | native                                 | 3.2 GByte                  |

| NAS-MPI<br>v3.3.1   | MPI                 | BT-MPI, CG-MPI, DT-MPI,<br>EP-MPI, FT-MPI, IS-MPI,<br>LU-MPI, MG-MPI, SP-MPI (9)                                                                  | В                                      | 1.7 GByte                  |

| HPCC<br>v1.4.3      | MPI                 | HPCC (single application<br>consisting of 16 workloads)                                                                                           | $4000 \times 4000$ matrix              | 19.3 GByte                 |

| NAS-MZ<br>v3.3.1    | MPI +<br>OpenMP     | BT-MZ, LU-MZ, SP-MZ $(3)$                                                                                                                         | В                                      | 230 MByte                  |

Table 2.1: Overview of the parallel benchmark suites used in the evaluation, showing parallelization API, benchmark names, input size and average memory usage per application.

evaluate how the behavior changes with different inputs. The highest input size of DC-OMP is B.

*PARSEC* (BIENIA et al., 2008) is a suite of 13 benchmarks that focus on emerging parallel workloads for modern multi-core architectures. PARSEC benchmarks are implemented with OpenMP and Pthreads. Most applications have a highly dynamic behavior. This dynamic behavior includes creating and stopping threads during execution, as well as allocating and deallocating memory dynamically All benchmarks were executed with the *native* input set, which is the largest input set available. We measure the full execution time of each PARSEC benchmark, not just the time spent in the parallel phase (referred to as Region Of Interest (ROI) in the PARSEC documentation and source code). This is done to use an evaluation scenario resembling real program behavior (BIENIA et al., 2008; SOUTHERN; RENAU, 2015) and to ensure better comparability of the results to the other benchmarks.

NAS-MPI (BAILEY et al., 1991; BAILEY et al., 1995) is the MPI implementation of the NAS Parallel Benchmarks (NPB), consisting of 9 HPC applications. All NAS-MPI applications are executed with the *B* input size. We use the BlackHole (BH) variant of the DT-MPI benchmark.

*HPCC* (High Performance Computing Challenge) (LUSZCZEK et al., 2005) is a single application that consists of 16 different HPC workloads, such as HPL (PETITET et al., 2012) and STREAM (MCCALPIN, 1995). It is implemented in MPI. We execute

Table 2.2: Overview of the scientific applications used in the evaluation, showing the section in which they are discussed, the parallelization API, benchmark names, input size and average memory usage per application.

| Application          | Section        | Parallel API     | Input size                                                              | Memory usage            |

|----------------------|----------------|------------------|-------------------------------------------------------------------------|-------------------------|

| Ondes3D<br>HashSieve | 7.5.4<br>7.5.5 | OpenMP<br>OpenMP | $300 \times 300 \times 300, 1000$ iterations<br>Lattice of dimension 80 | 1.2 GByte<br>34.6 GByte |

| BRAMS                | 6.5.6          | MPI              | lightgr                                                                 | 1.9 GByte               |

HPCC with a square input matrix of  $4000 \times 4000$  elements, leaving the other input parameters at their default.