# Automatic Verification of Sequential Circuits Using Temporal Logic

MICHAEL C. BROWNE, EDMUND M. CLARKE, DAVID L. DILL, AND BUD MISHRA

Abstract—Verifying the correctness of sequential circuits has been an important problem for a long time. But lack of any formal and efficient method of verification has prevented the creation of practical design aids for this purpose. Since all the known techniques of simulation and prototype testing are time consuming and not very reliable, there is an acute need for such tools. In this paper we describe an automatic verification system for sequential circuits in which specifications are expressed in a propositional temporal logic. In contrast to most other mechanical verification systems, our system does not require any user assistance and is quite fast—experimental results show that state machines with several hundred states can be checked for correctness in a matter of seconds!

The verification system uses a simple and efficient algorithm, called a model checker. The algorithm works in two steps: in the first step, it builds a labeled state-transition graph; and in the second step, it determines the truth of a temporal formula with respect to the state-transition graph. We discuss two different techniques that we have implemented for automatically generating the state-transition graphs: The first involves extracting the state graph directly from the circuit by exhaustive simulation. The second obtains the state graph by compilation from an HDL specification of the original circuit.

Index Terms—Asynchronous circuits, hardware verification, sequential circuit verification, temporal logic, temporal logic model checking.

#### I. Introduction

VERIFYING the correctness of sequential circuits has been an important problem for a long time. But lack of any formal and efficient method of verification has prevented the creation of practical design aids for this purpose. Since all the known techniques of simulation and prototype testing are time consuming and not very reliable, there is an acute need for such tools. In this paper we describe an automatic verification system for sequential circuits in which specifications are expressed in a propositional temporal logic. In contrast to most other mechanical verification systems, our system is fully automatic and does not require user assistance in the construction of proofs. Also, it is quite fast; experimental results show that state machines with several hundred states can be checked for correctness in a matter of seconds!

Propositional logic has long been accepted as an appropriate

Manuscript received February 26, 1985; revised March 24, 1986. This work was supported by the National Science Foundation under Grant MCS-82-16706.

M. C. Browne, E. M. Clarke, and D. L. Dill are with the Department of Computer Science, Carnegie-Mellon University, Pittsburgh, PA 15213.

B. Mishra was with the Department of Computer Science, Carnegie-Mellon University, Pittsburgh, PA 15213. He is now with the Department of Computer Science, New York University, New York, NY 10012.

IEEE Log Number 8610931.

formalism for describing and reasoning about combinational circuits. We believe that temporal logic may be equally useful for sequential circuits. Bochmann [3] was probably the first to use temporal logic to describe circuits. He verified an implementation of a self-timed arbiter using linear temporal logic and what he called "reachability analysis." Malachi and Owicki [11] identified additional temporal operators required to express interesting properties of circuits and also gave specifications of a large class of modules used in self-timed systems. Although these researchers contributed significantly toward developing an adequate notation for expressing the correctness of circuits, the problem of mechanically verifying a circuit using efficient algorithms still remained unsolved.

We show how a simple and efficient algorithm, called a *model checker*, can be used to verify various temporal properties of a sequential circuit. Roughly speaking, our method works by first building a labeled state-transition graph for the circuit. This graph can be viewed as a finite *Kripke structure* or *model*. By using the model checker we can determine the truth of a temporal formula relative to the state graph. Our algorithm has time complexity linear in both the size of the specification and the size of the state-transition graph. Moreover, if the formula is not true, the model checker will provide a counterexample if possible.

Thus, if we have correctly translated the circuit specification into a state-transition graph, we will know that a formula determined to be true by the model checker must also hold true for the corresponding circuit. We discuss two different techniques that we have implemented for automatically generating such graphs: The first involves extracting the state graph directly from the circuit by simulation. The second obtains the state graph by compilation from an HDL specification of the original circuit.

In the first approach a mixed gate- and switch-level circuit simulator is used to extract a state graph from a structural description of the sequential circuit. Usually, circuits are designed under the assumptions that some input sequences and combinations will not occur. The program exploits this to prevent a combinatorial explosion in the number of states that are generated, by allowing the user to specify a set of conditions under which the inputs can change. The simulator uses a unit-delay timing model in which the switching delays of all transistors and gates are assumed to be equal.

The second approach involves extracting the Kripke structure from a high-level state machine description language with a Pascal-like syntax (called SML). Since programs in the SML language must ultimately compile into circuits, the major data

type is *Boolean*. Furthermore, Boolean variables may be declared active high or active low, and use of mixed logic is encouraged. Programs are composed using the standard control structures if, while, and loop/exit. A cobegin is provided for simultaneous execution of statements, and there is a simple macro mechanism. The output of the SML compiler can also be used to generate a PLA, PAL, or ROM—thus, permitting state machines that have been verified by our techniques to be implemented as circuits.

The paper is organized as follows: Section II briefly describes the CTL specification language and how the model checker works. Section III discusses the automatic procedure that we have implemented for extracting a CTL model directly from a circuit and Section IV illustrates its use in verifying an asynchronous circuit from Seitz's chapter in Mead and Conway [12]. In Section V we outline the alternative approach of extracting a CTL model from a program in a high-level state machine description language with a Pascal-like syntax and illustrate its use with examples. The paper concludes in Section VI with a discussion of directions for future research including the possibility of making our approach hierarchical.

#### II. CTL AND EMC

The logic that we use to specify circuits is a propositional temporal logic of branching time, called CTL (computation tree logic). This logic is essentially the same as that described in [1], [6], and [9]. The syntax for CTL is as follows: Let  $\mathcal{O}$  be the set of all the atomic propositions in the language  $\mathcal{L}$ , then:

- 1) Every atomic proposition P in  $\mathcal{O}$  is a formula in CTL.

- 2) If  $f_1$  and  $f_2$  are CTL formulae, then so are  $\neg f_1, f_1 \land f_2, AXf_1, EXf_1, A[f_1Uf_2],$  and  $E[f_1Uf_2].$

In this logic the propositional connectives  $\neg$  and  $\land$  have their usual meanings of negation and conjunction. The temporal operator X is the next time operator. Hence, the intuitive meaning of  $AXf_1$  ( $EXf_1$ ) is that  $f_1$  holds in every (in some) immediate successor state of the current state. The temporal operator U is the *strong until* operator. The intuitive meaning of  $A[f_1Uf_2]$  ( $E[f_1Uf_2]$ ) is that for every computation path (for some computation path), there exists an initial prefix of the path such that  $f_2$  holds at the last state of the prefix and  $f_1$  holds at all other states along the prefix.

We also use the following syntactic abbreviations:

- $f_1 \lor f_2 \equiv \neg (\neg f_1 \land \neg f_2), f_1 \rightarrow f_2 \equiv \neg f_1 \lor f_2 \text{ and } f_1 \leftrightarrow f_2 \equiv (f_1 \rightarrow f_2) \land (f_2 \rightarrow f_1).$

- $AFf_1 \equiv A[\text{true } Uf_1]$  which means for every path, there exists a state on the path at which  $f_1$  holds.

- $EFf_1 \equiv E[\text{true } Uf_1]$  which means for some path, there exists a state on the path at which  $f_1$  holds.

- $AGf_1 = \neg EF \neg f_1$  which means for every path, at every node on the path  $f_1$  holds.

- $EGf_1 \equiv \neg AF \neg f_1$  which means for some path, at every node on the path  $f_1$  holds.

We also define the *weak until* operator u which is similar to the strong until except that it does not imply that the second condition is inevitable. For example,  $A[f_1uf_2]$  is satisfied when all paths have an initial sequence of states satisfying  $f_1$  immediately followed by a state satisfying  $f_2$  or consist of an infinite sequence of states satisfying  $f_1$ . The weak until can be

defined by a syntactic abbreviation  $A[f_1uf_2] \equiv \neg E[\neg f_2U(\neg f_1 \land \neg f_2)]$  which means that for every computation path,  $f_1$  is true in all states preceding the (first) state in which  $f_2$  is true.

The semantics of a CTL formula is defined with respect to a labeled state-transition graph. A CTL structure is a triple  $\mathfrak{M} = (S, R, \Pi)$  where

- 1) S is a finite set of states.

- 2) R is a total binary relation on  $S(R \subseteq S \times S)$  and denotes the possible transitions between states.

- 3)  $\Pi$  is an assignment of atomic proposition to states, i.e.,  $\Pi$ :  $S \to 2^{\circ}$ .

A path is an infinite sequence of states  $(s_0, s_1, s_2, \cdots)$  such that  $\forall_i [\langle s_i, s_{i+1} \rangle \in R]$ . For any structure  $\mathfrak{M} = (S, R, \Pi)$  and state  $s_0 \in S$ , there is an *infinite computation tree* with root labeled  $s_0$  such that  $s \to t$  is an arc in the tree iff  $\langle s, t \rangle \in R$ .

The truth in a structure is expressed by  $\mathfrak{M}$ ,  $s_0 = f$ , meaning that the temporal formula f is satisfied in the structure  $\mathfrak{M}$  at state  $s_0$ . The semantics of temporal formulae are defined inductively as follows.

- $s_0 \models P \text{ iff } P \in \Pi(s_0)$ .

- $s_0 \vDash \neg f \text{ iff } s_0 \not \vDash f$ .

- $s_0 \vDash f_1 \land f_2 \text{ iff } s_0 \vDash f_1 \text{ and } s_0 \vDash f_2.$

- $s_0 \models AXf_1$  iff for all states t such that  $\langle s_0, t \rangle \in R$ ,  $t \models f_1$ .

- $s_0 \models EXf_1$  iff for some state t such that  $\langle s_0, t \rangle \in R$ ,  $t \models f_1$ .

- $s_0 \vDash A[f_1Uf_2]$  iff for all paths  $(s_0, s_1, s_2, \dots)$ ,  $\exists_{i \ge 0}[s_i \vDash f_2 \land \forall_{0 \le j < i}[s_j \vDash f_1]]$ .

- $s_0 \models E[f_1 U f_2]$  iff for some path  $(s_0, s_1, s_2, \dots)$ ,  $\exists_{i \ge 0} [s_i \models f_2 \land \forall_{0 \le i < i} [s_i \models f_1]]$ .

There is a program called EMC (extended model checker) that verifies the truth of a formula in a model using these definitions. It uses efficient graph-traversal algorithms to check a formula in time linear in the size of the graph and in the length of the formula. (See [6] for details.)

There are two additional features of the model checker that turn out to be particularly useful in practice. The first extension is the addition of fairness constraints. Occasionally, we are only interested in the correctness of fair execution sequences. For example, we may wish to consider only execution sequences in which some process that is continuously enabled will eventually fire. This type of property cannot be expressed directly in CTL. In order to handle such properties we must modify the semantics of CTL slightly. Initially, the model checker will prompt the user for a series of fairness constraints. Each constraint can be an arbitrary formula of the logic. A path is said to be fair with respect to a set of fairness constraints if each constraint holds infinitely often along the path. The path quantifiers in CTL formulas are now restricted to fair paths. Examples of fairness constraints can be found in Sections IV and V. In [6] we show that handling fairness in this manner does not change the linear time complexity of the model checker.

The second feature is a counterexample facility. When the model checker determines that a formula is false, it will attempt to find a path in the graph which demonstrates that the negation of the formula is true. For instance, if the formula has the form AGf, our system will produce a path to a state in

which  $\neg f$  holds. This feature is quite useful for debugging. EMC is written in C and runs on a VAX® 11780 under Unix.®

#### III. EXTRACTING STATE GRAPHS FROM CIRCUITS

Perhaps the most common way to understand a circuit is to trace its operation, propagating sample values through one level of gates completely before proceeding with the next layer. This is an application of a *unit delay* timing model: one assumes that the delay between input signals and the corresponding output is exactly the same for all of the gates in the circuit. The unit delay assumption is frequently used for simulation at the gate and switch level.

We use the unit-delay assumption when *verifying* sequential circuits. In essence, we have automated the informal process of checking the circuit operation for all possible inputs. The unit-delay assumption may not catch all errors in asynchronous circuits. A circuit may malfunction only in the presence of unequal gate delays, in which case some other method must be used to detect the possible error. However, we believe that verification under the unit-delay assumption is a good way to debug many types of asynchronous circuits—perhaps as an initial step in a more thorough (and expensive) verification process.

We describe below a program that converts a mixed gateand switch-level description of a circuit into a state graph (called the *circuit processor* from now on). The resulting state graph and verification conditions (written in CTL) can then be fed to the model checker to do the actual checking.

The input to the circuit processor is a structural circuit description. It consists of a set of node and component declarations. A node can be declared to be an *input node* in which case it is assumed to be driven by an off-chip signal; otherwise, it is assumed to be an internal node serving as a connection point. Internal nodes also have the ability to store signals capacitively if they are not connected (directly or indirectly) to a power source. A component can be regarded as a box with a set of "formal nodes," similar to formal parameters in procedures in conventional programming languages. A component declaration consists of a component type and an association of its formal nodes with the actual nodes in the circuit. Components can be resistors, transistors, or Boolean gates.

Once the circuit description has been read, the circuit processor builds a state graph. The heart of the program is a mixed gate- and switch-level simulator. The states of the output state graph are characterized by the signals at the circuit nodes: There is at most one state corresponding to any set of node values and each state is labeled with the signals that have the value 1 in that state.

The construction of the state graph starts with a user-specified initial state and uses the simulator to find the successors to every new state it generates. The circuit processor also decides what values to use for the input nodes when finding the successors. A state can have more than one successor if there are several possible input values.

The simulation algorithm is the same as the one used in MOSSIM II, a widely used switch-level simulator. The algorithm and MOSSIM II are thoroughly explained elsewhere, so we summarize it only briefly here. (See [5].) The algorithm uses three "logical" values: 0, 1, and X (meaning "unknown").

Basically, the simulation performs a set of steps, each step simulating one unit delay. There are logical values assigned to the circuit nodes on entry to each step, either from the results of the previous step or from user-specified initial conditions. A step consists of two phases. First, the logical node values are used to determine whether the transistors are on, off, or unknown. The transistors are frozen in this state, giving a resistor circuit. In the second phase the node values and the resistor circuit are used to find new node values using an approximate model. This gives the logical node values for the next step.

We have augmented the algorithm to allow simulation of arbitrary Boolean gates. During the first phase of a unit step a Boolean result is computed from the logical values of the gate's input nodes. If the gate has a Boolean output of 1, the simulator adds a pullup resistor to the gate output node in the resistor circuit used in phase 2. If the Boolean result is 0, the simulator adds both a pullup and an appropriate pulldown resistor to the output node. Another approach could be to treat the output of the gate as a "weak" signal source; however, this would require reformulating the switch-level model, which assumes that sources provide very strong signals because they correspond to input pins driven from off-chip.

Since circuits are only expected to work when they are properly used, the program need not consider all inputs at all states. Instead, the user specifies a set of conditions under which the inputs can change. (These are assumptions about the operation of the circuit which are included in the circuit description, not properties to be proved.) The conditions are propositional formulas on the node values. The circuit processor determines whether a state satisfies the change condition for each input signal, and uses this information to decide whether that signal can change during the computation of the successor states. Each signal that can change has two possible values: the current value and its logical complement. Any combination of these values is a possible input. It is possible for the inputs to remain unchanged in every state.

It is sometimes useful for an input condition to be able to test whether a state is "stable." (In the unit delay model, a stable state is a state that is a successor of itself. The circuit can stay in such a state for an arbitrarily long time.) Usually, for example, a clock signal in a synchronous circuit should not change until the circuit is stable. We allow the atomic proposition *stable* to be used in input change conditions. The preprocessor labels a state with *stable* if that state is a

<sup>&</sup>lt;sup>®</sup> Vax is a registered trademark of Digital Equipment Corporation.

<sup>&</sup>lt;sup>®</sup> Unix is a registered trademark of AT&T Bell Laboratories.

This presents no problem for the model checker. We have extended it to accept a state graph in which the states have two sets of labels: one of nodes with I values and one of nodes with 0 values. A node with an X value appears in neither set. A state graph of this form represents a family of state graphs of the previous type; each member of the family is the result of substituting 0 or 1 for a node that has the value X in the original graph. A formula is satisfied by a state iff it is satisfied by the corresponding state in every element of this family of graphs.

end

- The procedure below uses a hash table that maps node value assignments to states.

- To construct the state machine, call this procedure on a node value assignment for the initial state.

```

procedure BuildGraph(Node value assignment) return a state

if there is state for the node values in the table

then

return the state:

else

Create a new state:

Label the state with nodes that have 1 values:

Store the state and node values together in the hash table;

for each possible input assignment do

Combine current values for internal nodes and input assignment into

a new node value assignment;

Simulate one step to find a new node assignment:

Call BuildGraph recursively on new node assignment;

Add value returned by the previous line to the successors of the

current state:

end:

end:

```

Fig. 1. State machine construction algorithm.

successor of itself. This occurs when the circuit has settled; it will stay in a stable state until the inputs change.

For example, the queue element we describe and verify below has an input signal named Init to initialize it. The circuit should be verified under conditions in which Init is raised, stays high until the circuit has stabilized (no other inputs may change during this time), then goes low and stays low. We give Init the value 1 at the beginning of the state graph construction (the program asks for this information). In the circuit description, the input change condition for Init is given by  $Init \land stable$ . This requires Init to stay high until the circuit stabilizes. It can then continue to be high, or go low. Once it goes low, it cannot go high again because the change condition says that it can only change when it is high.

A more detailed description of the program appears in Fig. 1.

## IV. Example: A Self-Timed Queue Element

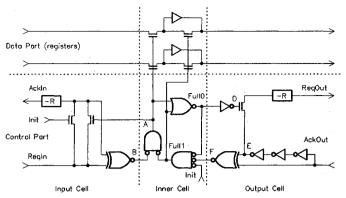

We apply this technique to a self-timed queue element. The circuit originally appeared in an article by Seitz on self-timed systems [14]. This circuit has practical importance because it can be used to connect pipelined computational units with variable processing time, maximizing the utilization of the connected units. The use of asynchronous design results in a very fast and small implementation of the queue. A diagram of the circuit is shown in Fig. 2. The queue consists of a control part and a data part. The data part is simply a shift register which has as many bits of parallel data as necessary. The control part has three major components: an input cell, an output cell, and any number of inner cells. The input and output cells convert two-cycle signals from the external world into four-cycle signals for the inner cells. The inner cells keep track of which cells of the shift register have data in them and handle the control signals to shift data through the register.

There is one unconventional component in the circuit that should be explained: the "negative resistor" (labeled "-R" in the diagram). This circuit is a chain of two inverters with a (relatively) high-value resistor feeding back from the output of

Fig. 2. Queue (FIFO) element.

the second inverter to the input of the first. This circuit stores its most recent input signal, and after two gate delays supplies the same signal on the output.

The queue is a speed-independent element: It assumes no real-time restrictions on the behavior of the circuits it is connected to. However, the internal design of the queue is *not* speed-independent. It uses a more liberal assumption that no series of 3 gates is faster than any other series of 2 gates. This is called the "3/2 rule."

We have applied our verification technique to the circuit in the case where there is a single inner cell. The unit-delay assumption is a refinement of the 3/2 rule. Any circuit satisfying the unit-delay rule certainly satisfies the 3/2 rule, but not the converse. If our verification finds a problem, then it is definitely a violation of the circuit design rules. On the other hand, a successful verification increases confidence in the circuit design but does not guarantee that the circuit is correct.

## A. Temporal Logic Specification of the Queue Element

In this subsection we give a variety of correctness conditions in CTL for the queue element. This is not a complete specification—just a sample of some interesting properties which we would like to check against the state graph constructed as in the previous section. We categorize the conditions as requiring *safety* or *liveness* properties. Informally, safety properties say that the circuit does not do anything bad, while liveness properties say that it does do something good.

First, we specify the correct behavior of the two-cycle interfaces with the external world. The following formulae apply to both the input and output cells. *ReqIn*, *ReqOut*, *AckIn*, and *AckOut* must be substituted for *req* and *ack*, as appropriate.

$$AG(\neg req \rightarrow A[\neg requ \neg ack])$$

$AG(req \rightarrow A[requack])$

$AG(\neg ack \rightarrow A[\neg ackureq])$   $AG(ack \rightarrow A[acku \neg req]).$

The first condition requires that if the *req* signal is low it must stay low until *ack* goes low; if *ack* is high because a previous request has not been acknowledged *req* is not allowed to change. The second formula gives the corresponding requirement when *req* is high. The third and fourth formulae require that *ack* not change unless *req* has the opposite value.

These previous four formulae are *safety* properties. For example, in the first formula it is not required that *ack* goes low—only that *req* cannot go high before *ack* goes low. It is also reasonable to give some liveness conditions for the two-cycle interfaces:

$$AG(reg \land \neg ack \rightarrow AFack) \quad AG(\neg reg \land ack \rightarrow AF \neg ack).$$

These formulae state that every request must inevitably be acknowledged. We do *not* require *req* to change after *ack* takes on the same value.

There is a problem in verifying these last two formulae. In a correct implementation of the queue element, if the register cell is already full and another input request arrives, the acknowledge signal for the new input must wait for the cell to become empty. This will only happen when the external circuit on the output side raises AckOut to indicate that it has read the contents of the register cell. We must assume that this external circuit responds to an output request in finite time.

The solution to this problem is to use the fairness constraint facility of the model checker. We can require a pending output request to be acknowledged inevitably by the fairness constraint

This condition says that the last request has been acknowledged. Any fair path must have infinitely many states satisfying this, so for any state in which there is a pending request ( $ReqOut \neq AckOut$ ), there is another state further along the path in which the request has been satisfied. We remind the reader that this is an assumption about the behavior of the circuit environment, not a condition to be verified. Given this constraint, the model checker checks the two liveness conditions above only over the paths in which the external circuit always responds to output requests.

There are also correctness conditions relating the input and output cells. We give a few sample formulae. First, an obvious safety condition is that if there is nothing in the inner cell  $(\neg Full 1)$  there will not be an output request until there is an input request,

$$AG(\neg Full 1)$$

$$\rightarrow A[(RegOut \leftrightarrow AckOut)u \neg (RegIn \leftrightarrow AckIn)]).$$

There are also a number of interesting liveness conditions. For example, if there is an unacknowledged input request and if the inner cell is empty, then the signal to load the shift register cell, A, will inevitably be raised,

$$AG(\neg (RegIn \leftrightarrow AckIn) \land \neg Full 1 \rightarrow AFA).$$

If the inner cell is full, there should always be an output request to make the data available,

$$AG(\neg Full \ 1 \rightarrow AX(Full \ 1 \rightarrow AF \neg (RegOut \leftrightarrow AckOut))).$$

This formula is somewhat subtle. Essentially, the nexttime operator is used to check the first state after a rising edge of *Full* 1. After this edge there must inevitably be an output request.

If the queue element is full and an output request is made and then acknowledged, the element should eventually become empty. This is specified by

$$AG(Full \ 1 \land \neg (ReqOut \leftrightarrow AckOut))$$

$$\rightarrow AX((RegOut \leftrightarrow AckOut) \rightarrow AF \neg Full 1)).$$

## B. Verifying the Circuit

When our program is used to build a state graph from the circuit description, the resulting state graph has 152 states. The input signal *Init* is set to 1 and the signals *ReqIn* and *AckOut* are set to 0 for the starting conditions (all internal signals are automatically initialized to a value that means "unknown"). We specify input change conditions requiring that the *Init* signal stay high until the circuit stabilizes, and that none of the other inputs change until *Init* goes low. Thus, the resulting state graph has a sequence of states at the beginning representing the initialization of the circuit, after which the *Init* signal stays low and the other signals are free to change. There are also input change conditions to require *ReqIn* and *AckOut* to conform to the two-cycle signaling protocol.

In actuality, the above verification conditions are modified to account for the *Init* signal: Every condition originally of the form AG(x) is transformed to  $AG(\neg Init \rightarrow x)$ , so uninitialized states are not considered in checking the formulae.

All the conditions check, except for the safety condition

$$AG(\neg Full 1$$

$$\rightarrow A[(RegOut \leftrightarrow AckOut)u \neg (RegIn \leftrightarrow AckIn)]).$$

The model checker provides a counterexample path in which there are two output requests in response to a single input request. This occurs because of a timing error in the circuit. The transistor in the output cell connected to ReqOut is on (because D=1) when AckOut goes high in response to ReqOut. The data path that eventually causes D to go low is four gates long, so D is still high when the change in AckOut propagates through the three inverters to E. This causes ReqOut to go low, creating a spurious request on the output.

It is not clear whether this phenomenon would cause a real circuit to fail—that depends on now accurately the 3/2 design rules model real circuits. However, the circuit definitely has a bug under those rules. This bug can be fixed by adding two more inverters between AckOut and E. All of the above conditions check out for the corrected circuit; however, we still cannot be sure that the resulting circuit is bug-free because the specification is incomplete and because we have not checked it under the less forgiving 3/2 timing model.

#### V. Verifying High-Level Descriptions of Circuits

In practice, many circuits are designed as finite state machines before they are implemented in hardware. For circuits designed in this manner, exhaustive simulation that constructs a finite state machine, as in the previous section, is unnecessary since the original finite state machine is already available. Therefore, we can verify the design before it is implemented in hardware. If a VLSI design tool that correctly implements finite state machines is used to layout the verified

design, we can be sure that the resulting circuit is correct.

In order to assist with the design and verification of finite state machines, we have designed a language named SML (state machine language). In addition to being useful for verification, SML also provides a succinct notation for describing complicated finite state machines. A program written in SML is compiled into a finite state machine, which can then be verified using the model checker or implemented in hardware. At Carnegie-Mellon University, we have implemented an SML compiler that runs on a VAX 11/780. We also have access to design tools that can implement a finite state machine produced by the compiler as either a ROM, an PLA, or a PAL.

## A. The Description Language and Its Semantics

An SML program represents a synchronous circuit that implements a Moore machine. At a clock transition, the program examines its input signals and changes its internal state and output signals accordingly. Since we are dealing with digital circuits where wires are either high or low, the major data type is *Boolean*. Each Boolean variable may be declared to be either an *input* changed only by the external world but visible to the program, an *output* changed only by the program but visible to the external world, or an *internal* changed and seen only by the program. The hardware implementation of Boolean variables may also be declared to be either active high or active low. The use of mixed logic in SML is permitted. Internal integer variables are also provided.

SML programs are similar in appearance to many imperative programming languages. SML statements include if, while, and loop/exit. A cobegin is provided to allow several statements to execute concurrently in lockstep. There is also a simple macro facility.

The semantics of SML programs are different from most programming languages, since we are not only interested in what a statement does, but how much time it takes to do it. In this respect, SML was influenced by the semantics of ESTEREL [2]. The complete semantics for SML will not be given here, but they will appear in a forthcoming paper [4]. A program state is an ordered pair  $\langle S, s \rangle$  consisting of a statement S and a function s that gives values to all of the identifiers. The semantics consist of a set of rewrite rules that describe how a program state can be transformed into new program state. Each rewrite rule also specifies whether it takes a clock cycle to make the transformation or not. For example, two typical rewrite rules are

$$\langle \mathbf{raise}(I); S, s \rangle \xrightarrow{1} \langle S, s' \rangle$$

where  $s' = s[I \mapsto \text{true}]$  (1)

$$\frac{E = \text{false}}{\langle \text{if } E \text{ then } S_1 \text{ endif; } S_2, s \rangle \stackrel{Q_*}{\longrightarrow} \langle S_2, s \rangle}. \tag{2}$$

The first rule states that a **raise** statement followed by an arbitrary statement S can be rewritten in one clock cycle to statement S while simultaneously changing s so that s'(I) = true. The second rule states that an **if** statement followed by an arbitrary statement  $S_2$  can be rewritten in no time to statement  $S_2$  if the condition is false.

Given any program state, we can repeatedly apply the rewrite rules to find a new state that can be reached in one clock cycle. This new state is a successor of the original state in the finite state machine. So starting from the initial program state (which consists of the entire program and a function which assigns 0 to all integers and false to all Booleans), we can repeatedly find successor states until we have built the entire finite state machine.

## B. Example: A Traffic Controller

The best way to illustrate the use of SML is by an example. We will use SML to design a traffic controller that is stationed at the intersection of a two-way highway going north and south and a one-way road going east. For the sake of simplicity, no turns are permitted. At the north, south, and east of this intersection, there is a sensor that goes high for at least one clock cycle when a car arrives. When the intersection is clear of cross traffic, the controller should raise a signal indicating that the car is permitted to cross the intersection. Once the car has crossed, the sensor that indicated the arrival of the car will go low.

Let the names of the sensors be N (north), S (south), and E (east). Furthermore, let N-Go, S-Go, and E-Go be the names of the output signals for each end of the intersection.

Now that the problem is defined, we can express the correctness conditions of the controller in CTL.

$$AG \neg (E\text{-Go} \land (N\text{-Go} \lor S\text{-Go})).$$

This formula is a safety property that is true if the controller does not permit collisions to occur. There are also several interesting liveness properties

$$AG(\neg N\text{-Go} \land N \rightarrow AFN\text{-Go})$$

$AG(\neg S\text{-Go} \land S \rightarrow AFS\text{-Go})$

$AG(\neg E\text{-Go} \land E \rightarrow AFE\text{-Go}).$

These formulas state that every request to enter the intersection is eventually answered, so the controller is starvation-free. If all three of these formulas are true, the controller is deadlock-free as well.

$$EF(N\text{-Go} \wedge S\text{-Go}).$$

This formula insures that simultaneous north and south traffic is possible. Since we want to maximize the amount of traffic, any good implementation should satisfy this formula.

In addition to specifying the desired behavior of the controller, we must also specify the behavior of the cars. In particular, we don't want a car to enter the intersection and stay there forever. Since the model checker allows the specification of fairness constraints that must be true infinitely often, we must rephrase this condition to be that the cars must be out of the intersection infinitely often. Since a car from the north is in the intersection if N-Go is true, and it stays there while N is true, the fairness constraint for cars from the north is  $\neg (N$ -Go  $\land N)$ . There are similar constraints for traffic from the south and east.

```

program intersect:

input N, S, E; output N-Go, S-Go, E-Go;

ternal NS-Lock, EW-Lock, N-Req, S-Req, E-Req;

while !(expr) do nop endwhile

endproc

io

11

loop if !N-Req & N then raise (N-Req) endif endloop

13

14

loop if !S-Req & S then raise (S-Req) endif endloop

15

16

loop if !E-Rea & E then raise (E-Rea) endif endloon

18

if N-Req then

wait (!EW-Lock);

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

40

41

42

43

44

45

46

47

48

49

50

50

51

cobegin raise (NS-Lock) | raise (N-Go) end:

if !S-Go then lower (NS-Lock) endif

lower (N-Go) | lower (N-Reg)

endif

endloop

loon

if S-Reg ther

wait (!EW-Lock):

cobegin raise (NS-Lock) | raise (S-Go) end;

wait (!S);

if !N-Go then lower (NS-Lock) endif

lower (S-Go) | lower (S-Req)

endloop

if E-Req then

raise (EW-Lock);

wait (!NS-Lock);

raise (E-Go):

cobegin lower (EW-Lock) | lower (E-Go) | lower (E-Req) end

endif

53

endprog

```

Fig. 3. A first attempt at writing a traffic controller in SML.

## C. An Implementation of the Traffic Controller in SML

One approach to this problem is to provide two locks: NS-Lock, which is true when north-south traffic is in the intersection, and EW-Lock, which is true when east-west traffic is in the intersection. Traffic from one direction is forbidden to enter the intersection if the lock in the other direction is true. Fig. 3 shows a program that uses this idea. The numbers at the beginning of each line were added for easy reference and are not part of the language.

A few comments are necessary to explain the operation of this program.

Line 5: In addition to declaring the two locks, N-Req, S-Req, and E-Req are also declared to be internal. N-Req will go high when a car arrives at the intersection from the north and go low when the car has crossed the intersection. S-Req and E-Req are similar.

Lines 7-9: Wait is a macro definition that delays until its parameter becomes true.

Line 12: If a car is not at the north end of the intersection (!N-Req), and the sensor at the north goes high (N), there is now a car at the north end of the intersection, so assert N-Req.

Lines 14 and 16: These statements do the same as Line 12 for cars from the south and east.

Lines 18-29: This statement controls traffic from the north. Once there is no traffic from the east (Line 20), the intersection is locked and the car is allowed to go (Line 21). After the car leaves the intersection (Line 22), the intersection is released if there is no traffic from the south in the intersection (!S-Go) (Line 24).

Lines 31-42: This statement controls traffic from the south. The algorithm is the same as for north traffic. If a car from the north enters the intersection (and raises NS-Lock) at the same time as a car from the south exits the intersection (and lowers NS-Lock), the conflict is resolved by leaving NS-Lock unchanged. Since NS-Lock is already high, it will remain high, so the intersection will remain locked.

Lines 44-52: This statement controls traffic from the east. Once a request is received, the intersection is locked (Line 46) and the car waits for the cross traffic to release the intersection (Line 47). When the intersection is clear, the car is permitted to cross (Line 48). After the car has crossed, the intersection is released (Line 50).

This program was compiled into a 43 state machine in approximately 10 s of CPU time on a VAX. However, the transitions of this state machine are dependent on the state of the input. In order to remove this dependence, each state had to be replaced with eight states, one for each possible

```

% /bin/time emc -c inter1.emc

CTL MODEL CHECKER (C version 2.5)

Taking input from interl.emc.

Fairness constraint: \sim (N\text{-Go \& }N).

Fairness constraint: \sim (S\text{-Go \& }S).

Fairness constraint: \sim (E\text{-Go \& }E).

Fairness constraint:

time: (798 232)

= EF(N-Go \& S-Go)

The equation is TRUE.

time: (812-236)

|=AG\sim (E-Go \& (N-Go | S-Go)).

The equation is TRUE

time: (825 241)

|=AG(N \& \sim N\text{-Go}) \rightarrow AF N\text{-Go}).

The equation is FALSE.

EF \sim (N \& \sim N\text{-Go} \rightarrow AF N\text{-Go})

is true in state 1 because of the path:

State 1: XCMP1 ESN

State 16: E-Req S-Req N-Req XCMP2

State 313: ESN E-Req S-Req EW-Lock NS-Lock N-Go XCMP39

State 313: ESN E-Req EW-Lock NS-Lock XCMP40

N \& \sim N\text{-Go} \rightarrow AFN\text{-Go}

is false in state 313 if:

1) ~(N & ~N-Go)

is false in state 313, AND

2) AF N-Go

is false in state 313.

\sim (N \& \sim N\text{-Go})

is false in state 313 because the following propositions are true:

N \sim N-Go

AF N-Go

is false in state 313 because

EG ~ N-Go

is true in state 313.

An example of such a path is:

State 313: ESNE-Req EW-Lock NS-Lock XCMP40

State 321: ESNE-Req S-Req N-Req EW-Lock NS-Lock XCMP41

State 321: ESNE-Req S-Req N-Req EW-Lock NS-Lock XCMP41

time: (886 275)

1:56 0 real

14.7 user

4.8 sys

```

Fig. 4. Verifying the first traffic controller program.

combination of inputs. An additional 30 s of CPU time was required to convert this state machine into a 344 state machine that the model checker can handle. We have already developed a new model checker algorithm that circumvents this problem and we hope to implement it in the near future.

## D. Verifying the Traffic Controller with the Model Checker

Fig. 4 shows a transcript of the model checker running on the program in Fig. 3. The numbers in parentheses are the total user cpu time and "system time," in 1/60ths of a second. As the transcript shows, the program allows simultaneous north and south traffic and is collision-free, but it is not deadlock-free. The model checker provides a counterexample that can be used to diagnose the problem. In state 312, cars from the north and the south are in the intersection, and there is a car from the east waiting to enter. Furthermore, both of the cars that are in the intersection are leaving (N and S are both false). But since N-Go is high, the car from the south doesn't release the intersection, and since S-Go is high, the car from the north does not release it either! As a result, NS-Lock is still high in state 313, so the car from the east cannot enter the intersection. When the next car from the north arrives (in state 321), it cannot enter the intersection because EW-Lock is high. But since the car from the east cannot enter the

```

program intersect;

3

output N-Go, S-Go, E-Go;

internal NS-Lock, EW-Lock, N-Req, S-Req, E-Req;

while !(expr) do nop endwhile

10

loop if !N-Req & N then raise (N-Req) endif endloop

13

loop if !S-Req & S then raise (S-Req) endif endloop

15

16

loop if !E-Req & E then raise (E-Req) endif endloop

17

18

if N-Req then

20

21

wait (!EW-Lock):

cobegin raise (NS-Lock) | raise (N-Go) end;

22

23

wait (!N):

cohegin

if !S-Go | !S then lower (NS-Lock) endif

24

25

26

27

28

lower (N-Go) | lower (N-Req)

endif

29

30

endloop

loop

if S-Req then

32

33

34

35

wait (!EW-Lock);

cobegin raise (NS-Lock) | raise (S-Go) end; wait (!S);

36

37

38

if !N-Go | !N then lower (NS-Lock) endif

39

40

lower (S-Go) | lower (S-Req)

end

endif

endloop

42

43

I

44

45

if E-Reg then

46

47

raise (EW-Lock);

wait (!NS-Lock):

raise (E-Go):

49

50

wait (!E):

cobegin lower (EW-Lock) | lower (E-Go) | lower (E-Req) end

51

endif

52

endloon

54

endprog

```

Fig. 5. The corrected traffic controller program.

intersection, EW-Lock will remain high, so we have a deadlock.

As the counterexample illustrates, the problem with the program in Fig. 3 is NS-Lock will not be lowered if cars from the north and the south exit the intersection simultaneously. A simple solution is to modify Line 24 so that NS-Lock is lowered if the car from the south is not in the intersection (!S-Go) or if the car from the south is exiting the intersection (!S). Line 37 can be changed in a similar manner. The resulting program is shown in Fig. 5. This program compiles into 31 states (248 states for the model checker). The correctness of this program is shown by the transcript in Fig. 6.

#### VI. CONCLUSION

The approaches presented here are practical for small- and medium-size sequential circuits. Verification is usually viewed as a way to guarantee correctness, and these techniques are no exception. However, we believe that these methods hold even more promise as debugging aids. Tools like those described in this paper could expedite the design process by localizing bugs quickly. They could also allow designers to improve designs more aggressively, freeing them from the natural reluctance to modify a design that is already known to work.

```

% /bin/time emc -c inter2.emc

CTL MODEL CHECKER (C version 2.5)

Taking input from inter2.emc..

Fairness constraint: \sim (N\text{-Go \& }N).

Fairness constraint: \sim (S\text{-Go \& }S).

Fairness constraint: \sim (E\text{-Go \& }E).

Fairness constraint:

time: (524 38)

= EF (N-Go & S-Go).

The equation is TRUE.

time: (535 41)

l = AG \sim (E-Go \& (N-Go | S-Go)).

The equation is TRUE

|= AG (N \& \sim N - Go \rightarrow AF N - Go).

The equation is TRUE.

time: (573 47)

|= AG (S \& \sim S\text{-}Go \rightarrow AF S\text{-}Go).

The equation is TRUE.

time: (600 48)

= AG (E & ~ E-Go \rightarrow AF E-Go).

The equation is TRUE.

time: (632.51)

1:49.0 real

10.5 user

1.0 sys

```

Fig. 6. Verifying the corrected traffic controller program.

Further research is needed in a number of areas. Timing is an important issue when verifying asynchronous sequential circuits. The unit-delay model used in Sections III and IV is easy to implement, but unrealistic. A more commonly used model in asynchronous circuit design assumes arbitrary delays in wires and/or gates. We have a technique for verifying circuits under an arbitrary gate delay model, which we have successfully applied to an asynchronous arbiter [8]. There are a variety of timing assumptions that are less conservative than arbitrary delay models, but more realistic than the unit-delay assumption. Obviously, the 3/2 model used in the design of the queue element example is one of these. Another assumes minimum and maximum delays for the circuit components. It would be useful to be able to verify circuits under these assumptions.

It is probably not practical to use these methods on large circuits, because of the corresponding size of the state graphs. Circuit designers cope with the complexity of large circuits by designing them hierarchically. It seems reasonable that the same circuits could be verified hierarchically by verifying small subcircuits in detail, then using simplified models of them as components in larger circuits. This process can be automated to some extent. If one uses a subset of CTL, small circuits can be simplified by "hiding" some of their internal nodes (more precisely, making it illegal to use them in CTL formulae) and merging groups of states that become indistinguishable into single states (this is called *restriction*) [7].

We verified the self-timed queue element in the specific case in which there was only one inner cell. In fact, there is a family of queues, each member having a different number of repeated inner cells. There are many families of circuits designed in this way, for example, systolic arrays in which the number of cells is a parameter. It would be useful to be able to verify entire families of circuits at one time, using a more general technique than the ones in this paper. We conjecture that inductive techniques could be applied to this problem.

## REFERENCES

- M. Ben-Ari, Z. Manna, and A. Pnueli, "The temporal logic of branching time," in *Proc. 8th ACM Symp. Principles Prog. Lang.*, Williamsburg, VA, Jan. 1981.

- [2] G. Berry and L. Cosserat, "The ESTEREL synchronous programming language and its mathematical semantics," Ecole Nationale Supérieune des Mines de Paris (ENSMP), Cetnre de Mathématiques Appliquées, Valbonne, France, 1984.

- [3] G. V. Bochmann, "Hardware specification with temporal logic: An example," *IEEE Trans. Comput.*, vol. C-31, Mar. 1982.

- 4] M. C. Browne and E. M. Clarke, unpublished manuscript, Dec. 1984.

- [5] R. E. Bryant, "A switch-level model and simulator for MOS digital systems," *IEEE Trans. Comput.*, Vol. C-33, Feb. 1984.

- [6] É. M. Clarke, E. A. Emerson, and A. P. Sistla, "Automatic verification of finite-state concurrent systems using temporal logic specifications: A practical approach," in *Proc. 10th ACM Symp. Principles Prog. Lang.*, Austin, TX, Jan. 1983.

- [7] E. M. Clarke and B. Mishra, "Automatic verification of asynchronous circuits," in *Proc. C-M.U. Workshop Logics of Programs*, Pittsburgh, PA, 1983, (Springer lecture notes in computer science).

- [8] D. L. Dill and E. M. Clarke, "Automatic verification of asynchronous circuits using temporal logic," in *Proc. 1985 Chapel Hill Conf.* VLSI, E. Fuchs, Ed. Rockville, MD: Computer Science.

- [9] E. A. Emerson and E. M. Clarke, "Characterizing properties of parallel programs as fixpoints," in *Proc. 7th Int. Collog. Automata, Lang. and Prog.*, Springer lecture notes in computer science, no. 85, 1981

- [10] J. Halpern, Z. Manna, and B. Moszkowski, "A hardware semantics based on temporal intervals," Dep. Comput. Sci., Stanford Univ., Stanford, CA, Rep. STAN-CS-83-963, Mar. 1983.

- [11] Y. Malachi and S. S. Owicki, "Temporal specifications of self-timed systems," in VLSI Systems and Computations, H. T. Kung, B. Sproull, and G. Steele, Eds. Rockville, MD: Computer Science, 1981.

- [12] C. A. Mead and L. A. Conway, Eds. Introduction to VLSI Systems. Reading, MA: Addison-Wesley, 1980.

- [13] R. Milner, A Calculus of Communicating Systems. Edinburgh, Scotland: Edinburgh Press, 1980.

- [14] C. Seitz, "System timing," in *Introduction to VLSI Systems*, C. Mead and L. Conway, Eds. Reading, MA: Addison-Wesley, 1980.

Michael C. Browne received the B.S. degree in computer engineering from Lehigh University, Bethlehem, PA, in 1982.

He is currently working on his doctoral dissertation at Carnegie-Mellon University, Pittsburgh, PA.

His interests include logics of programs and programming language semantics.

Edmund M. Clarke received the B.A. degree in mathematics from the University of Virginia, Charlottesville, in 1967, the M.A. degree in mathematics from Duke University, Durham, NC, in 1968, and the Ph.D. degree in computer science from Cornell University, Ithaca, NY, in 1976.

After leaving Cornell, he taught in the Department of Computer Science, Duke University, Durham, NC, for two years. In 1979 he moved to Harvard University, Cambridge, MA where he was an Assistant Professor of Computer Science in the

Division of Applied Sciences. He has been an Associate Professor of Computer Science at Carnegie-Mellon University, Pittsburgh, PA, since 1983. His interests include distributed systems, programming language semantics, theory of computation, and VLSI.

Dr. Clarke is a member of the Association for Computing Machinery, Sigma Xi, and Phi Beta Kappa.

David L. Dill received the Sc.B. degree in electrical engineering (computer science option) from the Massachusetts Institute of Technology, Cambridge, MA, in 1979, and the M.A. degree in computer science from Carnegie-Mellon University, Pittsburgh, PA, in 1982.

He is currently working on his doctoral dissertation at Carnegie-Mellon on the topic of verifying asynchronous circuits. His interests include programming languages, compilers, and applying concepts of software systems to hardware.

Mr. Dill is a member of the Association for Computing Machinery.

Bud Mishra received the B.Tech. degree from the Indian Institute of Technology, the M.S. and Ph.D. degrees, both from Carnegie-Mellon University, Pittsburgh, PA.

He joined the faculty of New York University, New York, in the Fall of 1985.