# **Ballistic InAs Nanowire Transistors**

Steven Chuang, †,|| Qun Gao, † Rehan Kapadia, †,|| Alexandra C. Ford, †,§,|| Jing Guo, † and Ali Javey\*,†,§,||

Supporting Information

ABSTRACT: Ballistic transport of electrons at room temperature in top-gated InAs nanowire (NW) transistors is experimentally observed and theoretically examined. From length dependent studies, the low-field mean free path is directly extracted as ~150 nm. The mean free path is found to be independent of temperature due to the dominant role of surface roughness scattering. The mean free path was also theoretically assessed by a method that combines Fermi's golden rule and a numerical Schrödinger-Poisson simulation to determine the surface scattering potential with the theoretical calculations being consistent with experiments. Near ballistic transport (~80% of the ballistic limit) is demonstrated experimentally for transistors with a channel

length of ~60 nm, owing to the long mean free path of electrons in InAs NWs.

KEYWORDS: Ballistic transport, scattering, surface roughness, mean free path, quantization, subbands

he scaling of electronic transistors for performance and density enhancement has been a major driving force behind the advancement of modern integrated circuit technology. As scaling becomes increasingly difficult, the electronics industry is moving toward unconventional materials and nonplanar structures. Both of these aspects are inherent in InAs nanowire (NW) transistors, making them a promising platform for future high-performance transistors. 1-5 One critical goal in scaling is to obtain ballistic devices, 6-9 where carriers are transported through the channel without undergoing scattering events. Ballistic devices are highly desirable as they offer minimal resistive voltage drop in the channel. Hence, ballistic operation presents the upper limit for the ON-state conductance of a transistor. InAs can potentially be used to fabricate ballistic transistors given its relatively long bulk electron mean free path  $(\lambda)$ . In this regard, detailed characterization of  $\lambda$  of InAs NWs is required, 11,12 especially as a function of subband population. Recently, we reported the direct observation of one-dimensional (1D) subbands in the electrical transfer characteristics of long-channel ( $L \sim 8 \mu m$ ) InAs NW field-effect transistors (FETs).<sup>13</sup> Given the large Bohr radius of InAs ( $\sim$ 34 nm),<sup>14</sup> strong quantization with prominent subband spacing is readily observed for sub-50 nm diameter NWs. The devices were passivated by a ZrO2 dielectric that resulted in the lowering of surface disorder, and thereby allowing for the direct mapping of the transport in individual 1D subbands. Given that for a ballistic NW, each 1D subband contributes a quantum unit of conductance of  $G_0 = 2e^2/h$ , <sup>15</sup> the

transmission probability and thereby  $\lambda$  can be directly assessed from electrical measurements. Here, by fabricating InAs NW FETs with different channel lengths down to ~60 nm, we experimentally extract  $\lambda \sim 150$  nm for electron transport in the first and second subbands. The experimental results are consistent with theoretical calculations of momentum relaxation times associated with surface roughness (SR) scattering mechanisms. Given the relatively long mean free path in InAs NWs, ultrashort channel FETs with  $L\sim 60$  nm are shown to exhibit a conductance of  $\sim 0.8G_0$  for the first subband, suggesting electron transport at ~80% of the ballistic limit, independent of temperature.

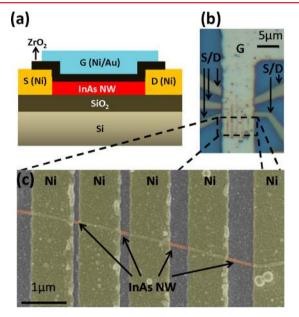

InAs NWs used in this study were grown by a vapor transport technique described previously. <sup>16</sup> The NWs were suspended in anhydrous ethanol and drop casted over a Si/ SiO<sub>2</sub> substrate. Multiple Ni (~40 nm thick) source/drain (S/ D) contact electrodes of varying spacing ( $L \sim 510-60 \text{ nm}$ ) were defined on each NW by electron-beam lithography, metallization, and lift-off. The sample was then annealed at 185 °C under vacuum in order to reduce the contact resistance at the Ni/InAs interface. Previous studies have shown that annealed Ni contacts to InAs NWs exhibit ohmic properties without parasitic resistances.  $^{17}$  A 15 nm  $\rm ZrO_2$  gate dielectric was deposited at 130 °C via atomic layer deposition (ALD), followed by a 130 °C forming gas anneal for 30 min to improve

Received: November 4, 2012 Published: December 20, 2012

<sup>&</sup>lt;sup>†</sup>Electrical Engineering and Computer Sciences, University of California, Berkeley, California 94720, United States

<sup>&</sup>lt;sup>‡</sup>Electrical and Computer Engineering, University of Florida, Gainesville, Florida 32611, United States

<sup>§</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, California 94720, United States

Berkeley Sensor and Actuator Center, University of California, Berkeley, California 94720, United States

Nano Letters Letter

the dielectric/InAs interface quality. Finally, a single Ni/Au (20/30 nm) top-gate electrode overlapping the S/D contacts was defined via photolithography. Figure 1 shows a cross-sectional schematic, optical image, and scanning electron micrograph (SEM) of the fabricated devices.

**Figure 1.** (a) Cross-sectional schematic of a top-gated InAs NW device explored in this study. (b) Optical image and (c) false color SEM image of the fabricated devices, featuring one nanowire contacted by multiple source/drain fingers for length dependent measurements.

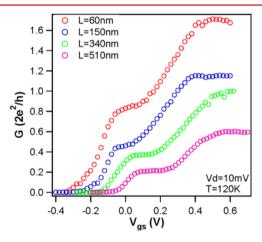

Low-field transfer characteristics of InAs NW FETs with  $L \sim$  60, 150, 340, and 510 nm at 120 K are shown in Figure 2. All

Figure 2. (a)  $G-V_{GS}$  plots for 26 nm diameter InAs NW FETs with varying channel lengths. The plots have been shifted in  $V_{GS}$  for presentation clarity.

devices are fabricated on a single NW. The diameter of the NW was measured by atomic force microscopy (AFM) as  $\sim$ 31 nm, which corresponds to an actual InAs diameter of  $\sim$ 26 nm considering the  $\sim$ 2.5 nm thick native oxide previously observed under transmission electron microscopy (TEM) for NWs grown by the same method. <sup>19</sup> Conductance was obtained by dividing the measured drain current by the applied drain voltage ( $V_{\rm DS}$  = 10 mV) and plotted in units of  $G_{\rm o}$ . Distinct step-

like features are observed in each conductance plot, which are due to quantization of the channel density of states, with each step attributed to the population of a single 1D subband. Importantly, the conductance value for each subband can be easily extracted from the plateaus of the  $G-V_{\rm GS}$  plots. Note that as we previously reported, the height of the second subband plateau is approximately twice that of the first subband for long channel devices where the transport is largely diffusive, <sup>13</sup> as evident in the  $L\sim510$  nm device (Figure 2). This phenomenon is due to the two-fold degeneracy of the second subband arising from the structural symmetry of cylindrical NWs. The conductance ratio of the second to first plateaus decreases as the channel length is reduced. This observation can be attributed to the difference in parasitic contact resistance  $R_c$  of the two subbands.

The total resistance of each subband plateau can be analytically expressed as<sup>20</sup>

$$R = R_{\rm c} + R_{\rm q} \left( 1 + \frac{L}{\lambda} \right)$$

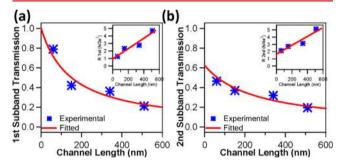

where  $R_{\rm q}$  is the quantum resistance, which is  $1/G_{\rm o}$  for the first subband and  $1/2G_{\rm o}$  for the second subband due to degeneracy. By plotting R versus L for each subband plateau,  $\lambda$  can be extracted from the inverse of the slope, and  $R_{\rm c}$  can be extracted from the y-intercept (Figure 3a,b, inset). The extracted  $R_{\rm c}$

**Figure 3.** Experimental and fitted transmission probability versus channel length plots for the (a) first and (b) second subbands. Resistance versus length plots are shown in the insets.

values are  $\sim 0$  and  $0.3/G_o$  for the first and second subbands, respectively. The absence of contact resistance for the first subband is expected given the negative Schottky barrier heights previously reported for bulk InAs/metal interfaces. The presence of a contact resistance for the second subband is indicative of a small Schottky barrier height to the higher energy subbands. As noted later in the manuscript, the device resistance is independent of temperature, suggesting that the Schottky barrier height and width must be small and thin, respectively, with electron tunneling at the metal interface being the primary source of carrier injection. Given that the barrier heights to the first two subbands are either negative or very small, the  $V_{\rm GS}$  dependence of  $R_{\rm c}$  is assumed to be negligible.

From the inverse slope of R versus L (Figure 3a,b inset), the electron mean free paths for the first and second subbands are extracted as  $\lambda_{n=1} \sim 150 \pm 40$  nm and  $\lambda_{n=2} \sim 160 \pm 50$  nm, respectively, which is in good agreement with previously extracted values using other techniques. By normalizing the observed G of 1st and 2nd subbands by  $G_o$  and  $2G_o$ , respectively, we can obtain the transmission coefficient T of carriers traversing our devices, which gauges how close the

Nano Letters Letter

subband conductance of the devices is to the theoretical limit of scaling. Plots of T versus L for the first two subbands are shown in Figure 3a,b. The shortest device ( $L \sim 60$  nm) in our study exhibits a T of  $\sim$ 80%, which is the highest value reported for inorganic semiconductors to date. The results highlight the near ballistic transport in InAs NWs when  $L < \lambda$ .

In order to better understand the observed transport characteristics,  $\lambda$  values due to SR scattering were assessed theoretically by a method that combines Fermi's golden rule and a numerical Schrödinger-Poisson simulation to determine the SR scattering potential. SR scattering was assumed to be the dominant scattering mechanism according to previous InAs NW and thin film mobility studies 14,19 and the lack of temperature dependence in transmission probability (shown later in this paper). The SR is described statistically by an exponentially decaying autocorrelation function with the parameters  $\Delta_{\rm m}$  (the RMS SR magnitude) and  $L_{\rm c}$  (the correlation length along the axis direction). Only SR in the axial direction of the NW is considered. From the calculated momentum relaxation time  $\tau_{sr}$ ,  $\lambda$  is calculated as  $\lambda = \nu_F \tau_{sr}$ , where  $v_{\rm F}$  is the initial Fermi velocity of the carrier. The details of this simulation approach are described in the Supporting Information. The results indicate that the SR parameters of  $\Delta_{\rm m} \approx 0.3$  nm and  $L_{\rm c} \approx 6$  nm result in  $\lambda \sim 175$  and 138 nm for the first and second subband at ~25 meV above the subband edge, in which 25 meV is about one half of the spacing between the first and second subbands. These theoretical values are consistent with the extracted experimental values. The low density-of-states (DOS) of scattering final states arising from the quasi-1D structure and low effective mass of InAs contributes to the long  $\lambda$ . Furthermore, the calculated  $\lambda$  of the first subband is slightly larger than that of the second subband due to the following reason. The scattering potential matrix element square of the second intrasubband scattering is about a factor of ~1.27 larger than that of the first subband, as calculated by Schrödinger-Poisson simulations, because the charge centroid of the second subband is closer to the surface. The experimentally extracted values for the first and second subbands, however, are nearly identical most likely due to the uncertainty in the experimental values.

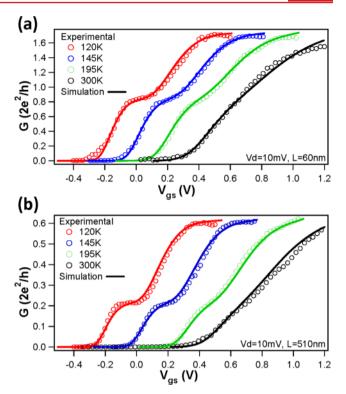

Next, we focus on the temperature-dependent transport of InAs NWs. Figure 4 shows the transfer characteristics for  $L \sim$ 60 nm (Figure 4a) and  $L \sim 510$  nm (Figure 4b) NW devices as a function of temperature (120-300 K). For both channel lengths, increasing the temperature only causes the broadening of the subbands population (i.e., conductance steps), without a change in the overall conductance of the device. Modeling was performed to shed light on the temperature dependency of the transfer characteristics. 13 Briefly, the subband density versus energy for a NW was obtained by analytically solving Schrodinger's equation for the device. The energy axis was converted to gate voltage by the relationship  $V_{GS} = E/e - (Q/e^{-1})$  $C_{ins}$ ), where E is electron energy, Q is the total charge in the NW, and  $C_{\rm ins}$  is the gate capacitance. The gate capacitance was obtained by a Poisson simulation as  $2.57 \times 10^{-10}$  F/m.<sup>22</sup> The following term,  $\Delta V_{\rm g} = \Delta Q_{\rm it}/C_{\rm ins}$ , was added to the previous calculations to account for a density of interface traps  $(D_{\rm it})$  of 3 × 10<sup>12</sup> states/cm<sup>2</sup> eV as previously reported for InAs/ZrO<sub>2</sub> interfaces<sup>23</sup> with  $\Delta Q_{it} = \Delta E D_{it}$ . A gate coupling factor of 0.8 was applied to  $C_{ins}$  to fit the data for the L=60 nm device, justified by the reduction of gate coupling in short channel devices. Each step in the subband density was multiplied by its corresponding experimental transmission probability to convert

**Figure 4.** Temperature dependent  $G-V_{\rm GS}$  plots for (a) L=60 nm and (b) L=510 nm InAs nanowire devices. Both experiment (open circles) and modeling (solid lines) data are presented. The plots have been shifted in  $V_{\rm GS}$  for presentation clarity.

the y-axis to conductance. The resulting curve was then broadened with the Fermi function. The curves from this model agree well with the experimental results, indicating that the transfer characteristics of these devices can be described by focusing on the available states for conduction, as opposed to the well-known diffusive transport MOSFET equations. Importantly, note that the transmission probability and gate coupling fitting parameters were kept constant over all temperatures. It can easily be seen that the experimental current levels do not drop below the model, indicating that transmission through the NWs does not degrade with temperature. Two deductions can be made from this temperature dependency observation. First, the  $\lambda$  extracted from the transmission probability values does not depend on temperature, implying that the dominant scattering mechanism is temperature independent SR scattering. A similar conclusion was previously made from the mobility analysis of long-channel InAs NW FETs. 19 Second, the transmission values extracted at 120 K can be extended to room temperature, implying that the  $L \sim 60$  nm device is  $\sim 80\%$  ballistic at room temperature.

In summary, the mean free path for carrier scattering in InAs NW FETs is directly extracted for electron transport in the first and second subbands by examining resistance as a function of channel length. Because of the observation of discrete subband transport in the transfer characteristics, direct analysis of the ballistic transport can be deduced with  $L\sim60$  nm devices exhibiting near-ballistic transport (~80% ballistic) independent of temperature. This represents one of the most ballistic device systems reported to-date at room temperature, owing to the relatively long mean free path of ~150 nm for the first subband transport. Surface roughness scattering is shown to be the dominant scattering mechanism. In the future, further improve-

Nano Letters Letter

ment of the surface properties and reducing the SR could potentially enhance the mean free path of the experimental NW FETs. Most importantly, this work provides a platform for the study of ultrascaled, nonplanar devices based on III—V material systems where quantization plays a major role in determining the electrical properties, given their relatively large Bohr radius.

#### ASSOCIATED CONTENT

### Supporting Information

Modeling surface roughness scattering. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: ajavey@eecs.berkeley.edu.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This work was funded by Intel, FCRP/MSD Focus Center and NSF E3S Center. The materials synthesis and characterization part of this work was partially supported by the Director, Office of Science, Office of Basic Energy Sciences, Materials Sciences and Engineering Division, of the U.S. Department of Energy under Contract No. DE-AC02-05CH11231. A.J. acknowledges a Sloan Research Fellowship, NSF CAREER Award, and support from the World Class University program at Sunchon National University. R.K. acknowledges an NSF Graduate Fellowship.

#### REFERENCES

- (1) Dayeh, S. A.; Aplin, D. P. R.; Zhou, X.; Yu, P. K. L.; Yu, E. T.; Wang, D. High Electron Mobility InAs Nanowire Field-Effect Transistors. *Small* **2007**, *3*, 326–332.

- (2) Alam, K. Transport and Performance of a Gate All Around InAs Nanowire Transistor. Semicond. Sci. Technol. 2009, 24, 085003.

- (3) Thelander, C.; Froberg, L. E.; Rehnstedt, C.; Samuelson, L.; Wernersson, L. E. Vertical Enhancement-Mode InAs Nanowire Field Effect Transistor with 50-nm Wrap Gate. *IEEE Electron Device Lett.* **2008**, 29, 206–208.

- (4) Thelander, C.; Rehnstedt, C.; Froberg, L. E.; Lind, E.; Martensson, T.; Caroff, P.; Lowgren, T.; Ohlsson, B. J.; Samuelson, L.; Wernersson, L. E. Development of a Vertical Wrap-Gated InAs FET. *IEEE Trans. Electron Devices* **2008**, *55*, 3030–3036.

- (5) Bessire, C. D.; Björk, M. T.; Schmid, H.; Schenk, A.; Reuter, K. B.; Riel, H. Trap-Assisted Tunneling in Si-InAs Nanowire Heterojunction Tunnel Diodes. *Nano Lett.* **2011**, *11*, 4159–4199.

- (6) Lu, W.; Xiang, J.; Timko, B. P.; Wu, Y.; Lieber, C. M. One-dimensional hole gas in germanium/silicon nanowire heterostructures. *Proc. Natl. Acad. Sci. U.S.A.* **2005**, *102*, 10046.

- (7) Biercuk, M. J.; Mason, N.; Martin, J.; Yacoby, A.; Marcus, C. M. Anomalous Conductance Quantization in Carbon Nanotubes. *Phys. Rev. Lett.* **2005**, *95*, 069902.

- (8) Xiang, J.; Vidan, A.; Tinkham, M.; Westervelt, R. M.; Lieber, C. M. Ge/Si nanowire mesoscopic Josephson junctions. *Nat. Nanotechnol.* **2006**, *1*, 208.

- (9) Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. Ballistic Carbon Nanotube Transistors. *Nature* **2003**, 424, 654–657.

- (10) Inoue, K.; Takayanagi, H. Local Tunneling Spectroscopy of a Nb/InAs/Nb Superconducting Proximity System with a Scanning Tunneling Microscope. *Phys. Rev. B* **1991**, *43*, 6214–6215.

- (11) Zhou, X.; Dayeh, S. A.; Aplin, D.; Wang, D.; Yu, E. T. Scanned Electrical Probe Characterization of Carrier Transport Behavior in InAs Nanowires. *J. Vac. Sci. Technol., B* **2006**, *24*, 2036.

(12) Zhou, X.; Dayeh, S. A.; Aplin, D.; Wang, D.; Yu, E. T. Direct Observation of Ballistic and Drift Carrier Transport Regimes in InAs Nanowires. *Appl. Phys. Lett.* **2006**, *89*, 053113.

- (13) Ford, A. C.; Kumar, S. B.; Kapadia, R.; Guo, J.; Javey, A. Observation of Degenerate One-Dimensional Sub-Bands in Cylindrical InAs Nanowires. *Nano Lett.* **2012**, *12*, 1340–1343.

- (14) Takei, K.; Fang, H.; Kumar, S. B.; Kapadia, R.; Gao, Q.; Madsen, M.; Kim, H. S.; Liu, C.-H.; Chueh, Y.-L. Plis, etc. Quantum Confinement Effects in Nanoscale-Thickness InAs Membranes. *Nano Lett.* **2011**, *11*, 5008–5012.

- (15) Datta, S. Quantum Transport: Atom to Transistor; Cambridge University Press: New York, 2005.

- (16) Ford, A. C.; Ho, J. C.; Fan, Z.; Ergen, O.; Altoe, V.; Aloni, S.; Razavi, H.; Javey, A. Synthesis, Contact Printing, and Device Characterization of Ni-Catalyzed, Crystalline InAs Nanowires. *Nano. Res.* **2008**, *1*, 32–39.

- (17) Chueh, Y.-L.; Ford, A. C.; Ho, J. C.; Jacobson, Z. A.; Fan, Z.; Chen, C.-Y.; Chou, L.-J.; Javey, A. Formation and Characterization of Ni<sub>x</sub>InAs/InAs Nanowire Heterostructures by Solid Source Reaction. *Nano Lett.* **2008**, *8*, 4528–4533.

- (18) Takei, K.; Chuang, S.; Fang, H.; Kapadia, R.; Liu, C.-H.; Nah, J.; Kim, H. S.; Plis, E.; Krishna, S.; Chueh, Y.-L; et al. Benchmarking the Performance of Ultrathin Body InAs-On-Insulator Transistors as a Function of Body Thickness. *Appl. Phys. Lett.* **2011**, *99*, 103507.

- (19) Ford, A. C.; Ho, J. C.; Chueh, Y.-L.; Tseng, Y.-C.; Fan, Z.; Guo, J.; Bokor, J.; Javey, A. Diameter-Dependent Electron Mobility of InAs Nanowires. *Nano Lett.* **2009**, *9*, 360–365.

- (20) Datta, S. Electronic Transport in Mesoscopic systems; Cambridge University Press: New York, 1997.

- (21) Wieder, H. H. Surface and Interface Barriers of  $In_xGa_{1-x}As$  Binary and Ternary Alloys. *J. Vac. Sci. Technol., B* **2003**, 21, 1915–1919

- (22) Nextnano<sup>3</sup>. Available on-line: http://www.nextnano.de.

- (23) Ko, H.; Takei, K.; Kapadia, R.; Chuang, S.; Fang, H.; Leu, P. W.; Ganapathi, K.; Plis, E.; Kim, H. S.; Chen, S.-Y.; et al. Ultrathin Compound Semiconductor on Insulator Layers for High Performance Nanoscale Transistors. *Nature* **2010**, *468*, 286–289.

# **Ballistic InAs Nanowire Transistors**

Steven Chuang<sup>1,4</sup>, Qun Gao<sup>2</sup>, Rehan Kapadia<sup>1,4</sup>, Alexandra C. Ford<sup>1,3,4</sup>, Jing Guo<sup>2</sup>, Ali Javey<sup>1,3,4</sup>,\*

<sup>1</sup>Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, 94720

<sup>2</sup>Electrical and Computer Engineering, University of Florida, Gainesville, FL, 32611

<sup>3</sup>Materials Sciences Division, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

<sup>4</sup>Berkeley Sensor and Actuator Center, University of California, Berkeley, CA, 94720

\* Corresponding author: ajavey@eecs.berkeley.edu

# **Supporting Information**

# Modeling surface roughness (SR) scattering

The theoretical model of SR scattering is based on the Born approximation and self-consistent solutions of the Schrodinger and Poisson equations [1]. By describing the SR statistically using an exponentially decaying autocorrelation function, the rate due to SR scattering is expressed as [2,3],

$$\frac{1}{\tau_{SR}(E)} = \frac{2 \pi e^2 M_S D_f(E)}{\hbar} \sqrt{2} \Delta_m^2 L_c \left( 1 + \frac{L_c^2 q^2}{2} \right)^{-1} (1 - \cos \Box)$$

where  $D_f(E)$  is the density of states for the scattering final states,  $L_c$  is the correlation length along axial direction,  $\Delta_m$  is the RMS SR magnitude, q is the axial wavevector along the z-direction, and  $\Box = \pi$  for backscattering in 1D transport. Only SR in the axial direction of the NW is considered and the SR in the azimuthal direction is neglected [3]. The validity of this assumption will be discussed later. The expression is different from the equation of the SR scattering rate in planar MOSFETs because the autocorrelation is related to its spectral function through a one-dimensional rather than two-dimensional Fourier transform for a NW with SR only along the axial direction.

The matrix element square of perturbing potential M<sub>s</sub> is defined as

$$\mathbf{M}_{\mathrm{snn}} = \left| \int \Psi_{\mathrm{n}} \left[ \frac{\Delta V_{\mathrm{m}}}{\Delta} \right] \Psi_{\mathrm{n}} d\mathbf{r} \right|^{2}$$

where  $\Psi_n$  is the envelope function for  $n^{th}$  subband and  $\Delta V_m$  is the SR perturbing potential which is calculated as the electrostatic potential variation by perturbing the NW radius by  $\Delta$  using a numerical self-consistent Schrödinger-Poisson simulation of

the NW cross section [1]. From the momentum relaxation scattering rate, the mean free path is obtained by using  $\lambda$  (E) =  $v_F$ (E)  $\tau_{SR}$ (E), where  $v_F$  is the initial Fermi velocity of the carrier.

Using numerical self-consistent Schrodinger-Poisson calculations [4], the matrix element squares are calculated as[1]  $M_{S11}\approx (17~\text{mV/nm})^2$ , and  $M_{S22}/M_{S11}\approx 1.27$ .  $\lambda$  is calculated for a NW radius  $R_{NW}\approx 13\text{nm}$  at the energies of E-E<sub>C1</sub> $\approx 25\text{meV}$  and E-E<sub>C2</sub> $\approx 25\text{meV}$  for the 1st and 2nd subbands, in which  $E_{ci}$  is the ith subband edge. The values of  $\lambda_{n=1}\sim 175\text{nm}$  and  $\lambda_{n=2}\sim 138\text{nm}$  are obtained by using  $\Delta_{m}\approx 0.3\text{nm}$  and  $L_{c}\approx 6$  nm as fitting parameters.

## References

- [1] Gámiz, F.; Roldán, J. B.; Cartujo-Cassinello, P.; López-Villanueva, J. A.; Cartujo, P. J. Role of Surface-Roughness Scattering in Double Gate Silicon-On-Insulator Inversion layers. *Appl. Phys.* **2001**, 89, 1764-1770.

- [2] Goodnick, S. M.; Ferry, D. K.; Wilmsen, C. W.; Liliental, Z.; Fathy, D.; Krivanek, O. L. Surface Roughness at the Si(100)-SiO<sub>2</sub> Interface. *Phys. Rev. B* **1985**, 32, 8171-8186.

- [3] Lenzi, M.; Gnudi, A; Reggiani, S.; Gnani, E.; Rudan, M.; Baccarani, G. Semiclassical Transport in Silicon Nanowire FETs Including Surface Roughness. Journal of Computational Electronics, **2008**, 7, 355-358.

- [4] Ford, A. C.; Kumar, S. B.; Kapadia, R.; Guo, J.; Javey, A. Observation of Degenerate One-Dimensional Sub-Bands in Cylindrical InAs Nanowires. *Nano. Lett.* **2012**, 12, 1340-1343.