∂ Open access • Proceedings Article • DOI:10.1109/SMACD.2016.7520741

# Basic analog and digital circuits with a-IGZO TFTs — Source link 🖸

Pydi Ganga Bahubalindruni, Vitor Grade Tavares, Pedro Barquinha, Rodrigo Martins ...+1 more authors

Institutions: University of Porto, Universidade Nova de Lisboa

Published on: 27 Jun 2016 - International Conference on Synthesis, Modeling, Analysis and Simulation Methods and

Applications to Circuit Design

Topics: Mixed-signal integrated circuit, Logic level, Digital electronics, NMOS logic and Integrated injection logic

# Related papers:

- · Low-Power Bootstrapped Rail-to-Rail Logic Gates for Thin-Film Applications

- · Organic Digital Logic and Analog Circuits Fabricated in a Roll-to-Roll Compatible Vacuum-Evaporation Process

- · High-Speed Plastic Integrated Circuits: Process Integration, Design, and Test

- · Some analog building blocks for TFT circuits

- · Comparison of MOSFET logic circuits

# Basic Analog and Digital Circuits with a-IGZO TFTs

Pydi Ganga Bahubalindruni\*, Vítor Tavares<sup>‡</sup>, Pedro Barquinha<sup>†</sup>, Rodrigo Martins<sup>†</sup> and Elvira Fortunato<sup>†</sup>

\*IIITD, Okhla Industrial Estate, Phase III, New Delhi, India - 110020 e-mail: (bpganga@iiitd.ac.in).

†CENIMAT/I3N, Departamento de Ciência dos Materiais, Faculdade de Ciências e Tecnologia, FCT,

Universidade Nova de Lisboa and CEMOP-UNINOVA, 2829-516 Caparica, Portugal.

<sup>‡</sup>INESC TEC and Faculty of Engineering, University of Porto, Campus FEUP, Rua Dr. Roberto Frias, 378, 4200-465 Porto, Portugal.

Abstract—This paper presents the characterization of fundamental analog and digital circuits with a-IGZO TFTs from measurements performed at normal ambient. The fundamental blocks considered in this work include digital logic gates, a low-power single stage high-gain amplifier with capcacitive bootstrapping and a level shifter/buffer. These circuits are important functional blocks in analog/Mixed signal IC design with oxide TFTs. Being fabricated at low temperature (< 200 °C), they can find potential applications in low-cost large-area flexible systems. Index Terms—Low-power circuits, high-gain amplifier, a-IGZO TFT.

### I. Introduction

Transparent conductive oxides (TCO), especially amorphous indium gallium zinc oxide (a-IGZO), as a semiconductor in thin-film-transistors (TFTs), is gaining considerable attention, because of its higher mobility compared to a-Si:H and organic TFTs and low-temperature fabrication [1], [2]. Though a-IGZO TFT technology is mainly meant for displays [3], its applications are extending to other low-cost large-area systems including wearable technology and RFIDs [4]. Consequently, analog/mixed signal design with this technology is gaining significant interest.

In spite of several advantages it offers, the technology imposes few limitations on circuit design, mainly due to:

- Lack of reliable complementary (p-type) transistor: Forming p-type oxide semiconductors [5], [6] is showing to be very difficult to accomplish, and those reported present a very poor hole-mobility [7]. Copper and tin based semiconductor oxides are gaining supporters as a possible basis for p-type oxide material [8]. However, p-type devices with good electrical characteristics, closer to the n-type have not yet been reported.

- Device electrical mobility is orders of magnitude lower when compared to the crystalline silicon.

Nevertheless, some work has already been reported towards basic digital circuit design, such as the transparent two-input logic gates operating up to  $5\,\mathrm{kHz}$  and fabricated at high temperature ( $600\,^\circ\mathrm{C}$ ) [9]. However, this work presents the characterization of logic gates with frequency of operation that goes up to  $10\,\mathrm{kHz}$  and fabricated at low temperature ( $<200\,^\circ\mathrm{C}$ ). An operational amplifier reported in [10] has  $16\,\mathrm{TFTs}$  to accomplish a gain of  $18.7\,\mathrm{dB}$  with a power

consumption of 0.9 mW. This paper presents a single-stage bootstrap amplifier based on a topology with three TFTs and a capacitor. It is showing a similar gain (18.6 dB) but much lower power consumption (0.3 mW). Consequently this circuit could find potential applications in wearable technologies or in battery assisted systems, where low power consumption is required. In addition to these circuits a level shifter is also characterized, which can also function as a buffer. This circuit is formed with four transistors. It can act not only as a driving circuit but also to lower the DC level of the signal by a significant amount, if needed. Note that all the circuits reported in this paper are confined to n-type TFTs.

## II. CIRCUIT DESIGN AND FABRICATION

# Logic Gates

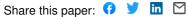

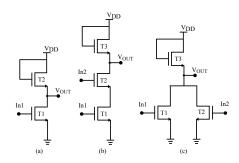

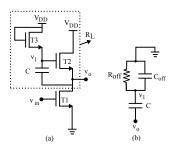

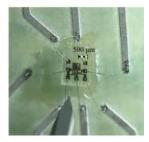

An inverter, two-input NAND and NOR gates circuit schematics are shown in Fig. 1. The NAND gate is formed by a series connection of two driving transistors (width:  $480\,\mu\text{m}$ ) with a diode connected load (width:  $40\,\mu\text{m}$ ). On the other hand, a NOR gate is designed with a parallel connection of two driving transistors and a diode connected load. A NAND gate and a single TFT micrograph with wire-bonding are presented in Fig. 2. For an inverter, when the input is low, T1 turns 'off'

Fig. 1. Logic gate schematics (a) Inverter (b) Two-input NAND (c) Two-input NOR

and no current flows in the circuit, resulting in a high output state, close to  $V_{DD}$  -  $V_{TH}$ . On the other hand, when the input is high T1 turns 'on' and causes a current flow that leads to a voltage drop on the diode connected transistor (T2). The output will be low, but not exactly zero due to the voltage drops on

Fig. 2. (a) Two input NAND gate (b) An isolated TFT with wire-bonding

the conducting transistors. For the NAND gate, when any of the inputs is low at least one of the transistors will be 'off' and no current flows in the circuit. The output becomes high, otherwise the output becomes low but not exactly to ground for the same reasons of the inverter. A similar reasoning can be applied to the NOR gate.

# Capacitive bootstrap amplifier (Amplifier1)

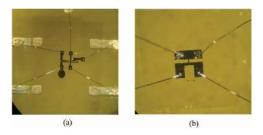

A high-gain topology only with n-type enhancement transistors is shown in Fig. 3a, where A<sub>f</sub> is the feedback factor. Its small signal equivalent is shown in Fig. 3b. When A<sub>f</sub> is one, signal levels at gate and source of T2 become equal.

Fig. 3. High-gain amplifier topology employing positive feedback, only with n-type transistors (a) Schematic (b) Small signal equivalent

By applying KCL at vo in Fig. 3b,

$$A = \frac{v_o}{v_{in}} = \frac{-g_{m1}}{(1 - A_f)g_{m2} + g_{ds2} + g_{ds1}} \tag{1}$$

$$A = -g_{m1}(R_L//r_{ds1}) (2)$$

where,

$$R_L = \frac{1}{(1 - A_f)g_{m2} + g_{ds2}}$$

(3)

By making A<sub>f</sub> close to unity, the effective active load resistance sets to  $R_L \approx \frac{1}{g_{ds2}} = r_{ds2}$ , this results in

$$A \approx -g_{m1}(r_{ds1}//r_{ds2}) \tag{4}$$

In order to guarantee a stable behavior, A<sub>f</sub> must always be kept below unity. Based on the topology shown in Fig. 3a, a highgain amplifier circuit schematic is presented in Fig. 4a. This circuit is referred to as Amplifier1 from here on. In this circuit, the active load (R<sub>L</sub>) is formed by T2, T3 and C. Transistor T3 is in cutoff, hence, its effective off resistance is significantly high. Due to the transistor intrinsic capacitance, T3 can be viewed as a parallel combination of a resistor and capacitor

Fig. 4. (a) High gain amplifier with capacitive bootstrapping (Amplifier1) (b) Feedback path (C and T3)

as shown in Fig. 4b. On the other hand, T1 and T2 are in saturation. For high frequency signals, capacitor (C) acts as a short-circuit so the feedback factor (A<sub>f</sub>) is supposed to be unity. However, Af depends on the aspect ratio of the transistor T3 (Coff is a function of the transistor aspect ratio due to the considerable overlap areas between the gate and source/drain) and C. From Fig. 4,

$$v_{1} = A_{f}v_{0}$$

$$= v_{0}\frac{1}{1 + \frac{1}{sC}(\frac{1}{R_{off}} + sC_{off})}$$

(5)

since Roff is very high, it can be simplified as

$$A_f = \frac{v_1}{v_0} = \frac{1}{1 + \frac{C_{off}}{C}} \tag{6}$$

From (6), making  $C >> C_{off}$ ,  $A_f$  can be made close to one to promise high gain. Consequently, transistor T3 should be made small. The fabricated circuit micrograph with wire-bonding is shown in Fig. 5. Because of the positive feedback path (Fig. 4b), a high-pass filter action can be noticed, though the lower cutoff frequency is very small. In this circuit, T1 and T2 widths are  $160 \,\mu\text{m}$  and T3 width is  $40 \,\mu\text{m}$ . A channel length of 20  $\mu$ m is used for all the TFTs, which is a reasonable value comparing to the total gate to source and drain overlap of  $10 \, \mu \text{m}$ .

Fig. 5. Capacitive bootstrap amplifier micrograph with wire-bonding

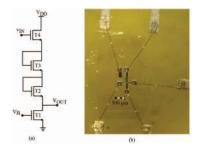

# Level Shifter:

The circuit is realized with four transistors. Its schematic and respective micrograph are shown in Fig. 6. Diode connected transistors (T2 and T3) are used to lower the DC level of the input signal, which is controlled by the bias voltage  $(V_B)$  applied at the gate of T1. With all transistors having the same dimensions (width =  $80\,\mu m$  and length =  $20\,\mu m$ ) and biased in saturation region, then:

$$v_{OUT} \approx K.v_{IN} - 3V_B \tag{7}$$

Since this circuit is fabricated on glass, which is a good insulator, body-effect is negligible unlike conventional CMOS devices, hence " $K \approx 1$ " can be achieved.

Fig. 6. Level shifter (a) schematic (b) Fabricated circuit with wire-bonding with Mo as source/drain metal

### **Fabrication**

Fabrication process of circuits and transistors in this work follow the same method as [12] with fabrication temperature < 200 °C, where the a-IGZO layer is deposited with RF magnetron sputtering. Though transparent devices can be achieved with TCO (e.g. IZO) source/drain electrodes, Mo is employed in this work, as it facilitates wire-bonding for easier circuit testing.

### III. RESULTS AND DISCUSSION

All circuits were simulated with an in-house model developed from the device measurements [12]. Meyer model was adopted for the bias dependent capacitance. Circuit simulations were carried out in the Cadence Virtuoso Analog Design Environment. In-house technology libraries were used to support the custom IC design flow. Circuits measurements took place at room temperature. Logic gates and Amplifier1 were characterized with the help of a buffer, which is formed by an external IC showing an equivalent load capacitance of 4 pF. On the other hand, the level shifter circuit is directly tested with an oscilloscope in order to determine the circuits driving ability.

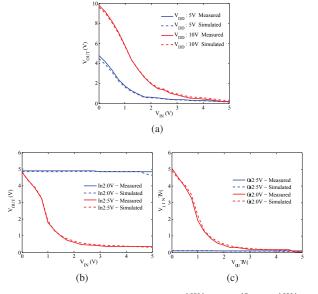

# Logic gates

Inverter voltage transfer characteristics (VTC) is shown in Fig. 7a, when the input ('In1') is swept between 0 to 5 V in steps of 0.25 V for two different power supply voltages ( $V_{DD}$ ) of 5 and 10 V. It can be noticed that almost full swing (high level  $\approx V_{DD}$  and low level  $\approx 0.15 \, \mathrm{V}$ ) results at the output. NAND and NOR gates VTCs are also presented in Fig. 7b and 7c with a  $V_{DD}$  of 5 V, when 'In2' is low and high, by sweeping 'In1', similar to the inverter.

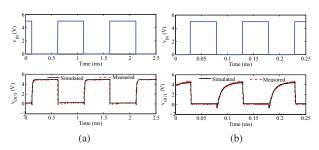

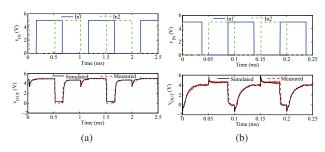

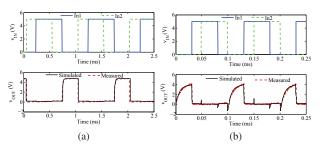

Logic gates (inverter, NAND and NOR) dynamical behavior at  $V_{DD} = 5 \, \mathrm{V}$  is also characterized. Their responses for an

Fig. 7. Logic gates VTC: (a) Inverter:  $\left(\frac{W}{L}\right)_{T2} = \frac{40~\mu m}{20~\mu m}$ ,  $\left(\frac{W}{L}\right)_{T1} = \frac{480~\mu m}{20~\mu m}$  and V<sub>DD</sub> 5 V and 10 V (b) NAND (c) NOR, where  $\left(\frac{W}{L}\right)_{T3} = \frac{40~\mu m}{20~\mu m}$ ,  $\left(\frac{W}{L}\right)_{T2} = \left(\frac{W}{L}\right)_{T1} = \frac{480~\mu m}{20~\mu m}$  and V<sub>DD</sub> 5 V, for both the logic gates.

Fig. 8. Inverter response, when the input signal frequency is (a)  $1\,\mathrm{kHz}$  (b)  $10\,\mathrm{kHz}.$

input signal with different frequencies of 1 kHz and 10 kHz are presented in Fig. 8, 9 and 10. At transitions of the input signals, small spikes in the output waveforms can be noticed, mainly at high frequency (10 kHz) due to the charge injection from the transistor capacitance that couple the input to the output. Both load and transistor capacitance are responsible for the charging and discharge effect in the output signals. It can also be observed that the output signal rise time is much

Fig. 9. NAND response, when the input signal frequency is (a)  $1\,\mathrm{kHz}$  (c)  $10\,\mathrm{kHz}.$

Fig. 10. NOR response, when the input signal frequency is (a)  $1\,\mathrm{kHz}$  (c)  $10\,\mathrm{kHz}$ .

higher than the fall time. This is because the load capacitor charges through a small load transistor and discharges through a wider driver transistor(s).

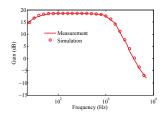

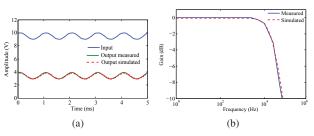

**Amplifier1:** Frequency response of Amplifier1 is shown in Fig. 11 for a load of 4 pF with a  $V_{DD}$  of 6 V. With an on-chip capacitance (C) of 47 pF, the circuit measurements result in a bandwidth of  $20\,\mathrm{kHz}$ , a gain of  $18.6\,\mathrm{dB}$  and a power consumption of  $345\,\mu\mathrm{W}$ .

Fig. 11. Amplifier1 response from simulation and measurements

**Level shifter:** Circuit response is shown in Fig. 12a, for an input defined as 9.5 + 0.5sin( $\omega$ t) and  $V_B=2\,V$  from simulations (transient analysis) and measurements. Fig. 12b shows the frequency response of the circuit, when it drives a load of (10 M $\Omega$ //16 pF). Resulted gain is  $\approx$  1, as expected and also the functional verification from (7) can be noticed in Fig. 12a. 3 dB bandwidth is  $\approx$  80 kHz and power consumption is 24  $\mu$ W. Performance metrics of the reported circuits (Amplifier1 and Level shifter) are compared with literature in Table. I.

Fig. 12. Level shifter response from simulations and measurements (a) Transient response (b) Frequency response

# IV. CONCLUSIONS

This paper presented the characterization of basic analog and digital circuits both from simulations and measurements. Circuit simulations are in very good agreement with the

### TABLE I PERFORMANCE COMPARISON

| Circuit            | No. of<br>TFTs | Power<br>(mW) | Bandwidth (KHz) | Gain<br>(dB) | Load                                |

|--------------------|----------------|---------------|-----------------|--------------|-------------------------------------|

| Source<br>follower | 4              | 0.024         | 80              | 0            | 10 MΩ//16 pF                        |

| Amplifier1         | 3              | 0.345         | 20              | 18.6         | 4 pF                                |

| [10]               | 16             | 0.9           | 54              | 18.7         | $1\mathrm{M}\Omega/\!/2\mathrm{pF}$ |

measured response. As these circuits were fabricated at low temperature they would find potential applications in largearea wearable electronics.

### ACKNOWLEDGMENT

This work is funded by the ERDF (European Regional Development Fund) through the Programme COMPETE (operational programme for competitiveness) and by the Portuguese Government through FCT – Foundation for Science and Technology, project ref. (FCOMP-01-0124-FEDER-013070); and also by the European Research Council through the Advanced Grant INVISIBLE (ERC-2008-AdG 228144). The work is partially funded by IIIT Delhi.

### REFERENCES

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, 2004.

- [2] E. Fortunato, D. Ginley, H. Hosono, and D. C. Paine, "Transparent conducting oxides for photovoltaics," MRS Bulletin, vol. 32, pp. 242– 247, Mar 2007.

- [3] J. H. Lee, D. H. Kim, D. J. Yang, S. Y. Hong, K. S. Yoon, P. S. Hong, C. O. Jeong, H. S. Park, S. Y. Kim, S. K. Lim, S. S. Kim, K. S. Son, T. S. Kim, J. Y. Kwon, and S. Y. Lee, "42.2: World's Largest (15-inch) XGA AMLCD Panel Using IGZO Oxide TFT," SID Symposium Digest of Technical Papers, vol. 39, no. 1, pp. 625–628, 2008.

- [4] B. D. Yang, J. M. Oh, H. J. Kang, S. H. Park, C. S. Hwang, M. K. Ryu, and J. E. Pi, "A Transparent Logic Circuit for RFID Tag in a-IGZO TFT Technology," *ETRI Journal*, vol. 35, no. 4, pp. 610–616, 2013.

- [5] J. F. Conley, "Instabilities in amorphous oxide semiconductor thinfilm transistors," *IEEE Transactions on Device and materials reliability*, vol. 10, no. 4, pp. 460–475, 2010.

- [6] U. Ozgur, Y. I. Alivov, C. Liu, A. Teke, M. Reshchikov, S. Dogan, V. Avrutin, S. J. Cho, and H. Morkoc, "A comprehensive review of ZnO materials and devices," *Journal of Applied Physics*, vol. 98, no. 4, pp. 041301–041301–103, 2005.

- [7] E. Fortunato, P. Barquinha, and R. Martins, "Oxide semiconductor thinfilm transistors: A review of recent advances," *Advanced Materials*, vol. 24, no. 22, 2012.

- [8] E. Fortunato, V. Figueiredo, P. Barquinha, E. Elamurugu, R. Barros, G. Gonalves, S.-H. K. Park, C.-S. Hwang, and R. Martins, "Thin-film transistors based on p-type Cu2O thin films produced at room temperature," *Applied Physics Letters*, vol. 96, no. 19, pp. –, 2010.

- [9] H. Luo, P. Wellenius, L. Lunardi, and J. Muth, "Transparent igzo-based logic gates," EDL, vol. 33, no. 5, pp. 673–675, May 2012.

- [10] C. Zysset, N. Munzenrieder, L. Petti, L. Buthe, G. Salvatore, and G. Troster, "IGZO TFT-Based All-Enhancement Operational Amplifier Bent to a Radius of 5 mm," *Electron Device Letters, IEEE*, vol. 34, no. 11, pp. 1394–1396, 2013.

- [11] A. G. W. Venes, B. Nauta, and R. J. van de Plassche, "Low power folding A/D converters," in Analog Circuit Design, pp. 105–124, 1996.

- [12] P. Bahubalindruni, V. Grade Tavares, P. Barquinha, C. Duarte, P. Guedes de Oliveira, R. Martins, and E. Fortunato, "Transparent Current Mirrors With a-GIZO TFTs: Neural Modeling, Simulation and Fabrication," *JDT*, vol. 9, no. 12, pp. 1001–1006, 2013.