University of Wollongong Research Online

University of Wollongong Thesis Collection

University of Wollongong Thesis Collections

1999

# Behaviour of variable speed drives under the influence of voltage sags

Rajagopalan Lakshmi Narayanan University of Wollongong

**Recommended** Citation

Narayanan, Rajagopalan Lakshmi, Behaviour of variable speed drives under the influence of voltage sags, Master of Engineering (Hons.) thesis, School of Electrical, Computer and Telecommunications Engineering, University of Wollongong, 1999. http://ro.uow.edu.au/theses/2544

Research Online is the open access institutional repository for the University of Wollongong. For further information contact Manager Repository Services: morgan@uow.edu.au.

#### NOTE

This online version of the thesis may have different page formatting and pagination from the paper copy held in the University of Wollongong Library.

## UNIVERSITY OF WOLLONGONG

## **COPYRIGHT WARNING**

You may print or download ONE copy of this document for the purpose of your own research or study. The University does not authorise you to copy, communicate or otherwise make available electronically to any other person any copyright material contained on this site. You are reminded of the following:

Copyright owners are entitled to take legal action against persons who infringe their copyright. A reproduction of material that is protected by copyright may be a copyright infringement. A court may impose penalties and award damages in relation to offences and infringements relating to copyright material. Higher penalties may apply, and higher damages may be awarded, for offences and infringements involving the conversion of material into digital or electronic form.

# **BEHAVIOUR OF VARIABLE SPEED DRIVES UNDER THE INFLUENCE OF VOLTAGE SAGS**

A thesis submitted in fulfilment of the requirements for the award of the degree

#### MASTER OF ENGINEERING (HONOURS)

from

#### UNIVERSITY OF WOLLONGONG

by

#### RAJAGOPALAN LAKSHMI NARAYANAN (MEngStud)

# SCHOOL OF ELECTRICAL, COMPUTER AND TELECOMMUNICATIONS

ENGINEERING, 1999

## CONTENTS

| ACK  | NOWLEDGEMENTS                                                  | vii  |

|------|----------------------------------------------------------------|------|

| ABS  | RACT                                                           | viii |

| LIST | OF SYMBOLS                                                     | ix   |

| СНА  | PTER 1 INTRODUCTION                                            |      |

| 1.1  | Variable Speed Drives in Process Plants                        | 1    |

| 1.2  | Voltage Sags and their Causes                                  | 2    |

| 1.3  | Types of Voltage Sags                                          | 3    |

| 1.4  | Impact of Voltage Sags on VSDs                                 | 3    |

|      | 1.4.1 Impact of a Balanced Sag                                 | 4    |

|      | 1.4.2 Impact of an Unbalanced Sag                              | 5    |

| 1.5  | Conventional Mitigation Strategies                             | 5    |

|      | 1.5.1 Mitigation Techniques by Hardware Modifications          | 6    |

|      | 1.5.2 Mitigation Techniques by Means of Improved               |      |

|      | Power Supply Conditions                                        | 8    |

|      | 1.5.3 Mitigation Techniques by Control Algorithm Modifications | 10   |

| 1.6  | Aim of the Thesis                                              | 11   |

| 1.7  | Contributions of this Thesis                                   | 12   |

| 1.8  | Scope of Work and Plan of the Thesis                           | 13   |

| СНА  | PTER 2 PROPOSED CONTROL STRATEGY AND                           |      |

|      | MODELLING OF VSDs                                              |      |

| 2.1  | Introduction                                                   | 15   |

| 2.2  | Proposed Control Strategy                                      | 16   |

|      | 2.2.1 Set Points for Control Strategy                          | 17   |

|      | 2.2.2 Control Sequence and Flow Charting                       | 18   |

| 2.3  | Control Loops in AC VSDs Operating Under Field Orientation     | 20   |

|      | 2.3.1 Control Model of an IM VSD                               | 21   |

|      | 2.3.2 Control Model of an SRM VSD                              | 25   |

| 2.4 | Proposed Additional Control Loops for DC Bus Voltage Control | 26 |

|-----|--------------------------------------------------------------|----|

|     | 2.4.1 Bus Voltage Control by Recovering Load Kinetic Energy  | 27 |

|     | 2.4.2 Bus Voltage Control by Recovering Magnetising Energy   | 29 |

| 2.5 | Power Balance Between AC Supply, Bus Capacitor and AC Motor  | 31 |

|     | 2.5.1 Power Flow Between AC Supply and DC Bus Capacitor      | 31 |

|     | 2.5.2 Power Flow Between DC Bus Capacitor and AC Motor       | 32 |

| 2.6 | Summary                                                      | 34 |

|     |                                                              |    |

## CHAPTER 3 PERFORMANCE OF A SYNCHRONOUS RELUCTANCE MOTOR DRIVE

| 3.1 | Introduction                                                 | 35 |

|-----|--------------------------------------------------------------|----|

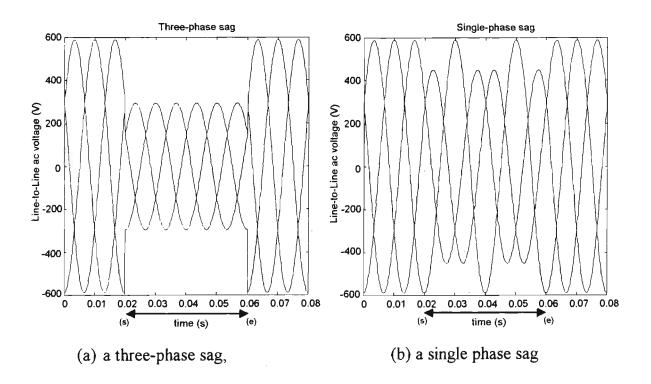

| 3.2 | Sag Types Under Study                                        | 36 |

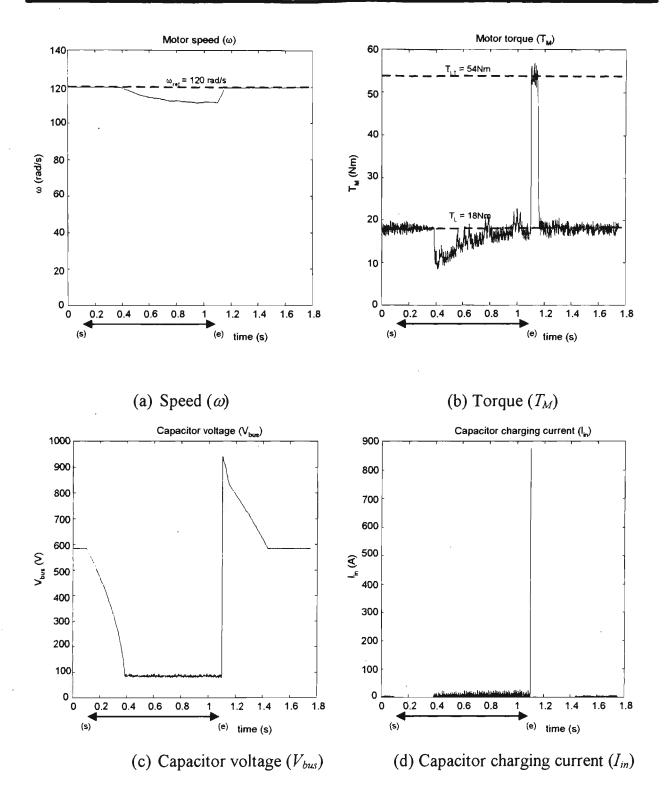

| 3.3 | Normal Speed Control Operation of an SRM VSD                 | 38 |

|     | 3.3.1 Performance Under Normal Operating Conditions - No Sag | 38 |

|     | 3.3.2 VSD Behaviour during a Voltage Sag                     | 43 |

|     | 3.3.3 Reasons For VSD Tripping on a Sag Condition            | 47 |

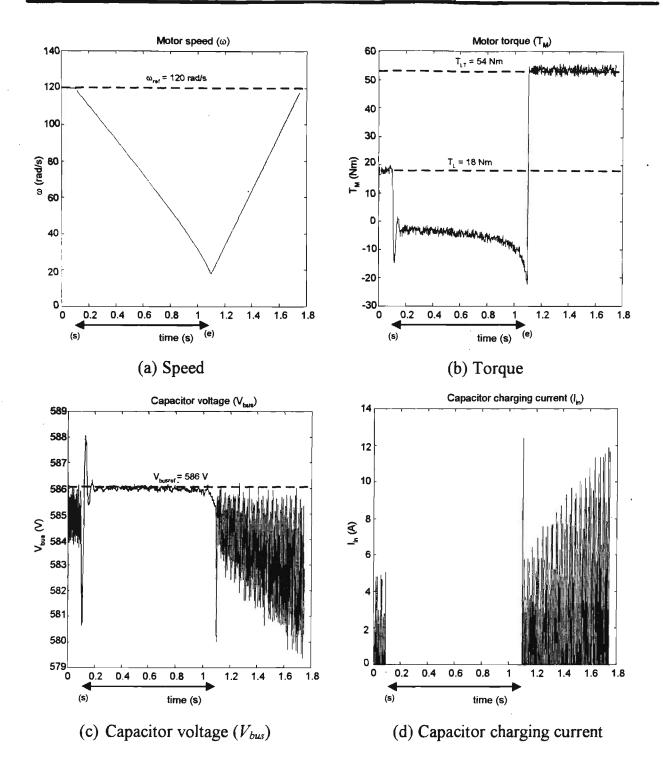

| 3.4 | Operation Under a Sag at High Speeds – Bus Voltage Control   |    |

|     | by Recovering Kinetic Energy                                 | 49 |

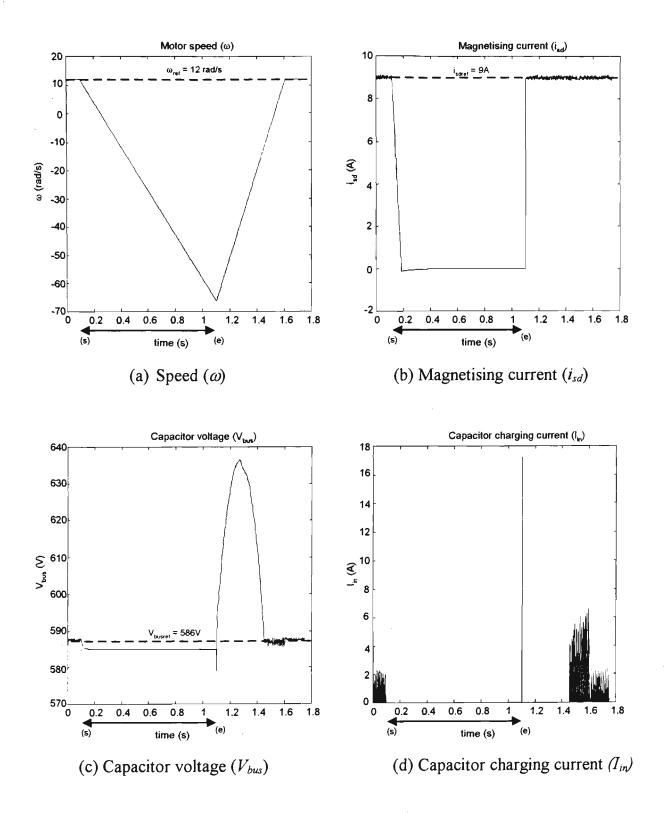

| 3.5 | Operation Under a Sag at Low Speeds – Bus Voltage Control    |    |

|     | by Recovering Magnetising Energy                             | 53 |

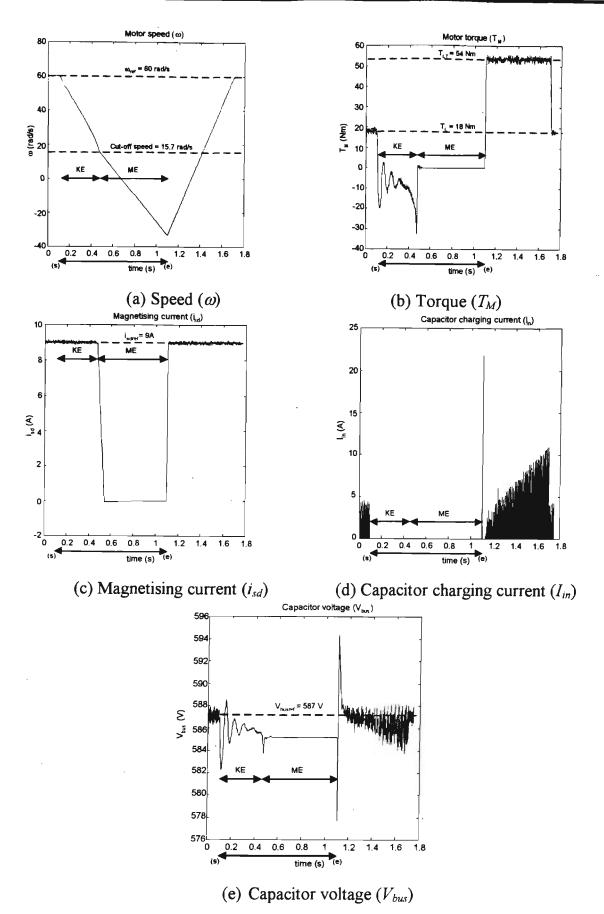

| 3.6 | Coordinated VSD Control at all Speeds                        | 55 |

| 3.7 | Effect of Lowering the Bus Capacitance                       | 57 |

| 3.8 | Summary                                                      | 60 |

|     |                                                              |    |

|     |                                                              |    |

## CHAPTER 4 PERFORMANCE OF AN INDUCTION MOTOR DRIVE

| 4.1 | Introduction                                                 | 61 |

|-----|--------------------------------------------------------------|----|

| 4.2 | Normal Speed Control Operation of an IM VSD                  | 62 |

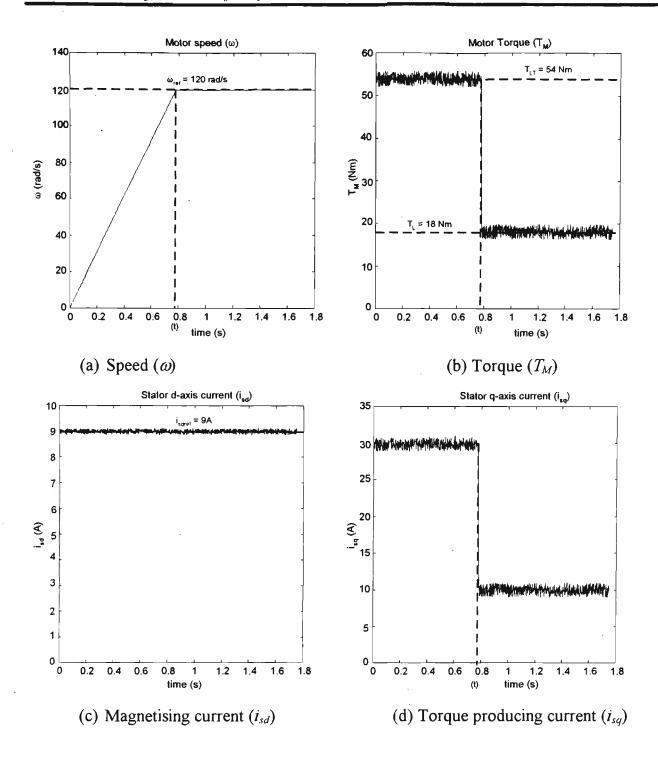

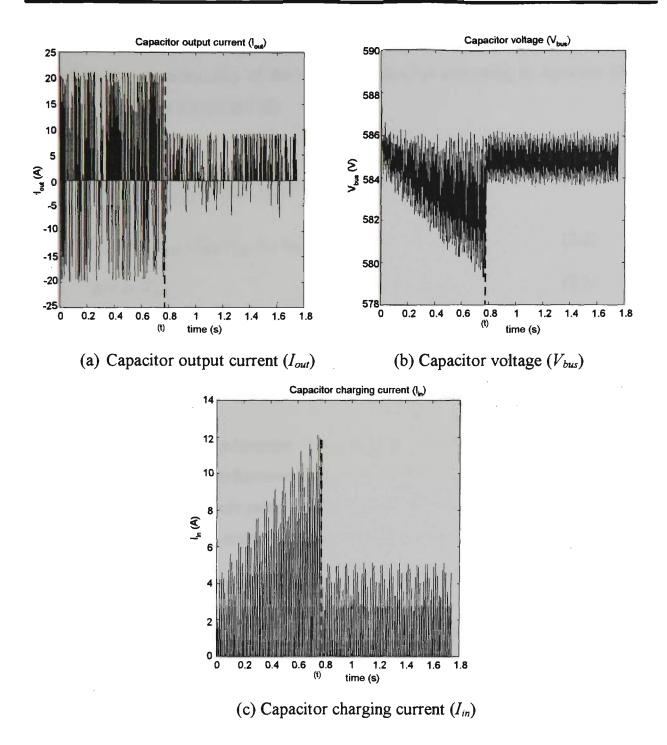

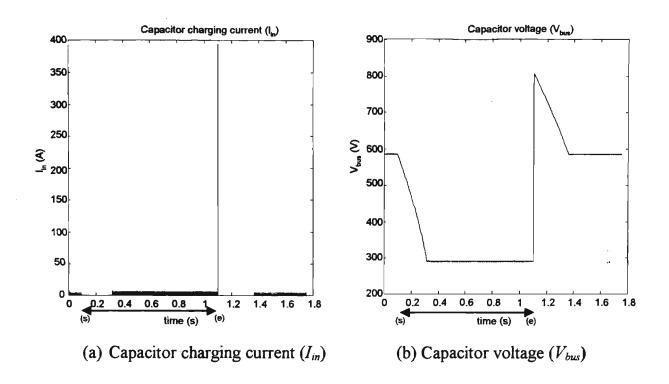

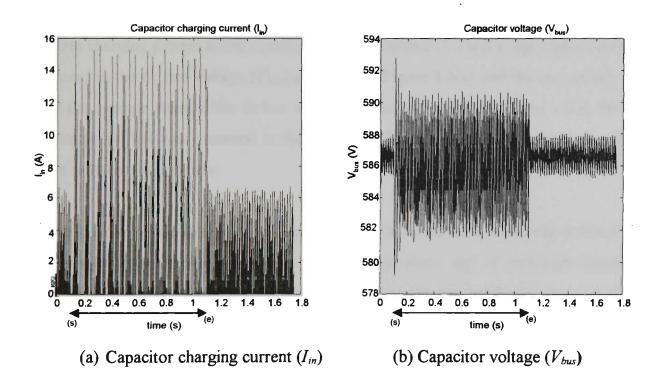

|     | 4.2.1 Performance Under Normal Operating Conditions - No Sag | 62 |

|     | 4.2.2 VSD Behaviour during a Sag                             | 69 |

|     | 4.2.3 Reasons for VSD Tripping on a Sag Condition            | 71 |

|     |                                                              |    |

| 4.3  | Operatio | n Under a Sag at High Speeds – Bus Voltage Control |   |

|------|----------|----------------------------------------------------|---|

|      | by Recov | vering Kinetic Energy                              |   |

| 4.4  | Operatio | n Under a Sag at High Speeds – Bus Voltage Control |   |

| ,    | by Recov | vering Magnetising Energy                          | - |

| 4.5  | Energy I | loss in Induction Motors during Flux Variations    | - |

| 4.6  | Optimun  | n Sag Ride-Through Control at Low Speeds           | 8 |

| 4.7  | Coordina | ated Sag Ride-Through Control at all Speeds        | 8 |

| 4.8  | Summary  | y .                                                | 8 |

| СН   | APTER 5  | CONCLUSIONS                                        |   |

| 5.1  | Conclusi | ons                                                | 8 |

| REF  | ERENCES  | 5                                                  | 8 |

| APPI | ENDIX A  | ENERGY LEVELS IN AN AC VSD                         | ç |

| APP  | ENDIX B  | MATHEMATICAL MODELLING OF AN                       |   |

|      |          | INDUCTION MOTOR                                    | Ģ |

| APP  | ENDIX C  | MATHEMATICAL MODELLING OF A                        |   |

|      |          | SYNCHRONOUS RELUCTANCE MOTOR                       |   |

| APP  | ENDIX D  | SWITCHING VECTOR SELECTION                         |   |

|      |          | IN FIELD ORIENTATION CONTROL                       | ] |

| APP  | ENDIX E  | PARAMETERS OF IM VSD                               |   |

| APP  | ENDIX F  | PARAMETERS OF SRM VSD                              | ] |

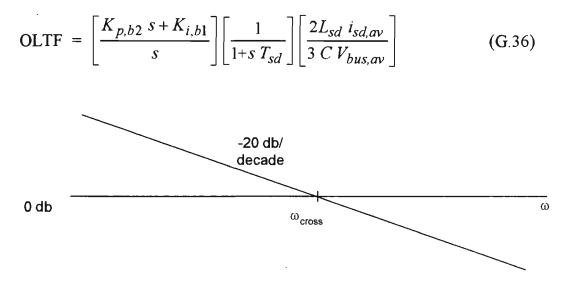

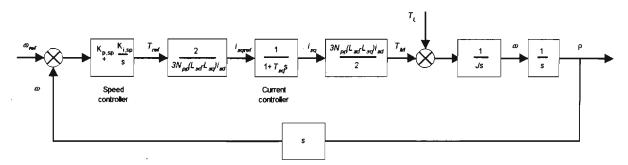

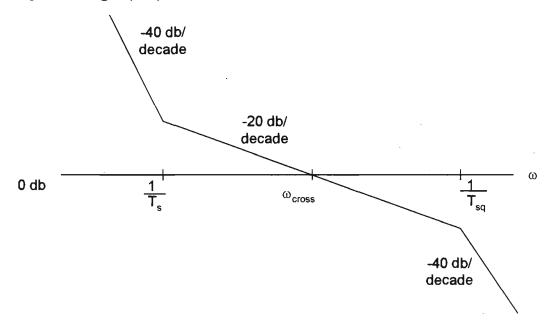

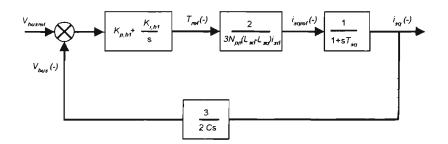

| APP  | ENDIX G  | TUNING OF CONTROLLERS FOR IM VSD                   |   |

| APP  | ENDIX H  | TUNING OF CONTROLLERS FOR SRM VSD                  | ] |

| APP  | ENDIX I  | PERFORMANCE OF SRM VSD WITH                        |   |

|      |          | FAN TYPE LOADS                                     | ] |

|      | ENDIX J  | PERFORMANCE OF IM VSD WITH                         |   |

| APPI |          |                                                    |   |

| APPI |          | FAN TYPE LOADS                                     | 1 |

iv

#### **DECLARATION**

This is to certify that the work reported in this thesis has been performed by the author unless specified otherwise. No part of it has been submitted as a thesis to any other University.

R. L. Narayanan

## dedicated to

My parents, Jai, Ashwin and all my beloved ones

#### ACKNOWLEDGEMENTS

I would like to thank my supervisors Dr. Don Platt and Dr. B. S. P. Perera for their supervision and invaluable guidance throughout this research. Without their additional effort, encouragement and support, it would not have been possible for me to learn many new things and do a research project in the area I always dreamt about.

I would like to extend my gratitude to all faculty, staff and technicians in the School of Electrical, Computer and Telecommunications Engineering for all the help I got when I was in need during this research work.

I also thank my friends, Dr. Ali Yazdian and Dr. Ali Dastfan, for their valuable technical assistance during the thesis.

I would like to thank my parents, grandparents, parents-in-law, brothers, sister and their families and all relatives and friends for their help, understanding, good wishes and moral support during my higher studies in Australia. I would like to express my affection and gratitude to my aunt, Mrs. Kameswari Viswanathan, who supported me during my previous education in India. Also, I would like to thank my grandfather, Mr. N. Srinivasan, who helped me choose my career path and motivated me to continue my further studies. I thank my wife, Jai, and my son, Ashwin, for their love and cooperation without which I would not have been able to complete this research.

I would like to sincerely thank the Integral Energy Power Quality Centre for the financial support I received during this research and would like to thank all its members for the confidence they entrusted on me.

Finally, I thank God for all the guidance and blessings.

#### ABSTRACT

In ac variable speed drives (VSDs) having an uncontrolled rectifier front-end, the effect of voltage sags are mainly observed in the dc bus characteristics. These VSDs are susceptible to nuisance tripping due to dc under-voltage or ac over-current faults which result in production loss, material wastage and require manual interventions in industrial processes. This thesis is aimed at improving the voltage sag ride-through performance of ac VSDs by improving the control algorithm. The proposed strategy recommends maintaining the dc link voltage constant at the nominal value utilising two control modes (a) by recovering the kinetic energy available in the rotating mass at high motor speeds and (b) by recovering the magnetising energy available in the motor winding inductances at low speeds. By combining these two modes, the VSD can be configured to ride-through voltage sags at all speeds. Additional control loops are suggested for this dc link voltage control.

The proposed control strategy was applied on a synchronous reluctance motor (SRM) VSD and on an induction motor (IM) VSD. In the case of an SRM VSD, both modes of this control strategy are found to work satisfactorily and sag ride-through can be achieved at all motor speeds.

In an IM VSD, the first mode of the control strategy, viz. closed loop dc voltage control by recovering the kinetic energy available in the system inertia is found to work satisfactorily and sag ride-through can be achieved at high motor speeds. However, due to the inherent IM characteristics, it was found that the magnetising energy present in an IM is not recoverable. The reasons for this behaviour are analysed and an alternative ridethrough scheme is suggested by accommodating the limitations encountered in the case of an IM so that the VSD is able to ride-through voltage sags at low speeds also.

This control strategy can provide a voltage sag ride-through performance at all motor speeds down to standstill. It is also shown that the transition between various control modes during a sag situation can be achieved relatively smoothly.

viii

#### LIST OF SYMBOLS

| $\alpha$ | 1  | 1   |           |

|----------|----|-----|-----------|

| С        | dc | bus | capacitor |

|          |    |     |           |

- *dt* sampling time

- $\delta$  load angle

- $\varepsilon$  rotor angle

- *f* supply frequency

- $I_l$  incoming phase current

- *I<sub>in</sub>* capacitor charging current

- *I*<sub>out</sub> dc current flowing between capacitor and the inverter

- $i_{mR}$  rotor magnetising current

- $\vec{i}_{mR}$  rotor magnetising current vector

- $\vec{i}_r$  rotor current space phasor

- *i<sub>rd</sub>* rotor current in d-axis

- $i_{rq}$  rotor current in q-axis

- $\vec{i}_s$  stator current space phasor

- *i*<sub>sd</sub> stator current in d-axis

- $i_{sq}$  stator current in q-axis

J system inertia

- $K_{p,bl}$  Bus Voltage Regulator 1 P gain

- $K_{i,bl}$  Bus Voltage Regulator 1 I gain

- $K_{p,b2}$  Bus Voltage Regulator 2 P gain

- $K_{i,b2}$  Bus Voltage Regulator 2 I gain

- $K_{p,sp}$  Speed controller P Gain

- $K_{i,sp}$  Speed controller I Gain

- *L* per phase line inductance

- $L_m$  mutual inductance

- $L_r$  rotor inductance

- $L_s$  stator inductance

| L <sub>sd</sub>   | stator inductance in d-axis                                  |

|-------------------|--------------------------------------------------------------|

| L <sub>sq</sub>   | stator inductance in q-axis                                  |

| L <sub>t</sub>    | total inductance of the ac machine                           |

| $\vec{\lambda}_s$ | stator leakage flux space phasor                             |

| $\lambda_{sd}$ ,  | stator flux linkage in d-axis                                |

| $\lambda_{sq}$    | stator flux linkage in q-axis                                |

| М                 | mutual inductance, and                                       |

| N <sub>P</sub>    | number of poles                                              |

| $N_{PP}$          | number of pole pairs                                         |

| р                 | power input to the motor                                     |

| ρ                 | magnetising (flux) axis position with respect to stator axis |

| R                 | per phase line resistance                                    |

| R <sub>r</sub>    | rotor resistance                                             |

| R <sub>s</sub>    | stator resistance                                            |

| $\sigma$          | total leakage factor                                         |

| $\sigma_{S}$      | stator Leakage factor                                        |

| $\sigma_r$        | rotor Leakage factor                                         |

| $T_L$             | load torque                                                  |

| $T_{M}$           | motor torque                                                 |

| $T_R$             | rotor time constant                                          |

| Tref              | torque reference                                             |

| $V_{bus}$         | bus capacitor voltage                                        |

| $V_{II}$          | line-to-line ac voltage                                      |

| $\vec{V_r}$       | rotor voltage vector                                         |

| V <sub>rd</sub>   | rotor voltage in d-axis                                      |

| $V_{rq}$          | rotor voltage in q-axis                                      |

| $\vec{V}_{s}$     | stator voltage vector                                        |

| $V_{sd}$          | stator voltage in d-axis                                     |

| $V_{sq}$          | stator voltage in q-axis                                     |

·

| ω | motor | angular | velocity |

|---|-------|---------|----------|

|---|-------|---------|----------|

$\omega_{cutoff}$  cut-off speed for control transition  $\omega_{mR}$  angular velocity of the magnetising vector  $\omega_{ref}$  velocity reference

$X_t$  total reactance of the ac machine

## **CHAPTER 1**

## **INTRODUCTION**

#### 1.1 VARIABLE SPEED DRIVES IN PROCESS PLANTS

Solid State Variable Speed Drives (VSDs) have already become an integral part of many process plants and their usage is on the rise in industrial, commercial and residential applications [1]. Recent developments in the areas of design of converters, motors and control systems have contributed to a significant increase in the usage of VSDs [2,3]. It is projected that, about 50-60% of the electrical energy generated will be processed by solid state power electronic devices by the year 2010 compared to the present day levels of 10-20% [4].

As the use of power electronics keeps growing, so does the awareness of power quality issues and their impact on the performance of supply sensitive equipment. Power quality disturbances can be of several types such as interruptions, sags and swells, transients, harmonic distortion, voltage fluctuations and noise [5]. They can lead to undesired consequences such as loss of efficiency, loss of plant life, loss of product quality, maloperation and trip-out of sensitive equipment [6]. Of all power quality disturbances, voltage sag seems to be the most common type. A power quality survey conducted by Bell Telephone Laboratories reports that 87.2% of the instances recorded were voltage sags [4]. Voltage sags are reported to be the most frequent cause of disrupted operations of many industrial processes, particularly those using modern electronic equipment which are sensitive to short supply variations [7].

VSDs are one of the most common power electronics based industrial equipment and they are also vulnerable to voltage sags [7-8]. In the presence of voltage sags, VSDs can malfunction or even fail [9,10]. Many industrial processes are controlled by VSDs either individually or in groups depending on the process requirement. A single VSD trip could bring the entire plant to a standstill. An interruption to the process usually

requires manual interventions and would result in enormous wastage of material and restarting delays which lead to severe losses. In order to increase productivity and avoid losses, reliability of VSD operation is of utmost importance in process plants.

This thesis is intended to study the VSD behaviour during voltage sags and enhance the sag ride-through performance.

In this chapter, the definition of voltage sags and their causes will be discussed. The various classifications of sags experienced by VSDs will be presented and will be referred to throughout this thesis. Then the effect of voltage sags on the performance of the VSDs will be discussed. Finally, the conventional mitigation strategies that are available in the literature will be mentioned and their advantages and disadvantages will be analysed.

#### **1.2 VOLTAGE SAGS AND THEIR CAUSES**

Voltage sag is a momentary reduction in the supply voltage and not complete loss of power [11]. Sags are usually characterised by their magnitude and duration. A voltage sag is defined as a decrease in the rms voltage magnitude at the supply frequency with typical values between 0.1- 0.9 p.u. and durations ranging from 0.5 cycles to 1 minute [5,10].

Voltage sags are usually caused by faults in the transmission and/or distribution system such as lightning strikes, tree or animal contacts [10-11]. High currents flowing due to short circuits either within the plants or on utility lines in the electrical neighbourhood result in voltage sags [12]. The sag persists as long as the short circuit current flows and it disappears when a fault clearing device interrupts the fault current. Starting of large motors and welding also can cause voltage sags. Methods for predicting magnitude, duration and frequency of voltage sags in an electrical network are suggested in [12]. The sag magnitude depends on the fault impedance, network impedance and fault location with respect to a sensitive load. Sag duration depends on

2

the clearing time of the fault clearing equipment and any intentional delays introduced to provide coordination between devices in series. In order to predict the frequency of occurrence of voltage sags, the reliability data for all voltage sag sensitive equipment in the electrical neighbourhood is required.

#### **1.3 TYPES OF VOLTAGE SAGS**

Voltage sags experienced by three-phase VSDs are classified into four types depending on the type of fault (viz. single-phase, phase-to-phase, or three-phase), the type of transformer connection and the type of load connection (Yor  $\Delta$ ) as follows [13-14]:

- a) **Type A:** All three phases drop voltage by the same amount in magnitude.

- b) **Type B:** Only one phase voltage magnitude drops.

- c) **Type C:** Two phases drop in voltage magnitude with change in their phase angles

- d) **Type D:** Two phases drop in voltage magnitude with change in phase angles and the third phase drop in magnitude only.

As seen from the above definitions, voltage sags may be accompanied by phase angle jumps. Transformer connections ( $\Delta$ -Y,Y-Y, etc.) also have an effect on the line voltage seen by the load during an unbalanced sag [7]. Moreover, one type of sag can transform into another type depending upon the transformer connections [11, 13].

#### 1.4 IMPACT OF VOLTAGE SAGS ON AC VSDs

Though, dc motor drives still have a presence in the drives market, their share is being overtaken by the ac VSDs because of the recent technological advances and the comparative advantages of ac motors over their dc counterparts [2-3,15]. Hence in this thesis only ac motor VSDs are examined.

About 80% of the modern AC drives are Voltage Source Inverter type, having a diode bridge front-end, a dc link capacitor (with an optional inductor) and a PWM inverter [7, 15-16]. In this VSD configuration, because the rectifier is an uncontrolled one, any variation in the ac supply would be reflected in the dc bus characteristics. With a balanced and rated ac supply, the diodes in the three-phase rectifier are forward biased when the line voltage exceeds the bus capacitor voltage and thus the rectifier output current is a repetitive pattern of six symmetrical pulses per cycle. Similarly the dc bus voltage is a symmetrical pattern of six peaks per cycle as the capacitor charges to the peak input voltage and discharges in between the peaks while supplying energy to the motor [7]. Hence, in such ideal ac supply conditions, the dc capacitor voltage is at the nominal value with minimal ripple content. The dc capacitor delivers the power required by the motor to operate at the set speed and torque levels.

However, when subjected to voltage sags, the VSD performance, especially the dc bus characteristics, is affected. The impact of balanced as well as unbalanced sags on the VSD behaviour is discussed in the following subsections.

#### 1.4.1 IMPACT OF A BALANCED SAG

When a balanced sag (Type A as mentioned in Section 1.3) appears on the VSD power supply, the capacitor voltage will still be a symmetrical pattern of six peaks per cycle but its average value will be lower than the nominal value depending on the sag magnitude [7]. When the dc bus voltage reduces, the energy available in the dc link also reduces and below a particular voltage, the VSD cannot deliver the rated torque at a certain speed. But the main problem with this dc voltage drop is the risk of damaging the rectifier components due to high capacitor charging currents when ac supply returns to normal level. The rectifier over-current transients can be much worse on voltage recovery than during a sag [17]. Hence the dc bus voltage fault when the bus voltage reaches a lower limit.

#### 1.4.2 IMPACT OF AN UNBALANCED SAG

In the case of unbalanced sags (Types B, to D as defined in Section 1.3), the conduction of diodes is not a symmetrical pattern any more. The capacitor charges to the peak of the line-to-line voltage and usually one or more of these peak voltages are less than the nominal capacitor voltage. This causes the capacitor to discharge for a longer duration until the next peak voltage is sufficient to forward bias the diodes. Often, the three-phase rectifier acts as a single phase rectifier with phase current as high as 4 or more times the rated value which causes the drive to trip due to over-current protection fault [7].

The phase angle jump also results in a similar situation as an unbalanced sag since it tends to reduce one or more line-to-line voltages thereby tripping the drive on either under-voltage or over-current faults [7].

Most older VSDs have their control electronics power supply derived from the AC input and hence they are very sensitive to supply variations which caused nuisance tripping [7].

Though voltage sags do not damage the equipment, they usually result in nuisance tripping of VSDs. It is reported that, a sag of magnitude more than 20% and duration more than 12 cycles is found to trip VSDs [4].

#### **1.5 CONVENTIONAL MITIGATION STRATEGIES**

The mitigation techniques aimed at improving the sag ride-through performance of the VSDs that are available in the literature can be broadly classified into three categories, viz. (1) hardware modifications, (2) provision of alternate power supplies and (3) control algorithm modifications. The various suggestions available in each group will be discussed in the rest of this section.

#### **1.5.1 MITIGATION TECHNIQUES BY HARDWARE MODIFICATIONS**

The following strategies suggest either changes in the hardware ratings or addition of extra hardware in a VSD in order to improve the voltage sag ride-through performance:

- a) increase the ac side reactance [7]

- b) increase the dc bus capacitance [7,18]

- c) decrease the dc bus capacitance [19]

- d) provision of large L-C filter at the rectifier output [19]

- e) over-dimension the diode-bridge rectifier [19]

- f) derive control electronics power supply from the dc bus capacitor by means of a Switch Mode Power Supply [7,18]

- g) dc bus voltage control during a sag by operating the dynamic braking IGBT in boost mode with the addition of three diodes and an inductor [20]

- h) have an active rectifier front end [21]

The advantages as well as disadvantages of the above strategies are discussed as follows:

a) Increasing ac side line reactors would help to smooth the rectifier currents during an unbalanced voltage sag and improve the ride-through performance against overcurrent tripping but would permanently account for a drop in the input voltage especially at higher line currents [7]. Also they add to the cost and size of the VSDs.

b) Larger bus capacitor ensures smaller ripple voltage in the dc bus and also improves the ride through capability of the VSD during a sag condition. But it results in higher recharging currents when the voltage returns to normal which may lead to damage of the rectifier components or tripping of the VSD on an over-current fault.

c) Interestingly, another suggestion contrary to (b) recommends to lower the dc bus capacitance value for some specific control strategies [19]. The advantage here is the

lower current peaks in the rectifier circuit whereas this strategy results in higher dc bus voltage ripple and reduced energy storage for sag ride-through operation.

d) Addition of an L-C filter in the dc link helps smooth the current in the rectifier thereby avoid VSD over-current tripping. Apart from that, it is also useful in limiting the ac side harmonic pollution generated by a VSD [19]. The main disadvantage here again is the extra cost and space requirement.

e) Another suggestion recommends to overrate the diode bridge to twice the normal current rating [19]. This strategy helps to take care of higher capacitor charging currents during unbalanced power supply and transients but it increases the cost.

f) Many older versions of VSDs derived power for the control electronics from the incoming ac supply which was also monitored for under-voltage trips. In such cases, the control power supply being sensitive to ac supply variations, caused large number of nuisance tripping during sags and transients. Hence, it is recommended to derive the power supply for control electronics from the dc bus [7,18] and the advantage is the capacitor backs up the power supply during supply variations. Most modern drives are already incorporating this feature.

g) Another strategy suggests controlling the dc bus voltage at a required level during a sag condition by the addition of three diodes and an inductor to the standard VSD hardware used in a VSI configuration [20]. These additional components, along with the lower half of the diode rectifier and the existing dynamic braking IGBT (which is a standard component in VSDs), can be operated as a boost rectifier during a sag and the bus voltage can be maintained at the desired value. It is reported that the performance of the VSD is unaffected, without any speed fluctuations, when subjected to a sag of magnitude 50% lasting for 30 cycles [20]. In spite of the high level of sag ride-through performance, the additional cost and space requirements cannot be justified for all types of VSD applications.

h) Use of a controlled front-end rectifier is recommended which will improve the dc bus characteristics of VSDs during voltage sags with the additional advantage being lower harmonic pollution in the power system [21]. But again, the main disadvantage is the additional cost.

It can be observed that, most of the hardware related mitigation strategies involve additional costs and increased space requirement in VSDs. Suggestions (a) to (d) are intended to delay the tripping so that VSDs can override sags of short duration. Suggestions such as (e) and (f) are already in usage in recent drives. Though strategies (g) and (h) help to improve the ride-through performance during adverse sag conditions, they are not popularly implemented mainly due to the cost and space constraints.

## 1.5.2 MITIGATION TECHNIQUES BY MEANS OF IMPROVED POWER SUPPLY CONDITIONS

Some sag ride-through mitigation strategies suggest to improve the power supply conditions rather than modifications in VSDs to overcome the discontinuity of operation during a voltage sag. The various suggestions alongwith their advantages as well as disadvantages are discussed below:

- a) transfer of supply between two independent power sources [11,22]

- b) use of thyristor controlled tap changer (CTCs) [4,23]

- c) use of a Motor Generator Set to provide power supply [4]

- d) use of a Power Line Conditioning Equipment [4]

- e) use of Uninterruptable Power Supply (UPS) for control electronics [18]

a) Transfer of power supply to an alternative source by means of solid state switches is recommended in [11] when a sag occurs. A very smooth transition is reported without any significant speed or torque disturbances in the VSD performance when a 24 kV power supply was transferred to an alternative system [11]. However, this solution calls for a very high capital investment. But the drawback of this solution, in spite of backing up the entire plant supply, is that it can only prevent external disturbances

from entering the local system but cannot prevent sags from being generated due to internal plant electrical faults.

b) Another suggestion recommends the use of a thyristor controlled tap-changer (CTC) in order to maintain the ac supply voltage at nominal levels [4,23]. The reported advantages are fast response, low total harmonic distortion (THD) and high efficiency. The disadvantages are the high cost and space requirements.

c) The use of a Motor Generator Set is suggested in order to supply critical loads such as VSDs [4]. The advantages are the ability to withstand deeper sags, high output regulation and electrical isolation. The disadvantages are high investment costs, maintenance, low efficiency and increased space.

d) Another strategy suggests the use of power line conditioners in the ac supply which results in very fast voltage regulation and low harmonic current distortion [4]. However it is also an expensive solution.

e) Use of an Uninterruptable Power Supply (UPS) is suggested for supplying the control electronics in [18]. This suggestion may guarantee uninterrupted control supply, but cannot prevent the VSD from tripping because of dc bus under-voltage or ac over-current faults.

From the above discussions, it can be realised that the main disadvantage of the power supply related suggestions is their high costs with most of the solutions more expensive than the cost of the VSDs. Also, they occupy considerable space. Moreover, since most of these type of strategies attempt to provide a plant-wide solution to power quality problems, they cannot take care of the disturbances which occur due to internal plant faults.

## 1.5.3 MITIGATION TECHNIQUES BY CONTROL ALGORITHM MODIFICATIONS

So far, sag ride-through strategies either by modifying the VSD hardware or by improving ac power supply conditions have been discussed. It was found that, most of the hardware related suggestions are aimed at delaying the VSD tripping during sags and they cannot prevent VSD tripping due to longer and deeper sags. Moreover, these solutions tend to increase the cost and space requirements in the VSD. The power supply related suggestions are too expensive to consider for most of the VSD applications. Also, they have other disadvantages such as additional space requirement, poor efficiency, maintenance requirements and inability to prevent sags occurring from within the plant. The ideal solution would be to enable the VSD to ride-through the voltage sags. The best means to achieve this objective would be by improving the control algorithm in the VSD. With this type of solution, the standard VSD hardware can be retained and the disadvantages such as additional cost and space can be avoided. The suggestions available in this category are:

- a) modulation index and stator frequency compensation [19]

- b) maintaining the inverter output synchronised with the motor i.e. operate the VSD with minimum losses [16,24]

- c) bus capacitor voltage control by recovering the kinetic energy available in the rotating mass [25]

The VSD performance characteristics when controlled by the above strategies are analysed below:

a) The first strategy suggests to compensate for the modulation index and stator frequency according to the dc bus voltage available during a sag. This leads to shifting the torque-speed characteristics towards the origin during a sag and this technique ensures maximum torque availability to the motor at all speeds despite a reduction in the motor speed [19]. But, since the dc bus characteristics are not improved by this control strategy, VSD tripping can still occur due to dc under-voltage or ac over-current faults as discussed in Section 1.4.

b) Another control based strategy recommends maintaining the supply output of the VSD synchronised with the induction machine flux and operate it at zero slip during a sag [16,24]. This means only a minimal power corresponding to the winding losses in the machine is drawn from the dc capacitor. This solution ensures that the dc voltage is reduced at a slower rate than during normal operation and thus extends the ride-through operation of the VSD during sags until the dc voltage reaches a very low level. The machine coasts towards zero speed. Since the inverter remains synchronised with the machine flux, the VSD can be automatically restarted on power supply recovery. Here, the sag ride-through performance depends on the dc bus voltage at the point of supply recovery which in turn depends on the losses in the motor.

c) Finally, another control strategy recommends maintaining the dc bus voltage at a required level by recovering the kinetic energy available in the rotating mass during a voltage sag condition [25]. This method can be employed for both field orientation and constant v/f (VVVF) controls. The kinetic energy can be recovered until the motor speed becomes zero. During this operation, the motor decelerates to zero speed at a faster rate than during normal coasting and this deceleration rate is proportional to the amount of energy regenerated and the load present on the motor. But, the kinetic energy decreases proportional to the square of the speed and it can be realised that due to this cumulative effect, the kinetic energy is highly speed dependent. So the sag ride-through performance under this strategy is limited by the load as well as motor speed. If the voltage sag persists even after the motor has come to standstill, then the capacitor voltage will start to reduce and the VSD can trip due to under-voltage or over-current faults as discussed in Section 1.4.

#### **1.6 AIM OF THE THESIS**

The main aim of the work presented in this thesis is to improve the sag ride-through performance of VSDs by modifying the control algorithm. The control strategies available in this category result in improved ride-through characteristics but their performance is limited by factors such as losses in the motor or non availability of kinetic energy at zero speed. An improved control strategy is proposed in this thesis which will enable extended voltage sag ride-through performance of the VSDs compared to the conventional strategies. The proposed strategy is an extension of the control strategy recommended in [25] where the dc bus capacitor voltage is maintained at a desired level by recovering the kinetic energy available in the rotating mass. It can be shown that during normal operation, a considerable amount of energy is available in the motor in the form of kinetic as well as magnetising energy as compared to the energy levels present in the dc bus capacitor (refer Appendix A). Therefore, whenever a voltage sag occurs, the dc bus voltage can be maintained at a desired level, by recovering the kinetic energy available in the rotating mass at high motor speeds and by recovering the magnetising energy available in the motor winding inductances at low speeds. Though the energy available in the inductances can supply the dc bus capacitor only for a short duration, the dc voltage will be maintained at the set value even after the complete energy is recovered from the motor because no further energy will be drawn from the dc capacitor during a sag. Once the ac supply returns to nominal level, normal VSD operation can be restored. The advantage of this control strategy over the conventional ones (which were discussed in Subsection 1.5.3) is that a sag ride-through performance can be achieved even after the motor reaching zero speed. This strategy is applicable for both induction motor (IM) as well as synchronous reluctance motor (SRM) VSDs.

#### **1.7 CONTRIBUTIONS OF THIS THESIS**

1) In this thesis, a new strategy is proposed to maintain the dc capacitor voltage by recovering the magnetising energy available in the ac motor winding inductances. This is demonstrated in the case of an SRM VSD.

Reasons for the inability to recover the magnetising energy in the case of an IM VSD are presented.

3) Utilising the concept of the proposed control strategy, an open loop dc bus voltage control is presented with optimum reduction of motor flux so that an IM VSD can ride-through voltage sags at low speeds.

4) A controlled coordination of bus voltage control is demonstrated by initially recovering kinetic energy from the rotating mass at high motor speeds and then the magnetising energy from the motor winding inductances at low speeds until zero speed so that the VSD rides through voltage sags at all speeds.

#### **1.8 SCOPE OF WORK AND PLAN OF THE THESIS**

In this thesis, the sag ride-through performance of both an IM VSD and an SRM VSD when controlled by the proposed strategy will be presented. Forthcoming chapters are organised as follows:

In <u>Chapter 2</u>, the outline and details of the proposed control strategy will be presented. The control set points and the order of control sequence will be justified. Since this strategy will be applied to both IM and SRM VSDs, simulation models will be presented for both these VSD types and the basic control loops used in these VSDs will be discussed. The design and implementation of the additional control loops required for the capacitor voltage control by recovering the energy available in the ac motors will be discussed and their coordination with the existing control loops in the VSDs will be described. Finally, the power flow relationship between various sections of the VSD system will be derived.

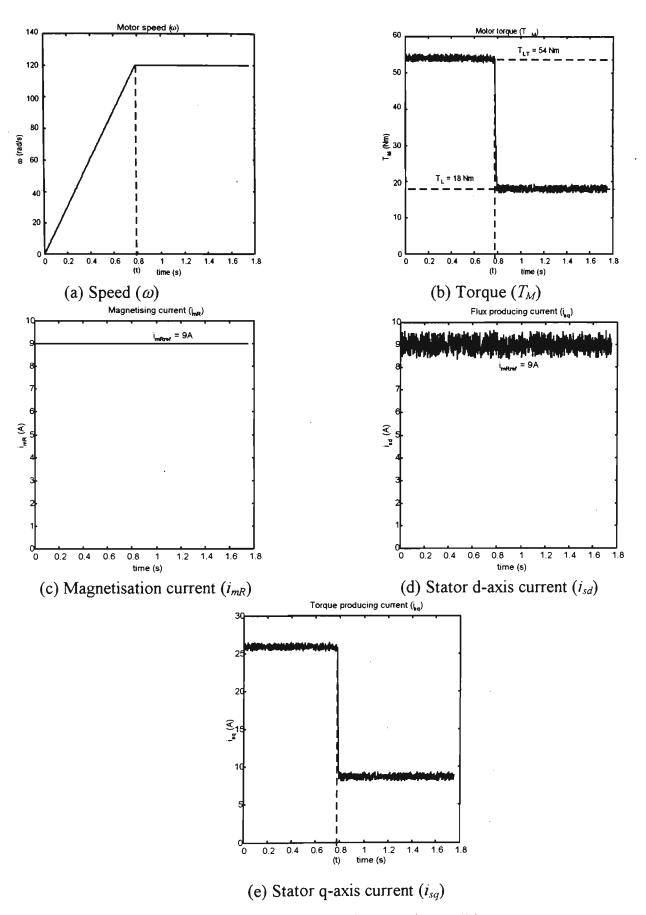

<u>Chapter 3</u> will present the performance results of the proposed control strategy in the case of an SRM VSD. Initially, the normal speed control operation of the simulation model will be verified and then the performance results with the proposed strategy at high as well as low motor speeds during a sag will be analysed. Finally, the sag ride-through performance at an intermediate speed will be presented where the coordinated transition of control from the kinetic energy recovery at high speeds to magnetising energy recovery at low speeds can be observed.

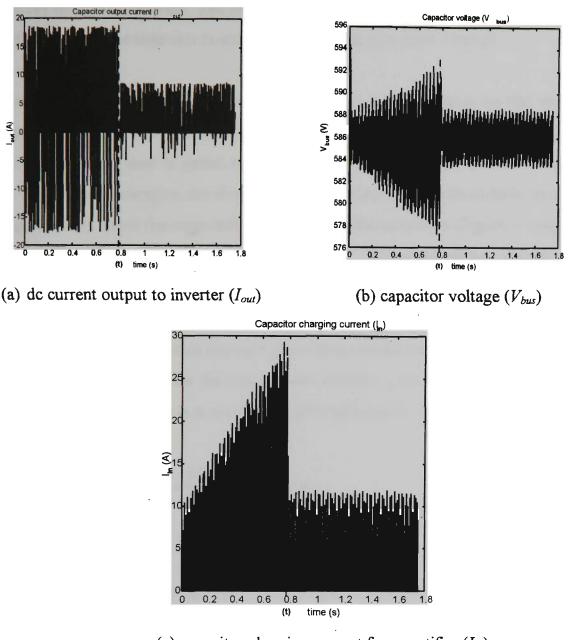

In <u>Chapter 4</u>, the performance of this control strategy will be analysed in the case of an IM VSD. Initially, the normal speed control operation will be verified. Then, the performance results during dc voltage control at high and low speeds in the presence

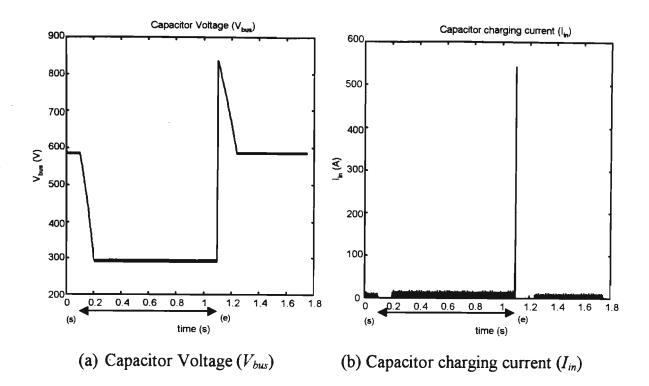

of a sag will be analysed. Because of the inability to recover the magnetising energy in the case of an induction motor, an alternative control scheme is proposed which can be utilised at low motor speeds. The combined operation using both these modes of the control strategy is presented in order to demonstrate the sag ride-through capability of the proposed strategy at all speeds.

<u>Chapter 5</u> summarises the performance of this control strategy for both IM and SRM VSDs.

## **CHAPTER 2**

## PROPOSED CONTROL STRATEGY AND MODELLING OF VSDs

#### 2.1 INTRODUCTION

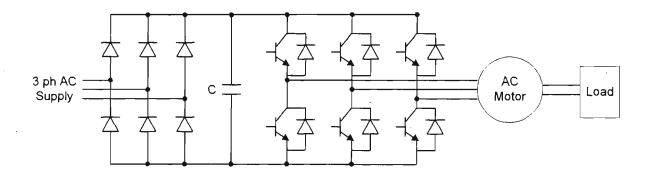

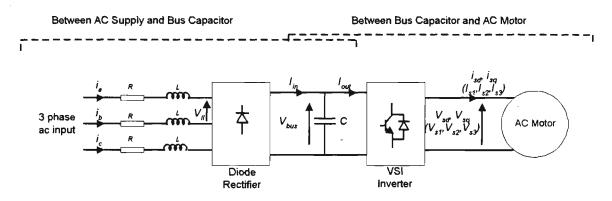

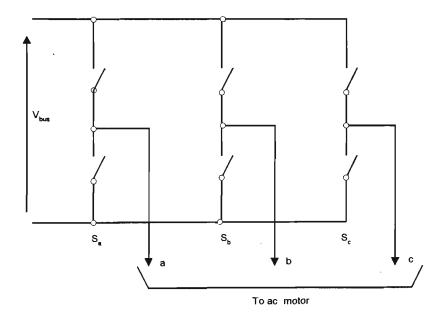

In this chapter, a control algorithm based mitigation technique that can be applied to an ac VSD in order to achieve an improved voltage sag ride-through performance is proposed. Since about 80% of recent ac drives have VSI configuration with a three stage topology (Fig. 2.1), i.e. a diode bridge rectifier front-end, a dc link capacitor and a PWM inverter [7, 15-16], an ac drive with this configuration alone will be considered in this thesis. Field orientation technique will be applied and the behaviour of IM and SRM VSDs when subjected to a voltage sag condition will be examined

Fig.2.1. VSD with a VSI configuration having a diode bridge front-end

As already mentioned in Section 1.4, disturbances in control power supply and drop in dc bus voltage are the two main causes for the interruption of VSD during voltage sags. The stability of control circuit power supply can be ensured by deriving it from the dc bus capacitor through a Switched Mode Power Supply (SMPS) [7,18], which will buffer the impact of ac supply fluctuations from affecting the control power supply. Now, the main

task of the VSD control system is to maintain the dc bus voltage at a desired level during a voltage sag so that the drive rides-through the sag without tripping due to the fault conditions which were discussed in Section 1.4.

As shown in Appendix A, during normal operating conditions, there is a considerable amount of energy present in an ac motor in the form of kinetic energy due to system inertia and magnetising energy in the motor winding inductances. When a voltage sag occurs, the dc bus voltage can be maintained at a desired level by coordinated recovery of energy from these two sources so that the continuity of operation of the VSD can be achieved.

In this chapter, the proposed control strategy will be discussed in further detail. Because this strategy requires modifications in the VSD control algorithm, there will be a brief mention about the basic control loops used in a VSD operating under field orientation which will be followed by a simplified block diagram representation of the IM and SRM VSDs for simulation purposes. Then, the design details of the additional control loops required by this strategy and their operation sequence in coordination with the existing control loops will be elaborated. Since there is a continuous flow of energy between the ac mains, dc bus capacitor and the ac motor, and moreover because the proposed control strategy aims to recover energy from the motor to the dc capacitor during a voltage sag, the power flow equations involving the ac mains, VSD and the ac motor will be presented.

#### 2.2 PROPOSED CONTROL STRATEGY

Out of the two sources of energy within the ac motor, viz. kinetic energy  $(\frac{1}{2}J\omega^2)$  and the magnetising energy  $(\frac{1}{2}LI^2)$ , the kinetic energy is the most dominant component and at rated motor speed, it usually accounts for several times the energy stored in the capacitor (refer Appendix A). The kinetic energy can be recovered from the rotating mass by operating the PWM inverter in the regeneration mode i.e. by operating the motor as a

generator and by reversing the flow of energy from the motor to the dc bus. The magnetising energy stored in the motor inductance can be recovered by forcing the magnetising current reference to a lower value when the inductance acts as a current source and feeds the stored energy back to the dc bus. The energy thus recovered in both cases can be utilised to maintain the dc bus voltage at a desired level during a sag.

In order to establish an efficient and simpler control system, it is better to attempt energy recovery from one source at a time. The fact that the motor requires magnetic field in order to function as a generator makes kinetic energy the first choice of energy source that can be recovered. When the motor functions as a generator, its speed falls more rapidly than normal coasting, i.e. with the incoming supply cut off. The rate of speed drop during regeneration depends on factors such as the amount of energy regenerated, the load torque and system inertia. When the motor speed reaches very low values, the stored kinetic energy reaches negligible proportions and the motor cannot deliver the power required at the dc bus. There is no advantage in reducing the speed below some limit. Hence, a cut-off speed limit is defined below which, this strategy would attempt to recover the energy available in the magnetising inductances.

#### 2.2.1 SET POINTS FOR CONTROL STRATEGY

Under normal circumstances, a voltage sag condition can be detected by the VSD control system by monitoring either the line-to-line ac supply voltage  $(V_{ll})$  or the dc capacitor voltage  $(V_{bus})$ . Since the proposed control strategy is aimed at maintaining the dc bus voltage at a desired value during a sag, a voltage sag should be detected in this case by monitoring the incoming three-phase supply voltage only. Since as per the definition, a voltage sag is reduction in rms supply voltage between 0.1 to 0.9 p.u. of the nominal value [5,10], whenever any of the three line-to-line supply voltages to the VSD drop below 90% of the nominal ac voltage, a sag condition is declared and remedial actions are taken.

The set point for the bus voltage  $(V_{busref})$  during a voltage sag is also very important for proper coordination of the VSD under the proposed strategy. In the case of a three phase rectifier, the dc bus voltage  $(V_{bus})$  is normally 1.35 times the rms line-to-line voltage  $(V_{ll})$ . When a voltage sag occurs, the dc bus voltage falls below the nominal level. The deeper the sag magnitude becomes, the lower the dc bus voltage will be and the higher will be the chances of the VSD tripping due to under-voltage or over-current faults (as already explained in section 1.4). Usually in a VSD, the under-voltage trip settings are user configurable and are kept as a percentage of the nominal voltage (typically between 70% and 85%) [19]. Ideally, the bus voltage should be maintained between the nominal voltage and trip setting when a sag occurs. Here, the bus voltage reference is kept as 100% of the nominal rated dc bus voltage for reasons that will be explained during the ride-through simulations in Chapters 3 and 4.

Earlier in this section, a cut-off speed for the control transition in the energy recovery from kinetic energy to magnetising energy was mentioned. Though theoretically the motor can be operated in regeneration mode down to zero speed, in this simulation the cut off point is kept at 10% of the rated speed because less than about 1% of the rated kinetic energy is available in the motor below this speed.

#### 2.2.2 CONTROL SEQUENCE AND FLOW CHARTING

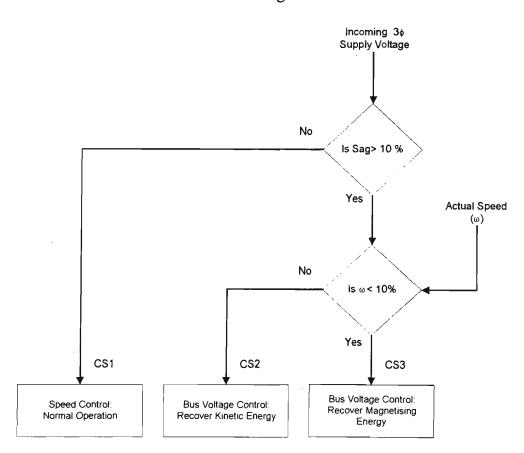

The sequential flowchart of the VSD control during a voltage sag condition is as shown in Figure 2.2.

It can be observed from the flowchart that, as per the proposed control strategy, there are three distinct situations involved with respect to the control of the VSD. They are summarised as follows:

Control Situation 1 (CS1): (No Voltage sag) VSD operation with normal speed control.

**Control Situation 2 (CS2):** (Voltage sag and motor speed > cut-off speed) DC bus voltage control by recovering load kinetic energy.

**Control Situation 3 (CS3):** (Voltage sag and motor speed < cut-off speed) DC bus voltage control by recovering magnetising energy.

The above control situations, which are indicated as CS1, CS2 and CS3 in the Figure 2.2, will be referred to in the remainder of the thesis while discussing the controller design and analysing the performance results. In order to achieve the desired sag ride-through operation, additional control loops are necessary within the VSD control system and they will be discussed in the following sections. Since it is intended to demonstrate the recovery of energy from the magnetising inductances, operation below motor base speed alone will be considered in this thesis and field weakening control will not be examined.

Fig.2.2. Flow chart for VSD control sequence during voltage sag condition

## 2.3 CONTROL LOOPS IN AC VSDs OPERATING UNDER FIELD ORIENTATION

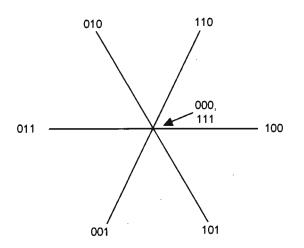

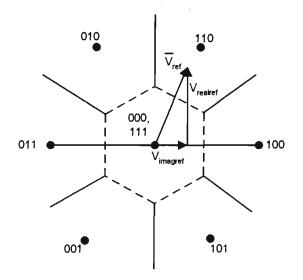

In this section, an overview of the basic control loops in an ac VSD will be presented and the control block diagrams of IM and SRM VSDs will be discussed. In field oriented control of ac motors, the three phase motor currents are transformed into two orthogonal components in a synchronous frame of reference which moves with respect to the stator axes, and they are defined as  $i_{sq}$ , the torque producing component and  $i_{sd}$ , the flux producing component [26]. The mathematical relationships between these current vectors for IM and SRM are shown in Appendices B and C respectively. A brief overview of the control loops used in ac VSDs is as follows:

For the speed control of an ac motor, two sets of control loops are used in the VSD, viz. (a) a speed controller working in conjunction with a current controller for the torque producing current component  $(i_{sq})$  and (b) a flux controller working in conjunction with another current controller for the flux producing current component  $(i_{sd})$  [27]. Usually all these controllers are of proportional-integral (PI) control type operating in closed loop configuration.

The main purpose of the speed controller is to regulate the motor speed at a set reference. The speed regulator generates the torque reference to the motor depending on the instantaneous speed error and the controller gain values. In closed loop speed control, the torque reference tends to control the motor to reach the set speed by minimising the speed error to zero. In order to protect the motor from being subjected to excessive currents, the speed regulator output is limited by a torque limiter. The limited torque reference is converted to torque producing current reference ( $i_{sqref}$ ) which forms the control input to the torque producing current regulator. This current regulator functions in a similar manner to the speed regulator but generates set points for motor terminal voltage so that, in closed loop control, the motor continues to run at the set speed for load torque variations between zero and the torque limit. When the load torque demand exceeds the

torque limit, the actual motor torque is clamped at this limit and the motor speed drops below the set reference.

The flux controller regulates the actual flux (or magnetising current) to the set value and it produces the flux producing current reference ( $i_{sdref}$ ). The corresponding current regulator controls the flux producing current component by again influencing the set points for motor terminal voltage.

Finally, the output of the above control loops, i.e. the voltage set points, decide the switching vector selection as required by the PWM inverter at any instant. Based on the selected vector, the switches in the three inverter legs (Fig.2.1) are either opened or closed, thereby connecting the motor terminals to either the positive or negative dc bus and thus the voltage applied to the motor is controlled by the VSD control system.

The functional block diagram representation of VSD control scheme for IM and SRM VSDs operating under field orientation is discussed in the following subsections.

#### 2.3.1 CONTROL MODEL OF AN IM VSD

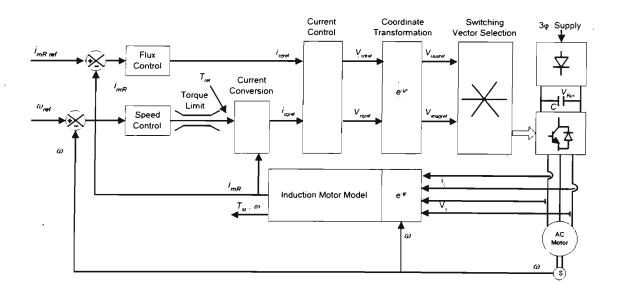

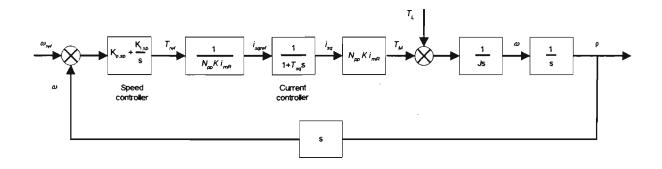

Figure 2.3 Functional block diagram of an IM VSD under field orientation control

Figure 2.3 shows the simplified block diagram representation of an IM VSD operating under field orientation, which is based on the motor modelling described in Appendix B. Tuning details of the controllers are discussed in Appendix E.

For speed control of an induction motor, the speed reference  $(\omega_{ref})$  and the magnetising current reference  $(i_{mRref})$  are the two main control inputs. The Flux Controller generates the flux producing current reference  $(i_{sdref})$  whereas the speed PI controller generates the torque reference, which after being limited, is converted to the torque producing current reference  $(i_{sqref})$  in the Current Conversion block. Based on the current references  $(i_{sdref}$ and  $i_{sqref})$ , the Current Control block generates the voltage set points  $(V_{sdref} \text{ and } V_{sqref})$ . In field oriented control of induction motors, the synchronous coordinates are displaced from the stator coordinates by an angle  $\rho$  as explained in Appendix B. In order to select the proper switching vector as required by the control system, it is necessary to transform these voltage reference values into real and imaginary coordinates fixed to the stator reference frame and this is done by the Coordinate Transformation block. Finally, the required switching sequence of the inverter switches is selected by the Switching Vector Selection block, the details of which are explained in Appendix D.

Based on the inverter switching sequence and the instantaneous dc bus voltage at the rectifier output, a three-phase ac voltage is applied to the motor terminals. In actual case, the flux and current controllers are of proportional-integral (PI) type and the motor speed is sensed by the control system from the speed sensor feedback (or by means of indirect speed estimation methods). Other motor variables such as voltages and currents in field coordinates and motor torque are computed from the terminal voltages and currents by the built-in motor model within the VSD as shown in the control block diagram (Figure 2.3).

However, in this simulation, the motor variables such as voltages ( $V_{sd}$  and  $V_{sq}$ ), currents ( $i_{sd}$  and  $i_{sq}$ ), torque ( $T_M$ ) and speed ( $\omega$ ) are calculated based on the actual switching vector selected and the instantaneous dc capacitor voltage ( $V_{bus}$ ), utilising the IM equations whose derivations are explained in Appendix B. The three-phase ac supply, diode bridge

rectifier and dc bus capacitor are also modelled in the VSD control system. The control equations used in the various control blocks are summarised as follows:

The <u>Flux Control</u> block calculates the motor flux producing current reference  $(i_{sdref})$  from the magnetising current reference  $(i_{mRref})$  utilising the following equation:

$$i_{sd} = i_{mR} + \frac{di_{mR}}{dt} T_R \tag{2.1}$$

where,

$i_{sd}$  - stator d-axis current,  $i_{mR}$  - rotor magnetising current,  $T_R$  - rotor time constant

The <u>Torque / Current Conversion</u> block utilises the following motor torque equation in order to calculate the torque producing current set point  $(i_{sqset})$  from the set torque reference  $(T_{ref})$ :

$$T_M = N_{pp} K i_{mR} i_{sq} \tag{2.2}$$

where,

$$K = \frac{2 * L_m}{3 * (1 + \sigma_r)}$$

$N_{pp}$  - number of pole pairs in the motor,

$i_{mR}$  - magnetising current reference,

$L_m$  - mutual inductance between stator and rotor windings, and

$\sigma_r$  - rotor leakage factor.

The <u>Current Control</u> block calculates the stator voltage set points in field coordinates  $(V_{sdref} \text{ and } V_{sqref})$  based on the following equations:

$$V_{sd} = R_s i_{sd} + \sigma L_s \left(\frac{di_{sd}}{dt} - \omega_{mR} i_{sq}\right) + (1 - \sigma) L_s \frac{di_{mR}}{dt}$$

(2.3)

$$V_{sq} = R_s i_{sq} + \sigma L_s \left(\frac{di_{sq}}{dt} + \omega_{mR} i_{sd}\right) + (1 - \sigma) L_s \omega_{mR} i_{mR}$$

(2.4)

where,

$R_s$  - stator resistance,

$L_s$  - stator inductance,

$\sigma$  - total leakage factor,

$\omega_{mR}$  - angular velocity of the magnetising vector

The <u>Coordinate Transformation</u> block transforms the selected voltage references ( $V_{sdref}$  and  $V_{sqref}$ ) from the synchronous coordinates to the stator coordinates according to equation (2.5):

$$\overline{V}_s = V_{s\_real} + jV_{s\_imag} = (V_{sd} + jV_{sq})e^{j\rho}$$

(2.5)

where,

$\rho$  - angle between the synchronous and stator coordinates.

$\vec{V_s}$  - stator voltage vector

The <u>Switching Vector Selection</u> block selects the appropriate operating sequence for the inverter switches, based on  $V_{realref}$  and  $V_{imagref}$  chosen in the Coordinate Transformation block. The details of vector selection are explained in Appendix D.

The <u>Induction Motor Model</u> calculates the actual motor voltages, currents (in d-q axes) and torque depending on the switching vector selected and the instantaneous capacitor voltage ( $V_{bus}$ ) utilising equations (2.1) to (2.5). The motor speed is calculated by integrating equation (2.6).

$$d\omega = \frac{\left(T_M - T_L\right)dt}{J} \tag{2.6}$$

where

$T_M$  – motor torque,  $T_L$  - load torque, and J - system inertia.

#### 2.3.2 CONTROL MODEL OF AN SRM VSD

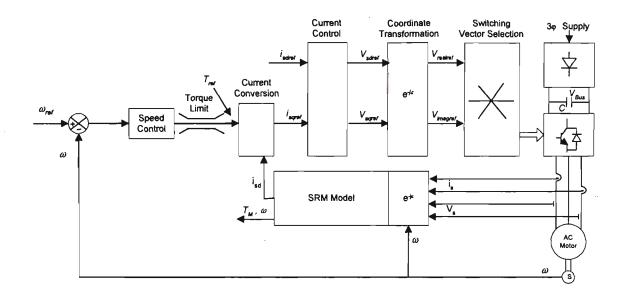

Fig 2.4 Functional block diagram of an SRM VSD under field orientation control

The simplified control block diagram of an SRM VSD under field orientation control is represented in Figure 2.4. The motor modelling and the tuning of the controllers are explained in Appendices C and F respectively.

In the case of an SRM VSD, velocity reference  $(\omega_{ref})$  and magnetising current reference  $(i_{sdref})$  form the control inputs. The main difference in the control of SRMs as compared to the induction motors is due to the orientation of the flux axis. In the case of an SRM, the flux axis aligns itself with the rotor axis and the magnetising current is the direct component of the stator current vector  $(i_{sd})$ . The details of the current vectors and their angular relationships in the various coordinates are explained in Appendix C for an SRM. The control of an SRM is similar to that of an IM with similar control blocks as explained in Subsection 2.3.1. The following SRM equations are used in the various control blocks:

$$T_M = \frac{3}{2} N_{pp} (L_{sd} - L_{sq}) i_{sd} i_{sq}$$

(2.7)

$$T_M - T_L = J \frac{dw}{dt}$$

(2.8)

$$V_{sd} = R_s i_{sd} + L_{sd} \frac{di_{sd}}{dt} - \omega L_{sq} i_{sq}$$

(2.9)

$$V_{sq} = R_s i_{sq} + L_{sq} \frac{di_{sq}}{dt} + \omega L_{sd} i_{sd}$$

(2.10)

$$\vec{V}_s = V_{s\_real} + jV_{s\_imag} = (V_{sd} + jV_{sq})e^{j\varepsilon}$$

(2.11)

where,

$T_{M}$ - motor torque  $T_{L}$ - load torque J - system inertia  $N_{pp}$  - number of pole pairs  $R_{s}$  - stator resistance  $L_{sd}, L_{sq}$  - stator inductance in d and q axes  $\varepsilon$  - rotor angle with respect to stator axis  $\omega$  - rotor angular velocity  $\overline{V}_{s}$  - stator voltage vector  $i_{sd}, i_{sq}$  - stator currents in d and q axes

$V_{sd}$ ,  $V_{sq}$  - stator voltages in d and q axes

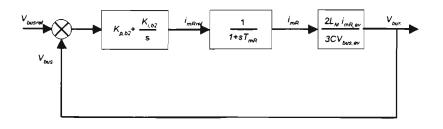

# 2.4 PROPOSED ADDITIONAL CONTROL LOOPS FOR DC BUS VOLTAGE CONTROL

It may be recalled from Section 2.2 that the main intent of the proposed control strategy is to maintain the capacitor voltage at the nominal value by recovering the kinetic as well as the magnetising energy available in the motor. Three control situations were defined, viz. (a) No sag situation (Control Situation 1), (b) A voltage sag condition with the motor running above the cut-off speed limit (Control Situation 2) and (c) A voltage sag condition with the motor with the motor running below the cut-off speed limit (Control Situation 3). An overview of the basic control loops for the speed control of IM and SRM VSDs was presented in Section 2.3. From the point of view of the proposed control strategy, these are the control

loops that will be in operation during a no sag situation (Control Situation 1). However, since there is a need to recover the energy present in the motor during a sag, additional control loops are necessary in the VSD control system. The control methodology, design and implementation of the additional control loops will be discussed in the following subsections and their sequence of operation in coordination with the existing control loops will be defined. Tuning details of the additional controllers are presented in Appendices E and F for IM and SRM respectively.

### 2.4.1 BUS VOLTAGE CONTROL BY RECOVERING LOAD KINETIC ENERGY

At higher motor speeds, the capacitor voltage can be controlled by recovering the kinetic energy available in the rotating mass. Kinetic energy can be recovered by operating the motor as a generator. Electrically this means reversal of the flow of current from the ac motor to the dc bus with rated flux applied to the motor. From a control point of view, this can be achieved by maintaining the flux reference to the motor constant at the rated value and by reversing the polarity of the torque reference ( $T_{ref}$ ) which, in turn, will reverse the flow of  $i_{sq}$ . This operation is further explained by the power balance equation (2.12) whose derivation will be shown in Section 2.5.

$$V_{bus} I_{out} = \frac{2}{3} \left( V_{sd} i_{sd} + V_{sq} i_{sq} \right)$$

(2.12)

where,

$V_{bus}$  – bus capacitor voltage  $I_{out}$  – dc current flowing between the bus capacitor and the inverter  $V_{sd}$ ,  $V_{sq}$  – stator voltages in synchronous coordinates  $i_{sd}$ ,  $i_{sq}$  – stator currents in synchronous coordinates

From equation (2.12), it can be noted that, by maintaining the flux  $(i_{sd})$  constant, if  $i_{sq}$  is reversed, the flow of the dc current  $I_{out}$  can be reversed from the motor to the dc bus

which will boost the capacitor voltage. This is the basis of the control utilised in Control Situation 2.

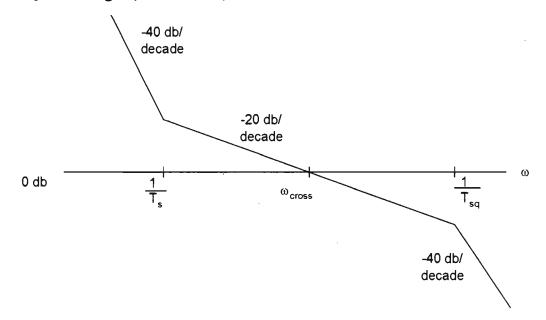

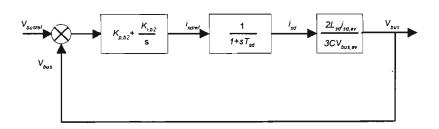

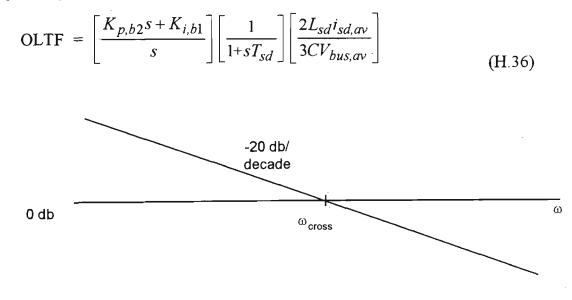

In a voltage sag condition, the recovery of kinetic energy must be controlled so that only the required amount of energy is recovered from the motor to maintain the capacitor voltage at the desired value. This can be done by the use of a closed loop proportionalintegral (PI) controller, which monitors the capacitor voltage against the set reference and produces a suitable torque reference. The polarity of the torque reference is reversed to that of normal speed control operation. A new PI controller is configured in the VSD control system for this purpose which will be referred to as Bus Voltage Controller 1 in further discussions.

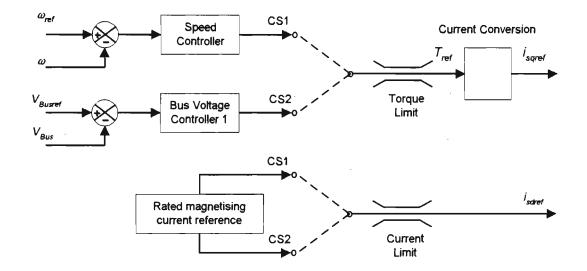

As described in Section 2.3, during normal speed control operation (Control Situation 1), the torque reference is generated by the Speed Controller in order to regulate the motor speed at the set reference. When a sag occurs, if the motor speed is above the cut-off limit (i.e. Control Situation 2), the torque control is switched to the Bus Voltage Controller 1. This controller applies a reverse torque reference and controls the capacitor voltage rather than motor speed. The Current Controller as well as rest of the control blocks (which are shown in Figures 2.3 and 2.4) operate exactly in the same manner as during speed control and motor speed is not controlled in this situation. Because of the regenerative operation, the motor speed will reduce rapidly during this control. While recovering the kinetic energy, the torque limiting circuit must be in circuit to ensure that the motor currents are within the allowable levels. The transition between the Speed Controller and Bus Voltage Controller 1 is reversible when the motor speed is above the cut-off limit, i.e. when a sag occurs, torque referencing switches from Speed Controller to Bus Voltage Controller 1 and vice versa if the sag disappears when the motor speed is still above the cut-off limit. The magnetising current reference is maintained at the rated value throughout this operation. Figure 2.5 shows the sequence of operation of the control system during a sag at high motor speeds. Control Situations 1 and 2 are indicated as CS1 and CS2 respectively.

Figure 2.5 Control loop to recover kinetic energy

Since the basis of speed and torque control operation is identical for IM and SRM VSDs, as explained in Section 2.3, the proposed control scheme is applicable for both motor types. The control strategy at motor speeds lower than the cut-off speed limit is discussed in the following subsection.

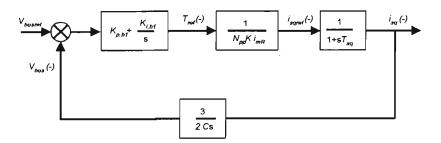

## 2.4.2 BUS VOLTAGE CONTROL BY RECOVERING MAGNETISING ENERGY

If a voltage sag occurs when the motor speed is below the cut-off limit (Control Situation 3), the magnetising energy stored in the motor inductance can be recovered to boost the bus capacitor voltage. This energy recovery can be achieved by lowering the magnetising current, (which is  $i_{sd}$  for an SRM and  $i_{mR}$  for an IM). From the stator voltage equations, (equations (2.3) and (2.9) respectively in the case of IM and SRM), it can be found that lowering the magnetising current reference results in the polarity reversal of the applied voltage  $V_{sd}$ . There is no torque needed during this control situation and hence  $i_{sq}$  is controlled to zero. From the power flow equation (2.12), which was referred to in Subsection 2.4.1, it can be noted that, with zero  $i_{sq}$ , reversal of  $V_{sd}$  reverses the flow of the

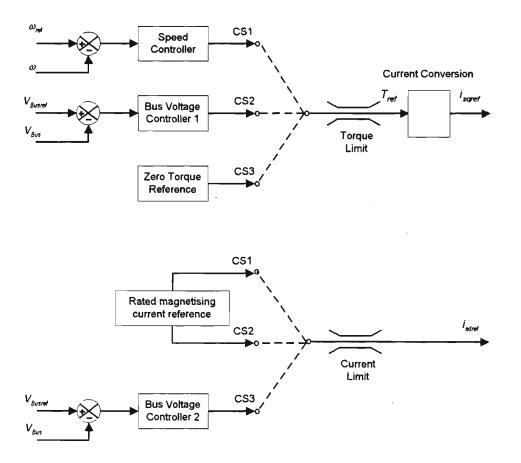

current  $I_{out}$  from the motor to the dc bus which will boost the capacitor voltage  $V_{bus}$ . In order to achieve a controlled recovery of this magnetising energy, another PI controller (Bus Voltage Controller 2) which monitors  $V_{bus}$  against the set reference is employed to control (reduce) the flux reference. Figure 2.6 shows the sequence of operation and Control Situations 1, 2 and 3 are indicated as CS1, CS2 and CS3 respectively.

Figure 2.6 Control loop to recover magnetising energy

It can be observed that, Control Situation 3 can be initiated from either Control Situation 1 (normal speed control) or from Control Situation 2 (kinetic energy recovery). When a sag is present and if the motor speed is below the cut-off speed, Control Situation 3 comes into effect. When the power supply returns to normal, normal speed control operation resumes and the motor is speed controlled with the rated flux applied to the motor.

# 2.5 POWER BALANCE BETWEEN AC SUPPLY, BUS CAPACITOR AND AC MOTOR

Fig. 2.7 Power flow diagram in an ac VSD

Since the proposed control strategy aims to recover energy from the motor to the dc capacitor during a voltage sag and also because there is a continuous flow of energy between the ac mains, dc link and the ac motor, the power flow equations relating the voltages and currents in these sources are discussed here. The VSD configuration considered in this thesis is shown in Figure 2.1. During motoring, power flows from the incoming ac supply to the dc bus capacitor (through the diode bridge rectifier) and from the bus capacitor to the motor (through the PWM inverter). When the motor is controlled in regeneration mode, the inverter reverses the direction of power flow from the motor to the dc capacitor. Figure 2.7 shows the power flow block diagram of the VSD configuration considered in this thesis. The currents and voltages in the ac motor are represented in synchronous coordinates. The derivation of power balance equations between ac-to-dc and dc-to-ac conversions are discussed in the following subsections.

#### 2.5.1 POWER FLOW BETWEEN AC SUPPLY AND DC BUS CAPACITOR

In a diode-bridge rectifier, when the line-to-line ac voltage  $(V_{II})$  is greater than the instantaneous capacitor voltage  $(V_{bus})$ , there will be a flow of current  $(I_i)$  from the conducting phases to the bus capacitor based on equation (2.13).

$$2L\frac{dI_l}{dt} = V_{ll} - 2RI_l - V_{bus}$$

(2.13)

where,

L – per phase line inductance

R – per phase line resistance

Under balanced supply conditions with a constant load, the individual phase currents will be a repetitive pattern of two symmetrical pulses in the positive as well as the negative half cycles. Hence, the capacitor charging current  $(I_{in})$  will be a uniform pattern of six pulses per cycle. The instantaneous capacitor voltage  $(V_{bus})$  can be calculated as:

$$C\frac{dV_{bus}}{dt} = I_{in} - I_{out}$$

(2.14)

The relationship between ac and dc quantities (i.e. voltages and currents) under balanced three-phase supply conditions is,

$$I_l = 0.816 I_{in} \tag{2.15}$$

$$V_{bus} = 1.35 \ V_{ll} \tag{2.16}$$

where,

$I_1$  - incoming phase current,

$I_{in}$  - capacitor charging current,

$V_{bus}$  - capacitor voltage,

$V_{ll}$  - line-to-line ac voltage

#### 2.5.2 POWER FLOW BETWEEN DC BUS CAPACITOR AND AC MOTOR

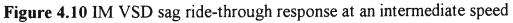

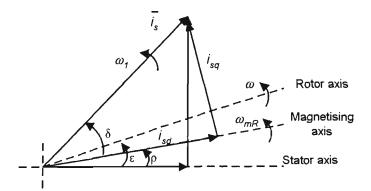

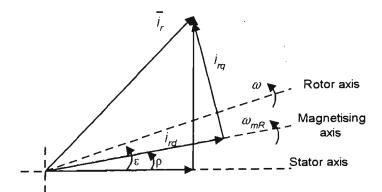

The relationships between the instantaneous power drawn from the bus capacitor and the power utilised by the ac motor is derived in this subsection. The angular relationships of current vectors in various reference frames are shown in Figure 2.8, which are explained in further detail in Appendices B and C for both IM and SRM.

Figure 2.8 Angular relationships between current vectors in steady state [26]

The stator voltage and current vectors  $(\vec{V_s}, \vec{I_s})$  can be expressed in terms of their three phase components as follows:

$$\vec{V}_s = V_{s1} + V_{s2}e^{j\frac{2\pi}{3}} + V_{s3}e^{j\frac{4\pi}{3}}$$

(2.17)

$$\vec{I}_{s} = I_{s1} + I_{s2}e^{j\frac{2\pi}{3}} + I_{s3}e^{j\frac{4\pi}{3}}$$

(2.18)

where,

$V_{s1}$ ,  $V_{s2}$ ,  $V_{s3}$  – individual phase voltages applied to the ac motor  $I_{s1}$ ,  $I_{s2}$ ,  $I_{s3}$  – individual phase currents in the ac motor

In a star connected system,  $I_{s1} + I_{s2} + I_{s3} = 0$  and hence, the instantaneous power p flowing into the ac motor can be derived as:

$$p = \frac{2}{3} \operatorname{Re}(\vec{V}_s \, \vec{I}_s^{*}) \tag{2.19}$$

Also, these stator voltage and current vectors  $(\vec{V_s} \text{ and } \vec{I_s})$  can be expressed in field coordinates. In the case of an IM,  $\rho$  is the instantaneous angle of the rotating magnetising axis with respect to the stationary frame of reference. (In the case of an SRM, this angle is  $\varepsilon$ , which is the angle of the rotor with respect to the stator axis. However the following result still holds good for both motors).

$$\bar{V}_{s} e^{-j\rho} = V_{sd} + jV_{sq}$$

(2.20)

$$\vec{I}_s \ e^{-j\rho} = i_{sd} + ji_{sq} \tag{2.21}$$

$$\vec{V}_{s} e^{-j\rho} \vec{I}_{s}^{*} e^{j\rho} = \vec{V}_{s} \vec{I}_{s}^{*} = (V_{sd} i_{sd} + V_{sq} i_{sq}) + j (V_{sq} i_{sd} - V_{sd} i_{sq})$$

(2.22)

Substituting equation (2.22) into (equation (2.19),

$$p = \frac{2}{3} \operatorname{Re}(\vec{V_s} \ \vec{I_s}^*) = \frac{2}{3} (V_{sd} \ i_{sd} + V_{sq} \ i_{sq})$$

(2.23)

From Figure 2.7, it can be seen that the input power p flowing into the motor from the capacitor (neglecting losses) is:

$$p = V_{bus} I_{out} \tag{2.24}$$

Combining equations (2.23) and (2.24), the power balance between the dc bus and ac motor is obtained as:

$$V_{bus} I_{out} = \frac{2}{3} \left( V_{sd} i_{sd} + V_{sq} i_{sq} \right)$$

(2.25)

#### 2.6 SUMMARY

In this chapter, the basis and details of the proposed control strategy were described. In order to enable sag ride-through of an ac motor VSD (with a VSI configuration), it is suggested to maintain the dc bus voltage at the nominal (rated) value by recovering the kinetic and magnetisation energy available in the motor. Operation of the basic control loops used for speed and current control of IM and SRM VSDs were discussed. In order to achieve the capacitor voltage control by recovering energy from the two sources, two additional control loops were proposed and their coordination with the existing controllers in the VSD was explained. The mathematical equations for power flow between the ac mains, dc bus capacitor and the ac motor controlled by field orientation technique were presented. As seen from the control structure of both IM and SRM, the proposed strategy is applicable to both the motor types. In the forthcoming chapters the simulation results of SRM and IM VSDs when controlled by this strategy will be analysed.

### CHAPTER 3

# PERFORMANCE OF A SYNCHRONOUS RELUCTANCE MOTOR DRIVE

#### 3.1 INTRODUCTION

In this chapter, the voltage sag ride-through performance of a synchronous reluctance motor variable speed drive (SRM VSD) under the proposed control strategy is presented. The details on the field orientation of an SRM can be found in Appendix C. The control of an SRM, as illustrated in Subsection 2.3.2, is modelled in MATLAB<sup>TM</sup>.

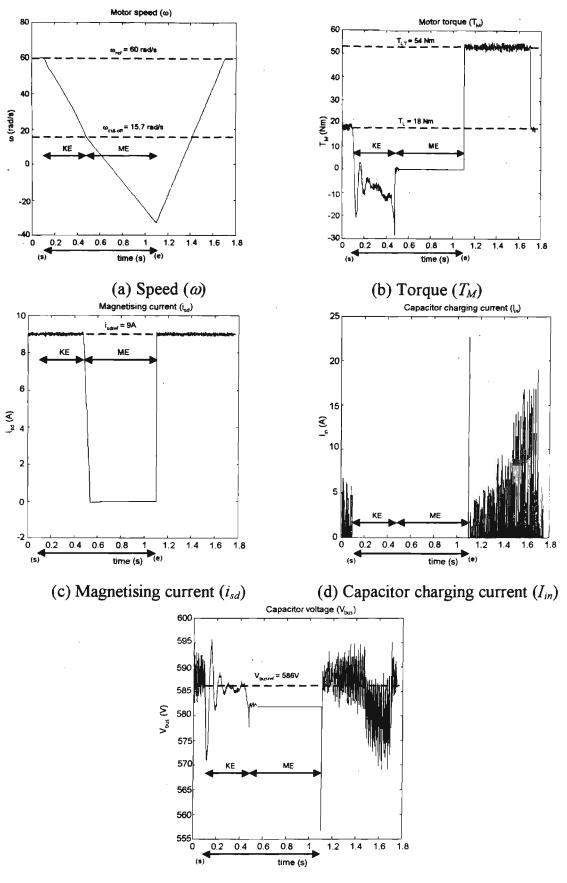

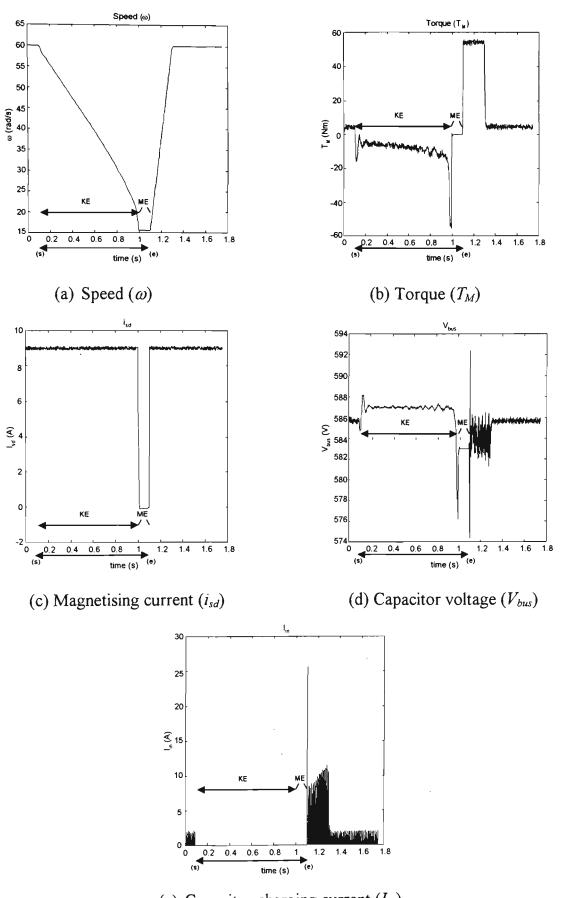

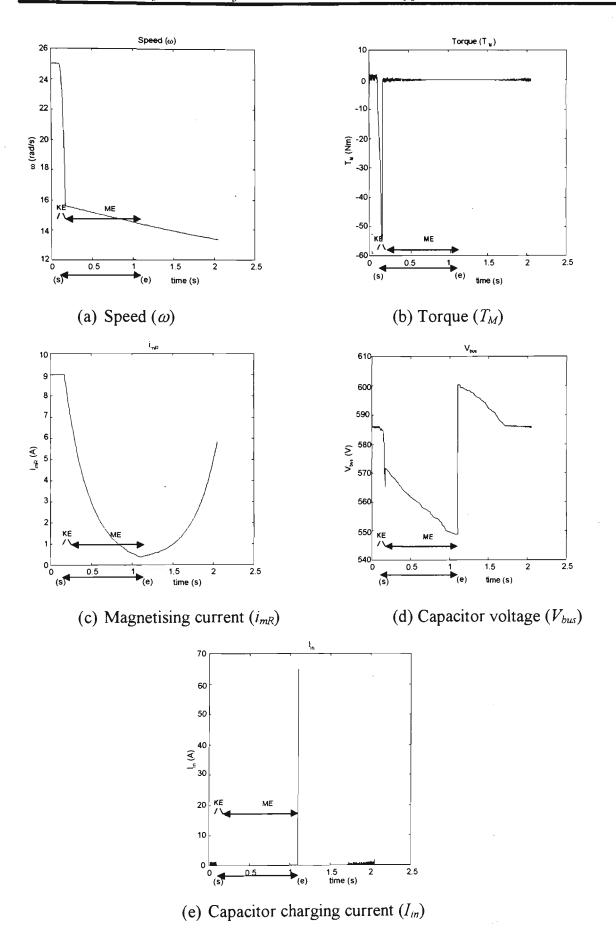

Initially, there will be a brief mention on the type of voltage sags that will be applied in this simulation. Then, the performance results of the SRM VSD during normal ac supply conditions as well as during a sag will be presented. From these results, the reasons for nuisance tripping of the VSD during a voltage sag will be discussed. Finally, the voltage sag ride-through performance of the SRM VSD utilising the proposed control strategy will be verified. It may be recalled that, as per the strategy defined in Section 2.2, the bus voltage will be maintained at the nominal value during a sag by recovering the kinetic energy available in the rotating mass when motor speed is above the cut-off limit (which is 10% of the motor base speed), or by recovering the magnetising energy available in the motor winding inductances below the cut-off speed limit. Because energy is recovered from two sources under different conditions, the simulation results will be presented in three parts, viz. (a) operation above the cut-off speed by recovering kinetic energy, (b) operation below the cut-off speed by recovering magnetising energy and (c) coordinated sag ride-through at all speeds by recovering from both sources of energy.

Since kinetic energy is proportional to the square of the motor speed, it can supply the dc bus for a longer duration and thus provide a longer sag ride-through operation if the rate of speed drop is low. The speed drop of the motor during kinetic energy recovery depends on two factors, viz. (a) amount of energy regenerated and (b) the load. The regenerated energy is utilised to charge the dc bus capacitor as well as to compensate for the resistive losses in the motor windings. The effect of reducing the bus capacitance will be studied on the voltage sag ride-through behaviour of the SRM VSD later in this chapter. As far as the effect of load is concerned, the sag ride-through duration will be maximum when the load on the motor is a minimum. In this thesis, both constant torque and fan type loads are considered. Fan type loads, in which the torque reduces with square of the motor speed  $(T_L \propto \omega^2)$ , are expected to respond to this control strategy for much longer duration as compared to constant torque loads. In this chapter, performance of the SRM VSD with a constant torque load will be discussed whereas the performance results for a fan type load will be discussed in Appendix I.

#### 3.2 SAG TYPES UNDER STUDY