Received February 17, 2020, accepted March 4, 2020, date of publication March 16, 2020, date of current version March 26, 2020. *Digital Object Identifier* 10.1109/ACCESS.2020.2980925

# Benchmarking of FinFET, Nanosheet, and Nanowire FET Architectures for Future Technology Nodes

### DANIEL NAGY<sup>1</sup>, GABRIEL ESPIÑEIRA<sup>®1</sup>, GUILLERMO INDALECIO<sup>®1</sup>, ANTONIO J. GARCÍA-LOUREIRO<sup>®1</sup>, KAROL KALNA<sup>®2</sup>, AND NATALIA SEOANE<sup>®1</sup>

<sup>1</sup>Centro Singular de Investigación en Tecnoloxías da Información, University of Santiago de Compostela, 15705 Santiago de Compostela, Spain <sup>2</sup>Nanoelectronic Devices Computational Group, Swansea University, Swansea SA1 8EN, U.K.

Corresponding author: Natalia Seoane (natalia.seoane@usc.es)

This work was supported in part by the Spanish Government under Project TIN2013-41129-P and Project TIN2016-76373-P, in part by the Xunta de Galicia and FEDER Funds under Grant GRC 2014/008, and in part by the Consellería de Cultura, Educación e Ordenación Universitaria (accreditation 2016–2019) under Grant ED431G/08. The work of Guillermo Indalecio was supported by the Programa de Axudas á Etapa Posdoutoral da Xunta de Galicia under Grant 2017/077. The work of Natalia Seoane was supported by the RyC Programme of the Spanish Ministerio de Ciencia, Innovación y Universidades under Grant RYC-2017-23312.

**ABSTRACT** Nanosheet (NS) and nanowire (NW) FET architectures scaled to a gate length ( $L_G$ ) of 16 nm and below are benchmarked against equivalent FinFETs. The device performance is predicted using a 3D finite element drift-diffusion/Monte Carlo simulation toolbox with integrated 2D Schrödinger equation based quantum corrections. The NS FET is a viable replacement for the FinFET in high performance (HP) applications when scaled down to  $L_G$  of 16 nm offering a larger on-current ( $I_{ON}$ ) and slightly better sub-threshold characteristics. Below  $L_G$  of 16 nm, the NW FET becomes the most promising architecture offering an almost ideal sub-threshold swing, the smallest off-current ( $I_{OFF}$ ), and the largest  $I_{ON}/I_{OFF}$  ratio out of the three architectures. However, the NW FET suffers from early  $I_{ON}$  saturation with the increasing gate bias that can be tackled by minimizing interface roughness and/or by optimisation of a doping profile in the device body.

**INDEX TERMS** Monte Carlo, Schrödinger quantum correction, FinFET, nanowire, nanosheet.

#### I. INTRODUCTION

Fin field effect transistor (FinFET) technology is the leading architecture for high performance (HP) applications. However, FinFETs will struggle to keep control of device electrostatics in future generations of complementary metal-oxide-semiconductor (CMOS) technology [1]. The eventual changeover to different architectures like nanosheet (NS) [2]–[5] or nanowire (NW) FETs [6], [7], and/or to different channel materials like Ge or III-Vs [8]–[10] requires thorough ground work. Therefore, physically-based 3D simulations play an essential role to benchmark the most promising candidates. Although many works already compared FinFET and NW FET architectures [2], [10]–[12], there are fewer that include a predictive physically based comparison of FinFET, NS and NW FETs [6], [13], [14]. These works

The associate editor coordinating the review of this manuscript and approving it for publication was Sun Junwei<sup>10</sup>.

use either drift-diffusion simulations [6] that cannot capture non-equilibrium carrier transport, or employ a quantum corrected Monte Carlo (MC) technique via a density gradient approach that requires calibration [7].

In this work, we will benchmark *n*-MOS transistors from the FinFET technology against the NS and NW FET solutions using VENDES, a 3D finite element (FE) quantum corrected MC and drift-diffusion (DD) toolbox with integrated 2D FE Schrödinger equation solver [15], [16]. The transistor dimensions and their shapes are precisely described by a simulation domain using FEs which assures that the accurate quantum mechanical confinement is considered in the carrier channel transport [17]. The three compared architectures of *n*-MOS transistors are assumed to have the same principal characteristics like the gate length, equivalent oxide thickness (EOT) of a high- $\kappa$  dielectric layer, and *n*-type doping in the source/drain and *p*-type doping in the channel having its optimal orientation in the  $\langle 110 \rangle$  crystallographic orientation

## IEEE Access

(on the (100) Si substrate) [18], [19]. Their particular designs follow the ITRS 2.0 prescriptions [20] and experimental transistors reported for the FinFET [21], NW FET [12], [22], and NS FET [23]. The objective is to show how these different architectures measure up against each other analysing the influence of doping, the gate length ( $L_G$ ) and the interface roughness (IR) in device performance via the main figures of merit: threshold voltage ( $V_T$ ), sub-threshold swing (SS), off-current ( $I_{OFF}$ ), on-current ( $I_{ON}$ ), and  $I_{ON}/I_{OFF}$  ratio.

#### **II. METHODOLOGY AND DESCRIPTION OF DEVICES**

VENDES is a 3D FE physically-based simulation toolbox for nanoscaled devices [17], [24], [25] that integrates a 2D Schrödinger equation (SCH) based quantum corrected 3D DD method (SCH-DD) to study the sub-threshold region, and a 2D SCH quantum corrected 3D MC (SCH-MC) to study the transistor on-region. One advantage of using SCH based quantum corrections is that they do not require calibration unlike density-gradient (DG) based corrections [25]. The SCH quantum corrections do not include the source-to-drain tunnelling [26]. However, the source-to-drain tunnelling is negligible for the gate length of the study, 12 nm [7], [27]. The SCH-DD technique is beneficial at gate biases below the threshold voltage  $(V_T)$  because the current obtained from the SCH-MC is too noisy there. However, at larger gate biases, the SCH-MC is needed because non-equilibrium transport plays a major role in carrier transport. The SCH-MC simulations account for the following Si related electron scattering mechanisms: electron interaction with acoustic and non-polar optical phonons (intra- and inter-valley) [28], electron interaction with ionised impurity scattering using the third-body exclusion [29] with static screening and Fermi-Dirac statistics [30], and electron scattering with the IR using Ando's model [31] in which the effective electric field is obtained in a real space device domain [32]. The IR scattering, which is sometimes inaccurately called a surface roughness scattering, refers to the carrier scattering on a potential induced by the interface between semiconductor and dielectric material. The IR between the semiconductor and the dielectric is typically characterised by a root mean square height (RMS<sub>height</sub>) of the roughness and the correlation length  $(\lambda_c)$  at which a roughness pattern re-occurs. The static screening model in the ionised impurity scattering uses Fermi energy and electron temperature self-consistently calculated from the electron density and the electron kinetic energy in the real space domain of a transistor [30], [33].

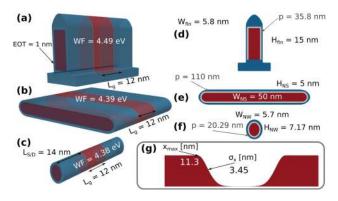

Fig. 1 shows the three device architectures (FinFET, NS and NW FETs) and their physical dimensions. The Fin-FET is designed using silicon-on-insulator (SOI) technology to minimise leakage current. The FinFET design aims to have a narrow width and a large height of its silicon body in order to achieve a large density of parallel transistors on the area of a chip. The gate-all-around (GAA) NW FET architecture is designed to have a tight gate control of electron transport through its silicon body to minimise the leakage current at very short gate lengths while still delivering the required drive

**FIGURE 1.** Schematics of the 12 nm gate length (a, d) FinFET, (b, e) NS and (c, f) NW FETs with device dimensions: physical gate length ( $L_G$ ), physical source/drain length ( $L_{S/D}$ ), channel width/height ( $W_{(dev)}$ ,  $H_{(dev)}$ ;  $\langle dev \rangle = fin$ , NW, NS), effective oxide thickness (EOT), work function (WF), effective perimeter (p), and (g) Gaussian doping profile: lateral straggle ( $\sigma_x$ ) and the end of maximum doping ( $x_{max}$ ).

current using stacked NWs. The NS FET architecture aims to reuse, with minimal changes that are explained in detail in [23], the FinFET fabrication process by turning a high thin fin horizontally into a nanoscale sheet, because lateral epitaxial material growth can deliver smoother interfaces at the top and bottom of NS body.

The SOI FinFET and the NW FET in this benchmarking study are based on larger experimental devices with gate lengths of 25 nm [21] and 22 nm [22], respectively, which were scaled following the ITRS guidelines [20] as detailed in [17], [34]. The NS FET is based on an experimental device with a gate length of 12 nm and 44/48 nm contacted poly pitch (CPP) ground rules [23]. The transistor doping profile, essential to simulate the nanoscale transistors, is very challenging to acquire from experimental work. Therefore, we reversed engineered the *n*-type and *p*-type doping profiles in the 12 nm gate length NS FET. We assumed a uniform *p*-type doping  $(1.0 \times 10^{15} \text{ cm}^{-3})$  in the device channel and a *n*-type Gaussian doping profile in the source/drain (S/D) regions (see Fig. 1 (g)). Three parameters were adjusted: (i) the maximum source/drain doping  $(N_{S/D})$ , (ii) the position  $(X_{\text{max}})$  where the doping starts to decay from  $N_{\text{S/D}}$ , and (iii) the Gaussian lateral straggle ( $\sigma_{max}$ ). This process is repeated until a good agreement is achieved in I<sub>D</sub>-V<sub>G</sub> characteristics between the experimental and the simulated data in the sub-threshold region obtained from the 3D SCH-DD. Further details on the reverse engineering process of doping profiles can be found in [34]. The best match was found for  $N_{\rm S/D}$  of 5.0  $\times$  10<sup>19</sup> cm<sup>-3</sup>,  $X_{\rm max}$  of 11.3 nm and  $\sigma_{\rm max}$  of 3.45 nm. The comparison of our simulated ID-VG characteristics against the experimental data of the 12 nm gate length NS FET showed a very good agreement at a low drain bias of 0.05 V (see the results in [35]).

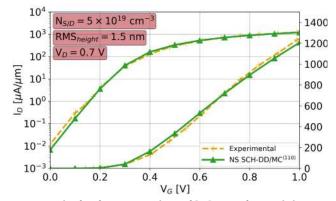

The SCH-MC simulations are then employed to verify the experimentally observed  $I_D$ -V<sub>G</sub> characteristics in the on-region. Fig. 2 compares  $I_D$ -V<sub>G</sub> characteristics of the simulated and the experimentally measured 12 nm gate length NS FET at a high drain bias of 0.7 V. These SCH-MC

**FIGURE 2.** Simulated versus experimental [23]  $I_D$ - $V_G$  characteristics, on both logarithmic (left) and linear (right) scales, for the 12 nm gate length NS FET at  $V_D = 0.7$  V with a channel orientation of (110) assuming  $RMS_{height} = 1.5$  nm in the IR scattering ( $\lambda_c = 1.7$  nm). The  $N_{S/D}$  is  $5 \times 10^{19}$  cm<sup>-3</sup>.

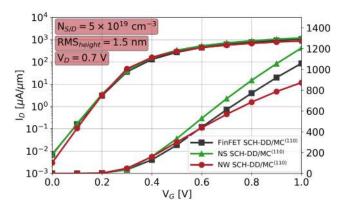

**FIGURE 3.** Simulated  $I_D$ - $V_G$  characteristics, on both logarithmic (left) and linear (right) scales, for the 12 nm gate length FinFET, NS and NW FETs at  $V_D = 0.7$  V with a channel orientation of (110) assuming  $RMS_{height} = 1.5$  nm in the IR scattering ( $\lambda_c = 1.7$  nm). The  $N_{S/D}$  is  $5 \times 10^{19}$  cm<sup>-3</sup>.

simulations assume that *RMS*<sub>height</sub> is 1.5 nm and the  $\lambda_c$  is 1.7 nm in electron scattering with the IR induced potential. These parameters which specify the quality of the interface between the silicon channel and dielectric layer, the  $\lambda_c$  and mean square root of the height *RMS*<sub>height</sub>, are typically not available from experimental work but the IR scattering has a great influence on the drain current in the on-region. Therefore, we have increased *RMS*<sub>height</sub> in 0.5 nm steps as shown by I<sub>D</sub>-V<sub>G</sub> characteristics in Figs. 3, 4 and 5 until a good agreement is achieved by comparing the on-current against experimental data at V<sub>D</sub> = 0.7 V (Fig. 2). The  $\lambda_c$  is assumed to be the same as for a nanoscale FinFET [17].

The benchmarking study considers that all three multi-gate architectures (FinFET, NS and NW FETs) are on the (100) Si substrate with the  $\langle 110 \rangle$  channel orientation [19]. All the transistors have the same *n*-type and *p*-type doping profiles and their work functions were adjusted to provide the same threshold voltages when  $L_G$  is 12 nm. Finally, the simulated I<sub>D</sub>-V<sub>G</sub> characteristics at low and high drain biases from the MC simulations are in a very good agreement with the experimental characteristics, without further need to include access resistance in any additional

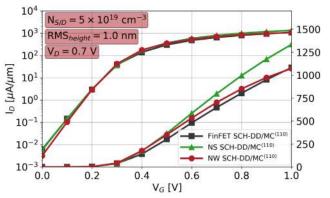

**FIGURE 4.** Simulated I<sub>D</sub>-V<sub>G</sub> characteristics at V<sub>D</sub> = 0.7 V, on both logarithmic and linear scales, for the 12 nm gate length FinFET, NS and NW FETs with a channel orientation of (110) assuming *RMS*<sub>height</sub> = 1.0 nm in the IR scattering ( $\lambda_c = 1.7$  nm). The N<sub>S/D</sub> is 5 × 10<sup>19</sup> cm<sup>-3</sup>.

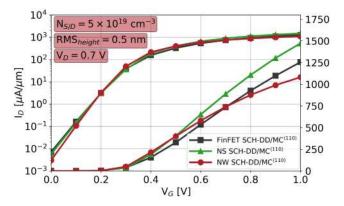

**FIGURE 5.** Simulated I<sub>D</sub>-V<sub>G</sub> characteristics at V<sub>D</sub> = 0.7 V, on both logarithmic and linear scales, for the 12 nm gate length FinFET, NS and NW FETs with a channel orientation of (110) assuming *RMS*<sub>height</sub> = 0.5 nm in the IR scattering ( $\lambda_c = 1.7$  nm). The N<sub>S/D</sub> is 5 × 10<sup>19</sup> cm<sup>-3</sup>.

post-processing [17], [34]. The characteristics are directly obtained by time consuming SCH-MC simulations of electron transport in the transistor domain including electrons in the heavily doped source/drain that provides a correct electron distribution for their injection into device channel [17], [33], [36]. These accurate simulations of electron transport in the heavily *n*-type doped source/drain of multi-gate nanoscale transistors with governing electron-ionised impurity interaction use the static screening with self-consistent calculations of Fermi energy and electron temperature [30] in the real-space device domain [17], [34].

#### **III. BENCHMARKS**

A comparison of the 12 nm gate length FinFET, NS and NW FETs  $I_{\rm D}$ - $V_{\rm G}$  characteristics is shown in Figs. 3, 4 and 5 at a drive bias ( $V_{\rm DD}$ ) of 0.7 V for the  $\langle 110 \rangle$  channel orientation assuming an *RMS*<sub>height</sub> of 1.5, 1.0 and 0.5 nm, respectively, and a  $\lambda_c$  of 1.7 nm. The figures of merit (FoM), summarised in Table 1, are extracted using FoMPy module [37], [38]. The  $V_{\rm T}$  values are obtained using the constant current method set to  $I_{\rm D} = 2.0 \ \mu A/\mu m$ . The off-current ( $I_{\rm OFF}$ ) is taken at  $V_{\rm G} = 0.0$  V, and the drive current ( $I_{\rm ON}$ ) at  $V_{\rm G} = V_{\rm DD}$ . Comparing the three architectures and assuming that the

|                                                                    | $N_{\rm S/D} = 5.0 \times 10^{19} \ {\rm cm}^{-3}$ |       |       | $N_{\rm S/D} = 1.0 \times 10^{20} \ {\rm cm}^{-3}$ |       |       | $N_{\rm S/D} = 1.5 \times 10^{20} \ {\rm cm}^{-3}$ |       |       |

|--------------------------------------------------------------------|----------------------------------------------------|-------|-------|----------------------------------------------------|-------|-------|----------------------------------------------------|-------|-------|

| FoM                                                                | FinFET                                             | NS    | NW    | FinFET                                             | NS    | NW    | FinFET                                             | NS    | NW    |

| V <sub>T</sub> [V]                                                 | 0.185                                              | 0.185 | 0.185 | 0.158                                              | 0.164 | 0.176 | 0.140                                              | 0.149 | 0.169 |

| SS [mV/dec]                                                        | 74                                                 | 71    | 65    | 77                                                 | 74    | 66    | 80                                                 | 76    | 67    |

| $I_{OFF}$ [nA/ $\mu$ m]                                            | 7.0                                                | 5.7   | 3.0   | 19.0                                               | 13.3  | 4.6   | 36.1                                               | 23.5  | 6.2   |

| $\mathrm{I_{ON}^{\langle 110  angle}}$ [ $\mu$ A/ $\mu$ m]         | 612                                                | 699   | 568   | 724                                                | 832   | 732   | 777                                                | 893   | 819   |

| $\frac{I_{\rm ON}}{I_{\rm OFF}} (\times 10^5) \langle 110 \rangle$ | 0.87                                               | 1.2   | 1.9   | 0.38                                               | 0.63  | 1.6   | 0.21                                               | 0.38  | 1.3   |

**TABLE 1.** Threshold voltage ( $V_T$ ), sub-threshold slope (SS), off-current ( $I_{OFF}$ ), on-current ( $I_{ON}$ ), and ON/OFF ratio ( $I_{ON}/I_{OFF}$ ) for FinFET, NS and NW FETs with the same 12 nm gate length assuming IR scattering with a  $RMS_{height}$  of 1.5 nm and  $\lambda_c$  of 1.7 nm.

maximum *n*-type S/D doping is  $N_{S/D} = 5 \times 10^{19} \text{ cm}^{-3}$ , the NW FET has the lowest SS and IOFF which indicates excellent control by the gate. In the on-region, a saturation of the drive current in the NW FET starts at  $V_{\rm G}$  of 0.6 V, leading to the lowest I<sub>ON</sub> for the three compared devices. Despite this, the NW FET still delivers the highest I<sub>ON</sub>/I<sub>OFF</sub> ratio. These NW FET characteristics, together with the possibility of stacking them vertically [3], [6], [7], suggest that the NW architecture makes an excellent candidate for low power applications. The NS FET has an ION/IOFF ratio 37% smaller than the ratio of the NW FET and delivers a slightly better performance in the sub-threshold than that of the FinFET. The NS architecture also has the highest  $I_{ON}$  indicating that the NS FET is a viable replacement for the FinFET in HP applications. The FinFET has an  $I_{ON}/I_{OFF}$  ratio 27% and 54% smaller than those of the NS and NW FETs, respectively. The FinFET has the largest SS and *I*<sub>OFF</sub> due to a weaker control by the gate. However, previous works have shown that the FinFET architecture is more resilient to intrinsic variability than the NW FET one [36].

#### A. SOURCE/DRAIN DOPING

The drive current can be incremented by increasing the *n*-type S/D doping of  $N_{\rm S/D} = 5 \times 10^{19} \text{ cm}^{-3}$  to  $1 \times 10^{20} \text{ cm}^{-3}$ and  $1.5 \times 10^{20}$  cm<sup>-3</sup> but with detrimental impact on the sub-threshold region related FoM (see Table 1). Increased S/D doping results in a lower  $V_{\rm T}$  value, for all three devices. On the other hand the SS, along with I<sub>OFF</sub>, increases for all the architectures. The NW FET is the most resistant against sub-threshold deterioration as the S/D doping is increased. The  $V_{\rm T}$  decreases by 16 (-8.6%), 26 (-19.5%) and 35 (-24%) mV for the NW FET, NS FET and FinFET, respectively, as the  $N_{\rm S/D}$  is increased from 5  $\times$  10<sup>19</sup> cm<sup>-3</sup> to  $1.5 \times 10^{20}$  cm<sup>-3</sup>. The same change in N<sub>S/D</sub> results in an increase of SS by 3%, 7% and 8% for the NW FET, NS FET and FinFET, respectively. Finally, the  $I_{OFF}$  is increased by 2.1, 4.1 and 5.2 times for the NW FET, NS FET and FinFET, respectively. In case of the on-region, the ION is increased by 44%, 28% and 27% for the NW FET, NS FET and FinFET, respectively. Moreover, the  $I_{ON}$  saturation in the NW FET occurs at larger applied biases due to a reduction of series

resistance in the S/D region, opening a possibility of *n*-type S/D doping engineering of NWs to achieve a better  $I_{\rm ON}$  with only a slight deterioration in the sub-threshold characteristics. The overall performance enhancement is compared through the  $I_{\rm ON}/I_{\rm OFF}$  ratio and we found that it decreases by -32%, -68% and -76% for the NW FET, NS FET and FinFET, respectively, as we increased the  $N_{\rm S/D}$  from  $5 \times 10^{19}$  cm<sup>-3</sup> to  $1.5 \times 10^{20}$  cm<sup>-3</sup>.

With an increase in the *n*-type S/D doping, the NW FETs still provide the largest  $I_{ON}/I_{OFF}$  ratio among the three compared architectures, although the NS FETs still deliver the largest  $I_{ON}$ . An increase in  $N_{S/D}$  affects the performance of the FinFET the most, leading to the worst sub-threshold characteristics and the lowest  $I_{ON}$ .

#### **B. INTERFACE ROUGHNESS**

Further improvement of device performance can be achieved through fabrication processes that reduce the IR [39] by either making the  $\lambda_c$  longer or minimising the *RMS*<sub>height</sub>. One advantage of reducing the RMS<sub>height</sub> is the increase in I<sub>ON</sub> without deterioration in the sub-threshold characteristics. Therefore, we study the effect of decreasing the RMS<sub>height</sub> from 1.5 nm (see Fig. 3) to 1.0 nm (see Fig. 4) and to 0.5 nm (see Fig. 5) for a maximum *n*-type S/D doping of  $N_{S/D}$  =  $5 \times 10^{19}$  cm<sup>-3</sup>. The NW FET shows the largest increase in I<sub>ON</sub>, 15.8% (30.1%), for the *RMS*<sub>height</sub> of 1.0 nm (0.5 nm). The NS FET increases its  $I_{ON}$  by 14.2% (27.3%) for the RMS<sub>height</sub> of 1.0 nm (0.5 nm). The FinFET shows the smallest increase in I<sub>ON</sub> of the three devices, 10.1% and 19.9%, for the 1.0 and 0.5 nm RMSheight, respectively. The NW FET cross-section (perpendicular to the transport direction) has a larger perimeter-conduction area ratio in the semiconductor than that of the other two architectures. This, together with the fact that this architecture is more affected by volume inversion [40], explains why the NW FET is more sensitive to IR scattering.

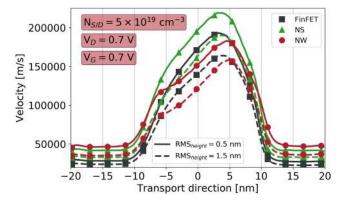

The average electron velocity along the channel from the source to the drain at  $V_G = 0.7$  V and  $V_D = 0.7$  V for the three studied transistor architectures, looking into two possible *RMS*<sub>height</sub> of 1.5 nm and 0.5 nm, is shown in Fig. 6. The largest average electron velocity is observed in the NS

**FIGURE 6.** Average electron velocity in the transport direction at  $V_G = 0.7 V$  and  $V_D = 0.7 V$  for the 12 nm gate length FinFET, NS and NW FETs with *RMS*<sub>height</sub> = 0.5 and 1.5 nm and a fixed  $\lambda_c$  of 1.7 nm.

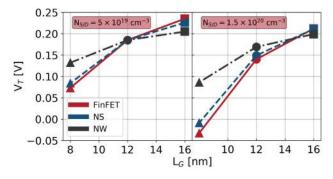

**FIGURE 7.** Threshold voltage ( $V_T$ ) vs. gate length ( $L_G$ ) for the Fin, NS and NW FETs at fixed gate metal workfunctions. The gate metal workfunctions of the three transistors are adjusted to provide the same  $V_T$  at the 12 nm gate length with  $N_{S/D} = 5 \times 10^{19}$  cm<sup>-3</sup>. The results are for  $N_{S/D} = 5 \times 10^{19}$  cm<sup>-3</sup> (left) and  $N_{S/D} = 1.5 \times 10^{20}$  cm<sup>-3</sup> (right).

FET, followed by the FinFET and the NW FET. The reduction in the  $RMS_{height}$  from 1.5 nm to 0.5 nm can result in an increase of the maximum electron velocity by about 12% in the 12 nm gate length NS FET and FinFET and by 10% in the equivalent NW FET.

#### C. GATE LENGTH

Finally, we study the effect of the  $L_{G}$  in the three device architectures. Fig. 7 shows threshold voltage vs. gate length for the three studied multi-gate architectures at two different maximum S/D dopings assuming fixed gate metal workfunctions. All three transistors have identical  $V_{\rm T}$  at the 12 nm gate length for  $N_{\rm S/D} = 5 \times 10^{19} {\rm cm}^{-3}$  as seen in Fig. 7 (left). The threshold voltage of the scaled FinFETs and NS FETs are very close because the two architectures have very similar quantum-mechanical confinement, providing them with comparable quantum gate capacitance. The NW FET has the strongest quantum-mechanical confinement in the body which makes this architecture more resilient to the gate length scaling. The negative  $V_{\rm T}$  observed for the 8 nm gate length Fin and NS FETs are a result of the fixed metal gate workfunctions adjusted to provide the same  $V_{\rm T}$  for the 12 nm gate length transistors (at a  $N_{S/D} = 5 \times 10^{19} \text{ cm}^{-3}$ ) and can be mitigated by metal gate workfunction engineering. Furthermore, as  $L_G$  is scaled down, the SS increases

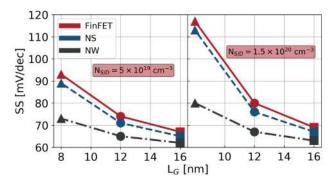

**FIGURE 8.** Sub-threshold swing (SS) vs. gate length ( $L_G$ ) for the Fin, NS and NW FETs. The results are for  $N_{S/D} = 5 \times 10^{19} \text{ cm}^{-3}$  (left) and  $N_{S/D} = 1.5 \times 10^{20} \text{ cm}^{-3}$  (right).

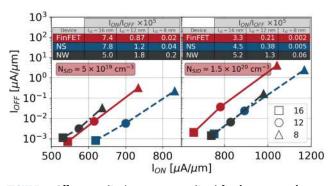

**FIGURE 9.** Off-current  $(I_{ON})$  vs. on-current  $(I_{OFF})$  for the 16, 12 and 8 nm gate length Fin, NS and NW FETs for  $N_{S/D} = 5 \times 10^{19}$  cm<sup>-3</sup> (left) and  $N_{S/D} = 1.5 \times 10^{20}$  cm<sup>-3</sup> (right). The  $I_{ON}/I_{OFF}$  ratios are also shown.

more dramatically in the FinFETs and NS FETs than in the NW FETs due to a weaker gate control over electron transport along the channel (see Fig. 8). The SS itself and its relative increase following the scaling down is more pronounced as the maximum *n*-type S/D doping is increased to  $1.5 \times 10^{20}$  cm<sup>-3</sup>. Fig. 9 shows the  $I_{\text{OFF}}$  vs.  $I_{\text{ON}}$  for the two extreme dopings. For the three devices, both the ION and  $I_{\text{OFF}}$  increase following a linear trend when  $L_{\text{G}}$  is reduced. At the lower S/D doping of  $5.0 \times 10^{19}$  cm<sup>-3</sup>, the 16 nm gate length NS FET has a 36% better  $I_{ON}/I_{OFF}$  ratio than the same gate length NW FET and the  $I_{ON}/I_{OFF}$  ratio of the 16 nm gate length FinFET is slightly lower (-5%) than that of the equivalent gate length NS FET. However, the NW FET has the largest  $I_{ON}/I_{OFF}$  ratio as the  $L_{G}$  is scaled below 16 nm (see Fig. 9). As the S/D doping is increased, the NW FET has also the highest  $I_{ON}/I_{OFF}$  ratio for all the investigated  $L_{Gs}$ .

#### **IV. CONCLUSION**

We have benchmarked the FinFET architecture against two possible alternatives, NS and NW FETs, to provide guidance towards the development of future multi-gate silicon technology nodes. The NS FET can be an excellent alternative to the FinFET for various digital applications because it offers a higher  $I_{ON}$  and slightly better sub-threshold region characteristics while reusing a similar fabrication process. However, sub-threshold characteristics of the NS FET and the FinFET deteriorate more than those of the NW FET for  $L_G$  scaled below 16 nm, so a change of transistor architecture to the NW will be essential. The NW FET offers reduced  $I_{OFF}$ , a nearly ideal SS, and a much better  $I_{ON}/I_{OFF}$  ratio than those of the NS FET and the FinFET at L<sub>G</sub> of 12 nm and 8 nm. However, the NW FET provides a much lower  $I_{ON}$  with respect to the on-current in the NS FET but the  $I_{ON}$  can be substantially increased by a reduction in the IR scattering (by decreasing *RMS*<sub>height</sub> or by increasing the  $\lambda_c$  of the IR), and/or by an increase in the *n*-type S/D doping. Finally, both the NS and NW FETs are stackable thus offering the same or even larger density of transistors on the same die area when compared to the side-by-side placement of FinFETs.

#### ACKNOWLEDGMENT

The authors would like to thank the Centro de Supercomputación de Galicia (CESGA) for the computer resources provided.

#### REFERENCES

- [1] X. He, J. Fronheiser, P. Zhao, Z. Hu, S. Uppal, X. Wu, Y. Hu, R. Sporer, L. Qin, R. Krishnan, E. M. Bazizi, R. Carter, K. Tabakman, A. K. Jha, H. Yu, O. Hu, D. Choi, J. G. Lee, S. B. Samavedam, and D. K. Sohn, "Impact of aggressive fin width scaling on FinFET device characteristics," in *IEDM Tech. Dig.*, Dec. 2017, p. 20.

- [2] D. Yakimets, M. G. Bardon, D. Jang, P. Schuddinck, Y. Sherazi, P. Weckx, K. Miyaguchi, B. Parvais, P. Raghavan, A. Spessot, D. Verkest, and A. Mocuta, "Power aware FinFET and lateral nanosheet FET targeting for 3nm CMOS technology," in *IEDM Tech. Dig.*, Dec. 2017, pp. 501–504.

- [3] L. Cai, W. Chen, G. Du, X. Zhang, and X. Liu, "Layout design correlated with self-heating effect in stacked nanosheet transistors," *IEEE Trans. Electron Devices*, vol. 65, no. 6, pp. 2647–2653, Jun. 2018.

- [4] J.-S. Yoon, J. Jeong, S. Lee, and R.-H. Baek, "Multi-V<sub>th</sub> strategies of 7-nm node nanosheet FETs with limited nanosheet spacing," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 861–865, 2018.

- [5] J. Yao, J. Li, K. Luo, J. Yu, Q. Zhang, Z. Hou, J. Gu, W. Yang, Z. Wu, H. Yin, and W. Wang, "Physical insights on quantum confinement and carrier mobility in Si, Si<sub>0.45</sub>Ge<sub>0.55</sub>, Ge gate-all-around NSFET for 5 nm technology node," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 841–848, 2018.

- [6] P. Feng, S.-C. Song, G. Nallapati, J. Zhu, J. Bao, V. Moroz, M. Choi, X.-W. Lin, Q. Lu, B. Colombeau, N. Breil, M. Chudzik, and C. Chidambaram, "Comparative analysis of semiconductor device architectures for 5-nm node and beyond," *IEEE Electron Device Lett.*, vol. 38, no. 12, pp. 1657–1660, Dec. 2017.

- [7] F. M. Bufler, R. Ritzenthaler, H. Mertens, G. Eneman, A. Mocuta, and N. Horiguchi, "Performance comparison of *n*-Type Si nanowires, nanosheets, and FinFETs by MC device simulation," *IEEE Electron Device Lett.*, vol. 39, no. 11, pp. 1628–1631, Nov. 2018.

- [8] K. Kalna, L. Yang, and A. Asenov, "Monte Carlo simulations of sub-100 nm InGaAs MOSFETs for digital applications," in *Proc. 35th Eur. Solid-State Device Res. Conf.*, Sep. 2005, pp. 169–172.

- [9] L. Czornomaz, N. Daix, K. Cheng, D. Caimi, C. Rossel, K. Lister, M. Sousa, and J. Fompeyrine, "Co-integration of InGaAs n- and SiGe p-MOSFETs into digital CMOS circuits using hybrid dual-channel ETXOI substrates," in *IEDM Tech. Dig.*, Dec. 2013, pp. 52–55.

- [10] M. Rau, E. Caruso, D. Lizzit, P. Palestri, D. Esseni, A. Schenk, L. Selmi, and M. Luisier, "Performance projection of III-V ultra-thin-body, FinFET, and nanowire MOSFETs for two next-generation technology nodes," in *IEDM Tech. Dig.*, Dec. 2016, pp. 758–761.

- [11] B. C. Paul, S. Fujita, M. Okajima, T. H. Lee, H.-S.-P. Wong, and Y. Nishi, "Impact of a process variation on nanowire and nanotube device performance," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2369–2376, Sep. 2007.

- [12] C. Dupre *et al.*, "15nm-diameter 3D stacked nanowires with independent gates operation: ΦFFET," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [13] S.-D. Kim, M. Guillorn, I. Lauer, P. Oldiges, T. Hook, and M.-H. Na, "Performance trade-offs in FinFET and gate-all-around device architectures for 7nm-node and beyond," in *Proc. IEEE SOI-3D-Subthreshold Microelectron. Technol. Unified Conf.*, Oct. 2015, pp. 1–3.

- [14] D. Jang, D. Yakimets, G. Eneman, P. Schuddinck, M. G. Bardon, P. Raghavan, A. Spessot, D. Verkest, and A. Mocuta, "Device exploration of NanoSheet transistors for Sub-7-nm technology node," *IEEE Trans. Electron Devices*, vol. 64, no. 6, pp. 2707–2713, Jun. 2017.

- [15] N. Seoane, D. Nagy, G. Indalecio, G. Espiñeira, K. Kalna, and A. García-Loureiro, "A multi-method simulation toolbox to study performance and variability of nanowire FETs," *Materials*, vol. 12, no. 15, pp. 2391–2406, 2019.

- [16] J. Lindberg, M. Aldegunde, D. Nagy, W. G. Dettmer, K. Kalna, A. J. García-Loureiro, and D. Perić, "Quantum corrections based on the 2-D Schrödinger equation for 3-D finite element Monte Carlo simulations of nanoscaled FinFETs," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 423–429, Feb. 2014.

- [17] M. Aldegunde, A. J. Garcia-Loureiro, and K. Kalna, "3D finite element Monte Carlo simulations of multigate nanoscale transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 5, pp. 1561–1567, May 2013.

- [18] L. Chang, M. Ieong, and M. Yang, "CMOS circuit performance enhancement by surface orientation optimization," *IEEE Trans. Electron Devices*, vol. 51, no. 10, pp. 1621–1627, Oct. 2004.

- [19] M. Yang, V. W. C. Chan, K. K. Chan, L. Shi, D. M. Fried, J. H. Stathis, A. I. Chou, E. Gusev, J. A. Ott, L. E. Burns, M. V. Fischetti, and M. Ieong, "Hybrid-orientation technology (HOT): Opportunities and challenges," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 965–978, May 2006.

- [20] ITRS 2.0. (2016). International Technology Roadmap for Semiconductors. [Online]. Available: http://www.itrs2.net/

- [21] V. S. Basker *et al.*, "A 0.063 μm<sup>2</sup> FinFET SRAM cell demonstration with conventional lithography using a novel integration scheme with aggressively scaled fin and gate pitch," in *Proc. Symp. VLSI Technol.*, Jun. 2010, pp. 19–20.

- [22] S. Bangsaruntip, K. Balakrishnan, S.-L. Cheng, J. Chang, M. Brink, I. Lauer, R. L. Bruce, S. U. Engelmann, A. Pyzyna, G. M. Cohen, L. M. Gignac, C. M. Breslin, J. S. Newbury, D. P. Klaus, A. Majumdar, J. W. Sleight, and M. A. Guillorn, "Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond," in *IEDM Tech. Dig.*, Dec. 2013, pp. 526–529.

- [23] N. Loubet *et al.*, "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET," in *Proc. Symp. VLSI Technol.*, Jun. 2017, pp. T230–T231.

- [24] A. J. Garcia-Loureiro, N. Seoane, M. Aldegunde, R. Valin, A. Asenov, A. Martinez, and K. Kalna, "Implementation of the density gradient quantum corrections for 3-D simulations of multigate nanoscaled transistors," *IEEE Trans. Comput.-Aided Design Integr.*, vol. 30, no. 6, pp. 841–851, Jun. 2011.

- [25] M. A. Elmessary, D. Nagy, M. Aldegunde, J. Lindberg, W. G. Dettmer, D. Peric, A. J. Garcia-Loureiro, and K. Kalna, "Anisotropic quantum corrections for 3-D finite-element Monte Carlo simulations of nanoscale multigate transistors," *IEEE Trans. Electron Devices*, vol. 63, no. 3, pp. 933–939, Mar. 2016.

- [26] B. Winstead and U. Ravaioli, "A quantum correction based on schrodinger equation applied to Monte Carlo device simulation," *IEEE Trans. Electron Devices*, vol. 50, no. 2, pp. 440–446, Feb. 2003.

- [27] D. Querlioz, J. Saint-Martin, K. Huet, A. Bournel, V. Aubry-Fortuna, C. Chassat, S. Galdin-Retailleau, and P. Dollfus, "On the ability of the particle Monte Carlo technique to include quantum effects in nano-MOSFET simulation," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2232–2242, Sep. 2007.

- [28] K. Tomizawa, Numerical Simulation of Submicron Semiconductor Devices (Artech House Materials Science Library). Norwood, MA, USA: Artech House, 1993.

- [29] B. K. Ridley, "Reconciliation of the Conwell-Weisskopf and brooksherring formulae for charged-impurity scattering in semiconductors: Third-body interference," J. Phys. C, Solid State Phys., vol. 10, no. 10, pp. 1589–1593, May 1977.

- [30] A. Islam and K. Kalna, "Monte Carlo simulations of mobility in doped GaAs using self-consistent Fermi–Dirac statistics," *Semicond. Sci. Tech*nol., vol. 26, no. 5, 2012, Art. no. 039501.

- [31] D. Ferry, *Semiconductor Transport*. New York, NY, USA: Taylor & Francis, 2000.

- [32] K. Kalna, M. Boriçi, L. Yang, and A. Asenov, "Monte Carlo simulations of III–V MOSFETs," *Semicond. Sci. Technol.*, vol. 19, no. 4, pp. S202–S205, Mar. 2004.

- [33] D. Nagy, M. A. Elmessary, M. Aldegunde, R. Valin, A. Martinez, J. Lindberg, W. G. Dettmer, D. Peric, A. J. Garcia-Loureiro, and K. Kalna, "3-D finite element Monte Carlo simulations of scaled Si SOI FinFET with different cross sections," *IEEE Trans. Nanotechnol.*, vol. 14, no. 1, pp. 93–100, Jan. 2015.

- [34] M. A. Elmessary, D. Nagy, M. Aldegunde, N. Seoane, G. Indalecio, J. Lindberg, W. Dettmer, D. Perić, A. J. García-Loureiro, and K. Kalna, "Scaling/LER study of Si GAA nanowire FET using 3D finite element Monte Carlo simulations," *Solid-State Electron.*, vol. 128, pp. 17–24, Feb. 2017.

- [35] K. Kalna, D. Nagy, A. J. García-Loureiro, and N. Seoane, "3D Schrödinger equation quantum corrected Monte Carlo and drift diffusion simulations of stacked nanosheet gate-all-around transistor," in *Proc. IWCN Book Abstract.* Tuwien, Wien: Institute for Microelectronics, May 2019, pp. 33–35.

- [36] D. Nagy, G. Indalecio, A. J. Garcia-Loureiro, M. A. Elmessary, K. Kalna, and N. Seoane, "FinFET versus Gate-All-Around nanowire FET: Performance, scaling, and variability," *IEEE J. Electron Devices Soc.*, vol. 6, pp. 332–340, 2018.

- [37] FoMPy. Accessed: Mar. 16, 2020. [Online]. Available: https://github.com/ gabrielesp/FoMpy

- [38] G. Espiñera, D. Nagy, A. García-Loureiro, N. Seoane, and G. Indalecio, "Impact of threshold voltage extraction methods on semiconductor device variability," *Solid-State Electron.*, vol. 159, pp. 165–170, Sep. 2019.

- [39] S. Jin, M. V. Fischetti, and T.-W. Tang, "Modeling of electron mobility in gated silicon nanowires at room temperature: Surface roughness scattering, dielectric screening, and band nonparabolicity," *J. Appl. Phys.*, vol. 102, no. 8, Oct. 2007, Art. no. 083715.

- [40] Y. Lee, K. Kakushima, K. Natori, and H. Iwai, "Corner effects on phonon-limited mobility in rectangular silicon nanowire metal-oxidesemiconductor field-effect transistors based on spatially resolved mobility analysis," J. Appl. Phys., vol. 109, no. 11, Jun. 2011, Art. no. 113712.

**DANIEL NAGY** received the M.Res. degree in nanoscience and nanotechnology and the Ph.D. degree in electronic and electrical engineering from Swansea University, Swansea, U.K., in 2013 and 2016, respectively.

He currently holds a postdoctoral position at the Centro Singular de Investigación en Tecnoloxías da Información (CITIUS), University of Santiago de Compostela, Santiago de Compostela, Spain.

**GUILLERMO INDALECIO** received the B.S. degree in physics and the Ph.D. degree in semiconductor device simulation from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 2010 and 2016, respectively.

He was a Visiting Researcher with Swansea University, Swansea, U.K., in 2015. He is currently a Postdoctoral Researcher with the University of Santiago de Compostela, Spain. His research interests include electronic devices simulation with

focus on computational techniques and novel techniques to understand variability sources.

**ANTONIO J. GARCÍA-LOUREIRO** received the Ph.D. degree from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 1999.

He was a Postdoctoral Visiting Researcher with The University of Edinburgh and the University of Glasgow, U.K., in 2001 and 2004, respectively. He is currently an Associate Professor with the Department of Electronics and Computer Science, University of Santiago de Compostela. His current

research interests are multidimensional simulations of nanoscale transistors and solar cells. He has 91 peer-review articles, more than 250 publications, and over 20 invited talks.

**KAROL KALNA** received the M.Sc. degree (Hons.) in solid state physics and the Ph.D. degree in condensed matter from Comenius University, Bratislava, Czechoslovakia/Slovakia, in 1990 and 1998, respectively.

He was a Research Scientist with the Institute of Electrical Engineering, Slovak Academy of Sciences, and a Postdoctoral Researcher with the University of Glasgow, U.K. He is currently a Professor of electronics leading the Nanoelectronic

Devices Computational Group, Swansea University, U.K. He has 98 peerreview articles, more than 250 publications, and over 20 invited talks. He held an EPSRC Advanced Research Fellowship, from 2007 to 2012, pioneering III–V MOSFETs for digital applications, since 2002.

**GABRIEL ESPIÑEIRA** received the B.S. degree in physics from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 2018, where he is currently pursuing the M.Res. degree in HPC. He is also working at the Centro Singular de Investigación en Tecnoloxías da Información (CITIUS), University of Santiago de Compostela.

**NATALIA SEOANE** received the Ph.D. degree from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 2007.

She was a Visiting Postdoctoral Researcher with the University of Glasgow, Glasgow, U.K., from 2007 to 2009, The University of Edinburgh, Edinburgh, U.K., in 2011, and Swansea University, Swansea, U.K., from 2013 to 2015. She is currently with the University of Santiago de Compostela. She has 45 peer-review articles and more than 100 publications.

• • •