## Bending induced electrical response variations in ultra-thin flexible chips and device modeling

Cite as: Appl. Phys. Rev. 4, 031101 (2017); https://doi.org/10.1063/1.4991532 Submitted: 05 March 2017 • Accepted: 25 May 2017 • Published Online: 11 July 2017

🔟 Hadi Heidari, Nicoleta Wacker and 🔟 Ravinder Dahiya

### ARTICLES YOU MAY BE INTERESTED IN

Review Article: Stress in thin films and coatings: Current status, challenges, and prospects Journal of Vacuum Science & Technology A **36**, 020801 (2018); https://doi.org/10.1116/1.5011790

Metal oxide semiconductor thin-film transistors for flexible electronics Applied Physics Reviews **3**, 021303 (2016); https://doi.org/10.1063/1.4953034

Physics of strain effects in semiconductors and metal-oxide-semiconductor field-effect transistors Journal of Applied Physics **101**, 104503 (2007); https://doi.org/10.1063/1.2730561

### APPLIED PHYSICS REVIEWS—FOCUSED REVIEW

# Bending induced electrical response variations in ultra-thin flexible chips and device modeling

Hadi Heidari,<sup>a)</sup> Nicoleta Wacker,<sup>a),b)</sup> and Ravinder Dahiya<sup>c)</sup>

Bendable Electronics and Sensing Technologies (BEST) Group, University of Glasgow, Glasgow G12 8QQ, United Kingdom

(Received 5 March 2017; accepted 25 May 2017; published online 11 July 2017)

Electronics that conform to 3D surfaces are attracting wider attention from both academia and industry. The research in the field has, thus far, focused primarily on showcasing the efficacy of various materials and fabrication methods for electronic/sensing devices on flexible substrates. As the device response changes are bound to change with stresses induced by bending, the next step will be to develop the capacity to predict the response of flexible systems under various bending conditions. This paper comprehensively reviews the effects of bending on the response of devices on ultra-thin chips in terms of variations in electrical parameters such as mobility, threshold voltage, and device performance (static and dynamic). The discussion also includes variations in the device response due to crystal orientation, applied mechanics, band structure, and fabrication processes. Further, strategies for compensating or minimizing these bending-induced variations have been presented. Following the in-depth analysis, this paper proposes new mathematical relations to simulate and predict the device response under various bending conditions. These mathematical relations have also been used to develop new compact models that have been verified by comparing simulation results with the experimental values reported in the recent literature. These advances will enable next generation computer-aided-design tools to meet the future design needs in flexible electronics. © 2017 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). [http://dx.doi.org/10.1063/1.4991532]

### TABLE OF CONTENTS

| I. INTRODUCTION                                  | 1  |

|--------------------------------------------------|----|

| II. HISTORICAL PERSPECTIVE                       | 2  |

| III. ULTRA-THIN CHIPS AND MECHANICAL             |    |

| BENDING                                          | 3  |

| A. Uniaxial bending of UTCs                      | 4  |

| B. Biaxial bending of UTCs                       | 5  |

| C. Torsional deformation of ultra-thin Si-chips. | 6  |

| IV. ELECTRICAL BEHAVIOR OF STRESSED              |    |

| SILICON AND CMOS TRANSISTORS                     | 6  |

| A. Stress effects in bulk Si                     | 6  |

| B. Stress effects in MOSFETs                     | 8  |

| V. COMPACT MODELING OF STRESS                    |    |

| EFFECTS IN CMOS DEVICES                          | 10 |

| A. Layout-dependent stress effects modelling     | 10 |

| B. Bending stress effect modelling               | 11 |

| VI. CIRCUIT-LEVEL STRESS EFFECTS                 | 12 |

| A. Circuit-level bending stress effects          | 13 |

| 1. Inverters                                     | 13 |

<sup>a)</sup>H. Heidari and N. Wacker contributed equally to this work.

<sup>c)</sup>Author to whom correspondence should be addressed: Ravinder.dahiya@ glasgow.ac.uk

| <ol> <li>2. Ring oscillators (RO)</li> <li>3. Current mirrors</li> </ol>         | 13<br>14 |

|----------------------------------------------------------------------------------|----------|

| 4. Operational amplifiers                                                        | 14       |

| <ol> <li>Memory cells</li> <li>B. Circuit-level bending stress effect</li> </ol> | 15       |

| mitigation<br>VII. CONCLUSION                                                    | 16<br>17 |

### I. INTRODUCTION

The last decade has witnessed tremendous advances in flexible and conformable electronics. Many applications have benefited and numerous new applications will arise from electronics that can bend and conform to threedimensional curvilinear shapes. For example, vital medical devices (e.g., retinal implants, pacemakers, and prostheses), intelligent clothing, flexible displays, robotics, and numerous wearable gadgets, which are needed to enable advances in emerging fields such as Internet of Things, robotics, and healthcare, will all require bendable and conformable electronics.<sup>1–11</sup> As for any new technology, the electronics over bendable substrates has its own share of challenges, a few of which (e.g., related to fabrication over large areas and integration on diverse flexible substrates<sup>12</sup>) have already received significant attention. With the field advancing

$\Theta$

<sup>&</sup>lt;sup>b)</sup>Now with Infineon Technologies, Munich, Germany.

towards circuits and systems, the new set of challenges that require attention are related to reliable and uniform operation of flexible integrated circuits (ICs) under various bending states. Numerous parameters such as the crystal structure of the electronic substrate, the design of devices and circuits and their layout with respect to various crystal axes, and the energy band structure are affected by bending induced stresses and strains through variations in electrical parameters such as charge carrier mobility and threshold voltage. The bending induced effects can bring significant deviation in the response of flexible electronics from their designed values and may influence their effective use in the target application. Therefore, it is critical to understand the behavior of devices and circuits under different bending conditions and the interplay between mechanics, solid-state physics, and electrical and electronic inputs. A few articles have reported some of the stress-induced effects,<sup>13</sup> but the modelling of such variations, for example, to enable future computer aided design (CAD) tools, has not been reviewed so far. This paper will fill this gap by using studies related to electronic devices on ultra-thin chips (UTCs) made from silicon (Si). The goals of this survey paper are to: (1) review various types of bending and related induced stresses experienced by the UTCs and their analytical relationships. Various deformation types, modes of stresses (static and dynamic), surface orientations, device channel directions, and gate electric fields are considered. While the primary focus is on the bending-induced stress, the fabrication process-induced effects are also discussed for the sake of completeness; (2) review the impact of different types of stresses on the DC behavior of electronic devices and gain insights into energy band structure and transport properties; (3) correlate the bending induced stress with the variations in the output of devices and circuits; and (4) advance CAD tools by presenting new compact models. The proposed device models follow the comprehensive studies based on changes in the electrical parameters of strained transistors. The challenges in circuit simulation and implementation have been identified. As flexible electronic systems are often unconstrained during bending, the terms stress and strain are used interchangeably throughout this paper.

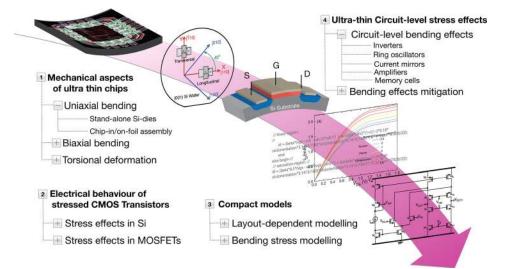

A visual summary of this paper is given in Fig. 1. The paper is organized as follows: Sec. II presents a historical perspective of the field. The mechanical aspects of various types of bending, including uniaxial, biaxial, and torsional deformations, experienced by UTCs are presented in Sec. III. Section IV describes the electrical behavior of Si resistors and transistors during bending and the effect of bending-induced stress on electrical parameters of devices on UTCs. A survey of compact modeling of stress effects on complementary metal-oxide-semiconductor (CMOS) is given in Sec. V followed by a detailed analysis of the stress effects at the circuit-level given in Sec. VI. Finally, outlook and concluding remarks are put forward in Sec. VII.

### **II. HISTORICAL PERSPECTIVE**

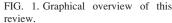

From the historical perspective, the field of flexible electronics has grown exponentially as evidenced by the trend in Fig. 2, which is based on the number of publications in this

FIG. 2. Plots showing publications since 1991 in the field of flexible electronics (y-axis on the right side), piezoresistive effects in all types of devices, i.e., planar as well and non-planar (y-axis on left side), modeling of devices responses in all types of devices after considering the piezoresistive effect (y-axis on the left side), and the modeling of device responses in all flexible electronic devices after considering the piezorsistive effect (y-axis on the left side). The data were extracted from Web of Science by searching keywords such as flexible electronics and modelling.

field since the early 1990s. The stress/strain or the piezoresistive effect related modeling of the response of devices based on various semiconducting materials also has a similar trend over the same period. However, until about 2005 the piezoresistive effect related studies were mainly based on electronics on planar and non-flexible substrates and they were carried out for different motivations-ranging from optimization of the fabrication process to enhancing the performance. For example, substrate-induced (global) or processinduced (local) uniaxial straining of Si, Ge-, and III-V (e.g., GaAs) alters the band structure so as to enhance the performance of metal-oxide-semiconductor field-effect-transistors (MOSFETs).<sup>14-22</sup> A few review articles have covered aspects such as uniaxial and biaxial strain on carrier mobility in MOSFETs,  $^{23-26}$  with a theoretical analysis of the physics of strained MOSFETs for different wafer surface orientations, channel directions, gate electric fields, and materials.<sup>23,24,26</sup> These studies have positive implications for similar investigations in bendable or flexible electronics. For example, they tell us that the mechanical stresses are not always detrimental, as conventionally considered. When applied in a controlled manner, the stresses or strain can also enhance the device performance as happened during the transition from micro to nanotechnology when straining of Si became an effective tool to attain improved device performance.<sup>23,27–32</sup> In fact, as explained in Sec. IV, the gains from studies on stress related variations can be higher in the case of flexible electronics as the stress-induced variations in device performances could be exploited to predict more than the just the response of devices under various bending conditions. For example, the responses of devices spread on flexible substrates carry a signature of the shape of the substrate, and mapping these variations during bending could be exploited to obtain more information about UTCs than just getting the electrical responses. A combined outcome of these wide range of studies on stress/strain or piezoresistive effects has been a number of methods that are either used to minimize or compensate (e.g., when stress/strain is considered detrimental) the thermomechanical stresses during the chip fabrication assembly and packaging operations<sup>33–35</sup> or methods to improve performance or obtain more information about electronic substrate (e.g., when stress/strain adds value).

The modeling of piezoresistive and bending induced effects in flexible electronics is relatively a new development,<sup>36</sup> as can be noted from Fig. 2. A few papers have reported limited analysis related to the effects of externally applied stresses on device modeling and simulation.<sup>37</sup> These include studies based on limited types of bending such as uniaxial stress-induced effects and using them to propose compact models and SPICE simulations.<sup>38,39</sup> However, many other stress effects such as those related to external applied biaxial and shear stress are yet to be investigated. An in-depth analysis of such effects and their modeling, as presented in this review article, will consolidate the field and potentially boost the research on this topic, which, at the current rate, is expected to yield about 100 publications by the year 2020 (Fig. 2). A general theory about the effects of bending will also enable new CAD tools which are needed to analyze bendable ICs prior to the manufacture and to develop mitigation strategies. The optimum IC design for flexible electronics requires complete understanding and accurate compact modeling of external-induced stress effects in complementary metaloxide-semiconductor (CMOS) devices.<sup>23</sup>

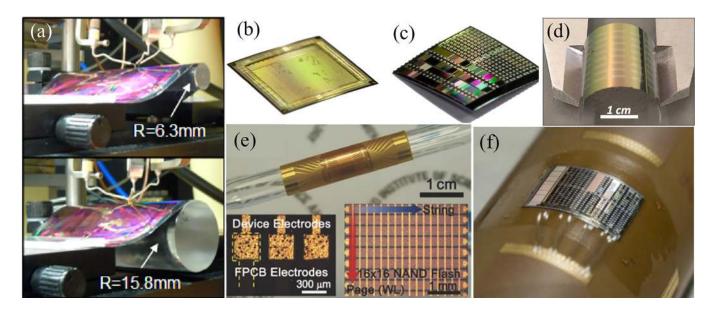

### **III. ULTRA-THIN CHIPS AND MECHANICAL BENDING**

To understand the limits of reliable operation of UTCs, it is important to examine their mechanical properties in terms of bending strength, bending direction, thickness, and defect formation and failure. UTCs with thicknesses  $<20 \,\mu m$ have been explored by many groups to obtain a compact high-performance flexible electronics by using techniques such as post-process wafer thinning by grinding or chemical etching<sup>30,40</sup> (e.g., Circonflex process<sup>41</sup>) and porous Si (e.g., Chipfilm<sup>TM</sup> technology<sup>42</sup>). The strength of UTCs varies with the methods adopted to obtain them.<sup>30,43</sup> For example, the  $15-20\,\mu m$  thick plasma treated UTCs have the highest strength of 2.34 GPa and can bend to  $R_{min} = 2.5$  mm. On the other hand, the UTCs obtained by grinding and polishing can be deformed up to  $R_{min} = 33$  mm. The UTCs obtained with the Dicing-by-Thinning process show the mechanical strengths ranging between 1.5 and 1.9 GPa for 70  $\mu$ m thick samples (and between 1.6 and 2.7 GPa for  $48 \,\mu m$  thick die).<sup>44</sup> The flexible electronic systems are fabricated either (i) directly on flexible substrates (e.g., glass, steel, polyimide) $^{45-49}$  by processing methods such as batch<sup>50</sup> and rollto-roll<sup>46,51–57</sup> or (ii) first on rigid substrates using the existing planar Si fabrication process and then transferred onto mechanically compliant substrates such as flexible plastic/ polyimide foils.<sup>30,42</sup> As mechanical properties of various materials are different, the role they play in the variation of device performance during bending could vary and this needs to be considered as well.

The mechanical strength of UTCs could also vary with the packaging type or with the degree of electronics present on them. For example, the UTCs mounted on compliant polymers with epoxy glue or encapsulated between polymeric layers can undergo multiple reversible bending and stretching.<sup>58–61</sup> The 3-point bending [3PB, shown in Fig. 4(a)] tests (initially developed to test thick samples for fracture strength<sup>62–65</sup>) on  $8\,\mu\text{m}$  thick UTCs reveal a mechanical strength of  $\sim$ 3 GPa.<sup>66</sup> Similar tests on UTCs embedded in flexible foil substrates<sup>67</sup> show an increase in fracture strength of up to  $\sim 190\%$  and a higher curvature of bending—which is up to  $\sim$ 85% more than the UTCs which are not embedded in flexible substrates.<sup>67</sup> Similarly, the mechanical strength of UTCs varies with the degree of electronics present on them. For example, 4-point bending [4PB, shown in Fig. 4(b)] tests have revealed that the blank (i.e., without active electronics) UTCs are mechanically stronger than those with CMOS circuitry.43,53,55,56

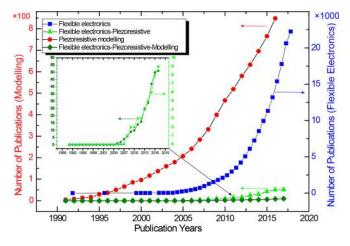

UTCs can experience different types of deformations such as tension (the body is subjected to pull), compressive (the body is under compression), shearing (when the external load tends to make a part of the body to slide on the other one), and torsional (when the external load tends to twist the body around an axis).<sup>68</sup> These deformation can be quantified in terms of stresses and strains having components such as

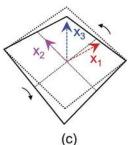

uniaxial, biaxial, and torsional, as shown in Fig. 3.<sup>68</sup> Their analysis in UTCs is essential to: (a) understand the strength (the capacity to withstand strain and stress without breaking), stiffness (how much the system deforms and how is the load transferred within it), failure (mechanisms, causes, and modes), and stability (reliability of the equilibrium) limits, (b) design of multilayered structures such as 3D ICs, and (c) accurately characterize the CMOS devices. Assuming plane stresses, for a  $(x_1, x_2)$  plane the stress tensor can be expressed as (engineering notation) as<sup>69</sup>

$$\boldsymbol{\sigma} = \begin{bmatrix} \sigma_{11} & \tau_{12} \\ \tau_{21} & \sigma_{22} \end{bmatrix},\tag{1}$$

where  $\sigma_{ij}$  (i = j) are the normal stress components and  $\tau_{ij}$  (i  $\neq$  j) denote the shear stress components. These components depend on the coordinate system and vary from point to point inside the material.

In addition, residual internal stresses, developed during fabrication, are also present as evident from the warpage in UTCs.<sup>66,70,71</sup> The mechanical properties of UTCs differ from their bulk counterparts due to differences in processing, size, material composition, and microstructure.<sup>72–74</sup> A comparison of Young's modulus E and the Poisson's ratio  $\nu^{68}$  of several materials frequently used in flexible electronics [e.g., singlecrystal Si, hydrogenated amorphous (a-Si:H), hydrogenated nanocrystalline Si (nc-Si:H), polycrystalline Si, Kapton<sup>®</sup>, and polyethylene naphthalate (PEN)] is given in Table I.75-82 The experimental techniques that have been used to study mechanical aspects of UTCs include (i) direct methods<sup>83,84</sup> such as xray diffraction<sup>85,86</sup> and micro-Raman spectroscopy<sup>87,88</sup> and (ii) indirect methods based on measuring the curvature $^{89}$  (e.g., optical interferometry,<sup>90</sup> laser scanning,<sup>91,92</sup> and microscope image monitoring in real time<sup>43</sup>). The subsection below presents the uniaxial and biaxial bending in UTCs.

TABLE I. Young's modulus and Poisson's ratio of some materials of interest.

| Material                                   | E-Modulus (GPa) | Poisson's ratio $\nu$ |  |

|--------------------------------------------|-----------------|-----------------------|--|

| Si <sub>(110)/(001)</sub> <sup>75,76</sup> | 168.9           | 0.064                 |  |

| Si<100>/(001) <sup>75,76</sup>             | 130.2           | 0.279                 |  |

| a-Si <sup>77</sup>                         | $136 \pm 9$     |                       |  |

| a-Si:H (10% H) <sup>78</sup>               | 150             | 0.2                   |  |

| a-Si:H (15% H) <sup>78</sup>               | 130             | 0.2                   |  |

| a-Si:H (20% H) <sup>78</sup>               | 110             | 0.2                   |  |

| nc-Si:H (SiH <sub>4</sub> 4sccm/10sccm)    | 25-45/55-70     |                       |  |

| Poly-Si <sup>76,79</sup>                   | $158 \pm 10$    | $0.22\pm0.01$         |  |

| Epoxy Epotek 301-2 <sup>80</sup>           | $3.66\pm0.04$   | 0.358                 |  |

| Polyimide Kapton <sup>81</sup>             | 5.37            | 0.320                 |  |

| PEN <sup>221</sup>                         | 5–6             | 0.3–0.4               |  |

FIG. 3. Distortion of the central-surface of an ultra-thin chip because (a) uniaxial bending along  $x_2$ , (b) biaxial bending with respect to the  $x_1$  and  $x_2$ , and (c) torsion with respect to  $x_1$ . ( $x_1$ ,  $x_2$ ,  $x_3$ ) is the Cartesian coordinate system and R is the radius of curvature.

### A. Uniaxial bending of UTCs

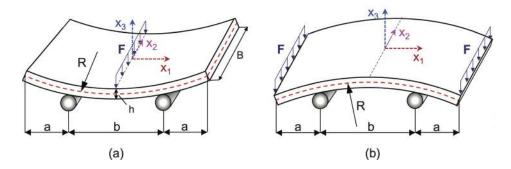

Uniaxial deformation occurs when the applied bending moment(s) deforms the UTC sample along an in-plane axis [e.g.,  $x_1$ , as shown in Fig. 3(a)]. In the 3PB test, an external load (uniformly distributed force **F**) is applied transversely along the middle line of the chip [Fig. 4(a)], where the induced uniaxial stress is maximum.<sup>93,94</sup> For small deflections, the maximum uniaxial stress, calculated using beam and plate bending theories, can be expressed as<sup>68,95,96</sup>

$$\sigma_{11}^{max} = \frac{3}{2} \cdot \frac{Fb}{Bh^2},\tag{2}$$

where F is the applied uniform distributed force, b is the distance between the two internal points (Fig. 4), and h and Bare the thickness and width of the plate, respectively. The thinner the chips are the more they deform. The finite element method (FEM) simulations indicate that the loaddeflection relationship is non-linear at large deformations.<sup>44,97,98</sup> Not much has been reported in the literature about the analytical models that capture the nonlinear relationship between loading force and maximum stress. The 4PB test is another alternative to characterize the UTCs, which is preferred sometimes because of better load distribution between the supports to prevent the UTCs from failing prematurely.99 In this case, each point of the cross-section suffers both a rotation around the x2-axis and a displacement along the x<sub>3</sub>-axis.<sup>100</sup> A uniform uniaxial stress  $\sigma_{11}$  is induced within the region between the two supports-tensile and maximum at the top of the sample, compressive and maximum at the bottom surface, and zero at the position of the neutral surface (red dashed line). In the case of UTCs, the curvature becomes very large and non-linear effects also appear. As a result,  $\sigma_{11}$  is calculated as<sup>101</sup>

$$\sigma_{11} = E \cdot x_3 \cdot \frac{1}{R} = E \cdot x_3 \cdot \frac{\partial^2 w / \partial x_1^2}{\left(1 + \left(\frac{\partial w}{\partial x_1}\right)^2\right)^{3/2}}, \quad (3)$$

where *R* is the radius of curvature, *E* shows the Young's Modulus, and *w* is the beam displacement. The parameters are measured experimentally<sup>43</sup> or determined theoretically from FEM simulations<sup>102</sup> and  $x_3$  is the coordinate along the out-of-plane direction.

In the case of UTCs packaged or embedded in thin foils,<sup>103</sup> several other factors, including increased thickness and the bonding/embedding, influence the bendability as compared to the blank or stand-alone dies. The controlled bending of such chips during characterization is achieved by

conforming them to a cylinder and then applying a uniform load, as shown in Fig. 5(a). The induced uniaxial stress in such samples, obtained by applying the load (stretching force **q** and bending moment **M**) to all layers, as shown in Figs. 5(b) and 5(c), is given by

$$|\sigma_{11}| = E \cdot (x_3 - e) \cdot \frac{1}{R},\tag{4}$$

where e defines the position of the neutral plane. For an mlayer composite structure, e can be determined as<sup>104</sup>

$$e = \frac{\sum_{k=1}^{m} E_k h_k \left[ h_k + 2 \sum_{n=0}^{k-1} h_n \right]}{2 \sum_{k=1}^{m} E_k h_k}.$$

(5)

For a single layer, Eq. (4) reduces to Eq. (2), and the neutral surface coincides with the middle surface. The analytical expression of strain can be obtained from Eqs. (4) and (5), by considering the Hooke's law.<sup>45,46,68,105</sup> The mechanical deformation of multilayered systems with adhesives (Fig. 5(c)) can be obtained using the theory of lap-joints.<sup>106-108</sup> It can be noticed that Eq. (4) considers only the effect of **M**, and the effect of **q** is ignored. The uniaxial stress at the top of an assembly comprising a 20  $\mu$ m UTC on 50  $\mu$ m Kapton foil and conforming to a cylinder of R = 10 mm in these samples has been reported to be  $|\sigma_{11}|^{(110)} \cong 212$  MPa and  $|\sigma_{11}|^{(100)} \cong 173$  MPa. The

FIG. 4. Classical flexural tests: (a) three-point bending (3PB) and (b) four point bending (4PB). F is the applied uniform distributed force. The neutral surface coincides with the middle plane of the plate and is shown in red.

values of *E* are summarized in Table I. The bending investigations on UTCs (h = 20  $\mu$ m) with CMOS circuitry encapsulated in a polyimide foil show that 347 MPa uniaxial stress is induced in the chip, for a minimum bending radius R = 5 mm.<sup>109</sup> Likewise, a three-layer system (composed of 20  $\mu$ m UTC, 10  $\mu$ m epoxy glue, and 50  $\mu$ m Kapton foil) bent on a cylinder of *R* = 10 mm experiences uniaxial stress between [200 and 260] MPa, at the top of the chip, for applied **M** and variable |**q**|  $\epsilon$  [0, 1] MPa mm.<sup>88</sup> The breaking tests performed on UTCs with CMOS circuitry adhesively attached to thin substrates reveal ~60% samples breaking at *R* = 6 mm.<sup>110</sup>

### **B.** Biaxial bending of UTCs

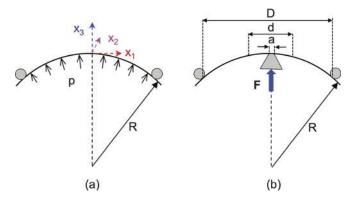

UTCs also experience spherical deformations when bending moments are applied to both in-plane axes  $x_1$  and  $x_2$ [Fig. 3(b)] or by a hydrostatic pressure applied on the entire surface. Biaxial flexural tests on plates, which have been used to evaluate the strength of ceramics for more than 40 years in various configurations such as ball-on-ring,<sup>111,112</sup> uniform pressure,<sup>113</sup> ring-on-ring,<sup>114</sup> or piston-on-threeballs,<sup>115</sup> have been adapted to investigate the biaxial strain effects in UTCs.<sup>116,117,150</sup> Properties such as phonon or electronic deformation potentials<sup>118,119</sup> are measured through these tests to find the fracture strength<sup>96,120–122</sup> or to investigate the 2D strain effects on the electrical behavior of

FIG. 5. Schematic representation of the bending of (a) ultra-thin chip in/on foil; (b) ultra-thin multilayered assembly case of chip-in-foil; and (c) ultrathin assembly of chip adhesively attached to foil.

MOSFETs.<sup>123,124</sup> In the case of thin samples, the fracture strength is influenced by the roughness and morphology of the surface,<sup>125</sup> which in turn are affected by the surface defects introduced through backside grinding, polishing, chemical etching, and edge defects caused by wafer sawing or dicing. In terms of mechanical analysis, the spherical deformation of plates and shells is more complex than the cylindrical or uniaxial deformations. For small deflections, these stresses are expressed analytically,<sup>68,69</sup> and for large deflections (larger than the thickness of the Si-plate), they are usually determined by non-linear FEM calculations.<sup>120</sup> Some examples are presented below.

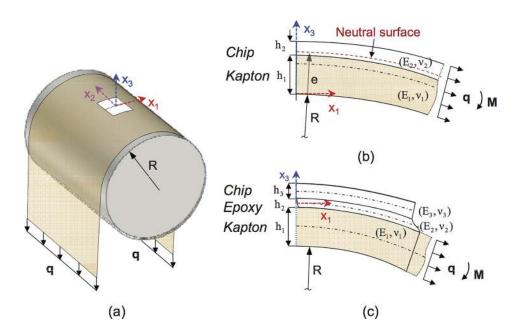

When a hydrostatic pressure p is applied to a thin Siwafer (e.g., thickness  $h \cong 280 \,\mu\text{m}$ ) [Fig. 6(a)], the induced stress can be expressed as a function of the pressure and radius of curvature R as<sup>69,119,126</sup>

$$|\sigma_{biax}| = \frac{R \cdot p}{h}.$$

(6)

The pressure results in spherical deformation of UTCs. The experimental and 3D FEM simulations for UTCs with thicknesses of 15, 25, and 50  $\mu$ m and an area of (10 × 10) mm<sup>2</sup> indicate that the induced biaxial stresses are evenly present in the central area of the chip and they increase towards the edge.<sup>117</sup> These studies also indicate that even if the single-crystal Si is anisotropic, its biaxial elastic modulus  $\left(\frac{E}{1-\nu}\right) \cong 180.5$ GPa (Ref. 127) is invariant for the (001)-Si crystal plane.<sup>128</sup> Spherical deformation using pressure used in the case of islands of a:Si (100 nm grown on top of 400 nm Si<sub>3</sub>N<sub>4</sub>) circuits fabricated on 50  $\mu$ m thin Kapton foil<sup>129,130</sup> shows 5% average biaxial strain for every steradian spherical deformation (subtending 66°).

The ball-on-ring test has also been used to investigate the fracture strength of spherically deformed UTCs.<sup>67</sup> In the ball-on-ring method, cylindrical deformation is achieved with a force **F**, applied in the center of the sample with a conical steel punch head of diameter *a*, as shown in Fig. 6(b).<sup>96,131</sup> The biaxial stress is observed at the central area of the wafer within a concentric circle of diameter *d*, where the induced radial stress equals the azimuthal (tangential) stress. With this bending method, an applied displacement of ~0.9 mm induces ~0.037% uniform biaxial strain in the center region of 100 mm wafers.<sup>124</sup> The stress

FIG. 6. Schematic representation of two classical biaxial bending tests used in the case of thin samples: (a) hydrostatic pressure; and (b) ball-on-ring.

variation obtained by FEM simulations<sup>124</sup> and the maximum stress is calculated as<sup>96,131</sup>

$$|\sigma_{biax}^{max}| = \frac{3|F|(1+\nu)}{4\pi\hbar^2} \cdot \left(1 + 2\ln\frac{D}{d} + \frac{1-\nu}{1+\nu} \cdot \frac{2D^2 - d^2}{4R^2}\right),\tag{7}$$

where *d* in turn can be expressed as a function of the thickness *h* and diameter a.<sup>96,118,131,132</sup>

### C. Torsional deformation of ultra-thin Si-chips

The shear stress analysis in UTCs is also important for investigating their torsional fracture strength. A very few publications have reported the investigation of flexible layered Si-structures subjected to torque.<sup>133</sup> Most of these investigations have been carried out by twisting bulk Sistrips around one axis (e.g.,  $\langle 110 \rangle$  or  $\langle 100 \rangle$ ) with test setup called torsional bridge.<sup>134</sup> The torsional stiffness of bulk Si has been investigated since 1996 (Refs. 135 and 136) and torsional tests have been used to determine the shear-moduli<sup>137</sup> and failure criteria.<sup>138</sup> The maximum shear stress induced by a torsional moment at the surface of UTC depends on the applied moment, thickness, and the shear coefficients of the material UTC is made of. The rotational angle can also be calculated as a function of applied moment.<sup>134</sup> Both the analytical results and the FEM simulation have been shown to have homogeneous shear stress induced at the surface with edges, thus offering an exception where the shear stress decreases rapidly. The shear stress analysis in UTCs can be described by the beam's theory based on small deformation assumption.<sup>68</sup> The mechanical analysis of UTCs subjected to torque can be explained with Karman's plate theory<sup>69</sup> of large deflections. Since the deformation of such thin systems is accompanied by large rotational angles, the stress analysis often requires 3D FEM simulations. One of the few publications that deal with the torsional deformation of thin multilayer polymer systems used as substrates in flexible electronics is the study by Lee and Liu.<sup>133</sup> Their results indicate that a sample having larger Young's modulus is easier to twist along the twisting direction than along the transverse direction and that the rectangular samples are easier to deform than the square ones.

### IV. ELECTRICAL BEHAVIOR OF STRESSED SILICON AND CMOS TRANSISTORS

The effects of uniaxial, biaxial, and shear stress on the electrical behavior of strained Si-resistors and MOSFETs are further summarized in this section. The physical mechanisms by which various types of stress change the electron transport in Si are also highlighted.

### A. Stress effects in bulk Si

Stresses change the electrical resistance of Si by significantly changing its resistivity even for small variation in geometry,<sup>139</sup> which is also termed as piezoresistivity.<sup>140</sup> As Si is anisotropic, the variation in its conducting properties<sup>141,142</sup> as a result of stress can be expressed as

$$\frac{dr_{ij}}{r} = \frac{d\rho_{ij}}{\rho} = \Pi_{ijkl} \cdot \sigma_{kl} + \Pi_{ijklmn} \cdot \sigma_{kl} \cdot \sigma_{mn} + \cdots, \quad (\forall) \, i, j, k, l, m, n = \{1, 2, 3\}, \tag{8}$$

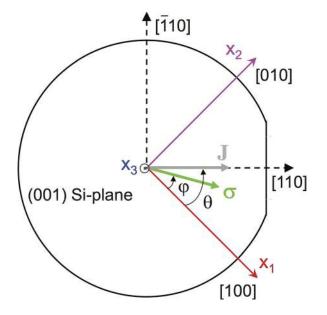

where r and  $\rho$  are the resistance and resistivity without stress,  $\sigma_{kl}$  and  $\sigma_{mn}$  are the components of stress tensor [Eq. (1)], and  $\Pi_{ijkl}$  and  $\Pi_{ijklmn}$  are the first- and second-order piezoresistive coefficients. The cubic symmetry of Si results in a simplified piezoresistive tensor,<sup>143</sup> which can be evaluated for different Si-surface orientations and for uniaxial and biaxial stress. For the (001) Si-surface (which is prevalent in the microelectronics industry) and in-plane uniaxial stress, the 1st order piezoresistive tensor reduces to three independent piezoresistive coefficients  $(\Pi_{11}^{(001)}, \Pi_{12}^{(001)}, \Pi_{44}^{(001)})^{144,145}$ and the 2nd order piezoresistive tensor reduces to nine.<sup>146,147</sup> For low stresses ( $\leq$ 500 MPa), the higher-order terms are usually neglected.  $\Pi_{11}^{(001)}$  ( $|\theta-\phi|=0^\circ)$  and  $\Pi_{12}^{(001)}$  ( $|\theta-\phi|=90^\circ)$ are the longitudinal and transverse piezoresistive coefficients. The angle  $\theta$  indicates the current flow direction and the angle  $\varphi$  the stress application direction, as sketched in Fig. 6. These coefficients are determined from measurements along  $\langle 100 \rangle$ -Si fundamental axes, which is also the principal stress axes (no shear stresses act along these directions).  $\Pi_{44}^{(001)}$  is the shear coefficient determined from  $\langle 110 \rangle$  measurements as the uniaxial stress along these axes consists of both hydrostatic and shear components. The axes  $[\bar{1}10]$  and [110] are parallel and perpendicular to the primary wafer flat and correspond to the orientation of most resistors and transistors in ICs. A general relationship for the (001) Si-plane  $\Pi^{(001)}$  ( $\Pi^{(001)}_{11}$ ,  $\Pi^{(001)}_{12}$ ,  $\Pi_{44}^{(001)}, \theta, \varphi$  is<sup>39</sup>

$$\Pi^{(001)} = \Pi_{11}^{(001)} \cdot \left( \cos^2\theta \cdot \cos^2\varphi + \sin^2\theta \cdot \sin^2\varphi \right) + \Pi_{12}^{(001)} \cdot \left( \cos^2\theta \cdot \sin^2\varphi + \sin^2\theta \cdot \cos^2\varphi \right) + 2 \cdot \Pi_{44}^{(001)} \cdot \sin\theta \cdot \cos\theta \cdot \sin\varphi \cdot \cos\varphi.$$

(9)

Typical values of piezoresistive coefficients, obtained experimentally for uniaxial stresses up to 174 MPa, are given in Tables II and III.<sup>144,147</sup> The piezoresistance coefficients depend on the impurity type and concentration. In conventional layout (Manhattan style), most transistors are built for  $\theta = 45^{\circ}$ . In that case, Eq. (9) becomes

$$\Pi^{(001)}(45^{\circ},\varphi) = \frac{\Pi_{11}^{(001)} + \Pi_{12}^{(001)}}{2} + \Pi_{44}^{(001)} \cdot \sin\varphi \cdot \cos\varphi.$$

(10)

TABLE II. Piezoresistive coefficients values  $(\times 10^{-12} Pa^{-1})$  for n-type Si of different doping concentrations (cm<sup>-3</sup>), measured at 300 K.

|                            | n-type Si         |                   |                   |                    |

|----------------------------|-------------------|-------------------|-------------------|--------------------|

| Piezoresistive coefficient | $6 	imes 10^{14}$ | $4\times 10^{16}$ | $1\times 10^{17}$ | $2 \times 10^{18}$ |

| Π <sub>11</sub>            | -1022             | -840              | -770              | -650               |

| $\Pi_{12}$                 | 534               | 430               | 390               | 330                |

| Π <sub>44</sub>            | -136              | -200              | -140              | -120               |

TABLE III. Piezoresistive coefficients values ( $\times 10^{-12} Pa^{-1}$ ) for p-type Si of different doping concentrations (cm<sup>-3</sup>), measured at 300 K.

|                            | p-type Si         |                   |                   |                   |

|----------------------------|-------------------|-------------------|-------------------|-------------------|

| Piezoresistive coefficient | $6 	imes 10^{14}$ | $4\times 10^{16}$ | $1\times 10^{17}$ | $2 	imes 10^{18}$ |

| Π <sub>11</sub>            | 66                | -0.0              | -60               | -40               |

| $\Pi_{12}$                 | -11               | 20                | 10                | 30                |

| Π <sub>44</sub>            | -1381             | 1190              | 1120              | 970               |

Sometimes, the longitudinal  $\Pi_L^{(001)}$  and transverse  $\Pi_T^{(001)}$  coefficients are used instead of the fundamental piezoresistance coefficients. These are

$$\Pi_{L}^{(001)} = \Pi^{(001)}(45^{\circ}, 45^{\circ}/225^{\circ}) = \frac{\Pi_{S}^{(001)} + \Pi_{44}^{(001)}}{2}, \quad (11)$$

$$\Pi_T^{(001)} = \Pi^{(001)}(45^\circ, -45^\circ/135^\circ/315^\circ) = \frac{\Pi_S^{(001)} - \Pi_{44}^{(001)}}{2},$$

(12)

where  $\Pi_{S}^{(001)} = \Pi_{11}^{(001)} + \Pi_{12}^{(001)}$ . The piezoresistance coefficients for other Si-planes and crystallographic directions can be calculated by applying tensor rotation from the reference to the target Cartesian coordinate systems.<sup>132,141</sup> For the (111)-Si plane, which is another common type of wafer used in IC fabrication, the uniaxial piezoresistive coefficients, for lightly doped *n*-type Si, with respect to the ([ $\overline{1}$ 10], [ $\overline{112}$ ], [111]) axes are **B** ( $B_1$ ,  $B_2$ ,  $B_3$ ) = (-312, 297, 61) (×10<sup>-12</sup> Pa<sup>-1</sup>).<sup>27</sup> The corresponding values for *p*-type Si are (718, 228, -448) (×10<sup>-12</sup> Pa<sup>-1</sup>). In an *n*-type material,  $B_1$  and  $B_2$  are the largest coefficients whereas  $B_3$  is quite small. On the other hand, in the case of a *p*-type material  $B_1$  and  $B_3$  have the largest values.

In the biaxial case, the stress is in-plane and symmetric  $\sigma_{11} = \sigma_{22}$  and  $\sigma_{33} = 0$ . The biaxial piezoresistive coefficient of Si is  $\Pi_B = \Pi_L + \Pi_T$ .<sup>123</sup> The resistors and MOSFETs have been extensively studied to determine the variation of mobility of electrons and holes with biaxial stress and to analyze the electronic band structure of biaxially strained-Si.148,149 These studies show that the electron mobility increases with tensile biaxial strain and decreases with compressive strain. The hole mobility increases with both tensile and compressive biaxial strain and is more pronounced in the case of compressive strain.<sup>123,148</sup> These observations do not depend on the channel direction. The value of the shear piezocoefficient ( $\Pi_{66}$ ) in biaxially strained (001) *p*-type Si has been shown to increase for compressive biaxial strain and decrease in the case of a tensile strain.<sup>149</sup> These observations are not always independent of dopant densities. For example, in the case of biaxial tensile strain, the decrease in the shear piezoresistive coefficient is more pronounced for low dopant densities, while for densities around  $10^{20} \text{ cm}^{-3}$ , it remains unaffected. Further, the value of shear piezoresistive coefficients varies linearly with the compressive biaxial strain but is highly nonlinear in the case of tensile strain.<sup>17</sup> The value of the shear piezoresistive coefficients also varies with temperature<sup>150</sup>-decreasing linearly and monotonically with the increase in temperature from -150 °C to +125 °C. The

coefficient value can also change sign for low temperature and low doping as the strain is increased. This means that it may be possible to adjust the temperature dependence for strained-Si with specific doping and biaxial strain. The biaxial elastic modulus of Si often used in such investigations is  $B_{001} \cong 181$  GPa.<sup>151</sup>

The effects of strain are also reflected through change in the positions of atoms, bond lengths, and the angles between the bonds.<sup>143</sup> For example, the high cubic symmetry  $(O_h)$ group) of the Si crystal is lowered with strain, which changes the energy band structure.<sup>152</sup> The effect of changes in the energy band structure on electronics is reflected through variation in the effective mass and hence the mobility, as explained below. The band structure of crystalline Si in the first Brillouin zone consists of six ellipsoidal degenerate energy valleys [Fig. 7(a)], which are also reflected through the cubic symmetry of Si. The ellipsoidal shape of the valleys can be characterized by two effective masses:<sup>153</sup> transverse  $m_t = 0.19m_0$  and longitudinal  $m_l = 0.91m_0$ , where  $m_0 = 9.11 \times 10^{-31}$  kg (511 keV) is the free electron rest mass. The electron conductivity effective mass of Si is proportional to the inverse of the sum over the effective masses in the different minima along the equivalent directions and is expressed as

$$m^* = \frac{3}{\frac{1}{m_l} + \frac{1}{m_t} + \frac{1}{m_t}} = 0.26 \cdot m_0.$$

(13)

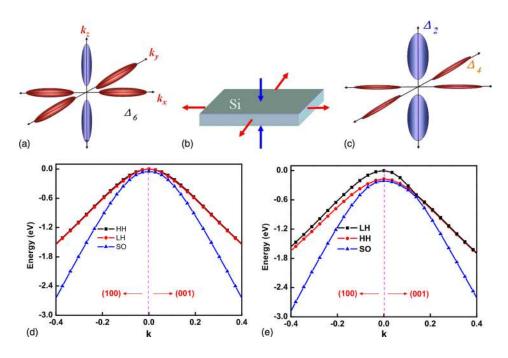

The applied strain lifts the original symmetry determined by band degeneracies and this leads to band warping<sup>154</sup> and changes the transport properties. The carrier mobility  $(\mu = \frac{q}{m^*} \cdot \tau)$  also changes with resulting variations in the effective mass ( $m^*$ ) and the scattering rate ( $1/\tau$ ) of phonons and impurities.<sup>143</sup> In the case of *n*-type Si, the stress-induced band splitting causes the electrons to locate in the lowenergy valleys. As an example, the biaxial stress splits the conduction-band minimum, as shown in Figs. 7(a)–7(c).

FIG 7 Si conduction and valence bands as a function of biaxial strain. (a) The six Si conduction band valleys along three different directions are equally populated without strain; (b) schematics of bulk Si under biaxial tensile strain: (c) under tensile strain. the valleys are split into two groups. Electrons tend to populate the lower  $\Delta_2$  valleys than the higher  $\Delta_4$  valley; (d) and (e) show the three-top valence band near the  $\Gamma$  point for the strainfree and 1.5% biaxial tensile-strained Si, respectively. Reprinted with permission from Yu et al., Phys. Rev. B 78(24), 245204 (2008). Copyright 2008 American Physical Society.

This consists of six equivalent  $\Delta_6$  valleys in the unstrained state, four in-plane  $\Delta_4$  valleys and two out-of-plane  $\Delta_2$  valleys.<sup>148</sup> On the other hand, in *p*-type Si the heavy-hole (HH) and light-hole (LH) valence bands minima are degenerated at the  $\Gamma$  point in the absence of stress as shown in Fig. 7(d). The tensile or compressive biaxial strain warps them significantly, with valence bands becoming highly anisotropic as shown in Fig. 7(e).<sup>123,155,156</sup> Such effects change the conductivity and resistivity ( $\rho$ ) of Si, which is related to the concentration of electrons (*n*) and holes (*p*) and their mobility  $\mu_n$  and  $\mu_p$  as  $\rho = 1/(qn.\mu_n + qp.\mu_p)$ , where *q* is the elementary charge.<sup>157</sup>

### **B. Stress effects in MOSFETs**

Various experiments on MOSFETs presented in the literature indicate that the mobility of charge carriers can vary with various stresses (tensile and compressive), as also explained previously in Section III. These variations can be directional as well as carrier type dependent. Generally, the channel direction differs from the stress direction. In a conventional layout, the MOSFETs are realized on the standard (001)-Si surface with current **J** flowing along  $\langle 110 \rangle$  (Fig. 8). However, devices oriented along the principal Si highsymmetry axes  $\langle 100 \rangle$  or processed on other Si-surfaces such as (110) and (111) are also often encountered. Therefore, the piezoresistive coefficient tensor should be evaluated separately from the channel mobility variation with stress.

Unlike bulk-Si, two aspects are specific to shear piezoresistive coefficients of the MOSFETs: *First*, in addition to the scattering on phonons and impurities, the carriers also experience Coulomb scattering at the oxide-Si interface.<sup>158</sup> As a result, their surface mobility at room temperature is much lower than bulk Si (e.g.,  $\mu_n \le 670 \text{ cm}^2/\text{V}$  s versus  $\le 1400 \text{ cm}^2/\text{V}$ V s for the bulk and  $\mu_p \le 250 \text{ cm}^2/\text{V}$  s versus  $\le 450 \text{ cm}^2/\text{V}$  s for the bulk).<sup>159,160</sup> The scattering takes place on the charges trapped at the interface and on the interface roughness.<sup>143</sup> *Second*, the applied vertical electric field creates a potential

FIG. 8. Common current flow (*J*) direction on (001) Si-plane.  $\sigma$  is the uniaxial stress. The angle  $\theta$  indicates the current flow direction and the angle  $\varphi$  the stress application direction, from the principal Si-axis.<sup>100</sup>

well which confines the carriers in the out-of-plane direction, quantizing the energy levels and changing the effective mass in the out-of-plane direction. The degeneracy between inplane and out-of-plane valleys is removed. In n-type MOSFETs, the conduction band valleys shift and split the minimum into sub-bands  $\Delta_2$  and  $\Delta_4$ .<sup>161</sup> Thus, even in the absence of strain, the energy levels are non-degenerate. The energy difference between the  $\Delta_2$  and  $\Delta_4$  sub-bands varies with the intensity of the transverse effective field. For example, an effective gate field of 1 MV/cm induces an energy difference  $\Delta E_0 = \sim 12 \text{ meV}$ , at T = 300 K, for an inversion electron density of 10<sup>13</sup> cm<sup>2</sup>.<sup>143</sup> The confinement field in the p-type MOSFETs shifts the degeneracy of valence band HH and LH sub-bands. A higher split can lead to lower interband scattering. In the case of (001)/(110), the 1 MV/cm surface field causes a splitting of  $\sim 25 \text{ meV}$ , at T = 300 K.<sup>162</sup> For (110)/(110), the same field splits more the HH and LH subbands and causes a lower inter-band scattering, thus resulting in a higher hole's mobility than (001)/(110) Si.

In the presence of stresses, the band splitting is due to the cumulative effect of both confinement-induced and straininduced band splitting. The strain alters the electrical characteristics of MOSFETs by changing the drain current  $I_{\rm D}$ through the effective carriers mobility  $\mu_{\rm eff}$ .<sup>163</sup> This is the spatial average of the mobility profile in the inversion layer, which can be modeled by the universal mobility curve.<sup>161</sup> The sensitivity of  $I_{\rm D}$  to stress is reported to have been caused primarily by the strain-induced changes of mobility.<sup>164,165</sup> If the stress-induced threshold voltage variation is low, the  $I_{\rm D}$  variation because of stresses is governed by variations in  $\mu_{\rm eff}$ . Like Eq. (8), the change in drain current can be expressed as

$$\frac{\Delta I_D}{I_D} = \frac{\Delta \mu_{eff}}{\mu_{eff}} = \Pi_{ijkl} \cdot \sigma_{kl} + \cdots,$$

(\forall ) *i*, *j*, *k*, *l*, *m*, *n* = {1, 2, 3}. (14)

For the low stress values (<500 MPa), the piezoresistive coefficients are determined by variations of  $I_D$  with stress in the linear or saturation regions of transistor characteristics. The piezoresistive coefficients can be calculated from the slope of mobility variation with respect to stress. These are significantly smaller in UTCs than their bulk counterparts, with values depending on the actual doping density and applied gate voltage. The piezoresistive coefficients also have some dependence on the channel length of MOSFETs. The source-drain parasitic resistances to the drain current also contribute to such variations.<sup>166</sup> For high stresses, the linear response piezo-model fails and the 2nd order terms must be considered. For (001) surface orientation and uniaxial stress, the piezoresistive coefficients are determined from uniaxial stress measurements in three cases: (a) longitudinal (stress || drain current  $I_{\rm D}$  ||  $\langle 110 \rangle$ ); (b) transverse (stress  $\perp$  $(I_D || \langle 110 \rangle))$ ; and (c) diagonal  $(\angle (I_D, [110]) = \theta = 45^\circ)$  while stress is applied longitudinal and transversal to the channel.<sup>167,168</sup>

For *n*-type MOSFETs, the experimental results show that  $\sim 100 \text{ MPa}$  uniaxial tensile stress applied along  $\langle 110 \rangle$ leads to ~5% increase in the electrons  $\mu_{eff}$  in the longitudinal case and only  $\sim 2\%$  in the transverse case.<sup>39</sup> A few values of the piezoresistive coefficients are given below in Table III. For *p*-type MOSFETs, the hole mobility depends on the Si surface and channel orientation. The (001)/(110) MOSFETs show an inferior surface hole mobility than the (110)/(110)MOSFETs.<sup>155</sup> This is due to a higher surface roughness scattering rate in (001)/(110) p-type MOSFETs than in (110)/(110) $\langle 110 \rangle$  p-type MOSFETs. The confinement field shifts the degeneracy of the HH and LH sub-bands. For example, a field of 1 MV/cm in a (001)/(110) p-type MOSFET, at T = 300 K, induces a splitting between the HH and LH subbands as large as  $\sim 25 \text{ meV}$ .<sup>162</sup> A tensile uniaxial stress of  $\sim 100 \text{ MPa}$  applied along the [110] direction causes an increase of  $\sim 4.5\%$  of the hole's mobility  $\mu_{eff}$  in the transverse case and a decrease of  $\sim -6\%$  in the longitudinal case.<sup>39,166</sup> The absolute values of the piezoresistive coefficients  $\Pi_{11}^{(001)}$  and  $\Pi_{12}^{(001)}$  of bulk MOSFETs are lower than bulk Si (Table III). However, the values of  $\Pi_{44}^{(001)}$  are similar. The differences arise from the presence of the confinement field in MOSFETs. In the case of the (111) Si-plane, the maximum mobility variation is obtained for the longitudinal case and the mobility variation is minimized when in the transverse case.

The studies related to the impact of stress on threshold voltage ( $V_{TH}$ ) of nanoscale strained-Si and SiGe MOSFETs reveal that  $V_{TH}$  decreases with increasing strain in the Si thin film. The  $V_{TH}$  roll-off affects the device characteristics and performance. The analyses of  $V_{TH}$  shift for uniaxial and biaxial stressed Si NMOS transistors with the  $\langle 110 \rangle$  channel direction on (001) wafers show a significantly larger linear shift of the  $V_{TH}$  (four times larger) for biaxial stress compared to the uniaxial case. This large variation in the biaxial case results from the stress-induced change in the Si electron affinity and bandgap.

The piezoresistive behavior of MOSFETs with similar configurations, under the same environmental conditions and in the presence of the same applied stress type and magnitude, is expected to be similar for devices on bulk Si and on UTCs. The difference between them arises from the mechanical stiffness (see Sec. III) related to the stress magnitude induced by a certain bending radius R. In this respect, UTCs in/on foils with different CMOS technologies have been reported to investigate the effects of piezoresistive behavior of MOSFETs. For example, short-channel singlecrystal-Si MOSFETs in a 0.8 µm CMOS process with 20 µm thickness on a 50  $\mu$ m thick Kapton foil substrate have been studied by bending on cylinders of radii of curvature down to 10 mm.<sup>88</sup> Smaller radii of curvature (R = 5 mm) have also been reported with mono-crystalline NMOS and P-type Meal Oxide Semiconductor (PMOS) transistors on  $20 \,\mu m$  thick UTCs in a 0.35  $\mu$ m CMOS process embedded into a polyimide foil, corresponding to a uniaxial stress  $\sigma_{22} \cong 347$ MPa.<sup>109</sup> Further enhancement in the minimum of radii of curvature (R  $\epsilon$  [1.6, 70] mm) is achieved in a-Si:H thin-film transistors (TFTs) fabricated on 25  $\mu$ m thick Kapton foil.<sup>169</sup>

### V. COMPACT MODELING OF STRESS EFFECTS IN CMOS DEVICES

As explained earlier, the stress leads to changes in semiconductor material properties such as change in band structure, effective mass, and electron affinity. From device viewpoint, all this is reflected in the changed mobility and threshold voltage, which eventually affect the device performance parameters such as drain current and transconductance. For an effective use of UTCs, an accurate and high-speed simulation of circuits based on a thin substrate is required. Currently, the simulation of the bending stress effects in ultra-thin devices is performed analytically using formulations available for understanding the analog operations. These effects are considered in conventional simulators for the planar architecture. Furthermore, due to the inherently slow simulation in the models based on numerical techniques, they are less desirable for ultra-thin devices. The performance indicators like accuracy, speed, and reliability are strongly connected to the compact models that are used to describe the device behavior, as also explained in Sec. I. This illustrates the importance of an accurate and efficient compact model for ultra-thin CMOS chips, which considers some of the stress/strain related variations discussed in Secs. III and IV. This section reviews the state-of-the-arts in this area.

#### A. Layout-dependent stress effects modelling

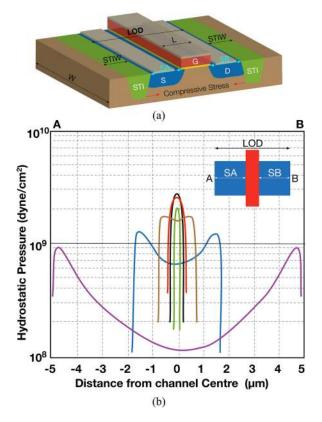

During the process of transistor isolation, it is a standard practice to make a shallow trench by etching the wafer and filling it with silicon oxide to isolate the active areas of MOSFET devices. This process exerts mechanical force, which is a compressive stress applied near to the diffusion areas. This stress is commonly referred to as the shallow trench isolation (STI) stress and termed as the Length of Oxide Diffusion (LOD) effect. Figure 9(a) shows the typical MOSFET layout surrounded by shallow trench isolation. SA and SB are the distances between trench isolation edges to Gate-polySi from the two ends. The LOD is expressed as LOD = SA + SB + L. Figure 9(b) shows the stress

FIG. 9. (a) Illustration of MOSFET device geometry using a STI scheme. (b) Stress distribution within the MOSFET channel. Reproduced from Xi *et al.*, Technical Report No. 94720 (University of California, Berkley, 2003).

distribution along the channel of MOSFET devices induced by the trench isolation. It can be noted that the stress of the central region increases dramatically with shrinking of the LOD.<sup>170</sup> The charge carrier mobility of the device is influenced through the band structure modification, as explained in Sec. IV. Furthermore, the doping profile variation results in  $V_{th}$  dependence of the stress effect. Both effects follow the same *1/LOD* trend but have different *L* and *W* scaling influence. This underlined the importance of modifying some parameters in the BSIM model to implement the phenomenological model.

To model the mechanical stress effects impacting MOSFET electrical behavior, Bianchi *et al.*<sup>171</sup> presented a model which accounts for the mobility variations and experimentally evidenced with complex MOSFET geometries. This model proves to be an efficient way to include mechanical stress effects into standard simulation models. In this work, the STI induced mechanical stress has been shown to be the dominant mechanism for stress variation in the channel, which modulates the charge carrier mobility as a function of MOSFET geometry.

Another compact and scalable model about the STI induced mechanical stress effect on MOS electrical performance is given in Ref. 172. This model includes the influence of STI stress on the mobility, saturation velocity, threshold voltage, and other important second-order effects and therefore it could simulate the layout-dependence of MOS performance with greater accuracy and efficiency. The model has been verified with different technologies, different

dimensions, and various layouts of MOS devices. Based on the model, new effective *SA/SB* formulas have been derived to improve the simulation efficiency and have also been verified by data from various layouts.

An analytical model to estimate the delay in the presence of process-induced mechanical stress in stacked transistors based inverters and logic gates has been reported by Alam *et al.*<sup>173</sup> Derived using a modified alpha-power law, this model considers the channel length modulation effect. The methodology to incorporate the impact of processinduced mechanical stress effects in the derived delay model has also been presented. The incorporation of stress effects in this model enables estimating the layout-dependent effects of process-induced mechanical stress. The model has also been compared with Technology Computer Aided Design (TCAD) calibrated HSPICE simulation setup using 45-nm Predictive Technology Model. The model derives a stressaware delay model which is usable in the method of logical blocks like inverter and NAND/NOR gates.

### B. Bending stress effect modelling

Several device modeling groups are dealing with the compact modelling of bulk MOSFET and advanced technologies such as double-gate (DG) MOSFET,<sup>174</sup> graphene FET transistors,<sup>175</sup> MoS<sub>2</sub>FET,<sup>176</sup> and CNTFET (Carbon NanoTube FET),<sup>177</sup> for analog and mixed circuits. The major goal is to bring simple solutions, which are numerically efficient and are close to device physics. These compact models also extensively explore the capabilities of Verilog-A and VHDL-AMS. However, only very few works have included the effect of stress in MOSFETs.<sup>39,178</sup>

In 2011, the authors reported a method to simulate the effect of uniaxial stress on MOSFETs.<sup>39</sup> To calculate the coefficients for arbitrary directions of current and stress in the (001) silicon (Si) plane, the model implemented a general relation with the fundamental piezoresistive coefficients. This method can perform static and dynamic simulations in linear and saturation regions. It is simulator-independent and does not depend on the source of uniaxial stress. The model is adaptable to other bulk CMOS nodes as well as technologies such as Si-on-insulator (SOI).

The MOSFET device aging has also been studied and implemented with SPICE circuit simulation.<sup>179</sup> For circuit simulation, the age-related degradation has been implemented as stress and associated key MOSFET parameters such as threshold voltage and mobility. The model operates with an optimization loop and starts the sequence with an initial set of parameters in Synopsys HSPICE as an external circuit simulator. It extracts device characteristic parameters including threshold voltage and drain current in the saturation and linear region. Subsequently, with an error function, the measured and simulated values have been compared to adjust the parameters and reach the minimum value of the error function. A compact model which demonstrates the simulations involving elastic deformation of a thin Si chip on a spherical holder is presented in Ref. 117. In this work, the simulation starts with a shell model which is validated through a convergence study and comparison with a 3D model. Following this, the influence of the anisotropic elastic behavior (single crystal) is considered in a bulge test condition and it was noted that isotropic and anisotropic Si simulation gave similar deformations. At the end, the spherical forming is accomplished with a shell model and an anisotropic law.

A deterministic compact model developed by Alagi *et al.* to investigate the parametric instability in elementary devices addresses the device instability, which can be traced back to microscopic reactions obeying the reversible first-order kinetics.<sup>180</sup> The model can describe the response to different periodic stimulus waveforms and is suitable for implementation in commercial electronic circuit simulators (Eldo UDRM). This methodology has been applied to model the negative-bias-temperature threshold voltage instability of a *p*-channel MOSFET. The comparator circuit simulated in this paper for threshold voltage recovery is crucial for circuit design.

A methodology to include parametric shifts induced by mechanical stress from wafer level chip scale package (WLCSP) in an analog circuit simulation flow is given in Ref. 181. Considering that the bending stress is homogeneous with packaging induced mechanical stress, their methodology enables analog system designers to identify circuit blocks with unacceptable sensitivity to WLCSP stress and provides a quantitative route for optimizing system floorplan and/or circuit layout. This is exemplified with an on-chip oscillator circuit suffering from an increased spread and yield loss caused by WLCSP stress variability. This issue has been resolved using a simulation flow which tuned using high-resolution experimental variability data measured on dedicated test chips. The method could be potentially useful for large area flexible electronics also.

Another interesting dimension of mechanical stress is its influence of the thermal behavior of devices. In this regard, the nonlinear model order reduction method is useful as it constructs the one-port dynamic compact models of nonlinear heat diffusion in UTC stacking technology.<sup>182</sup> The method leads to models of small state-space dimensions and allows accurate reconstruction of the time evolution of temperature field due to an arbitrary power waveform of practical interest. This model has not been investigated for MOSFETs, but it helps us gather the information about the thermal behavior of UTCs.

Recently, Ojha *et al.*<sup>183</sup> presented a physics-based compact model for longitudinal and transverse stress profile in the channel of an uniaxially strained bulk MOS transistor. The model predicts the stress profile for linear stress ( $\sigma_L$ ), linear thickness ( $t_L$ ), gate length ( $L_G$ ), and gate height ( $h_G$ ). The modeled stress profile is used to calculate the average stress and respective threshold voltage shift ( $\Delta V_{th}$ [ $V_{th}(\sigma_L \neq 0) - V_{th}(\sigma_L \approx 0)$ ]) for different ( $h_G$ ). The final strain induced  $V_{th}$  model has only three fitting parameters and includes both the transverse stress component ( $S_T$ , the stress component perpendicular to the direction of carrier flow) and the longitudinal stress component ( $S_L$ , the stress component in the direction of carrier flow). Finally, the accuracy of the reported model has been verified by comparing it with the measured data obtained from devices fabricated using a 28 nm CMOS technology.

Various bending induced effects described in Secs. III and IV can be used to develop a mathematical relation to describe the device model of the MOS transistor as

$$I_{D_{stress}} = I_{D_0} (1 + \Pi_{I_D} \cdot \sigma_{I_D}), \tag{15}$$

$$V_{th_{stress}} = V_{th_0} (1 + \Pi_{V_{th}} \cdot \sigma_{V_{th}}), \tag{16}$$

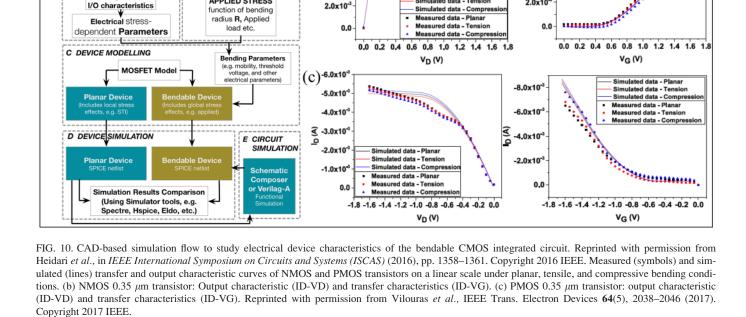

where  $I_{D_{stress}}$  and  $V_{th_{stress}}$  are the new effective drain current and threshold voltage parameters including bending stress.  $I_{D_0}$  and  $V_{th_0}$  are the original drain-current and thresholdvoltage of the transistor without stress, respectively. The piezoresistive coefficients proportional to the drain-current and threshold voltage are reflected by  $\Pi_{I_D}$  and  $\Pi_{V_{th}}$ .  $\sigma_{I_D}$  and  $\sigma_{V_{th}}$ are the bending stress proportional to drain-current and threshold-voltage, respectively. The authors reported the implementation of Eqs. (15) and (16) using a language description in the Cadence environment to predict the value and orientation of the bending stress and describe the behavior of the transistor.<sup>184</sup> Based on the three parameters (including drain-current, threshold-voltage, and orientation of the integrated transistor, which vary under the bending stress), a Verilog-A compact model was presented for MOSFETs developed in the standard CMOS technology. Figure 9(a) illustrates the CAD-based simulation flow by authors.<sup>184</sup> It involves different abstract levels for both planar and bent MOSFETs. The labels A, B, C, etc., identify the blocks at various levels of simulation. From this model, one can note that there are significant performance advantages in process-induced uniaxial stressed n-MOSFET, exhibiting a

**B** STRESS ANALYSIS

Analytical

chanical

Numerical

3D FEM

Model

APPLIED STRESS

(a) A DEVICE MEASUREMENT

Comparison

Flat

smaller drain-current variation and threshold voltage shift by monitoring the bending stress and changing the supply voltage. The efficiency of this model was demonstrated recently with experimental results on 20  $\mu$ m thick UTCs having devices and circuit realized in a standard CMOS technology.185 The measured and simulated transfer and output characteristic curves of NMOS and PMOS 0.35  $\mu$ m transistors on a linear scale under planar, tensile, and compressive bending conditions are shown in Figs. 10(b)-10(c). The maximum observed percentage difference in drain-current during bending for NMOS was found to be  $\sim$ 5.9%, while the percentage difference of simulated results was 4.4%. For PMOS, it was found to be  $\sim 2.4\%$ , while the simulated difference was 2.17%. These results proved >95% accuracy of the proposed model to predict the effect of the bending stress on the devices.

### **VI. CIRCUIT-LEVEL STRESS EFFECTS**

System is more than sum of its parts. In this regard, it is possible that the bending related effects observed in devices may or may not add up at the circuit level. Therefore, taking the discussion forward from devices to circuits, in this section we discuss the works where circuit level bending effects have been studied. We also use some of these circuits to establish the efficacy of Eqs. (15) and (16), which have been proposed to describe the stress induced changes in device response. These results open new avenues to predict the device behavior under various bending conditions and to explore the ways to compensate the bending effect or to take advantage of bending related changes extract more from the overall structure. For example, knowing the responses of

8,0x10

6.0x10

2.0x10

(4.0x10)

ulated data - Planar

Simulated data - Tension

nulated data - Planar nulated data - Tension nulated data - Compre

(b)<sup>1.0x10\*</sup>

E

õ 4.0x10

8.0x10<sup>-1</sup>

6.0x10

Appl. Phys. Rev. 4, 031101 (2017)

TABLE IV. Piezoresistive coefficients values of n-type MOSFETs measured along  $\langle 110\rangle~(\times 10^{-12} Pa^{-1}).$

| References                      | $\Pi_{11}^{(001)}$ | $\Pi_{12}^{(001)}$ | $\Pi_{44}^{(001)}$ | $\Pi_L^{(001)}$ | $\Pi_T^{(001)}$ |

|---------------------------------|--------------------|--------------------|--------------------|-----------------|-----------------|

| Dorda and Eisele <sup>222</sup> |                    |                    |                    | 300             | 200             |

| Canali et al. <sup>223</sup>    | 840                | -340               | 170-200            | 335             | 190             |

| Bradley et al. <sup>164</sup>   |                    |                    | 100                | 450             | 350             |

| Gallon et al. <sup>166</sup>    |                    |                    |                    | 485             | 210             |

| Chu et al. <sup>123</sup>       |                    |                    | 170                | 320             | 150             |

| Wacker et al.39                 |                    |                    |                    | 480             | 170             |

| Mahsereci et al. <sup>168</sup> | 420                | 260                | 310                | 495             | 185             |

devices spread over an area one can perform inverse calculations to predict the shape of substrates on which devices are present. This section also presents the methods that have been adopted to minimize or compensate the effects of bending in devices and circuits. Minimizing or mitigating the bending effect by placing devices in a neutral plane is one popular method that has been used in many circuits presented in this section.<sup>186–188</sup> Some of the circuits described in this section also use layout orientation to reduce the stress-induced effects. The mechanics and the electronic behaviors of various integrated circuits have been highlighted below (Tables IV and V).

### A. Circuit-level bending stress effects

### 1. Inverters

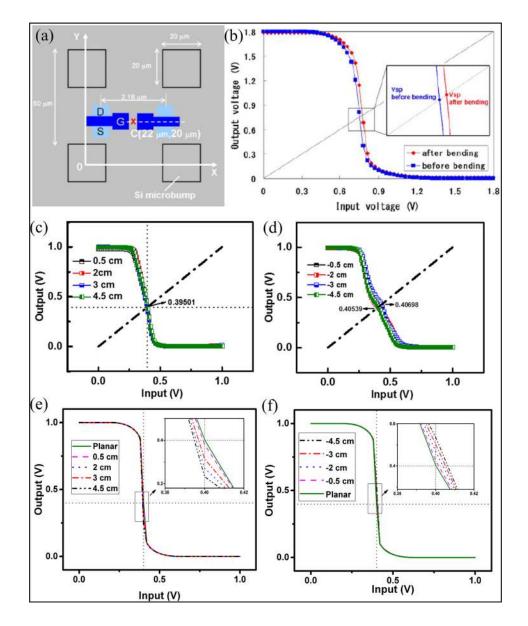

CMOS inverters are one of the most widely used circuits. They operate at relatively high speed with very little power. During bending, the inverters on UTCs show deviation from expected response, because of the changes in responses of their constitutive FETs, i.e., PMOS and NMOS and the underlying physics. Some of ultra-thin CMOS inverters reported in the literature are summarized in Table VI.<sup>186,188–191</sup> Only few of them have investigated the effect of bending stress on the performance. The performance of the thinned Si CMOS inverter circuit by Kino et al.<sup>191</sup> degrades under bending stress, as shown in Fig. 11(a) with MOSFET currents and CMOS inverter switching behaviors. It was observed [Fig. 11(b)] that the switching threshold point, V<sub>sp</sub>, slightly increased after bending stress. The  $V_{sp}$  increases with an increase in hole mobility or decrease in electron mobility as the  $\beta_n/\beta_p$  ratio increases under these conditions. Here,  $\beta_p$  and  $\beta_n$  are  $C_{ox}W_g/L_g$ and  $C_{ox}W_g/L_g$ ,  $C_{ox}$ ,  $W_g$ , and  $L_g$  indicate the hole mobility, electron mobility, gate capacitance, gate width and gate length, respectively. The increase of  $V_{sp}$  after bending shows that the

TABLE V. Piezoresistive coefficients values of p-type MOSFETs measured along  $\langle 110\rangle~(\times 10^{-12} Pa^{-1}).$

| References                           | $\Pi_{11}^{(001)}$ | $\Pi_{12}^{(001)}$ | $\Pi_{44}^{(001)}$ | $\Pi_L^{(001)}$ | $\Pi_T^{(001)}$ |

|--------------------------------------|--------------------|--------------------|--------------------|-----------------|-----------------|

| Colman <i>et al</i> . <sup>145</sup> | 10                 | -238               | -1278              | -753            | 525             |

| Canali et al. <sup>223</sup>         | 125                | -280               | (-1050)-(-1150)    | -600            | 500             |

| Bradley et al. <sup>164</sup>        |                    |                    | -950               | -500            | 450             |

| Chu et al. <sup>123</sup>            |                    |                    | -1030              | -710            | 320             |

| Wacker et al.39                      |                    |                    |                    | -620            | 440             |

| Mahsereci et al. <sup>168</sup>      | 101                | -280               | -1060              | -619            | 440             |

TABLE VI. Summarized comparison of flexible CMOS Inverters.

| Material                                     | Kim<br>et al. <sup>188</sup> | Sevilla<br>et al. <sup>189</sup> | Sachid <i>et al.</i> <sup>190</sup> | Hwang<br>et al. <sup>186</sup> | Kino<br>et al. <sup>191</sup> |

|----------------------------------------------|------------------------------|----------------------------------|-------------------------------------|--------------------------------|-------------------------------|

| Thickness (µm)                               | 1.7                          | 40                               | 0.007                               | 0.3                            | 30                            |

| $L_g^{a}(\mu m)$                             | 13                           | 0.25                             | 2                                   | 500                            | 0.22                          |

| $W_N(\mu m)$                                 | 300                          | 0.35                             | 3.3                                 | 40                             | 0.22                          |

| $W_P(\mu m)$                                 | 100                          | 0.45                             | 5.9                                 | 40                             | 0.22                          |

| Ion/Ioff                                     | $> 10^{5}$                   | N/A                              | $> 10^{7}$                          | $\sim 10^5$                    | N/A                           |

| $V_{sp}^{b}(\mathbf{V})$                     | 2.5                          | 0.4                              | -4                                  | N/A                            | $\sim 0.9$                    |

| $\mu_N (\mathrm{cm}^2/\mathrm{V}\mathrm{s})$ | 290                          | 132                              | 38                                  | 400                            | 1450                          |

| $\mu_p (\mathrm{cm}^2/\mathrm{V}\mathrm{s})$ | 140                          | 80                               | 238                                 | 70                             | 300                           |

${}^{a}L_{g}$  is the gate length.

${}^{b}V_{sp}$  is the voltage of the switching threshold point.

compressive stress increases with  $V_{sp}$ . Thus, local bending stress induced stress affects the CMOS inverter, leading to the circuit performance fluctuations in the Si chip. Another example by Sevilla et al.<sup>189</sup> reports thin (40  $\mu$ m) and flexible (1.5 cm bending radius) Si based functional CMOS inverters whose characteristics show reduced performance for bending radii higher than 1.5 cm as shown in Figs. 11(c) and 11(d). A comparison of these experimental results with the simulated output based on the compact model presented in Sec. IV B is shown in Figs. 11(e) and 11(f). The good agreement of simulation results with the experimental characterization shows that the model presented in this paper through Eqs. (15) and (16)could be the starting point for analyzing device behavior under bending conditions. The effects of circuit-level stress on inverter performance investigated by Shahrjerdi and Bedell<sup>205</sup> show that the electron mobility increases with tensile strain and decreases with compressive strain. On the other hand, the hole mobility increases with both tensile and compressive strain but the effect is more significant for compressive strain because the hole effective mass decreases with compressive strain but increases with tensile strain.<sup>161,205</sup> Since drain current is directly proportional to carrier mobility, higher drain current of the Si MOSFETs under strain can be attributed to high mobility.<sup>192</sup> Therefore, the local bending stress affects the I-V characteristics of both MOSFETs in the inverter and so the switching behavior of the CMOS inverter.

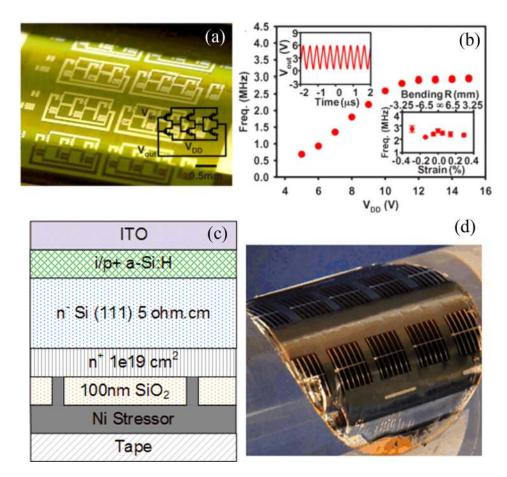

### 2. Ring oscillators (RO)

The ring oscillator (RO) is cascaded combination of delay stages (inverters), connected in a closed loop. The ROs are of great interest to electronic engineers because of numerous useful application and features such as (i) oscillation at low voltage, (ii) high frequency oscillation, and (iii) low power dissipation and many more.<sup>193</sup> Studying the effect of bending on 43-stage RO using a 250-nm process, Yuan *et al.*<sup>194</sup> noticed the speed enhancement under strained conditions. They have studied two types of inverter cell layouts: (i) PMOS channel is parallel to the NMOS channel. A speed enhancement of ~7.4% was noticed for uniaxial strain in a direction parallel to NMOS and perpendicular to PMOS. This is due to large current enhancement for both NMOS and PMOS. The speed enhancement for the second type of layout

FIG. 11. (a) Layout of Si microbumps and CMOS inverters in the thinned Si chip, and (b) CMOS inverter characteristic before and after bending. Reproduced with permission from Kino et al., Jpn. J. Appl. Phys., Part 1 52(4S), 04CB11 (2013). Copyright 2013 The Japan Society of Applied Physics. (c) Voltage transfer curve characteristics of flexible inverters at different bending downward radii and (d) upward radii. Reproduced with permission from J. Appl. Phys. Lett. 108(9), 094102 (2016). Copyright 2016 AIP Publishing LLC. (e) Simulated results (based on the developed compact model) at different bending downward radii corresponding to the characterizations shown in (c). (f) Simulated results corresponding to the characterizations shown in (d) for different bending upward radii.

where strain is perpendicular to NMOS and parallel to PMOS was found to be only ~1.5%, as no simultaneous enhancement for both NMOS and PMOS can be achieved. The mechanical study of ROs on the extremely thin flexible Si on insulator (ETSOI) process with a power supply voltage of 0.9 V also indicates a delay of ~16 ps.<sup>195</sup> The ultra-thin body of the Si channel in ETSOI devices allows aggressive scaling of the channel length into sub-20 nm range without incurring the detrimental short channel effects. Figures 12(c) and 12(d) show the schematic illustration of RO used for a flexible Si solar cell and a flexible 20  $\mu$ m thick Si, respectively.

### 3. Current mirrors

The current mirror is an important building block for linear integrated circuits especially amplifiers. In this circuit, the output current depends upon the aspect ratio, mobility, and feed current.<sup>196</sup> There are clearly observable changes in the output current when the current mirror fabricated on thin Si experiences bending. This is because under the strained condition the mismatching between transistors gains prominence. In an attempt to overcome the piezoresistive effects of bending to realize stable circuit, Hassan *et al.*<sup>197</sup> investigated ultrathin (20  $\mu$ m) CMOS current mirrors made up of orthogonally oriented transistors. The use of orthogonally configuration demonstrates the output current change ( $\Delta I_2/I_2$ ) related to the transistor's changes of drain current ( $\Delta I_D/I_D$ ) differences and can be written as