Bias-Stress Effect in Pentacene Organic Thin-Film Transistors

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

| Citation                | Ryu, K.K. et al. "Bias-Stress Effect in Pentacene Organic Thin-Film<br>Transistors." Electron Devices, IEEE Transactions On 57.5 (2010) :<br>1003-1008. ©2010 IEEE. |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| As Published            | http://dx.doi.org/10.1109/ted.2010.2044282                                                                                                                          |

| Publisher               | Institute of Electrical and Electronics Engineers                                                                                                                   |

|                         |                                                                                                                                                                     |

| Version                 | Final published version                                                                                                                                             |

| Version<br>Citable link | Final published version http://hdl.handle.net/1721.1/62183                                                                                                          |

# Bias-Stress Effect in Pentacene Organic Thin-Film Transistors

Kevin Kyungbum Ryu, *Student Member, IEEE*, Ivan Nausieda, *Student Member, IEEE*, David Da He, *Student Member, IEEE*, Akintunde Ibitayo Akinwande, *Fellow, IEEE*, Vladimir Bulović, and Charles G. Sodini, *Fellow, IEEE*

Abstract—The effects of bias stress in integrated pentacene organic transistors are studied and modeled for different stress conditions. It is found that the effects of bias stress can be expressed in terms of the shift in applied gate voltage  $\Delta V$  for a given current. An empirical equation describing  $\Delta V$  in terms of different gate and drain bias stress measurements and stress times is presented and verified. In the measured devices,  $\Delta V$  saturates at 14 V, independent of the gate bias-stress condition. A model based on carrier trapping rate equation that accounts for this  $\Delta V$  saturation is developed. The model suggests that the  $\Delta V$  saturation is due to the small density of traps compared to the channel carrier density.

*Index Terms*—Field-effect transistor (FETs), organic compounds, reliability, stability, stress, thin-film transistors (TFTs).

## I. INTRODUCTION

**O** RGANIC transistors offer opportunities in flexible electronics that integrate various sensors and actuators with electronic functions [1]. Transistors using pentacene, one of the most widely studied organic semiconductors, exhibit mobilities on par with hydrogenated amorphous silicon (a-Si:H). Such electrical performance is sufficient for many applications such as backplanes of organic light-emitting diode displays [2], imagers [3], and conformal large-area arrays of pressure and temperature sensors [4].

Although sufficient mobility has been achieved with organic transistors for various applications, it has been reported that the current–voltage (I-V) characteristics change with the application of prolonged voltages [5]–[11]. Such change is termed the bias-stress effect. The bias-stress effect is important for practical circuit applications and needs to be understood and reduced. Thus far, published works on the bias-stress effect in organic transistors have been predominantly conducted on SiO<sub>2</sub> gate dielectrics with unpatterned gates. Transistors with patterned gates are necessary for integrated circuits. In addition, there is limited study of different gate and drain bias-stress conditions. To evaluate the bias-stress effect of transistors, it

Manuscript received March 17, 2009; revised October 28, 2009. Current version published April 21, 2010. This work was supported in part by the FCRP Focus Center for Circuit & System Solutions (C2S2), one of six research centers funded under the Focus Center Research Program (FCRP), a Semiconductor Research Corporation entity, under Contract 2003-CT-888. The review of this paper was arranged by Editor J. Kanicki.

The authors are with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02139 USA (e-mail: ryu@mit.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2010.2044282

is necessary to investigate how the gate and drain bias stresses affect the I-V characteristics.

The bias-stress effect has also been reported in a-Si:H thin-film transistors (TFTs) and has been studied for decades [12]–[17]. In a-Si:H TFTs, the bias-stress effect is commonly described in terms of a threshold voltage shift. The threshold voltage shift is attributed to the trapping of channel carriers in electronic states, which are created by bias stress [12]. Carriers trapped in these states remain trapped until the defect states are thermally annealed out of the device [13]. In contrast, organic TFTs (OTFTs) normally do not require thermal anneal to reverse the bias-stress-induced changes [6].

In this paper, we study the bias-stress effect in pentacene OTFTs, taking advantage of the framework set by the a-Si:H TFT literature. The studied transistors have patterned gates and use parylene as the gate dielectric. The devices have subpicoampere gate leakage current. Similar to a-Si:H TFTs, the bias-stress effect in OTFTs can be described in terms of the shift in applied gate voltage for a given current  $\Delta V$ . We derive an empirical equation that models  $\Delta V$  for various stress conditions in source–gate bias ( $V_{\rm SG}$ ) and source–drain bias ( $V_{\rm SD}$ ). Measurements show that  $\Delta V$  saturates at a certain voltage independent of the stress  $V_{\rm SG}$ , contrary to what has been reported for a-Si:H TFTs [13], [16]. A model based on a carrier trapping rate equation suggests that this  $\Delta V$  saturation phenomenon is due to the small density of trap sites compared to the channel carriers.

## II. EXPERIMENTAL

Pentacene OTFTs were fabricated on a 4-in glass wafer (Schott D-263 borosilicate float glass) in a class-100 clean room. The wafer was first cleaned in a solution of sulfuric acid and hydrogen peroxide. A gate layer of 10-nm-thick chromium (for adhesion) and 60-nm-thick gold was e-beam evaporated and patterned by photolithography and wet chemical etching. A 175-nm-thick layer of parylene-N deposited by hot-filament chemical vapor deposition was used as the gate dielectric. Via holes were patterned in parylene by photolithography and reactive ion etching (RIE) in oxygen. A layer of 40-nm-thick gold, which serves as the source/drain layer, was then deposited by e-beam evaporation. Photolithography and wet chemical etching were used to pattern the layer. An 18-nm-thick pentacene film (Luminescence Technology) was blanket deposited by thermal evaporation at a rate of 0.9 nm/min. The pentacene was then encapsulated in a 200-nm-thick film of parylene-N,

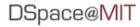

Fig. 1. (a) Photo and the cross-sectional schematic of the device. (b) Output characteristics and (c) transfer characteristics of a 1000/5-µm device.

allowing the pentacene/parylene stack to be photolithographically processed without exposing the pentacene to solvents. A subsequent RIE process defined islands of parylene and pentacene, isolating the active area of each OTFT. More details on processing can be found in [18]. Fig. 1(a) shows a photo of the completed transistor and a schematic of the cross section. Fig. 1(b) and (c) shows the measured output and transfer characteristics of a 1000/5- $\mu$ m device, respectively. The mobility of the completed OTFTs was 0.03 cm<sup>2</sup>/Vs. The devices were stored in nitrogen ambient, and no change in the *I*–*V* characteristics was measured over a month of storage.

## **III. MEASUREMENT AND RESULTS**

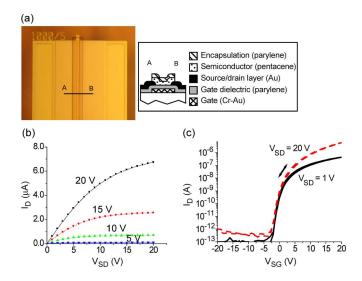

To avoid extrinsic degradation mechanisms in OTFTs [11], measurements were done in nitrogen ambient in the dark using an Agilent 4156C semiconductor parameter analyzer on a Signatone S-250 wafer prober with a temperature-controlled chuck. All the measurements were done on fresh  $1000/5-\mu$ msize devices at 20 °C. To first analyze the effects of bias stress on the overall transfer characteristics,  $I_D - V_{SG}$  was measured at  $V_{\rm SD} = 1~{\rm V}$  for  $-2 < V_{\rm SG} < 30~{\rm V}$  with a step size of 0.1 V on a fresh device. Bias stress was applied for a set time, and the I-V transfer characteristics were measured again. More bias stress was applied, and subsequent transfer characteristics were taken until the desired data were gathered. The sequence of measurements was automated to minimize the error that could be induced by instrument-setting time between the measurements. Fig. 2 shows the resulting measurement for a stress  $V_{\rm SG}$  of 30 V and  $V_{\rm SD}$  of 1 V for increasing stress time. We observe that the applied stress shifts the transfer characteristics in the positive  $V_{\rm SG}$  direction and that the shape of the transfer characteristics does not appreciably change with stress time. Thus, we can describe the after-stress transfer characteristics by shifting the original transfer characteristics of the device by a voltage, which we define as  $\Delta V$ .  $\Delta V$  conveniently describes the bias-stress effect in these devices: the drain current after bias stress can be expressed as  $I_D = f(V_{SG} - \Delta V, V_{SD})$ , where

Fig. 2. Transfer characteristics after bias stress at  $V_{\rm SG} = 30$  V and  $V_{\rm SD} = 1$  V at varying stress times t. The dashed lines show the shifted transfer characteristics of the unstressed device (t = 0 s). The inset shows the semilogarithmic plot of the same data.

$I_D = f(V_{\text{SG}}, V_{\text{SD}})$  is the measured I-V characteristics from a fresh device. Fig. 2 shows the applicability of this idea by shifting the original transfer characteristics and overlaying them (dashed lines) with the transfer characteristics taken after the various stress times (solid lines). The use of  $\Delta V$  to describe the bias-stress effect is common for a-Si:H TFTs [14] and has been demonstrated on other OTFTs [9], [10]. In the following, we measure  $\Delta V$  as a function of various bias conditions and time to better understand the source of the bias-stress effect and quantify its effect on the transfer characteristics.

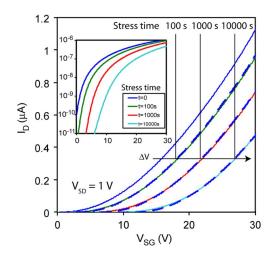

Measuring  $\Delta V$  by intermittently taking the I-V sweeps during stress measurements is unfavorable because the intermittent I-V sweeps introduce additional stress on the device. The nominally unchanging transfer characteristics shape allows us to measure the current while the device is under constant stress in the linear region and extract  $\Delta V$  information by using the prestress transfer characteristics. Such measurements of  $\Delta V$  are preferable because there is less measurement error introduced by stressing caused by the I-V sweeps. Although some error introduced by the initial I-V sweep is unavoidable, this error is relatively small as the device is held at stress conditions for less than a second. The measurements were taken for various stress  $V_{\rm SG}$  conditions. The results are shown in Fig. 3. The measured  $\Delta V$  can adequately be fitted to a stretched-exponential equation, i.e.,

$$\Delta V(t) = \Delta V_{\text{FINAL}} \left\{ 1 - \exp\left(-(t/\tau)^{\beta}\right) \right\}$$

(1)

where t is the stress time,  $\Delta V_{\text{FINAL}}$  is the voltage at which  $\Delta V$  converges, and  $\tau$  and  $\beta$  are fit parameters. The fit parameters are given in Table I.

The stress  $V_{\rm SG}$  was kept at a maximum of 40 V as the effects of gate dielectric breakdown were observed at higher voltages. The measured  $\tau$  and  $\beta$  are similar to measurements in other pentacene transistors in [10] ( $\beta \sim 0.4, \tau \sim 10^4$  s) and [11] ( $\beta \sim 0.28, \tau \sim 10^4$  s) and comparable to other organic semiconductors and a-Si:H TFTs [9], [16]. With the exception of stress  $V_{\rm SG}$  of 40 V near the breakdown voltage of the gate

Fig. 3. Time dependence of the induced  $\Delta V$  for various gate bias-stress conditions. Each stress condition has 50 data points per decade. The solid black lines, representing the stretched-exponential fit made to the data, are plotted on top of the data.

TABLE I FIT PARAMETERS TO DIFFERENT  $V_{\rm SG}$  Stress Conditions in the Stretched-Exponential Model

| Stress V <sub>SG</sub> (V) | $\Delta V_{FINAL}(V)$ | $\tau(s)$ | β    |

|----------------------------|-----------------------|-----------|------|

| 20                         | 14                    | 55000     | 0.43 |

| 25                         | 14                    | 12000     | 0.43 |

| 30                         | 14                    | 3900      | 0.44 |

| 35                         | 14                    | 1400      | 0.44 |

| 40                         | 14.5                  | 440       | 0.46 |

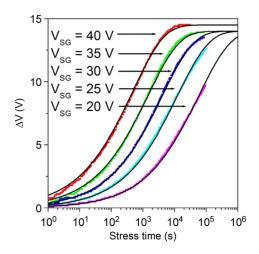

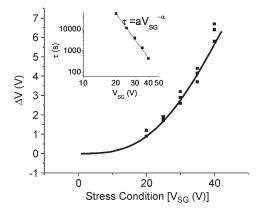

dielectric, it is notable that the  $\Delta V_{\rm FINAL}$  is not dependent of the stress gate bias. This is attributed to the fact that the channel carriers are not the limiting factor in saturating  $\Delta V$ for the measured devices. Further explanation on this point is made in Section IV. It is also notable that  $\tau$  decreases as  $V_{\rm SG}$ increases. To express  $\tau$  as a function of the gate bias,  $\tau$  versus  $V_{\rm SG}$  is plotted on a log-log scale in the inset of Fig. 4. By using  $\tau = aV_{\rm SG}^{-\alpha}$ , where  $a = 5.3 \times 10^{13}$  sV<sup> $\alpha$ </sup> and  $\alpha = 6.9$ , an adequate fit can be made. With this knowledge, (1) is expressed as an explicit function of  $V_{\rm SG}$ , i.e.,

$$\Delta V(t) = \Delta V_{\rm FINAL} \left\{ 1 - \exp\left(-\left(t/aV_{\rm SG}^{-\alpha}\right)^{\beta}\right) \right\}$$

(2)

where a,  $\alpha$ , and  $\beta$  are independent of  $V_{\rm SG}$ . Equation (2) is used to produce the solid line in Fig. 4, which plots  $\Delta V$ after 100 s of stress at different stress  $V_{\rm SG}$  measurements. To verify this equation, measured  $\Delta V$  data for different stress  $V_{\rm SG}$ measurements on multiple devices are also plotted in Fig. 4. A good fit to the measured data is produced.

The dependence of  $\Delta V$  on the drain bias is measured next. We observe that, as the drain bias during stress increases, the resulting  $\Delta V$  decreases, as shown in Fig. 5(a). It is notable that, while the current increases from zero at  $V_{\rm SD} = 0$  V to tens of microamperes at  $V_{\rm SD} = 30$  V, the  $\Delta V$  from bias stress decreases, indicating that neither the current nor hot carriers are the direct cause of  $\Delta V$ .

The  $V_{\rm SD}$  dependence can be explained by the conjecture that the  $\Delta V$  is caused by the channel carriers. The charge in the

Fig. 4.  $\Delta V$  versus stress  $V_{\rm SG}$  at t = 100 s. The  $V_{\rm SD}$  during stress was held at 1 V. Each stress condition was repeated three times, each time on a fresh device. The solid line is  $\Delta V$  predicted by (2). (Inset) Log–log plot of  $\tau$  versus  $V_{\rm SG}$ .

Fig. 5. (a)  $\Delta V$  versus stress  $V_{\rm SD}$  at t=600 s. The  $V_{\rm SG}$  during stress was held at 30 V. The induced  $\Delta V$  decreases with increasing  $V_{\rm SD}$ . (b) Data replotted in normalized charge.  $Q/Q_0$  was calculated with (3). The solid line represents a linear fit.

channel with a varying drain bias can be approximated by the following equation [17]:

$$Q = \frac{2C_i WL}{3} \frac{(V_{\rm SG} - V_{T0})^3 - (V_{\rm DG} - V_{T0})^3}{(V_{\rm SG} - V_{T0})^2 - (V_{\rm DG} - V_{T0})^2}$$

(3)

where  $C_i$  is the normalized capacitance of the dielectric, W and L are the width and length of the active layer, respectively, and  $V_{T0}$  is the initial threshold voltage. As  $V_{SD}$  increases, the accumulation charge density at the drain decreases, resulting in less charge in the channel.

Karim et al. [17] have first proposed for a-Si:H TFTs that the  $\Delta V$  for different drain biases can be modeled by multiplying the right-hand side of (2) by  $(Q/Q_0)$ , where  $Q_0$  is the charge in the channel with  $V_{SD} = 0$  V, which is  $WLC_i(V_{SG} - V_{T0})$ . The method was extended to OTFTs on SiO<sub>2</sub> by Zan and Kao [10]. We verify that the correction factor works well for the measured devices as well. Fig. 5(b) shows that the measured  $\Delta V$  at different  $V_{\rm SD}$  measurements linearly scales with  $Q/Q_0$ . Q was calculated using  $V_{T0} = 0$  V. We acknowledge that it is difficult to accurately measure a true  $V_{T0}$  because the devices are operating in accumulation mode, and there is a large number of traps located in the semiconductor or at the interface. The value of  $V_{T0}$  can be extracted from a semilog transfer characteristics plot in Fig. 1(c) by fitting a line to the slope in the subthreshold region. The uncertainty in  $V_{T0}$  is small compared to the stress  $V_{SG}$ , which is 30 V.

By combining the results from different stress  $V_{\rm SG}$  and  $V_{\rm SD}$  measurements, we can express  $\Delta V$  in terms of the stress  $V_{\rm SG}$  and  $V_{\rm SD}$ , i.e.,

$$\Delta V(t) = (Q/Q_0) \Delta V_{\text{FINAL}} \left\{ 1 - \exp\left(-\left(t/a V_{\text{SG}}^{-\alpha}\right)^{\beta}\right) \right\}$$

(4)

where a,  $\alpha$ ,  $\beta$ , and  $\Delta V_{\text{FINAL}}$  are independent of  $V_{\text{SG}}$  and  $V_{\text{SD}}$ , and Q and  $Q_0$  are calculated from (3).

### **IV. DISCUSSION**

In the previous section, we explored the empirical modeling of  $\Delta V$  with the stretched-exponential model under various bias-stress conditions. In this section, we derive the stretchedexponential equation from a simple trapping rate equation that offers physical insight into the cause of  $\Delta V$  and the interpretation of the fit parameters.

We assume that the  $\Delta V$  is caused by carriers being trapped in trap sites. To model this process, we define p to be the initial channel carrier density,  $p_T(t)$  to be the density of trapped carriers, and  $N_T$  to be the density of trap sites in the channel. p is used because pentacene is a hole transport semiconductor. p and  $N_T$  are fixed with respect to time, and  $p_T$  is a function of time. More specifically,  $p = C_i(V_{\text{SG}} - V_{T0})/q$ , where  $V_{T0}$  is 0 V, as defined in the previous section, and  $p_T(0) = 0$ .  $\Delta V$  can be expressed in terms of the trapped carriers. If all the traps are assumed to be at the semiconductor/dielectric interface

$$\Delta V = q p_T / C_i. \tag{5}$$

In order for carriers to be trapped, there needs to be both a free carrier and an empty trap. The rate equation that accounts for the trapping process can be written as follows:

$$dp_T/dt = k(p - p_T)(N_T - p_T)$$

(6)

where k is the rate constant. The term in the first bracket is the density of free carriers remaining in the device, and the term in the second bracket is the density of empty traps. It has been shown that, for an exponential distribution of barrier energy for traps, the rate constant k can be a function of time, where  $k = \beta k' t^{(\beta-1)}$ ,  $\beta < 1$  [15]. The rate of trapping decreases with time,

which can be physically related to the fact that, as traps with shorter time constants are filled, the time constants associated with the remaining empty traps are longer, resulting in a lower rate constant.

The differential equation (6) solved with the application of the boundary condition  $p_T(0) = 0$  yields

$$p_T(t) = \frac{pN_T \left(1 - \exp\left((p - N_T)k't^{\beta}\right)\right)}{N_T - p\exp\left((p - N_T)k't^{\beta}\right)}.$$

(7)

For  $N_T < p$ , (7) can be simplified, and when inserted into (5), it results in the following equation for  $\Delta V$ :

$$\Delta V(t) = \frac{qN_T}{C_i} \left( 1 - \exp\left(-(p - N_T)k't^\beta\right) \right) \tag{8}$$

which is in the form of a stretched exponential. By comparing (8) with (1), we can infer that  $\Delta V_{\text{FINAL}} = qN_T/C_i$ , which is independent of  $V_{\text{SG}}$ . In addition  $\tau$  in (1) can be related to the rate of trapping by  $1/\tau^{\beta} = (p - N_T)k'$ .

Similarly, for  $N_T > p$ , (7) can be simplified to result in

$$\Delta V(t) = \frac{qp}{C_i} \left( 1 - \exp\left(-(N_T - p)k't^\beta\right) \right) \tag{9}$$

which is also in the stretched-exponential form, but  $\Delta V_{\text{FINAL}} = qp/C_i$  and now depends on the channel carrier density p.  $p = C_i(V_{\text{SG}} - V_{T0})/q$ , and thus,  $\Delta V_{\text{FINAL}} = V_{\text{SG}} - V_{T0}$ .

For the measured OTFTs at stress  $V_{\rm SG}$  ranging from 20 to 35 V, we assume that  $N_T < p$  because  $\Delta V_{\rm FINAL}$  is independent of  $V_{\rm SG}$ . The assumption of  $N_T < p$  is also self-consistent with the observation that  $\Delta V_{\rm FINAL} < V_{\rm SG} - V_{T0}$ . In the measured OTFTs, the  $\Delta V$  saturates at 14 V, independent of  $V_{\rm SG}$  because the trap sites are exhausted before the channel carriers. In contrast, for stress  $V_{\rm SG} < 14$  V, it has been verified that  $\Delta V_{\rm FINAL} = V_{\rm SG} - V_{T0}$ , as predicted by the model for the case  $N_T > p$ . The  $\Delta V_{\rm FINAL}$  also saturates at  $V_{\rm SG} - V_{T0}$  for a-Si:H TFTs [13], [14], as a-Si:H TFTs are always stressed in the region  $N_T > p$ . This is expected in a-Si:H TFTs as the trap sites are created as the weak bonds within the a-Si:H are broken [12].

The measured OTFTs have  $C_i = 15 \text{ nF/cm}^2$ , and for the measured  $\Delta V_{

m FINAL}$  of 14 V,  $N_T$  is calculated to be 1.3 imes $10^{12}$  cm<sup>-2</sup>. This range of  $N_T$  is reasonable considering that the density of interface states in metal-oxide-semiconductor fieldeffect transistors is in the range of  $10^9 - 10^{12}$  cm<sup>-2</sup> [19]. The calculated  $N_T$  is also reasonable considering that the density of pentacene molecules at the interface is on the order of  $10^{14}$  cm<sup>-2</sup> and is greater than the density of defects. It is difficult to compare  $N_T$  with the results from other TFTs as this is the first report of  $\Delta V_{\text{FINAL}}$  that is independent of  $V_{\text{SG}}$ . Even so, if a comparison is to be made, the lower bounds for  $N_T$ in other works can be calculated by using the maximum  $\Delta V$ measured and using  $p_T = \Delta V \times C_i/q$ . Since there are enough traps to accommodate this  $p_T$ , the calculated  $p_T$  serves as a lower bound for  $N_T$ . Compared to this  $N_T$ , the  $N_T$  extracted from the OTFTs used in this paper is still lower, as shown in Table II. This low  $N_T$  may be attributed to the parylene dielectric and encapsulation, which provide low interface states with pentacene and protection from reactive O<sub>2</sub> and H<sub>2</sub>O during processing steps, respectively.

TABLE  $\,$  II  $\,$  N  $_{T}$  Calculated From This Paper and the Literature

| Semiconductor                         | Max<br>ΔV (V) | C <sub>i</sub><br>(F/cm <sup>2</sup> ) | $(\text{cm}^{-2})$   | Ref.         |

|---------------------------------------|---------------|----------------------------------------|----------------------|--------------|

| Pentacene on<br>Parylene              | 14            | 1.5×10 <sup>-8</sup>                   | $1.3 \times 10^{12}$ | This<br>work |

| PTAA on SiO <sub>2</sub>              | 19            | 1.9×10 <sup>-8</sup>                   | $2.3 \times 10^{12}$ | [9]          |

| T6 on SiO <sub>2</sub>                | 16            | $1.9 \times 10^{-8}$                   | $1.8 \times 10^{12}$ | [21]         |

| Pentacene on<br>AlO <sub>x</sub> /SAM | 0.8           | 7×10 <sup>-7</sup>                     | $3.5 \times 10^{12}$ | [22]         |

| a-Si on SiN                           | 40            | 1×10 <sup>-8</sup>                     | $2.5 \times 10^{12}$ | [23]         |

From the measurements, it is unclear whether the traps are located in the semiconductor, the semiconductor/ dielectric interface, or the dielectric. However, the long time for the bias-stress effect to settle indicates a slow trapping rate. Such a slow trapping rate suggests that there is a barrier for the carriers to be trapped. One possible mechanism is the trapping of carriers in traps located in the gate dielectric near the semiconductor/dielectric interface. The carriers are trapped via hopping into these states. Such a mechanism was proposed by Libsch and Kanicki for a-Si:H TFTs [13].

Another possible mechanism is the detrapping of electrons trapped in the semiconductor [11]. This mechanism explains the observed bias-stress effect by detrapping electrons that are initially trapped in the semiconductor gap states. The application of a negative bias on the gate electrode (positive  $V_{\rm SG}$ ) repels electrons trapped in the channel and detraps them. The drain current decreases as the number of extra holes that balanced the trapped electrons decreases. Although such mechanism explains the long time constant for the bias-stress effect to settle, we would expect a fast recovery of the original I-V characteristics when the stress is removed. However, it has been observed by Mathijssen *et al.* that time constants related to recovery are comparable to the bias-stress effect [9].

In polymer TFTs, bipolaron formation has been proposed for the cause of the slow channel carrier trapping [20]. The  $\Delta V$ dependence on  $V_{\rm SG}$  is cubic for short stress times as  $\alpha \times \beta$ in (2) is approximately 3. Although this observation excludes the bipolaron formation as the possible mechanism, a similar mechanism that involves three carriers for a formation of lower energy state may explain the slow trapping behavior. The exact mechanism causing the bias-stress effect remains elusive, and more research in the trapping mechanism in organic semiconductors will greatly enhance the understanding of the bias-stress effect.

### V. CONCLUSION

The bias-stress effect on pentacene OTFTs with patterned gates and parylene gate dielectric has been studied. The measured devices did not exhibit any measurable degradation due to storage. The bias-stress effect has been quantified in terms of  $\Delta V$ , which is the shift in gate bias voltage for a given current after bias stress.  $\Delta V$  has been measured for various stress conditions and times, and it has been found that the stretched-exponential equation can accurately model the measured  $\Delta V$ . An equation that models  $\Delta V$  for different stress  $V_{\rm SG}$  and  $V_{\rm SD}$  measurements has been presented and verified. It has been found that the current is not the cause of the bias-stress effect. The rate equation that describes the rate of channel carrier trap-

ping provides physical relevance to the fitting parameters used in the empirical stretched-exponential equation. In particular, the rate equation suggests that  $\Delta V_{\rm FINAL}$ , which is the value that  $\Delta V$  converges to, is independent of the stress gate bias due to a relatively small density of trap sites compared to the density of channel carriers. Possible mechanisms for the bias-stress effect are discussed. Further improvement in the bias-stress effect is anticipated in these devices, considering that they have not been optimized to enhance stability.

## ACKNOWLEDGMENT

This paper was carried out in part through the use of the Microsystems Technology Laboratories, Massachusetts Institute of Technology.

#### REFERENCES

- Y. Kato, T. Sekitani, M. Takamiya, M. Doi, K. Asaka, T. Sakurai, and T. Someya, "Sheet-type Braille displays by integrating organic fieldeffect transistors and polymeric actuators," *IEEE Trans. Electron Devices*, vol. 54, no. 2, pp. 202–209, Feb. 2007.

- [2] L. Zhou, A. Wang, S.-C. Wu, J. Sun, S. Park, and T. N. Jackson, "Allorganic active-matrix flexible display," *Appl. Phys. Lett.*, vol. 88, no. 8, p. 083 502, Feb. 2006.

- [3] I. Nausieda, K. Ryu, I. Kymissis, A. I. Akinwande, V. Bulovic, and C. G. Sodini, "An organic active-matrix imager," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 527–532, Feb. 2008.

[4] T. Someya, Y. Kato, T. Sekitani, S. Iba, Y. Noguchi, Y. Murase,

- [4] T. Someya, Y. Kato, T. Sekitani, S. Iba, Y. Noguchi, Y. Murase, H. Kawaguchi, and T. Sakurai, "Conformable, flexible, large-area networks of pressure and thermal sensors with organic transistor active matrixes," *Proc. Nat. Acad. Sci.*, vol. 102, no. 8, pp. 12321–12325, Aug. 2005.

- [5] S. J. Zilker, C. Detcheverry, E. Cantatore, and D. M. de Leeuw, "Bias stress in organic thin-film transistors and logic gates," *Appl. Phys. Lett.*, vol. 79, no. 8, pp. 1124–1126, Aug. 2001.

- [6] D. Knipp, R. A. Street, A. Volkel, and J. Ho, "Pentacene thin film transistors on inorganic dielectrics: Morphology structural properties, and electronic transport," J. Appl. Phys., vol. 93, no. 1, pp. 347–355, Jan. 2003.

- [7] T. Miyadera, S. D. Wang, T. Minari, K. Tsukagoshi, and Y. Aoyagi, "Charge trapping induced current instability in pentacene thin film transistors: Trapping barrier and effect of surface treatment," *Appl. Phys. Lett.*, vol. 93, no. 3, p. 033 304, Jul. 2008.

- [8] K. Suemori, S. Uemura, M. Yoshida, S. Hoshino, N. Takada, T. Kodzasa, and T. Kamata, "Influence of fine roughness of insulator surface on threshold voltage stability of organic field-effect transistors," *Appl. Phys. Lett.*, vol. 93, no. 3, p. 033 308, Jul. 2008.

- [9] S. Mathijssen, M. Colle, H. Gomes, E. Smits, B. de Boer, I. McCulloch, P. Bobbert, and D. M. de Leeuw, "Dynamics of threshold voltages shifts in organic and amorphous silicon field-effect transistors," *Adv. Mater.*, vol. 19, no. 19, pp. 2785–2789, Oct. 2007.

- [10] H.-W. Zan and S.-C. Kao, "The effects of drain-bias on the threshold voltage instability in organic TFTs," *IEEE Electron Device Lett.*, vol. 29, no. 2, pp. 155–157, Feb. 2008.

- [11] G. Gu, M. G. Kane, and S.-C. Mau, "Reversible memory effects and acceptor states in pentacene-based organic thin-film transistors," J. Appl. Phys., vol. 101, no. 1, p. 014 504, Jan. 2007.

- [12] M. J. Powell, S. C. Deane, and R. B. Wehrspohn, "Microscopic mechanisms for creation and removal of metastable dangling bonds in hydrogenated amorphous silicon," *Phys. Rev. B, Condens. Matter*, vol. 66, no. 15, p. 155 212, Oct. 2002.

- [13] F. R. Libsch and J. Kanicki, "Bias-stress-induced stretched-exponential time dependence of charge injection and trapping in amorphous thin-film transistors," *Appl. Phys. Lett.*, vol. 62, no. 11, pp. 1286–1288, Mar. 1993.

[14] M. J. Powell, C. van Berkel, and J. R. Hughes, "Time and temperature

- [14] M. J. Powell, C. van Berkel, and J. R. Hughes, "Time and temperature dependence of instability mechanisms in amorphous silicon thin-film transistors," *Appl. Phys. Lett.*, vol. 54, no. 14, pp. 1323–1325, Apr. 1989.

[15] A. Kuo, T. K. Won, and J. Kanicki, "Advanced amorphous silicon thin-

- [15] A. Kuo, T. K. Won, and J. Kanicki, "Advanced amorphous silicon thinfilm transistors for AM-OLEDs: Electrical performance and stability," *IEEE Trans. Electron Devices*, vol. 55, no. 7, pp. 1621–1629, Jul. 2008.

- [16] W. B. Jackson, J. M. Marshall, and M. D. Moyer, "Role of hydrogen in the formation of metastable defects in hydrogenated amorphous silicon," *Phys. Rev. B, Condens. Matter*, vol. 39, no. 2, pp. 1164–1179, Jan. 1989.

- [17] K. S. Karim, A. Nathan, M. Hack, and W. I. Milne, "Drain-bias dependence of threshold voltage stability of amorphous silicon TFTs," *IEEE Electron Device Lett.*, vol. 25, no. 4, pp. 188–190, Apr. 2004.

- [18] I. Kymissis, A. I. Akinwande, and V. Bulovic, "A lithographic process for organic field-effect transistors," *J. Display Technol.*, vol. 1, no. 2, pp. 289– 294, Dec. 2005.

- [19] J. D. Plummer, M. D. Deal, and P. B. Griffin, *Silicon VLSI Technology Fundamentals, Practice and Modeling.* Upper Saddle River, NJ: Prentice-Hall, 2000, p. 353.

- [20] A. Salleo and R. A. Street, "Kinetics of bias stress and bipolaron formation in polythiophene," *Phys. Rev. B, Condens. Matter*, vol. 70, no. 23, p. 235 324, Dec. 2004.

- [21] F. Di Girolamo, C. Aruta, M. Barra, P. D'Angelo, and A. Cassinese, "Organic film thickness influence on the bias stress instability in sexithiophene field effect transistors," *Appl. Phys. A: Mater. Sci. Process.*, vol. 96, no. 2, pp. 481–487, Aug. 2009.

- [22] U. Zschieschang, R. Weitz, K. Kern, and H. Klauk, "Bias stress effect in low-voltage organic thin-film transistors," *Appl. Phys. A: Mater. Sci. Process.*, vol. 95, no. 1, pp. 139–145, Apr. 2009.

- [23] B. Hekmatshoar, K. Cherenack, S. Wagner, and J. Sturm, "Amorphous silicon thin-film transistors with DC saturation current half-life of more than 100 years," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

**Kevin Kyungbum Ryu** (S'00) received the B.S. degree in electrical engineering from the Cooper Union for the Advancement of Science and Art, New York, NY, in 2003 and the M.S. and Ph.D. degrees in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, in 2005 and 2009, respectively.

He is currently with the Microsystems Technology Laboratories, Massachusetts Institute of Technology. His current research interests include the processing and characterization of devices using novel materials

such as graphene, organic, and metal-oxide thin-film transistors.

**Ivan Nausieda** (S'00) was born in Milwaukee, WI, in 1982. He received the B.S. degree in electrical and computer engineering from Carnegie Mellon University, Pittsburgh, PA, in 2004, the M.S. degree in applied physics from Harvard University, Cambridge, MA, in 2005, and the Ph.D. degree in electrical engineering from the Massachusetts Institute of Technology, Cambridge, in 2009.

He is currently with the Microsystems Technology Laboratories, Massachusetts Institute of Technology. He is interested in the commercialization of organic

thin-film transistors.

**David Da He** (S'08) received the B.A.Sc. degree in electrical engineering in 2005 from the University of Toronto, Toronto, ON, Canada, and the S.M. degree in electrical engineering in 2008 from the Massachusetts Institute of Technology, Cambridge, where he is currently working toward the Ph.D. degree in electrical engineering with the Microsystems Technology Laboratories.

His current research interests include organic integrated circuits and biomedical electronics

Akintunde Ibitayo (Tayo) Akinwande (S'81– M'86–SM'04–F'08) received the B.Sc. degree in electrical and electronic engineering from the University of Ife, Ife, Nigeria, in 1978 and the M.S. and Ph.D. degrees in electrical engineering from Stanford University, Stanford, CA, in 1981 and 1986, respectively.

During 1986, he was with Honeywell Inc., where he was initially engaged in research on GaAs complementary FET technology for very high-speed signal processing and, later, on pressure sensors,

Prof. Akinwande is a member of the Materials Research Society, the Society of Information Display, and the Electrochemical Society. He is the recipient of the 1996 National Science Foundation CAREER Award. He was on the Technical Program Committees for various conferences, including the Device Research Conference, the International Electron Devices Meeting, the International Solid-State Circuits Conference, the International Display Research Conference, and the International Vacuum Microelectronics Conference.

**Vladimir Bulović** received the B.S.E. and Ph.D. degrees from Princeton University, Princeton, NJ, in 1991 and 1998, respectively.

He is an Associate Professor of electrical engineering with the Massachusetts Institute of Technology (MIT), Cambridge, leading the Organic and Nanostructured Electronics Laboratory, codirecting the MIT-ENI Solar Frontiers Center and the MIT Solar Revolutions Project, and leading the MIT Energy Studies Minor. He founded QD Vision, Inc., Watertown, MA, which is focused on development

of quantum dot optolectronics, and Kateeva, Inc., Menlo Park, CA, which is focused on development of printed organic electronics. He is the author of 90 publications and the holder of 45 U.S. patents in the areas of organic and nanostructured light-emitting diodes, lasers, photovoltaics, photodetectors, chemical sensors, and programmable memories. His research interests include studies of physical properties of organic and organic/inorganic nanocrystal composite thin films and structures and the development of novel optoelectronic organic and hybrid nanoscale devices.

**Charles G. Sodini** (M'82–SM'90–F'95) received the B.S.E.E. degree from Purdue University, West Lafayette, IN, in 1974 and the M.S.E.E. and Ph.D. degrees from the University of California, Berkeley, in 1981 and 1982, respectively.

From 1974 to 1982, he was a member of the Technical Staff with Hewlett-Packard Laboratories, where he worked on the design of MOS memory. Since 1983, he has been with the Massachusetts Institute of Technology, Cambridge, where he is currently the LeBel Professor of Electrical Engineering

with the Microsystems Technology Laboratories. Along with Prof. Roger T. Howe, he is a coauthor of an undergraduate text on integrated circuits and devices entitled *Microelectronics: An Integrated Approach*. He was a cofounder of SMaL Camera Technologies, a leader in imaging technology for consumer digital still cameras and machine vision cameras for automotive applications. He also studied the Hong Kong/South China electronics industry in 1996–1997 and has continued to study the globalization of the electronics industry. His research interests are focused on mixed-signal integrated circuit and systems with emphasis on analog, RF, and millimeter-wave circuit design.

Dr. Sodini has served on a variety of IEEE Conference Committees, including the International Electron Device Meeting, where he was the 1989 General Chairman. He has served on the IEEE Electron Devices Society Administrative Committee and was the President of the IEEE Solid-State Circuits Society from 2002 to 2004. He is currently the Chair of the Executive Committee for the VLSI Symposia.