# Biasing Circuits for Voltage Controlled GSM Power Amplifiers

André van Bezooijen<sup>1</sup>, Dima Prikhodko<sup>1</sup> and A.H.M. van Roermund<sup>2</sup>

<sup>1</sup>Philips Semiconductors, Gerstweg 2, 6534 AE Nijmegen, The Netherlands <sup>2</sup>Eindhoven University of Technology, Den Dolech 2, 5600 MB Eindhoven, The Netherlands

*Abstract* — In GSM phones voltage controlled power amplifiers are used to vary the output power. Inaccuracies in output power levels are predominantly caused by drift in PA gain over temperature and input power. In this paper we present biasing circuits that implement an inherently accurate gain control curve. These circuits are based on temperature stabilised V/I-converters and current mirrors. Applying current driven biasing of the first RF-stage reduces the input power dependency of the gain. Measurements show an order of magnitude less drift in PA gain over temperature variations and about a factor five smaller drift over input power variations. The proposed circuits relax the dynamic range and stability requirements on the power control loop and they will help making phone output power calibrations redundant.

### I. INTRODUCTION

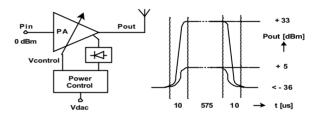

The main function of a GSM power amplifier (PA) is to amplify an incoming RF signal by a controllable amount to deliver the required in-burst output power accurately according to the GSM protocol. This might seem trivial but combining this with the many specifications on out-of-burst power, spurious emission, power added efficiency, stability, noise, ruggedness, cost and size makes it very challenging [1,2]. For meeting all these specifications the PA has to be embedded in a power control loop (see Figure 1). The output power, detected by an integrated sensor, is compared to a programmable reference value *Vdac*. The amplified and integrated error signal *Vcontrol* controls the gain of the PA by adjusting the bias currents of the RFstages.

This power control loop serves two main purposes. Firstly, it keeps in-burst output power levels of the phone constant over many varying parameters like ambient and PA mounting base temperatures, input power delivered by the modulator, battery supply voltage, operating frequency and process spreads. Thus, the loop compensates for drift in PA gain. Secondly, it provides a smooth ramp-up and ramp-down of the output power to limit spurious emission due to output power transitions. Power control loop design criteria on output power accuracy, on loop stability and on ramp-up and ramp-down speed are contradicting. To meet system requirements under all extremes it is, in spite of the use of such a loop, often necessary to calibrate phone output power levels.

Fig. 1. A power control loop is used to set the PA output power levels accurately and to provide smooth power ramp-up and ramp-down.

An alternative method to set the output power of a GSM phone accurately makes use of a series regulator in the PA supply. It determines the output power by adjusting the voltage headroom of the final stage that consequently operates in saturation over a wide power range. A disadvantage of this method is the relatively large size of the series regulator that is needed to minimise its power losses. A second limitation of this gain control method is its incompatibility with Edge-mode operation that requires good PA linearity. This approach will not be considered further.

There are two main causes for drift in PA gain: temperature drift of the bias currents and gain expansion of the class-A/B RF-stages.

Until the early nineties many GSM power amplifier modules were implemented with discrete components. And even today often relatively simple, discrete like, biasing circuit topologies are used in which the biasing current is determined by a control voltage applied to resistors in series with one of two base-emitter junctions. Due to the base-emitter voltage (Vbe) temperature coefficient of -2mV/°C such circuits tends to be rather temperature dependent. RF power amplifier stages are traditionally biased for class-A/B operation. They are voltage driven at the base and draw additional DC current under the influence of RF excitation. Consequently, the gain of such a voltage driven class-A/B amplifier stage depends on its DC-biasing level as well as on the amount of RF excitation at its input. It results in an expansion of the gain, which is so characteristic for this type of class-A/B stages.

In order to overcome these two major limitations of conventional biasing circuits, the circuits described below are based on cancellation of *Vbe* combined with current driven biasing of the first RF-stage. They are making use of a feed forward concept that is inherently accurate. DC-biasing methods with feedback loops have been avoided because loop stability is of major concern due to the large in-band as well as out-of-band impedance variations that are encountered in GSM PAs.

### II. BIASING OF RF LINE-UP

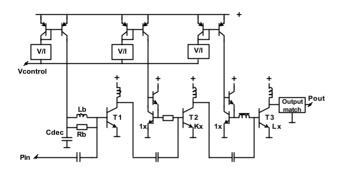

In GSM PAs it is common practice to use a cascade of voltage controlled variable gain stages to vary the output power [4]. Each stage provides a part of the total gain curve that covers more than 45dB of dynamic range in total. The take-over-points between the stages have to be chosen carefully otherwise bumps in the control curve will occur which hampers smooth ramp-up and ramp-down.

Fig. 2. GSM PA RF line-up with V/I-converters to determine the gain control curve by current driven biasing of the first RF -stage and voltage driven biasing of the 2<sup>nd</sup> and 3<sup>rd</sup>.

Figure 2 shows the RF line-up that we implemented to demonstrate feasibility of the proposed biasing circuits. *Vcontrol* is applied to the three voltage-to-current (V/I) converters that are controlling, via PNP current mirrors, the bias current of each of the three RF-stages. The first RFstage TI is current driven at its base via a resistor Rb and coil Lb in parallel. Rb provides, via the decoupling capacitor Cdec, for a relatively constant input VSWR even when the PA is shut off. Lb is used to improve the low frequency noise match of *T1* because its low frequency base shot noise is converted into the Rx-band by the input signal due to non-linearity of the first RF-stage. For a constant input power of 0dBm the operation of T1 changes from class-C, characterised by its relatively small current conducting angle, up to about class-A when Vcontrol increases. Adjusting the base bias current, a method that shows much similarity to gain control of a differential stage by varying its tail current, controls the output power, and thus the gain. Base current biasing prevents gain expansion and makes the first stage output power insensitive to the variation of input power that is typically in the range of -3to +3dBm. Moreover, because self-biasing of the first stage

is prohibited the PA can better be turned off, which is beneficial for meeting isolation specs and makes the PA less prone to slope variations in the control curve at output power levels far below 0dBm.

The applied base current and its current multiplication factor  $\beta$  thus determine the collector current of *T1*. To make the collector current independent on  $\beta$  the biasing circuit of the first RF-stage could be provided with a  $\beta$  compensation circuit that divides the V/I-converter output current by  $\beta$ before applying it to the PNP-mirror. Although simulations indicated improvements in gain accuracy, we did not implement such a  $\beta$  compensation circuit in hardware.

A major disadvantage of base current driven biasing is the reduction in breakdown voltage of the RF-transistor. Due to the high ohmic source resistance collector-base avalanche currents are amplifier by the RF-transistor itself, which limits its effective breakdown voltage to BVceo; about 6V for the process we is used for implementation. This prohibits usage of base current driven biasing of, for instance, the final stage where large collector voltages, up to about 18V, can occur under antenna mismatch conditions. Fortunately, the output power of the first RFstage turns out to be sufficiently independent of its input power and therefore there is no need for current driven biasing of the successive RF-stages.

The biasing circuits that interface with the second and third RF-stage are classic NPN current mirrors with base current compensation [5]. They provide accurate biasing even when the current mirror ratio of the RF-transistor and its reference transistor is large. Due to their low output impedance they can, under strong RF-excitation, deliver large base currents to the self-biasing RF-stages.

The actual PA gain control curve is defined by the three V/I-converters. They are based on very well know silicon IC design techniques that allow for implementation of well defined transfer functions as described in the section below.

# III. V/I-CONVERTER

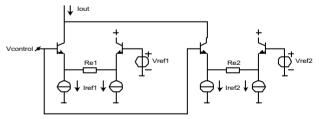

The biasing current of each of the three RF-stages is set by means of a non-linear V/I-converter, as shown in Figure 3. The converter consists of two parallel linearised differential pairs with a common single-ended output current *Iout* to interfaces with the single-ended PNP current mirror.

Fig. 3. Circuit concept of a semi-balanced non-linear V/Iconverter that determines the gain control curve of an RF-stage.

They make use of a stabilised reference voltage *Vstab* and stabilised bias currents *Iref1* and *Iref2*. Their balanced topology results in a cancellation of *Vbe* in the voltage to current transfer function and makes them supply voltage independent. The reference voltages *Vref1* and *Vref2* are implemented as fractions *M* and *N* of the common 2.8V stabilised voltage *Vstab* by means of resistive voltage dividers such that  $V_{ref1} = V_{stab} / M$  and  $V_{ref2} = V_{stab} / N$  hold true. The bias currents *Iref1* and *Iref2* are derived from the same *Vstab* and temperature stabilised resistors *R1* and *R2* (not shown) according to the equations  $I_{ref1} = V_{stab} / R_1$  and  $I_{ref2} = V_{stab} / R_2$ . The V/I-converter output current can be expressed as the sum of the output currents from each differential pair.

$$I_{out} = \frac{2*I_{ref1}}{1 + \exp(-\frac{V_{control} - V_{ref1} - V_{RE1}}{V_T})} + \frac{2*I_{ref2}}{1 + \exp(-\frac{V_{control} - V_{ref2} - V_{RE2}}{V_T})}$$

(1)

in which Vt is the thermal voltage kT/q that equals about 26mV at room temperature and  $V_{RE1}$  and  $V_{RE2}$  are the voltages across the emitter degeneration resistances that linearise the transconductance of each differential pair. From (1) it can be derived that a 1% opening of the first differential pair occurs at:

$$V_{control} = V_{stab} * \frac{1}{M} - V_{stab} * \frac{RE_1}{R_1} - 5 * V_t$$

(2)

which is a function of the stabilised reference voltage, resistor ratios and the thermal voltage Vt. The opening point is just slightly temperature dependent due to the relatively small temperature coefficient of  $0.1 \text{mV/}^{\circ}\text{C}$  in Vt. For  $V_{control} = V_{refl}$  the differential pair is fully in balance and thus  $I_{out}$  equals  $I_{refl}$  that is fully temperature independent. Similarly, a 99% opening of the first differential pair can be derived to occurs at:

$$V_{control} = V_{stab} * \frac{1}{M} + V_{stab} * \frac{RE_1}{R_1} + 5 * V_t$$

(3)

The output current almost equals 2\*Iref1, which also has only a weak dependency on Vt.

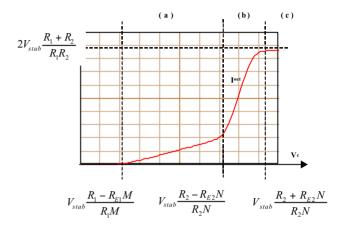

With two differential pairs in parallel a control curve, like depicted in Fig. 4 as used to bias the third RF-stage, can now be realised with accurately defined opening and deflection points. Three distinct regions, (a), (b) and (c), are visible. In region (a) the V/I-converter opens the RFtransistor gradually. The biasing of the third RF-stage determines the PA slope at medium output power levels. In region (b) the RF-excitation of the third RF-stage increases rapidly due to increased gain of the proceeding stages. To allow for sufficient self-biasing to occur, the bias current is increased steeply. At the end of the control curve (region c) the PA comes in power saturation and therefore there is no need for further increase of the bias current. Biasing control of the  $1^{st}$  and  $2^{nd}$  stage are realised in a similar manner.

Fig. 4. The opening points as well as the deflection points of the RF-transistor biasing current are well defined by resistor ratios and a stabilised voltage.

# IV. MEASUREMENT RESULTS

The RF-transistors and their biasing circuits have been implemented in a silicon bipolar MMIC as part of a prototype triple-band GSM/Edge power amplifier module. The chosen circuit topology, however, allows for partitioning of PA functions over various IC-technologies. For optimum RF performance, for instance, one or more RF-stages and their reference transistors could be implemented in GaAs HBT, whereas the V/I-converters and PNP mirrors can be implemented in silicon.

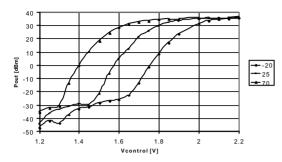

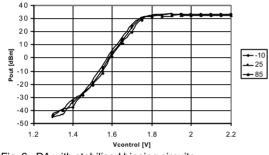

Evaluation is done on an 1800MHz line-up and compared to results on modules that make use of conventional biasing circuits at 900MHz. Measurements, shown in Figure 5 and 6, depict control curve drift of a PA based on conventional biasing circuits and of a PA with the biasing circuits as described in this paper. Both line-ups meet their maximum output power spec of 35dBm and 32dBm respectively. Conventional biasing circuits give more than 40dB drift in output power when ambient temperature varies from -20 to +70 °C. The PA with stabilised biasing circuits drifts about 5dB over a similar temperature range. For 0dBm output power this corresponds to a reduction in variation of *Vcontrol* from more than 350mV to less than 30mV.

Fig. 5. PA with conventional biasing circuits. Pin = 0dBm, f = 900MHz. T = -20, 25, 70°C

Fig. 6. PA with stabilised biasing circuits. Pin = 0dBm, f = 1800MHz. T = -10, 25, 85°C

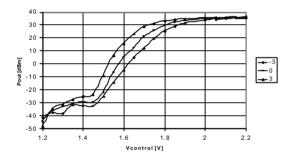

Fig. 7. PA with conventional voltage driven  $1^{st}$  RF-Stage. T = 25°C, f = 1800MHz. Pin = -3, 0, 3dBm

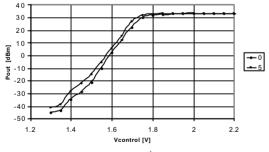

Fig. 8. PA with current driven  $1^{st}$  stage. T = 25°C, f = 1800MHz. Pin = 0, 5dBm

In Figure 7 and 8 measurement results are shown on output power variations caused by input power variations. The control curve of the PA with conventional biasing circuits shows a maximum drift of more than 20dB over 6 dB input power variation. The PA with current driven first RF-stage shows a 5dB change in output power over 5dB of change in input power. For 0dBm output power the variation in *Vcontrol* reduces from more than 100mV to approx. 20mV. Obviously, the gain expansion has been reduced significantly. Moreover, the measured curves indicate that PA isolation is improved and slope variations at very low output power are reduced.

## V. CONCLUSIONS

In this paper we presented biasing circuits for voltage controlled GSM power amplifiers that are inherently accurate and robust. They make use of semi-balanced nonlinear V/I-converters and current mirrors that can well be implemented in low cost silicon IC technology. It is demonstrated that PA temperature drift is reduced an order of magnitude. Applying bias current control of the first RFstage reduces the input power dependency of the gain with of factor of five. Applying these biasing circuit techniques reduces requirements on power control loop circuitry and will help to make phone output power calibrations redundant.

#### REFERENCES

- E. Jarvinen, "GaAs HBT power amplifier with smooth gain control characteristics", Proceedings of the 1998 IEEE Radio and Wireless Conference, pp 321 – 324.

- [2] P. Baltus and A. van Bezooijen, "Design Considerations for RF Power Amplifiers demonstrated through a GSM/EDGE Power Amplifier Module" AACD 2001 Noordwijk, The Netherlands.

- [3] D. Prikhodko, R. Burdenski, P Lok, F. van Straten, U. Maurer, J.Cairo, "Power amplifier with integrated power control loop". 32<sup>nd</sup> European Microwave Conference 2002.

- [4] K. Yamamoto, T.Asada, S.Suzuki, T.Miura, A.Inoue, S.Miyakuni, J.Otsuji, R.Hattori, Y.Miyazaki and T.Shimura, "A GSM/EDGE Dual-Mode, 900/1800/1900-MHz Triple-Band HBT MMIC Power Amplifier Module", 2002 IEEE RFIC Symp. pp 245 – 248.

- [5] E. Jarvinen, S. Kalajo, M. Matilainen, Bias Circuits for GaAs HBT Power Amplifiers", 2001 IEEE MTT-S Microwave Symp. Dig., vol. 1, pp 507 – 510.

- [6] Paul R. Gray and Robert G. Meyer, "Analysis and Design of Analog Integrated Circuits", pp.227 – 230, 3rd edition.