Received February 4, 2020, accepted February 20, 2020, date of publication February 24, 2020, date of current version March 3, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.2976003

# **Bidirectional Three-Level Stacked Neutral-Point-Clamped Converter for Electric Vehicle Charging Stations**

FRANCISCO EVERTON UCHÔA REIS<sup>®1</sup>, RENÉ PASTOR TORRICO-BASCOPÉ<sup>®1</sup>, FERNANDO LESSA TOFOLI<sup>®2</sup>, AND LUIZ DANIEL SANTOS BEZERRA<sup>®3</sup>

<sup>1</sup>Department of Electrical Engineering, Federal University of Ceará, Fortaleza 60020-181, Brazil

Corresponding author: Francisco Everton Uchôa Reis (evertonsx@gmail.com)

This work was supported by CAPES (Coordenação de Aperfeiçoamento de Pessoal de Nível Superior), CNPq (Conselho Nacional de Desenvolvimento Científico e Tecnológico), FAPEMIG (Fundação de Amparo a Pesquisa do Estado de Minas Gerais), and INERGE (Instituto Nacional de Ciência e Tecnologia em Energia Elétrica).

**ABSTRACT** Electric vehicles (EVs) powered by batteries and other energy storage devices (ESDs), e.g., ultracapacitors, are expected to play an important role in the development of a more sustainable future. In this context, charging stations (CSs) are supposed to become the main sources of energy for charging the batteries, being strongly dependent on power electronic converters. This paper analyzes a bidirectional single-phase, three-level stacked neutral-point-clamped (3L-SNPC) converter for CS applications, which may behave as a rectifier or an inverter depending on the power flow direction. Besides, the derived analysis can be easily extended to the development of a three-phase version. Considering that the CS is capable of integrating the utility grid and renewable energy sources, it is possible to absorb or inject energy into the ac grid with high power factor and reduced harmonic content of the current. The main advantages of the bidirectional topology are the existence of a three-level voltage waveform across each leg and the neutral point, while filtering requirements are reduced when compared with typical two-level structures used in EV CSs; the voltage stresses on all semiconductors are equal to half of the total dc-link voltage; power factor is nearly unity in any operation mode; and the voltages across the dc-link capacitors are balanced. The thorough design of the power and control stages is presented, as well as experimental results from a laboratory prototype are discussed in detail.

**INDEX TERMS** Bidirectional converters, charging stations, electric vehicles, resonant controller.

#### I. INTRODUCTION

Considering the imminent need to reduce the greenhouse gas emissions, as well the eventual depletion of fossil fuels, it is expected that internal combustion engine vehicles (ICEVs) will be replaced by electric vehicles (EVs) in a near future. The widespread use of EVs is also inserted in a more complex scenario involving microgrids and the smart grid concept, thus bringing major challenges to many research fields [1], [2].

Being an eco-friendly choice for transportation, plugin electric vehicles (PEVs) equipped with batteries can be employed as both mobile energy storage devices (ESDs) and generators capable of supplying the energy demand of

The associate editor coordinating the review of this manuscript and approving it for publication was Venkateshkumar  $M^{\Box}$ .

buildings if necessary [3]. In this context, fast and reliable charging is an essential feature that must be taken into account for the successful large-scale utilization of EVs [4]. This process also depends on distinct aspects, e.g., a equisition cost and technological evolution of ESDs, charging algorithms, infrastructure in terms of existing charging stations (CSs), among others [5].

The practical implementation of CS topologies relies strongly on power electronic converters considering that battery chargers can be directly supplied by either a common do link in do microgrids or indirectly through ac-do converters connected to the ac mains [6]. A thorough review on the state-of-the-art of CSs for EVs is presented in [7], being classified as off-board and on-board. It is clearly evidenced that the wide availability of CSs may lead to reduced energy storage requirements and costs associated with on-board chargers.

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, Federal University of São João del-Rei, São João del-Rei 36307-352, Brazil

<sup>&</sup>lt;sup>3</sup>Department of Industry, Federal Institute of Education Science and Technology of Ceará, Maracanaú 61939-140, Brazil

Thus, the development of off-board topologies based on several energy sources is of great interest since batteries can be charged more quickly [8].

The work developed in [9] proposes a two-stage CS configuration composed of a three-phase interleaved boost rectifier and a bidirectional three-level asymmetrical dc-dc converter. In this case, the dimensions of the filter elements required by the front-end stage are reduced owing to the interleaved operation. In order to minimize the complexity of the control system implementation in the front-end stage, a singlestage architecture employing a 24-pulse thyristor rectifier is suggested in [10] as a possible solution to minimize the harmonic content of the ac input current, although a bulky low-frequency phase-shift transformer is required. An interleaved ac-dc boost converter cascaded with an isolated dc-dc full-bridge topology based on a high-frequency transformer is also described in [11] as a prominent solution to achieve reduced size, weight, and volume. It is worth mentioning that high efficiency results since the switching losses in the active switches of the dc-dc converter operate under zero voltage switching (ZVS) condition. The use of wide-bandgap semiconductors in EV CSs is also addressed in [12], in which gallium nitride (GaN) and silicon (Si) semiconductors are paralleled in order to achieve both superior switching performance and affordable cost associated with high-current capability in a hybrid approach.

The integration of renewable energy sources with CS topologies is also an interesting choice. For instance, photovoltaic (PV) modules can be used to provide part of the energy required to charge the EVs, thus contributing to the minimization of power system loading. The batteries can be charged by either the modules or the utility grid, or even by both sources simultaneously. Besides, part of the generated power can be injected into the grid depending on the load demand. For instance, the architecture introduced in [13] consists of a PV CS based on a three-phase hybrid converter, which integrates an isolated dc-dc converter and a three-phase inverter for grid connection with low component count, but only few results obtained from a small-scale prototype are presented and discussed. A Z-source inverter (ZSI) is also employed in [14] as a solution to reduce the number of conversion stages in a PV-based approach, being this topology able to provide voltage boost and dc-ac power conversion.

This work proposes an architecture of EV CS based on the integration of distinct energy sources, i.e., PV modules and the utility grid. A bidirectional power converter, which is capable of operating as a rectifier or an inverter, is also described in detail as part of this structure. It is also worth mentioning that SAE J1772 standard defines two charging levels: AC Level 1 (120 Vac with currents ranging from 12 A to 16 A) and AC Level 2 (208-240 Vac for currents up to 80 A). In this context, the analyzed converter is classified as AC Level 1.

In order to preserve power quality indices associated with the ac grid, proportional plus resonant (PR) control is employed so that it is possible to regulate the dc-link voltage and also emulate the behavior of a resistive load by imposing a nearly sinusoidal waveform to the current. A detailed design procedure is presented and an experimental prototype is developed to evaluate the converter performance and validate the theoretical assumptions.

#### **II. PROPOSED TOPOLOGY**

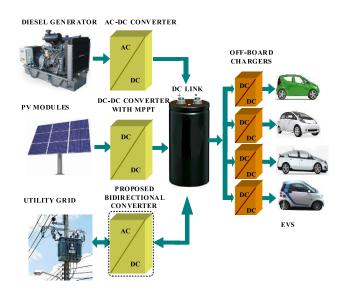

Fig. 1 shows the block diagram of a possible CS architecture, which relies on the use of renewable energy sources, the conventional ac grid to charge the batteries, and a backup power source represented by a diesel generator. Dc-dc converters are associated with each set of PV modules to supply power to a common dc link, which is responsible for charging the EVs. Good design flexibility exists while aggregating distributed energy resources and ESDs to the system, which are essentially related to dc currents and voltages and do not demand synchronization with the ac grid or cause reactive power flow. Another potential application lies in the possibility to supply distinct loads in residential and industrial environments, e.g., lamps, electric ovens, and universal motors, which can be directly connected to the symmetrical dc link with rated voltages of 230 V or 460 V without using battery chargers. The number of conversion stages can be reduced as a consequence, thus implying higher efficiency. Otherwise individual battery chargers can be employed to provide distinct dc voltage levels to several loads.

FIGURE 1. EV CS integrating the ac utility grid, PV modules, and a diesel generator.

It can be seen that a bidirectional power converter must also be used to control the grid current according to the energy demand. Many topologies can be chosen for this purpose, e.g., a bidirectional two-phase interleaved converter [15]. However, the voltage stress across the switches is equal to the dc-link voltage, what may lead to the use of metal oxide semiconductor field effect transistors (MOSFETs) with high voltage ratings and cost. In this case, conduction losses will

increase as a consequence since such semiconductors typically present high drain-source on-resistance.

Other suitable topologies for CS applications can also be found in the literature. A three-phase three-level neutral point clamped (3L-NPC) inverter is presented in [16], which employs 12 active switches. Besides, the capacitor voltage unbalance is of major concern and requires the use of complex and costly control schemes. According to [17], the three-level neutral stacked point clamped (3L-SNPC) and the three-level active stacked neutral point clamped (3L-ASNPC) inverters introduced in [18] and [19], respectively, present improved performance over traditional 3L-NPC ones due to the increase of the apparent switching frequency and better total loss balancing. The authors also propose a modified 3L-SNPC structure based on the use of insulated gate bipolar transistors (IGBTs) associated with only two MOSFETs operating at high frequency to minimize the switching losses. A similar configuration is also analyzed in [20]. Unfortunately, the component count in [17], [20] is still high when compared with the 3L-SNPC inverter.

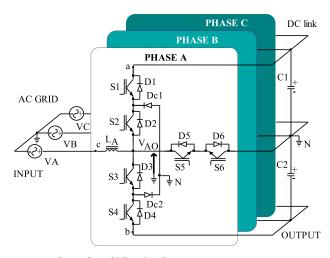

It is also worth mentioning that the topologies presented in [17]–[20] do only perform ac-dc power conversion and bidirectional versions of the aforementioned converters were not presented so far. Considering good tradeoffs between the number of components and efficiency, the 3L-SNPC structure proposed in [18] was adopted to provide bidirectional power flow capability, resulting in the structure shown in Fig. 2. Besides, it allows charging independent batteries or even injecting power into the ac grid in EV CS applications, what was not investigated so far in the literature.

**FIGURE 2.** Three-phase bidirectional 3L-SNPC converter.

The proposed bidirectional converter is composed of clamping diodes  $D_{c1}...D_{c6}$ ; active switches  $S_1...S_{18}$  and their respective body diodes  $D_1...D_{18}$ ; storage inductors  $L_A...L_C$ ; dc-link capacitors  $C_1$  and  $C_2$ ; ac voltage sources  $V_A$ ,  $V_B$ ,  $V_C$  corresponding to the phase voltages; and a dc voltage source that represents the dc link so that it is possible to evaluate the capability to provide bidirectional power flow. For this purpose, only phase A is analyzed as shown in Fig. 2,

considering that the cell was formerly introduced in [18]. In this case, three control loops are required to shape the currents through the inductors, balance the voltages across the capacitors, and regulate the dc-link voltage, resulting in bidirectional power flow capability and high power factor.

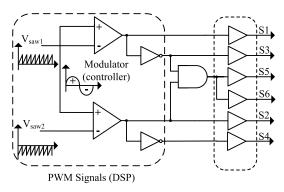

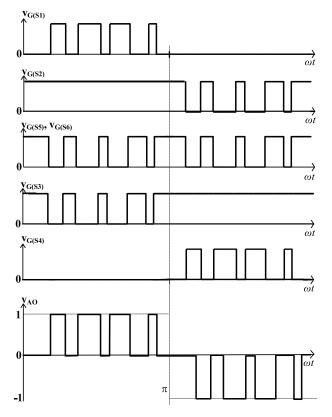

The phase-disposition sinusoidal pulse width modulation (PD-SPWM) is typically employed in NPC-based topologies [21]. However, this technique must be modified in the case of the converter shown in Fig. 2 in order to provide bidirectional power flow. This is why  $S_5$  and  $S_6$  have been added to the converter, behaving as a bidirectional switch for this purpose. Since the dc link is composed of two capacitors  $C_1$  and  $C_2$ , two carriers are necessary as represented in Fig. 3. In this case, only two switches are allowed to be on at the same time, while the remaining ones remain off according to Fig. 4. Switches  $S_1$  and  $S_2$  are only turned on when the modulator is greater than the carrier  $V_{saw1}$  during the positive half cycle. Otherwise, switches  $S_3$  and  $S_4$  will be turned on when the modulator is less than the carrier  $V_{saw2}$  during the negative half cycle. Analogously, switches  $S_5$  and  $S_6$  will be driven together when switches  $S_1$  and  $S_4$  are simultaneously off.

FIGURE 3. PD-SPWM and generation of the drive signals.

## III. DESIGN EXAMPLE

Table 1 summarizes the specifications used in the design of the power stage elements considering a single-phase version of the 3L-SNPC topology. It is also worth mentioning that the converter is designed to process one third of the total power required by its three-phase counterpart.

#### A. PRELIMINARY CALCULATION

Parameter  $\alpha$  corresponds to the ratio between the peak grid voltage and half of the total output voltage, i.e.:

$$\alpha = \frac{\sqrt{2} \cdot V_A}{(V_o/2)} = \frac{\sqrt{2} \cdot 127}{(460/2)} = 0.78 \tag{1}$$

The peak grid current  $I_{Apk}$  is given by:

$$I_{Apk} = \frac{\sqrt{2} \cdot P_o}{\eta \cdot V_A} = \frac{\sqrt{2} \cdot 2000}{0.97 \cdot 127} = 22.95 A$$

(2)

The average output current  $I_o$  is:

$$I_o = \frac{P_o}{V_o} = \frac{2000}{460} = 4.35 \,\text{A}$$

(3)

**FIGURE 4.** Drive signals of switches  $S_1 \dots S_6$ .

**TABLE 1.** Design specifications for the single-phase version of the converter.

| Parameter               | Specification         |

|-------------------------|-----------------------|

| Rms grid voltage        | $V_A = 127 \text{ V}$ |

| Grid frequency          | $f_{\rm g}$ =60 Hz    |

| Total dc-link voltage   | $V_o = 460 \text{ V}$ |

| Output power            | $P_o=2 \text{ kW}$    |

| Switching frequency     | $f_s$ =25 kHz         |

| Input voltage variation | ±20%                  |

| Theoretical efficiency  | $\eta = 97\%$         |

#### **B. BOOST INDUCTOR**

The boost inductance is given by

$$L_A = \frac{(V_o/2)}{4 \cdot f_s \cdot \Delta I_{\text{max}}} = \frac{(460/2)}{4 \cdot 25 \cdot 10^3 \cdot 4.59} = 501 \mu \text{H} \quad (4)$$

where  $\Delta I_{max}$  is the maximum peak-to-peak ripple of the inductor current.

In this case,  $L_A = 500 \,\mu\text{H}$  is adopted.

# C. STRESSES ON THE ACTIVE SWITCHES

The maximum voltages across all switches correspond to half of the total dc-link voltage, i.e.:

$$V_{S1...S6(\text{max})} = \frac{V_o}{2} = \frac{460}{2} = 230\text{V}$$

(5)

When the converter operates in rectifier mode, the currents through switches  $S_1$  and  $S_4$  are null. On the other hand,

the average and rms currents through  $S_2$ ,  $S_3$ ,  $S_5$ , and  $S_6$  are given by (6) and (7), respectively.

$$I_{S2,S3,S5,S6(avg)} = I_{Apk} \cdot \frac{1}{2} \cdot \left(\frac{1}{\pi} - \frac{\alpha}{4}\right)$$

$$= 22.95 \cdot \frac{1}{2} \cdot \left(\frac{1}{\pi} - \frac{0.78}{4}\right) = 1.42A \quad (6)$$

$$I_{S2,S3,S5,S6(rms)} = I_{Apk} \cdot \frac{1}{2} \sqrt{\left(\frac{1}{4} - \frac{2 \cdot \alpha}{3 \cdot \pi}\right)}$$

$$= 22.95 \cdot \frac{1}{2} \sqrt{\left(\frac{1}{4} - \frac{2 \cdot 0.78}{3 \cdot \pi}\right)} = 3.34A \quad (7)$$

However, when the converter operates in inverter mode, the average and rms currents through  $S_1$  and  $S_4$  are given by:

$$I_{S1,S4(avg)} = I_{Apk} \cdot \frac{\alpha}{4} = 22.95 \cdot \frac{0.78}{4} = 4.47A$$

(8)

$$I_{S1,S4(rms)} = I_{Apk} \cdot \sqrt{\frac{2 \cdot \alpha}{3 \cdot \pi}} = I_{Apk} \cdot \sqrt{\frac{2 \cdot \alpha}{3 \cdot \pi}} = 9.33 \text{A}$$

(9)

# D. STRESSES ON THE ANTIPARALLEL DIODES OF THE ACTIVE SWITCHES

The reverse voltage across all diodes is:

$$V_{A\_D1...D6(PIV)} = \frac{V_o}{2} = \frac{460}{2} = 230 \text{ V}$$

(10)

The average and rms currents through  $D_5$ ,  $D_6$ ,  $D_{c1}$ , and  $D_{c2}$  are given by (11) and (12), respectively.

$$I_{D5,D6,Dc1,Dc2(avg)} = I_{Apk} \cdot \frac{1}{2} \cdot \left(\frac{1}{\pi} - \frac{\alpha}{4}\right)$$

$$= 22.95 \cdot \frac{1}{2} \cdot \left(\frac{1}{\pi} - \frac{0.78}{4}\right) = 1.42A$$

$$I_{D5,D6,Dc1,Dc2(rms)} = I_{Apk} \cdot \frac{1}{2} \sqrt{\left(\frac{1}{4} - \frac{2 \cdot \alpha}{3 \cdot \pi}\right)}$$

$$= 22.95 \cdot \frac{1}{2} \sqrt{\left(\frac{1}{4} - \frac{2 \cdot 0.78}{3 \cdot \pi}\right)} = 3.34A$$

(12)

The average, rms, and peak currents through the antiparallel diodes  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$  are obtained from (13), (14), and (15), respectively.

$$I_{A\_D1...D4(avg)} = \frac{I_{Apk} \cdot \alpha}{4} = 4.47 \,\text{A}$$

(13)

$$I_{A\_D1...D4(rms)} = I_{Apk} \cdot \sqrt{\frac{2 \cdot \alpha}{3 \cdot \pi}} = 9.33 \,\text{A}$$

(14)

$$I_{A\_D1...D4(pk)} = I_{Apk} \cdot = 22.95 \,\text{A}$$

(15)

#### E. OUTPUT FILTER CAPACITORS

Capacitors  $C_1$  and  $C_2$  are responsible for keeping the dc-link voltage constant, being determined as:

$$C_1 = C_2 \ge \frac{P_o \cdot \Delta t}{2 \cdot (V_o^2 - V_{o(\min)}^2)} = \frac{2000 \cdot 8.33 \cdot 10^{-3}}{2 \cdot (230^2 - 225.4^2)}$$

= 3.98 mF (16)

where  $\Delta t$  is the hold-up time and  $V_{o(\min)}$  is the minimum value assumed by the dc-link voltage.

The output filter capacitors are assumed to be  $C_1 = C_2 = 3.92$  mF, represented by seven 560- $\mu$ F capacitors connected in parallel. The equivalent series resistance (ESR) of the association is  $R_{se} = 22.85$  m $\Omega$ .

#### IV. CONTROL SYSTEM

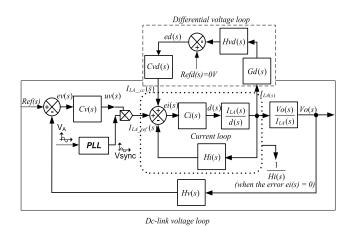

In order to achieve power factor correction (PFC), there are some consolidated techniques available in the literature, e.g., one cycle control [22] and average current mode control [23]. The PR control has the ability to track a sinusoidal reference, resulting in null steady-state error, while Fig. 5 shows the block diagram that represents the implementation of such approach. It can be seen that three loops are required to keep high power factor, minimized harmonic content of the grid current, regulated dc-link voltage, and balanced voltages across the output filter capacitors.

FIGURE 5. Block diagram of the control system.

The internal current loop is composed of PR controller  $C_i(s)$ , which is designed from the classical proportional-integral (PI) controller and modifies the control signal d(s) properly so that the input current is nearly sinusoidal and remains in phase with the grid voltage. On the other hand, the external voltage loop employs controller  $C_v(s)$ , which provides the current loop with a sinusoidal reference signal to be imposed to the current so that the dc-link voltage remains regulated. Finally, the differential voltage loop is represented by controller  $C_{vd}(s)$ , being responsible for keeping the voltages across capacitors  $C_1$  and  $C_2$  balanced as desired. In fact, the controller adds a small dc component to the reference signal of the current loop for this purpose. The detailed design procedure for such controllers is presented in the forthcoming sections employing the K factor as described in [24].

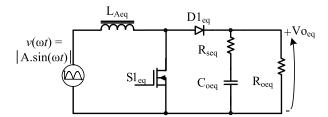

Table 2 defines the main parameters for the design of the current loop. Besides, according to [25], the equivalent circuit shown in Fig. 6 can be employed to simplify the small-signal modeling of the 3L-SNPC converter. Subscript "eq" is adopted for the representation of the converter elements in terms of equivalent components in the

TABLE 2. Parameters employed in the current loop design.

| Parameter                                                     | Specification                    |

|---------------------------------------------------------------|----------------------------------|

| Peak-to-peak voltage associated with the sawtooth carriers    | $V_d$ =5 V                       |

| Pulse width modulator gain<br>Hall-effect current sensor gain | $F_m(s)=0.2$<br>$K_{hall}=0.001$ |

| Shunt resistance connected to the current sensor output       | $R_{shuntx}$ =100 $\Omega$       |

| Inductor current gain                                         | $H_i(s) = 0.1 \text{ V/A}$       |

FIGURE 6. Equivalent circuit of the proposed converter used in the control system design.

circuit, i.e., inductor  $L_{A(eq)}$ ; switch  $S_{1(eq)}$ ; diode  $D_{1(eq)}$ ; output filter capacitor  $C_{o(eq)}$  and its respective ESR  $R_{se(eq)}$ ; and load resistor  $R_{o(eq)}$ . From the design specifications of the original converter, the equivalent parameters in Table 3 can be obtained.

**TABLE 3.** Parameter specifications of the equivalent converter.

| Parameter                            | Specification                                             |

|--------------------------------------|-----------------------------------------------------------|

| Rated rms input voltage              | <i>V</i> <sub>A</sub> =127 V                              |

| Range of the rms phase voltage       | $V_{A(min)} = 102 \text{ V} - V_{A(max)} = 152 \text{ V}$ |

| Ratio between the output voltages of |                                                           |

| the proposed 3L-SNPC and the         | $r_{v}=V_{o}/V_{o(eq)}=2$                                 |

| equivalent converter                 |                                                           |

| Total output voltage                 | $V_{o(eq)} = V_o/r_v = 230 \text{ V}$                     |

| Input filter inductor                | $L_{A(eq)} = L_A = 500  \mu \text{H}$                     |

| Switching frequency                  | $f_{s(eq)}=f_s=25 \text{ kHz}$                            |

| Switching period                     | $T_{s(eq)}=T_s=40 \mu s$                                  |

| Output power per phase               | $P_o=2 \text{ kW}$                                        |

| Average duty cycle                   | $D_{(eq)} = D = 0.5$                                      |

| Inductor series resistance           | $R_{\rm w}=100~{\rm m}\Omega$                             |

| Output filter capacitance            | $C_{o(eq)} = C_o \cdot r_v^2 = 15.68 \text{ mF}$          |

| ESR of the output filter capacitor   | $R_{se(eq)} = R_{se}/r_v^2 = 5.71 \text{ m}\Omega$        |

| Load resistance                      | $R_{o(eq)} = R_o / r_v^2 = 26.45 \Omega$                  |

#### A. INTERNAL CURRENT LOOP

First, it is necessary to obtain the control-to-inductor current transfer function, which is given by (17) [26].

$$G_i(s) = \frac{I_{LA}(s)}{d(s)} = \frac{(V_o/2)}{s \cdot L_A + R_w}$$

(17)

where  $R_w$  is the inductor series resistance.

In digital control systems, the time delay associated with the performed calculations  $T_d$  must be considered. This effect can be represented in terms of a simple first-order Padé approximation in the form:

$$G_d(s) = \frac{1}{T_d \cdot s + 1} \tag{18}$$

The following parameters are also considered in the design:

$$F_m(s) = V_d^{-1} \tag{19}$$

$$H_i(s) = K_{hall} \cdot R_{shunt}$$

(20)

The open-loop transfer function for the current loop can then be obtained as:

$$TFOL_{iu}(s) = F_m(s) \cdot G_i(s) \cdot G_d(s) \cdot H_i(s)$$

(21)

The PR controller is represented by the following expression:

$$C_i(s) = k_p + \frac{2 \cdot k_i \cdot \omega_c \cdot s}{s^2 + 2 \cdot \omega_c \cdot s + \omega_0^2}$$

(22)

where  $k_p$  and  $k_i$  are the proportional and integral gains, respectively; and  $\omega_c$  and  $\omega_0$  are the crossover angular frequency and resonance angular frequency, respectively.

Parameter  $k_p$  can be tuned similarly to a conventional PI controller, thus defining the dynamic behavior of the system, bandwidth, phase margin, and gain margin [27]. On the other hand, parameter  $k_i$  has little influence on the loop bandwidth and represents the controller gain. According to [27], it is possible to determine  $k_p$  and  $k_i$  from a conventional PI controller. Considering that it has one pole at the origin of the complex plane and adopting the pole and zero cancellation approach, the open-loop transfer function of the compensated loop can be simply given by:

$$TFOL_{ic}(s) = \frac{K_{PI} \cdot B}{s \cdot (s+a)}$$

(23)

where  $K_{PI}$  is the gain for the PI controller to be determined. Besides, parameters B and a are given by:

$$B = \frac{F_m \cdot H_i \cdot V_o}{T_d} \tag{24}$$

$$a = \frac{1}{T_d} \tag{25}$$

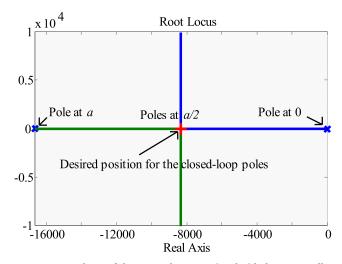

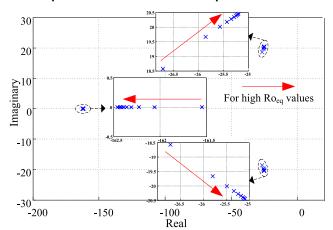

In order to obtain fast transient response without overshoot, the PI controller must be tuned so that the closed-loop poles are in the real axis and placed exactly in the middle of the root locus as shown in Fig. 7. It can then be stated that the closed-loop poles of the current loop will always be in the left half-plane, while stability is achieved for any value of  $K_{PI}$  in (23).

The value of  $K_{PI}$  that leads the poles to the same position defined as a/2 is [28]:

$$K_{PI} = \frac{a^2}{4 \cdot B} = \frac{\left(1.667 \cdot 10^4\right)^2}{4 \cdot 76666.7} = 905.73$$

(26)

According to the adopted procedure, the transfer function representing the PI controller can be written in the form:

$$C_{PI}(s) = K_{PI} \cdot \left(\frac{s \cdot L_A + R_w}{s}\right) \tag{27}$$

Thus, it is possible to calculate  $k_n$  and  $k_i$  as follows:

$$k_p = K_{PI} \cdot L_A = 0.45$$

(28)

$$k_i = K_{PI} \cdot R_w = 90.57 \tag{29}$$

FIGURE 7. Root locus of the current loop associated with the PI controller.

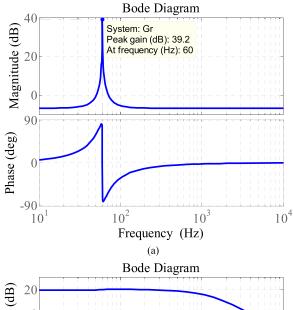

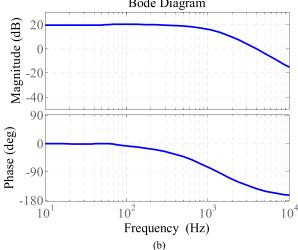

Considering  $\omega_c = 0.1$  Hz and  $\omega_0 = 2 \cdot \pi \cdot f_g = 377$  rad/s, the resulting Bode diagrams of the PR controller and the closed-loop transfer function of the compensated system are represented in Fig. 8.

Fig. 8 (a) shows that the controller gain is high at  $f_g = 60$  Hz, while the phase angle is null. In other words, the controller is able to ensure that the current remains nearly in phase with the grid current, as high power factor is obtained as a consequence. Besides, Fig. 8 (b) denotes that the current through  $L_A$  is in phase with the sinusoidal reference signal considering that the phase angle is null in this case. Besides, the gain remains constant at 20 dB for frequencies up to 1 kHz, thus providing fast response. The closed-loop response of the current loop is fast enough so that the current follows a sinusoidal reference at 60 Hz. Thus, it can be simplified in the form of  $1/H_i(s)$ , which is a constant value as represented in Fig. 8 (b).

The close-loop poles of the whole system were also determined for stability analysis purposes. Fig. 9 shows the three existing poles when  $R_{o(eq)}$  is varied. It can be stated that the system is stable when the load power varies because the poles remain in the left-half plane.

# B. EXTERNAL VOLTAGE LOOP

Since the current loop is inherently faster than the voltage one, its respective transfer function can be simplified in the form [29]:

$$A(s) = (H_i(s))^{-1} = 10$$

(30)

The gain of the Hall-effect voltage sensor manufactured by LEM is:

$$H_{\nu}(s) = 5/400 = 12.50 \cdot 10^{-3}$$

(31)

Finally, the open-loop transfer function of the voltage loop is given by:

$$TFOL_{vu}(s) = A(s) \cdot Z(s) \cdot H_v(s)$$

(32)

FIGURE 8. (a) Bode plot of the PR controller, (b) Bode plot of the closed-loop transfer function for the current loop.

**FIGURE 9.** Closed-loop poles for 10 values of  $R_{o(eq)}$ .

where Z(s) is:

$$Z(s) = \left[ (1 - D) \cdot \frac{R_{oeq} \cdot R_{seq}}{R_{oeq} + R_{seq}} \right] \cdot \left( \frac{s + \frac{1}{R_{seq} \cdot C_{oeq}}}{s + \frac{1}{C_{oeq} \cdot (R_{oeq} + R_{seq})}} \right)$$

(33)

The crossover frequency has been chosen as  $f_{cv} = f_g/6 = 10$  Hz, while the phase margin is  $60^{\circ}$ . The resulting transfer function of  $C_v(s)$  is:

$$C_{\nu}(s) = \frac{10.86 \cdot 2 \cdot \pi \cdot 2.97.}{s \cdot \left(\frac{s}{2 \cdot \pi \cdot 33.70} + 1\right)} \cdot \left(\frac{s}{2 \cdot \pi \cdot 2.97} + 1\right) \quad (34)$$

# C. DIFFERENTIAL VOLTAGE LOOP

Controlling the differential voltage is performed indirectly through the current loop, as a dc component can be added to the reference signal of the loop responsible for controlling  $I_{LA}(s)$ . Consequently, it is possible to maintain equal voltages across the dc-link capacitors even when unbalanced loads are supplied by the converter. Considering the ESRs of the capacitors, the transfer function of the inductor current to the differential voltage can be obtained as [24]:

$$Z_{d}(s) = \frac{V_{dif}(s)}{I_{LA}(s)} = \frac{0.5 \cdot R_{o} \cdot (R_{se} \cdot C_{o} \cdot s + 1)}{0.5 \cdot (R_{o} + R_{se}) \cdot C_{o} \cdot s + 1}$$

(35)

The open-loop transfer function is given by:

$$TFOL_{vdsc}(s) = A(s) \cdot Z_d(s) \cdot H_v(s)$$

(36)

The bandwidth of the differential voltage loop must be significantly narrower than the capacitor voltage ripple frequency so that the reference signal for the current loop is not distorted. Therefore, the crossover frequency is chosen as  $f_{cvd} = 5$  Hz and the phase margin is  $60^{\circ}$ , as the transfer function for controller  $C_{vd}(s)$  becomes:

$$C_{vd}(s) = \frac{0.69 \cdot 2 \cdot \pi \cdot 1.85}{s \cdot \left(\frac{s}{2 \cdot \pi \cdot 13.50} + 1\right)} \cdot \left(\frac{s}{2 \cdot \pi \cdot 1.85} + 1\right) \quad (37)$$

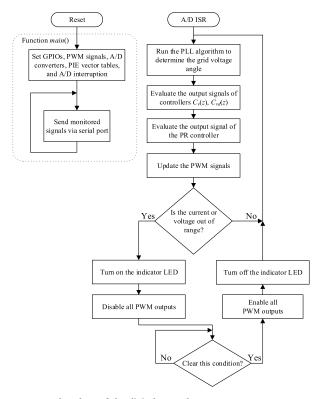

The designed analog controllers can be discretized using the bilinear transform considering that the sampling frequency is equal to the switching frequency. The resulting controllers are then embedded in a digital signal processor (DSP) so that operation with high power factor and low harmonic distortion is ensured. Fig. 10 represents the main functions of the DSP as associated with the digital control system.

#### V. EXPERIMENTAL RESULTS

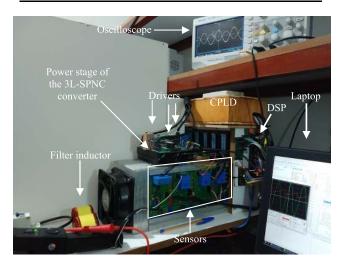

In order to validate the theoretical assumptions, a 2-kW experimental prototype was implemented and thoroughly evaluated considering the specifications given in Table 3 and the components listed in Table 4. Fig. 11 shows the experimental setup used in the tests, where the complex programmable logic device (CPLD) and DSP, drivers, power stage, laptop, among other components are evidenced. A three-phase transformer is used to provide isolation and an rms voltage of 127 V to the single-phase version of the topology assessed in the laboratory.

Protection devices, electromagnetic interference (EMI) filters, circuit breakers, and varistors are also included in the prototype. All voltage and current signals measured by the sensors are properly conditioned and filtered to mitigate noise and avoid anti-aliasing in the DSP. Besides, shielded cables are used to prevent interference in the control circuit. In order to implement the digital control system, Experimenter Kit

FIGURE 10. Flowchart of the digital control system.

TABLE 4. Components used in the experimental prototype.

| Component                                                      | Specification                 |

|----------------------------------------------------------------|-------------------------------|

| Drivers of switches $S_1S_2$ and                               | 02×2SC0108T2G0                |

| $S_3S_4$                                                       | 02/25001001200                |

| Drivers of switches $S_5$ - $S_6$                              | 01×2SC0106T2A1                |

| Switches $S_1S_6$                                              | IGBTs STGW80V60DF             |

| Diodes $D_{c1}$ , $D_{c2}$                                     | 02×30EPH06                    |

| Sensor for measuring the grid voltage and the dc-link voltages | 03×Hall-effect sensors LV25-P |

| Sensor for measuring the grid current                          | 01×Hall-effect sensors LA55-P |

FIGURE 11. Experimental setup.

associated with DSP TMS320F28335 was employed. CPLD EPM240T100C5N was adopted to generate the drive signals of switches  $S_5$  and  $S_6$ , as well as monitor the behavior of the

PWM signals and eventual failure warnings associated with the drivers.

The experimental prototype was evaluated considering the operation in both rectifier and inverter modes. A detailed discussion on the results is provided as follows.

## A. OPERATION IN RECTIFIER MODE

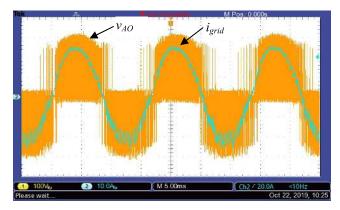

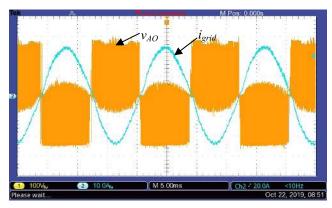

Fig. 12 shows the waveform corresponding to voltage  $v_{AO}$  as represented in Fig. 2, which has three levels as expected and is in accordance with the adopted modulation strategy.

FIGURE 12. Three-level voltage  $v_{AO}$  and phase current at the rated power condition in rectifier mode.

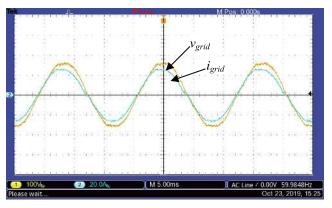

Fig. 13 presents the phase voltage and the current drawn from the grid. It can be stated that the current is sinusoidal and remains in phase with the voltage, resulting in a power factor of 0.9951 and total harmonic distortion (THD) of 2.03% considering the first 40 harmonic components.

FIGURE 13. Grid voltage and grid current at the rated power condition in rectifier mode.

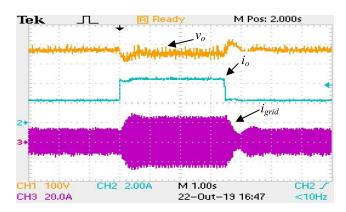

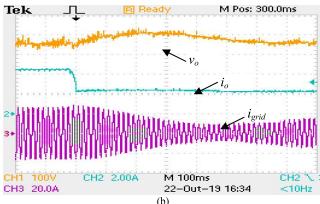

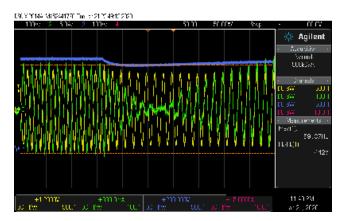

Fig. 14 shows the dynamic behavior of the converter when load steps from 50% to 100% of the rated power and viceversa occur. In either case, the dc-link voltage remains regulated at about 460 V in steady-state condition, while the grid current is nearly sinusoidal.

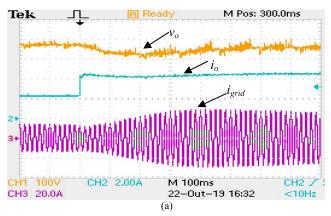

A detailed view of the output voltage and grid current during the positive and negative load steps is also provided in Fig. 15.

FIGURE 14. Behavior of the dc-link voltage and grid current during positive and negative load steps in rectifier mode.

FIGURE 15. Detailed view of the dc-link voltage and grid current in rectifier mode: (a) load step from 50% to 100% of the rated power, (b) load step from 100% to 50% of the rated power.

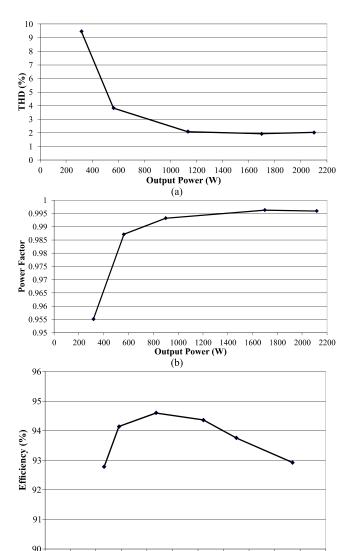

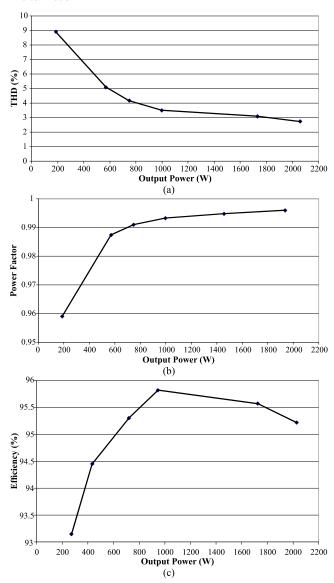

Fig. 16 shows the behavior of the current THD, power factor, and efficiency as a function of the output power, which are equal to 2.03%, 0.9951, and about 92.5% at the rated load condition, respectively. It can be stated that the harmonic distortion of the input current is low over the entire power range, while both the power factor and efficiency are high.

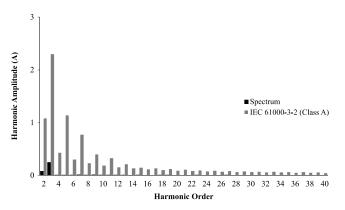

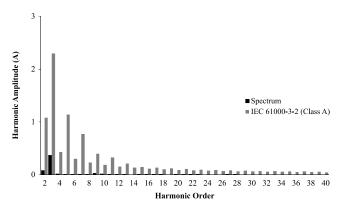

The harmonic content of the grid current at the rated load condition up to the 40<sup>th</sup> order is shown in Fig. 17. It is observed that 3<sup>rd</sup> harmonic is the most dominant component

FIGURE 16. Converter performance over a wide load range in rectifier mode: (a) THD, (b) power factor, (c) efficiency.

Output Power (W)

1000 1200 1400 1600 1800 2000 2200

200 400 600

and corresponds to 1.08% of the fundamental, i.e., 0.245 A, thus denoting that the adopted control strategy is capable of providing sinusoidal currents. Besides, all limits established by standard IEC 61000-3-2 for class A equipment are strictly respected.

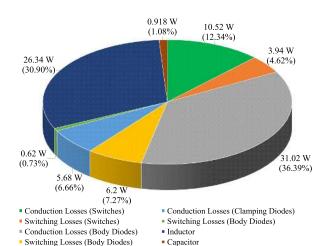

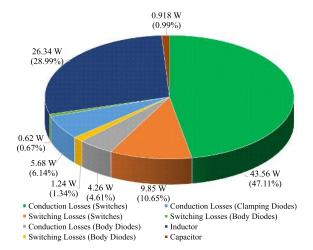

The losses in the power stage components of the single-phase topology considering the operation at the rated power are shown in Fig. 18. The overall losses are equal to 85.24 W and were determined using the methodology described in [30]–[32]. The major portions are associated with the conduction losses in the body diodes and the inductor losses.

# B. OPERATION IN INVERTER MODE

Fig. 19 presents the waveform of voltage  $v_{AO}$ , which also has three levels as a consequence of the adopted modulation

FIGURE 17. Harmonic spectrum of the grid current at the rated load condition in rectifier mode.

FIGURE 18. Loss breakdown at the rated load condition in rectifier mode.

FIGURE 19. Three-level voltage  $v_{AO}$  and phase current at the rated power condition in inverter mode.

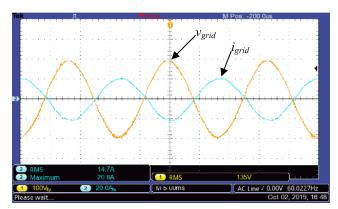

strategy, thus allowing minimizing the dimensions of inductor  $L_A$ . In inverter mode, the current is phase-shifted by 180° with respect to the grid voltage as shown in Fig. 20. The current shape is also sinusoidal, which is due to the use of a PR controller.

Fig. 21 represents the THD of the current injected into the grid, power factor, and efficiency as a function of the output power, which are lower than 3%, nearly unity, and higher

FIGURE 20. Grid voltage and grid current at the rated power condition in inverter mode.

FIGURE 21. Converter performance over a wide load range in inverter mode: (a) THD, (b) power factor, (c) efficiency.

than 95% at the rated load condition, respectively. Besides, the converter is capable of ensuring a sinusoidal shape to the current over a wide load range as expected.

Fig. 22 corresponds to the harmonic content of the grid current at the rated load condition. Once again, the most dominant component is the 3<sup>rd</sup> harmonic, being equal to 1.97% of the fundamental, i.e., 0.37 A. However, all the remaining components remain lower than 0.5%, thus demonstrating that the grid current is nearly sinusoidal. The converter operation is also in accordance with standard IEC 61000-3-2 for class A equipment.

FIGURE 22. Harmonic spectrum of the grid current at the rated load condition in inverter mode.

The loss breakdown at the rated power is also shown in Fig. 23, while the overall losses are 96.47 W in inverter mode [30]–[32]. The major portions are due to the conduction losses in the active switches and the inductor losses.

FIGURE 23. Loss breakdown at the rated load condition in inverter mode.

#### C. POWER FLOW DIRECTION

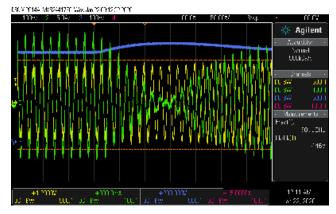

Fig. 24 presents a detailed view of the transition from inverter to rectifier mode, thus demonstrating the bidirectional power flow capability of the converter. It can be stated that the settling time of the dc-link voltage is about 300 ms, while the grid current remains nearly sinusoidal during this time interval. Besides, it takes almost eight cycles of the grid voltage so that the power flow inversion occurs.

The power flow when the converter changes from rectifier to inverter mode is shown in Fig. 25. Once again, it takes nearly 300 ms so that the dc-link voltage remains regulated in

FIGURE 24. Detailed view of the grid voltage (yellow), grid current (green), and dc-link voltage (blue) during the transition from inverter to rectifier mode.

FIGURE 25. Detailed view of the grid voltage (yellow), grid current (green), and dc-link voltage (blue) during the transition from rectifier to inverter mode.

steady-state condition. About eight cycles of the grid voltage are also required for the power flow inversion in this case.

# VI. CONCLUSION

A 3L-SNPC topology for EV CSs has been proposed in this work. Besides, a possible CS architecture is described, which allows the integration of the utility grid and renewable energy sources, e.g., PV and wind, where the energy surplus can be injected into the ac grid, thus contributing to the distributed generation scenario.

The main advantages addressed to the converter include the operation with high power factor, bidirectional power flow capability, as well as reduced current and voltage stresses on the semiconductors, which are quite important for practical applications involving off-board battery chargers. A step-by-step design procedure has been presented, which includes the power stage elements, modulation strategy, and control system.

Experimental results have demonstrated that the converter presents good performance when operating in both rectifier and inverter modes, thus justifying the choice of the PD-SPWM technique. Even though a single-phase topology has been developed, it is reasonable to state that the same

analysis can be promptly extended to a three-phase version, especially because the phases are associated with a common neutral point in wye configuration.

The transition between the operating modes occurs naturally considering that the dc-link voltage remains properly regulated and monitored by the control system. Power quality indices are maintained within acceptable levels due to the use of a PR controller, which is capable of providing a sinusoidal reference to the grid current so that it remains in phase with the voltage even at low power levels. This controller is designed based on a conventional PI counterpart, as a design methodology is described in detail.

#### **REFERENCES**

- C. Chen, L. Xiao, S. D. Duan, and J. Chen, "Cooperative optimization of electric vehicles in microgrids considering across-time-and-space energy transmission," *IEEE Trans. Ind. Electron.*, vol. 66, no. 2, pp. 1532–1542, Eab. 2010

- [2] Y. Shi, H. D. Tuan, A. V. Savkin, T. Q. Duong, and H. V. Poor, "Model predictive control for smart grids with multiple electric-vehicle charging stations," *IEEE Trans. Smart Grid*, vol. 10, no. 2, pp. 2127–2136, Mar. 2019.

- [3] Q. Yan, B. Zhang, and M. Kezunovic, "Optimized operational cost reduction for an EV charging station integrated with battery energy storage and PV generation," *IEEE Trans. Smart Grid*, vol. 10, no. 2, pp. 2096–2106, Mar. 2019.

- [4] E. Ucer, I. Koyuncu, M. C. Kisacikoglu, M. Yavuz, A. Meintz, and C. Rames, "Modeling and analysis of a fast charging sation and evaluation of service quality for electric vehicles," *IEEE Trans. Transp. Electrific.*, vol. 5, no. 1, pp. 215–225, Feb. 2019.

- [5] J. A. Domínguez-Navarro, R. Dufo-López, J. M. Yusta-Loyo, J. S. Artal-Sevil, and J. L. Bernal-Agustín, "Design of an electric vehicle fast-charging station with integration of renewable energy and storage systems," *Int. J. Electr. Power Energy Syst.*, vol. 105, pp. 46–58, Feb. 2019

- [6] M. F. Shaaban, S. Mohamed, M. Ismail, K. A. Qaraqe, and E. Serpedin, "Joint planning of smart EV charging stations and DGs in eco-friendly remote hybrid microgrids," *IEEE Trans. Smart Grid*, vol. 10, no. 5, pp. 5819–5830, Sep. 2019.

- [7] M. Yilmaz and P. T. Krein, "Review of battery charger topologies, charging power levels, and infrastructure for plug-in electric and hybrid vehicles," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2151–2169, May 2013.

- [8] Q. Cui, Y. Weng, and C.-W. Tan, "Electric vehicle charging station placement method for urban areas," *IEEE Trans. Smart Grid*, vol. 10, no. 6, pp. 6552–6565, Nov. 2019.

- [9] V. Monteiro, J. C. Ferreira, A. A. N. Meléndez, C. Couto, and J. L. Afonso, "Experimental validation of a novel architecture based on a dual-stage converter for off-board fast battery chargers of electric vehicles," *IEEE Trans. Veh. Technol.*, vol. 67, no. 2, pp. 1000–1011, Feb. 2018.

- [10] D. Zhang, H. Lin, Q. Zhang, S. Kang, and Z. Lu, "Analysis, design, and implementation of a single-stage multipulse flexible-topology thyristor rectifier for battery charging in electric vehicles," *IEEE Trans. Energy Convers.*, vol. 34, no. 1, pp. 47–57, Mar. 2019.

- [11] D. S. Gautam, F. Musavi, M. Edington, W. Eberle, and W. G. Dunford, "An automotive onboard 3.3-kW battery charger for PHEV application," *IEEE Trans. Veh. Technol.*, vol. 61, no. 8, pp. 3466–3474, Oct. 2012.

- [12] J. Lu, L. Zhu, G. Liu, and H. Bai, "Device and system-level transient analysis in a modular designed sub-MW EV fast charging station using hybrid GaN HEMTs + si MOSFETs," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 1, pp. 143–156, Mar. 2019.

- [13] A. Tazay and Z. Miao, "Control of a three-phase hybrid converter for a PV charging station," *IEEE Trans. Energy Convers.*, vol. 33, no. 3, pp. 1002–1014, Sep. 2018.

- [14] S. A. Singh, G. Carli, N. A. Azeez, and S. S. Williamson, "Modeling, design, control, and implementation of a modified Z-source integrated PV/Grid/EV DC charger/inverter," *IEEE Trans. Ind. Electron.*, vol. 65, no. 6, pp. 5213–5220, Jun. 2018.

- [15] F. Wang, Y. Luo, H. Li, and X. Xu, "Switching characteristics optimization of two-phase interleaved bidirectional DC/DC for electric vehicles," *Energies*, vol. 12, no. 3, p. 378, Jan. 2019.

- [16] D. Drennan and H. T. Mouton, "An experimental investigation into natural balancing of three level neutral point clamped multi-level inverters," in *Proc. IEEE AFRICON*. 6th Africon Conf. Afr., vol. 2, Oct. 2002, pp. 749–754 vol.2.

- [17] Y. Wang and R. Li, "Novel high-efficiency three-level stacked-neutral-point-clamped grid-tied inverter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 9, pp. 3766–3774, Sep. 2013.

- [18] D. Floricau, G. Gateau, M. Dumitrescu, and R. Teodorescu, "A new stacked NPC converter: 3L-topology and control," in *Proc. Eur. Conf. Power Electron. Appl.*, 2007, pp. 1–10.

- [19] D. Floricau, G. Gateau, and A. Leredde, "New active stacked NPC multilevel converter: Operation and features," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2272–2278, Jul. 2010.

- [20] Y. Wang and F. Wang, "Novel three-phase three-level-stacked neutral point clamped grid-tied solar inverter with a split phase controller," *IEEE Trans. Power Electron.*, vol. 28, no. 6, pp. 2856–2866, Jun. 2013.

- [21] P. Palanivel and S. S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques," *IET Power Electron.*, vol. 4, no. 8, pp. 951–958, 2011.

- [22] R. Brown and M. Soldano, "One cycle control IC simplifies PFC designs," in *Proc. 20th Annu. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, vol. 2, Mar. 2005, pp. 825–829.

- [23] W. Tang, F. C. Lee, and R. B. Ridley, "Small-signal modeling of average current-mode control," *IEEE Trans. Power Electron.*, vol. 8, no. 2, pp. 112–119, Apr. 1993.

- [24] H. D. Venable, "The K factor: A new mathematical tool for stability analysis and synthesis," in *Proc. Powercon*, 1983, p. H1-1.

- [25] G. C. Silveira, F. L. Tofoli, L. D. S. Bezerra, and R. P. Torrico-Bascope, "Analysis and small-signal modeling of a nonisolated high voltage step-up DC-DC boost converter," in *Proc. IEEE 13th Brazilian Power Electron.* Conf. 1st Southern Power Electron. Conf. (COBEP/SPEC), Nov. 2015, pp. 1–6.

- [26] L. M. Nodari, M. Mezaroba1, L. Michels, and C. Rech, "A new digital control system for a single-phase half-bridge rectifier with fast dynamic response," in *Proc. IEEE Energy Convers. Congr. Expo.*, Sep. 2010, pp. 1204–1211.

- [27] R. Teodorescu, F. Blaabjerg, M. Liserre, and P. C. Loh, "Proportional-resonant controllers and filters for grid-connected voltage-source converters," *IEE Proc. Electr. Power Appl.*, vol. 153, no. 5, pp. 750–762, 2006.

- [28] K. Ogata, Modern Control Engineering. Upper Saddle River, NJ, USA: Prentice-Hall, 2009.

- [29] N. X. Melo, R. Leão, R. Bascopé, and F. L. Antunes, "A boost converter to improve the low voltage ride-through capability of an adjustable speed drive," in *Proc. IX COBEP*, 2007, pp. 448–453.

- [30] B. Masserant and T. Stuart, "Experimental verification of calculated IGBT losses in PFCs," *IEEE Trans. Aerosp. Electron. Syst.*, vol. 32, no. 3, pp. 1154–1158, Jul. 1996.

- [31] A. Bhalla, J. Gladish, and G. Dolny, "Effect of IGBT switching dynamics on loss calculations in high speed applications," *IEEE Electron Device Lett.*, vol. 20, no. 1, pp. 51–53, Jan. 1999.

- [32] C. dos Santos and F. Antunes, "Losses comparison among carrier-based PWM modulation strategies in three level neutral-point-clamped inverter," in *Proc. Int. Conf. Renew. Energies Power Quality (ICREPQ)*, 2011, pp. 1035–1040.

**FRANCISCO EVERTON UCHÔA REIS** was born in Fortaleza, Ceará, Brazil, in 1986. He received the B.Sc. and M.Sc. degrees in electrical engineering from the Federal University of Ceará, Fortaleza, in 2009 and 2012, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

He is also an Assistant Professor with the Federal University of Piauí, Teresina, Brazil. His research interests include power supplies,

high-power factor rectifiers, nonisolated dc-dc converters, bidirectional converters, novel converter topologies, and solar photovoltaic systems. He is a member of IEEE Power Electronics Society (PELs).

**RENÉ PASTOR TORRICO-BASCOPÉ** received the B.Sc. degree in electrical engineering from San Simón University, Cochabamba, Bolivia, in 1992, and the M.Sc. and Ph.D. degrees in electrical engineering from the Federal University of Santa Catarina, Florianópolis, Brazil, in 1994 and 2000, respectively.

He is currently an Associate Professor with the Department of Electrical Engineering, Federal University of Ceará, Fortaleza, Brazil. His main

research interests include power supplies, power factor correction techniques, uninterruptible power systems, and renewable energy conversion systems.

**LUIZ DANIEL SANTOS BEZERRA** received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the Federal University of Ceará, Ceará, Brazil, in 2007, 2010, and 2018, respectively.

He is currently a Professor with the Department of Industry, Federal Institute of Education, Science, and Technology of Ceará (IFCE), Maracanaú, Brazil. His main research interests include power supplies, digital power factor cor-

rection techniques, uninterruptible power systems, digital control of power converters, and grid-connected photovoltaic systems. He is a member of the Brazilian Society of Power Electronics.

. .

**FERNANDO LESSA TOFOLI** received the B.Sc., M.Sc., and Ph.D. degrees in electrical engineering from the Federal University of Uberlândia, Uberlândia, Brazil, in 1999, 2002, and 2005, respectively.

He is currently an Associate Professor with the Federal University of São João del-Rei, São João del-Rei, Brazil. His research interests include power-quality-related issues, high power factor rectifiers, nonisolated dc-dc converters with

wide voltage conversion range, novel converter topologies, and solar photovoltaic systems.