### BORPH: An Operating System for FPGA-Based Reconfigurable Computers

by

Hayden Kwok-Hay So

B.S. (University of California, Berkeley) 1998M.S. (University of California, Berkeley) 2000

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

# GRADUATE DIVISION of the UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge: Professor Robert Brodersen, Chair Professor John Wawrzynek Professor Dorit S. Hochbaum

Fall 2007

The dissertation of Hayden Kwok-Hay So is approved:

Chair

Date

Date

Date

University of California, Berkeley

Fall 2007

# BORPH: An Operating System for FPGA-Based Reconfigurable Computers

Copyright 2007

by

Hayden Kwok-Hay So

#### Abstract

#### BORPH: An Operating System for FPGA-Based Reconfigurable Computers

by

Hayden Kwok-Hay So

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Robert Brodersen, Chair

Reconfigurable computing is a promising technology to meet future computational demand by leveraging flexibilities and the high degree of parallelism found in reconfigurable hardware fabrics, such as field programmable gate arrays (FPGAs). However, despite their promising performance researchers have demonstrated, reconfigurable computers are yet to be widely adopted. One reason is the lack of a common and intuitive operating system for these platforms.

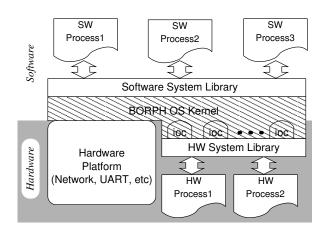

This dissertation work explores the design and implementation trade-offs of an operating system for FPGA-based reconfigurable computers, BORPH, the Berkeley Operating system for ReProgrammable Hardware. The goal of this work is to explore and demonstrate the feasibility of providing a systematic and easy to understand view into reconfigurable computers through OS support without incurring significant performance penalties. BORPH provides kernel support for FPGA applications by extending a standard Linux operating system. It establishes the notion of hardware process for executing user FPGA applications. Users therefore compile and execute hardware designs on FPGA resources the same way they run software programs on conventional processorbased systems. BORPH offers run-time general file system support to hardware processes as if they were software. The unified file interface allows hardware and software processes to communicate via standard UNIX file pipes. Furthermore, a virtual file system is built to allow access to memories and registers defined in the FPGA, providing communication links between hardware and software.

The functions of BORPH are demonstrated on a BEE2 compute module. Performances of BORPH are measured to identify bottlenecks of our system. The clean OS kernel/user separation of BORPH has allowed us to improve overall system performance without affecting existing user designs. Furthermore, BORPH's unified runtime environment has enabled designers to make fair and end-to-end comparisons among software/hardware implementations of the same application. Most importantly, since the introduction of BORPH to our FPGA-based platform, we have observed increased productivity among high-level application developers who have little experience in FPGA application design.

> Professor Robert Brodersen Dissertation Committee Chair

to my family,

to Carmen, and

to God be the Glory.

# Table of Contents

| Li       | st of | Figures                                                 | $\mathbf{v}$ |

|----------|-------|---------------------------------------------------------|--------------|

| Li       | st of | Tables                                                  | viii         |

| 1        | Intr  | oduction                                                | 1            |

|          | 1.1   | Related Work                                            | 4            |

|          | 1.2   | Chapter Overview                                        | 6            |

| <b>2</b> | Rec   | onfigurable Computers                                   | 8            |

|          | 2.1   | Reconfigurable Computer Architectures                   | 9            |

|          | 2.2   | Reconfigurable Fabrics                                  | 12           |

|          |       | 2.2.1 Granularity of Configuration                      | 13           |

|          |       | 2.2.2 Method of Configuration                           | 14           |

|          |       | 2.2.3 Field Programmable Gate Array                     | 20           |

|          | 2.3   | A Continuum of Computing                                | 23           |

|          |       | 2.3.1 Spatial and Temporal Computing                    | 23           |

|          |       | 2.3.2 Stored-Program Processor                          | 25           |

|          |       | 2.3.3 Fully Spatial Computation                         | 26           |

|          |       | 2.3.4 Between Spatial and Temporal Computing            | 27           |

|          |       | 2.3.5 Hardware/Software Terminology                     | 29           |

|          |       | 2.3.6 Physical and Virtual Machine                      | 30           |

|          | 2.4   | BEE2                                                    | 31           |

|          | 2.5   | Summary                                                 | 32           |

| 3        | BOI   | RPH: The Operating System                               | <b>34</b>    |

|          | 3.1   | Architectural Assumptions                               | 36           |

|          | 3.2   | Machine Abstraction Model                               | 36           |

|          |       | 3.2.1 Reconfigurable Fabrics as Coprocessors            | 37           |

|          |       | 3.2.2 Reconfigurable Fabrics as Computational Resources | 39           |

|          | 3.3   | Hardware Process                                        | 40           |

|   |     | 3.3.1 Process Creation                                                                                                                                       |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.3.2 The Lifecycle of a Hardware Process                                                                                                                    |

|   | 3.4 | Kernel Interface                                                                                                                                             |

|   |     | 3.4.1 Hybrid Message Passing System Call Interface                                                                                                           |

|   | 3.5 | File I/O                                                                                                                                                     |

|   |     | 3.5.1 Differences between Software and Hardware Design Patterns .                                                                                            |

|   |     | 3.5.2 High Speed Streaming Data I/O                                                                                                                          |

|   |     | 3.5.3 Runtime Streaming Mode Switching Support                                                                                                               |

|   |     | 3.5.4 File Streaming I/O Library                                                                                                                             |

|   | 3.6 | The ioreg Virtual File System                                                                                                                                |

|   |     | 3.6.1 Basic Operation $\ldots \ldots \ldots$ |

|   |     | 3.6.2 Organization of ioreg Virtual Files                                                                                                                    |

|   |     | 3.6.3 Example                                                                                                                                                |

|   |     | 3.6.4 Beyond Simple Register                                                                                                                                 |

|   |     | 3.6.5 Language Independence                                                                                                                                  |

|   |     | 3.6.6 Operating Mode                                                                                                                                         |

|   | 3.7 | Summary                                                                                                                                                      |

| 4 | Imr | plementation and Performance 7                                                                                                                               |

| т | 4.1 | Overview                                                                                                                                                     |

|   | 4.2 | Software Kernel Architecture                                                                                                                                 |

|   | 1.2 | 4.2.1 BOF file support                                                                                                                                       |

|   |     | 4.2.2 Reconfigurable Hardware Region (hwr) Support                                                                                                           |

|   |     | 4.2.3 FPGA Configuration and Resource Allocation                                                                                                             |

|   |     | 4.2.4 Software Fringe                                                                                                                                        |

|   |     | 4.2.5 Packet Communication Network                                                                                                                           |

|   |     | 4.2.6 Process Scheduler and Signal Handler                                                                                                                   |

|   | 4.3 | Base Architecture                                                                                                                                            |

|   |     | 4.3.1 The SelectMap Bus Controller                                                                                                                           |

|   |     | 4.3.2 Design of uK                                                                                                                                           |

|   | 4.4 | Performance of Base Architecture                                                                                                                             |

|   |     | 4.4.1 Hardware Process Creation                                                                                                                              |

|   |     | 4.4.2 Reading/Writing ioreg Files                                                                                                                            |

|   |     | 4.4.3 General File I/O from Hardware Processes                                                                                                               |

|   | 4.5 | Advanced On-Chip Architecture                                                                                                                                |

|   |     | 4.5.1 Elimination of PLB-to-OPB Bridge                                                                                                                       |

|   |     | 4.5.2 DMA Enabled Control FPGA                                                                                                                               |

|   | 4.6 | Porting BORPH                                                                                                                                                |

|   | 4.7 | Summary                                                                                                                                                      |

|   |     |                                                                                                                                                              |

| <b>5</b> | BO    | RPH Application Developments                                     | 98  |

|----------|-------|------------------------------------------------------------------|-----|

|          | 5.1   | Conventional FPGA Design Flow                                    | 98  |

|          |       | 5.1.1 Run Time Support                                           | 100 |

|          | 5.2   | Simulink-based Design Flow                                       | 101 |

|          | 5.3   | Sample Applications                                              | 104 |

|          |       | 5.3.1 Example 1: A Real-Time Wireless Signal Processing System . | 104 |

|          |       | 5.3.2 Example 2: Low-Density Parity-Check Decoders Emulation     | 106 |

|          |       | 5.3.3 Example 3: FPGA Video Processing with Commodity Software   | 107 |

|          | 5.4   | Summary                                                          | 109 |

| 6        | Con   | nclusions and Future Directions                                  | 110 |

|          | 6.1   | Future Directions                                                | 112 |

|          | 6.2   | Closing Remarks                                                  | 113 |

| Bi       | bliog | graphy                                                           | 115 |

# List of Figures

| 2.1  | 6 classes of reconfigurable computer architectures                     | 10 |

|------|------------------------------------------------------------------------|----|

| 2.2  | Simplified version of dedicated DSP blocks on a Virtex-4 FPGA. It is   |    |

|      | an example of coarse grain reconfigurable unit as it can perform only  |    |

|      | one of the several predefined mathematical functions                   | 13 |

| 2.3  | Gate arrays are programmed by metal and contact layer specialization.  | 15 |

| 2.4  | A PLA maps Boolean equations in sum-of-product forms directly with     |    |

|      | programmable connections in the AND-plane and OR-plane                 | 16 |

| 2.5  | Making a connection between two wires using pass transistors con-      |    |

|      | trolled by 1 bit of configuration memory                               | 17 |

| 2.6  | Mapping the truth table of 2-input XOR function directly using mem-    |    |

|      | ory with 4 locations of 1-bit wide data                                | 18 |

| 2.7  | All 16 possible 2-input truth tables                                   | 19 |

| 2.8  | A generic FPGA                                                         | 21 |

| 2.9  | Components of a generic FPGA                                           | 22 |

| 2.10 | A spectrum of computers                                                | 24 |

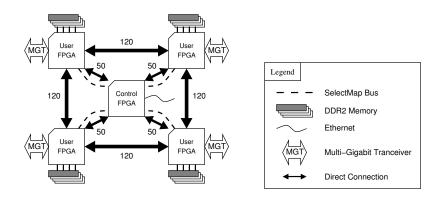

| 2.11 | Block diagram of a BEE2 compute module                                 | 31 |

| 2.12 | 0 2                                                                    |    |

|      | using a BEE2 compute module                                            | 32 |

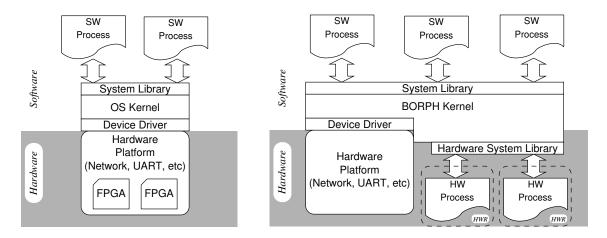

| 3.1  | Two ways of organizing reconfigurable fabrics in a reconfigurable com- |    |

|      | puter                                                                  | 37 |

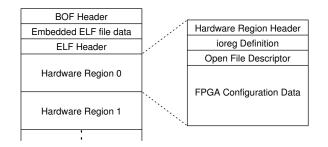

| 3.2  | Simplified BOF file format                                             | 42 |

| 3.3  | Executing a BOF file containing a free running counter. FPGA hard-     |    |

|      | ware is configured at prompt 1 and is unconfigured at prompt 3         | 43 |

| 3.4  | BORPH's hardware kernel interface is constructed from one or more      |    |

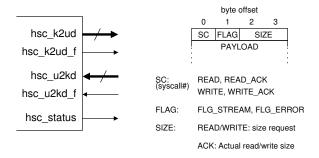

|      | I/O connection points (ioc)                                            | 48 |

| 3.5  | Left: BORPH's hardware system call (hsc) interface. Right: Format      |    |

|      | of packet transmitted through hsc.                                     | 48 |

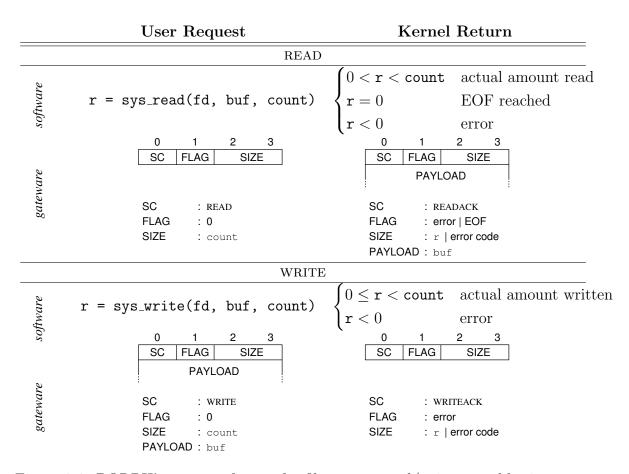

| 3.6  | BORPH's message format for file system read/write resembles its cor-   |    |

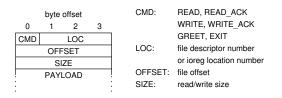

|      | responding UNIX system call prototype                                  | 53 |

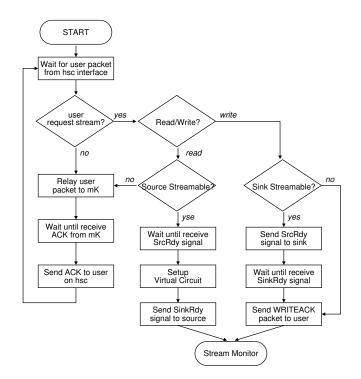

| 3.7         | A simplified flow diagram for iock packet handling. A streaming data connection is setup iff both source and sink are streamable and are                                                                                                          |    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | ready to stream data                                                                                                                                                                                                                              | 58 |

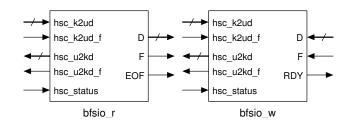

| 3.8         | The <b>bfsio</b> library contains two blocks. The read (bfsio_r) block gen-<br>erates read requests on behalf of the user and relays only data payload<br>and EOF information to user. The write (bfsio_w) translates a stream                    |    |

|             | of data from user into individual write request packets to the kernel.                                                                                                                                                                            | 59 |

| 3.9<br>3.10 | The /proc directory tree in of BORPH BORPH's IOREG interface allows interacting with hardware processes via virtual files. The register cntval contains current value of the free running counter in counter.bof. This counter can be disabled by | 62 |

|             | writing to cnten register                                                                                                                                                                                                                         | 64 |

| 3.11        | A simple packet format for message exchanges between BORPH main                                                                                                                                                                                   |    |

|             | kernel MK and its distributed kernel UK                                                                                                                                                                                                           | 65 |

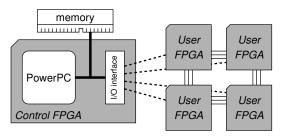

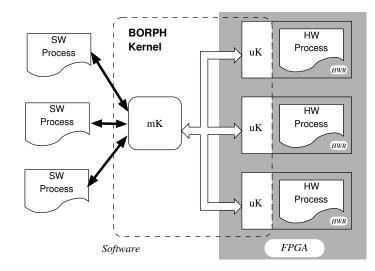

| 4.1         | The two logical components of BORPH: MK and UK. MK is the main<br>controlling software kernel. Each reconfigurable hardware region is<br>in dividually many and have here been lowed as the a VK                                                  | 71 |

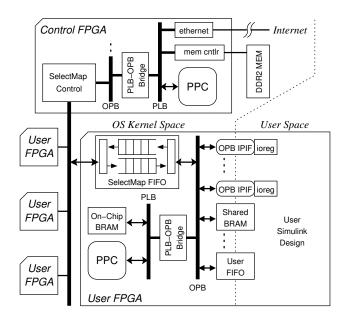

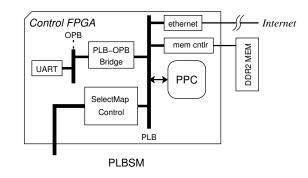

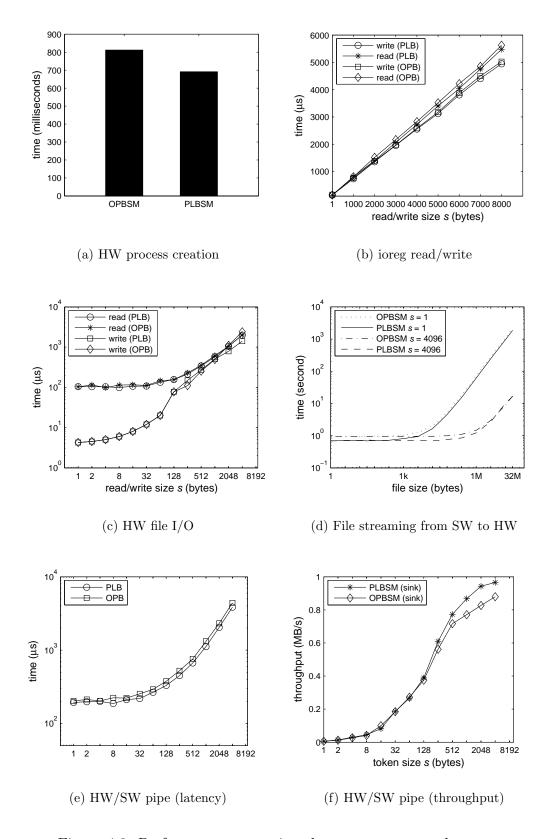

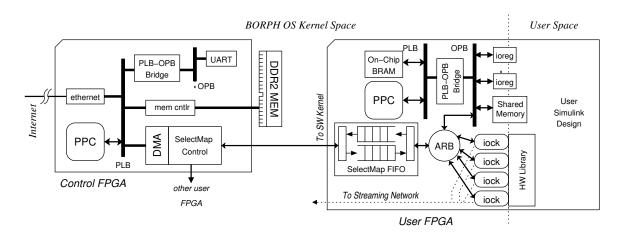

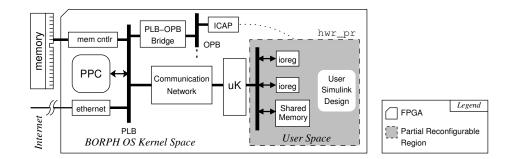

| 4.2         | individually managed by a low-level kernel called a UK Block diagram of BORPH system on a BEE2 compute module with                                                                                                                                | 71 |

| 4.2         | OPB-based SelectMap controller in control FPGA (OPBSM)                                                                                                                                                                                            | 75 |

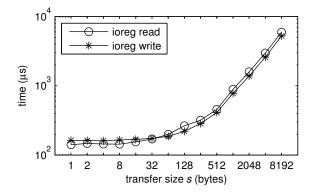

| 4.3         | Performance of reading/writing on-chip memory on a user FPGA using                                                                                                                                                                                | 10 |

| 1.0         | ioreg interface.                                                                                                                                                                                                                                  | 81 |

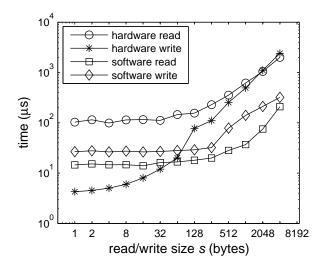

| 4.4         | Hardware process file I/O performance.                                                                                                                                                                                                            | 82 |

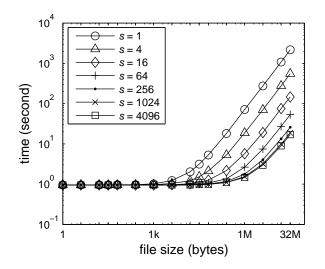

| 4.5         | The effect of data transfer size $s$ on total time required by a hardware                                                                                                                                                                         |    |

|             | process to sink a regular file. Time is measured from control FPGA.                                                                                                                                                                               | 84 |

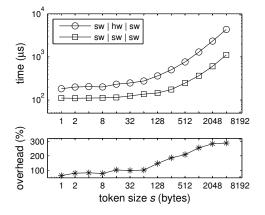

| 4.6         | Comparing software piped process chain with a mixed hardware/software                                                                                                                                                                             |    |

|             | chain                                                                                                                                                                                                                                             | 85 |

| 4.7         | PLB-based SelectMap controller (PLBSM)                                                                                                                                                                                                            | 87 |

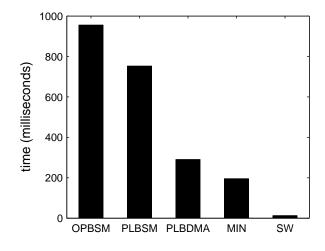

| 4.8         | Performance comparison between OPBSM and PLBSM                                                                                                                                                                                                    | 88 |

| 4.9         | Direct memory access (DMA) is enabled in the control FPGA for com-                                                                                                                                                                                |    |

|             | munication between PPC and the PLB-based SelectMap controller.                                                                                                                                                                                    |    |

|             | On a user FPGA, a hardware arbiter is implemented to allow direct                                                                                                                                                                                 |    |

|             | access to SelectMap bus from a user gateware design for file I/Os                                                                                                                                                                                 | 90 |

| 4.10        | Hardware process creation time in 3 different on-chip architectures                                                                                                                                                                               |    |

|             | compared with the theoretical minimum time and software process                                                                                                                                                                                   |    |

|             | creation time.                                                                                                                                                                                                                                    | 91 |

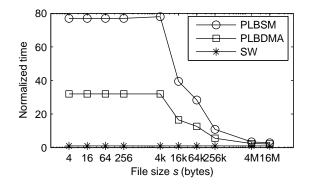

| 4.11        | Normalized time for hardware processes to finish streaming files of various sizes. stdloop.bof uses PPC on user FPGA for file operations,                                                                                                         |    |

|             | while direct file I/O through hsc is used in stdloop_hsc.bof                                                                                                                                                                                      | 93 |

| 4.12        | An example of porting BORPH to a single FPGA where user hardware                                                                                                                                                                                  |    |

|             | processes are executed on a partially reconfigurable region                                                                                                                                                                                       | 94 |

| 5.1 | An automatic hardware design flow that compiles high-level Simulink |     |

|-----|---------------------------------------------------------------------|-----|

|     | designs into executable BOF files                                   | 102 |

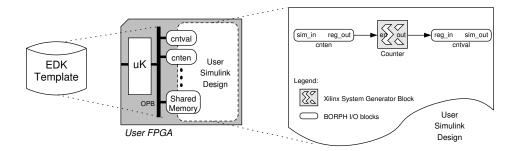

| 5.2 | Block diagram of a user FPGA. Compiled user Simulink designs are    |     |

|     | combined with a predefined EDK template of UK to generate user      |     |

|     | FPGA configurations                                                 | 103 |

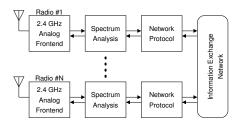

| 5.3 | Cognitive radio testbed system                                      | 105 |

# List of Tables

| 3.1 | Types of ioreg |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | ( | 65 | 5 |

|-----|----------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|---|

|-----|----------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|---|

### Acknowledgments

This work could not be completed without the help, support and prayers of my colleagues, friends and family.

I have to thank my advisor, Bob, for his continuous support throughout my time at Berkeley. It was his adventurous mindset that inspired the creation of BORPH. It was his well-rounded and open mind that nurtures such highly cross disciplinary work of FPGA operating system. His passion for people, life, the nature and ideas from any research fields is going to continue be my aspiration even after leaving Berkeley.

I have to thank Professor John Wawrzynek for introducing me into this exiting field of reconfigurable computing and for his invaluable recommendations on the design of BORPH. I also want to thank members of my dissertation and qualifying exam committee, Professor Dorit Hochbaum, Professor Pravin Varaiya, and Professor Eric Brewer, for their time, effort and recommendations.

Throughout my time at Berkeley, I have been supported financially by the DARPA, C2S2.

The success of BORPH is due largely to the availability of the fine FPGA systems, design flow, and their users at the Berkeley Wireless Research Center. I want to thank Greg Wright for envisioning the original BEE (at that time the Biggascale Emulation Engine); to Chen Chang and Pierre Droz for building the BEE and BEE2 machines; to Andrew Shultz, Pierre Droz and Henry Chen for fine tuning and promoting the Simulink FPGA design flow.

I want to thank all the users of BORPH whose feedbacks have been invaluable

for the development of BORPH. It was your comments such as "BORPH is my lifesaver" and "It (BORPH) has been instrumental in my research" that have kept the development of BORPH motivated. I must thank Artem Tkachenko in particular for serving as "guinea pigs" stepping on the never ending list of bugs during BORPH's early development.

To my family, I want to express my deepest gratitude for your endless support, enabling me to pursue this fine path of research at Berkeley, away from home, for many years.

To Pastor Samuel Wong, thank you for your support during my lowest point in my Ph.D. career.

To Carmen, thank you for your patience, support, encouragement, understanding, and prayer all these years.

Finally, and most importantly, I must thank my Lord for providing all the people and things that I am grateful for all these years; for carrying me through even the darkest valley and the brightest avenue; and for giving me the much needed patience and wisdom for research and for life.

> I will lift up mine eyes unto the hills, from whence cometh my help. My help cometh from the LORD, which made heaven and earth.

> > - Psalms 121:1-2

# CHAPTER 1

# Introduction

Reconfigurable computing has a long history. In 1960, Gerald Estrin proposed a "Fixed+Variable" machine that some believe to be the first reconfigurable computer[18]. This machine featured a fixed host processor and a section of reconfigurable hardware for application acceleration. Most reconfigurable computers (RCs) developed since then followed a similar machine organization.

However, the idea of computing using reconfigurable hardware has not been given as much attention as other simpler machine organizations. Until very recently, single processor systems have dominated the mass personal computer market. For high performance computing, researchers turn to various kinds of parallel processor architectures such as cluster of symmetric multi-processors (SMP). Over the years, the technology trend in computer architecture has been determined by two major factors: (1) Physical hardware implementation technology and (2) Ease of use. Implementation technology imposes a number of physical constraints on a computing system. For example, bus performance limits the scalability of bus-based shared memory SMP[17], while power dissipation limits performances of modern sophisticated super-scalar processors. Ease of use of a computer system, on the other hand, is a subjective measurement that takes on multiple meanings depending on context. Nevertheless, it is the ease of understanding and reason about that the original *sequential stored program* computer concept developed in the 1940s still prevails among modern computers. It was the desire to have a smooth application development environment that motivated the development of the first operating system on the EDVAC machine[36]. It was the observation that easy to use user interfaces greatly improve computer users' productivity that fueled the study of human computer interface.

Technology-wise, reconfigurable hardware has improved dramatically since the 1960s. Today, reconfigurable computers are capable of delivering orders of magnitude higher performance than software solutions on conventional processor systems[43]. Their high performances have made them viable computing platforms for a wide range of application domains, such as high speed digital signal processing[31], multi-media processing, speech recognition[27, 33], bioinformatics[16], and radio astronomy. However, despite their promising performances, researchers, particular those traditionally not accustomed to hardware/software design environments of RCs, remain reluctant to adopt such technology. The main reason for this remains that *reconfigurable computers are difficult to use*.

There are two classes of difficulties. The first class of difficulty relates to design methodologies for RCs, i.e. the process of translating a conceptual design into a machine understandable program or configuration. This class of difficulty arises during *compile time* of an application. In the context of a conventional processor system, such translation process involves two main steps. First, a conceptual design must be expressed in certain design language, such as C. Then, this user description must be translated by a compiler into a sequence of processor specific instructions according to the processor's predefined instruction set architecture (ISA).

Unfortunately, due to the flexible hardware architecture of RCs, this conversion process is not as straight forward as software compilation. Successful RC design methodology requires design languages that are high-level enough for them be easy to use yet powerful enough to fully express the parallel nature of an application. Furthermore, a smart compiler is needed to further extract implicit parallelism and sometimes even derive the correct computation architecture for each application. Finally, the tools must be able to efficiently perform placement and routing of the compiled application on to the physical reconfigurable hardware fabric of the target system to meet performance and resource constraints. In fact, the design methodology for RC is so important that it has been the focus for a majority of research in the reconfigurable computing field in the past.

The second class of difficulty involves how easy an RC application may interact with the system, user, and other applications during *run time*. It involves questions such as: "On which reconfigurable fabric, and for how long, should an application be executed?" "How does an application communicate with the user?" "How does an application perform general I/O operations?" Most existing RC systems have their own ad-hoc mechanisms to address the above system integration requirements. However, few research efforts have been put into addressing these common problems in a standardized and systematic way. The focus of this dissertation work, BORPH, approaches this class of problems systematically from an operating system design perspective.

The goal of BORPH is to improve usability of reconfigurable computer systems through operating system support. Instead of abstracting reconfigurable hardware of the system as accelerators for software programs, BORPH allows users to implement applications directly using these reconfigurable hardware fabrics. User hardware designs therefore run as normal UNIX process in the system like a software program. BORPH OS kernel provides standard UNIX services, such as file system access, to these hardware processes. Productivity of novel RC users are observed to have improved as a combined result of such familiar OS interface, a hardware design flow with libraries that integrates with BORPH, and the availability of commodity software to coexist with hardware designs within the same system.

### 1.1 Related Work

A number of research projects have approached the task of designing operating systems for FPGA-based reconfigurable computers[10, 48, 46, 30, 21]. All of them are devoted to the problem of dynamic FPGA resource allocation, memory sharing or virtualization between software and hardware tasks on FPGA-based systems. We are not aware of any prior work that systematically offer runtime support directly to hardware processes as BORPH does. Furthermore, instead of relying on abstract "task" models commonly found in other reconfigurable computer operating systems, the use of UNIX process semantics to model running FPGA designs is unique to BORPH.

On the other hand, most commercial FPGA-based reconfigurable computers[9, 51, 15, 6] are managed by off-the-shelf operating systems such as Linux and VxWorks. FPGAs on these systems are used mainly as software accelerators. Software and FP-GAs communicate through the conventional device driver layer while FPGA designs must utilize vendor specific libraries with custom APIs. As a result, even if machines from different vendors are constructed using identical FPGAs, the inconsistent system interface prevent designs targeting one machine to be easily ported to another. Such inconsistent system interface greatly hinder collaborations among FPGA researchers.

Much consideration has been put into the design of BORPH's kernel/user interface, making it as close to conventional UNIX system as possible. It is designed to lower the barrier-to-entry for novel FPGA users and to increase portability of reconfigurable application designs. The importance of an intuitive and unified interface is well acknowledged by a number of works[45, 37]. The work of UltraSONIC[47] shares a similar design philosophy as BORPH in providing a unifying coarse-grain hardware software component interface. Furthermore, the choice of POSIX conforming pthread interface in the work of hThread[2] echoes well with BORPH's design philosophy.

The main contribution of BORPH is that by leveraging conventional UNIX semantics to FPGA-based reconfigurable computing, it provides a unique, unified environment for both FPGA and software application designers. The UNIX semantics is familiar to developers across many research domains, thus lowering the barrierto-entry into FPGA-based reconfigurable computing. Furthermore, since BORPH is implemented as an extended Linux kernel, a BORPH managed system may leverage all commodity Linux software applications for developing, testing, benchmarking, and deploying FPGA applications.

### 1.2 Chapter Overview

Chapter 2 provides brief background information about reconfigurable computing. An overview of various reconfigurable computer architectures will be given. We will introduce one of the most common reconfigurable hardware fabrics in contemporary RC, the field programmable gate array (FPGA) and illustrate how one can configure such hardware to perform any digital logic. Finally, we will describe the FPGA-based reconfigurable machine, BEE2, on which BORPH currently runs.

Chapter 3 goes into details of BORPH design and implementation. The concept of hardware process will first be introduced. Based on this notion of hardware process, we will describe various BORPH features: the BORPH hardware kernel/user interface design; the hardware file I/O subsystem; and finally the IOREG virtual file system.

Chapter 4 evaluates the performance of BORPH. Three iterations of hardware system design will be described. The multiple implementations not only provide a concrete performance benchmark of various BORPH subsystems, they also illustrate the benefit of kernel/user separation in hardware. Finally, these benchmarks demonstrate how end-to-end performance comparison between software and hardware can be achieved through BORPH's unified hardware/software run-time environment. Chapter 5 explores the interaction between FPGA design methodologies and the run time operating system. Design methodologies for FPGA and other reconfigurable computers will first be briefly described. Then, the Simulink-based design flow developed at the Berkeley Wireless Research Center (BWRC) will be described as an illustration on how a design methodology integrates with BORPH. Finally, three actual FPGA applications are presented to illustrate how various features of BORPH work together to ease their development processes.

We will conclude this dissertation and provides insights into future research inspired by BORPH in Chapter 6.

# CHAPTER 2

# **Reconfigurable Computers**

This chapter provides a brief introduction into the field of reconfigurable computing. Broadly speaking, reconfigurable computing refers to machines that compute with dynamically reconfigurable data and control path. This is in contrast to a simple processor system in which only a single fixed data and control path is presented. As such, reconfigurable computing generally refers to a large spectrum of computers with drastically different designs and implementations. A number of excellent surveys are available in the literature [43, 8, 22, 42] and their results are not repeated here. Only a brief introduction is given here to make this dissertation self-contained.

In general, reconfigurable computers consist of zero or more physically presented sequential processors coupled with one or more reconfigurable fabrics. Such definition points to two important design aspects of reconfigurable computers: (1) The coupling of processor and reconfigurable hardware, i.e. their system architectures; and (2) The implementation of reconfigurable hardware.

## 2.1 Reconfigurable Computer Architectures

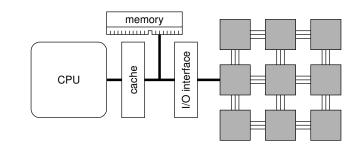

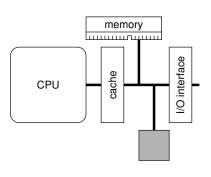

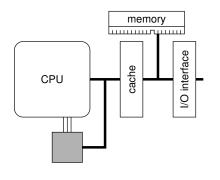

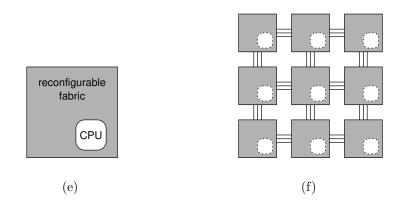

Todman *et al.* [43] extended the work of Compton and Hauck[8] and provided a 5-class classification of RC architectures as shown in Figure 2.1(a) to (e). The first four classes of systems are characterized by the physical presence of a single controlling processor. They differ in the way that the processor communicates with the reconfigurable fabric (RF) of the system.

In Figure 2.1(a), reconfigurable fabrics are connected to the processor through its system I/O bus. Although it provides the least data bandwidth between the processor and the RF, it is easiest to implement. A conventional processor-based system can be extended into a RC system by simply inserting an add-on card with reconfigurable fabrics to its peripheral bus. Because of this simplicity, it is by far the most common RC architecture found in commercial systems.

Figure 2.1(b) and 2.1(c) depict systems that incorporate RF into two different locations within the processor's memory subsystem. Data bandwidth between the processor and the RF is usually the performance bottleneck of a system. By connecting RFs directly to the processor's memory subsystem, these architectures provide the much needed bandwidth.

Figure 2.1(d) shows a system that integrates RF directly into the data path of the controlling processor as functional units. It allows the RF to have access to all local information about the running processor, such as the register file. Such tight integration ensures maximum integration between software and hardware. However, it is also this tight integration that limits RF speedup due to the lack of instruction

### 2.1. Reconfigurable Computer Architectures

(a)

(d)

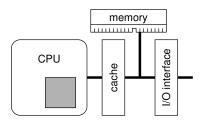

Figure 2.1: 6 classes of reconfigurable computer architectures.

level parallelism.

Figure 2.1(e) represents a new class of RC that is made only possible with advances in reconfigurable hardware technologies. Instead of connecting reconfigurable fabrics to a processor system, these machines embed processors within reconfigurable fabrics. These embedded processors can either be implemented physically or as *soft processors*. Soft processors are processors that are built as needed by an application using reconfigurable hardware. Examples are the MicroBlaze and PicoBlaze processors by Xilinx, as well as the Nios and Nios-II processors by Altera. This class of RC system has the benefit of allowing a user to determine the type and number of processors needed in the system, especially by using soft processor, thereby increasing system performance and efficiency. Most importantly, this class of system breaks away from the processor-centric compute model in the previous 4 classes of systems. By shifting away from the sequential compute model of the controlling processor, this class of system has much higher performance potential than the previous four.

Figure 2.1(f) illustrates the sixth class of system that consists of two or more machines in the previous 5 classes connected through a direct network. On a system level, these systems share similar properties such as system topology and routing strategies with conventional multi-processor systems. However, because of the proximity of computational fabric to the network, RC systems provide much higher potential performance benefit over multi-processor systems. For example, sending a word of data from a hardware application on one FPGA to another directly connected FPGA takes only a few clock cycles for synchronization. If the system is fully synchronized, latency can potentially be further reduced to zero cycle, virtually doubling the size of the FPGA. Even for large complicated RC systems that must utilize complex packets for communication, the fact that the very same computational reconfigurable hardware fabrics are used to manage these communication packets significantly reduces such communication overhead. In contrast, because of layers of software overhead, communication latency on multi-processor systems, particularly cluster based systems, are order of magnitude higher[29]. Moreover, some systems employ a run time reconfigurable direct network, forming a hierarchical reconfigurable system as a result. For example, the RAW machine consists of an array of processing elements connected through a user programmable network[41]. The routing of the network is controlled as part of the user program. At the same time, each RAW processing element is itself a simple reconfigurable computer consists of a processor coupled with a custom made FPGA.

### 2.2 **Reconfigurable Fabrics**

One of the most important structures that differentiate a reconfigurable computer from a conventional processor-based system is its reconfigurable fabric. Many different types of reconfigurable fabrics have been proposed in the literature. In general, they can be characterized by their granularities of configuration and their methods of configuration. This section explores the design space of reconfigurable hardware and concludes with an introduction to currently most widely used fabric: the field programmable gate array (FPGA).

Figure 2.2: Simplified version of dedicated DSP blocks on a Virtex-4 FPGA. It is an example of coarse grain reconfigurable unit as it can perform only one of the several predefined mathematical functions.

### 2.2.1 Granularity of Configuration

The configuration granularity of a reconfigurable hardware fabric affects its flexibility in implementing different logic functions. There is always a trade-off between flexibility and efficiency of the fabric. Fine grain reconfigurable fabrics are very flexible. They can be used to implement any sequential and combinational Boolean logic function, but are slower and physically bigger in general. On the other hand, coarse grain reconfigurable fabrics are faster, occupy smaller areas, but are limited to implementing only one of the predefined functions.

Some reconfigurable fabrics, such as modern FPGAs, contain a mix of both fine grain and coarse grain reconfigurable units. For example, Xilinx Virtex-4 FPGAs[50] contain dedicated blocks similar to that in Figure 2.2 for digital signal processing (DSP) applications. This block can be programmed by the user to perform a combination of multiplication, addition or subtraction. Although the same functions could have been implemented using general fine-grain programmable fabrics on the FPGA, having such dedicated blocks result in designs that are smaller, faster, and consume less energy.

Unfortunately, the correct mix of coarse grain and fine grain reconfigurable units

is highly application specific. As a reconfigurable computing platform, designers must adjust the mix according to the area, power and performance requirements for the target application domain.

### 2.2.2 Method of Configuration

In the 1970s, integrated circuit designers were looking for timely and cost effective ways to manufacture application specific integrated circuits (ASICs). The result was the development of integrated circuits that can be programmed after they are fabricated. These post-fabrication programmable integrated circuits subsequently evolve into modern day programmable logic devices.

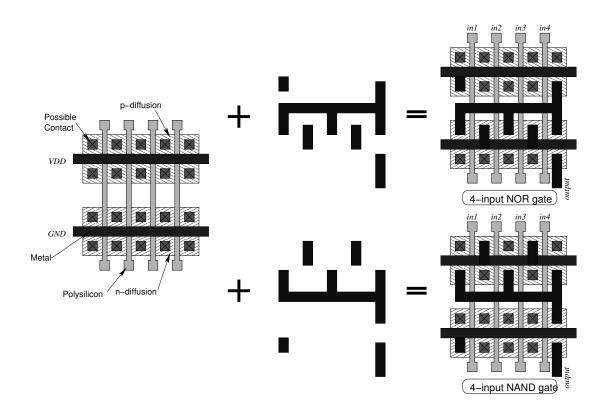

#### Non-Volatile, Single Program

Tracing back to their ASIC roots, early programmable logic devices are designed to be programmed only once: i.e., to program an IC to implement a specific application. One way to achieve such specialization is by pre-fabricating a *gate array* on silicon wafers as seen in Figure 2.3. Designing an ASIC is then reduced to a task of connecting these pre-fabricated transistor gates using upper metal layers. Manufacturing cost, as well as time-to-market, is therefore reduced as the number of fabrication mask is reduced. Strictly speaking, this method is not a post-fabrication logic programming mechanism. Nevertheless, this metal layer specialization is the predecessor for many subsequent programmable logic devices (PLDs).

Another non-volatile, single program method of configuration for PLDs is by using

Figure 2.3: Gate arrays are programmed by metal and contact layer specialization.

Figure 2.4: A PLA maps Boolean equations in sum-of-product forms directly with programmable connections in the AND-plane and OR-plane.

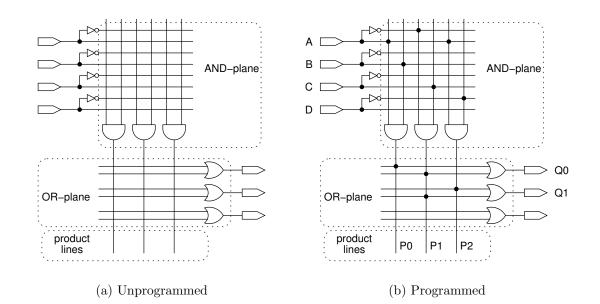

fuses or anti-fuses to form metal connections. They are usually used in dense PLDs such as programmable logic arrays (PLAs). As oppose to gate arrays, PLAs are truly post-fabrication programmable logic devices. Logically, a PLA is programmed by directly mapping user Boolean functions in sum-of-product forms to the device.

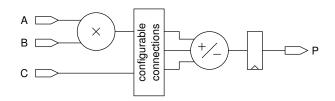

Figure 2.4(a) shows a simplified block diagram for a PLA. A typical PLA contains a programmable AND-plane connected to a programmable OR-plane. Similar to the gate array concept, a PLA is configured by programming wire connections that connect the two planes and I/O pins. These connections are either made of anti-fuses or programmable switches. An anti-fuse behaves in exact opposite ways of a normal electrical fuse: i.e., the two terminals of an anti-fuse are disconnected by default until it is "broken" by strong current.

The first step to implementing user logic is to generate all *product terms* by making

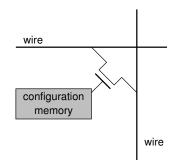

Figure 2.5: Making a connection between two wires using pass transistors controlled by 1 bit of configuration memory

appropriate connections to the AND-plane input. The results, carried in the set of vertical *product lines*, are then connected accordingly to the OR-plane to compute the final sum-of-products. For example, the PLA in Figure 2.4(b) is programmed to compute two equations:  $Q0 = AB + \overline{A}C$  and  $Q1 = A\overline{D} + \overline{A}C$ . Product lines P0, P1 and P2 carry the intermediate results AB,  $\overline{A}C$  and  $A\overline{D}$  respectively.

#### Non-Volatile, Multiple Program

Some manufacturers use non-volatile, but programmable memory technology such as erasable programmable read only memory (EPROM) and electrical erasable programmable read only memory (EEPROM) to implement programmable logic devices. For instance, instead of using anti-fuses, PLAs described above can be programmed using pass transistors that are controlled by PROMs (Figure 2.5).

Another way to build programmable logic devices is to implement Boolean logic directly using non-volatile memories. Performing logic operations using memory is best illustrated by an example.

Figure 2.6 shows the truth table of an *exclusive or* (XOR) Boolean operation

| Α | В             | Q | <br>address                      | data |

|---|---------------|---|----------------------------------|------|

| 0 | 0             | 0 | 0                                | 0    |

| 0 | 1             | 1 | 1                                | 1    |

| 1 | 0             | 1 | 2                                | 1    |

| 1 | 1             | 0 | 3                                | 0    |

|   | Trut<br>for X |   | (b) May<br>to 4 men<br>locations |      |

Figure 2.6: Mapping the truth table of 2-input XOR function directly using memory with 4 locations of 1-bit wide data.

where output (Q) is 1 only if exactly one of either A or B is 1. One way to implement an XOR operation in hardware is by mapping its truth table directly using a read only memory (ROM). Using input A and B as memory address, this ROM reads out the expected value of Q. In this particular example, a 0 is stored at locations 0 and 3 while a 1 is stored at locations 1 and 2. When a ROM is used for looking up values, it is referred as a lookup table (LUT).

Figure 2.7 shows all 16 possible truth tables with two inputs, A and B, and one output, Q. For instance, the 7<sup>th</sup> column from the left shows the same truth table as Figure 2.6 for an XOR operation. Figure 2.7 illustrates the benefit of implementing a simple 2-input XOR function using a LUT: configurability. By implementing lookup tables using programmable memory, the logic function of that a LUT implementation can be changed simply by changing data values in various memory locations. For instance, to implement an AND operation, one can simply write 0 to locations 0,1,2 and write a 1 to location 3.

|   |   | 90<br>0          | ß | 100 |   | 0  |   | R |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | \$ | /Q<br>4 | ¢          | ۲<br>۲ | b<br>/02 | <i>(</i> ) |

|---|---|------------------|---|-----|---|----|---|---|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|---------|------------|--------|----------|------------|

| A | В | ₹\$ <sup>6</sup> | Ŕ | Ŕ   | Þ | 12 | Ŷ | Þ | Ŕ | 1 the second sec | 1 | 12 | Ŗ       | $\sqrt{N}$ | 12     | ∕₹?      | <i>and</i> |

| 0 | 0 | 0                | 0 | 0   | 0 | 0  | 0 | 0 | 0 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 1  | 1       | 1          | 1      | 1        | 1          |

| 0 | 1 | 0                | 0 | 0   | 0 | 1  | 1 | 1 | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 | 0  | 0       | 1          | 1      | 1        | 1          |

| 1 | 0 | 0                | 0 | 1   | 1 | 0  | 0 | 1 | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 | 1  | 1       | 0          | 0      | 1        | 1          |

| 1 | 1 | 0                | 1 | 0   | 1 | 0  | 1 | 0 | 1 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 | 0  | 1       | 0          | 1      | 0        | 1          |

Figure 2.7: All 16 possible 2-input truth tables

In general, any Boolean logic function with n variables can be implemented by using a lookup table with n inputs. A LUT with n inputs is usually referred as an n-LUT. Each n-LUT can be configured to implement one of the  $2^{2^n}$  possible functions. However, large LUTs are expensive to build in terms of silicon area, speed, power and dollar cost. Therefore, lookup tables of moderate sizes from 3 to 6 inputs are usually used.

### Volatile Configuration

Most modern commercially available programmable devices utilize volatile memories, such as static random access memory (SRAM), or even simple on-chip registers, to store device configurations. Since the device configuration is volatile, these devices must be programmed every time a system is powered up. The programming is usually accomplished by reading configurations from an external PROM or through standardized in-system testing protocol such as that from the Joint Test Action Group (JTAG). Architecturally, these modern devices can be identical to devices described above. However, since programming a device is performed through writing to SRAM or hardware registers, the programming speed is order of magnitude faster than previous non-volatile configuration solutions. Furthermore, modern devices support dynamic partial configuration, which is the ability to reconfigure parts of the device while the rest of the device continues to operate without interruption.

Such versatility in programming has created opportunities for using even off-theshelf PLDs in reconfigurable computing. A number of commercial products[9, 51, 15] as well as numerous research projects[26] are based on off-the-shelf PLDs.

#### Custom, Multi-Context Configuration

Over the years, reconfigurable computing researchers have proposed a number of custom reconfigurable fabrics specific for their systems. Some of them are developed to integrate with existing processor datapath[38]. Others developed the notion of multi-context reconfigurable hardware fabrics[28, 25, 44, 11]. The idea of multi-context reconfiguration evolves from the need to reprogram a device in extreme speed. It is particularly useful for RC systems in which reconfigurable fabrics must switch between different functions quickly. As a result, these devices store multiple configurations in the device in parallel that can potentially be swapped in a single hardware cycle.

### 2.2.3 Field Programmable Gate Array

Field Programmable Gate Array (FPGA) is one of the most readily available commercial programmable logic devices. Starting as ASIC replacements similar to other PLDs, FPGAs have slowly evolved into complex embedded system platforms that are flexible and are able to deliver performances comparable to ASICs. The

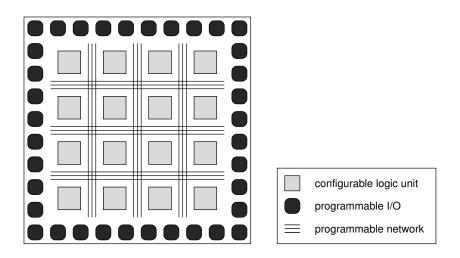

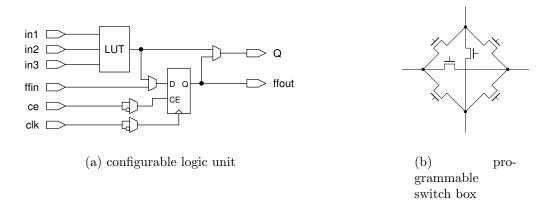

Figure 2.8: A generic FPGA

basic architecture of an FPGA is shown in Figure 2.8. FPGAs are generally made up of an array of configurable logic units connected with a programmable routing network. Programmable I/O blocks are used to control off-chip interfaces, such as signal directions and impedances of I/O pins.

#### Configurable Logic Unit

The basic building blocks of an FPGA are configurable logic units (CLUs) that are programmable according to user logic functions. Different FPGA manufacturers have slightly different implementations, such as "slices" for Xilinx FPGAs or "adaptive logic modules" for Altera FPGAs. Despite their different implementations, they share a similar basic design. Each configurable logic unit consists of a fine grain programmable combinational logic block that is optionally connected to one or more flip-flops (Figure 2.9(a)).

The programmable combinational logic block is usually implemented using lookup

Figure 2.9: Components of a generic FPGA

tables. A number of multiplexers (MUXs) are used to fine tune the behaviors of a CLU. They are used to select output from either the LUT or flip-flop, or both. They also control polarities of clock and other control signals. By carefully connecting the flip-flops and LUTs of different configurable logic units using the on-chip programmable routing network, *any* synchronous digital logic design can be implemented.

#### **Routing Network**

The routing network of an FPGA links different configurable logic units together to perform user defined logic. Many different routing networks have been proposed to balance performance with routability of an FPGA. FPGA routing networks are generally regular, consisting of groups of short local wires combined with long global wires. They are designed for maximum flexibilities without introducing long wire delays. Wire to wire connections are made through programmable switch boxes similar to that in Figure 2.9(b). Such programmable switch boxes allow flexible connections such as a T-joint.

## 2.3 A Continuum of Computing

On the surface, comparing the architecture of a single cycle processor with an ASIC design process seems remotely relevant. However, as it will be illustrated later, single cycle processors and ASIC designs can abstractly be viewed as extreme points in the broad spectrum of computing methods. This section gives an abstract understanding of reconfigurable computing with respect to other forms of computing in the hope to illustrate various benefits and trade-offs of reconfigurable computers.

#### 2.3.1 Spatial and Temporal Computing

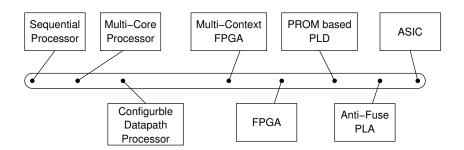

The fundamental function of a computer is to compute. Therefore, any machine that can perform the necessary computation to accomplish a user's conceptual design can be treated as a computer. In practice, there are many ways to perform computations. Example includes, but not limited to, sequential stored-program computing, communicating sequential processor (CSP), synchronous data flow, etc. Figure 2.10 organizes some of these computers in a hypothetical spectrum that corresponds roughly to how often the computer is reconfigured.

In general, machines on the left hand side of Figure 2.10 carries out computation sequentially, usually according to one or more instruction streams. Computations on these machines are serialized and spread over time. Consequently, they are in

Figure 2.10: A spectrum of computers

theory relatively slower than those machines on the right hand side of the spectrum. On the other hand, those machines on the right of the spectrum tend to perform computations in parallel. Since more computations are accomplished spatially at the same time, these machines are in theory faster.

In practice, however, parallel computation has its limitation. First, one must be able to express high level designs in parallel to take advantage of the underlying spatial computation paradigm. Unfortunately, it is a non-trivial problem. To effectively express a parallel high level design, a designer must possess fluent knowledge about the choice of design languages, software compilers or computer aided design (CAD) tools, as well as the underlying computer architecture. Second, parallel computations require multiple operations to take place at the same time. As a result, more time and efforts are needed to setup the machine and to route the appropriate data to perform these operations. Therefore, parallel machines are relatively less flexible than sequential machines during run-time.

One of the benefits of reconfigurable computers is therefore their theoretical abilities to deliver performance of highly parallel computers while offering flexibilities of traditional stored-program processors. Essentially, reconfigurable computers populate the middle section of Figure 2.10 by providing different mixes of spatial and temporal computing capabilities.

#### 2.3.2 Stored-Program Processor

On the far left of Figure 2.10 is a single cycle stored-program processor. Such processor carries out its operations according to a stored program. This stored program computing forms the fundamental computation architecture for almost all modern processors, which is sometimes referred as the "von Neumann" architecture. The notion of stored program machine can be dated back to the  $19^{th}$  century where mechanical looms used punch cards for controlling cloth patterns. The same punch card concept was used in the design of Charles Babbage's Analytical Machine in 1837. Punch cards are used in most early computers in the 1950s.

The use of punch cards in looms helps to clarify an important observation to understand reconfigurable computing: A processor instruction by itself is a simple machine configuration. This observation is especially apparent for a reduced instruction set computer (RISC) or a micro-coded machine where each machine instruction performs one simple task. For example, an add instruction configures the arithmetic and logic unit (ALU) of a processor to carry out an addition operation. It configures the ALU to take input from the correct register from the register file. It also configures the machine to write the result of the ALU to the correct output register. Given the sequential nature of stored-program computers, a "program" can be defined as a sequence of machine configurations. A sequential processor therefore "reconfigures" itself continuously according to the stored program.

Based on this observation, a stored program processor is therefore a fully temporal reconfigurable computer. At any given time, it performs only one operation. However, as observed by DeHon[12], it reconfigures itself after each operation, thereby spreading all operations over time.

#### 2.3.3 Fully Spatial Computation

On the other hand of the spectrum of computing is an application specific integrated circuit (ASIC). More precisely, it is the silicon wafer that is used to build an ASIC that is "configured" during the manufacturing process such that it will carry out certain computing operations. It is a form of fully spatial computation because at any given time, many operations are performed in parallel over space. Furthermore, the same set of operation is performed every time. In the case of a synchronous ASIC, the unit of time is a clock cycle. An ASIC never "reconfigures" itself. Once an ASIC is fabricated, its function is set.

Anti-fuse based PLAs are programmable after they are fabricated. However, they can only be programmed once. PROM based PLDs are truly *re*-configurable devices. However, because of the need of external configuring devices and their long configuration time, they are usually configured only once for a particular application and are rarely reconfigured over the life-time of a product.

On the other hand, FPGAs can be programmed in-system relatively quickly in the other of milliseconds. Because their configurations are stored in volatile memory, they can be reprogrammed quickly. As a result, despite being developed originally as replacements for ASICs, FPGAs are natural devices to perform fine grain reconfigurable computing.

#### 2.3.4 Between Spatial and Temporal Computing

Occupying the spectrum between a processor and an FPGA is a spectrum of reconfigurable computers that exploit the design space of temporal and spatial computing.

To add a temporal dimension to a fully spatial FPGA, multi-context devices are developed[28, 25, 44, 11]. Multiple configurations of the reconfigurable fabrics are stored, or cached, inside the device to allow rapid device reconfiguration. A temporal compute model is therefore established when a device is reconfigured (rapidly) as part of the native compute model. Furthermore, the temporal reconfiguration does not necessarily apply to the entire device. Modern FPGAs allow dynamic partial reconfiguration that reconfigures part of the device while the rest of the device continues to run.

On the other hand, to add a spatial dimension to a fully temporal processor, RCs such as PipeRench[38] introduced reconfigurable datapath to a simple sequential processor. Furthermore, RCs such as Garp[23] utilized reconfigurable fabrics as dynamically executed co-processors.

#### Trade-offs between Performance and Flexibility

The architectural design of a reconfigurable computer is often the result of a series of trade-offs between performance and flexibility. Depending on the context, the performance of a RC may be measured by its speed, power consumption or silicon area consumed. On the other hand, flexibility refers to how easy a machine can be programmed to perform different tasks.