# BREAKING THE ABSTRACTIONS FOR PRODUCTIVITY AND PERFORMANCE IN THE ERA OF SPECIALIZATION

A thesis

Presented to

The Academic Faculty

Ву

Jongse Park

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Computer Science

College of Computing

Georgia Institute of Technology August 2018

Copyright © Jongse Park 2018

## BREAKING THE ABSTRACTIONS FOR PRODUCTIVITY AND PERFORMANCE IN THE ERA OF SPECIALIZATION

### Approved by:

Dr. Hadi Esmaeilzadeh School of Computer Science College of Computing Georgia Institute of Technology

Dr. Hyesoon Kim School of Computer Science College of Computing Georgia Institute of Technology

Dr. Milos Prvulovic School of Computer Science College of Computing Georgia Institute of Technology Dr. Tushar Krishna School of Electrical and Computer Engineering College of Engineering Georgia Institute of Technology

Dr. Nam Sung Kim Department of Electrical and Computer Engineering University of Illinois, Urbana-Champaign

Date Approved: July 16, 2018

All things are difficult before they are easy

Thomas Fuller

Dedicated to my wife, Tsuping.

#### **ACKNOWLEDGEMENTS**

Foremost, I would like to express my sincere gratitude to my advisor Prof. Hadi Esmaeilzadeh for the continuous support of my Ph.D study and research, for his patience, motivation, enthusiasm, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to thank the rest of my thesis committee, Prof. Hyesoon Kim, Prof. Tushar Krishna, Prof. Milos Prvulovic, and Prof. Nam Sung Kim, for their encouragement, insightful comments, and hard questions.

I am grateful to my internship mentors for offering me amazing opportunities in their groups and leading me working on diverse exciting projects. At Microsoft Research, I had the privilege to closely work with Dr. Doug Burger and Dr. Eric Chung. At NVIDIA Research, I had the privilege to closely work with Steve Keckler, Arslan Zulfigar, and Eiman Ebrahimi.

I thank my fellow students in ACT Lab, Amir Yazdanbaksh, Bradley Thwaites, Divya Mahajan, Hardik Sharma, Joon Kyung Kim, Jacob Sacks, Emmanuel Amaro, Anandhavel Nagendrakumar, Soroush Ghodrati, and Ahmed Elthakeb, for the stimulating discussions, for the sleepless nights we were working together before deadlines, and for all the fun we have had in the last five years. I should also thank Prof. Mayur Naik and Dr. Xin Zhang for giving me tremendous help in growing as a researcher in the early phase of my Ph.D. study.

I am also deeply grateful to Dr. Seungryoul Maeng and Dr. Jaehyuk Huh for enlightening me the first glance of research.

I thank Kwanjeong Educational Foundation Scholarship for generous financial support for last five years and giving me opportunities to meet fellow researchers from various fields.

I would like to thank my family. My father, Sangkyu Park, my mother, Jungsuk Kong, my sister, Yoonse Park, my in-laws, Chungfu Wang, Hungnan Li, Tsufu Wang, Tsuming Wang, Tsuyu Wang, Tsui Wang, Sam Jon, my nephew, Logan Jon, and my unborn niece, Kidong, have given me unconditional love, trust, and support.

Last but not the least, I would like to express my deepest love and gratitude to my wife, Tsuping. I cannot imagine how my life as a Ph.D. student would have been without her. Her dedication, encouragement, and endurance helped me complete everything that I have achieved in recent years. Moreover, I thank my wife for sharing with me every moment of the last 10 years.

## **TABLE OF CONTENTS**

| Ackno   | wledgn   | nents                                                                 | V    |

|---------|----------|-----------------------------------------------------------------------|------|

| List of | Tables   |                                                                       | xii  |

| List of | Figure   | s                                                                     | xiii |

| Summ    | ary      |                                                                       | xvii |

| Chapte  | er 1:Int | roduction                                                             | 1    |

| 1.1     |          | ving Performance and Productivity for Acceleration of Ma-<br>Learning | 2    |

|         | 1.1.1    | Full Stack Solution for Scale-Out Acceleration of Learning            | 3    |

|         | 1.1.2    | Algorithmic Approaches to Accelerate Machine Learning.                | 4    |

| 1.2     | Impro    | ving Productivity in Approximate Computing                            | 5    |

|         | 1.2.1    | Practical Approximate Programming                                     | 6    |

|         | 1.2.2    | Crowdsourcing Quality Target Determination in Approximate Computing   | 7    |

| 1.3     | Thesis   | s Contributions                                                       | 8    |

| Chapte  | er 2:Sca | ale-Out Acceleration of Machine Learning                              | 10   |

| 2.1     | Introd   | uction                                                                | 10   |

| 2.2     | Distrib  | outed Learning                                                        | 16   |

|     | 2.2.1  | Learning as Stochastic Optimization               | 16 |

|-----|--------|---------------------------------------------------|----|

|     | 2.2.2  | Parallelizing Stochastic Optimization             | 17 |

| 2.3 | CoSM   | IC System Software                                | 19 |

|     | 2.3.1  | Execution and Acceleration Flow                   | 19 |

|     | 2.3.2  | Task Assignment in the System Software            | 20 |

| 2.4 | The C  | oSMIC Stack                                       | 22 |

|     | 2.4.1  | Programming Layer                                 | 22 |

|     | 2.4.2  | Compilation Layer                                 | 25 |

|     | 2.4.3  | System Layer                                      | 26 |

|     | 2.4.4  | Architecture Layer                                | 26 |

|     | 2.4.5  | Circuit Layer                                     | 29 |

| 2.5 | Templa | ate Architecture                                  | 29 |

|     | 2.5.1  | Accelerator Organization                          | 31 |

|     | 2.5.2  | Multi-Threaded Acceleration                       | 34 |

| 2.6 | CoSM   | IC Compilation                                    | 35 |

| 2.7 | In-Net | work Acceleration of Gradient Compression         | 39 |

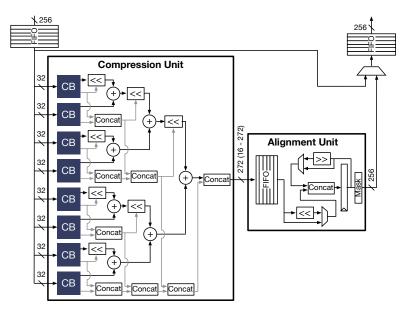

|     | 2.7.1  | Compression Algorithm                             | 40 |

|     | 2.7.2  | Decompression Algorithm                           | 41 |

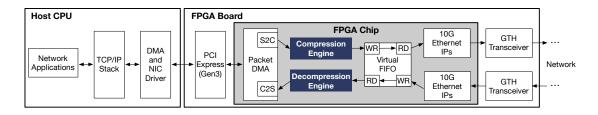

|     | 2.7.3  | Accelerator Architecture and Integration with NIC | 42 |

| 2.8 | Evalua | ation                                             | 46 |

|     | 2.8.1  | Methodology                                       | 46 |

|     | 2.8.2  | Experimental Results                              | 50 |

|     |        | 2.8.2.1 Performance Comparison                    | 50 |

|   |       |         | 2.8.2.2   | Scalability                                                 | 51 |

|---|-------|---------|-----------|-------------------------------------------------------------|----|

|   |       |         | 2.8.2.3   | Comparison of Different Acceleration Platforms .            | 53 |

|   |       |         | 2.8.2.4   | Sensitivity to Mini-Batch Size                              | 55 |

|   |       |         | 2.8.2.5   | Sources of Speedup                                          | 57 |

|   |       |         | 2.8.2.6   | Sensitivity to FPGA Resources and Bandwidth .               | 57 |

|   |       |         | 2.8.2.7   | Design Space Exploration                                    | 59 |

|   |       |         | 2.8.2.8   | Comparison with TABLA                                       | 61 |

|   | 2.9   | Relate  | ed Work   |                                                             | 62 |

|   | 2.10  | Concl   | usion .   |                                                             | 64 |

|   | 2.11  | Algori  | thmic App | proaches for ML Acceleration                                | 65 |

| C | hapte | r 3:Laı | nguage S  | Support for Approximate Programming                         | 68 |

|   | 3.1   | Introd  | uction .  |                                                             | 68 |

|   | 3.2   | Backg   | round .   |                                                             | 71 |

|   |       | 3.2.1   | Fine-Gra  | ained Approximation                                         | 71 |

|   |       | 3.2.2   | Coarse-   | Grained Approximation                                       | 72 |

|   | 3.3   | FlexJa  | ava Langı | uage Design                                                 | 73 |

|   |       | 3.3.1   | Safe Pro  | ogramming in FlexJava                                       | 73 |

|   |       | 3.3.2   | Modular   | Approximate Programming                                     | 78 |

|   |       | 3.3.3   | OO Prog   | gramming in FlexJava                                        | 81 |

|   |       | 3.3.4   |           | ity in FlexJava: Support for Coarse-Grained Aption          | 83 |

|   |       | 3.3.5   |           | for Expressing Quality Metrics, Quality Requireand Recovery | 85 |

| 3.4    | FlexJa | ava Implementation                                                  |

|--------|--------|---------------------------------------------------------------------|

|        | 3.4.1  | Implementation of Annotations                                       |

|        | 3.4.2  | Integrated Highlighting Tool                                        |

| 3.5    | Appro  | ximation Safety Analysis                                            |

|        | 3.5.1  | Core Language                                                       |

|        | 3.5.2  | Concrete Semantics                                                  |

|        | 3.5.3  | Static Analysis                                                     |

| 3.6    | Evalua | ation                                                               |

|        | 3.6.1  | RQ1: Number of Annotations                                          |

|        | 3.6.2  | RQ2: Programmer Effort/Annotation Time 99                           |

|        | 3.6.3  | RQ3: Energy Reduction and Speedup 101                               |

|        |        | 3.6.3.1 Fine-Grained Approximation                                  |

|        |        | 3.6.3.2 Coarse-Grained Approximation                                |

| 3.7    | Relate | ed Work                                                             |

| 3.8    | Concl  | usion                                                               |

| 3.9    |        | vare Description Lauguage (HDL) Support for Approximate vare Design |

| Chapte |        | derstanding and Controlling Quality in Approximate Comting          |

| 4.1    | Introd | uction                                                              |

| 4.2    | Overv  | iew 112                                                             |

| 4.3    | The T  | hree Games                                                          |

|        | 4.3.1  | Pollice Verso                                                       |

|        | 4.3.2   | WinABatt                                                 |

|--------|---------|----------------------------------------------------------|

|        | 4.3.3   | QnA                                                      |

| 4.4    | Statist | ical Analysis                                            |

|        | 4.4.1   | Binomial Proportion Confidence Interval                  |

| 4.5    | Statist | ical Quality Guarantees for Approximate Acceleration 126 |

| 4.6    | Evalua  | ation                                                    |

|        | 4.6.1   | Methodology                                              |

|        | 4.6.2   | Statistical Projections                                  |

|        | 4.6.3   | Collected Statistics from the Games                      |

|        | 4.6.4   | User Response Variations                                 |

|        | 4.6.5   | Changing the Tradeoff for Approximate Computing 139      |

|        | 4.6.6   | Discussion                                               |

| 4.7    | Relate  | ed Work                                                  |

| 4.8    | Concl   | usion                                                    |

| 4.9    | Other   | Work of This Author in Approximate Computing 144         |

| Chapte | r 5:Fut | ture Directions                                          |

| 5.1    | Pushii  | ng Intelligence to the Edge                              |

| 5.2    | Online  | e Learning at the Edge                                   |

| 5.3    | Private | e and Secure Learning                                    |

| Refere | nces .  |                                                          |

## **LIST OF TABLES**

| 2.1 | Benchmarks, algorithms, application domains, and datasets                                                                                                                         | 47  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | CPU, GPU, FPGA, and P-ASICs                                                                                                                                                       | 49  |

| 2.3 | Number of threads and FPGA resource utilization                                                                                                                                   | 60  |

| 3.1 | Error probabilities and energy savings for different operations in fine-grained approximation. We consider the three hardware settings of Mild, Medium, and Aggressive from [119] | 72  |

| 3.2 | Benchmarks, quality metrics, and results of safety analysis: analysis runtime and # of approximable data and operations                                                           | 95  |

| 4.1 | Applications and their quality metric.                                                                                                                                            | 127 |

## **LIST OF FIGURES**

| 2.1  | Execution and acceleration flow within each node                                                                                 | 19 |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | System software in a Sigma node                                                                                                  | 21 |

| 2.3  | The full CoSMIC stack                                                                                                            | 23 |

| 2.4  | (a) Programmer specifies the classification algorithm as its gradient and aggregation functions. (b) Translator outputs the DFG. | 24 |

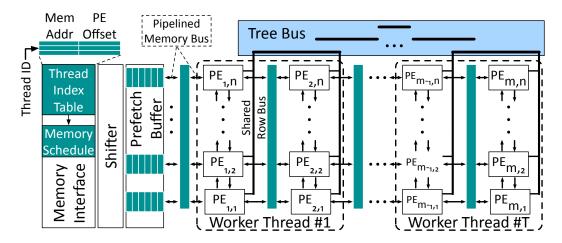

| 2.5  | CoSMIC Multi-Threaded Template Architecture                                                                                      | 30 |

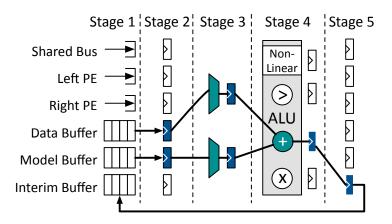

| 2.6  | Pipelined PE. Black highlights an Add operation (InterimBuffer[i] = DataBuffer[j] + ModelBuffer[k])                              | 32 |

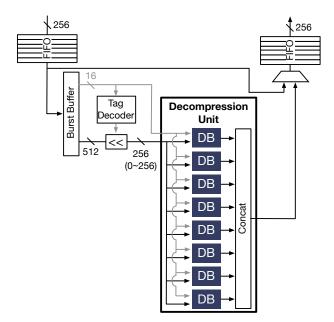

| 2.7  | Overview of NIC architecture integrated with compressor and decompressor                                                         | 43 |

| 2.8  | 256-bit burst compressor architecture                                                                                            | 44 |

| 2.9  | 256-bit burst decompressor architecture                                                                                          | 45 |

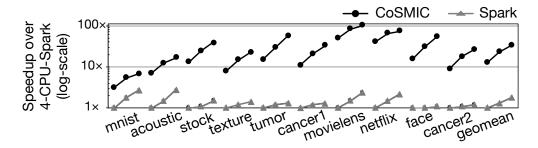

| 2.10 | Speedup over Spark as the number of nodes increases from 4 to 8 to 16. Baseline: Spark system with 4 nodes (4-CPU-Spark)         | 51 |

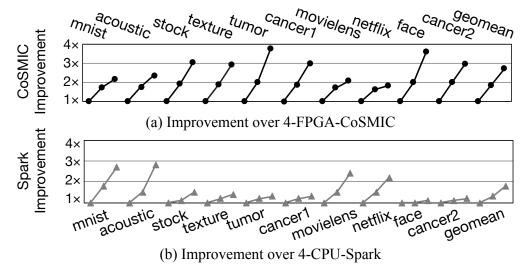

| 2.11 | Scalability comparison of CoSMIC and Spark as the number of nodes increases from 4 to 8 to 16                                    | 52 |

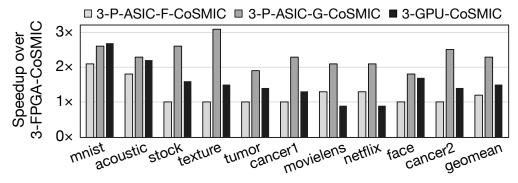

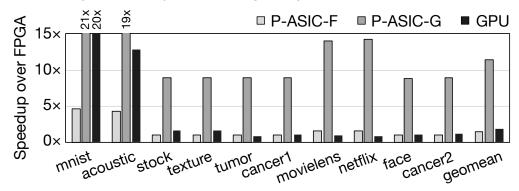

| 2.12 | System-wide speedup over 3-FPGA-CoSMIC                                                                                           | 53 |

| 2.13 | Computation speedup over FPGA                                                                                                    | 53 |

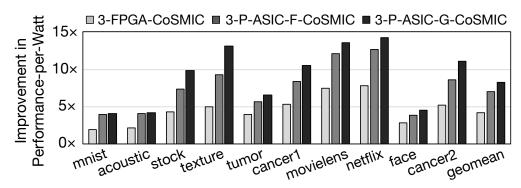

| 2.14 | Performance-per-Watt, baseline: 3-GPU system                                                                                     | 54 |

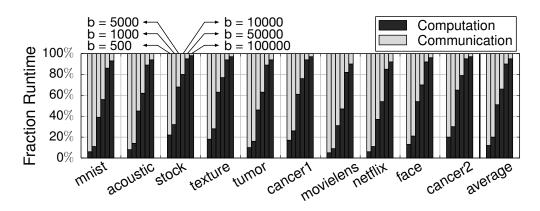

| 2.15 | Fraction of 3-FPGA-CoSMIC runtime.                                                                                               | 55 |

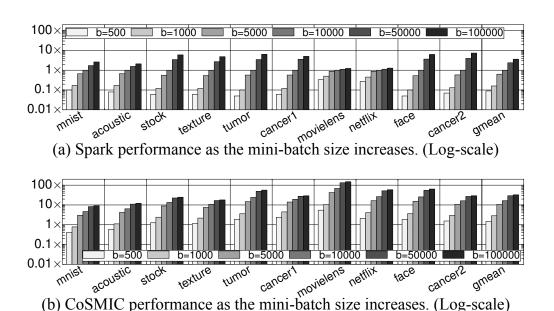

| 2.16 | baseline: 3-node Spark when the mini-batch size is 10,000                                                                                         | 56  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

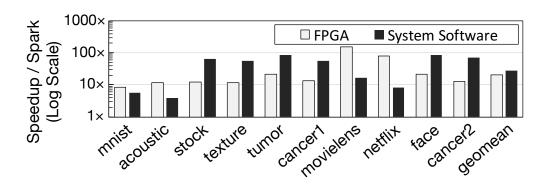

| 2.17 | Speedup breakdown between FPGAs and system software (aggregation, networking, and management) for 3-FPGA-CoSMIC                                   | 57  |

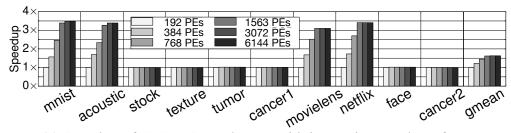

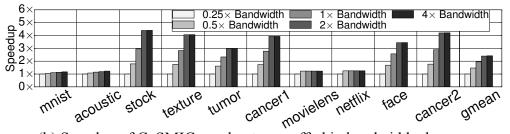

| 2.18 | Speedup comparison with varying number of PEs and memory bandwidth for CoSMIC accelerators                                                        | 58  |

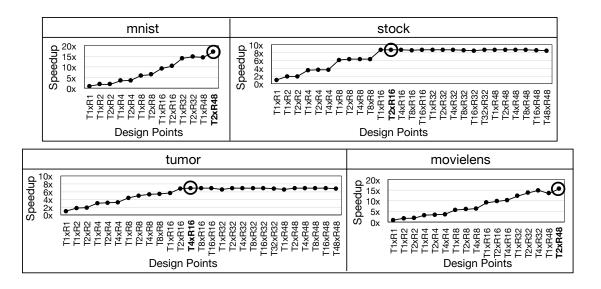

| 2.19 | Design space exploration; $Tx \times Ry$ , $x$ represents the number of threads and $y$ represents the number of rows; baseline: $T1 \times R1$ . | 59  |

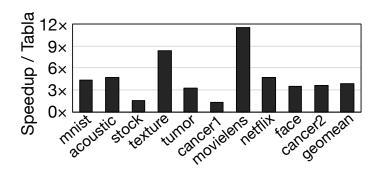

| 2.20 | Speedup of CoSMIC's template architecture over TABLA's                                                                                            | 61  |

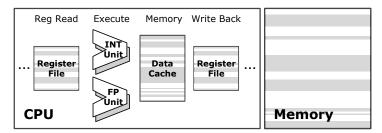

| 3.1  | A processor that supports fine-grained approximation. The shaded units perform approximate operations or store data in approximate storage        | 71  |

| 3.2  | An abstract class for defining the quality metric                                                                                                 | 86  |

| 3.3  | FlexJava annotations are implemented as a library                                                                                                 | 86  |

| 3.4  | Language syntax                                                                                                                                   | 89  |

| 3.5  | Semantic domains                                                                                                                                  | 89  |

| 3.6  | Concrete semantics of approximation safety                                                                                                        | 91  |

| 3.7  | Approximation safety analysis.                                                                                                                    | 93  |

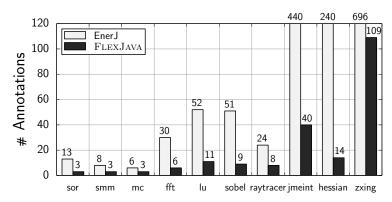

| 3.8  | Number of annotations required to approximate the same set of data and operations using EnerJ and FlexJava                                        | 97  |

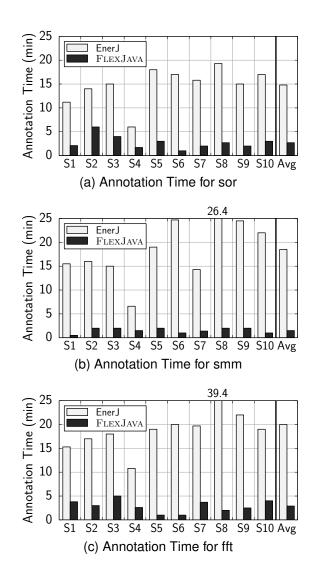

| 3.9  | Annotation time with EnerJ and FlexJava for (a) sor, (b) smm, and (c) fft. The x-axes denotes the user study subjects                             | 99  |

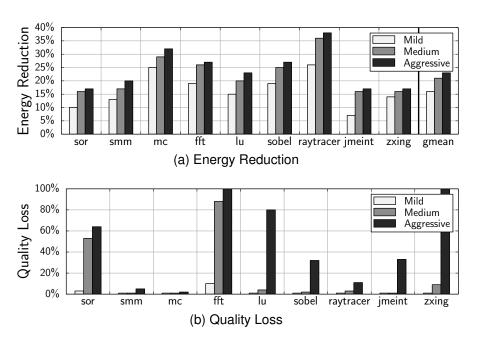

| 3.10 | (a) Energy reduction and (b) quality loss when approximating all the safe-to-approximate data and operations.                                     | 102 |

| 3.11 | Speedup, energy reduction, and output quality loss when the approximate annotated functions using the NPU                                         | 103 |

| 4.1 | AxGames is a crowdsourcing solution that transforms the trade-<br>off between quality and energy-performance gains from approxi-<br>mation to the tradeoff between the gains and user satisfaction                                                                                                                                                                                                         | 109 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

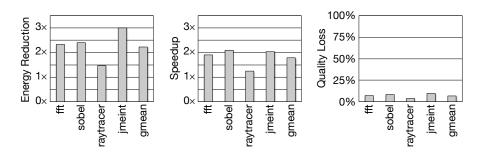

| 4.2 | An overview of the AxGames crowdsourcing solution which determines the user-driven quality target for a given approximated application.                                                                                                                                                                                                                                                                    | 112 |

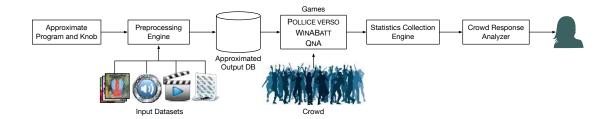

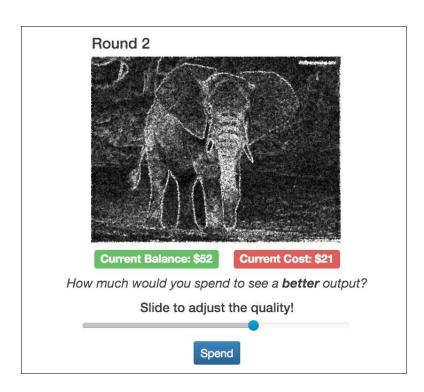

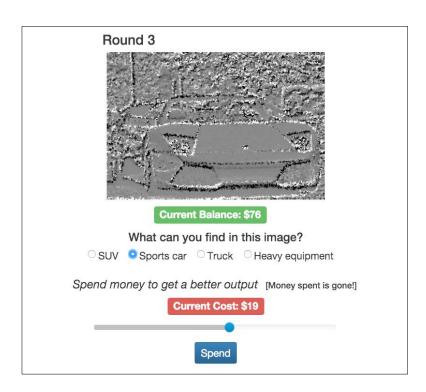

| 4.3 | A round of the Pollice Verso game when deployed for an approximated implementation of the jpeg application                                                                                                                                                                                                                                                                                                 | 116 |

| 4.4 | A round of the WinABatt game when deployed for an approximated implementation of the sobel application                                                                                                                                                                                                                                                                                                     | 119 |

| 4.5 | A round of the QnA game when deployed for an approximated implementation of the emboss application.                                                                                                                                                                                                                                                                                                        | 121 |

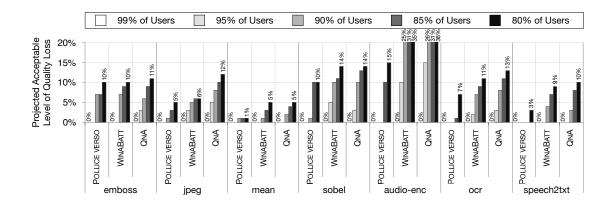

| 4.6 | Projected acceptable level of quality loss with 95% confidence. These levels of quality are projected by our statistical analysis based on the game plays of 100 Mechanical Turk workers. Starting from left, each bar corresponds to the level that is projected to satisfy 99%, 95%, 90%, 80%, and 80% of the applications' users. These projections vary significantly across the applications          | 132 |

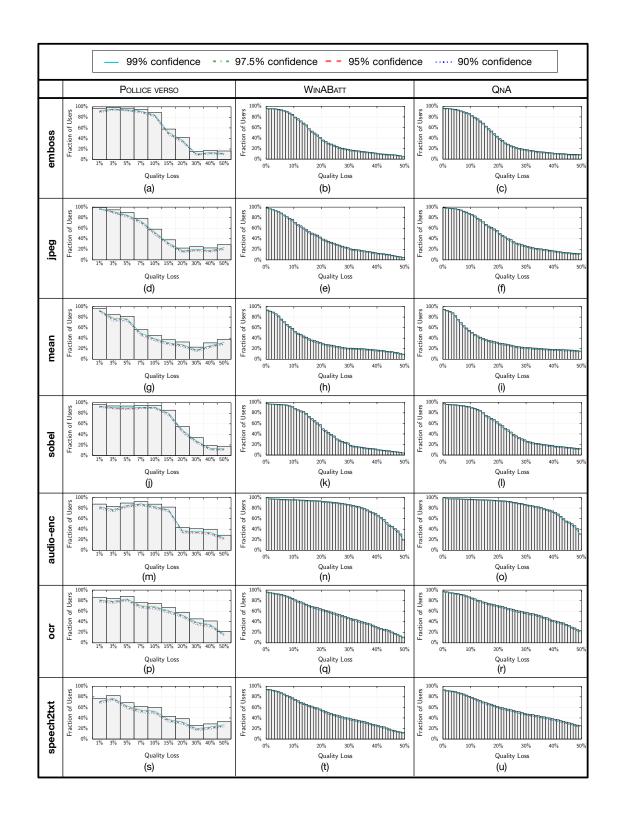

| 4.7 | The collected statistics and the statistical projections. The bars show the fraction of players that selected a certain level of quality loss as "Good Enough." The lines represent the lower bound of the binomial confidence interval with different degrees of confidence, including 99%, 97.5%, 95%, and 90%                                                                                           | 135 |

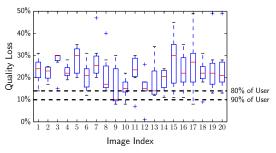

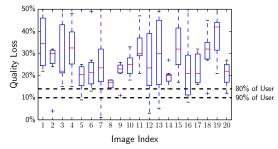

| 4.8 | The box plot distribution of the players' choices of quality for sobel. The dashed horizontal lines show the projected acceptable level of quality loss that satisfies 80% and 90% of the users with 95% confidence (a) based on WinABatt and (b) QnA                                                                                                                                                      | 137 |

| 4.9 | Outputs from the edge detection filter, sobel, for image 13 in Figure 4.8b. The leftmost output is the precise version and the rest are the approximated outputs. The approximated outputs (b) and (c) have 10% and 14% of quality loss that satisfy 90% and 80% of the users, respectively. The output (d) has 30% of quality loss, which is the median of the votes for the image 13 from the QnA plays. | 138 |

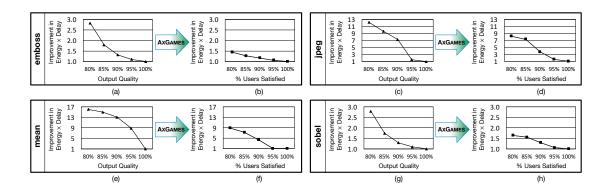

| 4.10 | Improvement in energy-delay products vs. output quality (a, c, e,     |     |

|------|-----------------------------------------------------------------------|-----|

|      | and g), and vs. % users satisfied. (b, d, f, and h). The results in   |     |

|      | (b), (d), (f), and (h) are based on the statistics collected from the |     |

|      | QnA plays.                                                            | 140 |

### **SUMMARY**

Over the last decades, general-purpose computing stack and its abstractions have provided both performance and productivity, which have been the main drivers for the revolutionary advances in IT industry. However, the computational demand of emerging applications grows rapidly and the rate of data generation exceeds the level where the capabilities of current computing systems can match. The challenges have coincided with the Dark Silicon era in which conventional technologies offer insufficient performance and energy efficiency. Thus, it is timely to move beyond conventional techniques and explore radical approaches that can overcome the limitations of general-purpose systems and deliver large gains in performance and efficiency. One such approach is specialization, where the hardware and systems are developed for a domain of applications. However, the specialization creates a tension between the performance and productivity, since (1) programmers need to delve into the details of specialized hardware, and (2) perform low-level programming. Hence, the objectives are (1) delivering large gains in performance and efficiency (2) while retaining automation and productivity through high-level abstractions. Achieving both of these conflicting objectives is a crucial challenge to place the specialization techniques in a position of practical utility, which is the main focus of this dissertation research. My works offer algorithm-driven computing stacks, which span from algorithms and languages to micro-architectural designs. I have primarily focused on two paradigms of specialization: acceleration and approximation.

### Chapter 1

### INTRODUCTION

Conventionally, general-purpose computing has offered both performance and productivity, which delivered numerous capabilities for our lives. However, the computational demand of emerging applications grows rapidly and the rate of data generation exceeds the level where the capabilities of current computing systems can match. The challenges have coincided with the Dark Silicon era in which conventional technologies offer insufficient performance and energy efficiency. To tackle these challenges, community has started exploring radical approaches that can overcome the limitations of general-purpose systems while providing large performance and efficiency benefits. In this dissertation, we focus on one such solution, hardware specialization. While the specialization techniques offer significant gains in performance and efficiency, they create a tension between the performance and productivity, since (1) programmers need to delve into the details of specialized hardware, and (2) perform low-level programming. Hence, the objectives are (1) delivering large gains in performance and efficiency (2) while retaining automation and productivity through high-level abstractions. Achieving both of these conflicting objectives is a crucial challenge to place the specialization techniques in a position of practical utility, which is the main focus of this dissertation research. My works offer algorithm-driven computing stacks, which span from algorithms and languages to micro-architectural designs. I have primarily focused on two paradigms of specialization: acceleration and approximation. My efforts in acceleration leverage algorithmic insights to redefine the hardware-software abstractions and enable programmers to automatically utilize hardware accelerators (e.g., FPGAs) in scale-out setting for emerging workloads, such as data analytics and machine learning. For approximation, I have devised programming language and crowdsourcing software engineering solutions that improve the productivity and utility of approximation technologies, and bridges the gap between unconventional research innovations and practical real-world applications.

## 1.1 Resolving Performance and Productivity for Acceleration of Machine Learning

A growing number of commercial and enterprise systems increasingly rely on compute-intensive Machine Learning (ML) algorithms. Hardware accelerators offer several orders of magnitude higher performance than general-purpose processors and provide a promising path forward to accommodate the needs of ML algorithms. Even software companies have begun to incorporate various forms of accelerators in their data centers. Microsoft's Project Brainwave integrated FPGAs in datacenter scale for real-time AI calculations and Google developed the TPU as a specialized matrix multiplication engine for machine learning. However, not only do the benefits come with the cost of lower programmability, but also the acceleration requires long development cycles and extensive expertise in hardware design. Moreover, conventionally, accelerators are integrated with the existing computing stack by profiling hot regions of code and offloading the computation to the accelerators. This approach is suboptimal since the stack is designed and optimized merely for CPUs, the sole processing platform up until very recently. To tackle these challenges, we

developed cross-stack and algorithm-hardware co-designed solutions that rebuild the computing stack for acceleration of machine learning. These solutions break the conventional abstractions of computing stack by reworking the entire layers of computing stack, which include programming language, compiler, system software, accelerator architecture, and circuit generator.

### 1.1.1 Full Stack Solution for Scale-Out Acceleration of Learning

Recently, community has started exploring mostly single-node acceleration techniques to meet the massive compute demand of ML. In a concurrent yet disjoint effort, others have also explored the use of distributed general-purpose systems (e.g., Spark and Hadoop) as a mean to scale the learning frameworks. However, there is a gap between these accelerators and scale-out systems due to the lack of solutions that enable distributed acceleration of learning at scale. To bridge these two paradigms, we developed CoSMIC [1], a full computing stack that constitutes language, compiler, system software, template architecture, and circuit generators, which enable programmable acceleration of learning at scale. CoSMIC enables programmers to exploit scale-out acceleration using FPGAs and Programmable ASICs (P-ASICs) from a high-level and mathematical Domain-Specific Language (DSL). Nonetheless, CoSMIC does not require programmers to delve into the onerous task of system software development or hardware design. CoSMIC achieves three conflicting objectives of efficiency, automation, and programmability, by integrating a novel multi-threaded template accelerator architecture and a cohesive stack that generates the hardware and software code from its high-level DSL. CoSMIC can accelerate a wide range of learning algorithms that are most commonly trained using parallel variants of gradient descent. The key is to distribute partial gradient calculations of the learning algorithms across the accelerator-augmented

nodes of the scale-out system. Additionally, CoSMIC leverages the parallelizability of the algorithms to offer multi-threaded acceleration within each node. Multi-threading allows CoSMIC to efficiently exploit the numerous resources that are becoming available on modern FPGAs/P-ASICs by striking a balance between multi-threaded parallelism and single-threaded performance. CoSMIC takes advantage of algorithmic properties of machine learning to offer a specialized system software that optimizes task allocation, role-assignment, thread management, and internode communication. While accelerators gain traction, their integration in the system stack is not well understood. CoSMIC takes an initial step toward such an integration for an important class of applications, while providing generality and a high-level programming interface.

### 1.1.2 Algorithmic Approaches to Accelerate Machine Learning.

As a preliminary effort for the CoSMIC project, in collaboration with my fellow graduate students, we developed a single-node FPGA accelerator generation framework for data analytics, dubbed TABLA [2], which enables FPGA acceleration from high-level specifications of algorithms. We open-sourced the code and it is available at <a href="http://act-lab.org/artifacts/tabla">http://act-lab.org/artifacts/tabla</a>. TABLA leverages the insight that many learning algorithms can be solved using stochastic gradient descent that minimizes an objective function. The solver is fixed while the objective function changes with the learning algorithm. Therefore, TABLA uses stochastic optimization as the abstraction between hardware and software. Consequently, programmers specify the learning algorithm by merely expressing the gradient of the objective function in our domain specific language. TABLA then automatically generates the synthesizable implementation of the accelerator for FPGA realization using a set of template designs. Real hardware measurements show orders of magnitude higher performance and power efficiency

while the programmer only writes 60 lines of code.

As a follow-on work, we developed DNNWEAVER [3], a framework that automatically generates a synthesizable accelerator for a given (DNN, FPGA) pair from a high-level specification in Caffe. To achieve large benefits while preserving automation, we devised hand-optimized design templates that the DNNWEAVER framework uses to generate the accelerators. First, DNNWEAVER translates a given high-level DNN specification to its novel ISA that represents a macro dataflow graph of the DNN. The DNNWEAVER compiler is equipped with our optimization algorithm that tiles, schedules, and batches DNN operations to maximize data reuse and best utilize target FPGA's memory and other resources. The final result is a custom synthesizable accelerator that best matches the needs of the DNN while providing high performance and efficiency gains for the target FPGA.

### 1.2 Improving Productivity in Approximate Computing

Approximate computing is another form of specialization, which brings forth an unconventional yet innovative computing paradigm that trades accuracy of computation for otherwise hard-to-achieve performance and efficiency. This new computing paradigm is built upon the property that emerging applications (e.g., sensor processing, translation, vision, and data analytics) are increasingly tolerant to imprecision. Leveraging this property, approximation techniques are able to provide orders of magnitude higher performance and efficiency gains, while maintaining the acceptable level of functionalities. However, these techniques are only pragmatic when (1) they are easy to use for the programmers, and (2) they produce acceptable output quality from the perspective of application users. To this end, my research efforts for approximation focus on improving

productivity and utility of approximation technologies by developing programming language and crowdsourcing-based software engineering solutions.

### 1.2.1 Practical Approximate Programming

While approximate computing is currently a hot area, the programmability of approximation techniques is still one of the pivotal challenges to enable their practical and prevalent use. State-of-the-art approximate programming models require extensive manual annotations on program data and operations to quarantee safe execution of approximate programs. The need for extensive manual annotations hinders the pragmatic use of approximation techniques. We developed a small set of language extensions, dubbed FlexJava, that significantly reduces the annotation effort, paving the way for practical approximate programming [4]. These extensions enable programmers to annotate approximationtolerant method outputs. The FlexJava compiler, which is equipped with an approximation safety analysis, automatically infers the operations and data that affect these outputs and selectively marks them as approximable while providing safety guarantees. The automation and the language-compiler co-design relieve programmers from manually and explicitly annotating data declarations or operations as safe to approximate. FlexJava is designed to support safety, modularity, generality, and scalability in software development. Compared to other models, FlexJava largely reduces the number of annotations and programmers spend significantly less time annotating programs based on our user study.

# 1.2.2 Crowdsourcing Quality Target Determination in Approximate Computing

Approximation is useful only if its impact on application output quality is acceptable to the users. However, there is a lack of systematic solutions and studies that explore users' perspective on the effects of approximation. We sought to provide one such solution for the developers to probe and discover the boundary of quality loss that most users will deem acceptable. We proposed AXGAMES, a crowdsourced solution that enables developers to readily infer a statistical common ground from the general public through three entertaining games [5]. The users engage in these games by betting on their opinion about the quality loss of the final output while the AXGAMES framework collects statistics about their perceptions. The framework then statistically analyzes the results to determine the acceptable levels of quality for a pair of (application, approximation technique). The three games are designed such that they effectively capture quality requirements with various tradeoffs and contexts. We recruited 700 participants/users through Amazon's Mechanical Turk to play the games that collect statistics about their perception on different levels of quality. Subsequently, the AXGAMES framework uses the Clopper-Pearson exact method statistically project the quality level that satisfies a given percentage of users. The developers can use these statistical projections to tune the level of approximation based on the user experience.

In addition to the aforementioned works, I have worked on many collaborative projects that aim to develop hardware-software co-designed approximation techniques. These techniques seek opportunities for approximation at various components of computing stack, which span from neural accelerators [6, 7] and memory subsystems [8] to GPUs [9] and hardware description languages [10].

### 1.3 Thesis Contributions

This dissertation makes the following contributions.

- 1. We propose a series of full-stack solutions that bridge the semantic gap between the programmers and specialized accelerators by leveraging the algorithmic insights of Machine Learning algorithms. We provide CoSMIC—Computing Stack for ML acceleration In the Cloud—that offers a complete computing stack for scale-out acceleration of machine learning, which comprises a domain-specific language, a compiler, a specialized runtime system, and a multi-threaded template architecture for the accelerator. As its prior effort, we propose TABLA—a single node predecessor of CoSMIC—that enables the automated acceleration of Machine Learning on FPGAs. DnnWeaver is another work in the same line of research, which enables the acceleration of DNN inference on FPGAs from high-level specification of DNN models. Chapter 2 describes these solutions in more detail.

- 2. We provide a practical and automated programming model, FlexJava, for approximation techniques, which leverages automated program analysis techniques for more effective approximate programming. Such effort is imperative to enabling the widespread applicability of approximation techniques. The FlexJava language is designed to be intuitive and support essential aspects of modern software development: safety, modularity, generality, and scalability. We believe that FlexJava takes an effective and necessary step toward leveraging approximation in modern software development. Chapter 3 elaborates the language constructs, analysis, and evaluation in detail.

3. We provide an automated programming tool, AxGames, that methodically utilize crowdsourcing in identifying the desirable application output quality from the final users. This readily available tool provides a path for the research community to better assess their innovative approximation techniques. The framework enables developers to conveniently study user responses at scale and gain statistical confidence when deploying approximated applications. Our results from examining a variety of applications show the necessity of solutions such as AxGames since the crowd's response to approximation varies drastically across different applications, tradeoff, and context. These results suggests that AxGames can add an unexplored, yet important, dimension to the research and development in approximate computing. Chapter 4 illustrates the three games, statistical analysis, and experiments including user studies, in more detail.

### **Chapter 2**

### SCALE-OUT ACCELERATION OF MACHINE LEARNING

### 2.1 Introduction

Prevalence of interconnected compute platforms has transformed the IT industry, which is now rapidly moving towards scale-out solutions that extract insights from data. Following this trend, systems that enable distributed computing on general-purpose platforms are gaining eminence (e.g., Spark [16] and Hadoop [17]). In a concurrent yet disjoint effort, due to the diminishing benefits from general-purpose processing, the community is developing mostly singlenode accelerators for a variety of applications, including machine learning [18, 19, 20, 21, 22, 23, 24, 25, 3, 2]. However, there is a gap between scale-out systems and accelerators due to the lack of solutions that enable distributed acceleration at scale. Moreover, it is not enough to just design and integrate accelerators independent from algorithms and programming interfaces. We need a holistic approach that reworks the fundamental hardware-software abstractions and enables a broad community of programmers to seamlessly utilize accelerators at scale for a specific domain of applications. Reusing the traditional stack for scale-out acceleration is inadequate as the entire computing stack is designed and optimized merely for CPUs, which were the sole processing platform up until recently. To that end, this work sets out to design a full

and specialized computing stack, dubbed CoSMIC<sup>1</sup>, for scale-out acceleration of learning.

CoSMIC offers the entire stack of layers to execute a wide range of learning algorithms on accelerator-augmented scale-out systems. These layers comprise a domain-specific language, a compiler, a specialized runtime system, and a multi-threaded template architecture for the accelerator. The template architecture can be automatically tailored for deployment on FPGAs or realization as custom Programmable ASICs (P-ASICs). FPGAs offer flexibility as well as efficiency and are becoming readily available in different markets [26, 27, 28, 29], now even in Amazon Elastic Compute Cloud (EC2) [29]. Not only have FPGAs become a lower-cost alternative to ASICs, but also serve as prototypes for custom chip design. However, designing efficient accelerators is onerous even when targeting a single-node FPGA and requires extensive expertise in both hardware design and application domain. This challenge is exacerbated in the scale-out setting due to the added complexity of task distribution and communication. Additionally, P-ASICs impose high non-recurring engineering costs over long design periods and usually need unintuitive or narrow programming interfaces. Furthermore, as technology is scaled, modern FPGAs and ASICs can harbor an ample amount of resources, whose effective utilization necessitates rethinking accelerator design paradigms. Therefore, to realize scale-out acceleration, we address the following triad of challenges when devising the CoSMIC full stack: (1) efficiently exploiting large number of on-chip resources, (2) enabling distributed acceleration using accelerator-augmented nodes, and (3) relieving programmers of distributed system coordination and the onus of hardware design. Furthermore, CoSMIC targets a wide class of learning algorithms and provides support for new learning models and algorithmic changes

<sup>&</sup>lt;sup>1</sup>CoSMIC: Computing Stack for ML acceleration In the Cloud

to the existing ones. To realize CoSMIC we were required to address the following research challenges.

# (1) How to enable scale-out acceleration of many ML algorithms, yet disengage programmers from hardware design.

To tackle this challenge, CoSMIC leverages a combination of two theoretical insights: (1) a wide range of learning algorithms are stochastic optimization problems, solved using a variant of gradient descent [30, 31, 2]; (2) differentiation is a linear mathematical operator, and thus the gradient over a set of data points can be calculated as an aggregated value over the partial gradients computed in parallel for each point [32, 33, 34, 35, 36, 37, 38]. A variety of learning algorithms can be parallelized using these two insights. Examples include, but are not limited to, recommender systems, Kalman filters, linear and nonlinear regression models, support vector machines, least square models, logistic regression, backpropagation, softmax functions, and conditional random fields. To implement these algorithms, one needs to have (1) the partial gradient calculation function, (2) the aggregation operator, and (3) the number of data points that are processed before each aggregation. The first layer of the CoSMIC stack exposes a high-level mathematical language to programmers to specify these three constructs, which capture the entirety of the learning algorithm. The next layer of the CoSMIC stack fully automates the scale-out acceleration. The CoSMIC compiler maps and schedules the operations on the distributed accelerators. The next layer, a specialized runtime system, assigns roles and tasks for the scale-out system components and orchestrates the distributed calculation of the partial gradients and their iterative aggregation. The final layer of the CoSMIC stack provides a novel multi-threaded template architecture for the accelerators. This layer can be automatically customized and tailored according to the high-level specification of the learning algorithm and

the constraints of the system.

# (2) How to design customizable accelerators that efficiently exploit the large capacity of advanced process technologies.

Advanced manufacturing processes have made integration of compute and storage resources on the chip. As a result, even modern FPGAs offer large capacities—e.g. Intel Arria 10 [39] instances comprise 1,518 DSP slices with 6.6 MBytes of storage and Xilinx UltraScale+ in Amazon EC2 [29] includes 6,840 DSP slices and 43 MBytes of storage. A single instance of learning algorithm may not effectively exploit resources since it is limited by the finegrained parallelism in its Dataflow Graph (DFG). Therefore, CoSMIC offers a novel Multiple-Instruction Multiple-Data (MIMD) multi-threaded template architecture that divides the resources across multiple instances of the learning algorithm as independent threads. The last layer of CoSMIC customizes this template and generates the final accelerator by striking a balance between the number of threads running on the chip and the resources assigned to each thread. The code generation differs for FPGAs and P-ASICs. For FPGAs, the generated core is tailored to one specific learning algorithm as the chip can be erased and reprogrammed for different applications. For P-ASICs, the generated accelerator is a programmable superset of the design that fits in the area and power budget of the chip. Any algorithm that can be expressed using the DSL can be compiled and accelerated on the generated P-ASIC. The generated code and template are in the form of Register-Transfer Level (RTL) Verilog code. The template architecture is designed, optimized, and implemented by experts once in Verilog, which ensures efficiency although CoSMIC generates the accelerators automatically. More specifically, the template is designed as a two-dimensional matrix of compute units to ensure data dependencies and within-thread communications do not curtail its scalability to rather large number of processing elements. We also designed a tree-like bus to connect the rows and allocated bidirectional communication across columns. Hence, the communication latency only grows by a logarithmic order with an increase in the number of compute units, improving on-chip scalability. Furthermore, CoS-MIC's backend compiler minimizes data movement by mapping operations to where their operands are located. This hardware-software co-design that aims to maximize effective resource utilization ensures effective utilization of on-chip resources, especially when they are plentiful.

# (3) How to devise the system software that is specialized for distributed multi-threaded acceleration of learning.

To be inline with the recent industry trends in integrating accelerators in datacenters [27, 28, 29], CoSMIC targets commodity distributed systems in which accelerators sit on the high-speed expansion slots (e.g., PCle). For generality, we assume no special connectivity between the accelerators although such connectivity will most likely improve the benefits of CoSMIC. CoSMIC aims to best utilize the system-wide resource on both CPUs and accelerators. CoSMIC achieves this objective by offering a lean and specialized system software layer that exclusively supports learning algorithms that can be trained using parallel variants of stochastic gradient descent. This specialized layer allows the CoS-MIC stack to assign the partial gradient calculation onto the accelerators while the CPUs perform aggregation and networking. This task assignment alleviates the use of accelerator resources for TCP/IP communication, avoids data copies to accelerator boards for aggregation, and enables using commodity distributed systems with CoSMIC. Moreover, it maximizes system-wide resource utilization as well as portability to different accelerator boards. Within each node, the system software maintains an internal thread pool. These threads handle the communication with the remote peer nodes. Internally managing this thread

pool avoids costly OS-level context switches. The system software layer also maintains another internal thread pool that asynchronously aggregates the partial gradients. In addition, this layer assigns roles to the nodes and orchestrates the exchange of partial gradients and their aggregation.

We evaluate the benefits of the CoSMIC stack using 10 different learning applications from various domains including medical diagnosis, computer vision, finance, audio processing, and recommender systems. We compare CoSMIC against Spark, a popular framework for scale-out computing using the optimized MLlib machine learning library [40]. On average, a 16-node CoSMIC with UltraScale+ VU9P FPGAs offers 18.8× speedup over a 16-node Spark system with Xeon E3 Skylake CPUs while the programmer only writes 22-55 lines of code. When scaling the nodes from 4 to 16, CoSMIC's performance improves by  $2.7\times$ , while Spark's performance scales only by  $1.8\times$ . We also compare the CoSMIC system with the distributed GPU (NVIDIA Tesla K40c) implementation. We report the benefits of CoSMIC for two P-ASIC implementations that match the compute resources and off-chip bandwidth of the FPGA and the GPU. On average, these P-ASICs offer 1.2× and 2.3× higher systemwide performance, while the GPU delivers 1.5× speedup over FPGA system. While using custom chips can improve computation time by  $11.4\times$ , the systemwide performance benefits are limited to 2.3×. Finally, with CoSMIC's novel multi-threaded accelerator architecture, the FPGA and the two P-ASIC systems respectively achieve 4.2 $\times$ , 6.9 $\times$ , and 8.2 $\times$  higher Performance-per-Watt than the GPU system. These results confirm that CoSMIC is an effective and vital initial step to enable acceleration of learning at scale. To this end, this work not only contributes the full stack of CoSMIC, but also defines a new multithreaded accelerator architecture, a novel communication-aware scheduling and mapping algorithm, and a lean and specialized system software for thread

management and system orchestration.

### 2.2 Distributed Learning

The CoSMIC stack empowers programmers to exploit accelerator-augmented distributed systems for a wide range of learning algorithms without requiring them to deal with the laborious task of hardware design and system software programming. Although providing higher performance drives this work, programmability and generality are its other two pillars. CoSMIC facilitates programming by exposing a math-oriented DSL to programmers to express various learning algorithms as stochastic optimization problems. The layers of the CoSMIC stack compile this high-level specification to generate the accelerator architecture, and offer the system software that orchestrates them for scale-out execution. This stack is not designed for a specific ML algorithm. Instead, it is adept at accelerating learning algorithms that can be trained using variants of gradient descent optimizer. This section provides the theoretical foundation of these type of algorithms.

### 2.2.1 Learning as Stochastic Optimization

CoSMIC targets a wide range of supervised machine learning algorithms. These algorithms have two phases: training and prediction (inference). We focus on training, as it is more complex and involves several passes of prediction-tuning over the training data. Since training involves prediction, CoSMIC can accelerate prediction as well.

Each machine learning algorithm is identified by a set of parameters  $(\theta)$  and a transfer function (g), that maps an input vector  $(X_i)$  to a predicted output vector  $(Y_i)$ . As Equation 2.1 illustrates, training is the process of finding  $\theta$  such that

the predicted output  $Y_i = g(\theta, X_i)$  has a minimum difference from the expected output  $Y_i^*$  for all input-output pairs  $(X_i, Y_i^*)$  in the training dataset.

Find

$$\theta \ni \{Loss = \sum_{i} f(\theta, X_i, Y_i^*) = \sum_{i} \langle g(\theta, X_i) - Y_i^* \rangle \}$$

is Minimized (2.1)

This unique loss function  $(\sum_i f(\theta,X,Y^*))$  defines each of the learning algorithms in our target class. A machine learning algorithm learns the model  $(\theta)$  by solving an optimization problem that minimizes this loss function  $(\sum_i \langle g(\theta,X_i) - Y^* \rangle)$ . To learn a model  $(\theta)$ , optimization algorithms iterate over the training data and gradually reduce the loss by adjusting the model parameters. One of the most common [31, 30, 63] optimization algorithm is Stochastic Gradient Descent (SGD). SGD is based on the observation that a function decreases fastest in the negative direction of its gradient.

$$\theta^{(t+1)} = \theta^{(t)} - \mu \times \frac{\partial (f(\theta^{(t)}, X_i, Y_i))}{\partial \theta^{(t)}}$$

(2.2)

As Equation 2.2 shows, each iteration t of SGD calculates  $\theta^{(t+1)}$  by updating  $\theta^{(t)}$  in the negative direction of the gradient  $(\partial f)$  with a learning rate  $(\mu)$ . The process is repeated until the loss is minimized. The gradient function varies with the learning algorithm, while the rest of the process is fixed. Hence, our stack requires programmers to specify the algorithm by expressing the gradient of its loss function  $(\frac{\partial f}{\partial \theta})$ .

### 2.2.2 Parallelizing Stochastic Optimization

SGD only consumes one input-output vector  $(X_i, Y_i)$  per iteration, traversing the entire data sequentially. Thus, basic SGD is impractical for scale-out acceleration, where the training data is large and dispersed across multiple nodes.

To enable scale-out acceleration, we exploit the insight that gradient is a linear operator. Therefore, the gradient over a set of data points can be computed by aggregating partial gradients calculated over partitions of this set. Different parallel variants of SGD [32, 33, 34, 35, 36, 37, 38] have been developed, which differ in how they iterate over the partitions and aggregate the partial gradients. For instance, the batched gradient descent algorithm [34] uses summation for aggregation, whereas the parallelized SGD [33] uses averaging. Equation 2.3 shows the use of parallelized stochastic gradient descent algorithm [33], for distributed learning.

$$Parallel_{j:1\rightarrow n}\langle \theta_j^{(t+1)} = SGD(\{XY_1, ..., XY_b\}, \theta^{(t)}, f)\rangle$$

(2.3a)

$$\theta^{(t+1)} = \frac{\sum_{j} \theta_{j}^{(t+1)}}{n} \tag{2.3b}$$

As shown, each node independently performs the traditional stochastic gradient descent for b input-output pairs  $(\{XY_1,...,XY_b\})$  and calculates a set of partial updates,  $\theta_j^{(t+1)}$ . These partial updates are aggregated with averaging, which yields the overall update  $(\theta^{(t+1)})$ . Equation 2.3a and 2.3b are repeated until the loss function f is minimized and the model is trained. The meta parameter b, called the mini-batch size, is the amount of local data that is processed before each aggregation step. CoSMIC expects the programmer to provide the gradient  $(\frac{\partial f}{\partial \theta})$ , aggregation operator  $(\sigma)$ , and mini-batch size (b). Using only this information, CoSMIC orchestrates the scale-out acceleration of the learning algorithm. The next section discusses the accelerated execution flow and the system software layer.

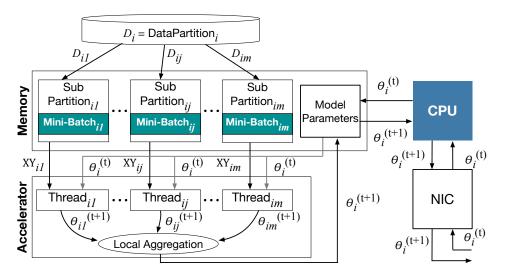

Figure 2.1: Execution and acceleration flow within each node.

### 2.3 CoSMIC System Software

CoSMIC targets scale-out systems with commodity nodes that use off-the-shelf CPUs. Each node hosts an accelerator board, identical across all the nodes and installed on a high-speed expansion slot such as PCIe. The nodes communicate through conventional TCP/IP stack via a Network Interface Card (NIC). We choose to use commodity host systems, networking hardware-software to alleviate dependency on a particular part. To understand the specialized system software layer of CoSMIC, we first need to delve into the overall execution flow across the nodes of the scale-out system.

#### 2.3.1 Execution and Acceleration Flow

Figure 2.1 illustrates a single node of the system. Each node stores a partition  $(D_i)$  of the training dataset. We have devised a multi-threaded ML accelerator for the nodes, which will be discussed in Section 2.5. To utilize multi-threading in the accelerator, the node further divides its data into equally sized subpartitions  $(D_{i1}, ..., D_{ij}, ..., D_{im})$ . These data sub-partitions are simultaneously

processed by the accelerator. In Figure 2.1, each accelerator Thread<sub>ij</sub> calculates its own private partial gradient  $( heta_{ij}^{(t+1)})$  by consuming a sub-partition of the training data. After the partial gradient updates are calculated, the multithreaded accelerator aggregates them locally and produces the node's partial gradient update  $(\theta_i^{(t+1)})$ . The host CPU sends this locally-aggregated partial gradient update  $(\theta_i^{(t+1)})$  to a special node that maintains the trained model parameters for a group of nodes. We refer to this special node as a Sigma node, while other nodes are called Delta nodes. The system software layer of CoS-MIC performs the aggregation in a hierarchical manner to avoid overwhelming a single Sigma node. In the first level of the hierarchy, the group Sigma node calculates the group aggregate. In the next level of the hierarchy, a master Sigma node combines the aggregates. Besides aggregation, the Sigma nodes compute their own partial gradient updates, as they are also equipped with accelerators. After the aggregation, the Sigma nodes distribute the updated model parameters back to all the nodes and threads and invoke training for the next mini-batch.

## 2.3.2 Task Assignment in the System Software

CoSMIC offers a lean and scalable system software layer that amortizes the cost of OS-level context switches, networking, and general thread scheduling; avoids unnecessary data copies; and matches tasks to the system resources. To devise this layer, we leverage the observation that aggregation is significantly less compute intensive than partial gradient calculations. Hence, the system software layer assigns the partial gradient calculation to the accelerators, while the CPUs perform aggregation and networking. This task assignment alleviates the use of accelerator resources for TCP/IP communication, avoids data copies to accelerator boards for aggregation, and enables using commodity distributed

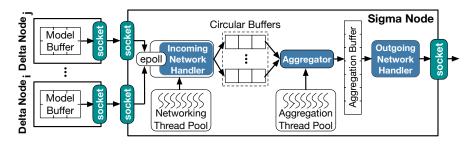

Figure 2.2: System software in a Sigma node.

systems. Moreover, it maximizes system-wide resource utilization and portability to different accelerator boards. To avoid extra data transfer with the memory and the host CPU, each accelerator internally aggregates the partial gradients for all its worker threads. Delta nodes send these partially aggregated gradients to their corresponding Sigma node. The system software workflow in the Sigma nodes is as follows.

Internal thread pools for networking and aggregation. Figure 2.2 illustrates the system software and its subroutines in the Sigma nodes. The main objective in devising these subroutines is to avoid the cost of generic thread management (creation, scheduling, and context switches) and networking by exploiting the specific execution flow of our class of learning algorithms. These subroutines need to open a socket for each communicating node. A naive approach would assign an active thread to handle each socket and spawn a thread to aggregate the received partial gradients. In contrast, the CoSMIC system software internally manages two thread pools, Networking Pool and Aggregation Pool as shown in Figure 2.2, limiting the number of active threads and reusing them as described below. When a Sigma node receives a partial update, our Incoming Network Handler catches the recv event using the Linux epoll system call. The epoll system call is effective since it does not require a linear scan on the list of monitored sockets. The Incoming Network Handler assigns a thread from the Networking Pool to copy the received data from the socket buffer in the kernel

space to a Circular Buffer for aggregation (Figure 2.2). We use Circular Buffers for concurrent networking and aggregation while each corresponding thread deals with smaller portions of data. As soon as the first chunk of data is copied, a thread from the Aggregation Pool starts processing the data and updates the Aggregation Buffer. This buffer holds the results of overall aggregation. The networking threads are data producers, while the aggregation threads are the consumers. Since Sigma nodes communicate with multiple other nodes, this approach uses the multi-threading capabilities of the CPUs to improve concurrency. The Circular Buffer reduces the memory required for aggregating partial results from multiple sources while enabling overlap between communication and computation. Our internally managed thread pools (1) alleviate the need to create an active thread for each connection, limiting the number of active threads; (2) reuse threads for different connections, mitigating the cost of context switching; and (3) use a producer-consumer semantics between the two thread pools, specializing their scheduling. These techniques avert the cost of generic thread management (creation, scheduling, and context switches), which is oblivious to the execution flow of machine learning.

### 2.4 The CoSMIC Stack

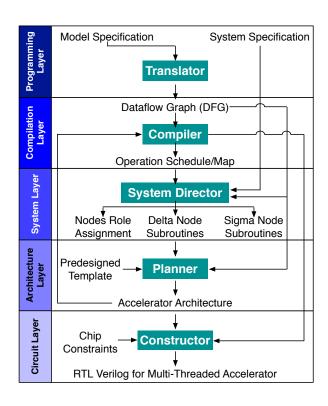

Figure 2.3 illustrates the layers of the CoSMIC stack and their interworking that orchestrates Sigma and Delta nodes and enable scale-out acceleration. This section discusses each layer briefly.

## 2.4.1 Programming Layer

Our stack makes the accelerator-augmented scale-out systems programmable from a high-level DSL. With CoSMIC, programmers use our extension of the

|                       |                                 | Partial Gradient                                               |  |  |

|-----------------------|---------------------------------|----------------------------------------------------------------|--|--|

| Programming<br>Layer  | Algorithmic Specification       | Aggregation Operator                                           |  |  |

|                       |                                 | Mini-Batch Size                                                |  |  |

|                       |                                 | Number of Nodes                                                |  |  |

|                       | System Specification            | Number of Groups                                               |  |  |

|                       |                                 | Accelerator Type                                               |  |  |

| Compilation           | Translator                      | Dataflow Graph (DFG)                                           |  |  |

| Layer                 | Compiler                        | Operation Schedule/Map                                         |  |  |

|                       | System Director                 | Node Roles                                                     |  |  |

|                       | System Subroutines: Delta Nodes | Accelerator Invocation Module                                  |  |  |

|                       | System Subroutines. Delta Nodes | Module for Communication with Sigma Node                       |  |  |

| System Layer          |                                 | Accelerator Invocation Module                                  |  |  |

| System Layer          |                                 | Networking Thread Pool for Communication with Delta Nodes      |  |  |

|                       | System Subroutines: Sigma Nodes | Circular Buffer for Consumer-Producer Networking & Aggregation |  |  |

|                       |                                 | Aggregation Thread Pool                                        |  |  |

|                       |                                 | Module for Communication with Next Level of Hierarchy Node     |  |  |

| Architecture<br>Layer | Hand-Optimized Template Design  | RTL Verilog                                                    |  |  |

|                       | Performance Estimation Tool     | Design Space of Possible Architectures                         |  |  |

|                       |                                 | Number of Threads                                              |  |  |

|                       | Planner                         | Resources per Thread                                           |  |  |

|                       |                                 | Accelerator Datapath                                           |  |  |

| Circuit Layer         | Constructor                     | RTL Verilog of the Multi-Threaded Accelerator                  |  |  |

Figure 2.3: The full CoSMIC stack.

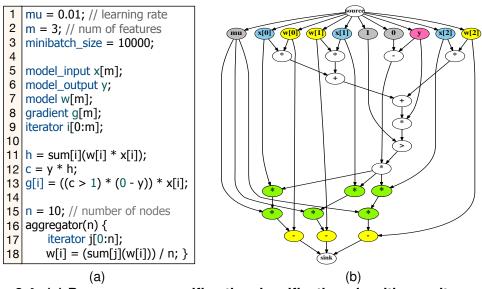

Figure 2.4: (a) Programmer specifies the classification algorithm as its gradient and aggregation functions. (b) Translator outputs the DFG.

high-level language, developed in the prior work [2] that focuses on *single-FPGA* acceleration of learning. We chose to extend this DSL since it has a one-to-one mapping to mathematical formulations instead of providing linear algebra primitives as proposed in the past [64]. Moreover, it is open source and publicly available (http://act-lab.org/artifacts/tabla). Using the extended language, programmers express the mathematical formula of the partial gradient and the aggregation operator in a textual format. Additionally, the programmer declares the mini-batch size. Figure 2.4a illustrates how a programmer uses our stack to accelerate the training of a binary classifier based on support vector machines. The first part of the code is the textual representation of Equation 2.4.

$$Gradient_{i} = \begin{cases} -y \times X_{i}, & ((\sum_{i} X_{i} \times W_{i}) \times y) > 1\\ 0, & ((\sum_{i} X_{i} \times W_{i}) \times y) \leq 1 \end{cases}$$

$$(2.4)$$

The code has three segments: data declarations, gradient formulation, and

aggregator specification. The DSL provides five data types: model\_input, model\_output, model, gradient, and iterator. These types denote the semantics of the variables in learning algorithms, and the statements represent the mathematical operations. For instance, the  $\sum_i X_i \times W_i$  term in Equation 2.4 is implemented as sum[i](w[i] \* x[i]), where x and w are declared as model\_input and model, respectively. The iterator i represents the subscript in  $\sum_i$ . The aggregation function of the parallelized SGD, which averages the partial gradients, is specified by w[i] = sum[j](w[i]) / n. This high-level expression is then converted to a Dataflow Graph (DFG) by the Translator (Figure 2.4b).

## 2.4.2 Compilation Layer

In a conventional computing stack, the next natural step after translation would be compilation. However, in our specialized stack, the order of the steps is different since the architecture of the accelerator has not yet been solidified. First, the Planner (from the architecture layer) needs to produce the architectural plan of the accelerator. In the FPGA case, this plan even depends on the DFG of the learning algorithm. In the P-ASIC case, although this plan is not dependent on the DFG, it still changes according to the chip constraints. The back-edge from the architecture layer to the compilation layer in the left diagram of Figure 2.3 illustrates the dependence of Compiler to the Planner. Once the architecture is planned, the Compiler leverages our novel mapping/scheduling algorithm to statically map operations to the accelerator Processing Engines (PEs). This static mapping is converted to state machines and control units that are embedded in the accelerator code for FPGA realization. For P-ASIC, the mapping is converted to microcodes. This static scheduling strategy avoids the von Neumann overheads and significantly simplifies the hardware which is necessary for the efficiency of the accelerator. As detailed in Section 2.6, our

mapping/scheduling algorithm also minimizes on-chip communication and alleviates the need for data preprocessing or marshaling. Compiler also generates the schedule for the template architecture's programmable memory interface that feeds a large number of PEs and streams data in without the need for PEs to request the data.

#### 2.4.3 System Layer

Section 2.3 already detailed the system layer. The topmost component of this layer is the System Director that assigns roles (Sigma or Delta) to the nodes and then configures and initiates the corresponding system subroutines. This role assignment is based on the system specification, which includes the total number of nodes, the number of groups, and the accelerator type (Figure 2.3, right).

## 2.4.4 Architecture Layer

In the conventional stack, this layer defines the Instruction Set Architecture (ISA) of a microprocessor. In CoSMIC, this layer is responsible for planning the architecture of the accelerator in accordance with the constraints of the target platform. The plan is generated with respect to our novel multi-threaded template architecture, which is a parametric RTL Verilog of customizable design. This template architecture can accelerate multiple instances of the partial gradients simultaneously. However, it is not specific to a learning algorithm and can be shaped according to the constraints of the acceleration platform (e.g., area) and the DFG of the algorithm in the case of FPGA acceleration. Instead, it is a two-dimensional matrix of customizable PEs that this layer needs stretches or squeezes in either dimension to match the chip specifications. The main challenge is allocating the chip resources in such a way that strikes a balance

between the single-threaded performance and multi-threaded parallelism. The Planner is responsible for this balanced plan by determining how many threads will be accelerated simultaneously; how many PEs will be allocated to each thread; and how the PE will be arranged in the 2D matrix of the accelerator. For P-ASICs, the Planner determines the largest number of PEs that fits in the area and power budget of the target chip. However, this metric depends on the PE buffer capacity that is decided according to a set of benchmarks. After determining the total number of PEs, the Planner steps are similar for P-ASICs and FPGAs. Thus, we only discuss the Planner in the context of FPGAs for brevity.

To determine these factors, the Planner takes in a high-level specification of the FPGAs, which includes the number of DSP units, the off-chip memory bandwidth, the number of on-chip Block RAMs (BRAMs), and the size of each BRAM (Figure 2.3). The first step is determining the number of columns (=# PEs in a row) and rows. The Planner uses the off-chip memory bandwidth to first set the number of columns equal to the number of words that can be fetched in parallel from memory (=off-chip bandwidth). Having fewer columns would waste bandwidth, while more would increase pressure on the internal interconnection between the PEs. The Planner will then determine the maximum row count as  $row_{max} = \frac{\#DSPs}{\#of\ Columns}$ .

Next, the Planner determines the number of threads and their PE allocation through design space exploration. However, this design space is prohibitively large, due to the copious amount of resources in the modern FPGAs. We prune this design space through the following intuitive design decisions. The Planner first calculates the amount of required storage and area for accelerating one worker thread based on its DFG. The ratio of total on-chip storage and area to this thread's footprint will be the upper bound on the number of simultaneous

threads. Then, we restrict the PE allocation to the row granularity, meaning each thread will have at least a row of PEs. Another parameter that affects the maximum number of threads is the programmer-provided mini-batch size, as it determines how many parallel threads can potentially be launched. The minimum of these parameters is the maximum number of possible threads:

$$t_{max} = min\left(\frac{\#BRAMs \times BRAM\ Size}{DFG.storage()},\ row_{max},\ Mini-Batch\ Size\right)$$

These design choices and the column/row arrangement restrict the design space from which the Planner needs to determine the optimal allocation of PEs to the threads. For instance, in UltraScale+, the design space is limited to 27 design points. However, the Planner still needs to explore this reduced design space. Instead of simulation, which will be intractable, we propose to equip the Planner with a performance estimation tool. The tool will use the static schedule of the operations for each design point to estimate its relative performance. This enables the Planner to choose the smallest, best-performing design point which strikes a balance between the number of cycles of data processing and off-chip data transfer. Performance estimation is viable, as the DFG does not change, there is no hardware managed cache, and the accelerator architecture is fixed during execution. Thus, there are no irregularities that can hinder estimation. As such, it takes less than five minutes to explore all the possible design points for UltraScale+. The result of this design space exploration is presented in Section 2.8. After this analysis, the Planner generates the Verilog code of the accelerator datapath from the template.

#### 2.4.5 Circuit Layer

As Figure 2.3 depicts, the Constructor is the main module of the Circuit layer and generates the final Verilog code by adding the control logic. In the case of FPGAs, to generate the state machines and control units, the Constructor needs the Compiler to first statically map and schedule all the operations. In this case, the accelerator avoids the von Neumann overhead by bypassing instruction fetch and decode stages. Instead, the Constructor statically converts the execution schedule to state machines and control logic. In the case of P-ASICs, the Constructor adds a control logic that enables microcode execution on the PEs. Then, it inserts these control units within the datapath Verilog code generated by the Planner and produces the final synthesizable Verilog code of the accelerators. The Planner, the Constructor, and the Compiler work in tandem to make CoSMIC a cohesively co-designed stack that delivers high gains.

# 2.5 Template Architecture

A major challenge in acceleration is the generality across a wide range of algorithms and applications while supporting a variety of platforms (e.g., various FPGA chips). It is also crucial to offer a solution that can adapt to new algorithms and algorithmic changes. A fixed architecture cannot offer enough flexibility and is not deployable on different chips. Therefore, CoSMIC offers a template architecture to accelerate learning at scale. This template is predesigned, yet re-organizable, providing the capability to implement different gradient calculations and parallel variants of gradient descent aggregations and updates. The template offers reusability while delivering high performance, as it is hand-crafted by experts (e.g., our team). Our stack stretches and squeezes the template to best match the DFGs and the target chip. Hence, it is modular

Figure 2.5: CoSMIC Multi-Threaded Template Architecture.

and scalable to maximally utilize the ample amount of resources in the servergrade FPGAs and P-ASICs.