# Bringing Model Checking Closer To Practical Software Engineering

Daniela Remenska

Dutch title: Modelchecken dichter bij de praktijk van

software engineering brengen

Printed by: Uitgeverij BOXpress || proefschriftmaken.nl

ISBN: 978-94-6295-432-8

Cover: artwork by Daniela Remenska

A digital version is available at: www.ubvu.vu.nl/dissertations

This work is part of the research programme of the Foundation for Fundamental Research on Matter (FOM), which is part of the Netherlands Organisation for Scientific Research (NWO).

#### VRIJE UNIVERSITEIT

# **Bringing Model Checking Closer To Practical Software Engineering**

#### ACADEMISCH PROEFSCHRIFT

ter verkrijging van de graad Doctor aan de Vrije Universiteit Amsterdam, op gezag van de rector magnificus prof.dr. V. Subramaniam, in het openbaar te verdedigen ten overstaan van de promotiecommissie van de Faculteit der Exacte Wetenschappen op maandag 8 februari 2016 om 11.45 uur in de aula van de universiteit, De Boelelaan 1105

door

Daniela Remenska

geboren te Skopje, Macedonië

promotor: prof.dr.ir. H.E. Bal copromotors: dr. J.A. Templon

dr.ir. T.A.C. Willemse

## Acknowledgements

They all said it's the most difficult one to write, but I did not believe them. After all, it's all about the people that made it happen. How hard can it be to express your gratitude? And then the day came when I kept staring at a blank page, while reflecting on the years that went by. Several of these numb evenings, it was never a good timing.

It all began with a "Welcome aboard!" and a big grin on your face, remember Jeff? Even before I embarked on this PhD journey. Thank you for making it happen, for believing in my potential, despite the goofy first impression I left. Thanks for making New York, San Francisco, CERN, NASA, ... all of it, a reality, and thanks all the great people I met through you. I will not forget our "tell it to your Teddy Bear" sessions, those reality checks every time I got stuck. Nevermind the awkward name, the technique is ingenious. And thanks to the smart geeks from the Grid group I had the honor to be part of: David, Ronald, Sven, Paco, Mischa, Oscar, Dennis, Jan Just, Tristan, Hurng. I learned a lot from you. Keep on rocking!

Henri, my gratitude goes to you, for the freedom you gave me to go for all the (un)successful ideas I had. Thank you for all your questions, your trust, criticism and patience with my chaotic thoughts. For accepting my failures, and praising my success. Kees, your reviews were invaluable, and so was your humor, and your midnight DAS4 attempts to tame the model checking beast. Thank you for that.

Tim, I guess it's somehow your destiny to end up working with & around awkward Macedonians. We can blame Dragan Bosnacki for that, this time. There are so many emails with silly braindumps I wish I could "undo send", yet you did not give up on me. Even during your sabbatical, with that poor hotel WiFi and your chopped robot voice. Thank you for your "I'm always up for a challenge" 5 years ago, the rest is history. I am indebted to Sonja Georgievska. If it wasn't for you, none of this would have had the slightest chance of happening. Thank you for making Holland a reality! Thank you for your sarcasm, really. Thank you for accepting me homeless with a lost 30kg luggage, on day one in Eindhoven. And introducing me to Zarko, Jasen, Natasa, Meri. A heartwarming hospitality bunch, if only they would migrate to the north also:P

Marcel, I have known you from the first day I set foot at Nikhef. Your laughter is genuine, I can hear it from miles. Thank you for all your efforts in making my first steps at CERN smooth. I met some fantastic people there. Philippe, Joel, Marko, Stefan, Fede, Vladimir, Ricardo, Adri: I never expected to feel at home so quickly, you took me like one of your own, you dear, warm, prodigious people, with a remarkable sense of humor! LHCb is the coolest of all LHC experiments, and I'm not just saying. I mean it. You are the bleeding edge. I learned so much from you. Rarely do I meet people who are so knowledgeable and modest at the same time. I miss you very much. Chris, my dear friend, thank you for making the Geneva stays enjoyable! Underground, the pit, hallways, highways, movies, brainstormings, New York, wine-tasting, guitar plays, Vijay on the radio (that we somehow missed). So much history, I hope our paths cross again.

Niksa...my dear Niksa. You know me too well. Thank you for all the "therapy sessions", all those wine & philosophy late night talks. You gave me a short escape, each time I needed one. You have your original way around my stubbornness,...hey, you even managed to get me off cigarettes. You are such a beautiful mind. Ana, Gordana, Ratko, Tanja, Sonja, Saska, Kiril, Igor: I have known you for what seems like ages. You have shaped me up as a person, and (perhaps too eagerly) put me on a pedestal. You make the trips to Skopje worthy. We may not see eachother often, but when we meet, it is nothing but love.

Ognen, I look up to you, you are my hero. The positive energy you spread is contagious. If I start listing all the things I'm thankful for, I will need an extra chapter. Jose, Bojana, Svetle, Ivana... my Macedonian gang, thank you for making me feel at home in Amsterdam. I'm so proud of all of you, and I feel lucky to have you in my life. No, I'm not being cheesy, you are spectacular. Riste and Irina: I really cherish the great times with you here, and I'm indebted to both, for your moving help, great Macedonian dinners, and witty advice in desperate times. Amsterdam feels emptier now (damn you, Germany!), but I am still secretly looking for ways to bring you back. Nikola and Bojan, my Ijburgers, we shall rediscover the Amsterdam squats together, I promise you. Sorry for the quarantined weekends in the past months, and thank you for those retro-gaming nostalgic moments.

Ana, your love at first sight is a mutual one, just so you know! Funny how smoking breaks can be the causality of many things, such as starting an incredible friendship. You were always late, but worth the wait. Philip, you social butterfly, thanks for being my Friday Night Skate support (literally), a party initiator so many times, and for the unforgettable boat tours around Amsterdam. Albana, Dirk, Bebe, David, Ben, Corina, Otto,... thank you for all the sleepless nights, for all the hilarious Cards Against Humanity games, barbecues, and all bottles of Prossecco reserved for my consumption. I seem unable to sustain my smile when I'm around you. No matter how bad the day has been, you can turn it into a blast. My Amsterdam

family, thank you for all intellectually inspiring conversations and advice. This journey would have been a boring one without you. Ry, sonce moe, thank you for your moral boost, your endless support and occasional distractions. For all the warm meals you cooked for me, and all Netflix Friday nights. Thank you for for putting up with my thesis frustrations, and believing in me.

Мама, тато, Фроси: ви благодарам на безрезервната поддршка и трпението со овој мој докторат. Ви благодарам на сите совети. Горда сум и се огледувам на вас, во секој поглед.

Finally, I would like to thank all the members of my thesis committee, for their valuable thesis reviews, dedication, and patience with the scheduling of my defense day.

Daniela Amsterdam, 2016

## Contents

| A  | cknow   | ledgements                                       | iii  |

|----|---------|--------------------------------------------------|------|

| Co | ontent  | SS .                                             | vii  |

| Li | st of i | Figures                                          | xi   |

| Li | st of   | Tables                                           | xiii |

| Li | st of . | Abbreviations                                    | xv   |

| 1  | Intr    | oduction                                         | 1    |

|    | 1.1     | Context and Research Objectives                  | 3    |

|    | 1.2     | Main Contributions                               | 5    |

|    | 1.3     | Dissertation outline                             | 6    |

| 2  | DIR     | AC: A Community Grid Solution                    | 9    |

|    | 2.1     | Introduction                                     | 9    |

|    | 2.2     | Workload Management System                       | 13   |

|    | 2.3     | Storage Management System                        | 16   |

| 3  | Forr    | nal Modeling and Analysis of Distributed Systems | 19   |

|    | 3.1     | Introduction                                     | 19   |

|    | 3.2     | Labeled Transition Systems                       | 19   |

|    | 3.3     | The mCRL2 Formalism                              | 22   |

|    | 3.4     | From DIRAC to mCRL2                              | 25   |

|    |         | 3.4.1 Control-Flow Abstractions                  | 27   |

|    |         | 3.4.2 Data Abstractions                          | 29   |

|    | 3.5     | Analysis and Issues                              | 32   |

|    |         | 3.5.1 Simulation and debugging                   | 33   |

viii CONTENTS

|   |      | 3.5.2    | Visualization                                                        | 34  |

|---|------|----------|----------------------------------------------------------------------|-----|

|   |      | 3.5.3    | Model checking                                                       | 36  |

|   | 3.6  | Discus   | ssion and Evaluation of the Approach                                 | 41  |

|   | 3.7  | Relate   | d Work                                                               | 43  |

|   | 3.8  | Conclu   | usions                                                               | 45  |

| 4 | Mod  | lel-Tran | sformation Methodology                                               | 47  |

|   | 4.1  | Introd   | uction                                                               | 47  |

|   | 4.2  | Model    | ling Interactions in UML                                             | 50  |

|   |      | 4.2.1    | Sequence Diagrams                                                    | 50  |

|   |      | 4.2.2    | Activity Diagrams                                                    | 54  |

|   | 4.3  | Transf   | ormation Methodology                                                 | 55  |

|   |      | 4.3.1    | The Object-Process Problem                                           | 55  |

|   |      | 4.3.2    | Design Choices in the Semantics of Sequence Diagrams                 | 57  |

|   |      | 4.3.3    | Mapping UML to mCRL2                                                 | 59  |

|   | 4.4  | Case S   | Study: DIRAC's Executor Framework                                    | 68  |

|   | 4.5  | Discus   | ssion and Evaluation of the Approach                                 | 71  |

|   | 4.6  | Concl    | usions                                                               | 72  |

| 5 | Assi | sting N  | on-Experts in Property Specification                                 | 73  |

|   | 5.1  | Introd   | uction                                                               | 73  |

|   | 5.2  | Backg    | round: Property Specification Patterns                               | 75  |

|   | 5.3  | Relate   | d Work                                                               | 77  |

|   | 5.4  | PASS:    | An Implementation and Extension of PSP                               | 80  |

|   |      | 5.4.1    | $\mu$ -calculus and the PSP system                                   | 80  |

|   |      | 5.4.2    | Pattern Extensions for $\mu$ -calculus                               | 84  |

|   |      | 5.4.3    | Sequence Diagrams for Visual Property Specification                  | 88  |

|   |      | 5.4.4    | Transforming a $\mu$ -calculus Formula Into a Monitor Process $$     | 89  |

|   |      | 5.4.5    | A Walk-Through Example                                               | 92  |

|   |      | 5.4.6    | PASS Integration in the Eclipse Platform                             | 93  |

|   | 5.5  | PASS 1   | by Example: Revisiting DIRAC                                         | 94  |

|   |      | 5.5.1    | PASS: The Property ASSistant                                         | 95  |

|   |      | 5.5.2    | PASSWebStart: The Alternative                                        | 99  |

|   |      | 5.5.3    | The DIRAC ProcessPool                                                | 100 |

|   | 5.6  | Proper   | rty Specifications with $\mu$ -calculus: A Survey of Published Works | 104 |

|   |      | 5.6.1    | Is the PSP Classification Useful?                                    | 104 |

|   |      | 5.6.2    | Is Manual Formalization of Properties Error-Prone?                   | 106 |

|   | 5.7  | Concl    | usions                                                               | 113 |

| ix |

|----|

|    |

| 6           | Con        | clusions                                      | 115 |

|-------------|------------|-----------------------------------------------|-----|

|             | 6.1        | Thesis summary                                | 116 |

|             | 6.2        | Limitations and Future Directions             | 118 |

| Sa          | menv       | atting                                        | 121 |

| A           | App        | endix                                         | 125 |

|             | <b>A.1</b> | Definitions                                   | 125 |

|             | A.2        | Proof of the Monitor Construction Correctness | 131 |

| $R\epsilon$ | feren      | ces                                           | 139 |

# List of Figures

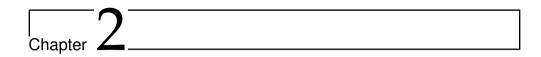

| 2.1  | LHCb job execution rate by site                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

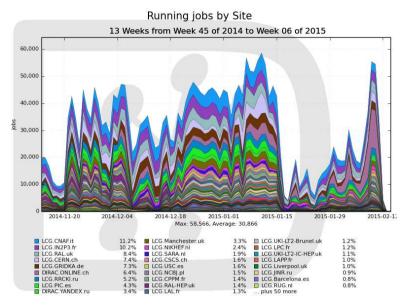

| 2.2  | LHCb data transfers throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

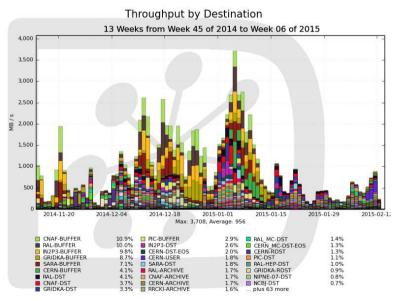

| 2.3  | DIRAC Architecture overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11 |

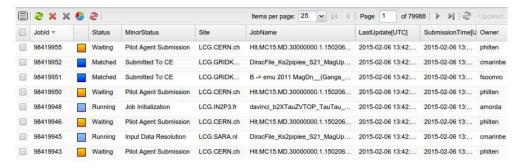

| 2.4  | LHCbDIRAC web portal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12 |

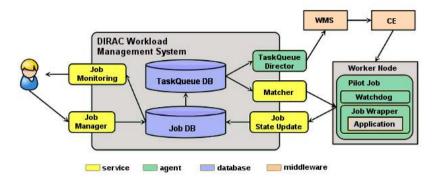

| 2.5  | DIRAC Workload Management System [158]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14 |

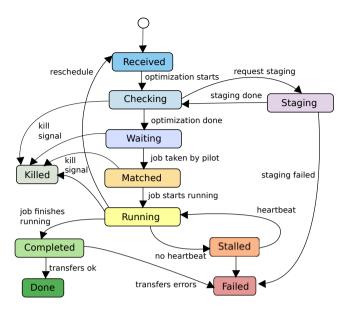

| 2.6  | DIRAC Job state machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 |

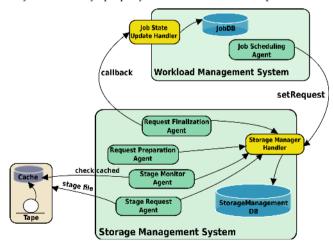

| 2.7  | DIRAC Storage Management System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

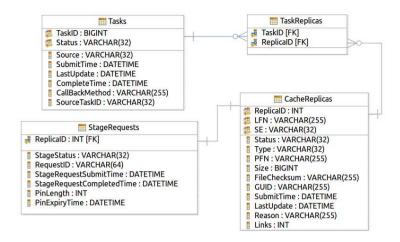

| 2.8  | Relationships between StorageManagement DB entities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17 |

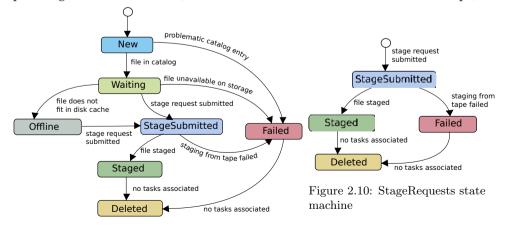

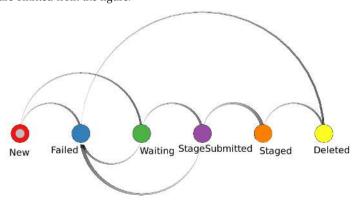

| 2.9  | CacheReplicas state machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

| 2.10 | StageRequests state machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

| 2.1  | Nicolate and a total and a second a second and a second a | 20 |

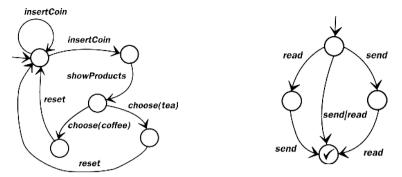

| 3.1  | Non-deterministic behavior of a vending machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3.2  | Behavior involving multi-actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20 |

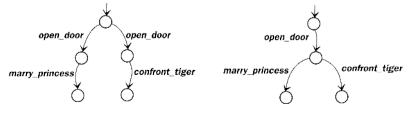

| 3.3  | The lady, or the tiger?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21 |

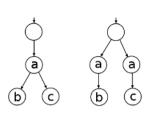

| 3.4  | Alternative and sequential process composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22 |

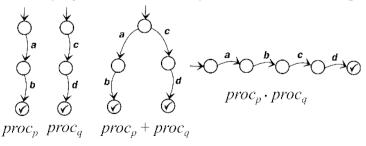

| 3.5  | Parallel process composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

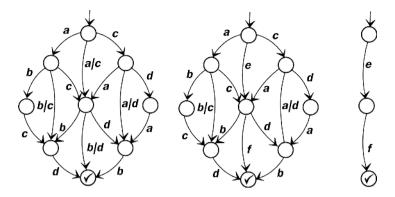

| 3.6  | Left: Control flow graph of a simple vending machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | Middle: Over-abstraction. Right: Under-abstraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

| 3.7  | CacheReplicas table description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29 |

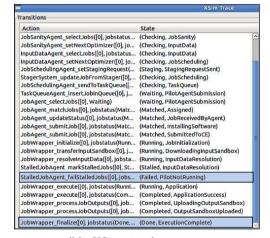

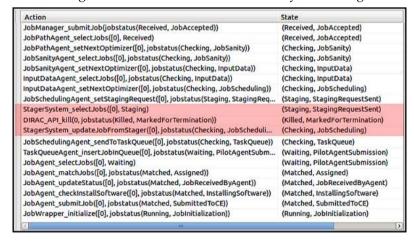

| 3.8  | Invalid job state transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33 |

| 3.9  | CacheReplicaMem process visualization with DiaGraphica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34 |

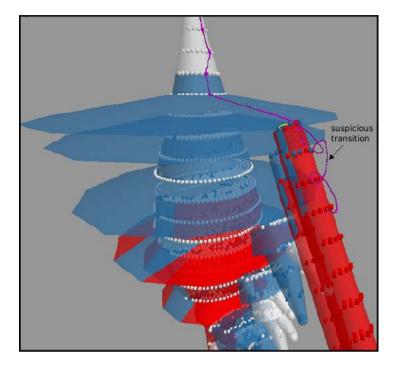

| 3.10 | State-space visualisation of the SMS with Itsview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35 |

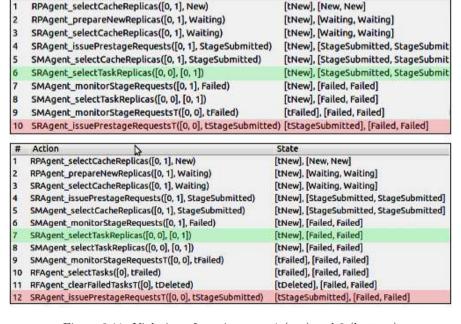

|      | Violation of requirements 1 (top) and 2 (bottom)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38 |

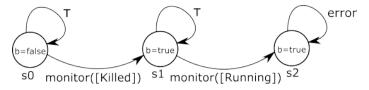

|      | Monitor automaton for requirement 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 3.13 | "Zombie" job starts running after being killed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39 |

| 3.14 | Race condition involving the stager callback no longer occurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40 |

xii LIST OF FIGURES

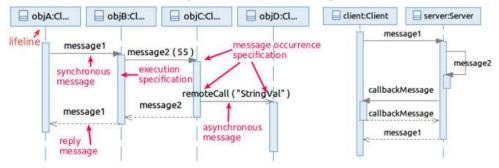

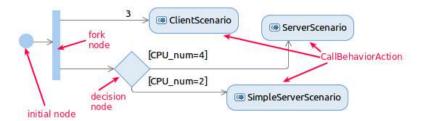

| 4.1  | Sequence diagrams notation                                                | 50  |

|------|---------------------------------------------------------------------------|-----|

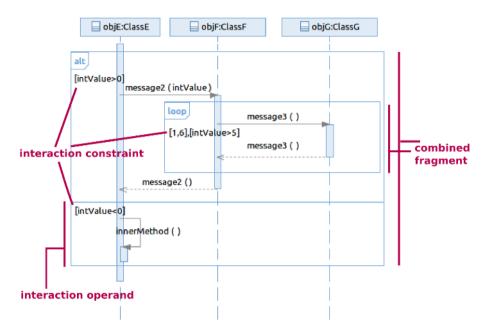

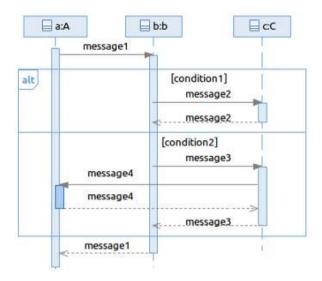

| 4.2  | Combined Fragments examples                                               | 52  |

| 4.3  | Example of par (left) and break (right) fragments                         | 53  |

| 4.4  | Formal and actual gates in <i>InteractionUse</i>                          | 53  |

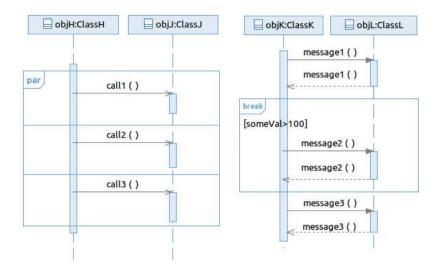

| 4.5  | Activity diagram example                                                  | 55  |

| 4.6  | Sequence diagram with alternative control flow                            | 56  |

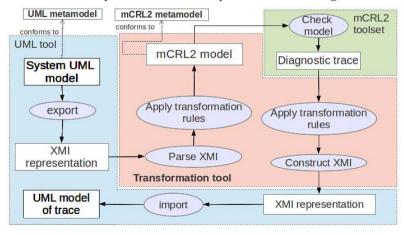

| 4.7  | Automated verification of UML models                                      | 59  |

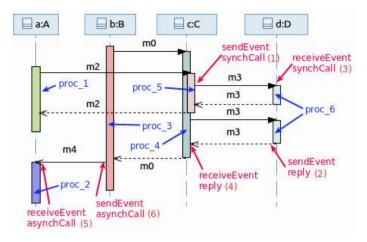

| 4.8  | Identifying event types along lifelines                                   | 60  |

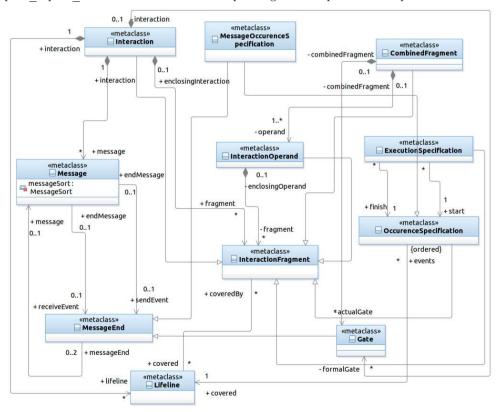

| 4.9  | Selected elements of the Interactions metamodel                           | 60  |

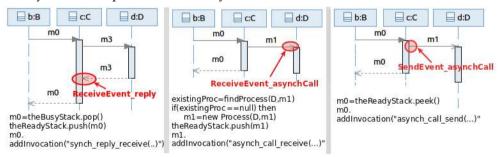

| 4.10 | Handling Case 4(left), Case 5(middle) and Case 6(right)                   | 63  |

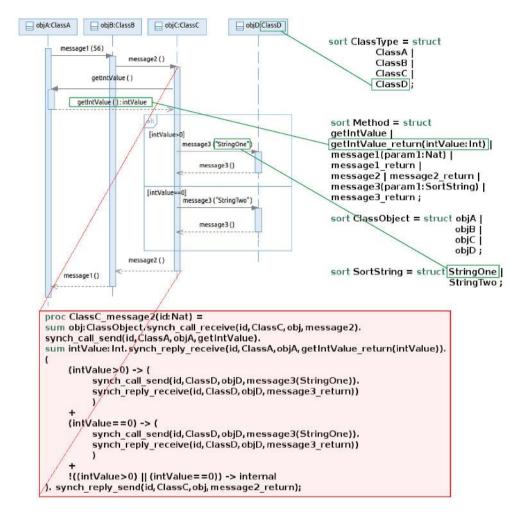

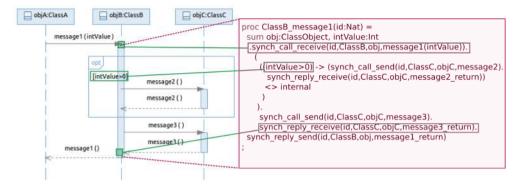

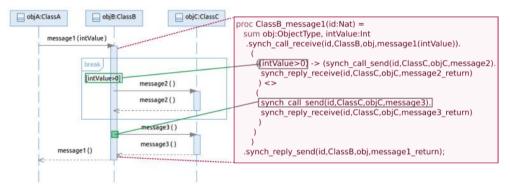

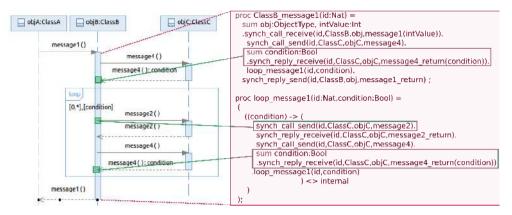

| 4.11 | Application of the SD transformation rules                                | 65  |

| 4.12 | Translation of the opt combined fragment                                  | 66  |

| 4.13 | Translation of the break combined fragment                                | 66  |

| 4.14 | Translation of the loop combined fragment                                 | 67  |

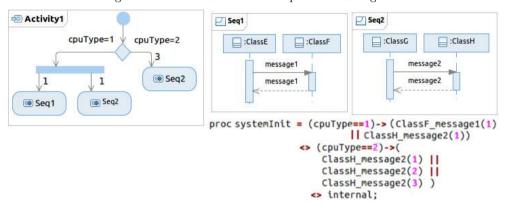

| 4.15 | Application of AD transformation rules for system-level concurrency setup | 67  |

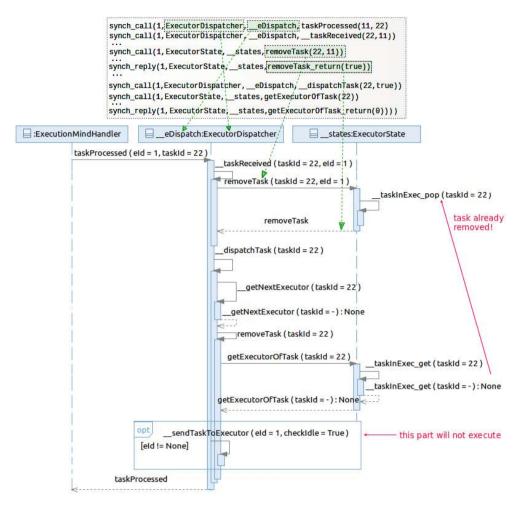

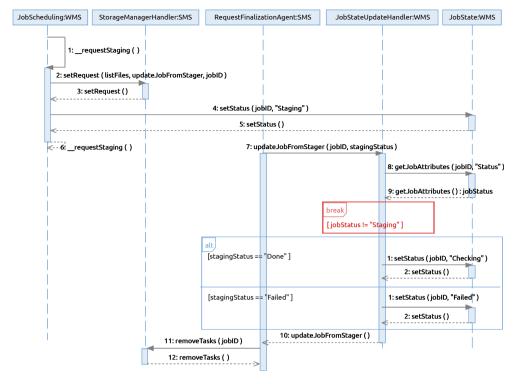

| 4.16 | SD trace showing a case of no-progress of tasks scheduling                | 70  |

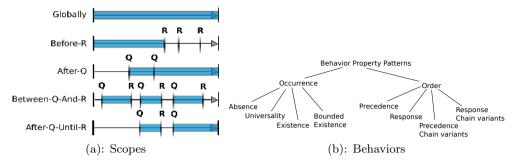

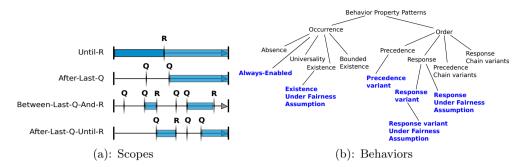

| 5.1  | Property Specification Patterns classification                            | 76  |

| 5.2  | Left: Prospec tool; right: CHARMY PSC graphical notation                  | 78  |

| 5.3  | Pattern Extensions incorporated in PASS                                   | 86  |

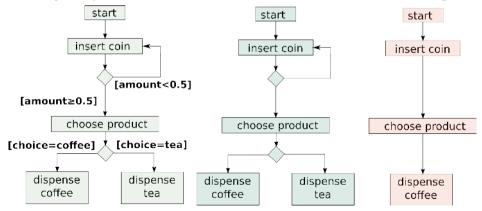

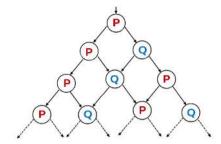

| 5.4  | Branching versus linear time Logic                                        | 87  |

| 5.5  | Branching time logic can capture <i>possibility</i> properties            | 87  |

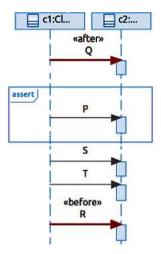

| 5.6  | UML2 Sequence Diagram with applied stereotypes                            | 89  |

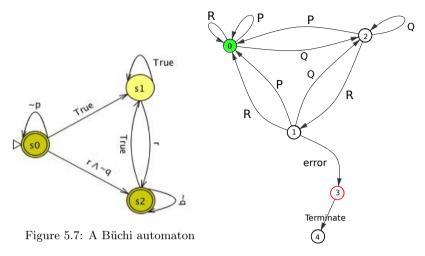

| 5.7  | A Büchi automaton                                                         | 90  |

| 5.8  | Transforming a $\mu$ -calculus formula into a monitor                     | 90  |

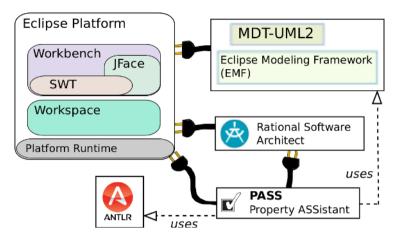

| 5.9  | PASS integration in Eclipse                                               | 94  |

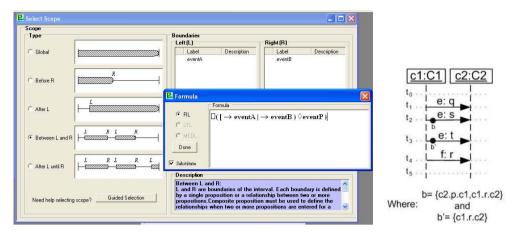

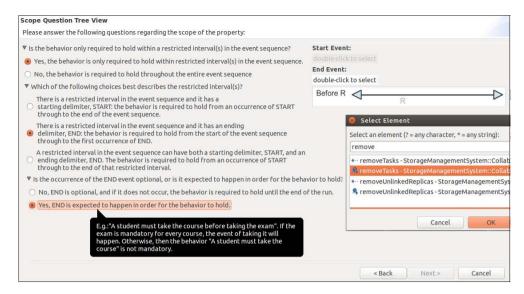

| 5.10 | Eliciting the scope for a property with PASS                              | 95  |

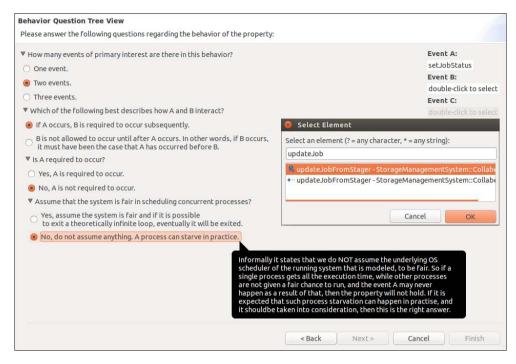

| 5.11 | Eliciting the behavior for a property with PASS                           | 96  |

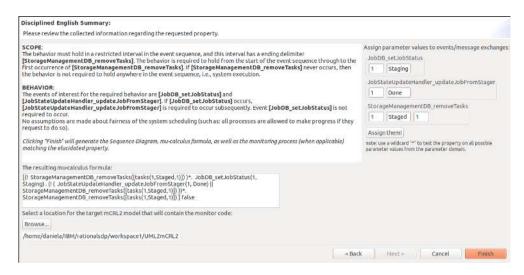

| 5.12 | Summary of the elicited property with PASS                                | 97  |

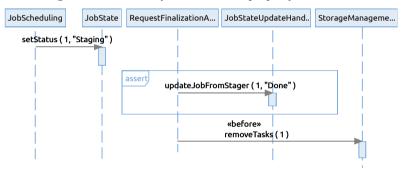

| 5.13 | A sequence diagram visualizing the elicited SMS property                  | 97  |

| 5.14 | Fix applied for the problem with "zombie" jobs                            | 98  |

| 5.15 | MySQL errors in the SMS logs                                              | 98  |

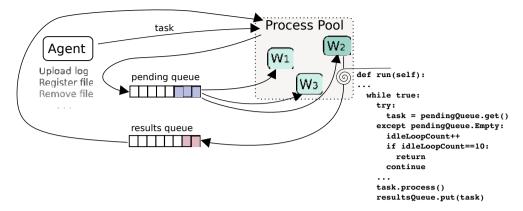

| 5.16 | DIRAC ProcessPool                                                         | 99  |

|      | ProcessPool deadlock trace                                                |     |

| 5.18 | Survey of $\mu$ -calculus specifications: patterns distribution           | 105 |

# List of Tables

| 3.1 | mCRL2 models statistics <sup>1</sup>                                         |

|-----|------------------------------------------------------------------------------|

| 5.1 | After-Q vs. After-Last-Q scope variations for different behavior patterns 84 |

| 5.2 | Formulas obtained with PASSWebStart                                          |

| 5.3 | Model checking results for the ProcessPool properties 102                    |

| 5.4 | Survey results: property specifications with $\mu$ -calculus 105             |

|     |                                                                              |

| A.1 | Structural Operational Semantics for the basic operators 136                 |

| A.2 | Structural Operational Semantics for the sum operator 136                    |

| A.3 | Structural Operational Semantics for the parallel operator 137               |

| A.4 | Structural Operational Semantics for the auxiliary parallel operators . 137  |

| A.5 | Structural Operational Semantics for the auxiliary operators 138             |

| A.6 | Structural Operational Semantics for recursion                               |

## List of Abbreviations

CERN European Organization for Nuclear Research

LHC Large Hadron Collider

WLCG Worldwide LHC Computing Grid

LHCb Large Hadron Collider beauty experiment

DIRAC Distributed Infrastructure with Remote Agent Control

WMS Workload Management System SMS Storage Management System

VO Virtual Organization

LTS Labeled Transition System

ACP Algebra of Communicating Processes

PBES Parametrized Boolean Equation Systems

LTL Linear Temporal Logic

CTL Computation Tree Logic

UML Unified Modeling Language

CASE Computer Aided Software Engineering

SM State Machine

AD Activity Diagram

SD Sequence Diagram

OCL Object Constraint Language

PSC Property Sequence Charts

LSC Live Sequence Charts

OMG Object Management Group

PSP Property Specification Patterns

SOS Structural Operational Semantics

## Introduction

Software systems are becoming increasingly complex, growing both in code base size and number of involved components. In effect, it becomes more challenging to detect certain design errors before it is too late, and these manifest in financial or human life losses. Testing [69], or running the software under different input stimuli in order to examine different possible behaviors and outputs, is a common form of verification in the software engineering life-cycle. One essential shortcoming of testing is that it is not exhaustive, i.e., cannot guarantee that all relevant behaviors have been covered with the tests. In the famous words of Dijkstra [58], program testing can be used to show the presence of bugs, but never to show their absence. This limitation is exacerbated in concurrent systems, where the order of events from various components is unpredictable and difficult to test or reproduce in a controlled manner. Certain design errors in such complex systems (e.g., deadlocks, race-conditions) are notoriously difficult to find purely by means of testing, simply because the number of different possible scenarios is typically prohibitively large.

Formal methods [48] offer more rigorous means of system verification. They should be considered a supplemental, rather than a replacement technique to testing and other means of verification, which contribute to improved quality of the system design and implementation. These mathematically-rooted techniques to prove system correctness, or the absence of system errors, have been a topic of research for several decades. A range of different approaches and supporting software tools have emerged over time, including theorem proving [144; 143], static analysis [173; 18; 54], and model checking [47], to name but a few. Despite the ongoing research effort, they are still considered somewhat exotic and are often met with resistance in many software industry circles. One of the major barriers to the wide acceptance of formal methods is the learning curve: engineers and programmers typically lack the training to use them, while managers are not aware of the context in which such methods should be applied, nor the potential benefits

of using them. An additional obstacle is the fact that their use typically amounts to maintaining two separate model implementations: a formal one, amenable to verification, and a "real" production one. On the other hand, proponents of formal methods claim that their application can substantially improve the software quality and reduce the costs and the risks of failure in the long run [36; 198; 86]. The reality is most likely somewhere in the middle. What started out as manual labor-intensive proof construction using axioms and inference rules, geared towards small sequential programs, has certainly moved far beyond merely adding program assertions to perform runtime program checks. In contrast to three decades ago, academia today is no longer just advocating verification with theoretical results; industry actually applies it, though still rather selectively. The root cause behind this limited penetration of formal methods in the broader industry has itself been a topic of research and debates [31; 146; 28].

One highly effective verification technique is model checking [47; 50; 156]. The rising success of this field stems from the availability of actively-maintained mature tools which automate the algorithmic procedure of determining whether an abstract mathematical model representation of the system satisfies certain behavioral properties, or requirements. These model checking tools expect a model expressed in some formal notation (such as a process algebra [17] or Petri Nets [160]), and a property to be verified, typically expressed as a formula in temporal or modal logic [49; 85]. These logics contain temporal operators such as "next", "eventually", "always", and "until", which allow for reasoning about behavior over time. Simply put, the entire state space of the model is automatically generated while all possible scenarios are exhaustively explored, making the technique equivalent to exhaustive model testing. The state space is typically represented by a state-transition graph (specifically, a Kripke Structure or a Labeled Transition System), a structure containing all reachable states (system snapshots containing values of all variables, including control stacks) and transitions (actions that change the system state). As a result, if an affirmative answer is given concerning a model and a property specification, one can be confident that the model does not contain problematic behavior with respect to the specified property. A strong point of model checking tools is their capability to produce counter-examples: traces leading to the situation that violates the checked property. This way one can get a detailed understanding of the root cause of the detected problem.

There are success stories [106; 111; 153; 193; 194; 18] of applying model checking in industrial research labs, and plenty of communication protocols and safety-critical modules have been put under scrutiny [104; 145; 77; 107; 16; 113; 30], unveiling bugs undetected before. Tools for automating such analysis are well supported and continuously improving (e.g., SPIN [108], NuSMV [44], mCRL2 [88], CADP [81], LOTOS [187]), but there is still a need to close the gap by involving the end-users

as stakeholders, and not only the research community and the theoretical computer science experts in the process. Further effort is required to reduce the barrier to practical use of most such tools, as well as to integrate them into the typical development environments and frameworks used in practical software engineering. This dissertation describes research that aims to achieve that.

## 1.1 Context and Research Objectives