National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

You he Your menore

Our file. Notice reference

#### **NOTICE**

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### **AVIS**

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

## Built-In Self-Diagnosis for Repairable Embedded RAMs

Robert Treuer

Department of Electrical Engineering

McGill University, Montreal

September 1992

A Thesis submitted to the Faculty of Graduate Studies and Research in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

© Robert Treuer, 1992.

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your hier. Notice intercence

Our ble Notice assertions

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition thèse à la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-87677-8

Built-in self-diagnosis for repairable embedded RAMs

#### Abstract

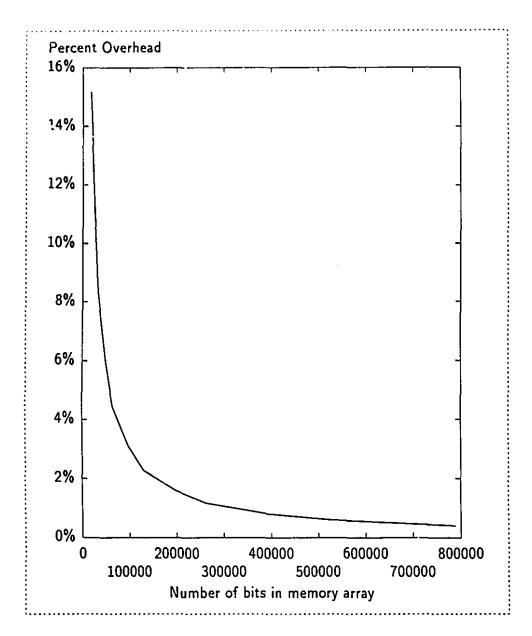

Embedded random access memories (RAMs) are increasingly being tested using built-in self-test (BIST) circuits, because an embedded RAM's signals are not accessible through input/output pins. Given current trends, the size of embedded RAMs will eventually grow so large that yield considerations will require the use of redundant lines for repair. Then, BIST circuits will need to not only detect faults, but also locate faults for repair. The designs of two different BISD circuits (one with, and the other without, self-repair capability) appropriate for repairable, embedded, (single-metal and single-polysilicon layered) CMOS static RAMs, are presented. The implementation of a BISD circuit — with self-repair — requires 15% extra area in a 16K SRAM, and 5% extra area in a 64K SRAM. The BISD circuit contains a reduced-instruction-set processor, which executes diagnosis algorithms stored in a read-only memory, and which uses some extra lines to access the memory. The new algorithms employ "hybrid serial/parallel" operations to access the memory when external repair is available, or "modular" operations to access it when self-repair is required.

#### Résumé

De plus en plus souvent, les mémoires vives encadrées sont examinées pour la présence des défectuosités par moyen des circuits d'auto-vérification incorporés, parce que les signaux d'une mémoire vive encadrée ne sont pas accessible à travers les ports d'entrées/sorties. Suivant les tendances actuelles, la superficie des mémoires vives encadrées s'augmentera tellement que le rendement de fabrication diminué obligera l'usage des lignes redondantes pour la réparation. Alors, les circuits d'auto-vérification incorporés devront non seulement découvrir les défectuosités, mais devront aussi localiser les défectuosités pour la réparation. Les conceptions de deux circuits d'auto-vérification incorporés différents (l'un avec, et l'autre sans, le pouvoir d'auto-réparation), qui sont convenables pour les mémoires vives statiques, encadrées et réparables, et fabriquées en CMOS (avec une couche d'aluminium et une couche de polysilicone), sont présentées. Un circuit d'auto-diagnose incorporé - avec auto-réparation - exige 15% de superficie supplémentaire dans une mémoire vive à 16K, et 5% dans une mémoire à 64K. Le circuit d'auto-diagnose incorporé contient un processeur à peu d'instructions, qui exécute les algorithmes diagnostiques emmagasinés dans une mémoire morte, et qui se sert des lignes supplémentaires pour accéder à la mémoire vive. Les nouveaux algorithmes emploient des opérations "hybrides en série/parallèle" pour accéder à la mémoire quand la réparation externe est disponible, ou des opérations "modulaires" pour y accéder quand l'auto-réparation est requise.

#### Acknowledgements

I would like to express my sincere gratitude to my thesis supervisor, Prof. Vinod Agarwal, for his advice, his friendship, and his insight, throughout the entire duration of my studies. His enthusiasm and his boundless patience are greatly appreciated.

In addition, I would also like to thank all of the past and present members — both students and staff — of the Lab (i.e. the Microelectronics and Computer Systems Laboratory, formerly known as the VLSI Lab) with whom I have been friends over the years. In particular, special thanks to Jacek Slaboszewicz, Michael Howells, Salim Juma, Christine Marquis, and Charles Arsenault, for their assistance on numerous occasions; and further thanks to my long-time friends Yervant Zorian, André Ivanov, Abu Hassan, and Namhyung Kim, who made ... stay in the Lab a more enjoyable experience.

On a personal level, I would like to thank my parents for their constant encouragement, forbearance and support.

This work was supported by scholarships from the Natural Sciences and Engineering Research Council of Canada, and from "le Centre de recherche informatique de Montréai." I also benefitted from an equipment and software grant made by Bell-Northern Research to our Lab.

# Table of Contents

| 1 | Int | rodu   | ction                                          | 1  |

|---|-----|--------|------------------------------------------------|----|

|   | 1.1 | Motiv  | vation for considering this subject            | 1  |

|   | 1.2 | Evalu  | ation Criteria                                 | 2  |

|   | 1.3 | Sumn   | nary of thesis                                 | 3  |

|   | 1.4 | Claim  | of original results to appear in thesis        | 4  |

| 2 | Ph  | ysica  | I Description of Embedded RAMs                 | 6  |

|   | 2.1 | Gener  | ral Structure of RAMs                          | 6  |

|   | 2.2 | Struc  | ture of Dynamic RAMs                           | 8  |

|   | 2.3 | Struc  | ture of Static RAMs                            | 12 |

|   | 2.4 | Redur  | ndancy for Static and Dynamic RAMs             | 17 |

|   | 2.5 | The n  | neaning of "embedded"                          | 18 |

| 3 | Fa  | ult M  | lodelling                                      | 19 |

|   | 3.1 | Gener  | ral Overview of Fault Models                   | 19 |

|   | 3.2 | Funct  | tional Faults affecting Memory Cells           | 20 |

|   |     | 3.2.1  | SAF: stuck-at fault                            | 20 |

|   |     | 3.2.2  | TF: transition fault                           | 20 |

|   |     | 3.2.3  | CF: coupling fault                             | 22 |

|   |     | 3.2.4  | NPSF: neighborhood pattern sensitive fault     | 25 |

|   | 3.3 | Funct  | tional Faults affecting Addressing             | 28 |

|   |     | 3.3.1  | AF/UuA: addressing fault — unused address      | 28 |

|   |     | 3.3.2  | AF/UrC: addressing fault — unreachable cell    | 28 |

|   |     | 3.3.3  | AF/MuA: addressing fault — multiused address   | 28 |

|   |     | 3.3.4  | AF/MrC: addressing fault — multireachable cell | 29 |

|   |     | 3.3.5  | Combinations of addressing faults              | 29 |

|   |     | 3.3.6  | SOAF: stuck-open addressing fault              | 30 |

|   | 3.4 | Faults | s affecting the Read/Write Circuitry:          | 33 |

|   |     | 3.4.1  | Stuck-open Access transistor:                                                   | 33 |

|---|-----|--------|---------------------------------------------------------------------------------|----|

|   |     | 3.4.2  | Stuck-open Precharge transistor:                                                | 34 |

|   |     | 3.4.3  | Stuck-open Equalization transistor:                                             | 35 |

|   |     | 3.4.4  | Stuck-open Sensing transistor:                                                  | 35 |

|   | 3.5 | Line F | aults                                                                           | 35 |

|   |     | 3.5.1  | SAF: stuck-at bit line fault                                                    | 35 |

|   |     | 3.5.2  | BF: bridged lines fault                                                         | 35 |

|   |     | 3.5.3  | SOF: stuck-open line fault                                                      | 36 |

|   |     | 3.5.4  | CF: coupled bit line fault                                                      | 36 |

|   | 3.6 | Dynai  | mic faults                                                                      | 36 |

|   |     | 3.6.1  | RecF: recovery fault                                                            | 36 |

|   |     | 3.6.2  | RetF: retention fault                                                           | 37 |

|   |     | 3.6.3  | IF: imbalance fault                                                             | 39 |

|   |     | 3.6.4  | SYNCF: synchronization fault                                                    | 39 |

| 4 | Br  | ief Su | ırvey of Literature                                                             | 40 |

|   | 4.1 | Publis | shed Surveys                                                                    | 40 |

|   | 4.2 | Exper  | rimental Results with SRAM March Tests                                          | 40 |

|   | 4.3 | More   | March tests for SRAMs                                                           | 44 |

|   |     | 4.3.1  | Direct BIST implementation of march tests                                       | 44 |

|   |     | 4.3.2  | BIST based on march tests with shifting                                         | 44 |

|   | 4.4 | Resul  | ts for DRAMs only                                                               | 45 |

|   |     | 4.4.1  | Parallel testing with March tests                                               | 45 |

|   |     | 4.4.2  | Parallel testing with Checkerboard tests                                        | 45 |

|   |     | 4.4.3  | Microcoded march and checkerboard tests                                         | 45 |

|   |     | 4.4.4  | BIST for Restricted Active and Restricted Static NPSFs in a Type-2 neighborhood | 46 |

|   |     | 4.4.5  | Fast BIST for RA and RSNPSFs in a Type-2                                        | 70 |

|   |     |        | neighborhood                                                                    | 46 |

|   |     | 4.4.6  | BIST for ANPSFs and SNPSFs in a Type-1 neighborhood                             | 47 |

|   | 4.5 | Inapr  | olicable Results                                                                |    |

|   | T   |        |                                                                                 |    |

|                                              |     | 4.5.1                               | Parallel test with signature analysis           | 47 |

|----------------------------------------------|-----|-------------------------------------|-------------------------------------------------|----|

|                                              |     | 4.5.2                               | BIST for SNPSFs in a Type-1 neighborhood        | 47 |

|                                              |     | 4.5.3                               | DFT based on tree RAM                           | 48 |

|                                              |     | 4.5.4                               | BIST based on random testing                    | 48 |

|                                              |     | 4.5.5                               | Concurrent testing                              | 48 |

| 5                                            | Hi  | gh-le                               | vel Algorithms                                  | 49 |

|                                              | 5.1 | Previ                               | ew of Test-only algorithms: detection of faults | 49 |

|                                              | 5.2 | Previo                              | ew of Diagnosis algorithms: location of faults  | 51 |

|                                              | 5.3 | Notat                               | ion for March Tests                             | 52 |

|                                              | 5.4 | Detec                               | tion & Diagnosis Algorithms and BISD Hardware   | 57 |

|                                              |     | 5.4.1                               | Serial Access to Memory                         | 58 |

|                                              |     | 5.4.2                               | Parallel Access to Memory                       | 64 |

|                                              |     | 5.4.3                               | Hybrid Serial/Parallel Access to Memory         | 64 |

|                                              |     | 5.4.4                               | Modular Access to Memory                        | 65 |

|                                              | 5.5 | Test-                               | only algorithms: detection of faults            | 66 |

|                                              |     | 5.5.1                               | Homogeneous Linked Faults                       | 66 |

|                                              |     | 5.5.2                               | Heterogeneous Linked Faults                     | 69 |

| 5.6 Diagnosis algorithms: location of faults |     | osis algorithms: location of faults | 71                                              |    |

|                                              |     | 5.6.1                               | SAF in Read/Write circuitry                     | 75 |

|                                              |     | 5.6.2                               | SAF & dominant-0 BF in Address decoders         | 78 |

|                                              |     | 5.6.3                               | Dominant-1 BF in Address decoders               | 81 |

|                                              |     | 5.6.4                               | Dominant-0/1 BF in Read/Write circuitry         | 82 |

|                                              |     | 5.6.5                               | SAF & BF in Memory cells                        | 88 |

|                                              |     | 5.6.6                               | CF in Memory cells                              | 91 |

|                                              |     | 5.6.7                               | Sequential SOAF                                 | 93 |

|                                              |     | 5.6.8                               | APNPSF location algorithms                      | 95 |

|                                              | 5.7 | Repai                               | r algorithms: allocation of spares              | 96 |

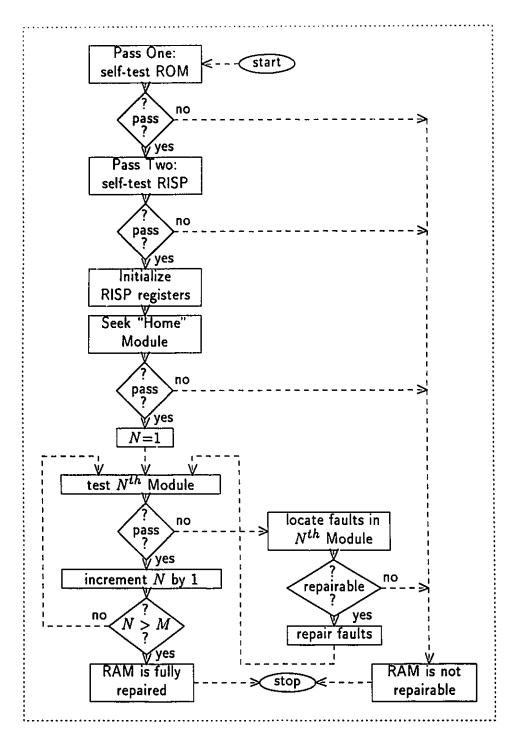

|                                              | 5.8 | Globa                               | control algorithm                               | 96 |

| 6 | De  | script | tion of Hardware Design:                      | 99  |

|---|-----|--------|-----------------------------------------------|-----|

|   | 6.1 | Gener  | al overview of test hardware                  | 99  |

|   |     | 6.1.1  | A Comparison of BIST Architectures            | 101 |

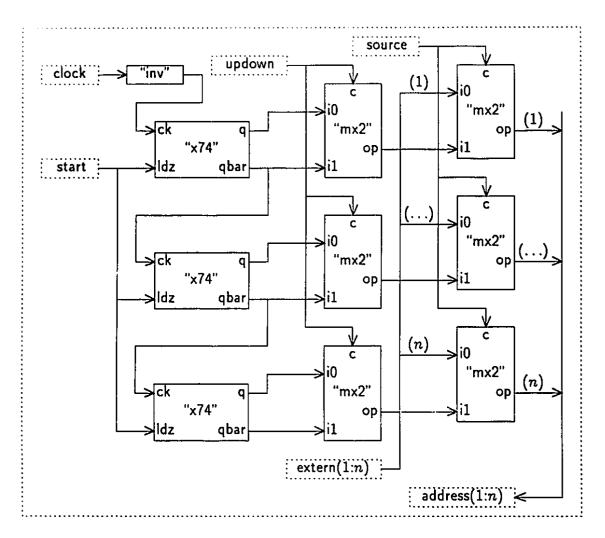

|   |     | 6.1.2  | BIST Address Generators                       | 104 |

|   |     | 6.1.3  | Pseudo-random pattern generators              | 104 |

|   | 6.2 | Descr  | iptions of the Cells, and their Operation     | 105 |

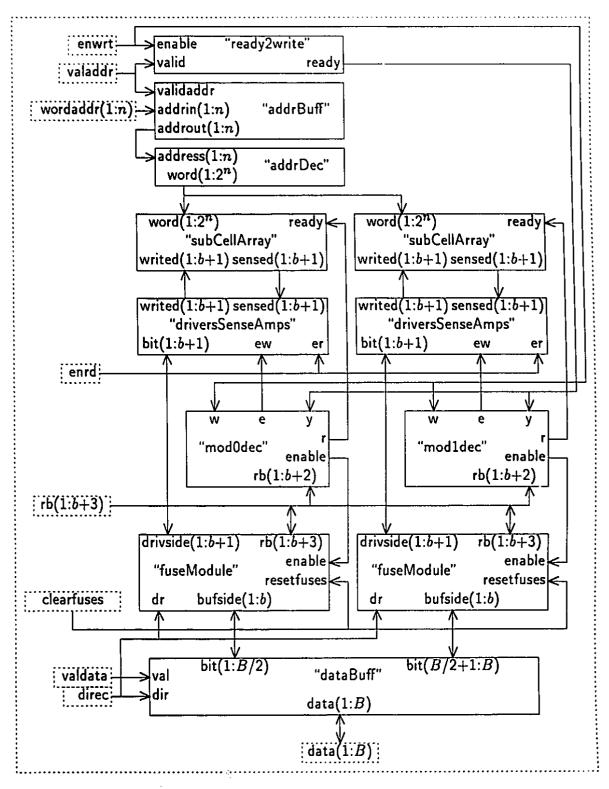

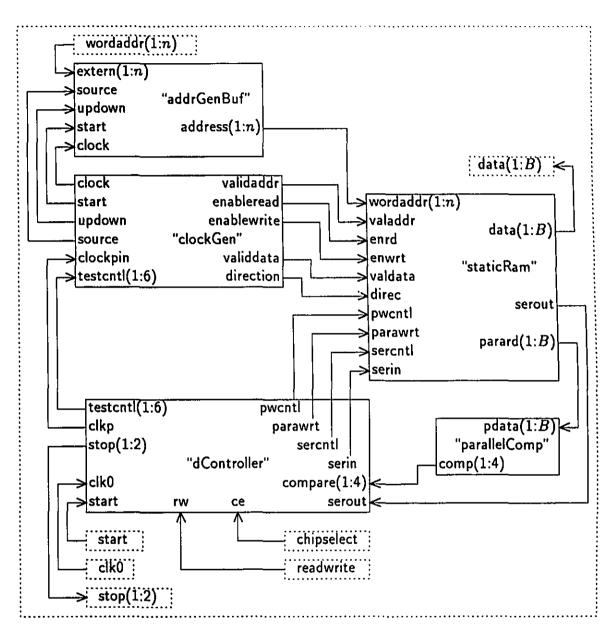

|   |     | 6.2.1  | "withRepair" (Fig. 6.1)                       | 105 |

|   |     | 6.2.2  | "diagnosisOnly" (Fig. 6.24)                   | 127 |

|   | 6.3 | Desig  | n costs and tradeoffs                         | 134 |

|   |     | 6.3.1  | Area Overhead                                 | 134 |

|   |     | 6.3.2  | Repair Choices                                | 136 |

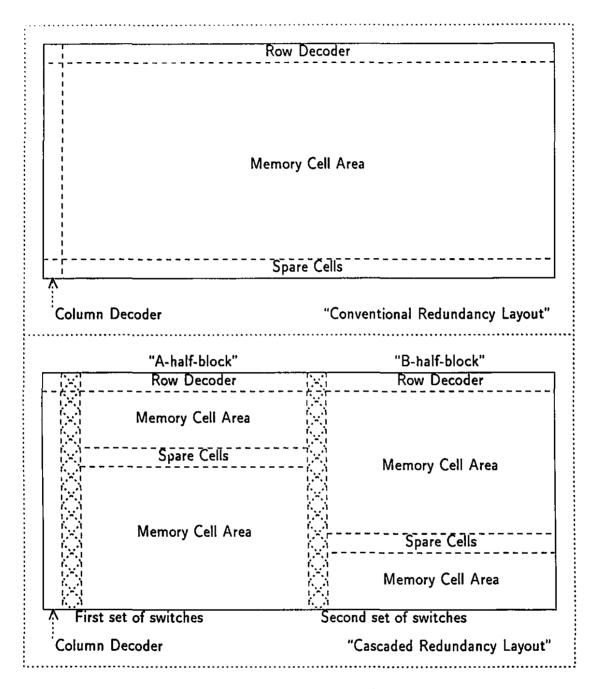

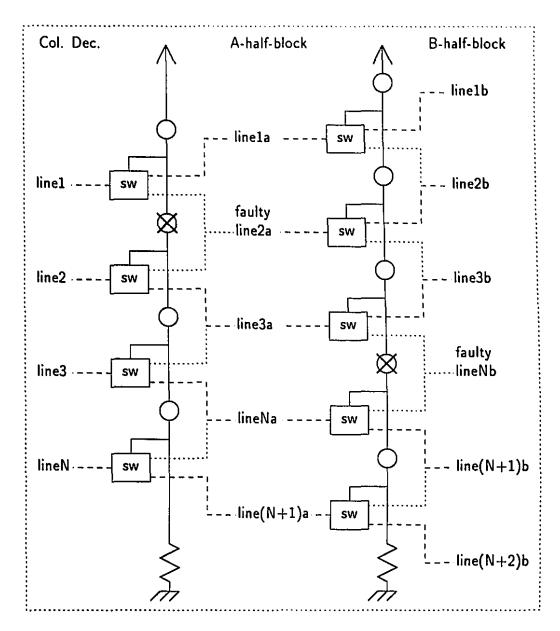

|   |     | 6.3.3  | Hierarchical Redundancy                       | 137 |

|   |     | 6.3.4  | Segmentation of Spares                        | 139 |

|   |     | 6.3.5  | Redundancy Choices                            | 141 |

| 7 | Lo  | w-lev  | el Algorithms:                                | 145 |

|   | 7.1 | Low-I  | evel notation for writing the algorithms      | 145 |

|   | 7.2 | Trans  | slation from High-level to Low-level notation | 151 |

| 8 | Co  | nclus  | sion                                          | 155 |

|   | 8.1 | Short  | Summary                                       | 156 |

|   | 8.2 | Signif | ficance of Original Results                   | 158 |

|   | 8.3 | Futur  | e Work                                        | 158 |

| 9 | Bi  | bliogi | raphy                                         | 160 |

# List of Figures

| 2.1  | A Typical Dynamic RAM                                        | . 9  |

|------|--------------------------------------------------------------|------|

| 2.2  | Sense Amplifier with Dummy Word Lines                        | 10   |

| 2.3  | Sense Amplifier with Direct Precharge                        | 11   |

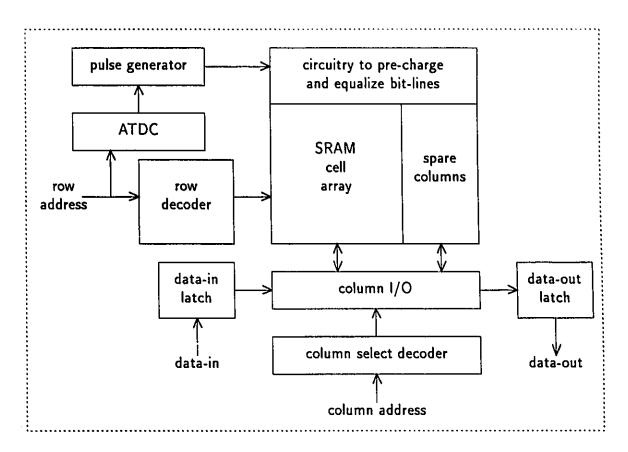

| 2.4  | A Typical Static RAM                                         | 13   |

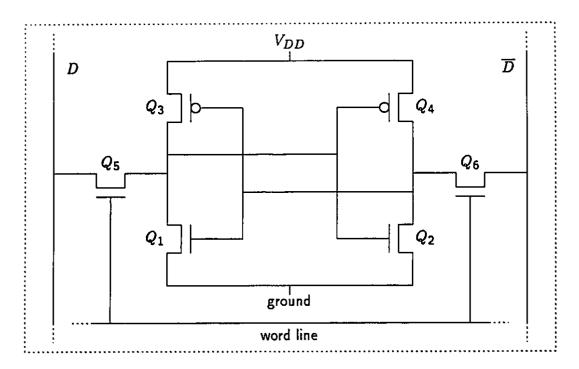

| 2.5  | Six Transistor (6-T) SRAM Cell                               | 14   |

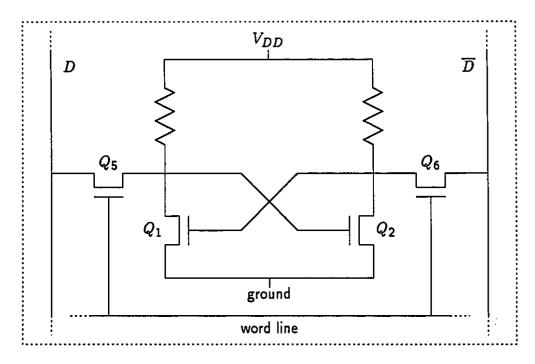

| 2.6  | Four Transistor (4-T) SRAM Cell                              | 14   |

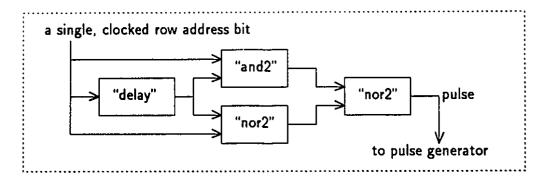

| 2.7  | One kind of Address Transition Detection Circuit             | 16   |

| 2.8  | Dynamic Multiple Word Line (DMWL) Scheme                     | 16   |

| 3.1  | Examples showing the Nine Combinations of Addressing Faults  | . 27 |

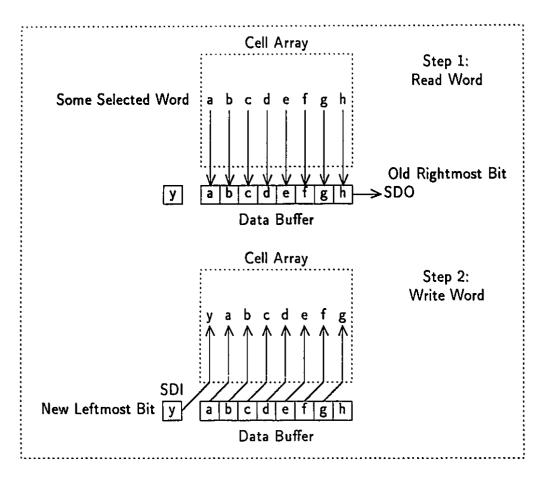

| 5.1  | Serial Read/Write in 2 steps, using "virtual" shift register | . 62 |

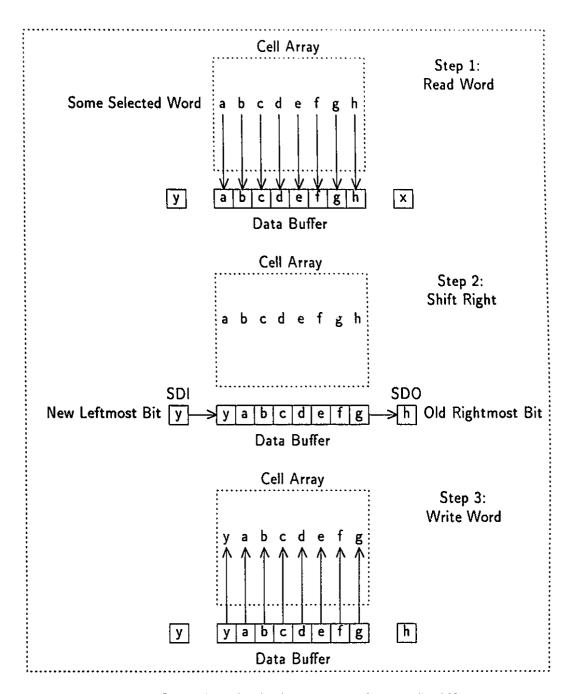

| 5.2  | Serial Read/Write in 3 steps, using "real" shift register    | 63   |

| 5.3  | Flow-chart of global Diagnosis and Repair procedure          | 97   |

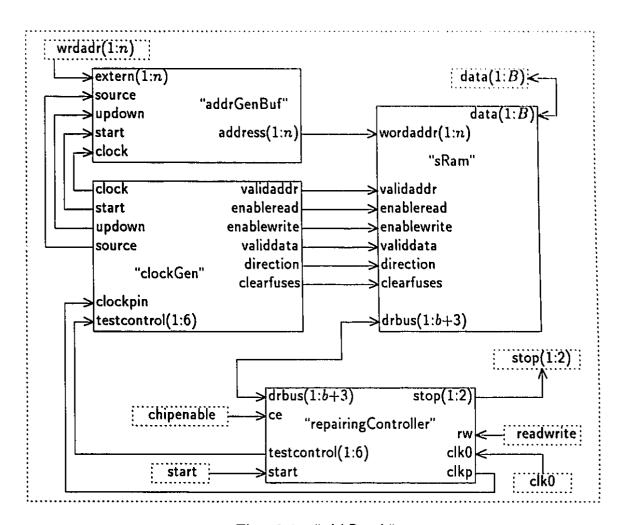

| 6.1  | "withRepair"                                                 | 106  |

| 6.2  | "addrGenBuf"                                                 | 107  |

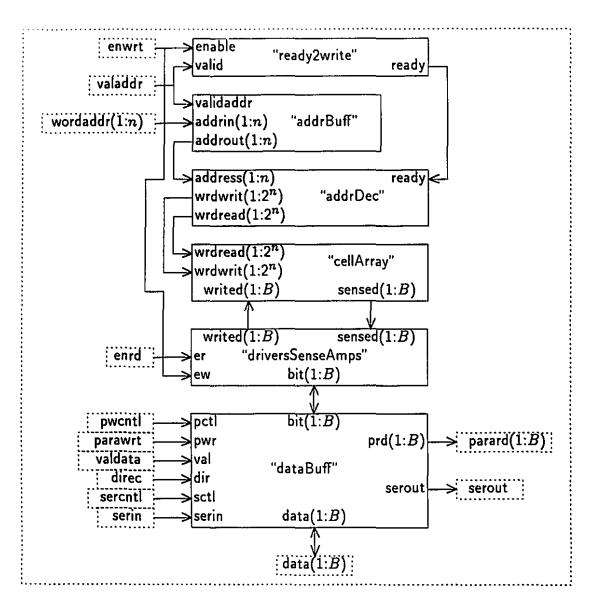

| 6.3  | "sRam" (repairable Static RAM)                               | 108  |

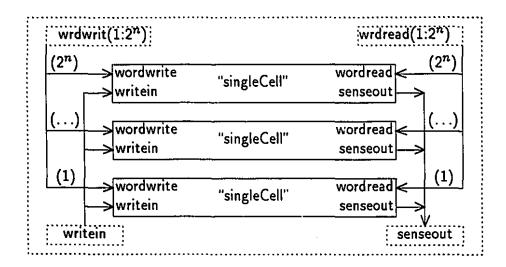

| 6.4  | "singleCell"                                                 | 110  |

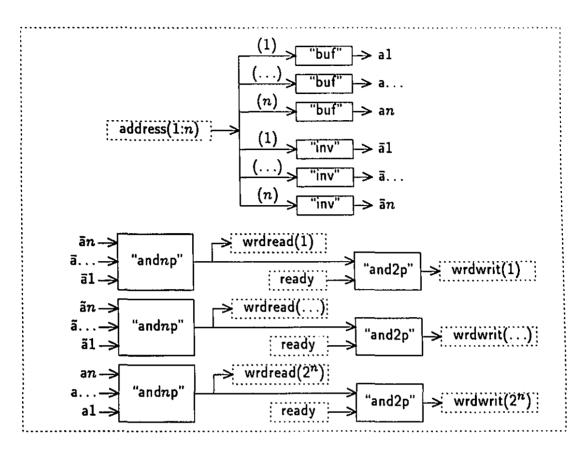

| 6.5  | "mod#dec" (module #0 decoder)                                | 111  |

| 6.6  | "fuseModule"                                                 | 112  |

| 6.7  | "softFuse"                                                   | 113  |

| 6.8  | "bidirecMux" (bidirectional multiplexer)                     | 113  |

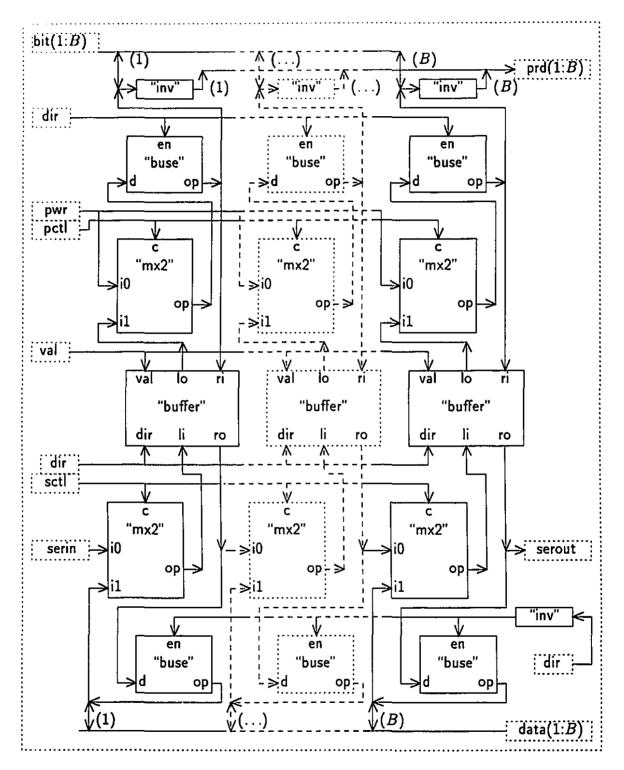

| 6.9  | "dataBuffer"                                                 | 114  |

| 6.10 | "repairingController"                                        | 115  |

| 6.11 | "alu" (b-bit arithmetic and logic unit)                      | 116  |

| 6.12 | "busPort"                             | 117 |

|------|---------------------------------------|-----|

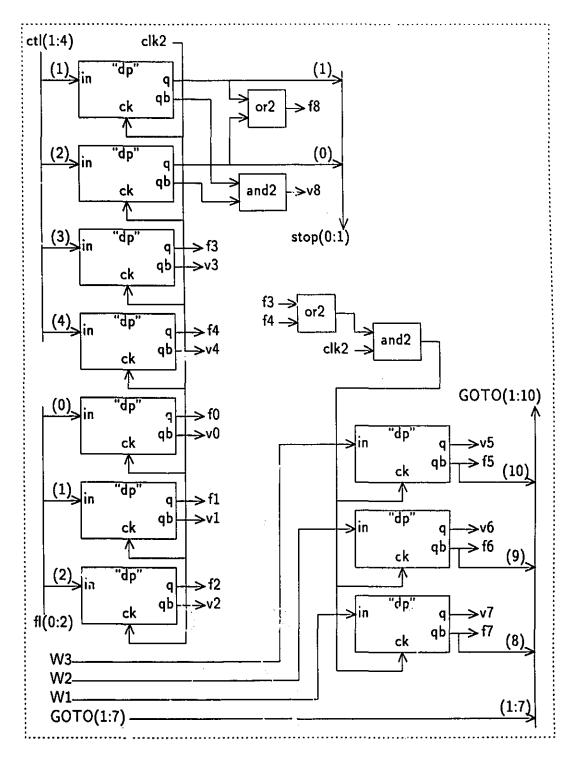

| 6.13 | "instrRegCntl" (part 1)               | 119 |

| 6.14 | "instrRegCntl" (part 2)               | 120 |

| 6.15 | "instrRegCntl" (part 3)               | 121 |

| 6.16 | "instrRegCntl" (part 4)               | 122 |

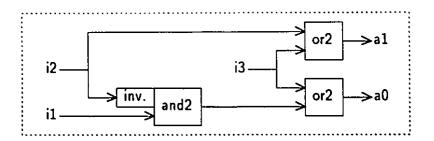

| 6.17 | "pe42" (priority encoder)             | 123 |

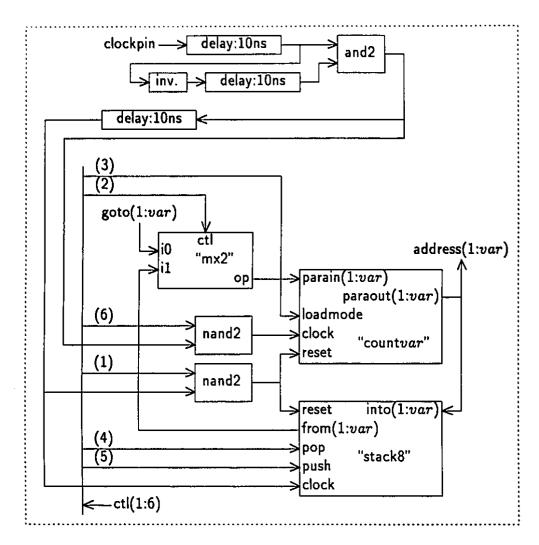

| 6.18 | "pCstack" (program counter stack)     | 125 |

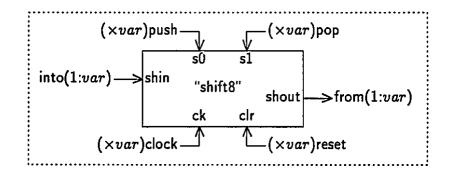

| 6.19 | "stack8" (8-item stack)               | 125 |

| 6.20 | "shift8" (8-bit shift register)       | 126 |

| 6.21 | "countvar" (var-bit counter)          | 126 |

| 6.22 | "countA"                              | 127 |

| 6.23 | "countB"                              | 127 |

| 6.24 | "diagnosisOnly"                       | 128 |

| 6.25 | "staticRam"                           | 129 |

| 6.26 | "addrDec"                             | 130 |

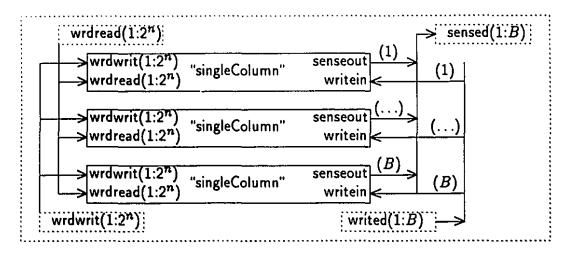

| 6.27 | "cellArray"                           | 131 |

| 6.28 | "singleColumn"                        | 131 |

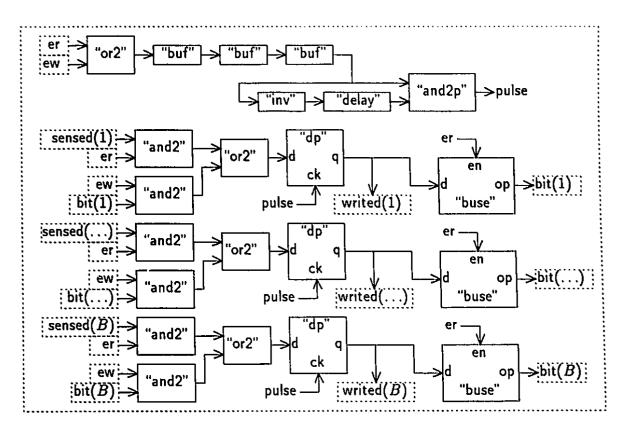

| 6.29 | "driversSenseAmps"                    | 132 |

| 6.30 | "dataBuff"                            | 133 |

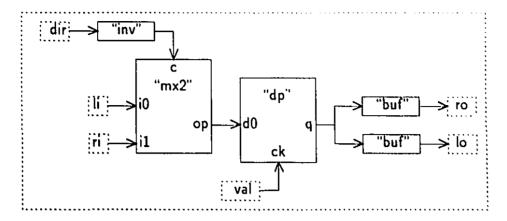

| 6.31 | "buffer"                              | 134 |

| 6.32 | Average area overheads for 6-T arrays | 135 |

| 6.33 | "Two Redundancy Techniques Compared"  | 139 |

| 6.34 | "Cascaded Redundancy"                 | 140 |

|      |                                       |     |

C

# List of Tables

| 3.1  | Summary of Functional Fault Models                                                                                                                                                                                                                                       | 21 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Summary of Dynamic Fault Models                                                                                                                                                                                                                                          | 22 |

| 4.1  | IFA-9 Algorithm — combinational sense amps                                                                                                                                                                                                                               | 42 |

| 4.2  | IFA-13 Algorithm — sequential sense amps                                                                                                                                                                                                                                 | 43 |

| 4.3  | Static Data Retention Algorithm — one-bit version                                                                                                                                                                                                                        | 43 |

| 4.4  | Shortest "Sequential Sense-Amp" March Tests                                                                                                                                                                                                                              | 44 |

| 5.1  | March-B Algorithm — one-bit version                                                                                                                                                                                                                                      | 50 |

| 5.2  | The new March-B+ Algorithm — one-bit version                                                                                                                                                                                                                             | 50 |

| 5.3  | MATS+ Algorithm — one-bit version                                                                                                                                                                                                                                        | 51 |

| 5.4  | The new MATS++ Algorithm — sequential sense amps                                                                                                                                                                                                                         | 51 |

| 5.5  | 8-bit "Primary" data backgrounds                                                                                                                                                                                                                                         | 53 |

| 5.6  | "Primary" 8-bit version of March-B+ Algorithm                                                                                                                                                                                                                            | 54 |

| 5.7  | 8-bit "Odd-Marching" data backgrounds                                                                                                                                                                                                                                    | 55 |

| 5.8  | 8-bit "Even-Marching" data backgrounds                                                                                                                                                                                                                                   | 55 |

| 5.9  | 8-bit "Odd-Walking" data backgrounds                                                                                                                                                                                                                                     | 56 |

| 5.10 | 8-bit "Even-Walking" data backgrounds                                                                                                                                                                                                                                    | 56 |

| 5.12 | $(U,D,L)$ representation of data backgrounds $\ldots$                                                                                                                                                                                                                    | 56 |

| 5.11 | "Marching" & "Walking" 8-bit version of March-B+ Algorithm                                                                                                                                                                                                               | 57 |

| 5.13 | Serialized march elements                                                                                                                                                                                                                                                | 59 |

| 5.14 | The "Galloping read-action:" $\binom{ra, \cdot}{\cdot, rb}$                                                                                                                                                                                                              | 71 |

| 5.15 | The "Walking read-action:" $\binom{ra}{\cdot}$ ; $rb$                                                                                                                                                                                                                    | 72 |

| 5.16 | The GALPAT Algorithm                                                                                                                                                                                                                                                     | 73 |

| 5.17 | An example of the "Generalized Galloping FOR-loop:" $\begin{pmatrix} ra, & \cdot, & wb, & rb, & \cdot \\ \cdot, & rc, & \cdot, & \cdot, & rc \end{pmatrix} \dots $ | 74 |

| 5.18 | Notation to represent selective addressing:  [address list](operation list) | 75 |

|------|-----------------------------------------------------------------------------|----|

| 5.19 | Detect stuck-at-1 data line                                                 | 75 |

| 5.20 | Locate stuck-at-1 data line, in bit-serial fashion                          | 76 |

| 5.21 | Detect stuck-at-0 data lines                                                | 78 |

| 5.22 | Initialize orthogonal addresses                                             | 78 |

| 5.23 | Locate a single stuck-at-1 address line                                     | 79 |

| 5.24 | Locate a single stuck-at-0 address line                                     | 80 |

| 5.25 | Locate several stuck-at address lines                                       | 81 |

| 5.26 | Locate one of a pair of dominant-1 shorted address lines                    | 82 |

| 5.27 | Locate remaining dominant-1 shorted address line                            | 83 |

| 5.28 | Data background for dominant-0 shorted bit lines                            | 83 |

| 5.29 | Locate dominant-0 shorted bit lines                                         | 85 |

| 5.30 | Locate dominant-1 shorted bit lines                                         | 85 |

| 5.31 | Case 1: Dominant-0 short sandwiched by Dominant-1 short                     | 86 |

| 5.32 | Case 2: Dominant-1 short sandwiched by Dominant-0 short                     | 86 |

| 5.33 | Case 3: overlapping Dominant-0 and Dominant-1 shorts, different widths      |    |

| 5.34 | Case 4: overlapping Dominant-0 and Dominant-1 shorts, equal widths          | 87 |

| 5.35 | Case 5: completely separate Dominant-0 and Dominant-1 shorts                | 87 |

| 5.36 | Initialize memory                                                           | 88 |

| 5.37 | Detect stuck-at-0 cell faults                                               | 89 |

| 5.38 | Locate stuck-at-1 cell faults                                               | 90 |

| 5.39 | The new Diagnostic March-B± Algorithm                                       | 90 |

| 5.40 | Locate Actively coupled and coupling cells                                  | 91 |

| 5.41 | Locate Actively coupled and coupling cells     | 92  |

|------|------------------------------------------------|-----|

| 5.42 | Locate Actively coupled and coupling cells     | 92  |

| 5.43 | Locate Actively coupled and coupling cells     | 93  |

| 5.44 | A Galloping algorithm to locate Coupling cells | 93  |

| 5.45 | Locate Stuck-open addressing faults            | 94  |

| 6.1  | Priority Encoder truth-table                   | 123 |

| 6.2  | 1-of-4 Multiplexer truth-table                 | 124 |

| 6.3  | 1-of-8 Multiplexer truth-table                 | 124 |

| 6.4  | BISD overhead for 6-T arrays                   | 136 |

| 6.5  | Overhead comparison for 4-T arrays             | 136 |

1 Introduction

## 1.1 Motivation for considering this subject

Random Access Memories (RAMs) are the densest circuits being fabricated today. Because their transistors and lines are packed so closely together, RAMs suffer from a very high average number of physical defects per unit area compared with other types of circuits, and this fact has motivated researchers to develop efficient RAM-test sequences that provide good fault coverage [Abadir and Reghbati 83], [van de Goor and Verruijt 90]. The published results have led some researchers to suggest that a better solution to the RAM testing problem can be obtained by redesigning and augmenting the peripheral circuits surrounding the cell array of the RAM, in order to improve the RAM's testability [Inoue et al. 87], [Sridhar 86]. Others have proposed the addition of even more extra circuitry to achieve a self-testing RAM, thereby dispensing with expensive external test equipment [Dekker et al. 89], [Franklin and Saluja 90], [Franklin et al. 90], [Mazumder and Patel 89], [Ohsawa et al. 87], [Ritter and Müller 87], [Saluja et al. 87], [Takeshima et al. 90], [You and Hayes 85]. The principal motivation behind the proposals for designed-for-testability RAMs and self-testing RAMs is the significant reduction in total testing time compared with conventional RAM testing procedures.

An embedded RAM usually cannot be tested by simply applying test patterns directly to the I/O pins, because the embedded RAM's data, address and control signals are not accessible through the I/O pins. As a result, there are some published design proposals for built-in self-testing embedded RAMs [Jain and Stroud 86], [Nadeau-Dostie et al. 90], [Nicolaidis 85], [Sun and Wang 84]. Given current trends, it is reasonable to expect that eventually the size of some embedded RAMs will grow so large that yield considerations will require these embedded RAMs to have spare rows and spare columns. When this happens, built-in test circuits will be needed that not only detect the presence of faults, but also specify the location of faults for repair purposes. A built-in self-diagnosis (BISD) method, which can test and locate faults in embedded RAMs, and which can be implemented using a small amount of extra area, is the subject of this thesis.

The heart of the proposed method is the Diagnosis and Repair Unit, which is composed of a small reduced-instruction-set-style processor, which executes instructions stored in a small read-only memory (ROM). When the embedded RAM is externally repairable (i.e., it has spare rows and columns that are programmed by blowing fuses with laser beam pulses), the Diagnosis and Repair Unit first locates all the faults, and then sends a repair procedure to the equipment which controls the laser beam. However, when the RAM is internally repairable (i.e., it has "soft fuses," which may be EEPROM cells or ordinary flip-flops), the Diagnosis and Repair Unit will program the "soft fuses" by itself, without help from any external equipment. The same Diagnosis and Repair Unit (DR-Unit) can be used to test, diagnose, and (optionally) repair more than one embedded RAM on the same chip.

### 1.2 Evaluation Criteria

١.)

The list below enumerates a possible set of parameters which can be used to evaluate the overall quality of a given built-in self-testing, self-diagnosing, and (possibly) self-repairing circuit design. Only methods which optimize most or all of these parameters are acceptable for implementation.

- \* The area overhead incurred by the extra circuitry (minimize).

- \* The effect of the extra circuitry on the *performance* of the original circuit (minimize).

- \* The time required to apply the tests and perform the diagnosis (minimize).

- \* The fraction of faults located by the built-in self-diagnosis (maximize).

- The repair algorithm's allocation of spare resources to repair faults (i.e., the generated repair-plan should deviate minimally from the optimal repairplan).

- \* The self-testability of the extra circuitry which actually performs the self-diagnosis and self-repair (maximize).

- \* The design time needed by an engineer to implement the given method (by minimizing the amount of custom redesign required for each new memory block; ideally, any software that generates layouts of complete memory modules could also generate, as part of each layout, the additional built-in self-diagnosis circuitry).

- \* The *flexibility* of the design, in particular:

- o independence of the fabrication technology being used,

- ability to accommodate to new and different fault types as the technology evolves, and

- applicability, with minor changes, to different types of memories, such as dual-port Static RAMs, and Dynamic RAMs with various addressing capabilities.

## 1.3 Summary of thesis

This thesis presents the details of how to design both self-diagnosing and self-repairing embedded RAMs (applicable to both Static and Dynamic RAMs), that

can be implemented using a reasonable amount of extra area. Chapter 2 presents a summary of the variety of physical implementations used to obtain static and dynamic RAMs. Chapter 3 presents an organized list of the various fault models described in the literature. Chapter 4 contains a short survey of the most relevant previously published work on the topic of BIST for RAMs and embedded RAMs. Chapter 5 gives a general view of the software components of such a design. The details of the hardware designs are presented in Chapter 6. The specific details of the software components, as they relate to the hardware, are given in Chapter 7.

## 1.4 Claim of original results to appear in thesis

As will be seen from what follows, the self-diagnosis designs proposed in this thesis, largely satisfy the evaluation criteria enumerated above. In particular, the new proposed designs possess several qualities which make them more attractive than any of the *more obvious* self-diagnosis designs.

- (1.) The new designs make use of the memory capacity of the embedded RAM itself during the execution of some of the diagnosis algorithms, and thereby save much silicon area which would otherwise be an additional part of the Diagnosis and Repair Unit, and which would only be used to provide temporary storage for the fault maps generated by some of the algorithms.

- (2.) The new algorithms are based on a combination of serial and parallel BIST hardware structures, where previous algorithms dealt with only one kind of BIST hardware structure.

- (3.) The new designs are non-intrusive because the only extra circuitry that is placed inside the memory array itself is a purely local bus; and because all the other extra circuitry can be placed almost anywhere on the same IC chip, provided that the local bus can be routed so that it links the embedded repairable RAM to the Diagnosis and Repair Unit.

- (4.) The new designs are *programmable* because they use a small, easilyalterable ROM to store the diagnosis and repair algorithms.

- (5.) With a very small allocation of additional hardware, the new designs can execute relatively complex diagnosis and repair algorithms, because the designs employ a data-path structure that functions almost like a small reduced-instruction-set processor.

- (6.) Chapter 5 contains a general description of how to modify any single-bit march test so that the same algorithm can be applied to any RAM with B-bit words. Previously published books and papers dealing with march tests have not shown the precise details of how this transformation is carried out in particular, the distinctions between "state-changing" and "state-retaining" march elements have not been made before, nor have the two types of Marching data backgrounds and two types of Walking data backgrounds been differentiated.

# 2 Physical Description of Embedded RAMs

### 2.1 General Structure of RAMs

Random access memories (also called read/write memories) allow binary data to be stored and fetched at approximately the same speed, currently ranging from a very fast 10 nanoseconds (ns) to a relatively slow 500 ns, depending on the fabrication technology, and the type of the memory. One measure of the operating speed of a memory is its access time  $t_a$ , which is the maximum time required to read a word from the memory. It is measured from the application of a new address on the address bus to the appearance of the valid data on the data bus. The process of reading or writing a word requires that various signals be applied to the address, control and data lines, and is called a read or write memory cycle. The memory cycle time  $t_c$  is the minimum time that must elapse between the initiation of two successive memory operations. Currently, the fastest DRAMs have access times of about 50ns, and cycle times of about 100ns.

Semiconductor random access memory (RAM) circuits are volatile; this means that if power to the RAM is shut off, then the stored information is lost. Semiconductor RAMs are mainly classified into two types: dynamic RAMs and static RAMs (the remaining type of RAM is the Content Addressable Memory, or CAM, which will not be considered in this thesis). Dynamic RAMs function by storing low or high voltages across capacitors. Because there is some leakage of

À

charge off these capacitors, the data must be periodically sensed and restored to their original voltages by refresh operations. These refresh cycles must periodically displace the normal data access cycles of a dynamic RAM circuit in order to prevent the irretrievable loss of stored data. Static RAMs do not require such refresh cycles nor any other kind of periodic data access (read or write), but can maintain stored information indefinitely, as long as the power supply is uninterrupted. In spite of the greater functional simplicity of static RAMs, it is dynamic RAMs which are more widely used in large quantities, because the price per bit and power per bit ratios are significantly less for dynamic RAMs than for static RAMs, with equivalent storage capacity. However in chips where the RAMs are embedded, mostly static RAMs are used, because static RAMs have much faster access times than dynamic RAMs with equivalent storage capacity.

The memory cell arrays of RAMs are organized into W words of B bits each, for a total information capacity of WB bits. The information capacity of a memory may also be quoted in terms of bytes, where 8 bits grouped together are known as a byte. Very often, the number of bits per memory word, designated by B, is a multiple of 8, such as 16 or 32, signifying that each memory word consists of a whole number of bytes, such as 2 or 4 bytes. Full-chip RAMs, that are used in the main memories of computers, are often organized to provide only a single data bit for read/write access at a time (i.e., B=1). Embedded RAMs may have any number of bits per word.

A binary-encoded group of input bits provides an address that points to a particular word of B bits. The data will either be read from or written to the addressed word. The access time is independent of the particular address chosen, and is determined by the time it takes one of the address decoder circuits to activate exactly one row or column select line. In most memory designs there are separate row address decoders and column address decoders because of the layout characteristics of the memory cell array, although there are some RAMs which use only row address decoders. In DRAMs there is usually only one address latch to

store the incoming address value (it really is only half of an address), and the latch will transmit its contents to either the row decoder or column decoder, as required. This multiplexing of addresses in DRAMs was not adopted merely because it results in lower pin-counts, but because the slowness of the sense amplifiers in detecting and amplifying the tiny signals from the cells, allows plenty of time for the column address to be decoded after the row address has been decoded first. In SRAMs, which have much faster read/write circuitry than DRAMs do, the full address is usually stored in one address register, and the appropriate address bits will be simultaneously transmitted to both the row and column decoders.

## 2.2 Structure of Dynamic RAMs

In DRAMs, the address decoders are also subject to control by the refresh logic. When the refresh line is activated by the refresh clock (typically every 1 to 5 milliseconds), the column decoder selects all columns. The row decoder selects the row specified by the value in the address latch. All of the bits in the chosen row are read out and then written back ("refreshed") simultaneously. During such a refresh cycle, the refresh logic has the additional function of disabling all input to and output from the data register.

"Reading" or "writing" a bit of data from a DRAM, first requires the selection of a word line by raising it from its *precharged* level of 0 volts to the supply voltage value (usually designated by  $V_{DD}$ ). All of the transfer gate transistors connected to the selected word line are turned on, and this causes charge to be transferred from each of the capacitors to their respective bit lines, and thus also causes the destructive reading of all the data in the chosen word. Before the charge from the cells was transferred to the bit lines, the bit lines were *precharged* to some pre-established value, usually to one half of the supply voltage. Each bit line has its own sense amplifier, whose function is to detect this charge transfer and to amplify the signal caused by it. The amplified signal ideally has a value of either

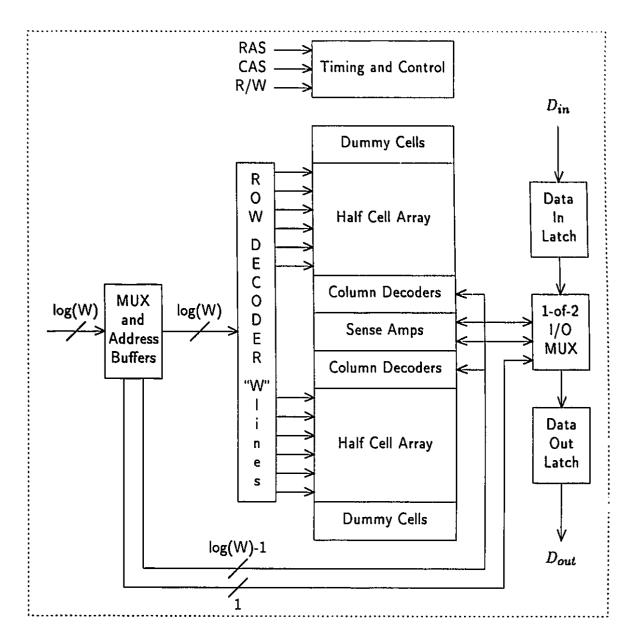

Fig. 2.1 A Typical Dynamic RAM

$V_{DD}$  or ground. The transfer gate transistors continue to remain on throughout this period so that the amplified signals from the sense amplifiers can be fed back into their respective cells to restore the word of data.

"Writing" one bit to a DRAM is performed almost exactly like "reading" one bit. The only difference is that exactly one sense amplifier does not feed back the sensed bit line value to restore the charge to one cell, but it takes a new value from

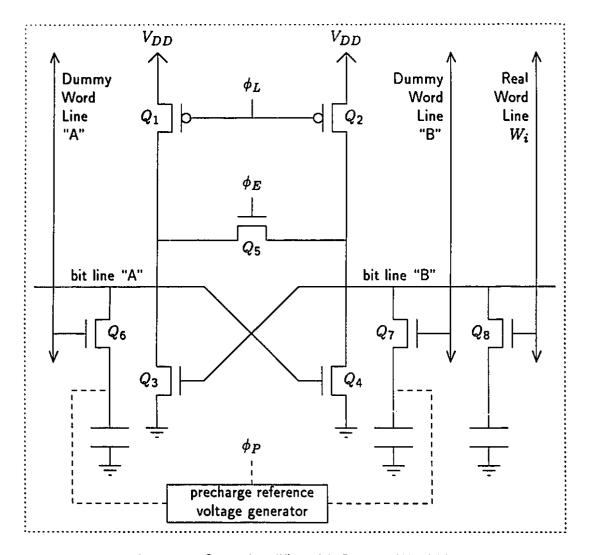

Fig. 2.2 Sense Amplifier with Dummy Word Lines

the data latch which stores a data bit that has been transmitted to the DRAM, and asserts this new value on the bit line to be stored into the one cell.

To maximize the signal into the sense amplifier, a large cell capacitance and a small bit line capacitance are desired. The bit line capacitance can be reduced by simply cutting the line in half and placing the sense amplifier in the middle between the two halves. As figure 2.1 shows, a DRAM makes use of half cell-arrays, dual column decoders, a central row of sense amplifiers, and dummy cells located on both sides, which are used to establish a voltage reference for the sense

$I_{\ell}$

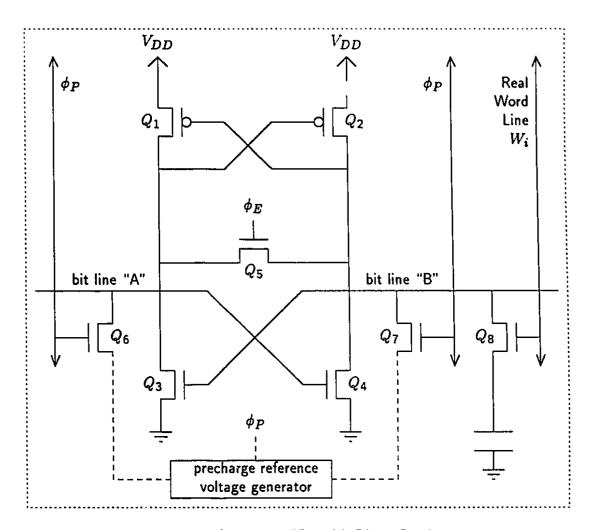

Fig. 2.3 Sense Amplifier with Direct Precharge

amplifiers. Because of how the sense amplifiers operate, one of the two half cell-arrays complements all incoming data bit, storing a "1" as a low voltage and a "0" as a high voltage. The output circuitry for that particular half cell-array performs another complementation to restore the data bit's original value.

As can be seen from figures 2.2 and 2.3, a sense amplifier is basically a differential amplifier that has been augmented with clock signals and a precharge reference voltage (typically  $V_{DD}/2$ ). The precharge voltage can be applied through the access transistor of each dummy word line, as shown in figure 2.2, or it can be applied directly to the bit lines, as shown in figure 2.3. In the first case, the

()

capacitances of the storage cells connected to the dummy word line are identical to the capacitances of all the other storage cells; this results in (1.) the dummy cells storing a charge halfway between  $V_{DD}$  and ground, and (2.) the real storage cell's capacitance being exactly counterbalanced by the dummy cell's capacitance on the other bit line half. In the second case, the dummy storage cells (not shown in figure 2.3) usually have half the capacitance (and hence almost half the size) of real storage cells, but this means that the dummy cells must be pre-charged to  $V_{DD}$  instead of  $V_{DD}/2$  in order to store the appropriate amount of charge; therefore, such dummy cells are precharged separately from the bit lines. All sense amplifiers contain an equalization transistor, gated by the clock  $\phi_E$ , in order to even out any unintended charge differences between the bit line halves after the precharging phase, and before the actual sensing operation takes place. The sense amplifiers discussed above are merely meant to be representative; in fact, there are many distinctly different sense amplifier designs that have been published — each DRAM manufacturer uses a different design.

### 2.3 Structure of Static RAMs

In Static RAMs, as shown in figure 2.4, no periodic clock signals are needed to retain the stored data. There are two main types of memory cells used in CMOS SRAMs. The 4-transistor (4-T) cell has four n-channel transistors and two polysilicon pull-up resistors. The resistors are created in a high-resistivity second polysilicon layer, which allows the resistors to be *stacked* on top of the rest of the cell. The resistors must be properly insulated from the transistors below by an appropriately thick oxide layer. In the 6-transistor (6-T) cell, the two resistors are replaced by two p-channel transistors. Because transistors are more resistant to  $\alpha$ -particle radiation and large temperature swings than resistors, the 6-T cell suffers from fewer soft errors than the 4-T cell. In addition, the 6-T cell consumes less power because its loads need very low standby current. As a result of these advantages, the 6-T cell CMOS SRAMs are preferred for military and other critical

Fig. 2.4 A Typical Static RAM

applications. SRAMs using the 4-T cells have smaller die sizes, and hence cost less to manufacture, which explains their popularity in commercial applications where a low price is a major concern.

Figure 2.5 shows a typical 6-T cell in CMOS. The cell uses a pair of cross-coupled inverters,  $Q_1$  through  $Q_4$ , as the storage latch, and two access transistors,  $Q_5$  and  $Q_6$ . The 4-T cell of figure 2.6 uses two polysilicon resistors to replace the transistors  $Q_3$  and  $Q_4$  of the 6-T cell, which results in a smaller cell area. The selection of these resistances is critical. If the resistance is too low then the static (or standby) power consumption will be too high. If the resistance is too high then the charge representing the value "1" that is stored on the gate of either  $Q_1$  or  $Q_2$  may be indistinguishable (given the effects of noise) from the charge representing the value "0". Complementary bit lines D and  $\overline{D}$  are used because it

Fig. 2.5 Six Transistor (6-T) SRAM Cell

Fig. 2.6 Four Transistor (4-T) SRAM Cell

is difficult to achieve reliable operation with a single bit line at high speeds, when the wide variations in operating temperature and device parameters are taken into account. The word line is kept tied to ground until the cells connected to it are to be accessed for reading or writing, which is when the word line's voltage is raised to  $V_{DD}$ .

Writing is performed by assigning the value to be written and its complement to the D and  $\overline{D}$  lines, respectively. To illustrate the write operation more clearly, assume that we are given a cell which currently stores a logical "0", and that we wish to now store a logical "1" in the same cell. The first step is to raise the Dline to  $V_{DD}$  and to lower the  $\overline{D}$  line to ground. Since the cell is storing a "0", this means that  $Q_1$  and  $Q_4$  are on, and that  $Q_2$  and  $Q_3$  are off. When the access transistors  $Q_5$  and  $Q_6$  are turned on, the two node voltages start to change. The transistor parameters are chosen in such a way that the resistances of  $Q_5$  and  $Q_6$ are much lower than the resistances of  $Q_1$  through  $Q_4$ . Note that there is now a path from  $V_{DD}$  on line D, through  $Q_5$ , through  $Q_1$ , to ground. Because  $Q_1$  has most of the resistance in this voltage divider, the voltage of the node between  $Q_5$ and  $Q_1$  has gone from 0 volts to greater than half of  $V_{DD}$ . This node is connected to the gates of  $Q_2$  and  $Q_4$ , and its new voltage will tend to turn off  $Q_4$  and turn on  $Q_2$ . Once  $Q_2$  has started to conduct, the voltage of the node between  $Q_4$  and  $Q_2$  will start to drop from greater than half of  $V_{DD}$  down to ground, and this will tend to turn off  $Q_1$  and turn on  $Q_3$ . Once  $Q_2$  and  $Q_3$  are completely turned on, and  $Q_1$  and  $Q_4$  are completely turned off, the write operation is successful, and the word line may then be returned to 0 volts.

Reading is performed by first precharging and equalizing the dual bit lines to half of  $V_{DD}$ , and then, just before the access transistors are turned on, allowing the bit lines to float. To illustrate the read operation more clearly, let us assume once more that the given cell currently stores a logical "0". When the word line is activated, the conducting path from bit line D through  $Q_5$ , through  $Q_1$ , to ground, pulls down the voltage of line D to 0 volts. Similarly, the conducting path

Fig. 2.7 One kind of Address Transition Detection Circuit

Fig. 2.8 Dynamic Multiple Word Line (DMWL) Scheme

from  $\overline{D}$  through  $Q_6$ , through  $Q_4$ , to the supply voltage, pulls up the voltage of line  $\overline{D}$  toward  $V_{DD}$ . In the fastest SRAMs, sense amplifiers are used to detect the initial voltage difference in order to complete the read operation more quickly.

SRAMs contain an address transition detection circuit (ATDC), which starts the precharging and equalization of the bit lines during the time it takes a new word line to become activated. This means that the row address lines are fed to both the row decoder and the ATDC, so that any change in row address is immediately followed by precharging and equalization. Since column access time is much faster than row access time, an ATDC is not connected to the column address lines. Figure 2.7 shows one bit slice of one type of ATDC.

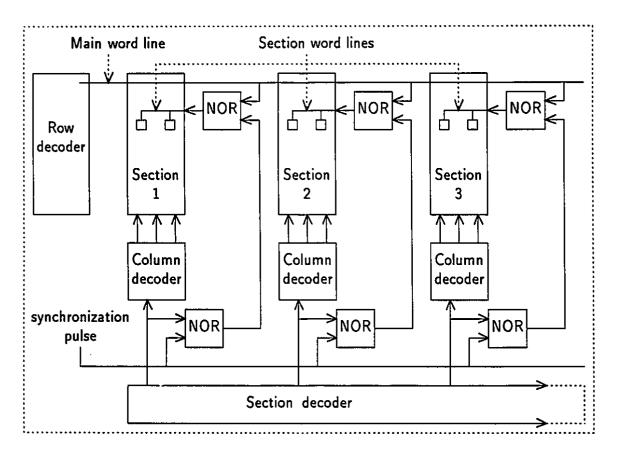

An additional way to reduce the access time is to use a *dynamic multiple word line (DMWL)* scheme. As figure 2.8 illustrates, there are two levels of word lines. The *main* word line is not directly connected to any of the memory cells, which causes the line's capacitance to be quite small, resulting in a reduction of word-line delay. Only one *section* word line is active at a time, and thus only a few cells are accessed at a time, which also shortens delay and reduces the power dissipation. The ATDC generates a synchronization pulse that enables NOR-gates which allow the selection of exactly one section word line.

### 2.4 Redundancy for Static and Dynamic RAMs.

Because densely packed memory chips are so highly vulnerable to defects, the yield of RAM chips is crucial to the commercial success of their manufacture. Due to their regular structure, RAMs can be efficiently made fault tolerant through the addition of redundant (spare) bit lines and word lines. Once a fault in a RAM has been located, the RAM can usually be repaired by disconnecting some faulty bit line or word line (when they constitute replaceable units) and by connecting some spare bit line or word line.

The most widely used technique of memory repair is permanent switching: Here the repair is accomplished by using a laser beam or a large electric current to blow some permanent fuses which disconnect the faulty lines and which connect the spare lines. This kind of repair can be performed only by the manufacturer,

and the extra hardware needed for fault repair (i.e., fuses and special decoders) is separate from any extra hardware that may be added for self-testing purposes.

Another means of dealing with defects is to use the fault tolerance technique of *coding*: Here neither fault location nor repair are done explicitly, instead the faults are simply masked by redundancies in the stored-information.

A third technique, which has been largely ignored by commercial chip manufacturers, is called *soft switching*: Here the repair is accomplished by programming EEPROM cells (or some other non-volatile memory cells) that control multiplexers which can disconnect faulty lines and connect spare lines. The EEPROM cells are paired with flip-flops, as in commercially available *Shadow SRAMs*. When the chip is powered-up, the contents of the EEPROM cells are written into the flip-flops, thereby providing default configuration parameters. Whenever a new fault is discovered, the new configuration parameters are initially stored in the flip-flops, before the slow reprogramming (i.e. 5 to 10 milliseconds) of one or more EEPROM cells, in order to change the default setting.

# 2.5 The meaning of "embedded".

$f \setminus$

In order to enhance the speed performance of VLSI chips by reducing communication flow through the I/O pins, it is becoming increasingly common that logic circuits and memories are being fabricated on the same chip. When the data, address and control signals of RAMs cannot be directly controlled or observed through the I/O pins, such on-chip RAMs are called "embedded RAMs." These embedded RAMs cannot be properly tested by applying test patterns directly to the I/O pins, therefore self-testing methods must be used. Researchers have proposed self-testing embedded RAM designs using random test patterns and deterministic test patterns.

### 3.1 General Overview of Fault Models

The types of fault models that previous researchers (surveyed in [Abadir and Reghbati 83], [van de Goor and Verruijt 90], and chapters 2, 3, 10, and 11 of [van de Goor 91]) have considered when proposing fault detection and/or location algorithms, and that might be repairable given appropriate forms of redundancy, are consolidated and described in this chapter. Three broad classes of faults can be distinguished:

- \* Functional faults originate in permanent physical failures in the internal device structure of memories which will cause incorrect functional behavior. The detection and location of functional faults is accomplished by applying carefully chosen data patterns to memory cells in specific addressing sequences.

- \* Dynamic faults refer to failures that occur when the memory is operated at normal operational speed, but no failures occur when operated at significantly slower speeds. Such frequency dependent malfunctions originate mostly from timing inconsistencies internal to the memory circuits.

- \* Parametric faults are usually associated with voltage and current values that fall outside the expected margins. These faults refer to situations like:

output voltage being too high or too low, excessive power consumption, insufficient fanout capabilities, etc. The detection of parametric faults generally involves techniques and instruments that are highly dependent on the fabrication technology used to make the IC chip, therefore no self-test scheme for such faults is practical, and for this reason no further attention will be given to parametric faults.

Some dynamic tests can be combined with functional tests in the same self-test algorithm because the functional test patterns are applied at normal operational speed, and hence these test patterns will detect frequency dependant faults as well. The sections below enumerate a wide variety of functional faults, including as well those particular dynamic faults which can be detected without the use of external test equipment.

## 3.2 Functional Faults affecting Memory Cells

#### 3.2.1 SAF: stuck-at fault

The logical value of a "stuck-at" memory cell is always 0 or 1, and can never be changed to the opposite value. A test to locate all SAFs must satisfy the condition: from every cell, both a 0 and a 1 must be read.

#### 3.2.2 TF: transition fault

A memory cell fails to undergo either a  $0 \to 1$  or a  $1 \to 0$  "transition" when that same cell is being written-to; "transition faults" are not identical to "stuck-at faults", because the value stored in a TF cell may be changed occasionally when a different cell is being written-to, and a "pattern sensitive fault" exists between the different cell and the TF cell. Hence, a cell with an "up transition fault" is able to undergo a  $1 \to 0$  transition when 0 is being written to it, but cannot undergo a  $0 \to 1$  transition when 1 is being written to it, however there may exist a "pattern

```

Functional Faults affecting Memory Cells

SAF: stuck-at fault

2: TF: transition fault

3: CF: coupling fault

a: CF/Inv: inversion coupling fault, (\uparrow; \uparrow) or (\downarrow; \uparrow)

b: CF/Id: idempotent coupling fault, \langle \uparrow; 0 \rangle or \langle \uparrow; 1 \rangle or \langle \downarrow; 0 \rangle or \langle \downarrow; 1 \rangle

c: CF/Dyn: dynamic coupling fault in SRAMs,

\langle r0, w0; 0 \rangle or \langle r0, w0; 1 \rangle or \langle r1, w1; 0 \rangle or \langle r1, w1; 1 \rangle

d: CF/St: state coupling fault, (0;0) or (0;1) or (1;0) or (1;1)

e: BF: bridging fault

4: NPSF: neighborhood pattern sensitive fault

a: ANPSF: active neighborhood pattern sensitive fault

b: PNPSF: passive neighborhood pattern sensitive fault

c: SNPSF: static neighborhood pattern sensitive fault

Functional Faults affecting Addressing

1: AF/UuA: addressing fault — unused address

2: AF/UrC: addressing fault — unreachable cell

3: AF/MuA: addressing fault — multi-used address

4: AF/MrC: addressing fault — multi-reachable cell

5: SOAF: stuck-open addressing fault

C: Faults affecting the Read/Write Circuitry:

1: Stuck-open Access transistor

2: Stuck-open Precharge transistor

3: Stuck-open Equalization transistor

4: Stuck-open Sensing transistor

D: Line Faults

1: SAF: stuck-at bit line fault

2: BF: bridged lines fault

3: SOF: stuck-open line fault

4: CF: coupled bit line fault

```

Table 3.1 Summary of Functional Fault Models

sensitive fault" which can cause the  $0 \to 1$  transition. Similarly, a cell with a "down transition fault" is able to undergo a  $0 \to 1$  transition when 1 is being

E: Dynamic faults

1: RecF: recovery fault

a: RecF/SA: sense amplifier recovery fault

b: RecF/W: write recovery fault

2: RetF: retention fault

a: RetF/SS: sleeping sickness

b: RetF/RL: refresh line stuck-at fault

c: RetF/SDL: static data loss fault

3: IF: imbalance fault

4: SYNCF: synchronization fault

Table 3.2 Summary of Dynamic Fault Models

written to it, but cannot undergo a  $1 \to 0$  transition when 0 is being written to it, however some kind of "pattern sensitive fault" may be able to cause the  $1 \to 0$  transition. A test to locate all TFs must satisfy the condition: every cell must undergo a  $1 \to 0$  transition and a  $0 \to 1$  transition, and must be read immediately after each transition before undergoing any additional transitions.

#### 3.2.3 CF: coupling fault

A pair of memory cells (x, y) are involved in a "coupling fault" when a write operation that causes a transition in one cell x (known as the *coupling cell*), also causes an unintended transition in another cell y (known as the *coupled cell*). However, the reverse action: a write operation that causes a transition in cell y, does not necessarily cause an unintended transition in cell x (if it does cause such a transition in cell x, then this action constitutes a second coupling fault which is distinct from the first). In the case of Dynamic RAMs, some of the coupling fault models are based on certain assumptions:

a) A read operation will not cause an error, which is reasonable since read signals are usually very weak and are therefore unlikely to influence the contents of other cells. b) A non-transition write will not cause a fault, which is necessary to allow for read operations to be fault free; in DRAMs, a read operation is destructive, and must therefore be followed by a non-transition write operation to restore the original contents of the disturbed cells.

#### Coupling faults are classified as:

- 1) inversion coupling faults (CF/Inv)

- 2) idempotent coupling faults (CF/Id)

- 3) dynamic coupling faults in SRAMs (CF/Dyn)

- 4) state coupling faults (CF/St)

- 5) bridging faults (BF)

In what follows, we use the notation  $\uparrow$  to signify a transition write to 1 in a cell which originally contained a 0. Analogously, the notation  $\downarrow$  signifies a transition write to 0 in a cell which originally contained a 1. The notation  $\updownarrow$  signifies an inversion of the original value stored in a cell. The notation w0 signifies a write to 0 in a cell whose original content is unspecified (i.e. the operation can be either a transition write or a non-transition write). Similarly, the notation w1 signifies a write to 1 in a cell whose original value is unspecified.

# 3.2.3.1 CF/Inv: inversion coupling fault, $\langle \uparrow : \uparrow \rangle$ or $\langle \downarrow : \uparrow \rangle$

An inversion coupling fault implies that an \(\phi\) or \(\p\) transition write in one cell causes the contents of a second cell to always invert. A test to locate all CF/Inv coupled cells must satisfy the condition: each coupled cell must be read after an odd number of inversions in the coupled cell that were caused by transition writes in the coupling cells.

# 3.2.3.2 CF/ld: idempotent coupling fault, $\langle \uparrow; 0 \rangle$ or $\langle \uparrow; 1 \rangle$ or $\langle \downarrow; 0 \rangle$ or $\langle \downarrow; 1 \rangle$

An idempotent coupling fault implies that an  $\uparrow$  or  $\downarrow$  transition write in one cell causes the contents of a second cell to always take the same value, 0 or 1.

A test to locate all CF/ld coupled cells must satisfy the condition: each coupled cell must be read after the coupled cell has been forced to the same value an unspecified number of times (but before the coupled cell could be forced to the opposite value), by transition writes in the coupling cells.

3.2.3.3 CF/Dyn: dynamic coupling fault in SRAMs,

$$\langle r0|w0;0\rangle$$

or  $\langle r0|w0;1\rangle$  or  $\langle r1|w1;0\rangle$  or  $\langle r1|w1;1\rangle$

A dynamic coupling fault can be viewed as a generalization of the idempotent coupling fault. A dynamic coupling fault implies that a read operation of value x, or a non-transition write of x, or a transition write to x, may each cause the contents of a second cell to always take the same value, 0 or 1. A test to locate all CF/Dyn coupled cells must satisfy the condition: each coupled cell must be read after the coupled cell has been forced to the same value an unspecified number of times (but before the coupled cell could be forced to the opposite value), by any types of read and write operations in the coupling cells.

# 3.2.3.4 CF/St: state coupling fault, (0;0) or (0;1) or (1;0) or (1;1)

A state coupling fault implies that if the coupling cell x contains a certain value, then the coupled cell y is forced to a particular value. At first glance, it would appear that state coupling faults are identical to dynamic coupling faults, but there is a clear distinction between them. State coupling faults can only occur between cells in the same word line, since all read and write operations take place concurrently among such cells. Dynamic coupling faults can only occur between cells in different word lines, since all read and write operations take place at different times. A test to locate all state coupled cells must satisfy the condition: each pair of state coupled cells (x,y) must be written to, in such a way that all four logical states are supposed to occur, namely (0,0), (0,1), (1,0) and (1,1).

# 3.2.3.5 BF: bridging fault

A set of memory cells (x, y, z, ...) are involved in a "bridging fault" when the

cells have a single combined value which is either the logical AND or the logical OR of the values x, y, z, etc. A test to locate all bridged cells must satisfy the condition: each possible pairing of bridged cells (x,y) must be written to, in such a way that all four logical states are supposed to occur, namely (0,0), (0,1), (1,0) and (1,1). BFs are usually caused by short circuits between cells or lines.

# 3.2.4 NPSF: neighborhood pattern sensitive fault

The "neighborhood pattern sensitive fault" class is defined as follows: the value, or the ability to change the value, of a base cell, is influenced by the values of, or changes to the values of, a specific group of cells (known as the neighborhood). The set of values of the specific group of cells is called the neighborhood pattern. The two most common neighborhoods are known, somewhat arbitrarily, as Type-1 and Type-2:

Type-1: this neighborhood consists of the four "closest" cells to the base cell, namely the cells just above, just to the right, just below, and just to the left, of the base cell. Base cells along an edge of the cell array actually have only three physically adjacent neighbors, but in the interests of symmetry, such a base cell is deemed to have a fourth "adjacent" neighbor, which is the corresponding cell along the opposite edge of the array. Base cells at the corners of the cell array have only two physically adjacent neighbors, and they are deemed to have two more "adjacent" neighbors, which are in fact the horizontally opposite and vertically opposite corner cells (the remaining diagonally opposite corner cell is not in the neighborhood).

Type-2: this neighborhood consists of the eight "closest" cells to the base cell, namely the cells of the Type-1 neighborhood plus the four diagonally closest cells to the base cell. Hence, the eight cells of the neighborhood plus the base cell form a 3 × 3 square with the base cell as the center. Analogous to Type-1 neighborhoods, the base cells along an edge of the cell array have deemed "adjacent" neighbors along the opposite edges of the array.

The neighborhood pattern sensitive fault class is only used with reference to dynamic RAMs, and never with reference to static RAMs, because NPSFs model the effects of undesirable charge leakages between the capacitances in single-transistor dynamic RAM cells. NPSFs do not model any faulty behavior known to exist in static RAMs.

# 3.2.4.1 ANPSF: active neighborhood pattern sensitive fault

An active neighborhood pattern sensitive fault exists when: the base cell changes its value, in response to changes in the neighborhood pattern. A test to locate ANPSFs must satisfy this condition: every base cell must be read in state 0 and state 1, for all possible changes in the neighborhood pattern.

#### 3.2.4.2 PNPSF: passive neighborhood pattern sensitive fault

A passive neighborhood pattern sensitive fault exists when: the base cell is forced to retain a specific value, in response to a certain neighborhood pattern. A test to locate PNPSFs must satisfy this condition: every base cell must be written and read in state 0, and written and read in state 1, for all permutations of the neighborhood pattern.

# 3.2.4.3 SNPSF: static neighborhood pattern sensitive fault

A static neighborhood pattern sensitive fault exists when: the base cell *changes* to a specific value, in response to a *certain* neighborhood pattern. A test to locate SNPSFs must satisfy this condition: every base cell must be read in state 0 and state 1, for all permutations of the neighborhood pattern.

C

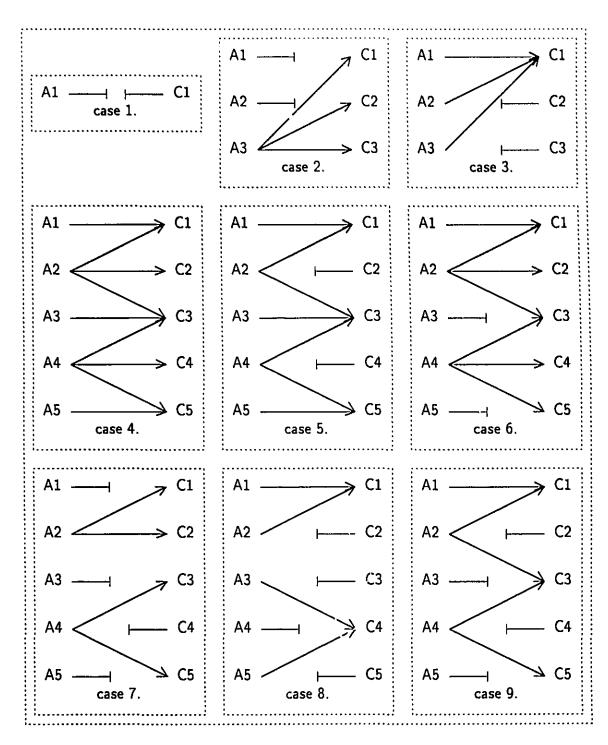

Fig. 3.1 Examples showing the Nine Combinations of Addressing Faults

# 3.3 Functional Faults affecting Addressing

These faults refer to physical failures in the row and column address decoders and in the address latch. Without loss of generality, only memories with one-bit words (B=1) will be discussed in this section. There are four types of non-sequential "addressing faults":

# 3.3.1 AF/UuA: addressing fault — unused address

The "unused address" fault occurs when a given address is unable to access any cell at all. This looks like a shortage of one cell with respect to the number of addresses. When a read operation is performed at an "unused address", the response is technology dependant; in some cases, the response will consistently appear to be a logical 1 or a logical 0, but in other cases, the response may be completely unpredictable and may depend on neighboring leakage currents and other noise in the memory.

# 3.3.2 AF/UrC: addressing fault — unreachable cell

The "unreachable cell" fault occurs when there is no address which can reach a given cell. This given cell is never accessed. This looks like a surplus of one cell with respect to the number of addresses.

# 3.3.3 AF/MuA: addressing fault — multiused address

The "multiused address" fault occurs when a given address accesses two or more cells simultaneously. This looks like a surplus of cells with respect to the number of addresses. When a read operation is performed at a "multiused address", the response is technology dependant; in some cases, the response will consistently appear to be the logical AND or the logical OR of the cells actually accessed, but in other cases, the response may be completely unpredictable function of the accessed cells.

٠.,

#### 3.3.4 AF/MrC: addressing fault — multireachable cell

The "multireachable cell" fault occurs when two or more different addresses can access the same cell. This looks like a shortage of cells with respect to the number of addresses. Since write operations are performed on a "multireachable cell" using one or more illegal addresses, in addition to the single legal address, it is required that any test to locate such faults must read from the cell before any writing using the legal address can mask out the effect of writing from an illegal address.

#### 3.3.5 Combinations of addressing faults

Because there are exactly as many addresses as there are cells, none of these faults can exist in isolation. The only possible combinations must balance the apparent shortage of cells caused by faults UuA and MrC, with the apparent surplus of cells caused by faults UrC and MuA. The following nine cases list all possible combinations, and examples illustrating these cases are presented in figure 3.1.

- 1: UuA, with UrC.

- 2: UuA, with MuA.

- 3: MrC, with UrC.

- 4: MrC, with MuA.

- 5: MrC, with a combination of UrC and MuA.

- 6: a combination of UuA and MrC, with MuA.

- 7: UuA, with a combination of UrC and MuA.

- 8: a combination of UuA and MrC, with UrC.

- 9: a combination of UuA and MrC, with a combination of UrC and MuA.

Those combinations which contain one or more MrCs (namely: 3, 4, 5, 6, 8 and 9) are susceptible to fault masking when a legally addressed write operation on a "multireachable cell" overwrites the faulty contents that resulted from an earlier, illegally addressed write operation on the same cell. Cases 6, 8 and 9 are further complicated by the possibility that a given "multireachable cell" may have only illegal addresses, when its sole legal address is subject to an "unused address" fault.

#### 3.3.6 SOAF: stuck-open addressing fault

The above discussion of different addressing fault types is incomplete because it assumes that the address decoder circuits cannot be transformed into sequential logic by some physical defect. However, a "stuck-open fault" in one of the transistors can change the decoder into a sequential circuit (i.e., a circuit with some kind of memory capability). This type of fault is common in address decoders built out of CMOS technology. CMOS "fully complementary logic" gates are a combination of a pull-up network made from pMOS transistors, and a pull-down network made from nMOS transistors. In a CMOS complementary logic gate, exactly one of the two networks is always conducting, while the other is not conducting.

A single transistor is said to be stuck-open when it cannot conduct because of an open gate, open source or open drain connection. An entire CMOS logic gate is said to be stuck-open when either its pull-up or its pull-down network is prevented from conducting due to one or more stuck-open transistors in that network, while the remaining network is in a legally non-conductive state. As a consequence of neither network being able to conduct, the output line is not driven to 0 or 1, but takes on a high impedance state. The output level will therefore be determined by the charge stored by the capacitance of the output line, which implies that when the input signals change and the logic gate becomes "stuck-open", then the

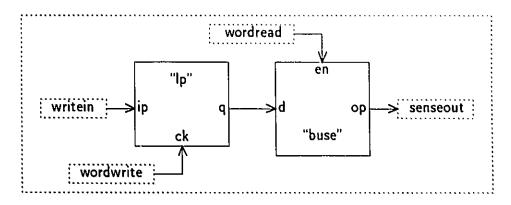

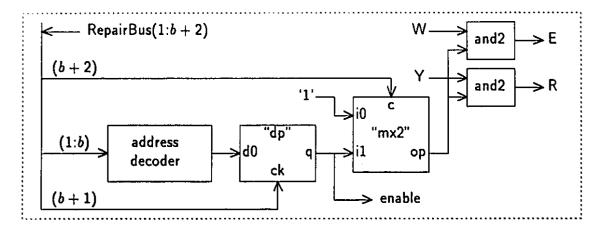

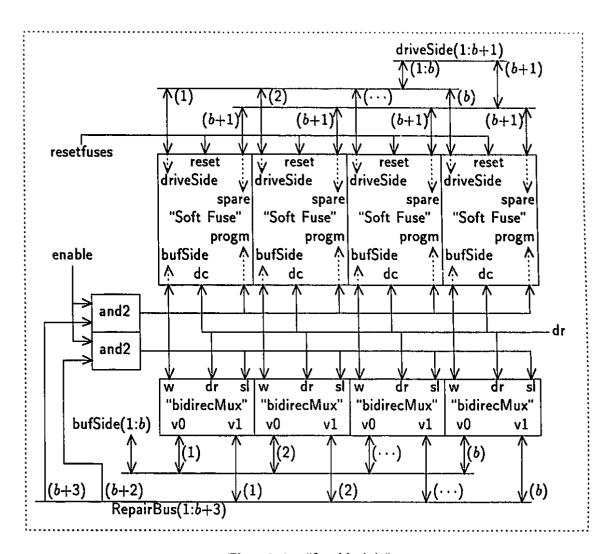

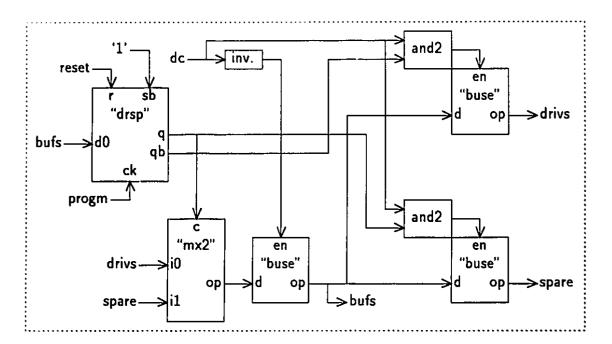

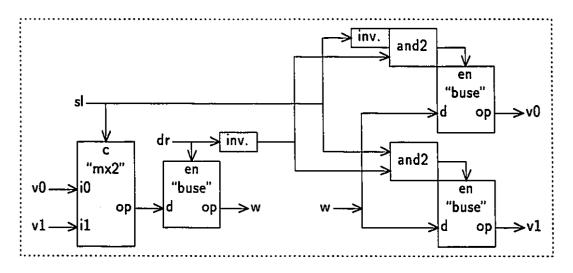

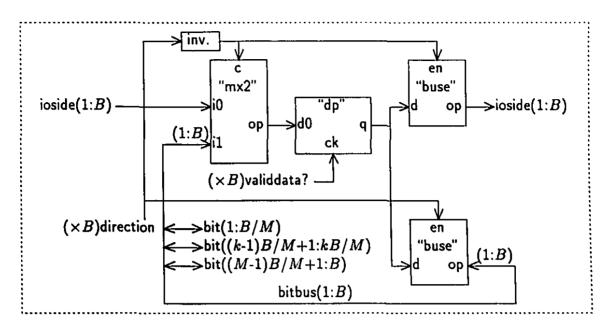

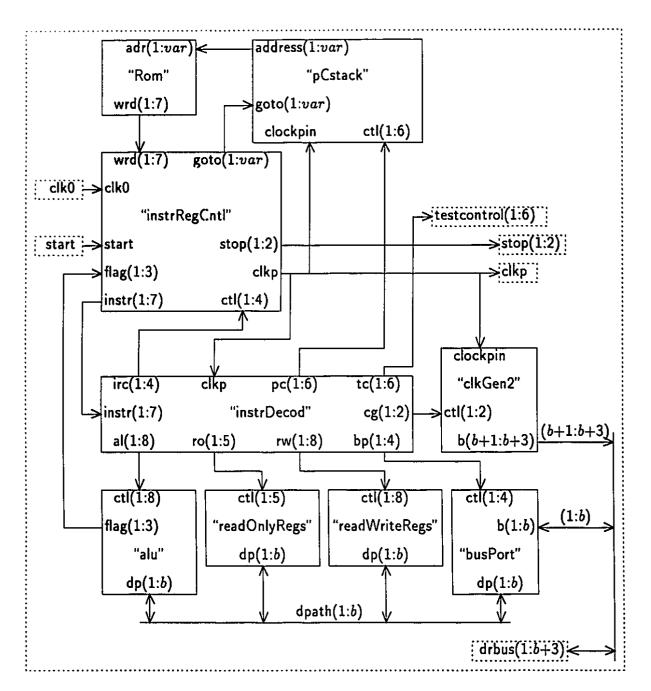

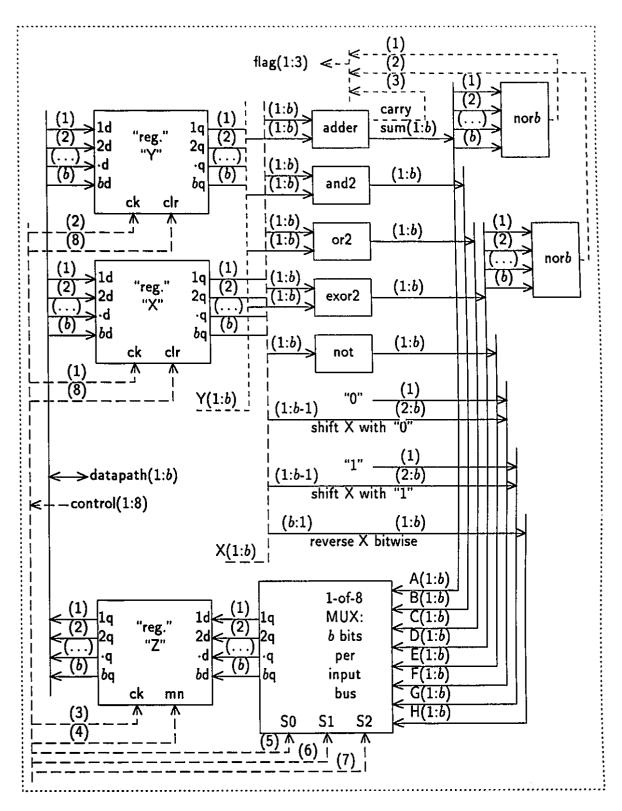

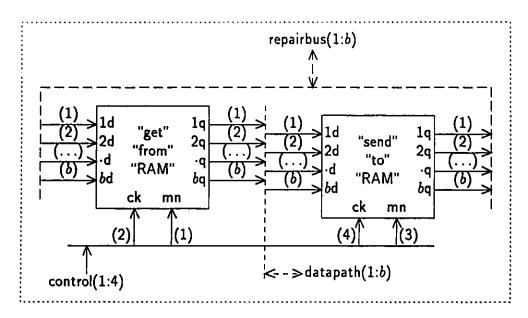

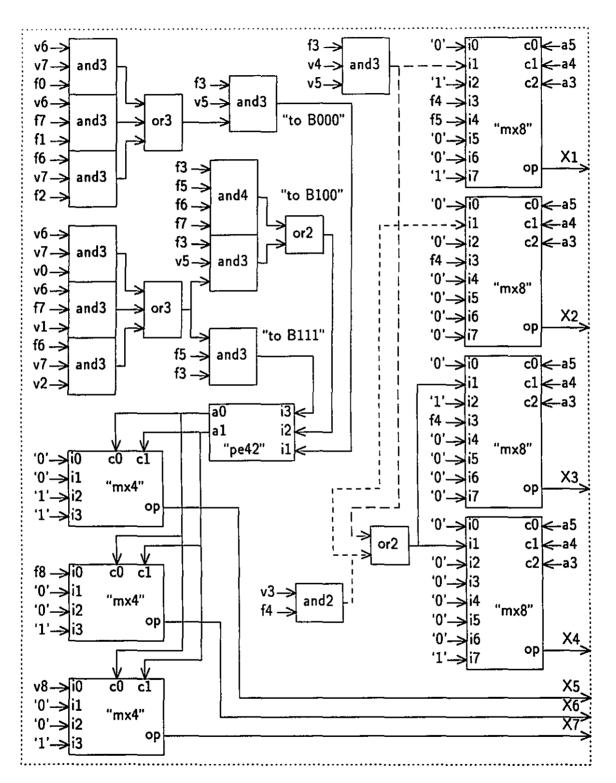

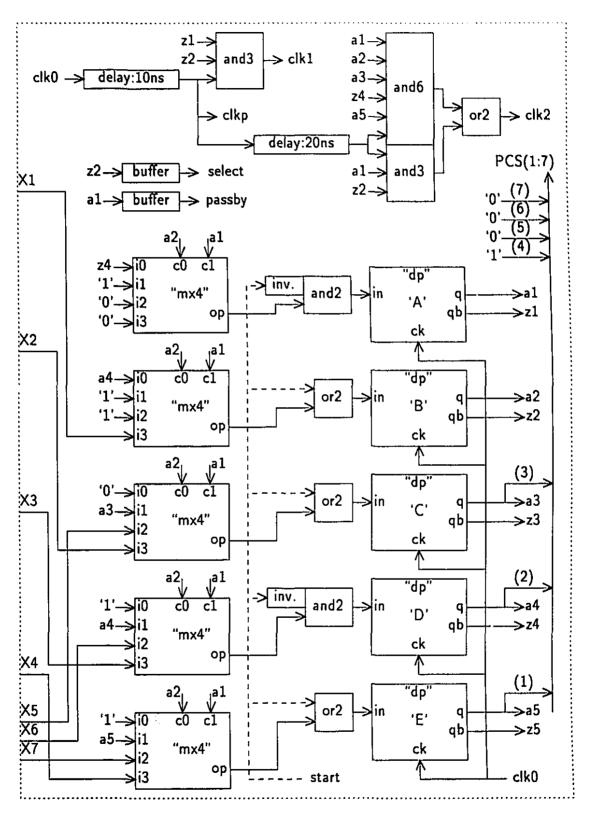

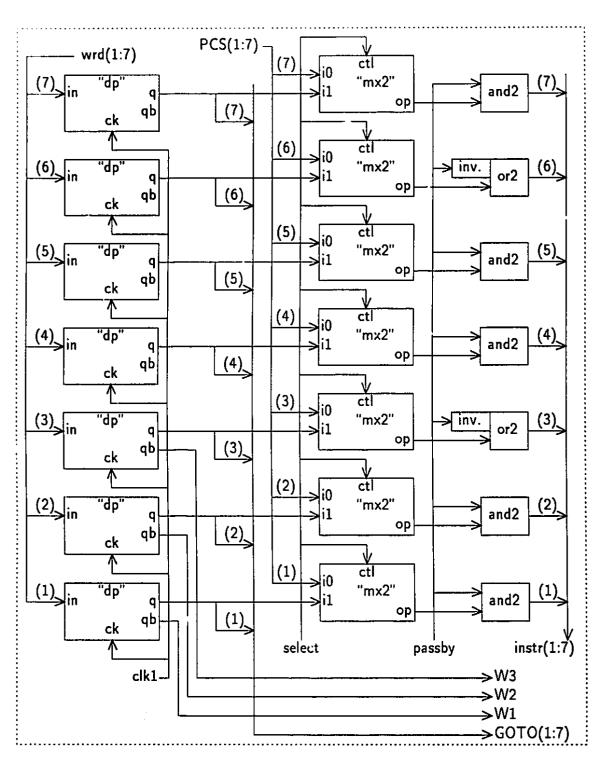

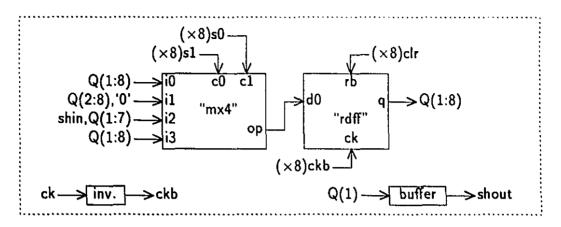

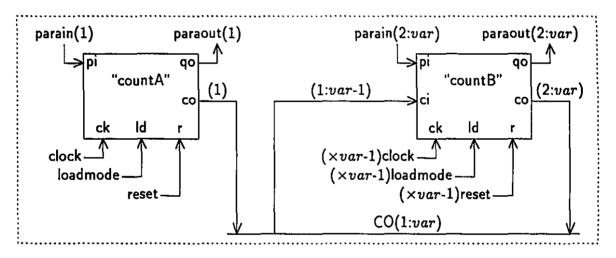

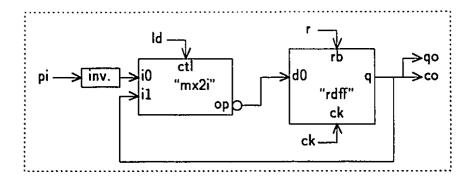

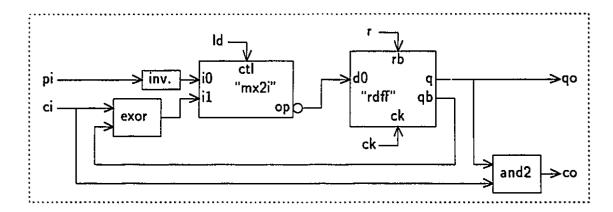

output retains its *previous* logic value, regardless of which output value the new input signals are supposed to elicit.