# Calibration System for Electronic Instrument Transformers With Digital Output

Branislav Djokić, Senior Member, IEEE, and Eddy So, Fellow, IEEE

Abstract—A high-accuracy system for calibration of electronic instrument transformers with digital output is described. Its design is based on International Electrotechnical Commission (IEC) standards 61850, 60044-8, and 60044-7. The performance of the calibration system has been evaluated. Its estimated relative uncertainty  $(2\sigma)$  is within  $40 \cdot 10^{-6}$  in magnitude and within 40  $\mu$ rad in phase.

*Index Terms*—Calibration system, digital output, electrical current transducers (ECTs), electronic voltage transducers (EVTs), instrument transformers, optical instrument transformers.

#### I. INTRODUCTION

E LECTRICAL/ELECTRONIC current and voltage trans-formers/transducers (ECTs and EVTs, respectively) can be based on optical principles (e.g., Faraday's and Pockel's effect, respectively) usually equipped with electrical components, on air core coils, on iron core coils, with electrical and/or electronic components (shunts, capacitors and active circuitry). They are used for measurement or for protective purposes and are provided with analog and digital outputs. Optical instrument transformers have been in use on a limited base for about two decades, and they have been calibrated occasionally. However, the optical instrument transformers with digital output have not been deployed yet on a larger scale. Consequently, calibration laboratories have an interest in getting prepared for calibration of those new transformers with digital output [1], [2]. This task of getting ready is not quite straightforward due to a lack of the relevant technical information from the manufacturers as to the specifics of how the digital data will be made available. It is therefore necessary to rely mostly on information provided in IEC standards on electronic current and voltage transducers [3], [4], International Electrotechnical Commission (IEC) standard 61850 [5], [6], and standard 8802-3 [7]. The Power Systems Instrumentation and Measurement Committee (PSIM) of the IEEE Power Engineering Society (PES) has sponsored a working group to develop the Standard for Optical Current and Voltage Sensing Systems, which is intended to address digital interface to measurement and protection equipment [8].

Depending on the transducer type, the sensor produces a quantity proportional to either current or voltage at its input. A secondary converter (SC) transmits this quantity to a merging unit (MU), which has a digital output and supplies substation measurement and protective equipment with time-coherent

sets of current and voltage data. As specified in [5], a communications link between SC and MU may be proprietary. The merging unit can be connected to up to seven ECTs (three measuring, three protective, and one for neutral) and up to five EVTs (three measuring/protective, one for bus-bar, and one for neutral). A communications link between the MU and the substation measurement and protective equipment is specified [5], [6] to be Ethernet [7].

The purpose of instrument transformer calibration is to obtain information about the amplitude ratios and phase deviations of an instrument transformer output signal with respect to its input signal at specified measurement conditions. One of the possible approaches is to convert the transformer digital output into an analog signal and proceed with the calibration by means of analog calibration methods.

It is also possible to transform the analog output of the reference measurement system into the digital domain and perform the comparison with the transformer digital output data by means of digital signal processing techniques, such as discrete Fourier transform/fast Fourier transform (DFT/FFT) or digital filtering [9]. This paper describes a new measurement system that can be used for calibrating instrument transformers with digital output in the digital domain under various measurement conditions.

## **II. PRINCIPLE OF OPERATION**

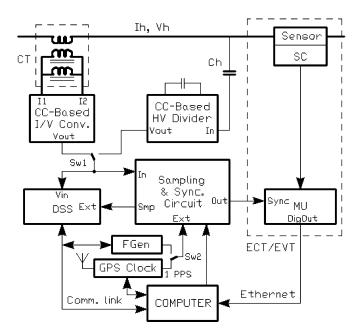

A block diagram of the calibration system for electronic transformers/transducers with digital output is shown in Fig. 1. The electronic transformer/transducer, either an ECT or EVT, is represented by a sensor, SC, MU, and a link between the SC and MU. The calibration system consists of a high-accuracy two-stage current transformer (CT) and current comparator (CC)-based I/V converter [10] or a CC-based high-voltage (HV) divider [11] with an HV gas-dielectric capacitor  $C_h$ , a high-accuracy digital sampling system (DSS), sampling and synchronizing circuitry (SSC), and a computer.

A switch  $S_{w1}$  represents symbolically a selection of either ECT or EVT for calibration. For calibration of an ECT, its primary current  $I_h$  is converted into a voltage  $V_{out}$  by means of the high-accuracy two-stage CT and the CC-based I/V converter. For a calibration of an EVT, its primary voltage  $V_h$  is converted into a low-voltage  $V_{out}$  by means of the CC-based HV divider with the HV gas capacitor  $C_h$ . The conversion of input high current  $I_h$  or high voltage  $V_h$  into its low-voltage replica  $V_{out}$  is performed with a low uncertainty that does not affect substantially the overall calibration uncertainty budget.

The voltage  $V_{out}$  is sampled by the digital sampling system based on a high-accuracy sampling analong-to-digital (A/D)

Manuscript received July 2, 2004; revised November 1, 2004.

The authors are with the Institute for National Measurement Standards, Na-

tional Research Council of Canada, Ottawa, ON K1A 0R6, Canada.

Digital Object Identifier 10.1109/TIM.2004.843420

Fig. 1. Block diagram of the calibration system.

converter. The computer implements all of the control and communications functions as well as the algorithm for error calculation (DFT or digital filtering). Software had to be developed to accommodate the requirements of ECT/EVT calibration. Thus, in addition to communication interfaces, it had to allow specification of the ECT/EVT parameters, such as nominal primary and secondary currents/voltages, HV capacitor values, settings of HV dividers, and I/V converters.

The role of the SSC is to provide the sampling signal as well as synchronization for the DSS. As defined in [5], the sampling rate  $f_s$  can be 10, 12, 16, 20, 40, 48, 80, 200 or 400 times the rated power frequency  $f_r$ . Thus, for the power frequency of 60 Hz, the highest sampling rate is 24 kHz. The sampling circuitry has been implemented so that it can handle all of the above sampling rates. It has also been implemented with multiple options for providing the sampling signal, by means of a fixed-frequency oscillator (FFO), a phase-locked loop (PLL), a programmable frequency divider (PFD), or an external sampling signal.

The FFO consists of an oscillator, a programmable divider to ensure variable sampling rate  $f_s$ , and a one-shot circuit to ensure needed polarity and sampling pulse duration. Since the least common multiple of the specified sampling rate multiplication factors is 1200, the oscillator frequency  $f_o$  has to be a multiple of  $f_{0 \min} = 1200 \cdot f_r$ , which, divided by an appropriately chosen integer division ratio, can provide any of the aforementioned sampling rates. Sampling based on the fixed-frequency oscillator assumes that  $f_r$  is known in advance and constant.

In order to provide specified sampling rates with the PLL, the input signal frequency is first multiplied by a multiple of 1200, producing a frequency  $f_o$ . This frequency  $f_o$  is then divided by an appropriately chosen integer division ratio to give any of the specified sampling rates. In this way, PLL parameters do not have to be changed when the sampling rate is changed. Sampling based on PLL assumes that the  $f_r$  nominal value is known in advance.

The PFD provides frequency multiplication by N without phase locking and requires 2 programmable dividers (by N and by M) and an oscillator of frequency  $f_o$ . Input signal period  $1/f_{in}$  is measured with the clock  $f_o/N$  by a counter enabled during one input signal period and latching the result (M) into a register. The oscillator frequency  $f_o$  divided by M represents the sampling signal  $f_s$  whose frequency is N times the input signal frequency  $f_{in}$ . The advantage of using PFD is that it has much wider operating range than PLL without stability problems related to PLL operation, while its disadvantage is the appearance of a truncation error when the input signal frequency deviates from its nominal value.

The SSC can also accommodate an external sampling signal for the DSS, such as a signal from a function or pulse generator, which can be controlled by a computer over an interface (e.g. IEEE 488 bus).

One of the most important issues is the synchronization between the DSS and the ECT/EVT under test so that the time-coherent data sets are obtained. From the data sets with known timing relationship, magnitude and phase errors of the ECT/EVT under test can be determined. In addition to achieving the specified sampling rate by FFO, PLL or PFD, the SSC provides synchronization of the sampling pulses within one period  $T_0 = 1/f_0$  with respect to the synchronization signal. The synchronization is performed periodically, e.g. on a command coming from the computer, or once a second (1 pulse/s) as required in [3]. One pulse per second can be generated by a commercial or custom-built clock generator under computer control.

For measurement and protection, a common time base at the substation level, or even at the power system level, is important to ensure that time-coherent data sets originate from all ECTs and EVTs available in the area of interest. A global positioning system (GPS) satellite-controlled clock can be used for that purpose. For calibration purposes, it is essential to provide time-coherent data sets from the MU and the DSS. The MU supplies a 2-B sample counter value in every universal data set [3]. With a synchronization once a second, the maximum number of samples in that interval is  $400 \cdot f_r$ , or 24 000 at  $f_r = 60$  Hz, which is less than  $2^{16} - 1$ , enough to uniquely identify samples.

## **III. PERFORMANCE EVALUATION**

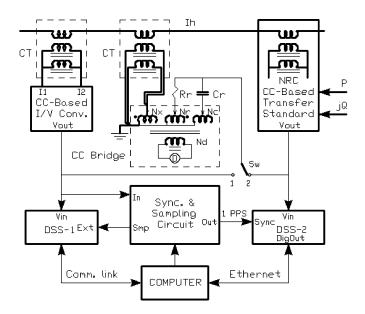

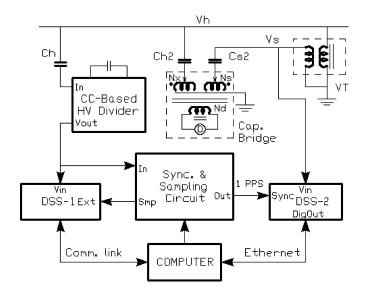

To evaluate the performance of the system for calibration of electronic instrument transformers with digital output, an ECT or EVT with digital output was needed. Since no commercial ECT or EVT with digital output was available for testing/calibration, a unit was designed at NRC according to the IEC requirements. It is based on a two-stage CT and transimpedance amplifier, or conventional inductive voltage transformer (VT), as shown in Figs. 2 and 3, respectively. It is equipped with a high-accuracy sampling A/D converter, an embedded microcomputer, and Ethernet interface, depicted together as DSS-2 in Figs. 2 and 3. It allowed validation of possible calibration scenarios with various synchronization options.

The ECT calibration system performance was evaluated as shown in Fig. 2 using a CC-based transimpedance amplifier (transfer standard) that was modified to introduce at its output a known and adjustable in-phase (P) error of up to 1% and/or a quadrature (Q) error of up to  $\pm 0.3\%$  [12].

Fig. 2. Block diagram of the test setup for verification of the ECT calibration system.

Fig. 3. Block diagram of the test setup for verification of the EVT calibration system.

The EVT calibration system performance was evaluated as shown in Fig. 3, using an inductive voltage transformer 6600 V/110 V, from no-load to the full-burden conditions, at different primary voltages and different power factors. VT accuracy was not essential for the measurement and was useful only for providing repeatable calibration points during the evaluation. DSS-1 was used in conjunction with a high-voltage divider to provide a low-voltage replica of the primary high voltage.

The differences in measurement results obtained by the digital sampling and those obtained by either the current comparator bridge with a reference resistor  $R_r$  and reference capacitor  $C_r$ , or the current-comparator-based capacitance bridge, were less than  $35 \cdot 10^{-6}$  for magnitude and 30  $\mu$ rad

TABLE ISources of Uncertainty

| Sources of Uncertainty       |                               |              |

|------------------------------|-------------------------------|--------------|

| Component                    | Magnitude [10 <sup>-6</sup> ] | Phase [µrad] |

| Two-Stage CT or HV Capacitor | 2 or 10                       | 10           |

| I/V Converter or HV Divider  | 10                            | 10           |

| Digital Sampling System      | 35                            | 30           |

| Synchronization              | 0                             | 20.5         |

| Root-Sum-of-Squares          | 36.5 or 37.8                  | 39.0         |

|                              |                               |              |

for phase. When the capacitance bridge was used to calibrate the ratio and phase directly between the two voltages that are sampled, the differences were within  $15 \cdot 10^{-6}$  and  $15 \mu$ rad.

If an external sampling signal is used for both the calibration system and the ECT/EVT under test, the data samples are supposed to be taken simultaneously. However, if the propagation delays of the sampling signal along its paths to the two sampling devices are different, they will create an equivalent phase shift. This phase shift can be accounted for as an offset. The synchronization of the sampling pulses by means of FFO, PLL, or PFD introduces an uncertainty of one period  $T_0 = 1/f_0$  with respect to the synchronizing signal and cannot be accounted for as an offset. Therefore,  $f_0$  has to be sufficiently high to keep the synchronization uncertainty low. At  $f_r = 60$  Hz, setting  $f_0$  to  $2^8 \cdot f_{0 \min} = 18.432$  MHz, a frequency that can still be easily managed by common electronic components such as oscillators, counters, and PLL circuits, will introduce phase uncertainty of less than 20.5  $\mu$ rad. If necessary, the synchronization uncertainty can be further reduced by increasing  $f_0$ .

The sources of uncertainty are summarized in Table I.

Presently, the most stringent accuracy class defined in [13] is 0.3%. Assuming that a calibration system should have, preferably, at least ten times smaller uncertainties than those for accuracy class 0.1% [3] requires the uncertainties to be less than  $100 \cdot 10^{-6}$  for magnitude and less than  $145.4 \,\mu$ rad for phase. The new calibration system has estimated uncertainties over two and a half times better than these requirements.

#### IV. CONCLUSION

A high-accuracy system for calibration of electrical/electronic instrumentation transformers/transducers with digital output has been described. It has been shown that a point-to-point connection, as described in [5], between a merging unit and a calibration system is sufficient for calibrating an ECT/EVT with digital output. The calibration system has been built based on IEC Standards 61850, 60044-8, and 60044-7, and its performance evaluated. It is estimated that its relative uncertainty  $(2\sigma)$  in magnitude is within  $40 \cdot 10^{-6}$  and in phase is within  $40 \ \mu$ rad. Such a system would also allow a possibility of doing on-site calibrations.

#### ACKNOWLEDGMENT

The authors would like to thank D. Bennett of the National Research Council of Canada for his assistance in testing of the prototype.

# REFERENCES

- E. So, R. Arseneau, and D. Bennett, "A current-comparator-based system for calibration of optical instrument transformers with analog and digital outputs," in *Dig. CPEM 2002*, Ottawa, ON, Canada, Jun. 2002, Dig. No. 02CH37279, p. 252.

- [2] J. I. Juvik, "Influence of time delay in calibration systems for instrument transformers with digital output," in *Dig. CPEM 2000*, Sydney, Australia, Jun. 2000, pp. 359–360.

- [3] Instrument Transformers—Part 8: Electrical Current Transducers, Draft of IEC 60044-8, TC38WG27, 2000.

- [4] Instrument Transformers—Part 7: Electronic Voltage Transformers, IEC 60 044-7, 1999.

- [5] Communication Networks and Systems in Substations, Part 9-1: Specific Communication Service Mapping (SCSM)—Sampled Analogue Values Over Serial Unidirectional Multidrop Point to Point Link, Draft of IEC 61850-9-1, TC38WG27, 2003.

- [6] Communication Networks and Systems in Substations, Part 9-2: Specific Communication Service Mapping (SCSM)—ACSI Mapping on an IEEE 802-3 Based Process Bus, Draft of IEC 61850-9-2, TC38WG27, 2000.

- [7] Information Technology—Telecommunications and Information Exchange Between Systems—Local and Metropolitan Area Networks—Specific Requirements—Part 3: Carrier Sense Multiple Access With Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications, ISO/IEC 8802-3, 2001.

- [8] PAR P1601 Standard for Optical A.C. Current and Voltage Sensing Systems, IEEE PES PSIM/Transformer Working Group, Dec. 2001.

- [9] B. Djokić and E. So, "Phase measurement of distorted periodic signals based on nonsynchronous digital filtering," *IEEE Trans. Instrum. Meas.*, vol. IM-50, no. 4, pp. 864–867, Aug. 2001.

- [10] E. So, "The application of the current comparator technique in instrumentation and measurement equipment for the calibration of nonconventional instrument transformers with non standard rated outputs," *IEEE Trans. Power Del.*, vol. 7, no. 1, pp. 46–52, Jan. 1992.

- [11] —, "The application of the current comparator in instrumentation for high voltage power measurement at very low power factors," *IEEE Trans. Power Del.*, vol. PWRD-1, no. 1, pp. 98–104, Jan. 1986.

- [12] E. So, R. Arseneau, D. Bennett, T. L. Nelson, and B. C. Waltrip, "NRC-NIST intercomparison of calibration systems for current transducers with a voltage output at power frequencies," *IEEE Trans. Instrum. Meas.*, vol. IM-52, no. 2, pp. 424–428, Apr. 2003.

- [13] IEEE Standard Requirements for Instrument Transformers, IEEE Standard C57.13, 1993.