Received February 21, 2021, accepted March 5, 2021, date of publication March 9, 2021, date of current version March 17, 2021. *Digital Object Identifier* 10.1109/ACCESS.2021.3064859

# Capacitor Lifetime Extension in a Hybrid Active Neutral-Point-Clamped Inverter With Reduction of DC-Link Ripple Current and Common-Mode Voltage

# SANG-WON AN<sup>®1</sup>, (Graduate Student Member, IEEE), SEOK-MIN KIM<sup>®2</sup>, (Member, IEEE), AND KYO-BEUM LEE<sup>®1</sup>, (Senior Member, IEEE)

AND KYO-BEUM LEE<sup>1</sup>, (Senior Member, IEEE) <sup>1</sup>Department of Electrical and Computer Engineering, Ajou University, Suwon 16499, South Korea <sup>2</sup>Power Solution Business Group, LS Electric Company Ltd., Anyang 14118, South Korea

Corresponding author: Kyo-Beum Lee (kyl@ajou.ac.kr)

This work was supported in part by the Korea Electric Power Corporation under Grant R19X001-20, and in part by the Korea Institute of Energy Technology Evaluation and Planning (KETEP) and the Ministry of Trade, Industry, and Energy (MOTIE) of the Republic of Korea under Grant 20206910100160.

**ABSTRACT** This paper proposes a reduction method for DC-link ripple current and common-mode voltage (CMV) in a hybrid active neutral-point-clamped (ANPC) inverter. A Si and SiC hybrid ANPC inverter has been developed recently to overcome the extremely high cost of a full-SiC ANPC inverter. A hybrid ANPC requires much fewer SiC MOSFETs than a full-SiC ANPC inverter while providing a comparable power density. Voltage source inverters such as hybrid ANPC inverters utilize electrolytic capacitors, which have a large capacitance per volume, as a DC link. However, an electrolytic capacitor is one of the most vulnerable components in a power electronic converter due to its small allowable ripple current. A large ripple current flowing into the electrolytic capacitor generates a heat loss, which shortens the lifetime of the capacitor. Furthermore, the common-mode voltage (CMV) causes an undesirable leakage current and electromagnetic interference. The CMV depends on the pulse-width modulation of the voltage source inverters. The proposed method enhances the reliability of the hybrid ANPC inverter by reducing the DC-link ripple current and CMV simultaneously. The effectiveness and validity of the proposed method are verified through simulations and experimental results.

**INDEX TERMS** Capacitor, common-mode voltage, neutral point ripple current, hybrid ANPC inverter, space vector modulation.

# I. INTRODUCTION

Multilevel inverters are suitable for high-power and medium-voltage renewable energy generation systems because of their small filter size, gradual dv/dt, and outstanding harmonic characteristics [1]–[3]. A three-level neutralpoint-clamped (NPC) inverter is one of the most widely used multilevel inverters [4], [5]. However, it has the disadvantage of an unbalanced distribution of losses between the switching devices. The unbalanced loss causes a temperature imbalance between the switching devices, which results in different lifetimes of the switches [6]. To overcome this drawback,

The associate editor coordinating the review of this manuscript and approving it for publication was Pinjia Zhang<sup>(D)</sup>.

an active NPC (ANPC) inverter topology, which replaces the clamping diodes of the NPC inverter with a Si IGBT, and its pulse-width modulation (PWM) strategies have been developed [7]–[9]. In addition, a study for full SiC-based ANPC inverter was conducted to maximize its power density and efficiency [10]. As SiC devices have low switching loss, a SiC-based inverter can be driven with high switching frequency, thereby reducing the filter size of the output stage. However, SiC devices are several times more expensive than Si devices. Thus, a Si and SiC hybrid ANPC inverter has been proposed in [11] to alleviate this problem. Although the Si and SiC hybrid ANPC inverter requires only two SiC devices per leg, it has a switching loss similar to that of a full-SiC ANPC inverter.

A hybrid ANPC inverter utilizes electrolytic capacitors as the DC-link to stabilize the DC-link voltage. Electrolytic capacitors have a short lifetime due to the wear out caused by the electrolyte evaporation and electrochemical reaction [12]. The electrolyte evaporation and electrochemical reaction depend on the hot-spot temperature of the capacitor, which varies with the loss caused by its equivalent series resistance (ESR). As the loss caused by the ESR varies with the root mean square (RMS) value of the ripple current flowing to the capacitor, the reliability of the capacitor can be improved by reducing the ripple current of the capacitor [13]. Some studies have attempted to reduce the DC-link ripple current. In [14], [15], methods for reducing the DC-link ripple current in a two-level back-to-back converter were proposed. These methods were implemented by changing the offset voltage for the discontinuous PWM or shifting the carrier. However, they are applied to a back-to-back converter. A switching method for reducing the DC-link ripple current of a three-level inverter was proposed in [16]. Although the proposed switching method could reduce both the DC-link ripple current and common-mode voltage (CMV), the performance for the reduction of the DC-link ripple current was insufficient.

CMV is generated in a PWM inverter such as a hybrid ANPC inverter. It is a major area of interest in motor drive applications and photovoltaic (PV) inverters. It is well known that bearing currents, shaft voltage, electromagnetic interference (EMI), and leakage current are induced by CMV [17]. In addition, as the CMV issue is exacerbated with the increase in switching frequency, it must be addressed in hybrid ANPC inverters operating at a high switching frequency [18]. The two types of solutions to cope with CMV are hardware and software solutions. In [19]-[21], strategies for CMV reduction using an active or passive filter were studied. Although these hardware solutions have demonstrated an outstanding CMV reduction performance, they require additional devices. Hence, software solutions based on PWM were proposed in [22]-[27]. [22] proposed a new CMV reduction method suitable for Quasi Z-source three-level inverter. This method modified large-medium-zero vector modulation (LMZVM) for quasi Z-source three-level inverter by applying the additional shoot-through voltage vector. An improved space vector modulation (SVM) is proposed in [23] to reduce CMV and compensate the neutral point (NP) AC and DC unbalance for the three-level inverters. Its CMV and NP balancing control is performed by calculating and applying a suitable small vector duty cycle to LMZVM. In [24] and [25], a double modulation wave CBPWM strategy and virtual SVPWM was proposed to reduce CMV for three-level inverter. Although these strategies reduce NP AC voltage ripple and CMV effectively, the number of switching of power semiconductors increases when performing pulse width modulation (PWM). In [26], hybrid modulation method of LMZVM and largemedium-small vector modulation (LMSVM) is proposed for CMV reduction and DC voltage balance in DC-link capacitors. The proposed hybrid modulation method reduces CMV and maintains voltage of each the split capacitor to  $V_{DC}/2$  simultaneously by applying LMSVM according to the division of space vector diagram. In [27], a common-mode voltage reduction pulsewidth modulation (CMV-R PWM) is proposed. This method also reduces CMV by using a different voltage vector instead of the existing small vector, and applies a separate controller to control the DC-link capacitor voltage stable. However, all of these methods do not consider the effect of the DC-link ripple current according to the change in the PWM method.

This paper presents a switching strategy to suppress the DC-link ripple current and CMV in a hybrid ANPC. The proposed switching scheme is simply implemented by replacing the voltage vectors that cause the large capacitor current and high peak-to-peak CMV with different voltage vectors. In addition, the proposed method extends the lifetime of the DC-link capacitor and reduces the leakage current in the hybrid ANPC. The feasibility and effectiveness of the proposed switching scheme have been demonstrated through simulations and experiments.

#### **II. OPERATION OF HYBRID ANPC INVERTER**

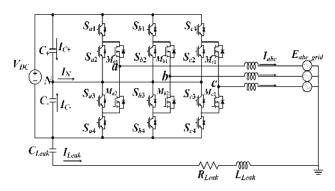

A leg of hybrid ANPC is composed of four Si IGBTs and two SiC MOSFETs as shown in Fig. 1 [11]. SiC MOSFETs, which have a low switching loss, should take most of the switching burden to minimize switching losses. Therefore, separate reference voltages for controlling the Si IGBT and SiC MOSFET are required to decrease the power loss of the hybrid ANPC inverter.

FIGURE 1. Configuration of a hybrid ANPC inverter.

Fig. 2 shows normalized reference pole voltage and the reference voltages for the Si IGBTs and SiC MOSFETs. Their reference voltages are represented by (1) and (2), respectively [11].

$$V_{xN\_IGBT}^{*} \begin{cases} 1 & (V_{xN\_norm}^{*} \ge 1) \\ 0 & (V_{xN\_norm}^{*} < 1) \end{cases}$$

(1)

$$V_{xN\_MOSFET}^* = V_{xN\_norm}^* - V_{xN\_IGBT}^*.$$

(2)

When the command voltage is in the positive half-period, the reference voltage  $V_{xN\_IGBT}^*$  is clamped to 1. Accordingly, for the half-period, the IGBTs  $S_{x1}$ ,  $S_{x3}$  are turned ON, and the IGBTs  $S_{x2}$ ,  $S_{x4}$  are turned OFF. When the reference voltage is

FIGURE 2. Reference pole voltages (a) Normalized reference pole voltage, (b) pole voltages for Si IGBT and SiC MOSFET.

in the negative half-period,  $V_{xN}^*$  IGBT is clamped to 0. Accordingly, the IGBTs  $S_{x2}$ ,  $S_{x4}$  are turned ON and the IGBTs  $S_{x1}$ ,  $S_{x3}$  are turned OFF. A reference voltage such as that in (2) is used for the PWM of the SiC MOSFET. When this modulation method is applied to a hybrid ANPC inverter, the Si IGBT operates at the line frequency and the SiC MOSFET operates at the switching frequency. Consequently, the losses caused by the Si IGBT are mostly conduction losses, and most of the switching losses are generated by the SiC MOSFET. A MOSFET has a small switching loss, and this modulation method increases its power conversion efficiency. The pole voltages of the hybrid ANPC inverters have four switching states ([N],  $[O^+]$ ,  $[O^-]$ , and [P]). When  $V_{xN IGBT}^*$  is 1,  $S_{x1}$  and  $S_{x3}$  are turned on and the [P]- and [O<sup>+</sup>]-states are generated according to the switching operation of the SiC MOSFET. In contrast, when  $V_{xN \ IGBT}^*$  is zero,  $S_{x2}$  and  $S_{x4}$  are turned on and the [N]- and [O<sup>-</sup>]-states are generated by the switching of the SiC MOSFET.

# **III. REALIABILITY OF CAPACITOR**

A power converter is composed of various components. The failure distribution of the capacitor accounts for a significant portion of the failure distribution [28]. Among capacitors, electrolytic capacitors are frequently used as the DC-link due to their large capacitance per volume and low cost. An electrolytic capacitor has three failure modes: short circuit, open circuit, and wear-out failure. Among these failure modes, wear-out failure is an inevitable but controllable failure mode. Therefore, the reliability of the capacitor can be improved by delaying the occurrence time of wear-out failure. Aged capacitors have reduced capacitance and increased ESR due to the wear-out caused by electrolyte evaporation. In particular, after the capacitance decreases by 20% and the ESR doubles, the rates of change of the capacitance and ESR are accelerated rapidly. This point is generally regarded as the wear-out failure of the capacitor [29].

The process of lifetime prediction was studied in [13] to predict the wear-out failure of capacitors. First, the loss caused by the ESR of the capacitor is as follows:

$$P_{loss,ESR} = \sum_{i=1}^{n} [I_{RMS}^2(f_i) \times \text{ESR}(f_i)], \qquad (3)$$

where  $I_{RMS}(f_i)$  and ESR( $f_i$ ) are the RMS value of the ripple current and the ESR at frequency  $f_i$ , respectively. From the above equation, it can be observed that the loss caused by the ESR depends on the RMS value of the capacitor current. The hot-spot temperature of the capacitor is expressed by

$$T_{hot-spot} = T_{ambient} + R_{ha} \times P_{loss,ESR},$$

(4)

where  $T_{ambient}$  is the ambient temperature and  $R_{ha}$  is the equivalent thermal resistance for the variation in temperature from ambient to hot-spot temperature. The lifetime of the capacitor is finally calculated using the hot-spot temperature as follows:

$$L = L_0 \times \left(\frac{V}{V_0}\right)^{-p_0} \times 2^{\frac{T_0 - T_{hot-spot}}{p_1}},\tag{5}$$

where  $L_0$ ,  $V_0$ ,  $T_0$ , and V are the rated lifetime, rated voltage, maximum allowable hot-spot temperature, and real voltage, respectively. For the electrolytic capacitor, the constant  $p_0$ ranges from approximately 3 to 5 and  $p_1$  is approximately 10 [13]. From the above lifetime model, it can be observed that the lifetime of the capacitor increases, as the hot-spot temperature of the capacitor decreases. As the hot-spot temperature is dependent on the loss, which decreases with a reduction in the RMS value of the capacitor current, the lifetime of the capacitor is extended by reducing the ripple current of the capacitor.

### IV. ANALYSIS ON DC-LINK RIPPLE CURRENT AND CMV

The currents flowing to the upper and lower DC-link capacitors are combined at the neutral point as shown in Fig. 1, which is expressed as

$$I_N = I_{C+} + I_{C-}, (6)$$

where  $I_{C+}$  and  $I_{C-}$  are the upper- and lower-side capacitor currents, respectively. Therefore, it is possible to reduce the ripple current of the upper and lower DC-link capacitors by reducing the neutral point ripple current. Only in the case of the [O<sup>+</sup>] or [O<sup>-</sup>] state, the phase current flows to the neutral point through the inner switches  $S_{x2}$  or  $S_{x3}$ , which are connected to the neutral point. For example, if the switching state is [PO<sup>+</sup>N], the b-phase current  $I_b$  flows to the neutral point; in contrast, in the case of [PO<sup>+</sup>O<sup>-</sup>], the b- and c-phase currents  $I_b + I_c$  flow to the neutral point. The neutral point currents according to the switching state of the three-level inverter are shown in Table 1.

| TABLE 1. St | witching state and | d magnitude of | f neutral point curren | t. |

|-------------|--------------------|----------------|------------------------|----|

|-------------|--------------------|----------------|------------------------|----|

| Switching state                                     |              | Neutral point current $(I_N)$ |  |

|-----------------------------------------------------|--------------|-------------------------------|--|

| Large vector [PPN], [PNP], [NP<br>[NNP], [NPN], [PN |              | 0                             |  |

|                                                     | [OPN], [ONP] | Ia                            |  |

| Medium vector                                       | [PON], [NOP] | $I_b$                         |  |

|                                                     | [PNO], [NPO] | $I_c$                         |  |

|                                                     | [OPP], [ONN] | $I_a$                         |  |

|                                                     | [POO], [NOO] | $I_b + I_c = -I_a$            |  |

| Small vector                                        | [POP], [NON] | $I_b$                         |  |

|                                                     | [OPO], [ONO] | $I_a + I_c = -I_b$            |  |

|                                                     | [PPO], [NNO] | $I_c$                         |  |

|                                                     | [OOP], [OON] | $I_a + I_b = -I_c$            |  |

| Zero vector [PPP], [OOO], [NNN]                     |              | 0                             |  |

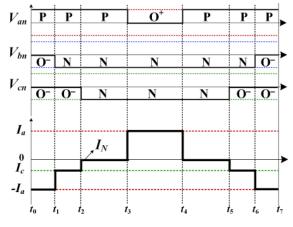

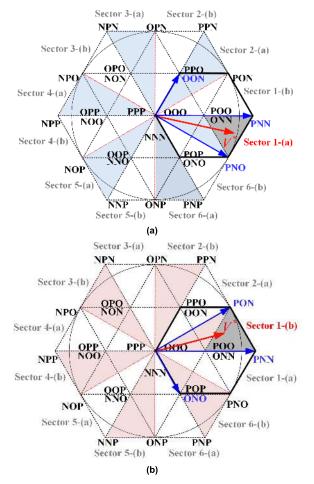

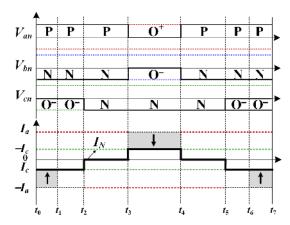

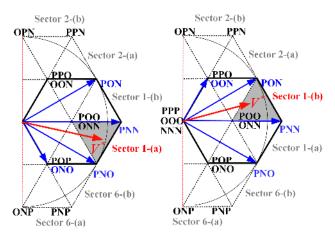

Fig. 3 shows the space vector diagram and reference voltage vector in conventional space vector PWM (SVPWM). In the marked sector, the order of magnitudes of the output currents is  $|I_a| > |I_b| > |I_c|$ . In conventional SVPWM, the voltage vectors (large vector: [PNN], medium vector: [PNO<sup>-</sup>], small vectors: [PO<sup>-</sup>O<sup>-</sup>], [O<sup>+</sup>NN]) are used to generate the reference voltage vector  $V^*$ .

FIGURE 3. Space vector diagram in conventional SVPWM.

Fig. 4 shows the switching sequence used to generate the reference voltage vector in Fig. 3 and the resulting neutral point current  $I_N$ . In this sector, the absolute value of  $I_a$  is the largest; hence, the use of [PO<sup>-</sup>O<sup>-</sup>] and [O<sup>+</sup>NN] causes the

FIGURE 4. Neutral point current according to the switching states in conventional SVPWM.

largest capacitor ripple current.  $[PO^-O^-]$  and  $[O^+NN]$  are the small vectors adjacent to the reference voltage vector.

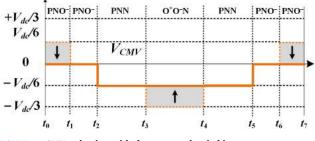

In a typical three-phase voltage source inverter, CMV is the average value of the three-phase output voltages and is expressed as

$$V_{CMV} = \frac{V_{an} + V_{bn} + V_{cn}}{3}$$

(7)

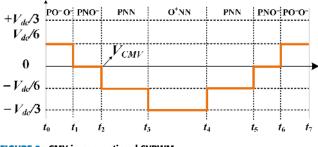

where  $V_{an}$ ,  $V_{bn}$ , and  $V_{cn}$  are the three-phase output pole voltages. As shown in Fig. 5, the CMV changes from  $V_{dc}/6$  to  $-V_{dc}/3$  within a switching period in Sector 1-(a). Among the switching states, the small vectors ([PO<sup>-</sup>O<sup>-</sup>] and [O<sup>+</sup>NN]) generate the largest ( $V_{dc}/6$ ) and smallest ( $-V_{dc}/3$ ) values of CMV. That is, both a large current ripple and a peakto-peak value of CMV are caused by the small vector closest to the  $V^*$ .

FIGURE 5. CMV in conventional SVPWM.

# V. REDUCTION OF DC-LINK RIPPLE CURRENT AND CMV A. PROPOSED SWITCHING METHOD

According to the analysis presented in Section IV, the small vector adjacent to the reference voltage induces a large ripple in the DC-link current and a higher peak-to-peak voltage as well. This paper proposes a switching scheme utilizing another vector instead of the small vectors adjacent to the reference voltage. For implementing the proposed method, the space vector diagram is divided into six sectors, and each sector is divided into sections (a) and (b). The substituted vectors are small and medium vectors located in

**FIGURE 6.** Sector segmentation and voltage vectors for generating the reference voltage, (a) Sector 1-(a), (b) Sector 1-(b).

the other sector and current sector, respectively. In section (a) of each sector, the small vector in the next sector is selected to replace the existing small vector. In contrast, in section (b) of each sector, the small vector in the previous sector is selected. Fig. 6(a) shows examples of generating the reference voltage vector  $V^*$  using the proposed method in Sector 1-(a). Conventional SVPWM selects  $[PO^-O^-]$ ,  $[O^+NN]$ ,  $[PNO^-]$ , and [PNN] to generate  $V^*$ . However, the proposed method uses  $[O^+O^-N]$  and  $[PNO^-]$  instead of the small vectors  $[O^+NN]$  and  $[PO^-O^-]$ . The switching sequence is  $[PO^-O^-]$ - $[PNO^-]$ -[PNN]- $[O^+NN]$ -[PNN]- $[PNO^-]$ - $[PNO^-]$ -[PNN]-[PNN]- $[PNO^-]$ - $[PNO^-]$  when the proposed switching scheme is applied.

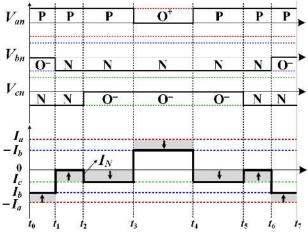

Fig. 7 shows the reconfigured switching sequence obtained using the proposed method for generating the reference voltage vector in Sector 1-(a). As analyzed above, the vectors  $[PO^-O^-]$  and  $[O^+NN]$  in Sector 1-(a) are replaced with  $[PNO^-]$  and  $[O^+O^-N]$ .  $[PNO^-]$  and  $[O^+O^-N]$  are symmetrically located on the basis of  $[PO^-O^-]$  and  $[O^+NN]$ , and are applied for the same dwelling time as  $[PO^-O^-]$  and  $[O^+NN]$ , so that the same reference voltage as in conventional SVPWM

FIGURE 7. Reduction of neutral point current with a reconfigured switching sequence using the proposed switching strategy.

FIGURE 8. CMV reduction with the proposed switching strategy.

can be generated. As the substitution, the c-phase current, which is the smallest current in Sector 1-(a), flows to the neutral point. Using the proposed technique, only a zero current or the smallest current among the three-phase output currents flows to the neutral point in all the sectors. The reduction of the neutral point current induces the suppression of the DC-link ripple current, which causes an increase in the service life of the DC-link capacitor.

In addition, the peak-to-peak value of the CMV is reduced by applying the proposed switching scheme, which does not use the small vector closest to the reference voltage. Fig. 8 shows the CMV within a cycle when the proposed switching method is applied. Due to the use of [PNO<sup>-</sup>] and  $[O^+O^-N]$ , the CMV varies from  $-V_{dc}/6$  to zero. The peakto-peak value of the CMV is reduced to approximately 1/3 of the CMV obtained when applying conventional SVPWM. Reduction of CMV improves system reliability by reducing EMI and bearing current.

The proposed method incurs the same amount of loss as conventional SVPWM. This is because the number of switching operations and the turn-on time of each switch are the same as those in conventional SVPWM. However, as shown in Table 2, the proposed switching scheme increases the period to maintain the same switching state. If the same switching state persists, the total harmonic distortion (THD) deteriorates as the current continues to increase or decrease during this period. Although the proposed method itself causes a deterioration of the THD, when it is applied to a system having a leakage current such as a PV inverter, the THD

# IEEE Access

TABLE 2. Switching sequences obtained with the proposed method.

| Sector | Proposed switching strategy                                                                                                                 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1-(a)  | [PNO <sup>-</sup> ]-[PNO <sup>-</sup> ]-[PNN]-[O <sup>+</sup> O <sup>-</sup> N]-[PNN]-[PNO <sup>-</sup> ]-[PNO <sup>-</sup> ]               |

| 1-(b)  | [PO <sup>-</sup> N]-[PO <sup>-</sup> N]-[PNN]-[O <sup>+</sup> NO <sup>-</sup> ]-[PNN]-[PO <sup>-</sup> N]-[PO <sup>-</sup> N]               |

| 2-(a)  | [O <sup>+</sup> PO <sup>-</sup> ]-[PPN]-[PO <sup>+</sup> N]-[PO <sup>+</sup> N]-[PO <sup>+</sup> N]-[PPN]-[O <sup>+</sup> PO <sup>-</sup> ] |

| 2-(b)  | [PO <sup>+</sup> O <sup>-</sup> ]-[PPN]-[O <sup>+</sup> PN]-[O <sup>+</sup> PN]-[O <sup>+</sup> PN]-[PPN]-[PO <sup>+</sup> O <sup>-</sup> ] |

| 3-(a)  | [O <sup>-</sup> PN]-[O <sup>-</sup> PN]-[NPN]-[NO <sup>+</sup> O <sup>-</sup> ]-[NPN]-[O <sup>-</sup> PN]-[O <sup>-</sup> PN]               |

| 3-(b)  | [NPO <sup>-</sup> ]-[NPO <sup>-</sup> ]-[NPN]-[O <sup>-</sup> O <sup>+</sup> N]-[NPN]-[NPO <sup>-</sup> ]-[NPO <sup>-</sup> ]               |

| 4-(a)  | [O <sup>-</sup> O <sup>+</sup> P]-[NPP]-[NPO <sup>+</sup> ]-[NPO <sup>+</sup> ]-[NPO <sup>+</sup> ]-[NPP]-[O <sup>-</sup> O <sup>+</sup> P] |

| 4-(b)  | [O <sup>-</sup> PO <sup>+</sup> ]-[NPP]-[NO <sup>+</sup> P]-[NO <sup>+</sup> P]-[NO <sup>+</sup> P]-[NPP]-[O <sup>-</sup> PP]               |

| 5-(a)  | [NO <sup>-</sup> P]-[NO <sup>-</sup> P]-[NNP]-[O <sup>-</sup> NO <sup>+</sup> ]-[NNP]-[NO <sup>-</sup> P]-[NO <sup>-</sup> P]               |

| 5-(b)  | [O <sup>-</sup> NP]-[O <sup>-</sup> NP]-[NNP]-[NO <sup>-</sup> O <sup>+</sup> ]-[NNP]-[O <sup>-</sup> NP]-[O <sup>-</sup> NP]               |

| 6-(a)  | [PO <sup>-</sup> O <sup>+</sup> ]-[PNP]-[O <sup>+</sup> NP]-[O <sup>+</sup> NP]-[O <sup>+</sup> NP]-[PNP]-[PO <sup>-</sup> O <sup>+</sup> ] |

| 6-(b)  | [O <sup>+</sup> O <sup>-</sup> P]-[PNP]-[PNO <sup>+</sup> ]-[PNO <sup>+</sup> ]-[PNO <sup>+</sup> ]-[PNP]-[OO <sup>-</sup> P]               |

degradation can be offset by the leakage current reduction effect of the proposed switching method. The impact of the proposed switching method on the THD will be discussed through simulation and experimental results.

In addition, the proposed switching method is applicable to all three-level inverters such as NPC-type or T-type inverters and hybrid ANPC inverters.

# B. COMPARISON WITH EXISTING DC-LINK RIPPLE CURRENT REDUCTION METHOD

In [16], a DC-link ripple current reduction method (Method-I) is proposed. This switching method reduces neutral-point ripple current and CMV simultaneously. These effects are similar to the proposed method in this paper. However, the reduction ratio of the neutral-point ripple current is different between the Method-I and proposed method.

Fig. 9 Shows the space vector diagram for each sector in Method-I. In Sector 1-(a), Method-I selects  $[PO^-N]$  and  $[O^+NO^-]$  vectors instead of  $[PO^-O^-]$  and  $[O^+NN]$  vectors, while the proposed method selects  $[PNO^-]$  and  $[O^+O^-N]$ . When a vector is selected in this way, the b-phase current, which is the second largest vector in Sector 1-(a), flows to the neutral point. As a result, the neutral point ripple current reduction effect of Method-I is inferior to the proposed switching method. Fig. 10 shows the NP current reduction effect when Method-I is applied. The a-phase current caused by  $[PO^-O^-]$  and  $[O^+NN]$  is replaced by b-phase current. However, the neutral point reduction effect is inferior to the proposed method in which a smaller c-phase current flows to the neutral point instead of the b-phase current.

# C. COMPARISION WITH EXISTING CMV REDUCTION METHOD

Fig. 11(a) shows CMV in Sector 1-(a) when LMZVM used in [22] and [23] is applied. LMZVM is a method of generating a reference voltage using only large, medium, and zero

**FIGURE 9.** Sector segmentation and voltage vectors for generating the reference voltage in Method-I.

**FIGURE 10.** Reduction of neutral point current with a reconfigured switching sequence using the Method-I.

vectors. This is the same as replacing small vectors  $[PO^-O^-]$  and  $[O^+NN]$  with zero vector and large vector. When the proposed LMZVM is applied, the amount of change in CMV is reduced to  $V_{DC}/3$ .

In [26], for DC balance of DC-link capacitors, LMZVM and LMSVM are applied to some of Sector 1-(a). Fig. 11(b) shows CMV in Sector 1-(a) when the LMSVM used in [26] is applied. Even when the LMSVM used for DC voltage balance is applied, the change in CMV is  $V_{DC}/6$ .

Fig. 11(c) shows the CMV in Sector 1-(a) when a switching method proposed in [16] and [27]. In this switching method, [PO<sup>-</sup>N] and [O<sup>+</sup>NO<sup>-</sup>] vectors are applied instead of [PO<sup>-</sup>O<sup>-</sup>] and [O<sup>+</sup>NN] vectors in Sector 1-a, and accordingly, the change of CMV is reduced to  $V_{DC}/6$  as well.

As the above analysis, the proposed method has the CMV reduction performance corresponding to that of the existing CMV reduction methods.

# **VI. SIMULATION RESULTS**

The hybrid ANPC inverter was simulated using the PSIM software tool, and the simulation environment is shown in Table 3.

FIGURE 11. CMV reduction performance, (a) LMZVM, (b) LMSVM, (c) Method-I and the method in [27].

TABLE 3. Simulation specifications.

| Parameter                   | Value                   |  |

|-----------------------------|-------------------------|--|

| Rated power                 | 15 [kW]                 |  |

| Grid voltage (line-to-line) | 380 [V <sub>rms</sub> ] |  |

| Grid frequency              | 60 [Hz]                 |  |

| Switching frequency         | 30 [kHz]                |  |

| DC-link voltage             | 600 [V]                 |  |

| DC-link capacitor           | 1000 [µF]               |  |

| Filter inductor             | 1.5 [mH]                |  |

Fig. 12 provides the comparison between conventional SVPWM and the proposed method in terms of the output current, neutral point currents  $I_N$ , and gate signals of the IGBT and MOSFET. The neutral point current  $I_N$  is reduced from 5.82 A<sub>RMS</sub> to 2.34 A<sub>RMS</sub>, which represents a reduction of 58%. The THD of the three-phase current is changed from 1.10% to 2.32% after applying the proposed method. The THD characteristic is degraded when the proposed method is applied. In addition, the low and high switching operations of the IGBTs and MOSFETs in the hybrid ANPC are maintained even when the proposed method is applied.

Table 4 and 5 shows the specification and the comparison of capacitor lifetimes calculated using (3)-(5). In case of conventional SVPWM,  $P_{loss,ESR}$  and  $T_{hot-spot}$  are calculated

#### TABLE 4. Specification of DC-link Capacitor (DS138S).

| Parameter                                    | Value        |  |  |

|----------------------------------------------|--------------|--|--|

| Ambient temperature, $T_a$                   | 60 [°C]      |  |  |

| Allowable hot-spot temperature, $T_{\theta}$ | 105 [°C]     |  |  |

| Equivalent thermal resistance, $R_{ha}$      | 6 [K/W]      |  |  |

| ESR                                          | 105 [mΩ]     |  |  |

| Rated lifetime, $L_0$                        | 1.14 [years] |  |  |

#### TABLE 5. Comparison of capacitor lifetimes.

| Modulation method         | Capacitor lifetime |

|---------------------------|--------------------|

| Conventional SVPWM        | 19.78 [years]      |

| Proposed switching scheme | 32.61 [years]      |

FIGURE 12. Output current, neutral point current, and gating signals with and without the proposed switching method.

as 1.76 W, and 70.52 °C when the simulation conditions of Table 3 is applied. In this case, the lifetime of the DC-link capacitor calculated by (5) is 19.78 years. When the proposed method is applied,  $P_{loss,ESR}$  decreases to 0.31 W by reducing the neutral point current. Thus, the  $T_{hot-spot}$  decreases to 61.88 °C. In this case, the lifetime of the capacitor increases to 32.61 years.

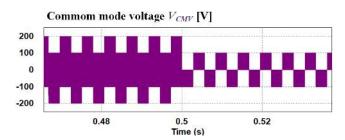

Fig. 13 shows the CMV of the hybrid ANPC inverter. The CMV has a magnitude ranging from -100 to 200 V and -200 to 100 V before applying the proposed switching

FIGURE 13. Comparison of CMV reduction performances.

FIGURE 14. Output current and neutral point current when the leakage current is considered.

method. After applying the proposed method, the magnitude of the CMV varies from -100 to 0 V and 0 to 100 V.

Fig. 14 depicts the output currents, neutral point currents, and leakage currents before and after applying the proposed switching scheme. A leakage capacitor (0.3  $\mu$ F) and a resistor (10  $\Omega$ ) were installed to confirm the effect of the decrease in  $I_{Leak}$  due to the reduction of CMV. The output current before applying the proposed technique has a THD of 7.20% due to the leakage current flowing into the leakage capacitor. The RMS values of the neutral point current  $I_N$  and leakage current ILeak are 5.90 A and 1.44 A, respectively. When the proposed method was applied, the leakage current was decreased by the reduction of the CMV. The RMS value at this time was 0.35 A, which was reduced by approximately 76% compared with the aforementioned value, and the THD of the output current was rather improved. Therefore, the proposed method is suitable for applications such as PV inverters having a leakage current.

Fig. 15 provides represents the line-to-line voltage with conventional SVPWM, Method-I and the proposed

FIGURE 15. Simulation waveforms of line-to-line voltage, (a) Conventional SVPWM, (b) Method-I, (c) proposed switching method.

switching method. As shown in Fig. 15(a), the change of line-to-line voltage within one switching period is  $V_{DC}/2$ . When the Method-I is applied, the variation of the line-to-line voltage is increased to  $V_{DC}$  in some sections as shown in the Fig. 15(b). In addition, when applying the proposed switching method, the change of the line-to-line voltage also increases from  $V_{DC}/2$  to  $V_{DC}$  in some sections as shown in Fig. 15(c). This causes an increase in output current THD. Although the quality of the output current is degraded, the blocking voltage of power switch is the same as the conventional SVPWM and the hot-spot temperature of the capacitor is reduced due to the reduction of the ripple current of the capacitor.

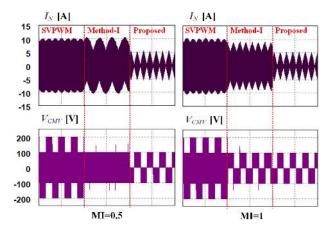

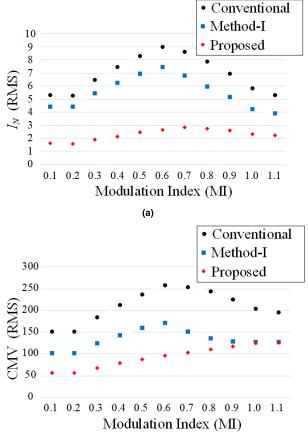

Fig. 16. shows the comparison of the performances for the reduction of  $I_N$  and CMV among conventional SVPWM, the switching method in [16] (Method-I), and the proposed method. Based on Sector 1-(a), Method-I replaces the  $[PO^{-}O^{-}]$  and  $[O^{+}NN]$  states with  $[PO^{-}N]$  and  $[O^{+}NO^{-}]$ . The replaced vectors cause the second largest current in Sector 1-(a) to flow to the neutral point. Method-I can reduce the DC-link ripple current by approximately 25%. It also reduces the peak-to-peak value of the CMV by 1/3 compared with conventional SVPWM in the case of a high modulation index (MI). Moreover, Method-I has a similar CMV reduction performance as the proposed method, but its  $I_N$  reduction performance is not sufficient. In addition, Method-I shows low performances for the reduction of the neutral point current and CMV in the case of low MI. In contrast, the proposed switching method maintains good performances for the reduction of I<sub>N</sub> and CMV regardless of MI. Fig. 17 compares

FIGURE 16. Neutral point current and CMV according to the switching method and MI.

(b)

**FIGURE 17.** Comparison of performances for the reduction of neutral point current and CMV, (a) reduction of neutral point ripple current, (b) CMV reduction.

the performances for the reduction of  $I_N$  and CMV according to the switching method and MI.

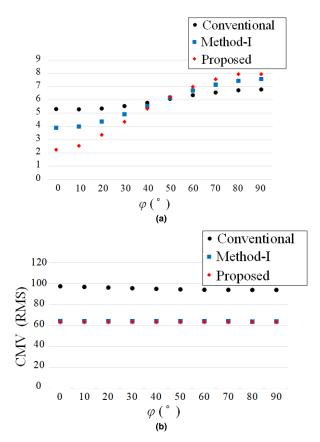

Fig. 18 compares the  $I_N$  and CMV reduction performance according to the switching method and power factor (PF) angle. Simulation was performed with the MI set to 1.1. In the case of the proposed method, the outstanding  $I_N$  reduction performance was shown at the low PF angle, but the reduction

**FIGURE 18.** Comparison of performances for the reduction of neutral point current and CMV according to the PF angle, (a) neutral point ripple current, (b) CMV.

performance decreased as the PF angle increased. However, CMV reduction performance is maintained regardless of the power factor angle.

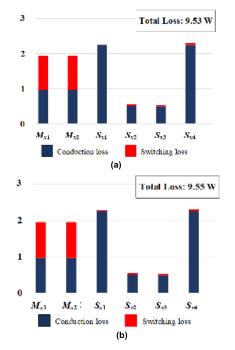

Fig. 19 shows the comparison of power losses between the conventional SVPWM and proposed switching method. As the analysis in Section V, even if the proposed method is applied, the number of switching and the dwelling time of the active voltage vector are the same as the conventional SVPWM. The power loss when before and after applying the proposed switching scheme are theoretically equivalent. As shown in Fig. 19(a) and (b), most of the switching losses are concentrated in the SiC MOSFET due to the special switching operation of the hybrid ANPC. The total loss that occurs in a leg is 9.53 W. When the proposed switching method is applied, the pattern of the loss distribution remains the same and the total loss is 9.55 W. This result indicates that the power loss of the proposed switching scheme is almost the same as the power loss of the conventional SVPWM.

# **VII. EXPERIMENTAL RESULTS**

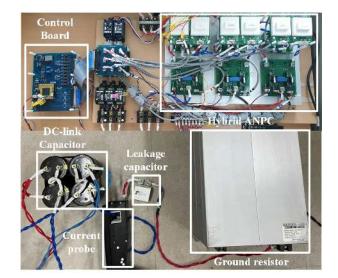

Experimental results were obtained using a prototype of the hybrid ANPC inverter to verify the proposed switching scheme. The hardware setup for the experiment is shown in Fig. 20, and the experimental environment is the same as the simulation environment shown in Table 3. The controller board is composed of the DSP (TMS320F28377S).

### TABLE 6. Performance Comparison between the CMV Reduction Methods.

| Switching method                       | Peak-to-peak value of CMV | Voltage level of<br>line-to-line voltage | CMV fluctuation time within $T_s$ | Simultaneous<br>switching | Switching time within <i>T<sub>s</sub></i> |

|----------------------------------------|---------------------------|------------------------------------------|-----------------------------------|---------------------------|--------------------------------------------|

| Conventional SVPWM                     | $V_{DC}/2$                | 5-level                                  | 6                                 | Ν                         | 6                                          |

| [16], [27]<br>(Method-I and CMV-R PWM) | $V_{DC}/6$                | 5-level, 3-level                         | 6                                 | Ν                         | 6                                          |

| [22], [23] (LMZVM)                     | <i>V<sub>DC</sub></i> /6  | 5-level, 3-level                         | 2                                 | Y                         | 6                                          |

| [26] (hybrid modulation)               | $V_{DC}/6$                | 5-level, 3-level                         | 2 or 4                            | Y                         | 4 or 6                                     |

| Proposed switching method              | $V_{DC}/6$                | 5-level, 3-level                         | 2                                 | Y                         | 6                                          |

FIGURE 19. Comparison of power losses (a) conventional SVPWM, (b) proposed switching method.

The Si-IGBTs in the hybrid ANPC inverter are implemented by using the SK75GBB066T which is an IGBT module made by Semikron. For the SiC MOSFETs, C2M0040120D made by CREE is used.

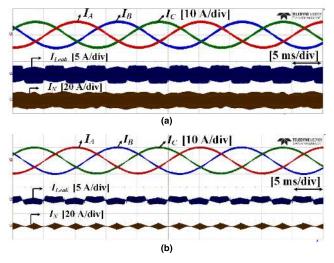

Fig. 21 shows the comparative result of the three-phase current and  $I_N$ . In Fig. 21(a), the RMS value of  $I_N$  is 6.10 A with conventional SVPWM. After applying the proposed switching method, the RMS value of  $I_N$  is considerably suppressed to 2.93 A<sub>RMS</sub> in Fig. 21(b). The reduction ratio of  $I_N$  is consistent with that of the simulation. The quality of the output current is degraded by applying the proposed switching method. The THD of the output current increases from 1.3% to 2.6%.

Fig. 22 shows the experimental waveforms of the lineto-line voltage of switching methods. In the conventional SVPWM, the line-to-line has five level voltage. On the other hand, in Method-I and the proposed method, the voltage level in some sections decreases to three. Because of this

FIGURE 20. Experimental setup.

effect, the THD of the output current increase. Therefore, an appropriate system filter design is required. However, the blocking voltage per power semiconductor is the same as the conventional SVPWM.

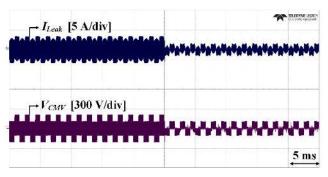

Fig. 23 shows the performance of the proposed switching method for the reduction of the leakage current  $I_{Leak}$  and CMV. To consider  $I_{Leak}$ , a leakage capacitor (0.3  $\mu$ F) and a resistor (10  $\Omega$ ) were connected between the bottom of the DC-link capacitor and the rear end of the load. It can be observed that  $I_{Leak}$  decreased with the reduction in the CMV by the proposed method. The peak-to-peak value of the CMV was suppressed from  $V_{dc}/2$  to  $V_{dc}/6$  as in the previous analysis and simulation results. Consequently, the RMS value of  $I_{Leak}$  was also reduced from 1.79 to 0.55 A, which indicates a reduction of 71%.

As shown in Fig. 24, in the case of conventional SVPWM, a high peak-to-peak value of CMV induced a large  $I_{Leak}$ , which deteriorated the quality of the current. The THD of the output current was 5.75%, and the RMS value of  $I_N$  was 6.11 A. When the proposed switching method was applied, the improvement of the THD of the output current with the reduction of  $I_{Leak}$  was more dominant than the deterioration of the THD of the switching technique itself. The THD of the current improved from 5.75% to 4.28% after applying the

FIGURE 21. Experimental waveforms of the output current and neutral point current of (a) conventional SVPWM, (b) proposed switching method.

FIGURE 22. Experimental waveforms of the line-to-line voltage, (a) conventional SVPWM, (b) Method-I, (c) proposed switching method.

proposed method. Therefore, the proposed method is suitable for applications such as PV inverters.

**FIGURE 23.** Experimental waveforms of the performances of the proposed switching method for the reduction of the leakage current and CMV.

**FIGURE 24.** Experimental waveforms of the output current and neutral point current when the leakage current is considered, (a) conventional SVPWM, (b) proposed switching method.

**FIGURE 25.** Experimental waveforms of the output current and neutral point current when the leakage current is considered.

Table 6 shows the performance comparison between the CMV reduction methods. All the CMV reduction methods reduce the peak-to-peak value of CMV to  $V_{DC}/6$ . However, all the methods have a disadvantage of voltage level reduction line voltage in some section which degrades the quality of the output currents. The LMZVM and proposed switching method have the minimum value of the CMV fluctuation time between the CMV reduction method. On the other hand,

since LMZVM and proposed method perform simultaneous switching, the quality of output current is worse than other methods.

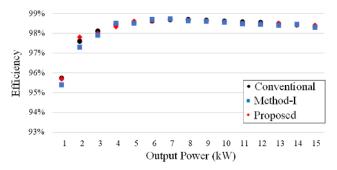

Fig. 25 shows the result of efficiency test according to the type of the modulation methods. The efficiency test is implemented by using the power analyzer (WT3000) made by Yokogawa. In both Method-I and the proposed switching method, the power loss in the inverter is theoretically the same. This is because the dwelling time of the active voltage vector and the number of switching are the same. However, since the THD characteristic of the output current is degraded compared to the conventional SVPWM, the additional loss due to the harmonic currents. However, this loss occupies small ratio, and as the result of the actual efficiency test, the switching methods have almost the same efficiency.

# **VIII. CONCLUSION**

This paper proposed a switching method for a hybrid ANPC inverter to reduce the DC-link ripple current and CMV. The switching states causing a large DC-link ripple current and high CMV were defined. The proposed switching method replaced the small vector causing a large neutral current and high CMV with other voltage vectors. The proposed switching method can be implemented through simple software programming. The proposed method also extends the service life of the capacitor approximately 1.7 times. In addition, when this method is applied to a PV inverter, the quality of the output current is improved with the reduction in the leakage current due to the reduced CMV. The validity and effectiveness of the proposed method were demonstrated through simulations and experimental results.

## REFERENCES

- [1] K.-B. Lee and J.-S. Lee, *Reliability Improvement Technology for Power Converters*. Singapore: Springer, 2017.

- [2] J. Rodríguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel voltage-source-converter topologies for industrial medium-voltage drives," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2930–2945, Dec. 2007.

- [3] L. Franquelo, J. Rodriguez, J. Leon, S. Kouro, R. Portillo, and M. Prats, "The age of multilevel converters arrives," *IEEE Ind. Electron. Mag.*, vol. 2, no. 2, pp. 28–39, Jun. 2008.

- [4] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Pérez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553–2579, Aug. 2010.

- [5] J. Rodriguez, S. Bernet, P. K. Steimer, and I. E. Lizama, "A survey on neutral-point-clamped inverters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- [6] Y. Deng, J. Li, K. H. Shin, T. Viitanen, M. Saeedifard, and R. G. Harley, "Improved modulation scheme for loss balancing of three-level active NPC converters," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2521–2532, Apr. 2017.

- [7] T. Bruckner and S. Bernet, "Loss balancing in three-level voltage source inverters applying active NPC switches," in *Proc. IEEE Power Electron. Spec. Conf.*, Jun. 2001, pp. 1135–1140.

- [8] L. Ma, T. Kerekes, P. Rodriguez, X. Jin, R. Teodorescu, and M. Liserre, "A new PWM strategy for grid-connected half-bridge active NPC converters with losses distribution balancing mechanism," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 5331–5340, Sep. 2015.

- [9] Y. Jiao and F. C. Lee, "New modulation scheme for three-level active neutral-point-clamped converter with loss and stress reduction," *IEEE Trans. Ind. Electron.*, vol. 62, no. 9, pp. 5468–5479, Sep. 2015.

- [10] D. Barater, C. Concari, G. Buticchi, E. Gurpinar, D. De, and A. Castellazzi, "Performance evaluation of a three-level ANPC photovoltaic gridconnected inverter with 650-V SiC devices and optimized PWM," *IEEE Trans. Ind. Appl.*, vol. 52, no. 3, pp. 2475–2485, May/Jun. 2016.

- [11] Q.-X. Guan, C. Li, Y. Zhang, S. Wang, D. D. Xu, W. Li, and H. Ma, "An extremely high efficient three-level active neutral-point-clamped converter comprising SiC and Si hybrid power stages," *IEEE Trans. Power Electron.*, vol. 33, no. 10, pp. 8341–8352, Oct. 2018.

- [12] H. S. Chung, H. Wang, F. Blaabjerg, and M. Pecht, *Reliability of Power Electronic Converter Systems*. London, U.K.: IET, 2016.

- [13] H. Wang, P. Davari, H. Wang, D. Kumar, F. Zare, and F. Blaabjerg, "Lifetime estimation of DC-link capacitors in adjustable speed drives under grid voltage unbalances," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4064–4078, May 2019.

- [14] A. Tcai, H.-U. Shin, and K.-B. Lee, "DC-link capacitor-current ripple reduction in DPWM-based back-to-back converters," *IEEE Trans. Ind. Electron.*, vol. 65, no. 3, pp. 1897–1907, Mar. 2018.

- [15] L. Shen, S. Bozhko, G. Asher, C. Patel, and P. Wheeler, "Active DClink capacitor harmonic current reduction in two-level back-to-back converter," *IEEE Trans. Power Electron.*, vol. 31, no. 10, pp. 6947–6954, Oct. 2016.

- [16] S.-M. Kim, I. J. Won, J. Kim, and K.-B. Lee, "DC-link ripple current reduction method for three-level inverters with optimal switching pattern," *IEEE Trans. Ind. Electron.*, vol. 65, no. 12, pp. 9204–9214, Dec. 2018.

- [17] D. Han, C. T. Morris, and B. Sarlioglu, "Common-mode voltage cancellation in PWM motor drives with balanced inverter topology," *IEEE Trans. Ind. Electron.*, vol. 64, no. 4, pp. 2683–2688, Apr. 2017.

- [18] H. Chen and H. Zhao, "Review on pulse-width modulation strategies for common-mode voltage reduction in three-phase voltage-source inverters," *IET Power Electron.*, vol. 9, no. 14, pp. 2611–2620, Nov. 2016.

- [19] J. Huang and H. Shi, "A hybrid filter for the suppression of commonmode voltage and differential-mode harmonics in three-phase inverters with CPPM," *IEEE Trans. Ind. Electron.*, vol. 62, no. 7, pp. 3991–4000, Jul. 2015.

- [20] M. C. Di Piazza, M. Luna, and G. Vitale, "EMI reduction in DC-fed electric drives by active common-mode compensator," *IEEE Trans. Electromagn. Compat.*, vol. 56, no. 5, pp. 1067–1076, Oct. 2014.

- [21] C. T. Morris, D. Han, and B. Sarlioglu, "Reduction of common mode voltage and conducted EMI through three-phase inverter topology," *IEEE Trans. Power Electron.*, vol. 32, no. 3, pp. 1720–1724, Mar. 2017.

- [22] C. Qin, C. Zhang, A. Chen, X. Xing, and G. Zhang, "A space vector modulation scheme of the quasi-Z-source three-level T-type inverter for common-mode voltage reduction," *IEEE Trans. Ind. Electron.*, vol. 65, no. 10, pp. 8340–8350, Oct. 2018.

- [23] X. Xing, X. Li, F. Gao, C. Qin, and C. Zhang, "Improved space vector modulation technique for neutral-point voltage oscillation and common-mode voltage reduction in three-level inverter," *IEEE Trans. Power Electron.*, vol. 34, no. 9, pp. 8697–8714, Sep. 2019.

- [24] P. Liu, S. Duan, C. Yao, and C. Chen, "A double modulation wave CBPWM strategy providing neutral-point voltage oscillation elimination and CMV reduction for three-level NPC inverters," *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 16–26, Jan. 2018.

- [25] W. Jiang, P. Wang, M. Ma, J. Wang, J. Li, L. Li, and K. Chen, "A novel virtual space vector modulation with reduced common-mode voltage and eliminated neutral point voltage oscillation for neutral point clamped threelevel inverter," *IEEE Trans. Ind. Electron.*, vol. 67, no. 2, pp. 884–894, Feb. 2020.

- [26] J.-S. Lee and K.-B. Lee, "New modulation techniques for a leakage current reduction and a neutral-point voltage balance in transformerless photovoltaic systems using a three-level inverter," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1720–1732, Apr. 2014.

- [27] X. Zhang, X. Wu, C. Geng, X. Ping, S. Chen, and H. Zhang, "An improved simplified PWM for three-level neutral point clamped inverter based on two-level common-mode voltage reduction PWM," *IEEE Trans. Power Electron.*, vol. 35, no. 10, pp. 11143–11154, Oct. 2020.

- [28] E. Wolfgang, "Examples for Failures in Power Electronics Systems," presented at the ECPE Tuts. Rel. Power Electron. Syst., Nuremberg, Germany, Apr. 2007.

- [29] K. Abdennadher, P. Venet, G. Rojat, J.-M. Retif, and C. Rosset, "A realtime predictive-maintenance system of aluminum electrolytic capacitors used in uninterrupted power supplies," *IEEE Trans. Ind. Appl.*, vol. 46, no. 4, pp. 1644–1652, Jul. 2010.

**SANG-WON AN** (Graduate Student Member, IEEE) received the B.S. and M.S. degrees in electrical and computer engineering from Ajou University, Suwon, South Korea, in 2019 and 2021, respectively. His research interests include multilevel inverters, grid-connected systems, and reliability.

**SEOK-MIN KIM** (Member, IEEE) received the B.S. degree in electronic engineering from Sejong University, Seoul, South Korea, in 2013, and the M.S. degree in space survey information technology and the Ph.D. degree in electrical and computer engineering from Ajou University, Suwon, South Korea, in 2016 and 2020, respectively. He is currently working as a Senior Research Engineer with the Power Conversion Research and Development Team, LS Electric Company Ltd., Anyang,

South Korea. His research interests include grid-connected systems, multilevel inverters, and reliability.

**KYO-BEUM LEE** (Senior Member, IEEE) received the B.S. and M.S. degrees in electrical and electronic engineering from Ajou University, Suwon, South Korea, in 1997 and 1999, respectively, and the Ph.D. degree in electrical engineering from Korea University, Seoul, South Korea, in 2003.

From 2003 to 2006, he was with the Institute of Energy Technology, Aalborg University, Aalborg, Denmark. From 2006 to 2007, he was with the

Division of Electronics and Information Engineering, Jeonbuk National University, Jeonju, South Korea. He joined the Department of Electrical and Computer Engineering, Ajou University, in 2007. His research interests include electric machine drives, renewable power generations, and electric vehicle applications. He is currently an Associate Editor of the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, the IEEE TRANSACTIONS ON POWER ELECTRONICS, the *Journal of Power Electronics*, and the *Journal of Electrical Engineering & Technology*.

. . .