## Carbon nanotube memory devices of high charge storage stability

J. B. Cui,<sup>a)</sup> R. Sordan, M. Burghard, and K. Kern

Max-Planck-Institut fuer Festkoerperforschung, Heisenbergstr. 1, D-70569 Stuttgart, Germany

(Received 3 July 2002; accepted 30 August 2002)

Molecular memory devices with semiconducting single-walled carbon nanotubes constituting a channel of 150 nm in length are described. Data storage is achieved by sweeping gate voltages in the range of 3 V, associated with a storage stability of more than 12 days at room temperature. By annealing in air or controlled oxygen plasma exposure, efficient switching devices could be obtained from thin nanotube bundles that originally showed only a small gate dependence of conductance. © 2002 American Institute of Physics. [DOI: 10.1063/1.1516633]

Recent progress in the assembly of a small number of molecules between two electrodes in sandwich configuration has resulted in electrical devices revealing switching behavior<sup>1,2</sup> or negative differential resistance.<sup>3</sup> These achievements strongly encourage the development of molecular electronic devices<sup>4</sup> with the potential to overcome the limitations of silicon-based microelectronics.<sup>5</sup> Single-walled carbon nanotubes (SWCNTs), with a diameter in the nanometer range and a length of several micrometers, are especially attractive for that purpose due to their electronic, mechanical, and chemical properties.<sup>6</sup> To date, a number of molecular devices have been realized with SWCNTs, including fieldeffect transistors,<sup>7,8</sup> room-temperature single-electron transistors,<sup>9,10</sup> logic gate circuits,<sup>11</sup> inverters,<sup>12</sup> and electro-mechanical switches.<sup>13,14</sup> Very recently, the first prototypes of memory devices based on SWCNT field-effect transistors were also reported.<sup>15,16</sup> Here, we report easy-to-fabricate SWCNT memory devices exhibiting an extraordinarily high charge storage stability of more than 12 days at room temperature.

In our experiments, SWCNT raw material (arcdischarge product purchased from Carbolex®, Lexington, USA) was dispersed in an aqueous surfactant solution (1 wt % lithium-dodecylsulfate), and purified by centrifugation. The tubes were then deposited on a highly Sb-doped silicon wafer with a 100 nm thick thermally grown SiO<sub>2</sub> layer previously surface modified by amino-silanization. Typically one third of the deposited objects are individual SWCNTs, whereas two thirds consist of small SWCNT bundles with a diameter in the range of 2-4 nm. Source and drain contacts (15 nm AuPd without any adhesion layer), separated by  $\sim$ 150 nm, were defined on top of the SWCNTs by electronbeam lithography. The  $n^+$ -doped Si wafer was used as the back gate. All electrical measurements were performed under ambient conditions, except for the temperature dependence which was studied with the sample in a vacuum  $(p=10^{-4})$ mbar).

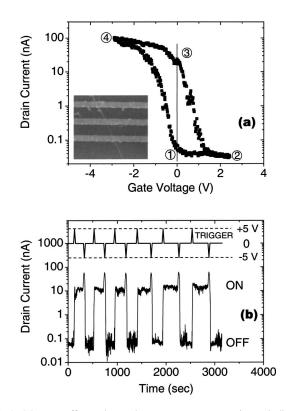

A significant fraction (~50%) of the investigated semiconducting SWCNTs (thin bundles) revealed memory effects, as reflected in reproducible hysteresis in the drain current ( $I_D$ ) versus gate potential ( $V_G$ ) characteristics. A representative example is displayed in Fig. 1(a), which shows the  $I_D - V_G$  curve of an individual SWCNT (~2 nm in height) at room temperature. The gate voltage was swept continuously from 0 to +3 V, then to -3 V, and back to 0 V, corresponding to the loop (1) $\rightarrow$ (2) $\rightarrow$ (3) $\rightarrow$ (4) $\rightarrow$ (1). The observed conductance decrease for increasing gate potential is in accordance with the known *p*-type semiconducting behavior of air-exposed SWCNTs.<sup>7,17</sup> The two conductance states at  $V_G$ =0 V (points (1) and (3)) differ by more than two orders of magnitude, associated with a threshold voltage shift of 1.25 V. The reversibility of switching between the high con-

FIG. 1. Memory effects observed at room temperature in an individual SWCNT with a diameter of  $\sim 2$  nm. The bias voltage  $V_{\text{bias}}$  is 10 mV. (a), Hysteretic behavior of drain current as a function of gate voltage. A threshold voltage shift of  $\sim 1.25$  V is observed upon sweeping the gate voltage along the points  $(\bigcirc) \rightarrow (\bigcirc) \rightarrow (\bigcirc) \rightarrow (\bigcirc)$ . The inset on the left-hand side shows the atomic force microscopy image of the nanotube between electrode lines separated by  $\sim 150$  nm. (b), Switching behavior of the memory device at  $V_G = 0$  V by triggering the device with the gate voltage signal shown in the inset. The peaks observed when the device is switched from the ON to the OFF state correspond to the maximum drain current at the gate voltage of -5 V.

3260

© 2002 American Institute of Physics

Downloaded 17 Oct 2002 to 134.105.248.20. Redistribution subject to AIP license or copyright, see http://ojps.aip.org/aplo/aplcr.jsp

<sup>&</sup>lt;sup>a)</sup>Electronic mail: j.cui@fkf.mpg.de

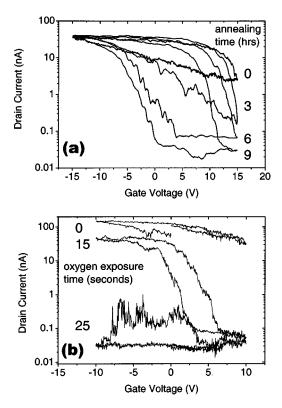

FIG. 2. (a), Evolution of memory effects in a thin SWCNT bundle upon thermal annealing at 335 K in air. The different loops correspond to the data obtained at room temperature with  $V_{\text{bias}}=1 \text{ mV}$  after annealing for 0, 3, 6, and 9 hr, respectively. (b) Memory effects for a thin SWCNT bundle at room temperature after subsequent oxygen plasma treatments. The three curves correspond to the data obtained with  $V_{\text{bias}}=10 \text{ mV}$  after plasma exposure for 0, 15, and 25 s, respectively.

ductance (ON) and low conductance (OFF) states within the SWCNT device is demonstrated in Fig. 1(b). The two stable states at  $V_G = 0$  V can be reproducibly adjusted by triggering the device with the gate voltage signal (varying between  $\pm 5$  V) displayed in the inset. When the devices were held at zero-gate voltage or removed from the sample holder, and stored under ambient conditions, both the ON and OFF state turned out to be stable over a period of at least 12 days.

Memory devices of the same high storage stability could be obtained also from thin SWCNT bundles which consisted of a mixture of semiconducting and metallic tubes, and therefore showed only a weak gate dependence of conductance. For that purpose, two different methods proved to be effective. In the first case, the samples were heated for several hours in air. Figure 2(a) illustrates the evolution of hysteretic behavior of a SWCNT bundle subjected to three annealing steps, performed at 335 K for 3, 6, and 9 h in total, respectively. While before annealing, no clear hysteresis loop was observed within the gate voltage range of  $\pm 15$  V, pronounced memory effects are found after 6 h annealing. The ratio between the current in the ON and OFF state has increased from 10 at the beginning to more than  $10^3$  after 9 h of annealing. It is further noticed that although the OFF current is significantly decreased upon annealing, the ON current remains almost unchanged. Noteworthy, SWCNT bundles revealing similar hysteresis at the beginning as in Fig. 2(a), but annealed in a vacuum ( $p = 10^{-7}$  mbar) at 340 K for 9 hr, displayed only little change in the  $I_D - V_G$  curves.

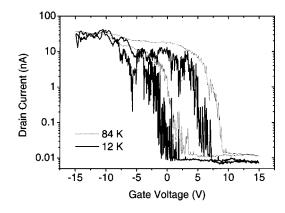

FIG. 3. Low-temperature (84 and 12 K) memory effects in the annealed SWCNT bundle of Fig. 2(a).

treatment at room temperature. Starting from a thin SWCNT bundle with small gate dependence, corresponding to the top curve in Fig. 2(b), a significantly increased gate dependence and hysteresis were obtained after 15 s of oxygen plasma treatment (50 W, oxygen pressure 0.5 mbar). As can be seen from the middle loop, the conductance of the plasma-modified bundle can be modulated via the gate potential over almost three orders of magnitude. For longer plasma treatments, destruction of the nanotubes became apparent. The bottom loop indicates that after 25 s of oxygen plasma exposure, the conductance of the bundle has decreased by more than three orders of magnitude, and no regular hysteresis can be detected any more.

The changes observed in Figs. 2(a) and 2(b) could be explained by two possible effects of the heat treatment in air and the exposure to oxygen plasma. First, the metallic tube(s) within a SWCNT bundle may be preferably oxidized under these conditions, resulting in an increased gate dependence due to the remaining, intact semiconducting tubes. Second, oxidation-related defects are likely to be formed in the remaining amorphous carbon particles on the bundle surface, in the originally intact metallic tubes within a bundle, or at the SiO<sub>2</sub> surface.<sup>15</sup> These types of defects could act as charge storage traps, and their close proximity to the surface of the semiconducting SWCNT(s) would account for the large threshold voltage shifts observed for small gate potentials. Charge carriers injected from the SWCNT(s) into these traps will allow the devices to function similar to electrically erasable, programmable, read-only memories.<sup>18</sup> That such closely attached charge storage units are indeed responsible for the memory effects is supported by electrical measurements at low temperatures. This is exemplified in Fig. 3, which shows data obtained from the same bundle as in Fig. 2(a). Although at 12 K, the threshold voltage shift is reduced by a factor of  $\sim 2$  as compared to room temperature, the switching between the ON and OFF states differing by more than three orders of magnitude in conductance is still existent at lower temperatures. Reproducible switching was detected down to 5 K. It is noticed that the curve measured at 12 K displays numerous sharp peaks originating from singleelectron charging of the tube, which is generally observed at sufficiently low temperatures.<sup>19</sup> The persistence of hysteresis at low temperature excludes that mobile ions within the SiO<sub>2</sub> insulator are the origin of the memory effects, since ion hopping is frozen out at liquid-helium temperature due to the

The second method involves controlled oxygen plasma ping is frozen out at liquid-helium temperature due to the Downloaded 17 Oct 2002 to 134.105.248.20. Redistribution subject to AIP license or copyright, see http://ojps.aip.org/aplo/aplcr.jsp

high associated activation energies in the range of 0.4-0.6 eV.<sup>20</sup> The memory effects observed in the SWCNTs before intentional modification (Fig. 1) may also be related to oxidation-related defects as charge storage sites, in this case, introduced by slow reaction with air at room temperature.

The two presented methods used to fabricate nanoscale memory devices from SWCNT bundles are technologically straightforward, and avoid the need to separate SWCNT bundles from individual SWCNTs during sample preparation. The obtained devices can be reversibly switched between bistable states by small gate potentials, and exhibit a high storage stability of >12 days at room temperature. Although the chemical nature of the modifications deserves further careful investigation, the memory devices represent a significant extension of the range of SWCNT applications. When assembled into large arrays, the SWCNT switching elements could be used as key building blocks for low-cost memories with ultrahigh storage densities. Improved device characteristics may be achieved via more defined SWCNT modifications, for example by chemical attachment of functional groups capable of charge storage.

- <sup>2</sup>M. A. Reed, J. Chen, A. M. Rawlett, D. W. Price, and J. M. Tour, Appl. Phys. Lett. **78**, 3735 (2001).

- <sup>3</sup>J. Chen, M. A. Reed, A. M. Rawlett, and J. M. Tour, Science **286**, 1550 (1999).

- <sup>4</sup>J. Jortner and M. Ratner, *Molecular Electronics* (Blackwell Science, Oxford, 1997).

- <sup>5</sup>J. D. Meindl, Q. Chen, and J. A. Davis, Science **293**, 2044 (2001).

- <sup>6</sup>J. T. Hu, T. W. Odom, and C. M. Lieber, Acc. Chem. Res. **32**, 435 (1999).

- <sup>7</sup>S. J. Tans, A. R. M. Verschueren, and C. Dekker, Nature (London) **393**, 49 (1998).

- <sup>8</sup>K. Liu, M. Burghard, S. Roth, and P. Bernier, Appl. Phys. Lett. **75**, 2494 (1999).

- <sup>9</sup>H. W. C. Postma, T. Teepen, Z. Yao, M. Grifoni, and C. Dekker, Science **293**, 76 (2001).

- <sup>10</sup>J. B. Cui, M. Burghard, and K. Kern, Nano Lett. 2, 117 (2002).

- <sup>11</sup> V. Derycke, R. Martel, J. Appenzeller, and P. Avouris, Nano Lett. 1, 453 (2001).

- <sup>12</sup>X. L. Liu, C. Lee, C. W. Zhou, and J. Han, Appl. Phys. Lett. **79**, 3329 (2001).

- <sup>13</sup>T. W. Tombler, C. W. Zhou, L. Alexseyev, J. Kong, H. J. Dai, L. Lei, C. S. Jayanthi, M. J. Tang, and S. Y. Wu, Nature (London) **405**, 769 (2000).

- <sup>14</sup>T. Rueckes, K. Kim, E. Joselevich, G. Y. Tseng, C. L. Cheung, and C. M. Lieber, Science 289, 94 (2000).

- <sup>15</sup> M. S. Fuhrer, B. M. Kim, T. Durkop, and T. Brintlinger, Nano Lett. 2, 755 (2002).

- <sup>16</sup>M. Radosavljevic, M. Freitag, K. V. Thadani, and A. T. Johnson, Nano Lett. 2, 761 (2002).

- <sup>17</sup> R. Martel, T. Schmidt, H. R. Shea, T. Hertel, and P. Avouris, Appl. Phys. Lett. **73**, 2447 (1998).

- <sup>18</sup>P. Horowitz and W. Hill, *The Art of Electronics* (Cambridge University Press, New York, 1980).

- <sup>19</sup>See, for example, A. Bezryadin, A. R. M. Verschueren, S. J. Tans, and C. Dekker, Phys. Rev. Lett. 80, 4036 (1998).

- <sup>20</sup>G. Greeuw and J. F. Verwey, J. Appl. Phys. 56, 2218 (1984).

<sup>&</sup>lt;sup>1</sup>C. P. Collier, E. W. Wong, M. Belohradsky, F. M. Raymo, J. F. Stoddart, P. J. Kuekes, R. S. Williams, and J. R. Heath, Science **285**, 391 (1999).