# **Purdue University** Purdue e-Pubs

Other Nanotechnology Publications

Birck Nanotechnology Center

2-1-2008

# Carbon nanotubes for high-performance electronics - Progress and prospect

Joerg Appenzeller Birck Nanotechnology Center, Purdue University, appenzeller@purdue.edu

Follow this and additional works at: http://docs.lib.purdue.edu/nanodocs

Part of the Nanoscience and Nanotechnology Commons

Appenzeller, Joerg, "Carbon nanotubes for high-performance electronics - Progress and prospect" (2008). Other Nanotechnology Publications. Paper 171.

http://docs.lib.purdue.edu/nanodocs/171

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# Carbon Nanotubes for **High-Performance Electronics—Progress** and Prospect

The prospect, for nanotube field effect transistors that can compete with silicon technology, is extremely promising but critical tasks still lie ahead.

By J. Appenzeller, Senior Member IEEE

ABSTRACT | Carbon nanotube devices offer intrinsic advantages for high-performance logic device applications. The ultrasmall body of a carbon nanotube—the tube diameter—is the key feature that should allow aggressive channel length scaling, while the intrinsic transport properties of the nanotube ensure at the same time high on-currents. In addition, the narrowness of the tube is critical to implementation of novel device concepts like the tunneling transistor. By understanding the unique capabilities of carbon nanotubes and using them in unconventional designs, novel nanoelectronic applications may become feasible. However, much better control of materials quality must be obtained, and new fabrication processes must be developed before such applications can be realized.

**KEYWORDS** | Carbon nanotube; nanoelectronics; dimensional transport; tunneling device

#### I. INTRODUCTION

With the field of nanoelectronics still in its infancy, the challenges to the realization of practical applications are becoming more obvious. In the past, merely demonstrating the operation of a device was of interest, but attention is beginning to shift toward issues such as performance relative to established devices and technologies. Eventually, practical matters of cost and manufacturability will become central. This is true in particular for carbon

Manuscript received November 2, 2006; revised August 2, 2007. The author is with IBM T.J. Watson Research Center, Yorktown Heights, NY 10598 USA.

Digital Object Identifier: 10.1109/JPROC.2007.911051

nanotubes, which have been extensively explored as electronic materials over the last five years or so. Here we review the current understanding of the promise of carbon nanotubes for electronic applications. We conclude with a brief sketch of some outstanding problems in the development of a practical high-performance carbon nanotube device technology.

We focus on field-effect transistors (FETs) that make use of semiconducting carbon nanotubes as channel material between two metal electrodes that act as source and drain contacts. It is often stated that the smallness of carbon nanotubes should enable high levels of integration. However, to compete with the established silicon device technology, it is important that the new material offer additional advantages such as high speed and low power consumption.

# II. NANOTUBES FOR A HIGH **ON-STATE PERFORMANCE**

In general, switching speeds of FETs can be improved in two distinct ways [1]. The dominant approach, pursued now for many decades, is to reduce the device dimensions. The classical scaling scheme ensures that all fields, the drain as well as the gate field, are scaled simultaneously by adjusting gate-oxide thickness, junction depth, and doping level together with the gate length. The performance improvement in this case is a result of the possibility to reduce the supply voltage without sacrificing the on-state current level. The second approach to improved switching speed is the improvement of material properties, particularly the mobility of electrons and/or holes.

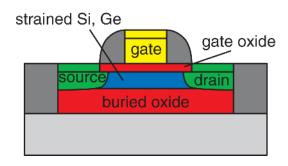

Fig. 1. Schematic of a transport enhanced MOSFET. Through the introduction of strained silicon or germanium higher channel mobilities, and thus a better on-state performance of the device, are achieved.

Interestingly, experience suggests that shrinking conventional semiconductor devices to very small dimensions comes at the expense of a reduced channel mobility. Consider the use of strained silicon or germanium as channel material as sketched in Fig. 1. Reduction of the channel length must be realized while preserving so-called long-channel device characteristics (where the gate field rather than the drain field controls the electrostatics inside the transistor channel). In the past this has been accomplished by simultaneously scaling the gate length  $L_{

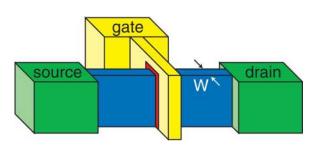

m g}$  and the gate oxide thickness  $t_{ox}$ . But with gate-oxide thicknesses approaching 1 nm, gate leakage currents prevent a further reduction. Although the introduction of new high-dielectricconstant (high-k) gate insulators may help, the most important option left at this point is to reduce the thickness of the channel  $t_{\text{body}}$  itself. This is the reason why ultrathin body devices such as FinFETs (see Fig. 2) have received increasing attention in recent years [2]. However, various studies [3] have shown that reducing the body thickness of the channel comes at the price of a reduced mobility, primarily due to an increase in surface roughness scattering. For a silicon structure with  $t_{\text{body}} \approx 1 \text{ nm}$ , Uchida et al. [4] find, e.g., a mobility reduction by a factor of four in case of an n-type silicon metal-oxide semiconductor (MOS) FET. The same trend is to be expected using

Fig. 2. Sketch of a FinFET structure with the gate impacting the two sides of the fin simultaneously. The important length scale, the "body thickness"  $t_{\rm body}$ , is the width W of the fin.

alternative channel materials that allow for an improved on-state performance in a bulk-type device. So far, it has not been demonstrated that both high mobilities and ultrathin body channels with dimensions of just a few nanometers can be attained in a planar structure.

On the other hand, body thicknesses as small as a few nanometers are indeed desirable from an electrostatics standpoint. The screening length  $\lambda$  derived for a planar gate, planar channel geometry, such as a single-gated MOSFET on silicon on insulator is [5], [6]

$$\lambda = \sqrt{\frac{\varepsilon_{\text{body}} \cdot t_{\text{body}} \cdot t_{\text{ox}}}{\varepsilon_{\text{ox}}}}.$$

(1)

For a body thickness of  $t_{\rm body}=1$  nm,  $t_{\rm ox}=1$  nm and an epsilon ratio of  $\varepsilon_{\rm body}/\varepsilon_{\rm ox}=3$ , one can calculate with the help of (1) a screening length of around  $\lambda=1.5$  nm. With the rule of thumb that the actual gate length should be approximately three times larger than the length scale lambda on which potential variations occur, this should allow  $L_{\rm g}$  to be reduced to around 4.5 nm.

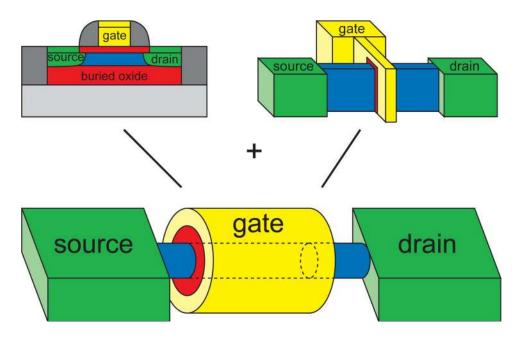

#### A. Optimum Device Design

In the context of the above discussion, carbon nanotubes (CNs) offer an obvious intrinsic advantage. They are the ideal combination of a high mobility, ultrathin body channel if used in a CNFET design as shown in Fig. 3. The figure depicts a coaxially gated CNFET structure—a device that has not been realized experimentally so far but has been simulated extensively [7], [8]. A dielectric film (red) is wrapped around a portion of an undoped semiconducting nanotube. A metal gate (yellow) surrounds the dielectric. Portions of the tube (blue) are ungated to reduce parasitic contributions [9] from the overlap between the gate and the source/drain contacts (green). Those ungated regions have to be heavily doped to allow for a low series resistance in the on-state. (It is worth noting that while doping of carbon nanotubes has been explored by various groups [10]-[13], critical requirements in the context of high-performance devices have still not been met.1) This device design would allow optimum gate control and thus the most aggressive gate length scaling. At the same time, the carbon nanotube ensures through its intrinsic property of ballistic transport over several hundred nanometers at room temperature [14]-[16] and a large carrier velocity of around  $8 \cdot 10^7$  cm/s [17] large currents in the transistor on-state.

While gate-all-around silicon nanowire FETs with excellent performance specs have already been demonstrated [18], [19], experimental demonstration of a

<sup>&</sup>lt;sup>1</sup>For device applications, high doping levels need to be achievable in a controllable and reproducible way. Moreover, dopants need to be immobile, air staible and need to withstand postprocessing at least up to a couple of hundred degrees Celsius.

Fig. 3. Combining the right type of high-mobility channel material with an ultrathin body semiconductor allows for improved on-state performance.

coaxially gated CNFET is still evolving. After the initial demonstration of transistor operation in 1998 [20], [21], more sophisticated device designs with individually gated nanotube transistors and improved device performance were soon reported [22]-[24]. Today's CNFETs reach transconductance values  $g_{\rm m}$  per tube in the 10–20  $\mu S$ range [25], [26] with theoretically predicted values as high as  $\sim 60 \ \mu S$  for reasonably scaled gate capacitances [7]. Since channel widths are only ~1 nm, these transconductances are substantially larger per unit width than those reported in any other material system.

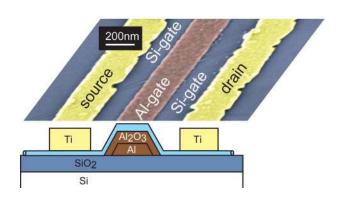

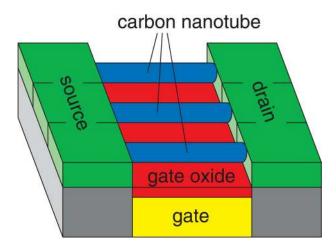

A recent example of a CNFET is shown in Fig. 4. The design that has been adopted with the gate on top of [27]

Fig. 4. Scanning electron microscope of a dual-gate CNFET. Both the silicon substrate and the local aluminum gate allow electrostatic control of the nanotube channel. The schematic below shows the vertical arrangement of gates, contacts, and the nanotube.

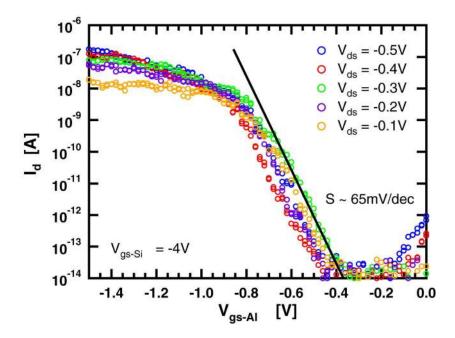

and underneath the nanotube [28], [29] resembles to a large extent the CNFET sketched in Fig. 3. Conventional looking device characteristics are obtained when the silicon gate is biased sufficiently negative (to simulate high p-type doping) and the aluminum gate is swept. Fig. 5 shows the subthreshold characteristics of the dual-gate CNFET with an excellent inverse subthreshold slope of around S = 65 mV/dec. The main difference between the dual gate device and the coaxially gated CNFET is that the latter will ultimately allow for the most aggressive channel length scaling. Consequently, various groups are working on ways to create a uniform dielectric layer around a carbon nanotube [30], [31].

By means of atomic layer deposition, Farmer and Gordon [31] even managed to wrap both a thin aluminum oxide layer and a tungsten nitride metal layer around a carbon nanotube—a critical step towards a coaxially gated CNFET.

#### **B.** Contact Formation in CNFETs

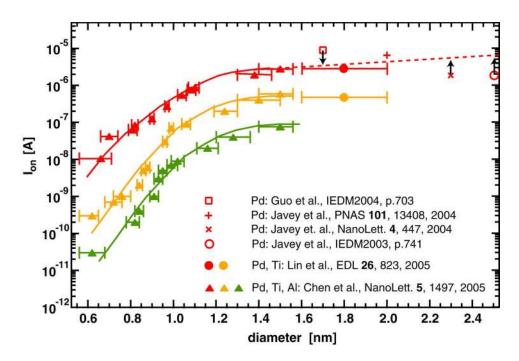

In addition to gate control, it is equally important for high-performance nanotube devices that proper contact formation is ensured. To explore the impact of various contact materials on the CNFET performance, Chen et al. [32] have built around 100 nanotube devices with three different types of metal electrodes. Source/drain contacts from palladium, titanium, and aluminum were used to study the CNFET on-state performance. Interestingly, it was found that despite identical processing, devices with the same type of contact material still exhibited oncurrents  $I_{\text{on}}$  that differed by orders of magnitude. Through

Fig. 5. Subthreshold characteristics of the dual-gate CNFET at room-temperature. The silicon back gate is biased at  $V_{\rm gs-Si} = -4~V$  while the aluminum gate voltage is varied.

Fig. 6. Diameter and workfunction dependence of the CNFET on-current for a variety of samples from different sources.

detailed study of the nanotube diameter distribution by transmission electron microscopy (TEM), the authors were able to separate the impact of the two critical parameters—the tube diameter  $t_{\rm body}$  and the contact metal work function  $\Phi_{\rm M}$ —on the transistor on-current. Fig. 6 summarizes the findings. In the plot,  $I_{\rm on}$  is evaluated at a

supply voltage of  $V_{\rm dd} = 0.5$  V for p-type CNFET devices.<sup>2</sup> Note the two important trends: 1)  $I_{\rm on}$  increases with

<sup>2</sup>It is important to note that nanotube devices without doping and a gate that impacts the entire tube channel, including the contact areas, always show both n-type and p-type behavior at the same time, as is discussed in detail [33].

increasing nanotube diameter  $t_{\text{body}}$  and 2)  $I_{\text{on}}$  increases with increasing  $\Phi_{\rm M}$  ( $\Phi_{\rm Pd} > \Phi_{\rm Ti} > \Phi_{\rm Al}$ ).

Both of the trends can be easily understood within the framework of Schottky barrier dominated transport in CNFETs [34], [35]. The smaller the nanotube bandgap and the larger the workfunction of the metal that is used as contact material, the lower the Schottky barrier at the metal contact/nanotube interface to the valence band. A p-type device exhibits high on-current levels under these conditions. A small bandgap arises for tubes with a large diameter and consequently a larger  $t_{\text{body}}$  results in an increase of  $I_{on}$ . The universal character of the plot becomes apparent when considering that nanotubes from different sources all follow the same trend. Tubes, e.g., produced by means of an arc-discharge [25] generally exhibit diameters of 1.6-2 nm and show a much narrower on-current distribution if used in a field-effect device design than tubes produced by the method of laser ablation [36] with significantly smaller diameters. Electrical data from other groups (see history within Fig. 6) also support the main picture that current variations from device-to-device are less processing related than previously assumed but instead strongly depend on  $t_{\text{body}}$ . The arrows at some of the data points indicate that different gate oxide thicknesses, channel lengths, and/or drain voltages were used for those CNFETs and that the extracted on-currents would have to be corrected accordingly for a fair comparison.

## C. AC Characteristics and Capacitance Considerations

All of the preceding discussion is relevant to the dc performance of CNFETs while it is, of course, the high frequency response that matters. However, measuring the ac performance of CNFETs cannot employ conventional measurement schemes. The input impedance of a nanotube transistor even with ideal contacts is much larger than 50  $\Omega$  and the associated gate capacitance  $C_g$ , typically in the attofarad range, is much smaller than what can be resolved with a conventional measurement setup. At the same time, it is rather challenging to keep parasitic capacitance contributions smaller or comparable to  $C_g$ . This is why the first reports on ac performance of CNFETs did not appear until 2004 [37], [38].

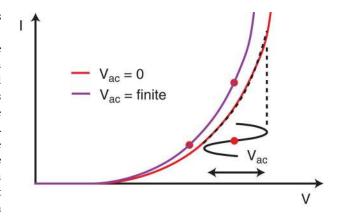

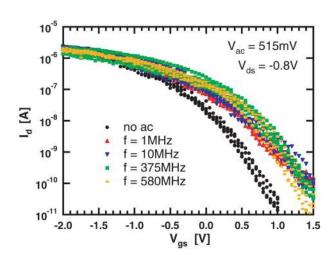

Fig. 7 illustrates how these measurements were performed in a rather unconventional way. The idea is that the dc current of a device can be impacted by an ac voltage contribution if the associated IV-characteristic is nonlinear. Applying a voltage Vac effectively results in a larger measurable dc current I. This is true as long as the corresponding ac signal can propagate inside the device structure. Observing the dc signal of an FET structure can thus provide insights into its ac performance. Fig. 8 shows an actual measurement of the current change as a function of the gate voltage  $V_{\rm gs}$  for different frequencies. The ac signal is applied to the source of the CNFET.

Fig. 7. The graph illustrates how an ac voltage  $V_{\rm ac}$  superimposed on a dc bias V results in a measurable change of the dc current signal for nonlinear device characteristics.

Between 1 and 580 MHz, the curves all show effectively the same change in  $I_d$ . Up to this frequency, the device operates without any signal deterioration that would result in a decrease of the device current level towards the curve labelled "no ac." The maximum reported frequency of 580 MHz measured with this approach is limited by the measurement setup and not the intrinsic tube properties.

Progress after this initial demonstration has been rapid. Measurements with a frequency up to 2.6 [39], 8 [40], 12 [41] (note that both semiconducting and metallic nanotubes contributed), and 50 GHz [42] have been reported. However, experimental data still do not reach the predicted terahertz performance range [43]. At this time, there is still a strong need to obtain further information about the intrinsic ac performance limits of CNFETs.

Fig. 8. Actual measurement on the ac response of a carbon nanotube transistor.

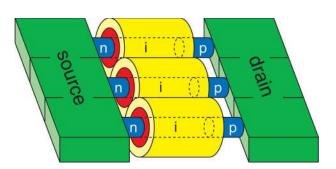

Fig. 9. Schematics of a gated array of carbon nanotubes. The total current is enhanced by utilizing several nanotubes in parallel.

A device geometry that would be desirable in this context is sketched in Fig. 9. By using several nanotubes in parallel, the sample impedance is reduced while the total gate capacitance is increased. If the device layout ensures at the same time that parasitic capacitance contributions are not too large, a structure as shown will prove useful in a more conventional S-parameter measurement. More details about current key problems and envisioned solutions are addressed in the later sections.

#### D. A CNFET-Based Ring Oscillator

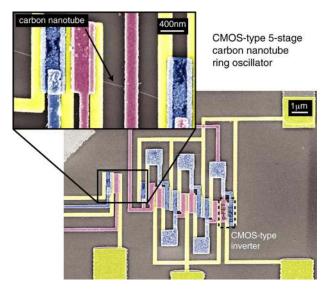

The fabrication of circuits is an important benchmark in the development of carbon nanotube devices. In 2006,

Fig. 10. Implementation of a CMOS-type five-stage ring oscillator on a single carbon nanotube.

Chen *et al.* [44] demonstrated the first complete circuit on one individual carbon nanotube. The circuit, a ring oscillator, that is shown in Fig. 10 consists of 12 individual nanotube transistors, with six of them operating as p-type FETs (purple colored gates) and six as n-type FETs (blue colored gates).

Five pairs of p- and n-CNFETs are used to create the five inverter stages. The sixth inverter (marked by the dashed square in Fig. 10) operates as a readout stage. The signal from this inverter is input into a spectrum analyzer to monitor the frequency response of the ring oscillator (RO). The main breakthrough that made this application possible is again related to the unique properties of nanotubes. As has been discussed in Section II-B, the metal workfunction of the source/drain electrode can substantially impact the device on-state by means of the metal Fermi level lineup with the semiconducting nanotube. For the ring oscillator, the same property was employed to adjust the threshold voltage of the p-type and n-type FETs. By using two types of metal gates, palladium and aluminum, one segment of the same undoped nanotube was used as a p-type CNFET while the other one operates as an n-type CNFET. Since dopant fluctuations in the channel of conventional silicon devices can become a serious issue for scaled FETs, adjusting the device characteristics without the introduction of dopants is desirable. A one-dimensional system as a nanotube does not suffer from surface state pinning [45], and the impact of the metal gate workfunction directly translates into a threshold voltage shift of the CNFET device characteristics, as has been experimentally demonstrated in the context of the RO for the first time.

The spectrum measured with the CNFET ring oscillator showed a frequency response up to 72 MHz [46]. While this result is still far below the expected intrinsic response of nanotubes as discussed in Section II-C, it is quantitatively understandable exclusively as a result of the circuit layout. Taking into account the build-in parasitic contributions due to wiring and gate-to-source/drain overlap as well as the circuit-to-substrate capacitance, the expected frequency response can indeed not exceed the measured value. The intrinsic nanotube properties are thus not limiting the circuit performance at this point in time, and an improved circuit layout can be expected to substantially improve the ac performance of next-generation nanotube-based circuits.

# III. NANOTUBE DEVICE CONSIDERATIONS FOR REDUCED POWER CONSUMPTION

Having discussed the on-state performance of CNFETs in the previous sections, this section focuses on device designs for reduced power consumption. It is once more the particular transport in nanotubes that lends itself to a novel type of device concept. As discussed in Section II, the screening length  $\lambda$  can be on the order of nanometers in carbon nanotubes due to their small body thickness—the nanotube diameter. Since band-bending occurs on the length scale of  $\lambda$ , potential barriers in nanotube-based devices are typically very thin, and tunneling phenomena are very pronounced in all types of CNFETs [47]. While in most instances rather undesirable, the device concept described below makes explicit use of the tunneling properties in CNFETs.

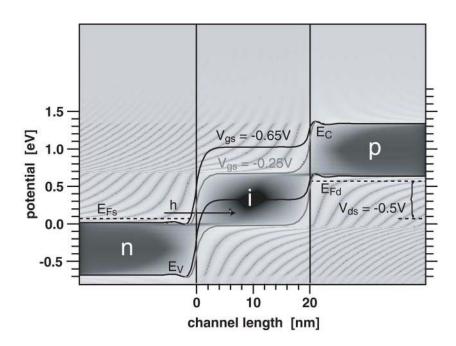

The transistor structure that enables the so-called tunneling CNFET (T-CNFET) consists of a sequence of n-type, intrinsic, and p-type doping, as illustrated in Fig. 11, and has been proposed recently as a viable device concept for carbon nanotubes [47], [48]. Its operation can be understood as follows: the device is in its off-state if the gated intrinsic portion of the nanotube prevents current flow between the two highly doped areas (n-type on the left and p-type on the right). This is the case for  $V_{

m gs} = -0.25 \;

m V$ , half of the applied drain voltage of  $V_{\rm ds} = -0.5$  V, as displayed in Fig. 11. The device turns on for more negative drain voltages. At  $V_{\rm gs} = -0.65\,$  V, for example, the intrinsic portion of the semiconducting tube is moved sufficiently upwards to allow for hole injection from the n-type region of the nanotube by band-to-band (BTB) tunneling into the intrinsic part indicated by the arrow in Fig. 11.

The most important aspect is that the transition between the device on-state and off-state is accomplished with a change of gate voltage  $\Delta V_{\rm gs}$  that is smaller than what is needed for a conventional MOSFET to change the current by the same amount. In other words, the inverse subthreshold slope S is smaller than ~60 mV/dec at room temperature. This becomes possible since the device offstate is no longer determined by the electrons or holes in the high energetic tail of the Fermi distribution as in conventional MOSFETs. In fact, the high energetic charges get back-reflected into the source while the carriers close to the Fermi level are most relevant for the band-to-band tunneling process. This effective "cooling" of the electronic system is the key for obtaining small S-values. While in principle, by utilizing BTB-tunneling, S-values smaller than 60 mV/dec are also achievable in silicon MOSFET [49], experimentally this situation has not yet been realized [50], [51]. Carbon nanotubes, on the other hand, offer the ideal combination of intrinsic properties such as ballistic transport, ultrasmall  $t_{\text{body}}$ , small effective masses for electrons and holes, and a direct energy bandgap to make gate-controlled tunneling a highly effective concept for T-CNFETs.

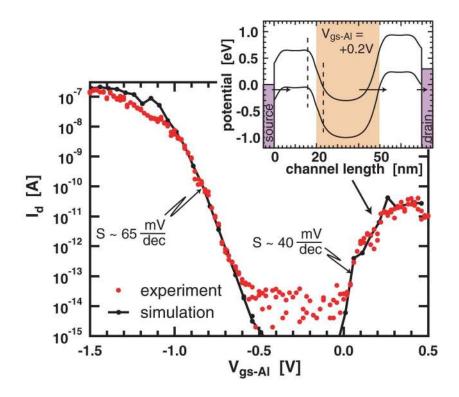

Experimentally, this n/i/p doping profile has not yet been demonstrated in a T-CNFET configuration. However, experimental evidence for the possibility to obtain inverse subthreshold slopes smaller than  $\sim$ 60 mV/dec has been obtained recently [52]. The nanotube device structure employed for this is shown in Fig. 4. By using the silicon back gate to effectively dope the nanotube segments close to the metal electrodes, a p/i/p doping profile is implemented. Scanning the voltage  $(V_{gs-Al})$  at the aluminum gate in the middle of the device structure, a subthreshold characteristic as shown in Fig. 12 is obtained.

Fig. 11. Simulation of the conduction and valence band for a T-CNFET at V $_{

m ds}=-0.5$  V for two different gate voltages of  $m{V}_{

m gs} = -0.65$  V (on-state) and -0.25 V (off-state), respectively. The parameter set used for the calculation is E  $_{

m g} = 0.7\,$  eV,  $oldsymbol{t}_{

m ox} =$  1 nm,  $oldsymbol{t}_{

m body} =$  1 nm, and  $oldsymbol{m}^* =$  0.1  $oldsymbol{m}_0$ .

Fig. 12. Experimental and simulated  $I_{\rm d}(v_{\rm gs-Al})$  for a drain voltage of  $v_{\rm ds}=-0.5$  V and  $v_{\rm gs-Si}=-3$  V. The upper inset shows the band bending situation under tunneling conditions from the simulation.

The red circles in Fig. 12 are data taken at room temperature. At negative  $V_{\mathrm{gs-Al}}$  values, the device operates as a conventional p-type FET in the on-state. Increasing the aluminum gate voltage (making it more positive) turns the device off, similar to the situation in a conventional MOSFET. For even larger  $V_{gs-Al}$ , the band-to-band tunneling conditions displayed in the upper inset of the figure are reached. Holes injected from the source undergo two BTB-tunneling events before reaching the drain electrode. The crucial finding is that it is indeed possible in a gate-controlled tunneling process to obtain an inverse subthreshold slope substantially smaller than ~60 mV/ dec-a proof of principle that the proposed T-CNFET concept is indeed a viable approach. In the displayed case,  $S \approx 40 \text{ mV/dec}$  has been achieved.<sup>3</sup> Moreover, Fig. 12 also shows the result of our simulations [52].

Simulations in Figs. 11 and 12 were carried out using the nonequilibrium Green's function (NEGF) formalism [54]. The charge in and current through the transistor are calculated self-consistently using the NEGF formalism together with a modified one-dimensional (1-D) Poisson equation according to Young [6]. The 1-D Poisson equation accounts for the impact of gate oxide thickness  $t_{\rm ox}$  and tube diameter  $t_{\rm body}$  on the electrostatics conditions inside the

nanotube channel. An effective mass description is adopted for the conduction and valence band, and the complex band structure in the semiconducting nanotube gap is taken into account by an energy-dependent effective mass [55]. For channel lengths below a couple of hundred nanometers, it is appropriate to assume ballistic transport conditions. Despite the fact that this approach simplifies the actual situation, excellent quantitative agreement between experiment and simulation is achieved, as apparent from Fig. 12. This indicates in particular that the main aspect of the tunneling device is indeed captured by the simulation.

Fig. 13. Schematic of an array of coaxially gated T-CNFETs as envisioned for low power consumption applications. The parallel tube array ensures that reasonable current levels are attained.

<sup>&</sup>lt;sup>3</sup>After submission of this manuscript, we became aware of a recently published paper [53] that demonstrated a T-CNFET exhibiting an S-value of 25 mV/dec.

The next important step is to combine the abrupt switching behavior through gate-controlled tunneling with a high on-current level in the device. While tunneling processes typically do not allow for a high transistor onstate performance, the intrinsic properties of nanotubes discussed above—in particular the small achievable value of  $\lambda$ —ensure reasonable currents per unit width [47]. Further increasing  $I_d$  is achievable by means of an array of FETs, as discussed in Section II-C. Fig. 13 shows a schematic of the envisioned array of T-CNFETs with the desirable n/i/p doping profile. For most aggressive length scaling, a coaxially gated transistor structure is used according to Section II-A.

## IV. FUTURE PROSPECTS AND KEY PROBLEMS

With such promising results obtained in exploratory devices, it is time to consider the very difficult challenges that must still be met in order to fabricate practical highperformance devices and circuits. Indeed, many of the processes needed to build the preferred device structures sketched above simply do not exist, or exist in only rudimentary form. Great improvements and further invention will be needed in:

- growth and placement:

- controlled synthesis of nanotubes of given diameter and chirality or postgrowth separation of nanotubes by diameter and chirality;

- lithographically templated placement of nanotubes;

- enabling processes and technologies: 2)

- conformal deposition of ultrathin high-k dielectrics on nanotubes;

- charge-transfer doping of nanotubes with a high degree of degeneracy;

- devices and circuits:

- development of low power circuits based on nanotubes' unique tunneling properties;

- integration of nanotubes in circuit architectures that consider their one-dimensional character.

For example, all existing processes for synthesis or growth of nanotubes produce tubes with a range of diameters and chiralities. Unless far more selective growth processes can be developed (along the lines of recent progress [56], [57]), the starting material will have to be purified. Progress in purification is being reported [58]-[61], giving hope that "electronic grade" nanotubes will eventually be available. Progress is also being made in chemical functionalization of nanotubes so that they will attach preferentially to lithographically patterned structures [62]-[65]. However, there is still a gulf between these promising early results and the extremely tight control of placement that would be needed to build a structure like that of Fig. 13. Moreover, devices as those displayed in Fig. 13 require a very tight gate control through ultrathin high-k gate dielectrics and extremely abrupt doping profiles. Further progress along the lines of the existing work discussed in Section II-A is urgently needed. Lastly, the various device ideas and considerations have to be translated into actual nanotube-based circuits. Those circuits should make use of existing architectures to the largest possible extent while at the same time benefiting from the unique nanotube properties. The ring oscillator design discussed above [44], [46] is just the first step in this direction.

#### V. SUMMARY

The discussion in the previous sections clearly highlights the uniqueness of carbon nanotubes for transistor applications. Both the demonstrated as well as predicted on- and off-state performance of tube-based devices is extremely promising. Tasks ahead that will have an immediate impact on nanotube devices are related to an improved control of doping profiles and the formation of arrays of CNFETs. The coaxially gated nanotube transistor is certainly one of the most critical demonstrations on the device level that is missing at this point in time. With future activities focusing more on the aspect of ac transport in carbon nanotube devices and circuit applications, critical insights will certainly become available in the near future. Lastly, it is worth noting that most of the findings discussed in the previous sections on logic also apply to analog applications, and the smaller amount of transistors needed for analog circuits may facilitate implementation. ■

#### REFERENCES

- [1] International technology roadmap for semiconductors, San Jose, CA, 2004. [Online]. Available: http://www.itrs.net/ Links/2004Update/2004\_05\_ERD.pdf

- [2] J. Kedzierski, P. Xuan, E. H. Anderson, J. Bokor, T. King, and C. Hu, "Complementary silicide source/drain thin-body MOSFETs for the 20 nm gate length regime," in IEDM Tech. Dig., 2000, pp. 57-60.

- [3] K. Uchida, H. Watanabe, A. Kinoshita, J. Koga, T. Numata, and S. Takagi, "Experimental study on carrier transport

- mechanism in ultrathin-body SOI n- and p-MOSFETs with SOI thickness less that 5 nm," in IEDM Tech. Dig., 2002, pp. 47-50.

- [4] K. Uchida, J. Koga, and S. Takagi, "Experimental study on carrier transport mechanisms in double- and single-gate ultrathin-body MOSFETs," in IEDM Tech. Dig., 2003, pp. 805-808.

- [5] R.-H. Yan, A. Ourmazd, and K. F. Lee, 'Scaling the Si MOSFET: From bulk to SOI to bulk," IEEE Trans. Electron Devices, vol. 39, pp. 1704-1710, 1992.

- [6] K. Young, "Short-channel effect in fully-depleted SOI MOSFETs," IEEE Trans. Electron Devices, vol. 36, pp. 399-402, 1989.

- [7] J. Guo, M. Lundstrom, and S. Datta, "Performance projections for ballistic carbon nanotube field-effect transistors," Appl. Phys. Lett., vol. 80, pp. 3192-3194, 2002.

- [8] J. P. Clifford, D. L. John, L. C. Castro, and D. L. Pulfrey, "Electrostatics of partially gated carbon nanotube FETs," IEEE Trans. Nanotechnol., vol. 3, pp. 281-286, 2004.

- [9] D. L. John and D. L. Pulfrey, 'Switching-speed calculations for Schottky-barrier carbon nanotube field-effect transistors," J. Vac. Sci. Technol. A, vol. 24, pp. 708-712, 2006.

- [10] M. Bockrath, J. Hone, A. Zettl, P. L. McEuen, A. G. Rinzler, and R. E. Smalley, "Chemical

- doping of individual semiconducting carbon nanotube ropes," *Phys. Rev. B*, vol. 61, pp. R10606–R10608, 2000.

- [11] M. Shim, A. Javey, N. W. S. Kam, and H. Dai, "Polymer functionalization for airstable n-type carbon nanotube field-effect transistors," *J. Amer. Chem. Soc.*, vol. 123, pp. 11 512–11 513, 2001.

- [12] V. Derycke, R. Martel, J. Appenzeller, and P. Avouris, "Cotrolling doping and carrier injection in carbon nanotube transistors," Appl. Phys. Lett., vol. 80, pp. 2773–2775, 2002.

- [13] J. Chen, C. Klinke, A. Afzali, K. Chan, and P. Avouris, "Self-aligned carbon nanotube transistors with novel chemical doping," in *IEDM Tech. Dig.*, 2004, pp. 695–698.

- [14] S. Wind, J. Appenzeller, and P. Avouris, "Lateral scaling in carbon nanotube field-effect transistors," *Phys. Rev. Lett.*, vol. 91, pp. 058301-1–058301-4, 2003.

- [15] A. Javey, J. Guo, Q. Wang, M. Lundstrom, and H. Dai, "Ballistic carbon nanotube field-effect transistors," *Nature*, vol. 424, pp. 654–657, 2003.

- [16] T. Dürkop, S. A. Getty, E. Cobas, and M. S. Fuhrer, "Extraordinary mobility in semiconducting carbon nanotubes," *Nano Lett.*, vol. 4, pp. 35–39, 2004.

- [17] M. S. Dresselhaus, G. Dresselhaus, and P. Avouris, Carbon Nanotubes: Synthesis, Structure, Properties, and Applications. Berlin, Germany: Springer-Verlag, 2001.

- [18] K. H. Yeo et al., "Gate-all-around (GAA) twin silicon nanowire MOSFET (TSNWFET) with 15 nm length gate and 4 nm radius nanowires," in *IEDM Tech. Dig.*, 2006, pp. 539–542.

- [19] N. Singh et al., "Ultra-narrow silicon nanowire gate-all-around CMOS devices: Impact of diameter, channel orientation and low temperature on device performance," in IEDM Tech. Dig., 2006, pp. 547–550.

- [20] S. J. Tans, A. Verschueren, and C. Dekker, "Room-temperature transistor based on a single carbon nanotube," *Nature*, vol. 393, pp. 49–51, 1998.

- [21] R. Martel, T. Schmidt, H. R. Shea, T. Hertel, and P. Avouris, "Single- and multi-wall carbon nanotube field-effect transistors," Appl. Phys. Lett., vol. 73, pp. 2447–2449, 1998.

- [22] A. Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, "Logic circuits with carbon nanotube transistors," *Science*, vol. 294, pp. 1317–1320, 2001.

- [23] A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen, M. Lundstrom, and H. Dai, "High-k dielectric for advanced carbon-nanotube transistors and logic gates," *Nature Mater.*, vol. 1, pp. 241–246, 2002.

- [24] S. Wind, J. Appenzeller, R. Martel, V. Derycke, and P. Avouris, "Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes," Appl. Phys. Lett., vol. 80, pp. 3817–3819, 2002.

- [25] Y.-M. Lin, J. Appenzeller, Z. Chen, Z.-G. Chen, H.-M. Cheng, and P. Avouris, "High performance dual-gate carbon nanotube FETs with 40-nm gate length," *IEEE Electron Device Lett.*, vol. 26, pp. 823–825, 2005.

- [26] A. Javey, J. Guo, D. B. Farmer, Q. Wang, E. Yenilmez, R. G. Gordon, M. Lundstrom, and H. Dai, "Self-aligned ballistic molecular transistors and electrically parallel nanotube arrays," *Nano Lett.*, vol. 4, pp. 1319–1322, 2004.

- [27] A. Javey, J. Guo, B. Farmer, Q. Wang, D. Wang, R. G. Gordon, and M. Lundstrom, and H. Dai, "Carbon nanotube field-effect transistors with integrated ohmic contacts and high-k gate dielectrics," *Nano Lett.*, vol. 4, pp. 47–450, 2004.

- [28] Y.-M. Lin, J. Appenzeller, and P. Avouris, "Novel structures enabling bulk switching in carbon nanotube FETs," in *Proc. 62th Device Res. Conf.*, 2004, pp. 133–134.

- [29] Y.-M. Lin, J. Appenzeller, J. Knoch, and P. Avouris, "High-performance carbon nanotube field-effect transistor with tunable polarity," *IEEE Trans. Nanotechnol.*, vol. 4, pp. 481–489, 2005.

- [30] Y. Lu, S. Bangsaruntip, X. Wang, L. Zhang, Y. Nishi, and H. Dai, "DNA functionalization of carbon nanotubes for ultrathin atomic layer deposition of high k dielectrics for nanotube transistors with 60 mV/decade switching," J. Amer. Chem. Soc., vol. 128, pp. 3518–3519, 2006.

- [31] D. B. Farmer and R. G. Gordon, "Atomic layer deposition on suspended single-walled carbon nanotubes via gas-phase noncovalent functionalization," *Nano Lett.*, vol. 6, pp. 699–703, 2006.

- [32] Z. Chen, J. Appenzeller, J. Knoch, Y.-M. Lin, and P. Avouris, "The role of metal-nanotube contact in the performance of carbon nanotube field-effect transistors," *Nano Lett.*, vol. 5, pp. 1497–1502, 2005.

- [33] M. Radosavljevic, S. Heinze, J. Tersoff, and Ph. Avouris, "Drain voltage scaling in carbon nanotube transistors," Appl. Phys. Lett., vol. 83, pp. 2435–2438, 2003.

- [34] S. Heinze, J. Tersoff, R. Martel, V. Derycke, J. Appenzeller, and P. Avouris, "Carbon nanotubes as Schottky barrier transistors," Phys. Rev. Lett., vol. 89, pp. 106801-1–106801-4, 2002.

- [35] J. Appenzeller, J. Knoch, V. Derycke, R. Martel, S. Wind, and P. Avouris, "Field-modulated carrier transport in carbon nanotube transistors," *Phys. Rev. Lett.*, vol. 89, pp. 126801-1–126801-4, 2002.

- [36] A. Thess, R. Lee, P. Nikolaev, H. Dai, P. Petit, J. Robert, C. Xu, Y. H. Lee, S. G. Kim, A. G. Rinzler, D. T. Colbert, G. E. Scuseria, D. Tomanek, J. E. Fischer, and R. E. Smalley, "Crystalline ropes of metallic carbon nanotubes," *Science*, vol. 273, pp. 483–487, 1996.

- [37] J. Appenzeller and D. J. Frank, "Frequency dependent characterization of transport properties in carbon nanotube transistors," Appl. Phys. Lett., vol. 84, pp. 1771–1773, 2004.

- [38] D. J. Frank and J. Appenzeller, "High frequency response in carbon nanotube field-effect-transistors," *IEEE Electron Device* Lett., vol. 25, pp. 34–36, 2004.

- [39] S. D. Li, Z. Yu, S. F. Yen, W. C. Tang, and P. J. Burke, "Carbon nanotube transistor operation at 2.6 GHz," *Nano Lett.*, vol. 4, pp. 753–756, 2004.

- [40] J.-M. Bethoux, H. Happy, G. Dambrine, V. Derycke, M. Goffman, and J.-P. Bourgoin, "An 8-GHz f<sub>t</sub> carbon nanotube field-effect transistor for gigahertz range applications," *IEEE Electron Device Lett.*, vol. 27, pp. 681–683, 2006.

- [41] X. Huo, M. Zhang, P. C. H. Chan, Q. Liang, and Z. K. Tang, "High frequency S parameters characterization of back-gate carbon nanotube field-effect transistors," in *IEDM Tech. Dig.*, 2004, pp. 691–694.

- [42] S. Rosenblatt, H. Lin, V. Sazonova, S. Tiwari, and P. L. McEuen, "Mixing at 50 GHz using a single-walled carbon nanotube transistor,"

- Appl. Phys. Lett., vol. 87, pp. 153 111–153 113, 2005.

- [43] L. C. Castro, D. L. John, D. L. Pulfrey, M. Pourfath, A. Gehring, and H. Kosina, "Method for predicting f<sub>T</sub> for carbon nanotube FETs," *IEEE Trans. Nanotechnol.*, vol. 4, pp. 699–704, 2005.

- [44] Z. Chen, J. Appenzeller, Y.-M. Lin, J. S. Oakley, A. G. Rinzler, J. Tang, S. Wind, P. Solomon, and P. Avouris, "An integrated logic circuit assembled on a single carbon nanotube," *Science*, vol. 311, p. 1735, 2006.

- [45] F. Leonard and J. Tersoff, "Role of Fermi-level pinning in nanotube Schottky diodes," *Phys. Rev. Lett.*, vol. 84, pp. 4693–4696, 2000.

- [46] Z. Chen, J. Appenzeller, P. M. Solomon, Y.-M. Lin, and P. Avouris, "High performance carbon nanotube ring oscillator," in *Proc. 64th Device Res. Conf.*, 2006, pp. 171–172.

- [47] J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, "Comparing carbon nanotube transistors—The ideal choice: A novel tunneling device design," *IEEE Trans. Electron Devices*, vol. 52, pp. 2568–2576, 2005.

- [48] S. O. Koswatta, D. E. Nikonov, and M. S. Lundstrom, "Computational study of carbon nanotube p-i-n tunneling FETs," in IEDM Tech. Dig., 2005, pp. 525–528.

- [49] K. K. Bhuwalka, J. Schulze, and I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the δp<sup>+</sup> layer," Jpn. J. Appl. Phys., vol. 43, pp. 4073–4078, 2004.

- [50] W. Hansch, P. Borthen, J. Schulze, C. Fink, T. Sulima, and I. Eisele, "Performance improvement in vertical surface tunneling transistors by a boron surface phase," *Jpn. J. Appl. Phys.*, vol. 40, pp. 3131–3136, 2001.

- [51] K. K. Bhuwalka, S. Sedlmaier, A. K. Ludsteck, C. Tolksdorf, J. Schulze, and I. Eisele, "Vertical tunnel field-effect transistor," *IEEE Trans. Electron Devices*, vol. 51, pp. 279–282, 2004.

- [52] J. Appenzeller, Y.-M. Lin, J. Knoch, and P. Avouris, "Band-to-band tunneling in carbon nanotube field-effect transistors," *Phys. Rev. Lett.*, vol. 93, pp. 196805-1–196805-4, 2004.

- [53] Zhang et al., "Carbon nanotubes: From growth, placement and assembly control to 60mV/ decade and sub-60mV/decade tunnel transistors," IEDM Tech. Dig., 2006, pp. 431–434.

- [54] S. Datta, Electronic Transport in Mesoscopic Systems. Cambridge, U.K.: Cambridge Univ. Press, 1998.

- [55] H. Flietner, "The E(k) relation for a two-band scheme of semiconductors and the application to the metal-semiconductor contact," *Phys. Stat. Sol.*, vol. 54, p. 201, 1972.

- [56] S. M. Bachilo, L. Balzano, J. E. Herrera, F. Pompeo, D. E. Resasco, and R. B. Weisman, "Narrow (n,m)-distribution of single-walled carbon nanotubes grown using a solid supported catalyst," J. Amer. Chem. Soc., vol. 125, p. 11 186, 2003.

- [57] Y. M. Li, D. Mann, M. Rolandi, W. Kim, A. Ural, S. Hung, A. Javey, J. Cao, D. W. Wang, E. Yenilmez, Q. Wang, J. F. Gibbons, Y. Nishi, and H. Dai, "Preferential growth of semiconducting single-wall carbon nanotubes by a plasma enhanced CVD method," *Nano Lett.*, vol. 4, p. 317, 2004.

- [58] Z. Chen, X. Du, M.-H. Du, C. D. Rancken, H.-P. Cheng, and A. G. Rinzler, "Bulk separative enrichment in metallic or semiconducting single-walled carbon nanotubes," *Nano Lett.*, vol. 3, pp. 1245–1249, 2003.

- [59] R. Krupke, F. Heinrich, M. M. Kappes, and H. V. Lohneysen, "Surface conductance induced dielectrophoresis of semiconducting

- single-walled carbon nanotubes," Nano Lett., vol. 4, pp. 1395-1399, 2004.

- [60] H. Q. Peng, N. T. Alvarez, C. Kittrell, R. H. Hauge, and H. K. Schmidt, "Dielectrophoresis field flow fractionation of single-walled carbon nanotubes," J. Amer. Chem. Soc., vol. 128, pp. 8396-8397, 2006.

- [61] M. S. Arnold, A. A. Green, J. F. Hulvat, S. I. Stupp, and M. C. Hersam, "Sorting carbon nanotubes by electronic structure using density differentiation," Nature Nanotechnol., vol. 1, pp. 60-65, 2006.

- [62] J. Liu et al., "Controlled deposition of individual single-walled carbon nanotubes on chemically functionalized templates," Chem. Phys. Lett., vol. 303, pp. 125-129, 1999.

- [63] K. Keren, R. S. Berman, E. Buchstab, U. Sivan, and E. Braun, "DNA-templated carbon nanotube field-effect transistor," Science, vol. 302, pp. 1380-1382, 2003.

- [64] J. B. Hannon, A. Afzali, C. Klinke, and P. Avouris, "Selective placement of carbon nanotubes on metal-oxide surfaces, Langmuir, vol. 21, pp. 8569-8571, 2005.

- [65] C. Klinke, J. B. Hannon, A. Afzali, and P. Avouris, "Field-effect transistors assembled from functionalized carbon nanotubes," Nano Lett., vol. 6, pp. 906-910, 2006.

#### ABOUT THE AUTHOR

J. Appenzeller (Senior Member, IEEE) received the M.S. and Ph.D. degrees in physics from the Technical University of Aachen, Germany, in 1991 and 1995, respectively.

His Ph.D. dissertation investigated quantum transport phenomena in low-dimensional systems based on III/V heterostructures. He spent one year as a Research Scientist with the Research Center, Juelich, Germany, before he became an Assistant Professor with the Technical University of Aachen in 1996. During his professorship he explored mesoscopic electron transport in different materials, including carbon nanotubes and

superconductor-semiconductor hybrid devices. From 1998 to 1999, he was with the Massachusetts Institute of Technology, Cambridge, as a Visiting Scientist, exploring the ultimate scaling limits of silicon MOSFET devices. From 2001 to 2007, he was with the IBM T.J. Watson Research Center, Yorktown, NY, as a Research Staff Member mainly involved in the investigation of the potential of carbon nanotubes and silicon nanowires for a future nanoelectronics. Since 2007, he has been a Professor of electrical and computer engineering at Purdue University, West Lafayette, IN, and Scientific Director of nanoelectronics with the Birck Nanotechnology Center. His current interests include novel devices based on low-dimensional nanomaterials as nanowires, nanotubes, and graphene.