## CASCADED MULTILEVEL CONVERTER BASED TRANSMISSION STATCOM: SYSTEM DESIGN METHODOLOGY AND DEVELOPMENT OF A $12 \mathrm{kV} \pm 12 \mathrm{MVAr}$ POWER-STAGE

# A THESIS SUBMITTED TO THE GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES OF MIDDLE EAST TECHNICAL UNIVERSITY

BY

#### BURHAN GÜLTEKİN

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR

THE DEGREE OF DOCTOR OF PHILOSOPHY

IN

ELECTRICAL AND ELECTRONICS ENGINEERING

### Approval of the thesis

## CASCADED MULTILEVEL CONVERTER BASED TRANSMISSION STATCOM: SYSTEM DESIGN METHODOLOGY AND DEVELOPMENT OF A 12kV ±12MVAr POWER-STAGE

submitted by **BURHAN GÜLTEKİN** in partial fulfillment of the requirements for the degree of **Doctor of Philosophy in Electrical and Electronics Engineering Department, Middle East Technical University** by,

| Prof. Dr. Canan ÖZGEN  Dean, Graduate School of <b>Natural and Applied Sciences</b> |  |

|-------------------------------------------------------------------------------------|--|

| Prof. Dr. İsmet ERKMEN  Head of Department, Electrical and Electronics Engineering  |  |

| Prof. Dr. Muammer ERMİŞ Supervisor, Electrical and Electronics Engineering          |  |

| Examining Committee Members :                                                       |  |

| Prof. Dr. H. Bülent ERTAN  Electrical and Electronics Engineering, METU             |  |

| Prof. Dr. Muammer ERMİŞ Electrical and Electronics Engineering, METU                |  |

| Prof. Dr. Işık ÇADIRCI Electrical and Electronics Engineering, Hacettepe University |  |

| Prof. Dr. Aydın ERSAK Electrical and Electronics Engineering, METU                  |  |

| Prof. Dr.Arif ERTAŞ  Electrical and Electronics Engineering, METU  Date: 14-09-2012 |  |

| presented in accordance v | vith academic rules a<br>e rules and conduct, | and eth<br>I have | ent has been obtained and ical conduct. I also declare fully cited and referenced ork. |

|---------------------------|-----------------------------------------------|-------------------|----------------------------------------------------------------------------------------|

|                           |                                               |                   |                                                                                        |

|                           | Name, Last name                               | :                 | Burhan GÜLTEKİN                                                                        |

|                           | Signature                                     | :                 |                                                                                        |

|                           | iii                                           |                   |                                                                                        |

|                           |                                               |                   |                                                                                        |

## **ABSTRACT**

CASCADED MULTILEVEL CONVERTER BASED TRANSMISSION STATCOM: SYSTEM DESIGN METHODOLOGY AND DEVELOPMENT OF A 12kV ±12MVAr POWER-STAGE

GÜLTEKİN, Burhan

Ph.D., Department of Electrical and Electronics Engineering

Supervisor : Prof. Dr. Muammer ERMİŞ

September 2012, 177 pages

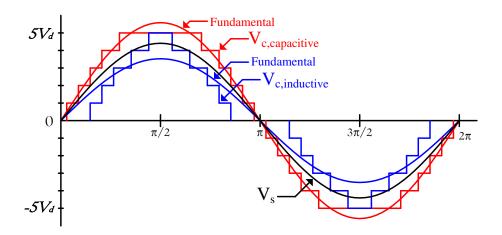

This research and development work deals with the design methodology for Cascaded Multilevel Converter (CMC) based Transmission STATCOM (T-STATCOM) and development of a ±12MVAR, 12kV line-to-line wye-connected, 11-level CMC. This CMC module constitutes the basic building block of T-STATCOM systems. Sizing of the CMC module, number of H-Bridges in each phase of the CMC, AC voltage rating of the CMC, the number of paralleled CMC modules in the T-STATCOM system, optimum value of series filter reactors and determination of busbar in the power grid to which the T-STATCOM system is going to be connected are also discussed in the thesis in view of IEEE Std.519-1992, current status of HV IGBT technology and the required reactive power variation range for the T-STATCOM application. In the field prototype of the CMC module, the AC voltages are approximated to sinusoidal waves by Selective Harmonic Elimination Method (SHEM) and by the use of an optimized series input filter reactor. The use of n number of HBs in each phase provides us n number of freedom

in the application of SHEM. One of them is allocated to the fundamental component while n-1 is for the elimination of low order harmonics. Since n is chosen to five in the prototype system, 5th, 7th,11th and 13th harmonic components are successfully eliminated in the AC voltage waveforms of the CMC module. The equalization of DC link capacitor voltages is achieved according to Modified Selective Swapping (MSS) algorithm. MSS is applied every 400µs period if needed to obtain a perfect equalization of DC link capacitor voltages at the expense of higher switching frequency and hence switching losses. In this research work, an L-shaped laminated bus has been designed and the HV IGBT driver circuit has been modified for optimum switching performance of HV IGBT modules in each HB circuit. The performances of the HB circuit and the resulting 11-level CMC module have been obtained not only in the laboratory but also in the field. Design works for HB and the CMC are based on MATLAB and PSCAD simulations. The laboratory and field performance of the HB circuit and CMC module is found to be satisfactory and quite consistent with the theoretical results and design objectives. In addition to these, 154 kV, ±50MVAr T-STATCOM prototype has been designed, implemented and installed at Sincan Transformer Substation-Ankara primarily for the purposes of reactive power compensation and terminal voltage regulation. The T-STATCOM prototype is composed of five parallel operated CMC modules developed within the scope of this PhD thesis research work. The T-STATCOM configuration permits the operation of any number of CMC modules in the range from one to five for experimental purposes. The performance of this T-STATCOM system is also presented in this PhD thesis as a sample application.

Keywords: Transmission STATCOM, Cascaded Multilevel Converter (CMC), Modified Selective Swapping (MSS)

## KASKAT ÇOK SEVİYELİ ÇEVİRGEÇ TABANLI İLETİM STATKOM: SİSTEM TASARIM YÖNTEMİ VE BİR 12kV ±12MVAr GÜÇ KATI GELİŞTİRİLMESİ

GÜLTEKİN, Burhan

Doktora, Elektrik Elektronik Mühendisliği Bölümü

Tez Yöneticisi : Prof. Dr. Muammer ERMİŞ

Eylül 2012, 177 sayfa

Bu araştırma ve geliştirme çalışması, H-Köprülü Çok Seviyeli Çevirgeç temelli İletim STATCOM sistemleri için tasarım yöntemini ve bir adet ±12MVAR, 12 kV, Y-bağlı, 11-seviyeli H-Köprülü Çok Seviyeli Çevirgeç yapısının geliştirilmesini içermektedir. Geliştirilen bu çevirgeç modülü İletim STATCOM sistemleri için temel bir yapı teşkil etmektedir. Ayrıca bu tezde, geliştirilen çok seviyeli çevirgecin gücü, her fazında kullanılacak H-Köprü sayısı, çevirgecin tasarlanacağı AC gerilim değeri, İletim STATCOM sisteminde kullanılacak paralel çevirgeç sayısı, modüle bağlanacak en uygun seri filtre reaktörü değeri ve T-STATCOM'un güç sisteminde bağlanacağı baranın belirlenmesi konuları IEEE 519-1992 standardı, YG IGBT'lerin güncel teknolojisi ve uygulama için istenen reaktif gücün değişim aralağına göre irdelenmiştir. Geliştirilen çok seviyeli çevirgecin AC gerilim şekilleri, Seçici Harmonik Eleme Metodu (SHEM) ve en uygun değerdeki seri filtre reaktörünün kullanılması ile sinüs dalgalarına yaklaştırılmıştır. Her faz için n tane H-Köprü kullanımı SHEM uygulaması için n tane eşitliğin kullanım özgürlüğünü

tanımaktadır. Bu eşitliklerden biri temel bileşen için kullanılırken geri kalan n-1 tanesi de düşük dereceli harmoniklerin yok edilmesi amacıyla kullanılabilmektedir. Geliştirilen prototip sistem için n sayısı beş olarak seçildiğinden çevirgeç çıkış gerilimlerinde 5., 7., 11. ve 13.harmonik bileşenleri başarılı bir şekilde elenmiştir. Çevirgeçte kullanılan DA bağ kondansatör gerilimleri Düzenlemiş Seçici Yer Değiştirmeli algoritması ile eşitlenmiştir. Gerektiğinde 400µs periyotlarla uygulanan bu metod sayesinde yüksek anahtarlama frekansı ve daha fazla kayba rağmen DA bağ gerilimleri için mükemmel bir eşitlik sağlanmıştır. Bu araştırma çalışmasında her H-Köprü için L seklinde bir lamine bara yapısı tasarlanmış ve YG IGBT'lerde optimum anahtarlama performansı elde etmek için sürücü devreleri değiştirilmiştir. H-Köprü ve elde edilen 11-seviyeli Çevrigeç performansları hem laboratuvarda hem de sahada elde edilmiştir. H-Köprü ve çevirgeç için MATLAB ve PSCAD benzetimleri ile tasarım çalışmaları yürütülmüştür. Laboratuvar ve sahada elde edilen verilerin hem H-Köprü hem de çevirgeç için oldukça tatminkar olmasının yanısıra teorik sonuçlar ve tasarım hedefleriyle gayet uyumlu olduğu gözlemlenmiştir. Bunlara ek olarak, bir adet 154 kV, ±50MVAr İletim STATCOM prototipi tasarlanıp geliştirilmiş ve Ankara'da bulunan Sincan Trafo Merkezinde reaktif güç kompanzasyonu ve bara gerilim düzenlenmesi amaçları için kurulmuştur. Kurulan sistem bu doktora tez çalışmasında geliştirilen beş adet çok seviyeli çevirgecin paralel kullanımından oluşmaktadır. İletim STATCOM yapısı, birden beşe kadar çevirgecin deneysel amaçla kullanılmasına olanak vermektedir. Bu İletim STATCOM sisteminin performansı da ayrıca bir uygulama örneği olarak da tezde verilmiştir.

Anahtar Kelimeler: İletim STATKOM, Çok Seviyeli Çevirgeçler, Düzenlenmiş Seçici Yerdeğiştirme

## **ACKNOWLEDGMENTS**

I would like to express my deepest gratitude to my supervisor Prof. Dr. Muammer Ermiş not only for his guidance, criticism, encouragements and insight throughout this research but also for his continuous confidence in me, and his unforgettable and valuable contributions to my career.

I would like to show my gratitude also to Prof. Dr. Işık Çadırcı for her guidance, criticism, encouragements and insight throughout this research.

I would like to thank Prof. Dr. H. Bülent Ertan for his suggestions and comments in my thesis progress committee.

The prototype system, developed within the scope of this research work, is a part of the National Power Quality Project (Project No: 105G129). I would like to express my special thanks to the Public Research Grant Committee (KAMAG) of TÜBİTAK for their full financial support.

Special thanks to Turkish Electricity Transmission Co. (TEİAŞ) for their courage to give us a chance to apply this novel technology. I am especially thankful to Yener Akkaya, Semih Bideci and Hikmet Toygar and the other staff of TEİAŞ for their great effort to design and installation of high voltage switchgears and to finish the civil works of the system in a short time.

The assistance of the valuable staff in Power Electronics Department of TUBITAK UZAY is gratefully acknowledged. I am especially thankful to all technical staff for their substantial assistance and companionship during development and field tests of prototype system.

I would like to acknowledge my colleagues for their crucial contributions to this research work: Cem Özgür Gerçek for his contribution to computer simulations, Tevhid Atalık for his contribution to designing and programming the DSP Boards, Mustafa Deniz for his contribution to designing and programming the FPGA Boards, Erkan Koç for his contribution to design and implementation the PLC based monitoring system, Nazan Biçer for her contribution to the power stage design and production, Kemal Nadir Köse for his contribution to design and production of Water Cooling System, Adnan Açık for his contribution to the design of capacitor protection circuit and finally Cezmi Ermiş for his contribution to the design and construction of the concrete platform of the developed STATCOM.

I would like to express my deepest gratitude to my family for their patience, sacrifice, encouragement and continuous morale support.

Finally, I would like to express my deepest gratitude to my wife Şehnaz and my son Birol Salih for their presence, patience, sacrifice, endless support and encouragement.

## **TABLE OF CONTENTS**

| PΙ         | AGIARISMiii                                                      |

|------------|------------------------------------------------------------------|

| AI         | SSTRACTiv                                                        |

| ÖZ         | <i>L</i> vi                                                      |

| <b>A</b> ( | CKNOWLEDGEMENTSviii                                              |

| LI         | ST OF TABLESxiii                                                 |

| LI         | ST OF FIGURESxv                                                  |

| N(         | OMENCLATURExxiii                                                 |

| AI         | BBREVIATIONSxxiv                                                 |

| CI         | HAPTERS                                                          |

| 1.         | INTRODUCTION1                                                    |

|            | 1.1.Overview                                                     |

|            | 1.2.Scope of the Thesis                                          |

| 2.         | OPERATING PRINCIPLES OF CMC BASED TRANMISSION                    |

|            | STATCOM14                                                        |

|            | 2.1.System Description                                           |

|            | 2.2.Active and Reactive Power Control                            |

|            | 2.3. Wave Shaping                                                |

|            | 2.4. Voltage Balancing of DC Link Capacitors                     |

|            | 2.4.1. Some Conventional Methods                                 |

|            | 2.4.2. Conventional Selective Swapping (CSS) Method34            |

|            | 2.4.3. Modified Selective Swapping (MSS) Method41                |

| 3.         | SYSTEM DESIGN AND SIZING50                                       |

|            | 3.1. Introduction                                                |

|            | 3.2. Determination of Connection Point and Sizing of T-STATCOM50 |

|            | 3.3. Sizing of CMC Module                                        |

|            | 3.4.Design of Series Filter Reactor                              |

|            | 3.4.1. THD Values in AC Input Voltage of CMC56                   |

|    | 3.4.2.     | Effect of Series Filter Inductance on THD and TDD             | .58   |

|----|------------|---------------------------------------------------------------|-------|

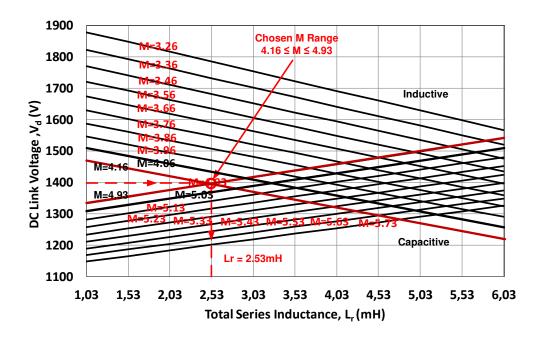

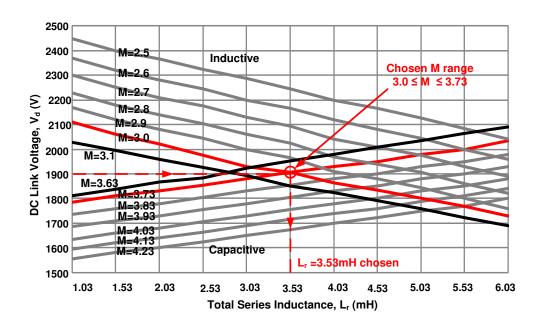

|    | 3.4.3.     | Effect of Series Filter Inductance on DC Link Voltage         |       |

|    |            | and Modulation Index Values                                   | .63   |

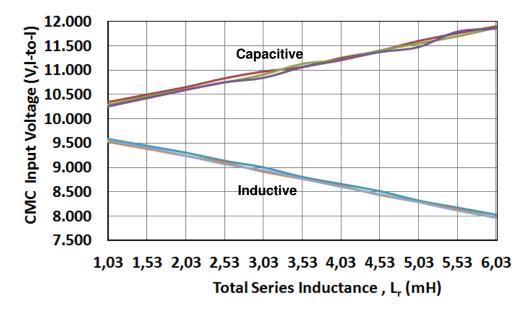

|    | 3.4.4.     | Effect of Series Filter Inductance on AC Input Voltage of CMC | .66   |

|    | 3.4.5.     | Conclusions                                                   | .67   |

| 4. | DESIGN     | OF A CASCADED MULTILEVEL                                      |       |

|    | CONVER     | RTER (CMC) MODULE                                             | .70   |

|    | 4.1. Desig | n of CMC Module                                               | .70   |

|    | 4.1.1.     | Design of the H-Bridge (HB) Circuit                           | .71   |

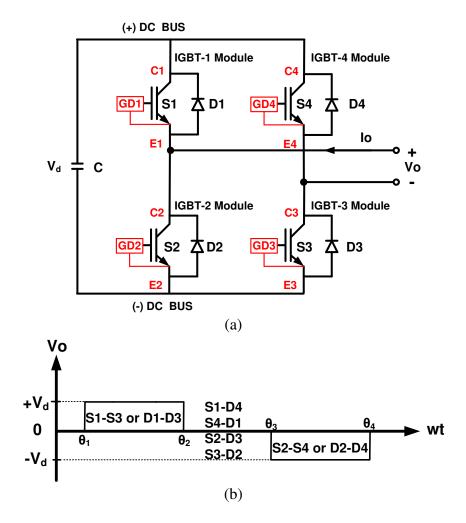

|    | 4.1        | .1.1.The structure and operation of HB Circuits               | .72   |

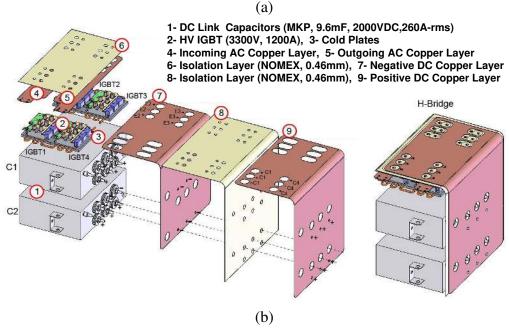

|    | 4.1        | .1.2.L-shaped Laminated Bus Design with 3-conducting Layers   | .79   |

|    | 4.1        | .1.3.Selection of Power Semiconductor Switches                | .82   |

|    | 4.1        | .1.4.Optimization of IGBT Switching Waveforms                 | .89   |

|    | 4.1        | .1.5.Choice of DC Link Capacitor                              | .92   |

|    | 4.2. Desig | n of Control System                                           | .101  |

|    | 4.2.1.     | DSP Board                                                     | .104  |

|    | 4.2.2.     | FPGA Board                                                    | . 107 |

|    | 4.2.3.     | Programmable Logic Controller (PLC)                           | .108  |

|    | 4.3. Switc | hing Strategies for the Application of Selective Swapping     | .109  |

| 5. | THE IMP    | PLEMENTATION OF T-STATCOM SYSTEM AND                          |       |

|    | FIELD P    | ERFORMANCE RESULTS                                            | 116   |

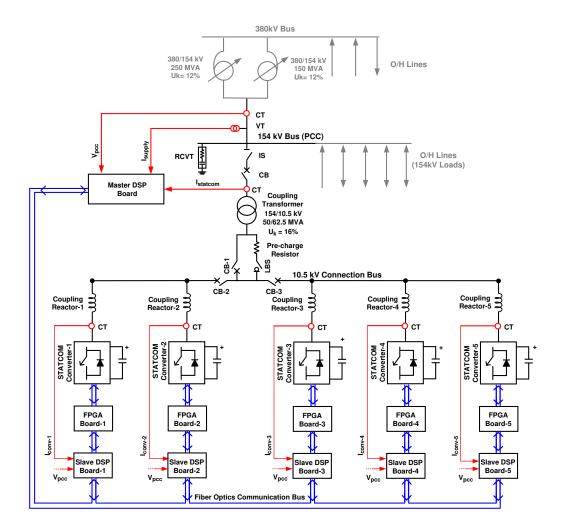

|    | 5.1.The In | nplementation of T-STATCOM System                             | .116  |

|    | 5.1.1.     | Power System Characteristics                                  | .120  |

|    | 5.2. Field | Performance Results                                           | .125  |

|    | 5.2.1.     | Field Performance of HB                                       | .125  |

|    | 5.2        | 2.1.1.Switching Waveforms of IGBT Modules                     | .128  |

|    | 5.2        | 2.1.2.DC Link Current and Voltage Waveforms                   | .129  |

|    | 5.2.2.     | Field Performance of CMC Module                               | .130  |

|    | 5.2        | 2.2.1. Voltage Waveforms at the Input of CMC                  | .130  |

|    | 5.2        | 2.2.2.Transient Performance of CMC Module                     | .137  |

|    | 5.2        | 2.2.3. Performance of Selective Swapping Methods on           |       |

|    | Balancing DC Link Capacitor Voltages13                    | 9 |

|----|-----------------------------------------------------------|---|

|    | 5.2.3. Field Performance of T-STATCOM System              | 5 |

|    | 5.2.3.1. Voltage and Current Waveforms at MV (10.5 kV)    |   |

|    | and HV (154 kV) sides14                                   | 5 |

|    | 5.2.3.2.Voltage and Current Harmonics at PCC (154 kV)14   | 7 |

|    | 5.2.3.3.Effects of Series Reactors on Voltage Harmonics14 | 8 |

|    | 5.2.3.4.Terminal Voltage Regulation (V-mode)14            | 9 |

|    | 5.2.3.5.Reactive Power Compensation (Q-mode)              | 1 |

|    | 5.2.3.6. Transitions Between Full Capacitive              |   |

|    | and Full Inductive Modes15                                | 3 |

| 6. | CONCLUSIONS15                                             | 5 |

|    | REFERENCES16                                              | 2 |

|    | APPENDICES                                                |   |

|    | A. SHEM EQUATIONS FOR 11-LEVEL CMC17                      | 0 |

|    | B. PERMISSIBLE REGINOS FOR THD AND TDD RECOMENDED         |   |

|    | BY IEEE STD.519-199217                                    | 2 |

|    | C. RATINGS OF COMMERCIALLY AVAILABLE HV IGBTS17           | 3 |

|    | D. SOAS OF MITSUBISHI CM1200HC-66H HV IGBT MODULE174      | 4 |

|    | CIRRICULUM VITAE17                                        | 5 |

## **LIST OF TABLES**

| TABLES      | Same and it along the stirms of STATCOM and and                  | _   |

|-------------|------------------------------------------------------------------|-----|

|             | Some practical applications of STATCOM systems                   | . 3 |

|             | The total number of required power components for M-level        |     |

| ]           | DCMC, FCMC and CMC                                               | . 9 |

| Table 2.1 N | Number of steps in CMC AC voltages and low order voltage         |     |

| 1           | harmonics eliminated as a function of number of HBs              | 24  |

| Table 2.2 ( | Optimum angles with respect to modulation index values for       |     |

| (           | CMC having 3HBs                                                  | 24  |

| Table 2.3 ( | Optimum angles with respect to modulation index values for       |     |

| (           | CMC having 5HBs                                                  | 25  |

| Table 2.4 C | Optimum angles with respect to modulation index values for       |     |

| (           | CMC having 7HBs                                                  | 25  |

| Table 2.5   | The number of redundancy modes for 11-level CMC                  | 36  |

| Table 2.6   | The number of redundancy modes for 15-level CMC                  | 37  |

| Table 2.7   | The variations in DC link voltage of HB1 in phase-A of           |     |

| -           | 11-level CMC operating at -10MVAr (Theoretical)                  | 46  |

| Table 2.8 T | The variations in DC link voltage of HB1 in phase-A of           |     |

| -           | 11-level CMC operating at +10MVAr (Theoretical)                  | 47  |

| Table 3.1   | The effects of series filter inductance on system design         | 68  |

| Table 3.2 7 | The comparison of CMC topologies                                 |     |

| •           | with three, five and seven HBs                                   | 68  |

| Table 4.1 7 | The operation states of the HB Circuit                           | 73  |

| Table 4.2 H | Effective Switching Frequency of Semiconductors                  |     |

| •           | with CSS and MSS methods                                         | 87  |

| Table 4.3   | The comparison of diode reverse recovery and IGBT peak currents, |     |

| ä           | and turn-on and reverse recovery losses for IGBT modules         | 92  |

| Table 4.4 C | Current Harmonic Components seen in                              |     |

| ]           | DC link current for both full capacitive                         |     |

|             | •                                                                |     |

| and full inductive operation modes                                           |

|------------------------------------------------------------------------------|

| Table 4.5 Technical Specifications of IC Boards in Figure 4.24               |

| Table 5.1 The technical specifications of the installed T-STATCOM system 117 |

| Table 5. 2 The electrical characteristics of the power system                |

| at which T-STATCOM system is connected                                       |

| Table 5.3 The monthly maximum reactive power variations of                   |

| the PCC from Nov.2008 to June.2009                                           |

| Table 5.4 CMC voltage harmonics at +10MVAr                                   |

| Table 5.5 CMC voltage harmonics at -10MVAr                                   |

| Table 5.6 Performance of selective swapping algorithms                       |

| Table 5.7 PCC line-to-ground voltage harmonics measured                      |

| by RCVT sensors                                                              |

| Table 5.8 154kV side current harmonics at rated power                        |

| $(I_L=188A, I_{SC}=20kA)$                                                    |

| Table 5.9 10.5kV voltage harmonics measured by RCVT sensors 148              |

| Table 5.10 CMC current harmonics at rated power                              |

| Table 6.1 Effect of main system parameters on cost and performance           |

| Table 6.1 (Cont'd) Effect of main system parameters                          |

| on cost and performance162                                                   |

## **LIST OF FIGURES**

| <b>FIGURES</b> |                                                                                                                                                                            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1     | V-I characteristic of SVC systems ( $V_s$ , $I_{cap}$ and $I_{ind}$ are supply voltage, SVC capacitive and inductive currents, respectively                                |

| Figure 1.2     | A practical SVC System[2]                                                                                                                                                  |

| Figure 1.3     | V-I characteristic of STATCOM systems (V <sub>s</sub> , I <sub>cap</sub> and I <sub>ind</sub> are supply voltage, STATCOM capacitive and inductive currents, respectively) |

| Figure 1.4     | A practical D-STATCOM System[3]                                                                                                                                            |

| Figure 1.5     | One phase single line diagrams of 5-level a) DCMC and b) FCMC 7                                                                                                            |

| Figure 1.6     | The output voltage waveform of 5-level DCMC and 5-level FCMC 8                                                                                                             |

| Figure 1.7     | One phase single diagram of 5-level CMC9                                                                                                                                   |

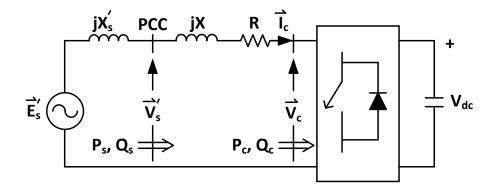

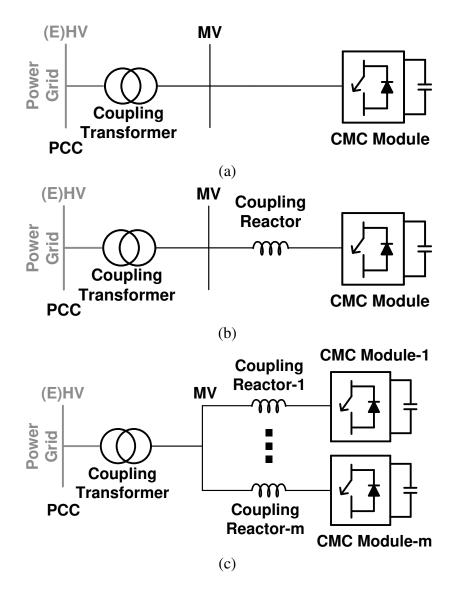

| Figure 2.1     | Single line diagram of a T-STATCOM based on a single CMC 14                                                                                                                |

| Figure 2.2     | Circuit diagram of a star-connected CMC consisting of                                                                                                                      |

|                | n series connected HBs in each phase                                                                                                                                       |

| Figure 2.3     | Simplified single line diagram of T-STATCOM                                                                                                                                |

| Figure 2.4     | Phasor diagram for lossy system (exaggerated)                                                                                                                              |

| Figure 2.5     | The definitions of $\delta$ and $\theta$                                                                                                                                   |

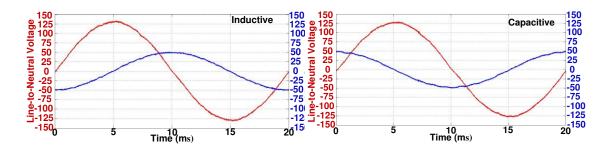

| Figure 2.6     | Sample line-to-neutral voltage waveforms at the                                                                                                                            |

|                | supply side and CMC side (Theoretical)                                                                                                                                     |

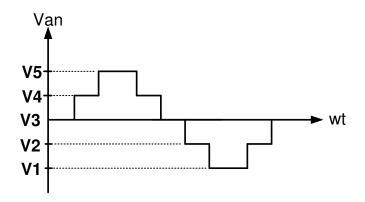

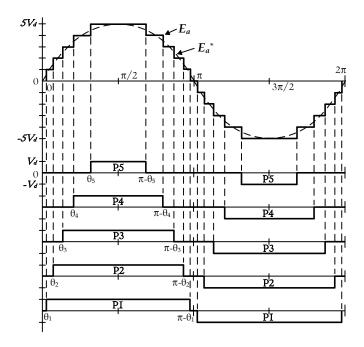

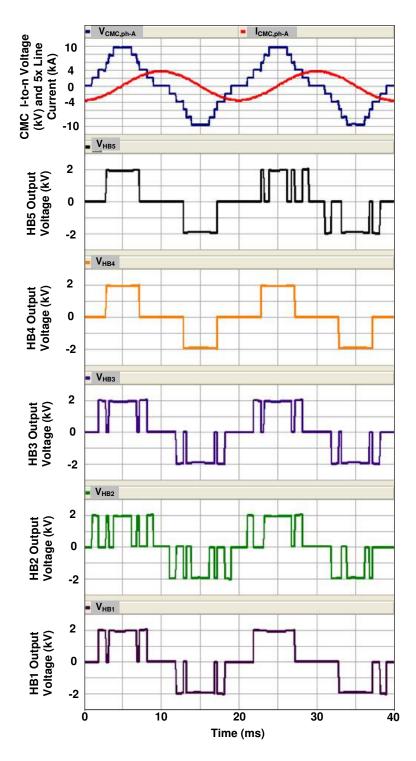

| Figure 2.7     | 11-level line-to-neutral voltage waveform [46]                                                                                                                             |

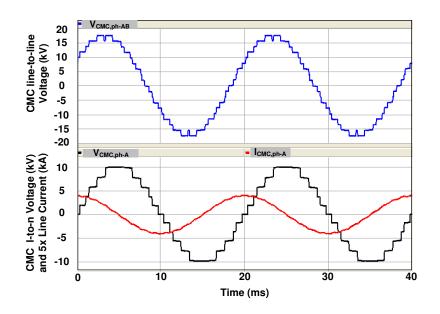

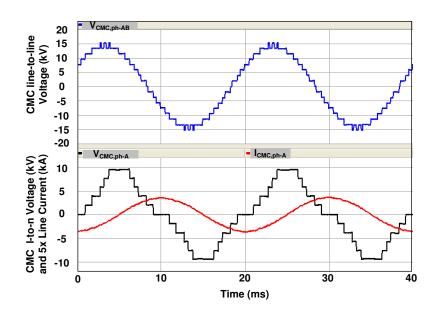

| Figure 2.8     | CMC line-to-line and line-to-neutral voltages                                                                                                                              |

|                | with line current of phase-A full capacitive case                                                                                                                          |

|                | (CSS Method/PSCAD Simulations)                                                                                                                                             |

| Figure 2.9     | CMC line-to-line and line-to-neutral voltages                                                                                                                              |

|                | with line current of phase-A full inductive case                                                                                                                           |

|                | (CSS Method/PSCAD Simulations)                                                                                                                                             |

| Figure 2.1     | 0 CMC line-to-neutral voltage with HB output voltages                                                                                                                      |

|                | in phase-A for full capacitive case                                                                                                                                        |

|                | (CSS Method/PSCAD Simulations)                                                                                                                                             |

| Figure 2.11 CMC line-to-neutral voltage with HB output voltages                   |

|-----------------------------------------------------------------------------------|

| in phase-A for full inductive case                                                |

| (CSS Method/PSCAD Simulations)                                                    |

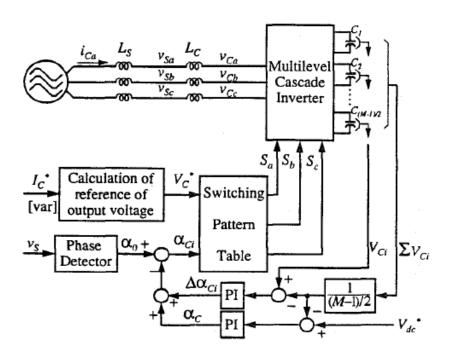

| Figure 2.12 The $\alpha/\Delta\alpha$ method for DC link capacitor balancing [48] |

| Figure 2.13 The rotational angle method for DC link capacitor balancing [49] 3    |

| Figure 2.14 The rotational of switching angles [49]                               |

| Figure 2.15 Redundant Modes of a)+3 $V_d$ and b) $0V_d$ levels                    |

| Figure 2.16 Redundant Modes of +1V <sub>d</sub> level                             |

| Figure 2.17 Redundant Modes of +2V <sub>d</sub> level                             |

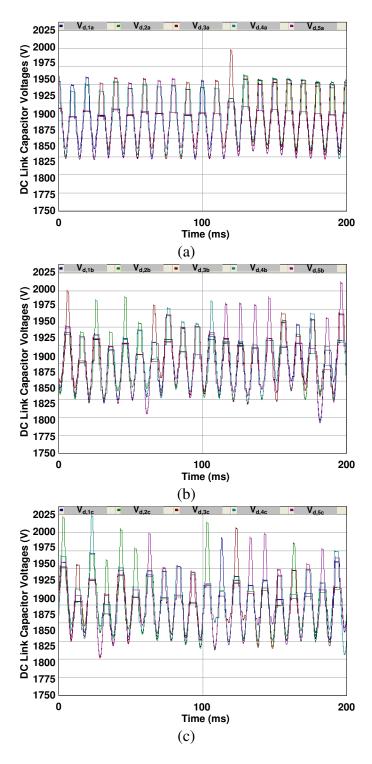

| Figure 2.18 The variations in the instantaneous DC link voltages of               |

| a) phase-A, b) phase-B and c) phase-C HBs of 11-level CMC                         |

| for full capacitive case (PSCAD Simulations)                                      |

| Figure 2.19 The variations in the instantaneous DC link voltages of               |

| a) phase-A, b) phase-B and c) phase-C HBs of 11-level CMC                         |

| for full inductive case (PSCAD Simulations)4                                      |

| Figure 2.20 The variations in the instantaneous DC link voltages of               |

| 1st HBs in three phases of 11-level CMC for                                       |

| a) full inductive, b) full capacitive cases (PSCAD Simulations) 4                 |

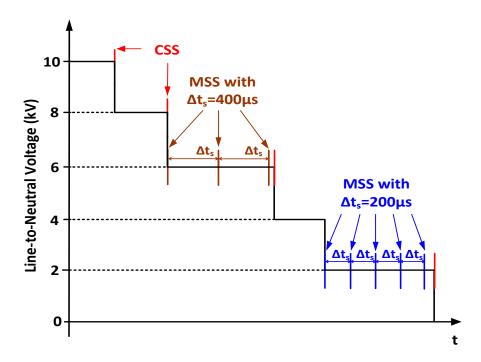

| Figure 2.21 The illustration of CSS and MSS                                       |

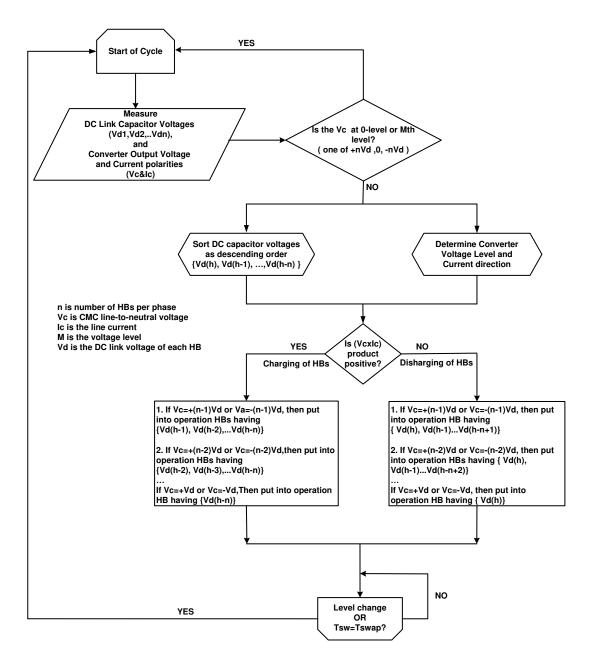

| Figure 2.22 The flowchart for MSS method employed in M-level CMC 4                |

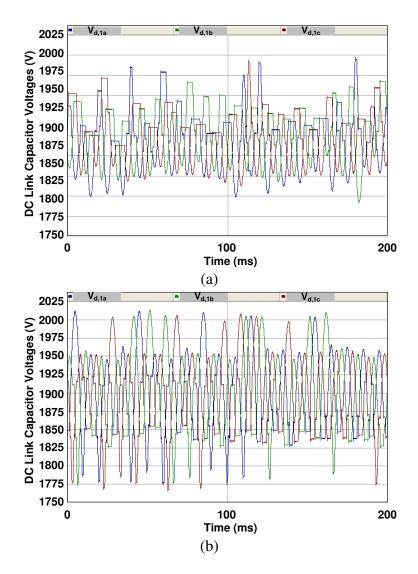

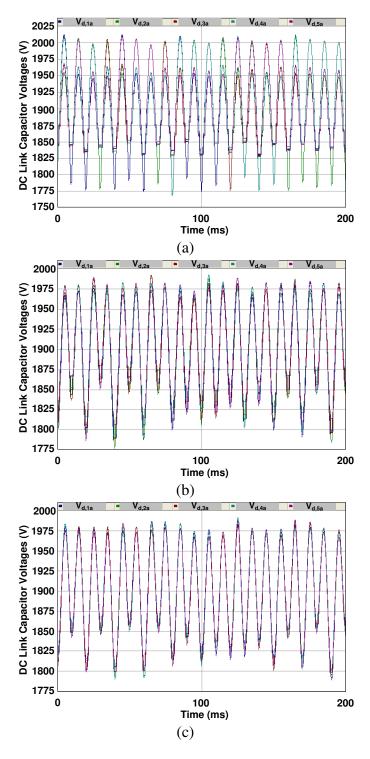

| Figure 2.23 The variations in the instantaneous DC link voltages of               |

| the CMC under a) CSS, b) MSS with $\Delta t_s$ =400 $\mu s$ and                   |

| c) MSS with $\Delta t_s$ =200 $\mu s$ for full capacitive case                    |

| (PSCAD Simulations)                                                               |

| Figure 2.24 The variations in the instantaneous DC link voltages of               |

| the CMC under a) CSS, b) MSS with $\Delta t_s$ =400 $\mu s$ and                   |

| c) MSS with $\Delta t_s$ =200 µs for full inductive case                          |

| (PSCAD Simulations)                                                               |

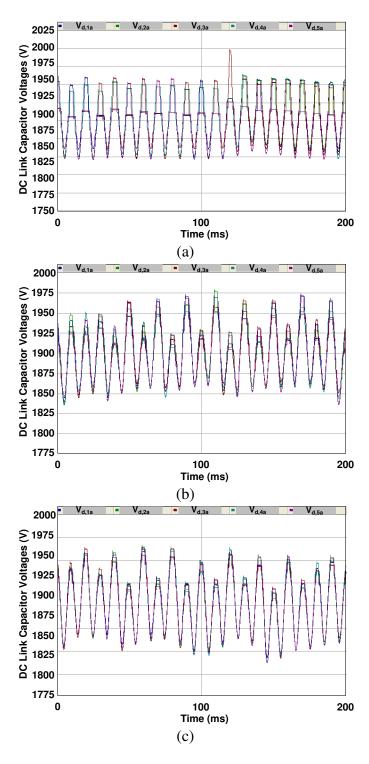

| Figure 2.25 The performance of CSS and MSS methods on the instantaneous           |

| peak-to-peak variations in the DC link voltage of an HB unit                      |

| (Theoretical) 4                                                                   |

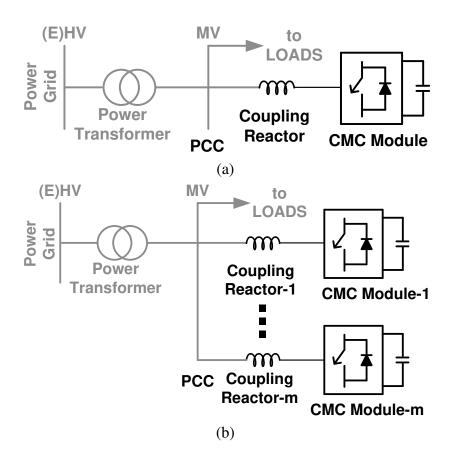

| Figure 3.1 Connection alternatives for T-STATCOM system ((a) and             |

|------------------------------------------------------------------------------|

| (b) connection to the MV side of existing power transformer) 51              |

| Figure 3.2 Connection alternatives for T-STATCOM system ((a),(b),and (c)     |

| connection to the power grid via a special coupling transformer) 52          |

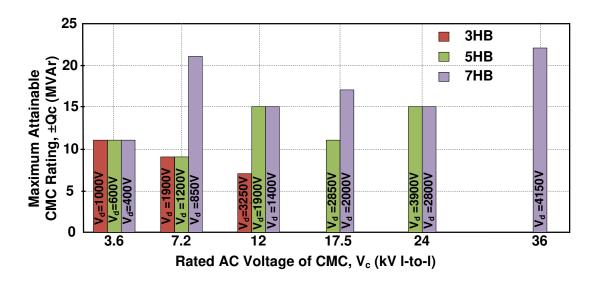

| Figure 3.3 Maximum attainable CMC ratings calculated as a function of rated  |

| AC voltage of CMC (V <sub>c</sub> ) for three different CMC topologies       |

| (in view of HV IGBT technology by June 2012)55                               |

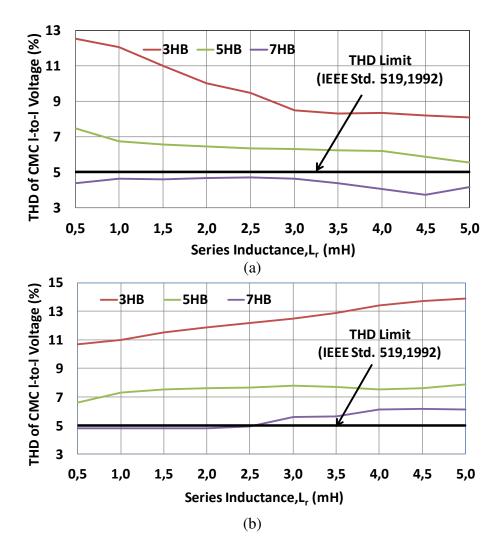

| Figure 3.4 THD variations against series inductance for AC input voltage     |

| of CMC Topologies ((a) Capacitive Case; (b) Inductive Case) 58               |

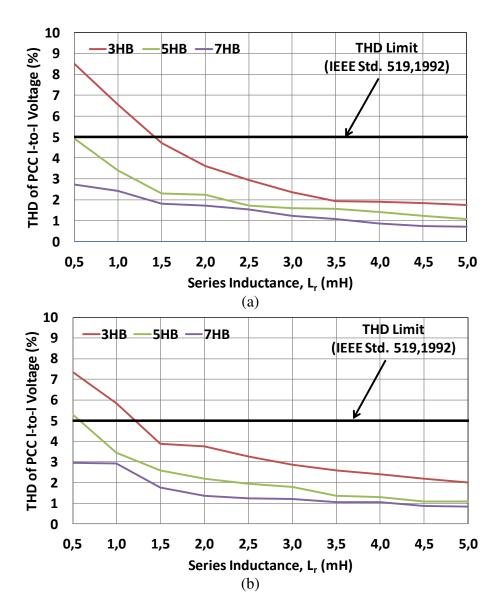

| Figure 3.5 THD variations against series inductance for CMC Topologies       |

| at MV PCC ((a) Capacitive Case; (b) Inductive Case)                          |

| Figure 3.6 TDD variations against series inductance for CMC Topologies       |

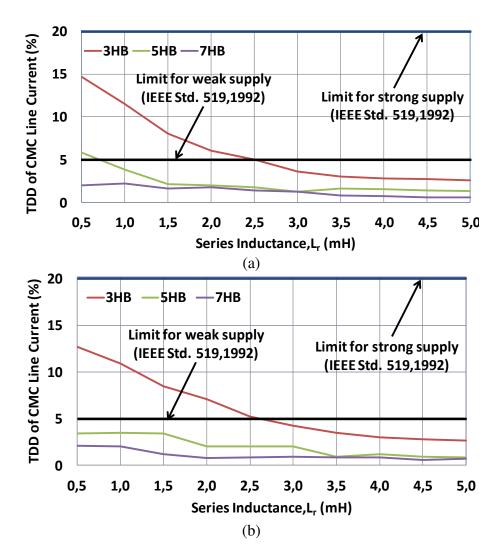

| at MV PCC ((a) Capacitive Case; (b) Inductive Case)                          |

| Figure 3.7 THD variations against total series inductance for CMC Topologies |

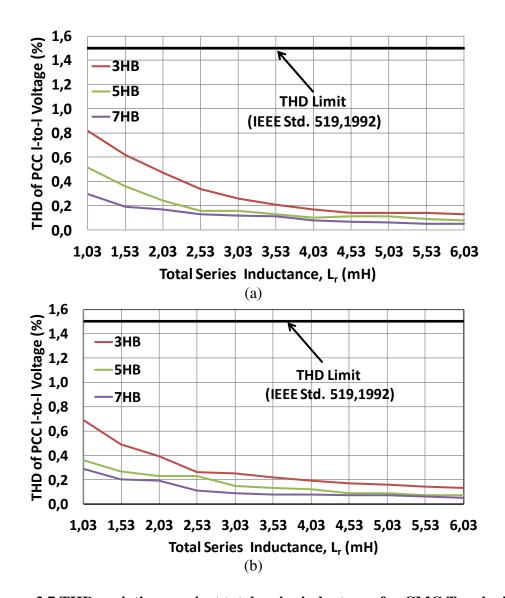

| at HV PCC ((a) Capacitive Case; (b) Inductive Case)61                        |

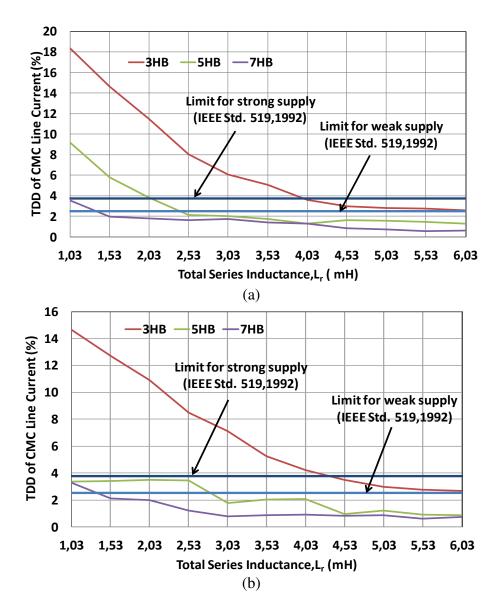

| Figure 3.8 TDD variations against total series inductance for CMC Topologies |

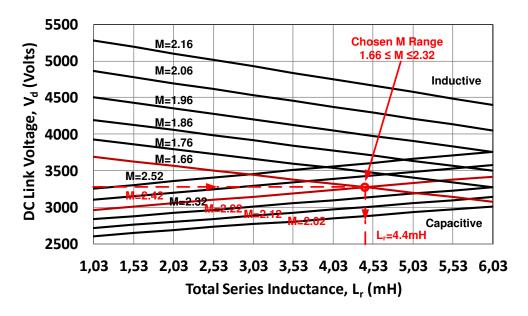

| at HV PCC ((a) Capacitive Case; (b) Inductive Case)62                        |

| Figure 3.9 Variations in DC link voltage against total series inductance     |

| for different values of modulation index,                                    |

| M in the case of CMC with 3HBs/Theoretical                                   |

| Figure 3.10 Variations in DC link voltage against total series inductance    |

| for different values of modulation index,                                    |

| M in the case of CMC with 7HBs/Theoretical                                   |

| Figure 3.11 Variations in DC link voltage against total series inductance    |

| for different values of modulation index, M                                  |

| in the case of CMC with 5HBs/Theoretical65                                   |

| Figure 3.12 Effect of series filter inductance on CMC input voltage          |

| Figure 4.1 Designed and implemented 3-phase, 12kV, ±12 MVAr                  |

| Y-connected 11-level CMC module                                              |

| Figure 4.2 Single line diagram of (a) the HB Circuit                         |

| and (b) its typical output voltage                                           |

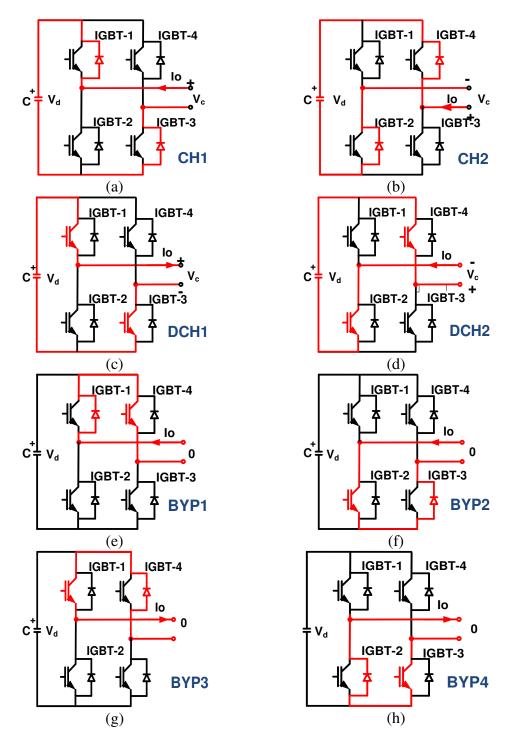

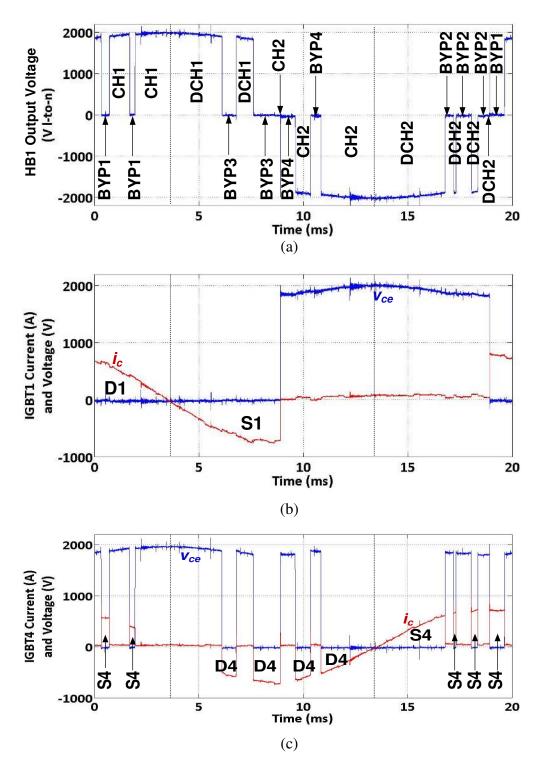

| Figure 4.3 The operation modes of HB: a) Charging-1(CH1),                  |

|----------------------------------------------------------------------------|

| b) Charging-2(CH2),c) Discharging-1 (DCH1),                                |

| d) Discharging-2 (DCH2), e) By-pass-1 (BYP1),                              |

| f) By-pass-2 (BYP2), g) By-pass-3 (BYP3), h) By-pass-4 (BYP4) 74           |

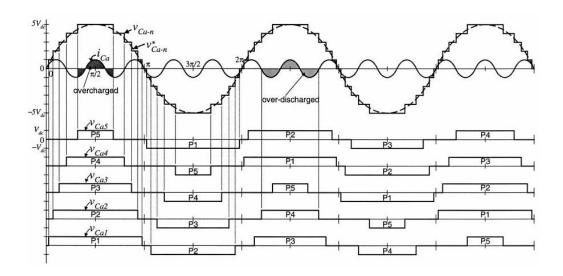

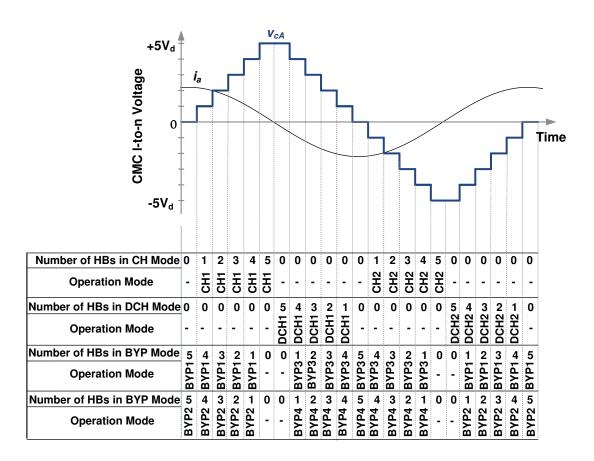

| Figure 4.4 11-level line-to-neutral voltage waveform                       |

| with definition and sequence of HB operation modes                         |

| for capacitive operation of the CMC                                        |

| Figure 4.5 11-level line-to-neutral voltage waveform                       |

| with definition and sequence of HB operation modes                         |

| for inductive operation of the CMC                                         |

| Figure 4.6 Voltage spikes superimposed on the line-to-neutral CMC          |

| voltages with MSS method (Δts =400μs, field data)77                        |

| Figure 4.7 Line-to-neutral voltage and line current waveforms              |

| recorded in the field at 154kV PCC                                         |

| Figure 4.8 General view (a) and structure (b) of the designed HB79         |

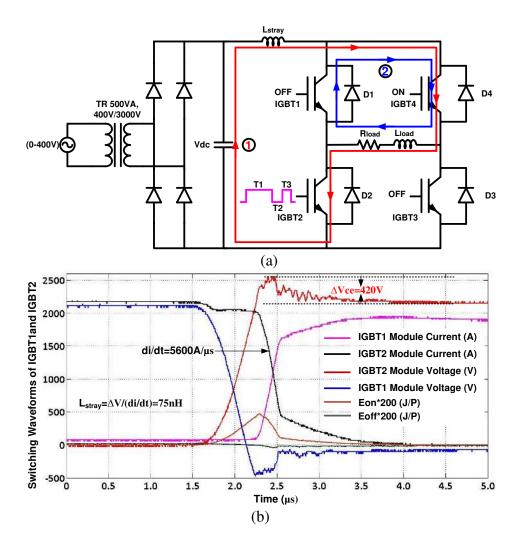

| Figure 4.9 Performance of HB in the Laboratory (a)Test Circuit,            |

| and (b) switching waveforms of IGBT1, D1and IGBT2 81                       |

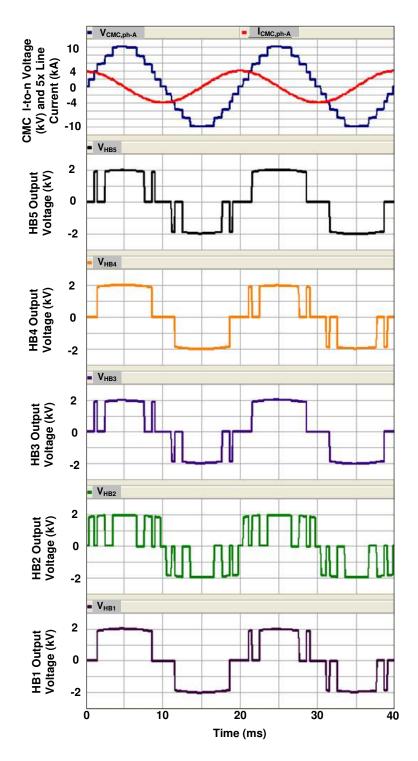

| Figure 4.10 Power semiconductors current, HB output voltage and CMC l-to-n |

| voltage waveforms for Q=-10MVAr at PCC with CSS method                     |

| (PSCAD Simulations)                                                        |

| Figure 4.11 Power semiconductors current, HB output voltage and CMC l-to-n |

| voltage waveforms for Q=+10MVAr at PCC with CSS method                     |

| (PSCAD Simulations)                                                        |

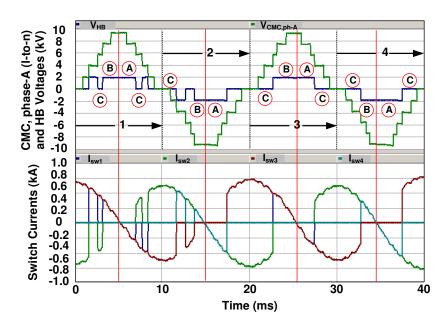

| Figure 4.12 Power semiconductors current, HB output voltage and CMC l-to-n |

| voltage waveforms for Q=-10MVAr at PCC with MSS method at                  |

| $\Delta t_s$ =400 $\mu$ s (PSCAD Simulations)                              |

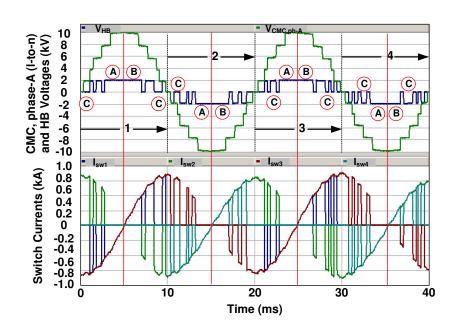

| Figure 4.13 Power semiconductors current, HB output voltage and CMC l-to-n |

| voltage waveforms for Q=+10MVAr at PCC with MSS method at                  |

| $\Delta_{ts}$ =400µs (PSCAD Simulations)84                                 |

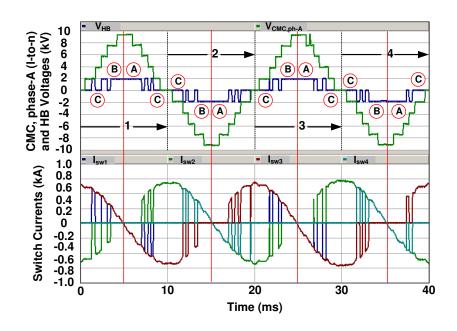

| Figure 4.14 Power semiconductors current, HB output voltage and CMC l-to-n |

|----------------------------------------------------------------------------|

| voltage waveforms for Q=-10MVAr at PCC with MSS method                     |

| $\Delta t_s$ =200 $\mu$ s (PSCAD Simulations)                              |

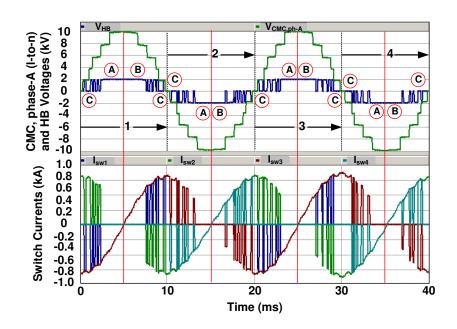

| Figure 4.15 Power semiconductors current, HB output voltage and CMC l-to-n |

| voltage waveforms for Q=+10MVAr at PCC with MSS method at                  |

| Δts=200μs (PSCAD Simulations)85                                            |

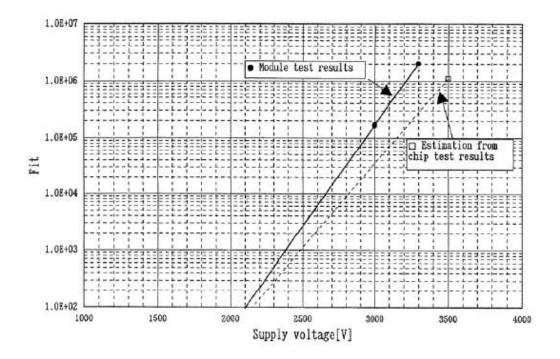

| Figure 4.16 Relationship of FIT values and applied DC link voltages for    |

| CM1200HC-66H HV IGBT [55]88                                                |

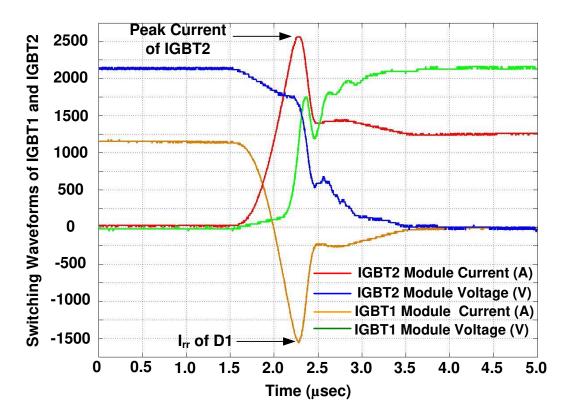

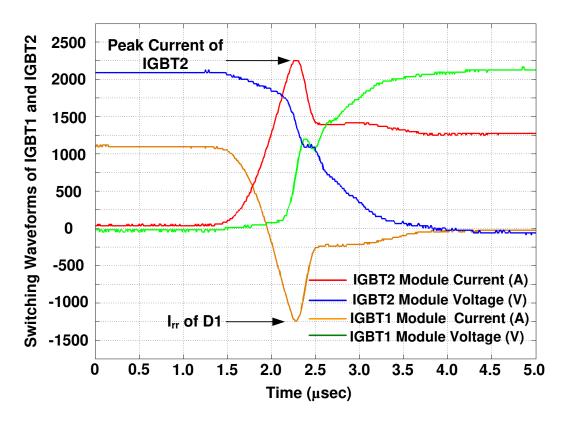

| Figure 4.17 The switching waveforms during turn-on of IGBT2 with standard  |

| gate driver circuit at nearly I <sub>c</sub> (rated)90                     |

| Figure 4.18 The switching waveforms during turn-on of IGBT2 with modified  |

| gate driver circuit at nearly I <sub>c</sub> (rated)                       |

| Figure 4.19 The variations in peak-to-peak voltage                         |

| ripple against capacitance value                                           |

| Figure 4.20 The variations in DC link voltage and current of HB1           |

| with its output voltage for Q=-10 MVAr at PCC                              |

| (PSCAD Simulations)                                                        |

| Figure 4.21 The variations in DC link voltage and current of HB1           |

| with its output voltage for Q=+10 MVAr at PCC                              |

| (PSCAD Simulations)                                                        |

| Figure 4.22 The variations of harmonic components in DC link voltage       |

| and current for Q=-10 MVAr at PCC (PSCAD Simulations) 97                   |

| Figure 4.23 The variations of harmonic components in DC link voltage       |

| and current for Q=+10 MVAr at PCC (PSCAD Simulations) 98                   |

| Figure 4.24 The block diagram of the digital control system of CMC         |

| with control panel                                                         |

| Figure 4.25 The diagram of control system for the designed CMC module 103  |

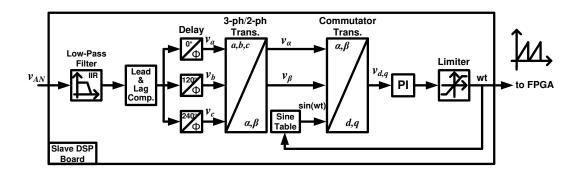

| Figure 4.26 Generation of Q <sub>ref</sub> and Q <sub>c</sub> by DSP Board |

| Figure 4. 27 PLL generation by the DSP Board                               |

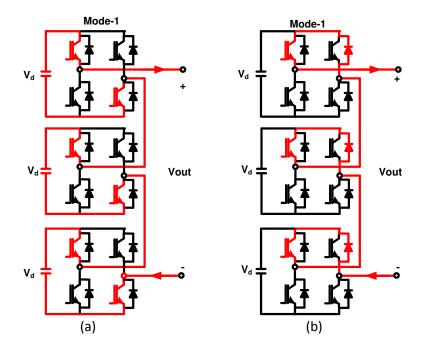

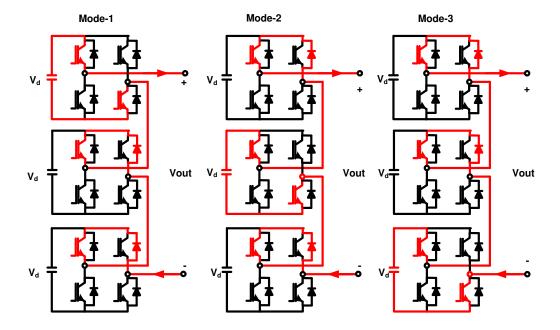

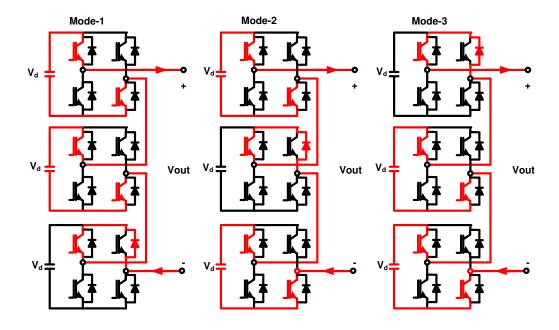

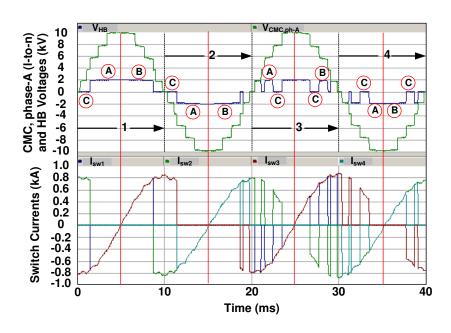

| Figure 4.28 Illustration of a) operation modes of IGBT modules in phase-A  |

| of the CMC before (Mode-1), during (Mode-2) and                            |

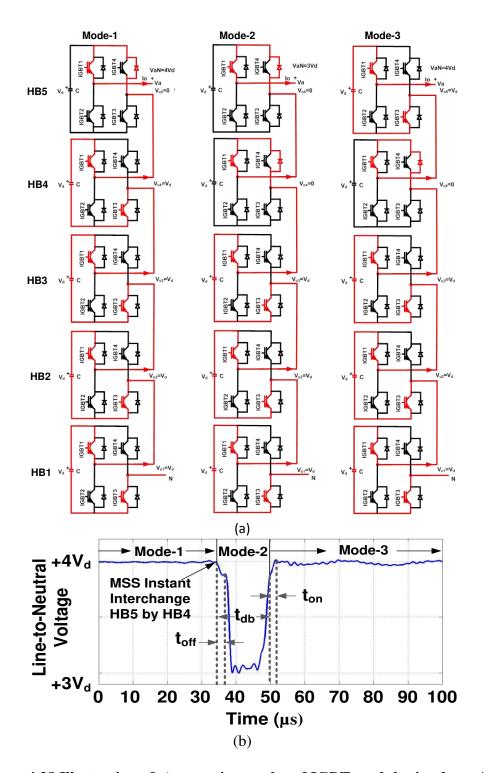

| after (Mode-3) the MSS operation b) voltage spike –Vd                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------|----|

| superimposed on +4Vd level (Field data)                                                                                  | 0  |

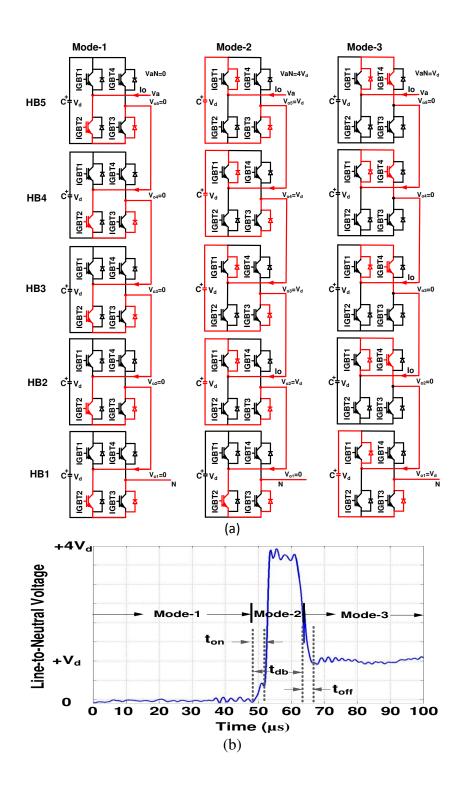

| Figure 4.29 Illustration of a) operation modes of IGBT modules in phase-A                                                |    |

| of the CMC before (Mode-1), during (Mode-2) and                                                                          |    |

| after (Mode-3) the MSS operation b) voltage spike +4Vd                                                                   |    |

| superimposed on zero level (Field data)                                                                                  | 2  |

| Figure 5.1 Simplified single line diagram of the implemented T-STATCOM 11                                                | 6  |

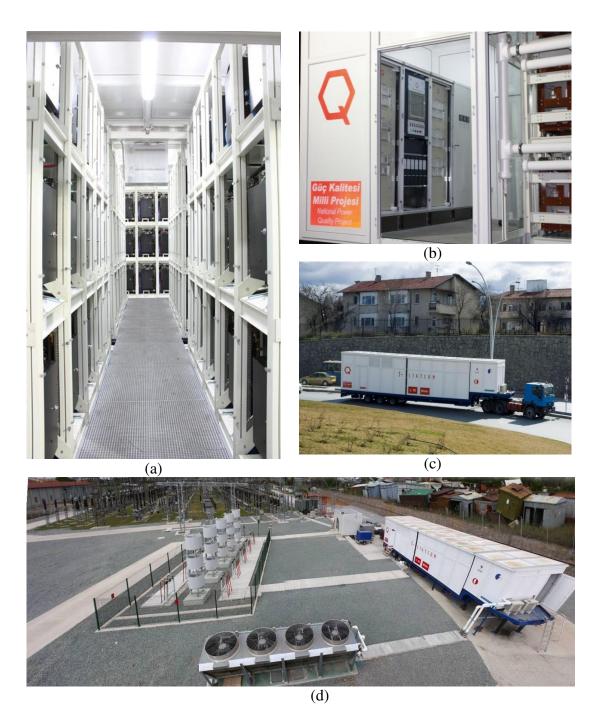

| Figure 5.2 154 kV, ±50 MVAr T-STATCOM based on 11-level CMC installed                                                    |    |

| at 380kV/154kV Sincan Transformer Substation                                                                             |    |

| ((a) Interior view of trailer with power stages, (b) Control cabinets,                                                   |    |

| (c) Trailer for ±50 MVAr T-STATCOM on road                                                                               |    |

| (WxLxH:3700mmx16800mmx4300mm), and                                                                                       |    |

| (d) General view of T-STATCOM)                                                                                           | 8  |

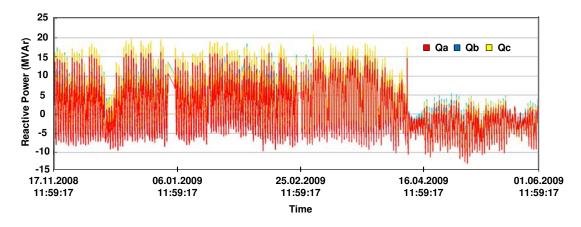

| Figure 5.3 The variations in reactive power per phase at PCC side                                                        |    |

| (Nov.2008-June.2009, field data)                                                                                         | 20 |

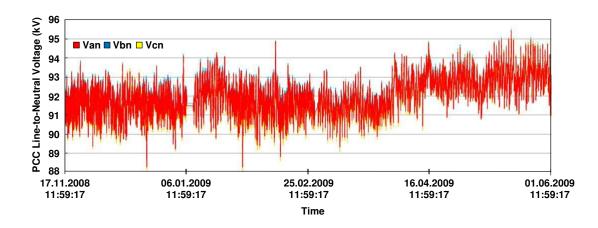

| Figure 5.4 The variations in PCC side line-to-neutral voltages                                                           |    |

| (Nov.2008-June.2009, field data)                                                                                         | 21 |

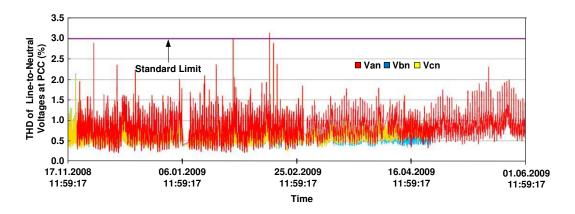

| Figure 5.5 The variations in THD of PCC line-to-neutral voltages                                                         |    |

| (Nov.2008-June.2009, field data)                                                                                         | 22 |

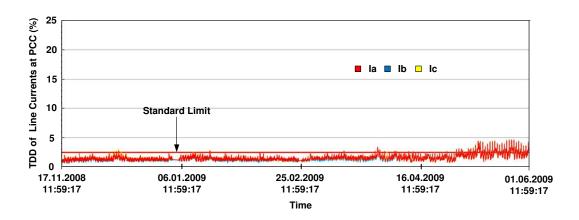

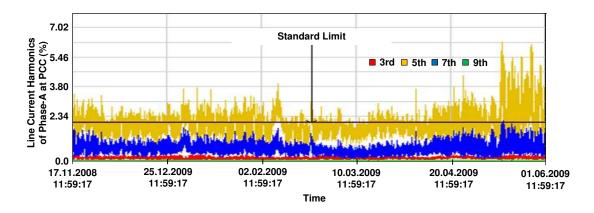

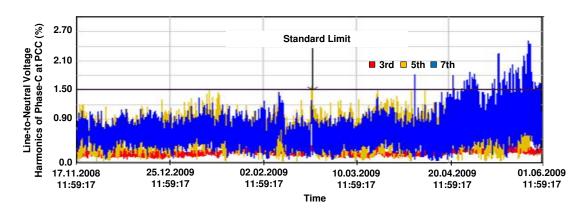

| Figure 5.6 The variations in TDD of PCC line currents                                                                    |    |

| (Nov.2008-June.2009, field data)                                                                                         | 22 |

| Figure 5.7 The variations in 3 <sup>rd</sup> , 5 <sup>th</sup> , 7 <sup>th</sup> and 9 <sup>th</sup> harmonic components |    |

| of PCC phase-A line current (Nov.2008-June.2009, field data) 12                                                          | 23 |

| Figure 5.8 The variations in 3 <sup>rd</sup> , 5 <sup>th</sup> and 7 <sup>th</sup> harmonic components of PCC            |    |

| phase-C line-to-neutral voltage (Nov.2008-June.2009, field data) 12                                                      | 23 |

| Figure 5.9 Field performance of HB1 in phase-A over one-cycle a) HB1 output                                              |    |

| voltage and its operation modes b) IGBT1 module voltage and current                                                      | ıt |

| waveforms c) IGBT4 module voltage and current waveforms 12                                                               | 26 |

| Figure 5.10 Switching Waveforms of IGBT1 and IGBT2 in the field for                                                      |    |

| I <sub>c</sub> =770A for turn-off characteristics                                                                        | 27 |

| Figure 5.11 Switching Waveforms of IGBT1 and IGBT2 in the field for                                                      |    |

| $I_{c}$       | =770A for turn-on characteristics                                         | 28 |

|---------------|---------------------------------------------------------------------------|----|

| Figure 5.12 D | OC link voltage and current of HB1 in phase-A of CMC                      |    |

| m             | nodule-1 when T-STATCOM delivers -50MVAr to the PCC                       |    |

| (1            | lµs averaged field data)1                                                 | 29 |

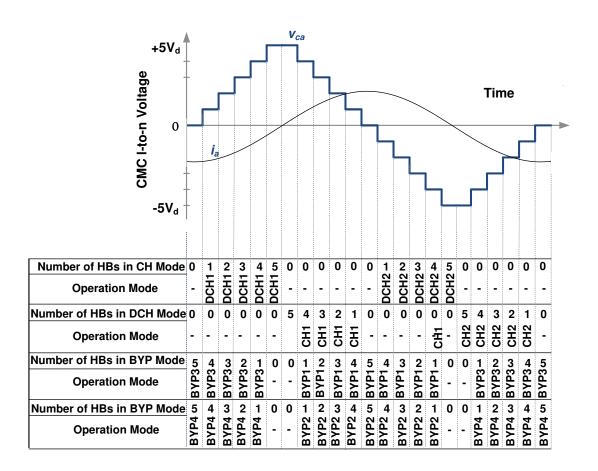

| Figure 5.13 T | The waveforms of a) line-to-line and b) line-to-neutral voltages          |    |

| fc            | or a CMC at full inductive operation mode under                           |    |

| C             | Conventional Selective Swapping (CSS) method 1                            | 31 |

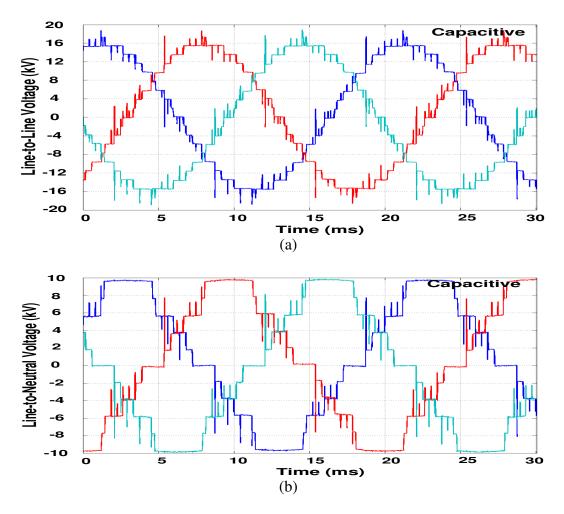

| Figure 5.14 T | The waveforms of a) line-to-line and b) line-to-neutral voltages          |    |

| fc            | or a CMC at full capacitive operation mode under                          |    |

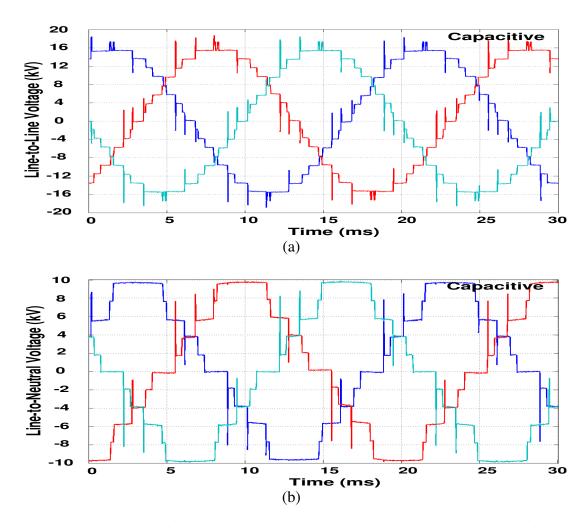

| C             | Conventional Selective Swapping (CSS) method 1                            | 32 |

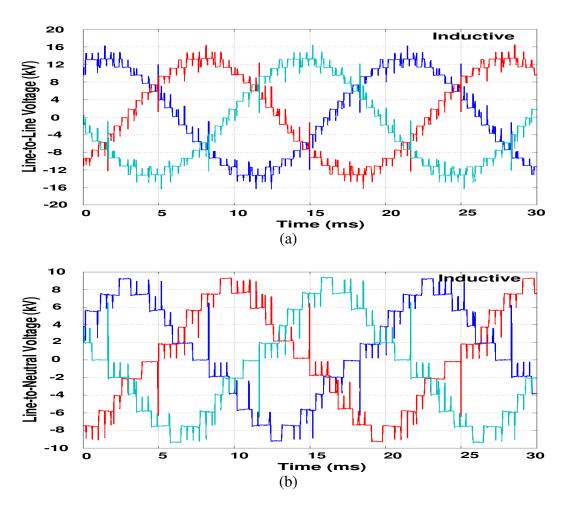

| Figure 5.15 T | The waveforms of a) line-to-line and b) line-to-neutral voltages          |    |

| fc            | or a CMC at full inductive operation mode under                           |    |

| M             | Modified Selective Swapping (MSS) method with $\Delta t_s$ =400 $\mu s$ 1 | 33 |

| Figure 5.16 T | The waveforms of a) line-to-line and b) line-to-neutral voltages          |    |

| fc            | or a CMC at full capacitive operation mode under                          |    |

| M             | Modified Selective Swapping (MSS) method with $\Delta t_s$ =400 $\mu s$ 1 | 34 |

| Figure 5.17 T | The transient-free transitions of CMC without                             |    |

| fe            | eedforward controller (CMC-side field data) 1                             | 36 |

| Figure 5.18 T | The transient-free transitions of T-STATCOM with                          |    |

| fe            | eedforward controller (CMC-side field data) 1                             | 37 |

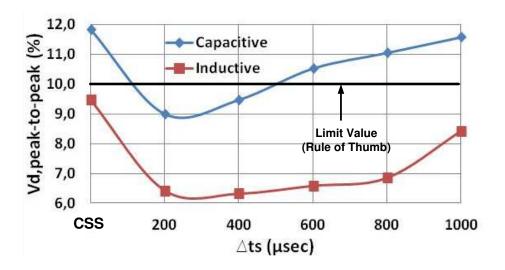

| Figure 5.19 V | Variations in the DC link voltage of an H-Bridge under                    |    |

| C             | Conventional Selective Swapping (CSS)                                     |    |

| ((            | (a) full inductive case, (b) full capacitive case, field data) 1          | 39 |

| Figure 5.20 V | Variations in the dc link voltage of an H-Bridge under                    |    |

| M             | ASS method with $\Delta t_s = 400 \ \mu s$                                |    |

| ((            | (a) full inductive case; (b) full capacitive case, field data) 1          | 40 |

| Figure 5.21 V | Variations in the dc link voltage of an H-Bridge under                    |    |

| M             | ASS method with $\Delta t_s = 200 \ \mu s$                                |    |

| ((            | (a) full inductive case; (b) full capacitive case, field data) 1          | 41 |

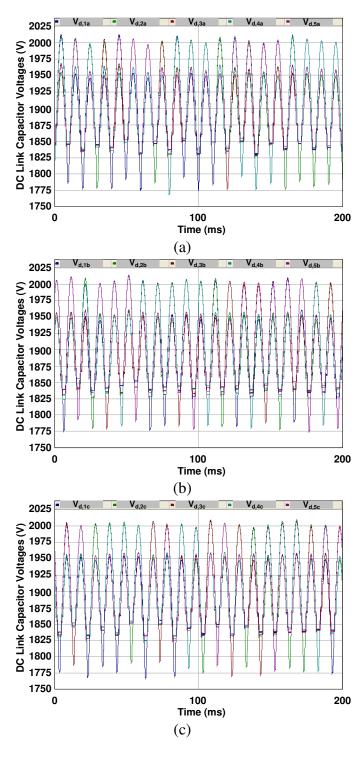

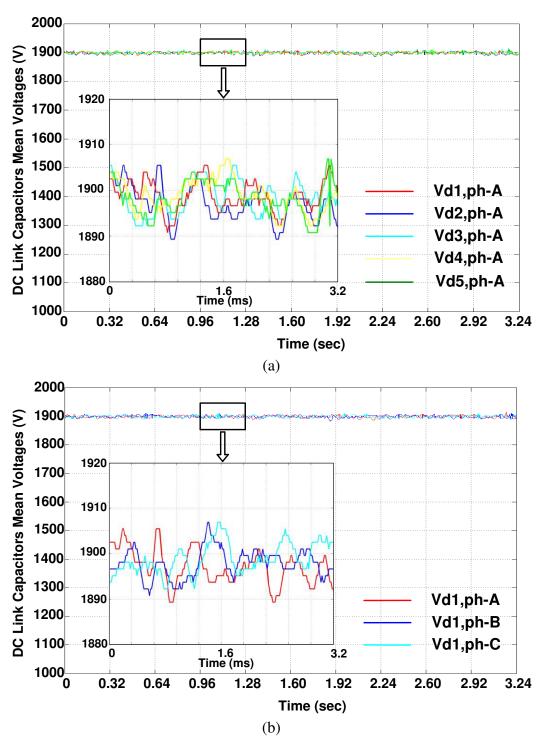

| Figure 5.22 V | Variations in the DC link mean voltages of a CMC                          |    |

| ((            | (a) DC link voltages of HBs in phase-A; (b) DC link voltages              |    |

| of HB1s in three phases, Field data)                                               |

|------------------------------------------------------------------------------------|

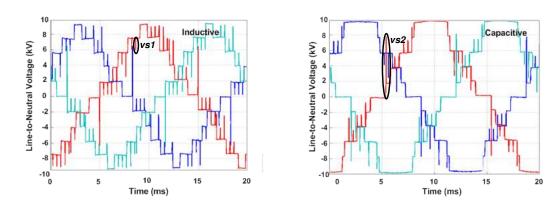

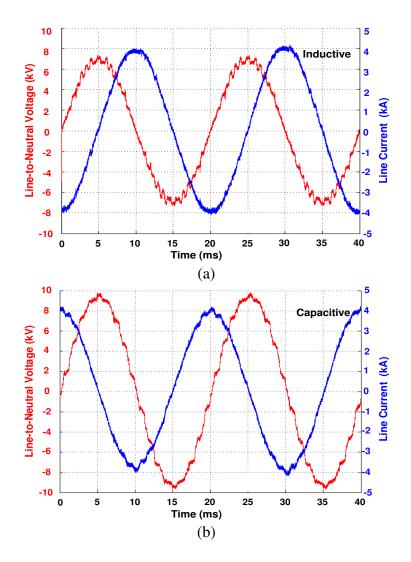

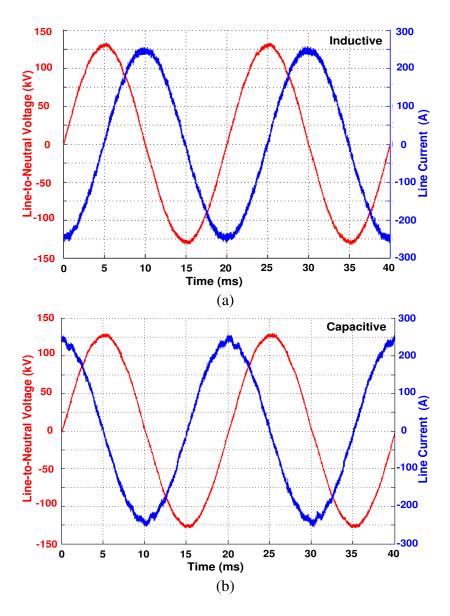

| Figure 5.23 Line-to-neutral voltage and line current waveforms at MV side of       |

| T-STATCOM ((a) full inductive; (b) full capacitive, field data) 144                |

| Figure 5.24 Line-to-neutral voltage and line current waveforms at HV side of       |

| T-STATCOM ((a) full inductive; (b) full capacitive, field data) 145                |

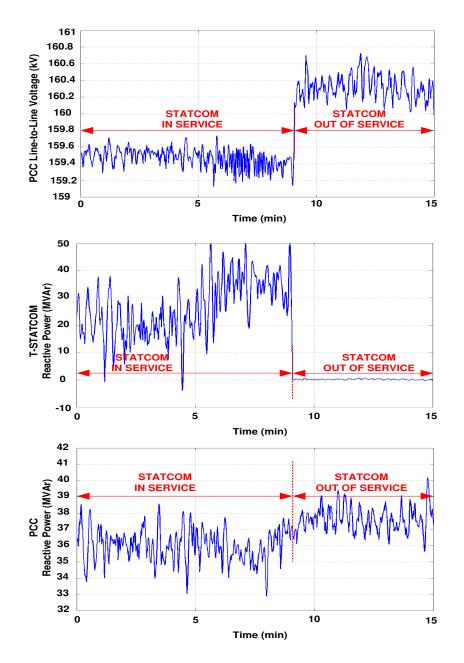

| Figure 5.25 The performance of T-STATCOM in V-mode (Field data) 149                |

| Figure 5.26 The performance of T-STATCOM in Q-mode (Field data)                    |

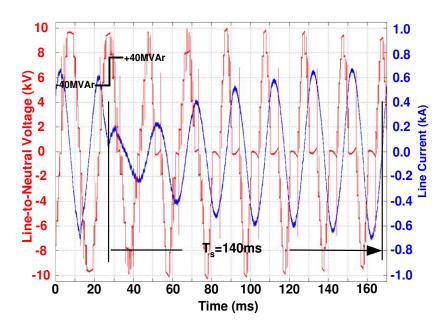

| Figure 5.27 Transition from a) from full inductive to full capacitive              |

| (10.5 kV side, field data) b) full capacitive to                                   |

| full inductive (154 kV side, field data)                                           |

| Figure 5.28 Variations in line-to-ground voltage and current during the transition |

| from full inductive to full capacitive (10.5 kV side, field data) 153              |

| Figure 5.29 Variations in line-to-ground voltage and current during the transition |

| from full capacitive to full inductive (10.5 kV side, field data) 154              |

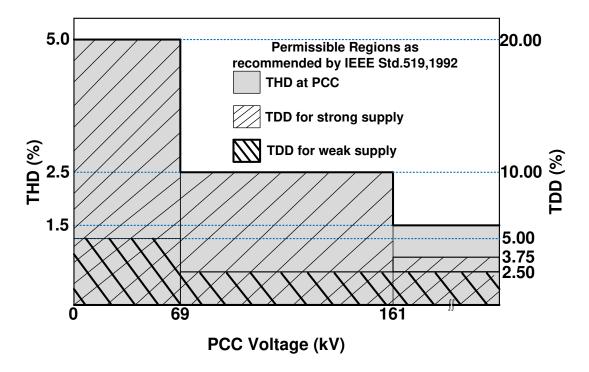

| Figure B.1 Permissible regions for total harmonic distortion (THD) and total       |

| demand distortion (TDD) as a function of rated voltage                             |

| at point of common coupling (PCC) as recommended                                   |

| by IEEE Std.519, 1992                                                              |

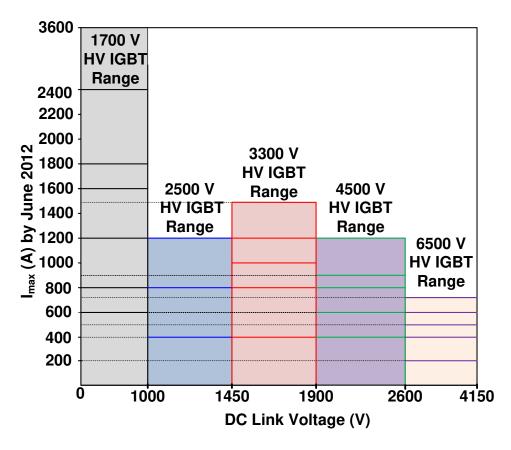

| Figure C.1 Collector current and collector-emitter voltage ratings of commercially |

| available High Voltage Insulated Gate Bipolar Transistors                          |

| (HV IGBTs) by June 2012 with respect to                                            |

| DC link voltages of HB                                                             |

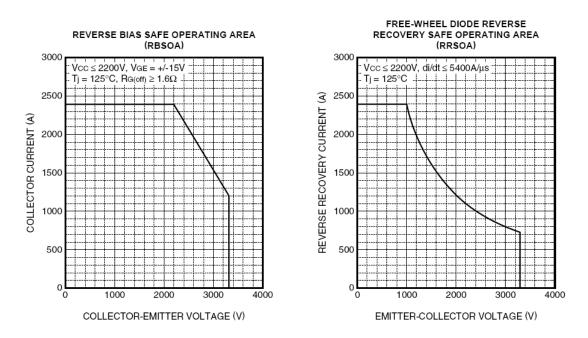

| Figure D.1 Safe Operating Areas (SOA) of HV IGBT modules specified in              |

| datasheet of MITSUBISHI CM1200HC-66H                                               |

## **NOMENCLATURE**

Es': Internal source voltage referred to CMC side

Xs': Internal source reactance referred to CMC side

PCC: Point of Common Coupling

Vs': Fundamental voltage component at Point of Common Coupling (PCC) referred to CMC side

X: Total series reactance including leakage reactance of the coupling transformer referred to CMC side and reactance of input filter reactors

R: Total series resistance including internal resistance of the coupling transformer referred to CMC side and internal resistance of the input filter reactors

Vc: Fundamental component of the CMC AC voltage

Ic: Fundamental component of the CMC line current

θ: Phase angle between  $\vec{V}_c$  and  $\vec{I}_c$

δ: Power angle between  $\overrightarrow{V}'_s$  and  $\overrightarrow{V}_c$ .

Z: Impedance angle,  $tan^{-1}(X/R)$

Ps, Qs: Active and reactive power inputs to T-STATCOM at PCC

Pc, Qc:Active and reactive power inputs to CMC

## **ABBREVIATIONS**

FACTS Flexible AC Transmission Systems

SVC Static VAr Compensators

STATCOM Static Synchronous Compensators

SC Synchronous Condensers

TCR Thyristor Controlled Reactor

D-STATCOM Distribution type STATCOM

GTO Gate Turn-off thyristors

IGBT Insulated Gate Bipolar Transistors

IEGT Injection Enhanced Insulated Gate Transistor

IGCT Integrated Gate Commutated Thyristors

MV Medium Voltage

T-STATCOM Transmission type STATCOM

MC Multilevel Converter

DCMC Diode Clamped Multilevel Converters

FCMC Flying Capacitor Multilevel Converters

CMC Cascaded Multilevel Converters

HB H-Bridge

THD Total Harmonic Distortion

PCC Point of Common Coupling

TDD Total Demand Distortion

SHEM Selective Harmonic Elimination Method

CSS Conventional Selective Swapping

MSS Modified Selective Swapping

ESL Equivalent Series Inductance

ESR Equivalent Series Resistance

RCVT RC Type Voltage Transformer

### **CHAPTER 1**

### INTRODUCTION

#### 1.1 Overview

Flexible AC Transmission Systems (FACTS) has been defined by the IEEE [1] as a power electronic based system and other static equipment that provide control of one or more AC transmission system parameters to enhance controllability and increase power transfer capability. Nowadays, FACTS are being increasingly used in power systems, to enhance the system utilization and power transfer capacity as well as the stability, security, reliability and power quality of AC system interconnections.

In general, FACTS controllers can be divided into three categories:

- 1. Series controllers,

- 2. Shunt controllers

- 3. Combined series-shunt controllers.

Among FACTS controllers, the shunt controllers have widely been used because of their problem-solving capabilities from transmission to distribution levels. It is well known that by using appropriate amount of compensated reactive current or power, the transmitted power carrying capacity can be increased and the voltage profile of the transmission line can be controlled. Also, shunt controllers can improve transient

stability, and damp power oscillations for the interconnected transmission networks. For distribution networks, they are mainly used for the purposes of power factor correction, flicker mitigation, load balancing and harmonic mitigation.

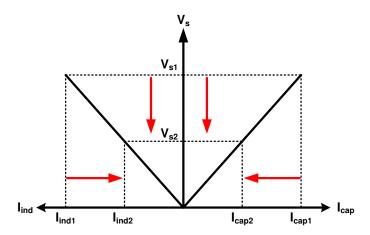

Shunt controllers can be classified as Static VAr Compensators (SVC) and Static Synchronous Compensators (STATCOM). SVCs use synchronously connected inductor and/or capacitor banks and absorb/generate controllable reactive power. The reactive power is dependent upon the system parameters especially it is directly proportional to the source voltage and any decrease in the source voltage reduce the inductive and reactive current components as shown in Figure 1.1 and hence decreases the reactive power compensation capability of SVC system Figure 1.2 shows a practical

Figure 1.1 V-I characteristic of SVC systems ( $V_s$ ,  $I_{cap}$  and  $I_{ind}$  are supply voltage, SVC capacitive and inductive currents, respectively)

Figure 1.2 A practical SVC System [2]

application of an SVC system composed of Thyristor Controlled Reactor (TCR) and fixed capacitor banks installed by TUBITAK-UZAY Power Electronics Department for reactive power compensation of a ladle furnace.

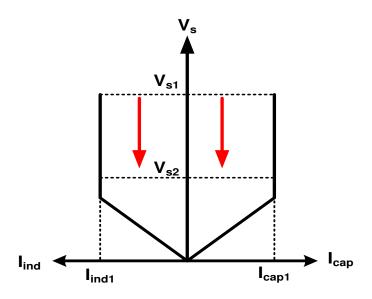

The concept of STATCOM employing turn-off-capability semiconductor based power converters instead of the use of inductor or capacitor banks for VAr generation was firstly disclosed by Gyugyi [3]. In view of reactive power operation, STATCOM systems look like Synchronous Condensers (SC) connected to the power grids. SC is in fact a synchronous generator operating at no load. By changing field current of the machine, the reactive power generated/absorbed is changed. If SC is over-excited by the field current, it generates capacitive reactive power while it is under-excited, it absorbs inductive reactive power. The major drawback of SCs is their relatively slow transient response against rapid load changes. STATCOM may give instant response to the rapidly changes of the power grid thanks to their power converters. Unlike SVCs, their reactive power capability is independent from the supply voltage variations and by switching power converters appropriately; reactive power is manipulated for both capacitive and inductive operating regions. The V-I

characteristics of STATCOM and a practical Distribution type STATCOM (D-STATCOM) system are shown in Figure 1.3 and Figure 1.4, respectively.

Figure 1.3 V-I characteristic of STATCOM systems ( $V_s$ ,  $I_{cap}$  and  $I_{ind}$  are supply voltage, STATCOM capacitive and inductive currents, respectively)

Figure 1.4 A practical D-STATCOM System [4]

Since 1980's, Static Synchronous Compensator (STATCOM) systems have been increasingly used in the transmission, distribution, and utilization of electrical energy [5-27]. Some practical applications of STATCOMs are presented in Table 1.1.

**Table 1.1 Some practical applications of STATCOM systems**

| System              | Ratings         | Converter<br>Topology       | Semiconductor<br>Switch |  |

|---------------------|-----------------|-----------------------------|-------------------------|--|

| Static VAR          | 20MVA/77kV      | Multipulse/2-level          | Conventional fast       |  |

| Generator, Japan,   |                 | Voltage Source              | switching thyristor     |  |

| 1980                |                 | Converter (VSC)             | (SCR)                   |  |

| Static VAR          | 80MVA/154kV     | Multipulse/2-level          | Conventional fast       |  |

| Generator, Japan,   |                 | VSC                         | switching thyristor     |  |

| 1993                |                 |                             | (SCR)                   |  |

| TVA STATCON,        | ±100MVAr/161kV  | Multipulse/2-level          | 4.5kV/4.0kA GTO         |  |

| Tennessee, 1995     |                 | VSC                         |                         |  |

| Seattle Iron&Metals | 5MVA/4.16kV     | 2-level VSC                 | 1.2kV/0.6kA IGBT        |  |

| D-STATCOM,          |                 |                             |                         |  |

| Washington, 1999    |                 |                             |                         |  |

| Henan STATCOM,      | 20MVA/220kV     | Multipulse/2-level          | 4.5kV/4.0kA GTO         |  |

| China, 1999         |                 | VSC                         |                         |  |

| VELCO               | 2x43MVA/115KV   | 2-level VSC                 | 6.0kV/6.0kA GTO         |  |

| STATCOM,            |                 |                             |                         |  |

| Vermont-USA,        |                 |                             |                         |  |

| 2001                |                 |                             |                         |  |

| SDG&E Talega        | ±100MVAr/138kV  | 2-level VSC                 | 6.0kV/6.0kA GTO         |  |

| STATCOM,            |                 |                             |                         |  |

| California, 2002    |                 |                             |                         |  |

| STATCOM Based       | ±75MVAr/275kV   | Cascaded Multilevel         | 6.0kV/6.0kA GTO         |  |

| Relocatable SVC,    | and             | Converter (CMC), $\Delta$ - |                         |  |

| England, 2001       | 400kV           | Connected                   |                         |  |

| Convertible Static  | 2x(±100MVAr)/   | 3-level Diode               | Series operation of     |  |

| Compensator, New    | 345 kV          | Clamped Multilevel          | GTOs                    |  |

| York, 2003          |                 | Converter (DCMC)            |                         |  |

| Shinkansen          | 60MVA/ 77kV     | 2-level VSC                 | Series operation of     |  |

| STATCOM, Japan,     |                 |                             | 2.5kV/1.8kA Flat        |  |

| 2003                |                 |                             | Packaged IGBTs          |  |

| Holly STATCOM,      | ±95MVAr/138kV   | 3-level Diode               | Series operation of     |  |

| Texas, 2004         |                 | Clamped Multilevel          | 2.5kV/1.8kA Press-      |  |

|                     |                 | Converter (DCMC)            | Pack IGBTs              |  |

| Tinaz STATCOM,      | ±0.75MVAr/36 kV | 2-level Current             | 4.5kV/4.0kA IGCT        |  |

| Muğla, 2005         |                 | Source Converter            |                         |  |

|                     |                 | (CSC)                       |                         |  |

| SVC Plus, New       | 2x(±50MVAr)/    | Modular Multilevel          | Press-Pack IGBT         |  |

| Zeland, 2009        | 220 kV          | Converter (MMC)             |                         |  |

In these practical STATCOM systems implemented in the field, various power semiconductors have been employed i.e., silicon-controlled rectifiers (conventional fast switching thyristors) [5], Gate Turn-off thyristors (GTO) [6,7,9-11,14], Insulated Gate Bipolar Transistors (IGBT) [8,12,13,15,16,19-22,26,27], Injection Enhanced Insulated Gate Transistor (IEGT) [15] and Integrated Gate Commutated Thyristors (IGCT) [18,23-25]. Two-level, six-pulse bridge converters with relatively high switching frequencies and relatively low installed capacities are usually being the characteristics of Distribution type STATCOM (D-STATCOM) systems [18, 23-25]. These are usually connected to the Medium Voltage (MV) load bus via a step-up coupling transformer. However, Transmission type STATCOM (T-STATCOM) systems have much higher installed capacities and therefore the power semiconductors in their converter system/s should be switched at lower frequencies. That is why in practical applications of T-STATCOM systems either multi-pulse converters based on two-level six-pulse bridge [5-7,9,15] or three-level Neutral Point Clamped (NPC) [17] converters with inter-magnetics or Multilevel Converter (MC)s [10-14,16,18,19-21] are to be utilized. Cascaded Multilevel Converter (CMC)s [12,20-22],Diode Clamped Converter and Multilevel (DCMC)s [10,11,13,14,16,18,19] are generally employed in field prototypes or commercial types of T-STATCOM applications. These systems are connected to the High Voltage (HV) or extra high voltage (EHV) buses of the transmission systems via coupling transformers.

Various topologies, modulation methods, control techniques and application areas of MCs are reviewed in [28-33]. In literature, Multilevel Converters for T-STATCOM applications are classified in three groups:

- a) Diode Clamped Multilevel Converters (DCMC),

- b) Flying Capacitor Multilevel Converters (FCMC),

- c) Cascaded Multilevel Converters (CMC).

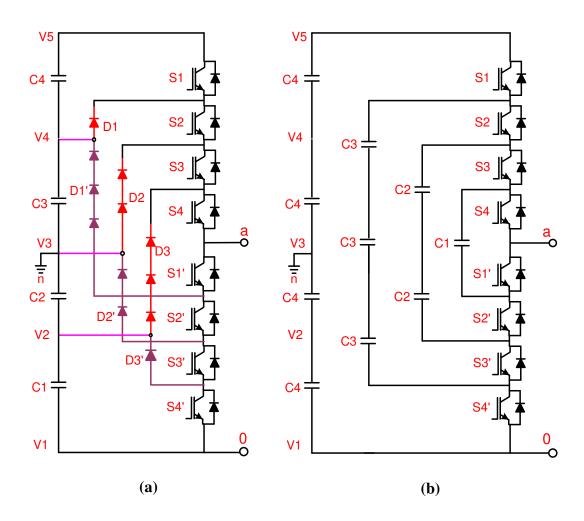

The single line diagram and the output voltage waveform of the 5-level DCMC and FCMC are given in Figure 1.5 and Figure 1.6. In DCMC, clamping diodes are used to divide up the DC link voltage for the voltage levels by using series capacitors. The clamping diodes balance out the voltage sharing between the semiconductor switches which are not triggered into conduction. To have the same reverse voltage blocking capability, series operation of clamping diodes are employed. As the number of level increases for the DCMC output voltage, the number of clamping diodes also increases. Due to this fact, DCMC is impractical for high voltage high applications.

Figure 1.5 One phase single line diagrams of 5-level a) DCMC and b) FCMC

Figure 1.6 The output voltage waveform of 5-level DCMC and 5-level FCMC

In FCMC, instead of clamping diodes in DCMC, clamping capacitors are used in addition to the main DC link capacitors to obtain a staircase output voltage waveform shown by Figure 1.6. By using proper clamping capacitor combinations, it is possible to control the charging of clamping capacitors. As the number of level increases, the number of clamping capacitors increases as well.

To obtain 5-level output voltage waveform shown in Figure 1.6, two series connected H-Bridge (HB) circuits as shown in Figure 1.7 are used. The multilevel converter topology based on the series connection of HBs is called Cascaded Multilevel Converter (CMC). Since CMC topology is based on H-Bridge (HB) circuits connected in series, it has the advantage of modularity and flexibility. Modularized circuit layout and packaging is possible due to the usage of the same structure for each level and there is no need to use clamping diodes or capacitors required for DCMC and FCMC. The modular structure also gives the opportunity to adjust the number of output voltage levels easily by changing only the number of HBs in series.

The comparison of M-level DCMC, FCMC and CMC is given in Table 1.2 in accordance with the number of total power components needed for 3-phase application. The voltage ratings of the devices are taken as equal to have a fair comparison among the converter topologies.

Figure 1.7 One phase single diagram of 5-level CMC

Table 1.2 The total number of required power components for M-level DCMC, FCMC and CMC

| M-level Converter Topology           |               |                 |           |  |  |  |

|--------------------------------------|---------------|-----------------|-----------|--|--|--|

| Converter Type                       | DCMC          | FCMC            | CMC       |  |  |  |

| Number of Switching Device           | 3x2x(M-1)     | 3x2x(M-1)       | 3x2x(M-1) |  |  |  |

| Number of DC Link Capacitors         | M-1           | M-1             | 3x(M-1)/2 |  |  |  |

| Number of Clamping Diodes            | 3x(M-1)x(M-2) | 0               | 0         |  |  |  |

| <b>Number of Clamping Capacitors</b> | 0             | 3x(M-1)x(M-2)/2 | 0         |  |  |  |

Although it requires more main DC link capacitors, the least number of needed power components is achieved by the utilization of M-level CMC as can be seen from Table 1.2. A very high amount of the total capacitance is required for the

FCMC topology. This is unacceptable for high voltage levels due to the equalization problem of capacitors as well as the high cost. In DCMC topology with higher levels than three-level configuration, oversized capacitors or complex balancing circuits and methods should be employed in high voltage-high power applications for the equalization problem of DC link capacitors. The usage of series connected clamping diodes also yields the need of voltage sharing circuits which complicates the packaging of practical applications. Due to its modularity, flexibility and less number of power components, CMC topology is the most promising alternative for T-STATCOM applications among the multilevel converters. It is possible to reach high voltage levels by the use of more HBs in series for CMC topology. The only problem is the balancing of the individual DC link capacitor voltages of each HB. This problem can be overcome by employing some equalization methods.

The major operational problem of CMCs is the equalization of DC link capacitor voltages. The equalization of DC link capacitor voltages are investigated and some novel strategies are recommended in [34-52] for various CMC topologies. Commercial CMC-based T-STATCOMs employ either GTO or GCT/IGCT devices with inverse-parallel connected power diodes. To limit di/dt overvoltages on GTOs during turn-off operation, bulky snubber circuits were used [12]. To equalize individual capacitor voltages, high frequency IGBT based auxiliary circuits supplied from low voltage side were employed. Specially designed isolating transformers were used to isolate auxiliary circuits from the power stage of CMC.

An important contribution to the solution of voltage equalization problem of DC link capacitors is known as the Selective Swapping Algorithm [50-52] which can be embedded in the control algorithm of CMC, thus eliminating the need for bulky auxiliary circuits. Although the effectiveness of voltage equalization algorithm decreases as the number of H-bridges connected in series and/or peak-to-peak ripple content of the capacitor voltage increase/s, it provides the lowest switching frequency for the power semiconductors.

## 1.2 Scope of the Thesis

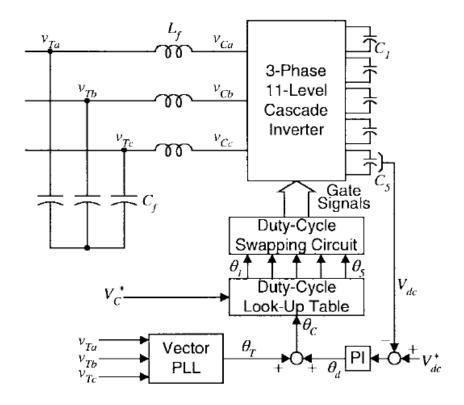

This research and technology development work deals with the sizing, system and power-stage designs of an HV IGBT based CMC for T-STATCOM applications. System design and the number of H-Bridge (HB)s in each phase of the Y-connected CMC are achieved in view of Total Harmonic Distortion (THD) at Point of Common Coupling (PCC), and also of Total Demand Distortion (TDD) of the line currents and individual harmonic current limits recommended by IEEE Std.519-1992. A 12 kV, ±10 MVAr, 11-level CMC Module power stage with five HBs in each phase is designed and then implemented to deliver ±10MVAr to 154kV transmission bus (PCC) via a series filter reactor and 154/10.5kV coupling transformer. Therefore, the CMC Module presented in this work constitutes the building block of large T-STATCOM systems. The Selective Harmonic Elimination Method (SHEM) is applied to synthesize T-STATCOM voltage waveforms at power frequency (50Hz) and the Modified Selective Swapping (MSS) Algorithm is exercised to balance the DC link capacitor voltages, perfectly at the expense of higher switching frequency, and hence switching losses. The power stage is carefully designed and its performance is optimized in view of the current HV IGBT technology.

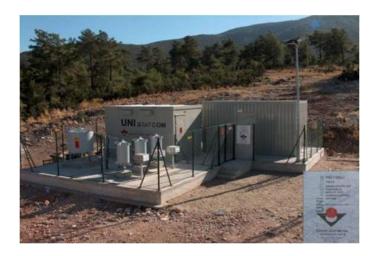

A 154kV, ±50 MVAr, 11-level T-STATCOM system by the parallel use of five CMCs built in this work has been implemented in the field primarily for the purposes of reactive power compensation and terminal voltage regulation, and secondarily for power system stability. Since the operating voltage of CMC is chosen to be 10.5 kV (max.12 kV) line-to-line, it is connected to 154 kV line-to-line transmission bus through a specially designed 50/62.5 MVA Y-Y connected (YNyn vector group) coupling transformer and each CMC module is connected to the secondary side of the coupling transformer via a series filter reactor bank.

This research work has made the following original contributions to the area of Cascaded Multilevel Converter based Transmission STATCOM Systems:

- Optimized design for the sizing, system and power stage of Cascaded

Multilevel Converter based T-STATCOM systems has been investigated.

- A 12kV, ±10MVAr HV IGBT based CMC has been designed and implemented as a building block of large T-STATCOM systems. Then, a 154kV, ±50MVAr Transmission STATCOM system based on five of this CMC is implemented in the field for the purposes of reactive power compensation and terminal voltage regulation as well as power stability improvement [21].

- The effect of total series inductance on system design has been investigated in details.

- The Conventional Selective Swapping (CSS) Method has been modified and the effect of swapping time on the system performance has been exercised. The comparison of Conventional and Modified Selective Swapping Algorithms has also been presented by the computer simulations and field results.

- The switching strategies have been discussed for Selective Swapping Methods and alternatives for eliminating or reducing the voltage spikes as a result of swappings have also been declared.

- This is the first application of CMC based T-STATCOM with wire-bond HV IGBTs and Modified Selective Swapping (MSS) Algorithm in the world. Thanks to MSS method, the usage of bulky auxiliary circuits for equalization of the DC link voltages has been eliminated and a compact H-Bridge (HB) unit has been designed and implemented.

#### The outline of the thesis is given below:

In Chapter 2, operation principles of the Cascaded Multilevel Converter based T-STATCOM systems have been discussed in detail. Active and Reactive power control with waveform synthesizing used for STATCOM systems are clearly presented. Moreover, the methods proposed in the literature for the equalization

problem of DC link capacitors used for CMCs have been reviewed with the details of the Modified Selective Swapping Algorithm.

Chapter 3 presents the system design and sizing for CMC and T-STATCOM systems. The major considerations for determining the connection point of T-STATCOM systems are given in view of Total Harmonic Distortion (THD) at Point of Common Coupling (PCC), Total Demand Distortion (TDD) of the line currents and individual harmonic current limits recommended by IEEE Std.519- 1992. Also, the effect of total series inductance on the system performance has been investigated in detail.

The design issues including HB circuit, control system and switching strategies for the application of selective swapping methods for Cascaded Multilevel Converters have been presented in Chapter 4. The choice of power semiconductors and capacitors used in each HB are given with the design details of the laminated busbar with 3-conducting layer.

In Chapter 5, the system implementation with the field performance results have been demonstrated. The waveforms and technical results of the system performance have been given.

Conclusions and recommendations for the future work are given in Chapter 6. All the theoretical and practical considerations of the thesis study is justified and concluded in this chapter once more.

#### **CHAPTER 2**

# OPERATING PRINCIPLES OF CMC BASED TRANSMISSION STATCOM

## 2.1 System Description

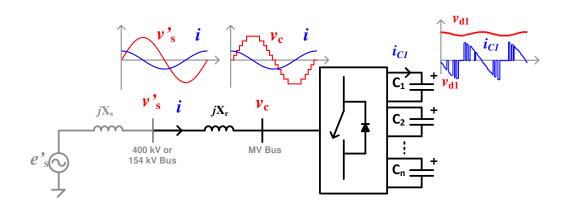

Figure 2.1 shows single line diagram of a Transmission type Static Synchronous Compensator (T-STATCOM) based on a single Cascaded Multilevel Converter (CMC). It is shown to be connected to Extra High Voltage (EHV) or High Voltage (HV) busbar of the transmission system via a medium voltage (MV) to EHV or HV coupling transformer. Therefore, in Figure 2.1,  $X_r$  represents the total leakage reactance of

Figure 2.1 Single line diagram of a T-STATCOM based on a single CMC

the coupling transformer and if needed the reactance of the series filter reactor. Waveforms of EHV or HV bus voltage,  $v_s$ ', line current of T-STATCOM, i, AC voltage of the CMC,  $v_c$ , voltage of each DC link capacitor,  $v_{d1}$ , and the current through each DC link capacitor,  $i_{C1}$  are also sketched on Figure 2.1.  $e_s$ ',  $X_s$ ' and  $v_s$ ' are respectively internal source voltage, source reactance and EHV or HV bus voltage all referred to the CMC side.

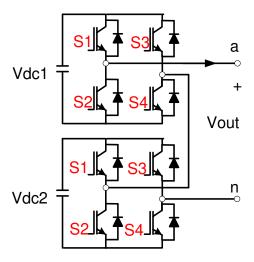

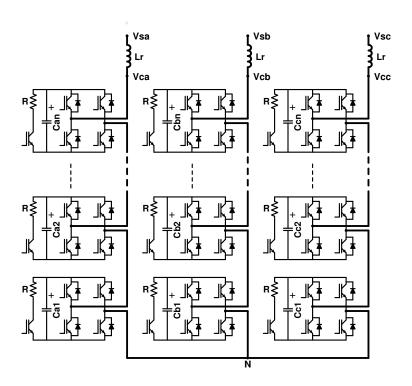

Circuit diagram of star-connected CMC consisting of n number of series connected H-Bridges (HBs) in each phase is as shown in Figure 2.2. n seriesly connected H-Bridges give l=2n+1 steps in line-to-neutral voltage waveforms and l=4n+1 steps in line-to-line voltage waveforms, where l is the number of levels from positive peak to negative peak of the waveform under consideration. The DC link of each HB in the CMC is equipped with a DC/DC converter controlled discharge resistor (R) to discharge C when the CMC is disconnected from the supply for inspection or maintenance purpose.  $L_r$  is the equivalent inductance of the total filter reactance,  $X_r$ , in Figure 2.1. A T-STATCOM system operates at power frequency (50Hz or 60Hz) as a shunt connected Flexible AC Transmission System (FACTS) device and performs one or more than one of the following functions at the EHV or HV bus to which the T-STATCOM is connected:

- a. Terminal Voltage Regulation

- b. Control of Reactive Power Flow in O/H Lines

- c. Power System Stability Improvement

These are achieved by continuously varying the reactive power generated by the T-STATCOM in both capacitive and inductive regions as will be described in the forgoing sections.

Figure 2.2 Circuit diagram of a star-connected CMC consisting of n series connected HBs in each phase

#### 2.2 Active and Reactive Power Control

Single-phase Y-equivalent circuit model of the T-STATCOM and its phasor diagram are given in respectively in Figure 2.3 and Figure 2.4, where:

E<sub>s</sub>': Internal source voltage referred to CMC side

X<sub>s</sub>': Internal source reactance referred to CMC side

PCC: Point of Common Coupling

$V_s$ ': Fundamental voltage component at Point of Common Coupling (PCC) referred to CMC side

X: Total series reactance including leakage reactance of the coupling transformer referred to CMC side and reactance of input filter reactors

Figure 2.3 Simplified single line diagram of T-STATCOM

Figure 2.4 Phasor diagram for lossy system (exaggerated)

- R: Total series resistance including internal resistance of the coupling transformer referred to CMC side and internal resistance of the input filter reactors

- V<sub>c</sub>: Fundamental component of the CMC AC voltage

I<sub>c</sub>: Fundamental component of the CMC line current

θ: Phase angle between  $\vec{V}_c$  and  $\vec{I}_c$

δ: Power angle between  $\overrightarrow{V}_s$  and  $\overrightarrow{V}_c$

$\phi$ : Impedance angle,  $\tan^{-1}(X/R)$

P<sub>s</sub>, Q<sub>s</sub>: Active and reactive power inputs to T-STATCOM at PCC

P<sub>c</sub>, Q<sub>c</sub>: Active and reactive power inputs to CMC

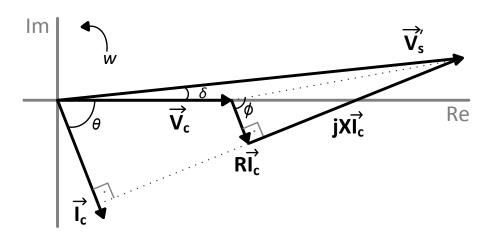

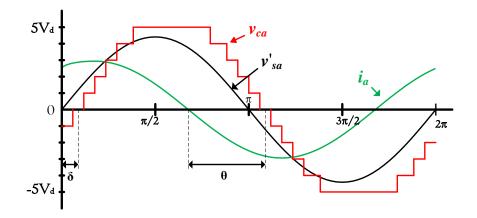

The definitions of  $\theta$  and  $\delta$  are expressed by the aid of Figure 2.5.

Figure 2.5 The definitions of  $\delta$  and  $\theta$

In Figure 2.4, all voltages and currents are fundamental values and active and reactive powers are per phase values.  $P_s$ ,  $P_c$ ,  $Q_s$  and  $Q_c$  in Figure 2.3 can be expressed respectively as in (1.1)-(1.4), in terms of terminal quantities  $V_s$  and  $V_c$  and angles  $\theta$  and  $\delta$  without consideration of harmonic components due to their negligible effects.

$$P_s = V_s' I_c \cos(\theta + \delta) \tag{1.1}$$

$$P_c = V_c I_c \cos \theta \tag{1.2}$$

$$Q_s = V_s' I_c \sin(\theta + \delta) \tag{1.3}$$

$$Q_c = V_c I_c \sin \theta \tag{1.4}$$

Since  $\vec{V}_c = V_c \angle 0$ ,  $\vec{I}_c = I_c \angle (-\theta)$ ,  $\vec{V'}_s = \vec{V'}_s \angle \delta$ ;

T-STATCOM Current is

$$\vec{l}_c = (\vec{V'}_s - \vec{V}_c)/(R + jX)$$

. (1.5)

Complex power input to T-STATCOM:

$$\vec{S}_S = P_S + jQ_S = \vec{V}_S' \vec{I}_C^* \tag{1.6}$$

$$\vec{S}_{S} = \vec{V}_{S}' (\vec{V}_{S}' - \vec{V}_{C}/R + jX)^{*} = (V_{S}'^{2} - V_{S}'V_{C}(\cos\delta + j\sin\delta))/(R - jX)$$

(1.7)

Multiplying numerator and denominator by (R+jX):

$$\vec{S}_{s} = (V'_{s}^{2}R + jV'_{s}^{2}X - V'_{s}V_{c}[R\cos\delta - X\sin\delta + j(R\sin\delta + X\cos\delta)])/Z^{2}$$

(1.8) where,  $Z = \sqrt{(R^{2} + X^{2})}$ .

Real power input to T-STATCOM:

$$P_{s} = Re\{\vec{S}_{s}\} = (V'_{s}[V_{c}X\sin\delta - V_{c}R\cos\delta + V'_{s}R]/Z^{2})$$

$$\tag{1.9}$$

Reactive power input to T-STATCOM:

$$Q_s = Im\{\vec{S}_s\} = (V_s'[V_s'X - V_cX\cos\delta - V_cR\sin\delta]/Z^2)$$

(1.10)

Complex power input to CMC:

$$\vec{S}_c = P_c + jQ_c = \vec{V}_c \vec{I}_c^* \tag{1.11}$$

$$\vec{S}_c = \vec{V}_c \left( \vec{V'}_s - \vec{V}_c / R + jX \right)^* = (V'_s V_c (\cos \delta - j \sin \delta) - V_c^2) / (R - jX)$$

(1.12)

Multiplying numerator and denominator by (R+jX):

$\vec{S}_c = (V'_s V_c [R\cos\delta + X\sin\delta + j(X\cos\delta - R\sin\delta) - V_c^2 R - jV_c^2 X])/Z^2 \quad (1.13)$

Real power input to CMC:

$$P_c = Re\{\vec{S}_c\} = (V_c[V_s'X\sin\delta + V_s'R\cos\delta - V_cR]/Z^2)$$

(1.14)

Reactive power input to CMC:

$$Q_c = Im\{\vec{S}_c\} = (V_c[V'_s X \cos \delta - V_c X - V'_s R \sin \delta]/Z^2)$$

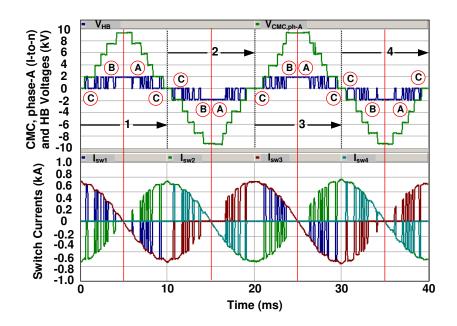

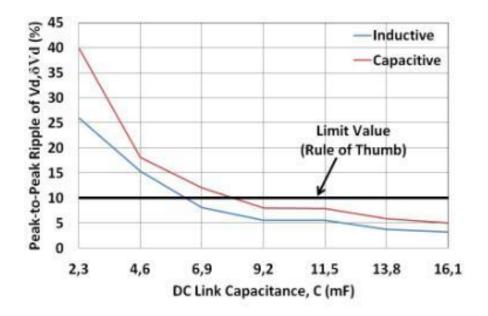

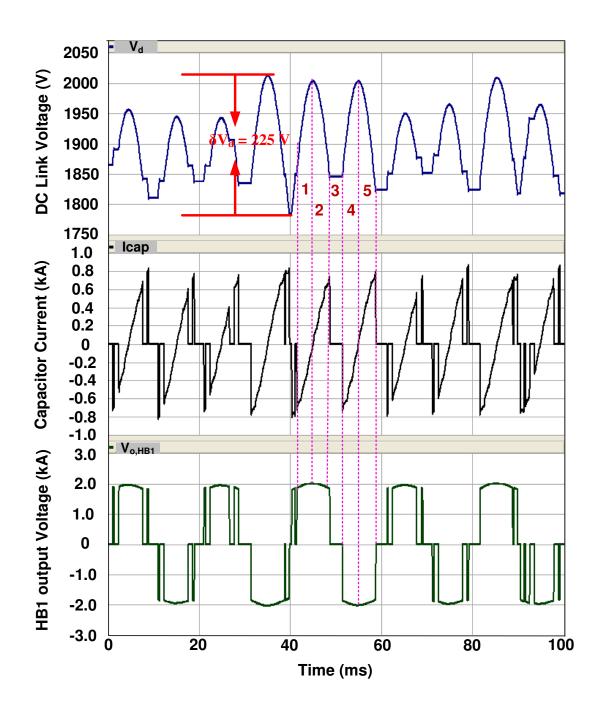

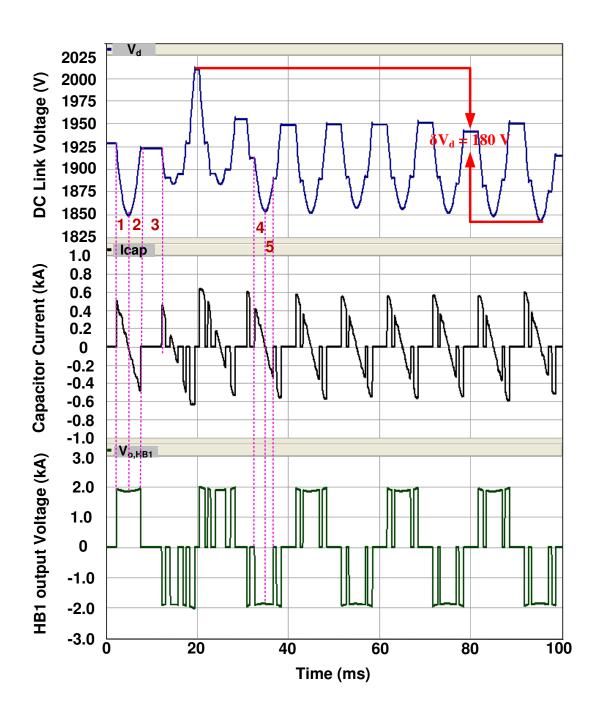

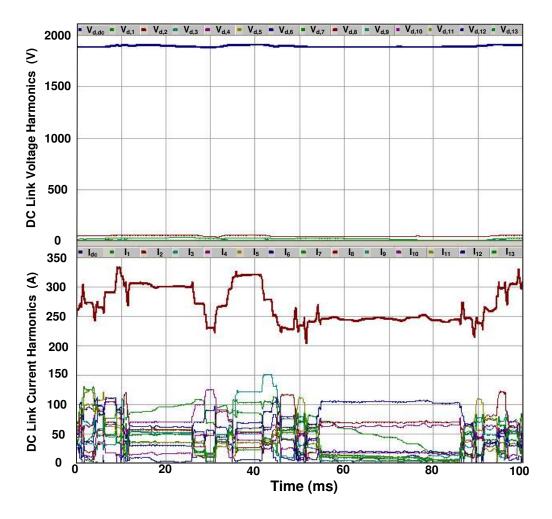

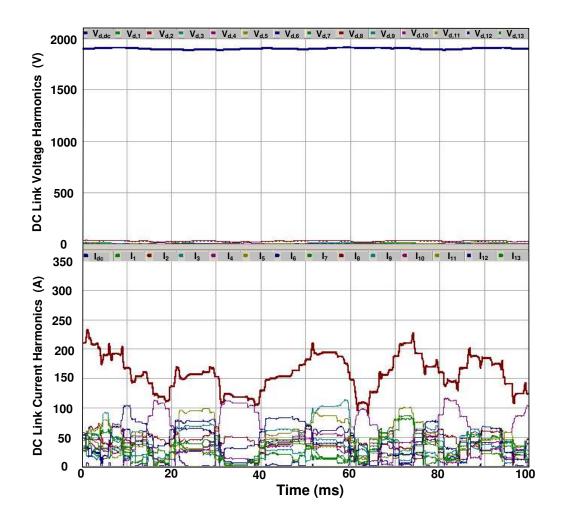

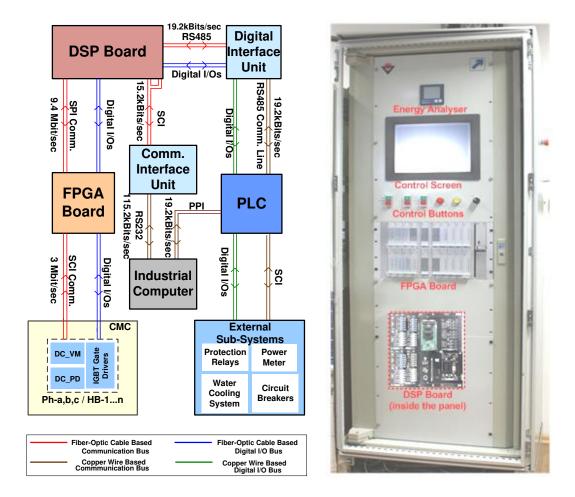

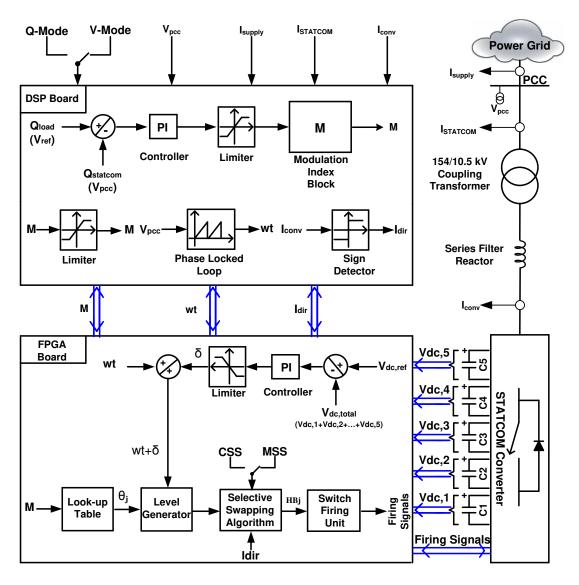

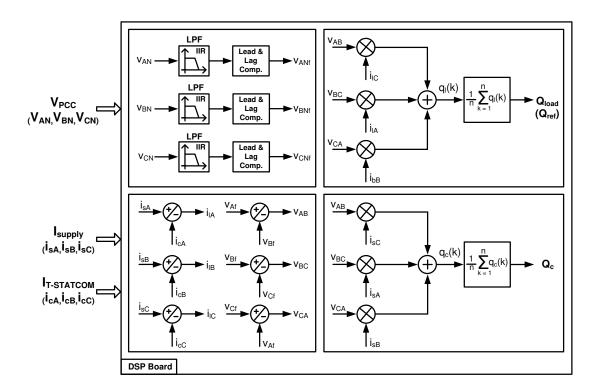

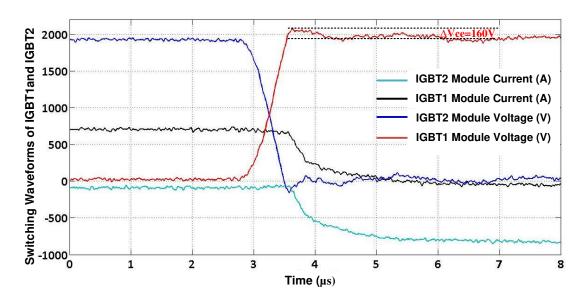

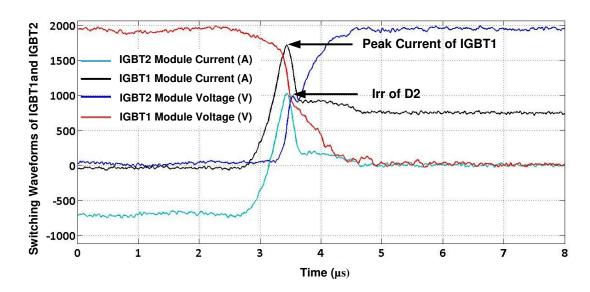

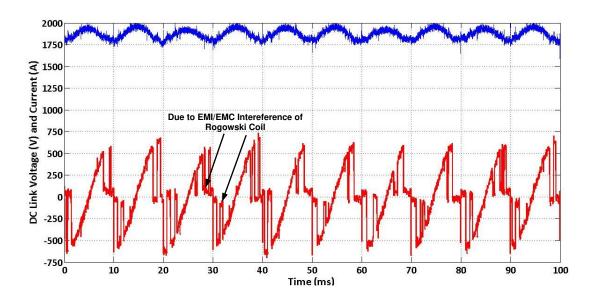

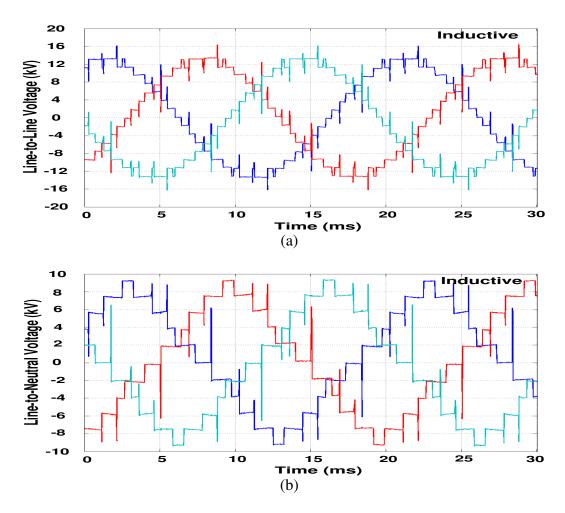

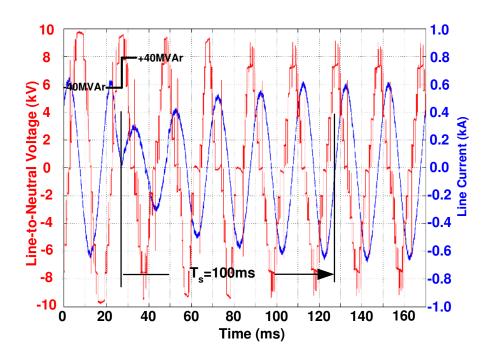

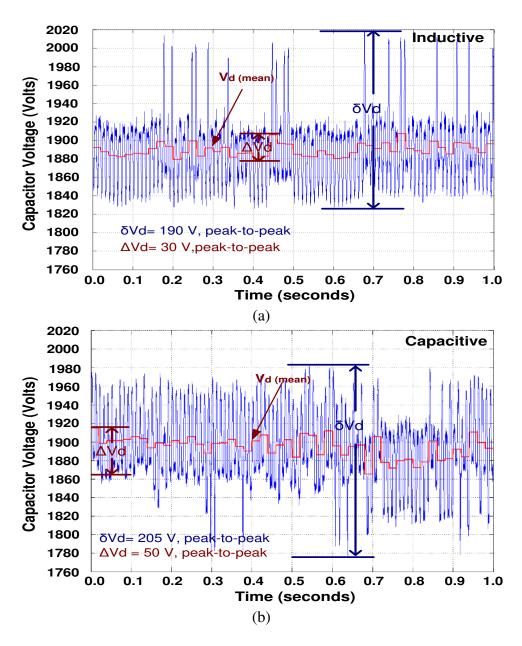

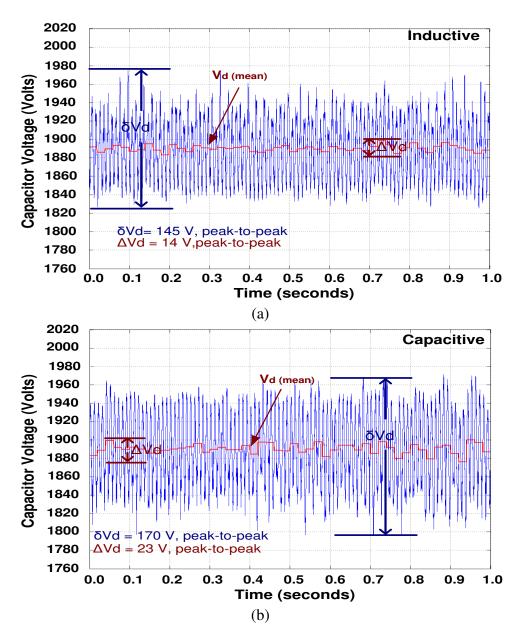

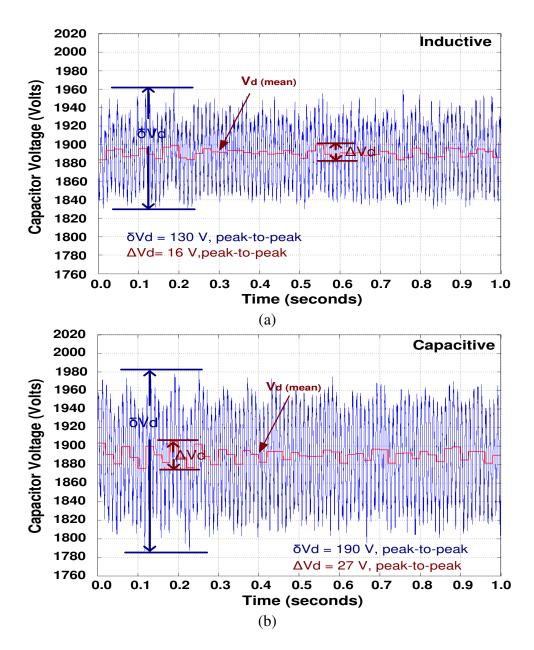

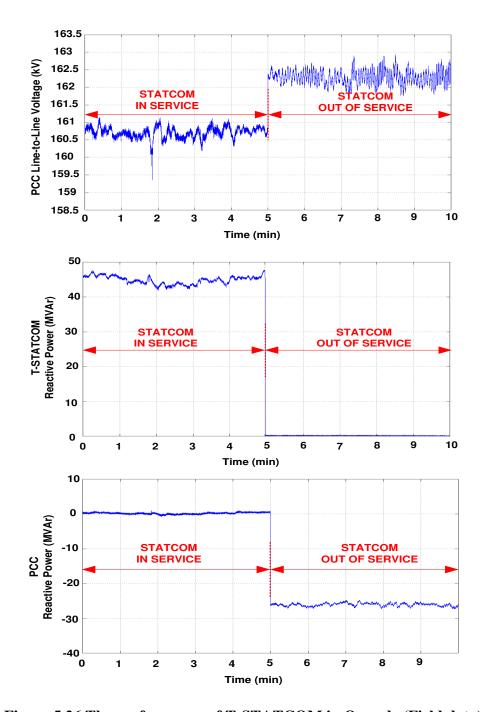

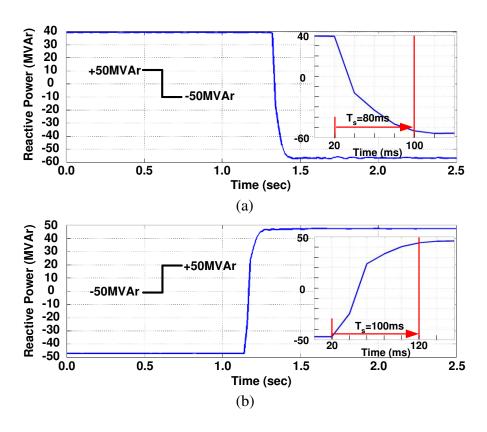

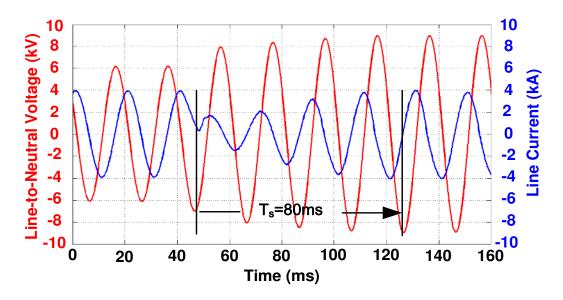

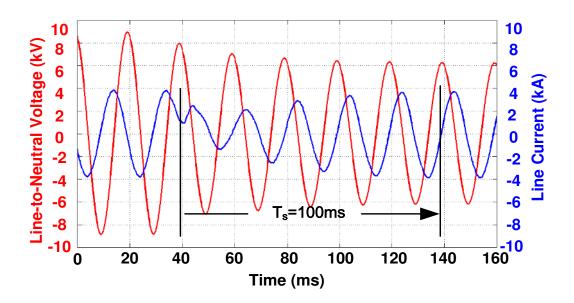

$$\tag{1.15}$$