**Delft University of Technology**

# Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures

Incandela, Rosario M.; Song, Lin; Homulle, Harald; Charbon, Edoardo; Vladimirescu, Andrei; Sebastiano, Fabio

**DOI** 10.1109/JEDS.2018.2821763

Publication date 2018 Document Version Final published version Published in IEEE Journal of the Electron Devices Society

# Citation (APA)

Incandela, R. M., Song, L., Homulle, H., Charbon, E., Vladimirescu, A., & Sebastiano, F. (2018). Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures. *IEEE Journal of the Electron Devices Society*, *6*. https://doi.org/10.1109/JEDS.2018.2821763

# Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

## Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Characterization and Compact Modeling of Nanometer CMOS Transistors at Deep-Cryogenic Temperatures

Rosario M. Incandela, *Student, IEEE, Lin Song, Harald Homulle, Edoardo Charbon, Fellow, IEEE, Andrei Vladimirescu, Fellow, IEEE, and Fabio Sebastiano, Senior Member, IEEE*

Abstract—Cryogenic characterization and modeling of two nanometer bulk CMOS technologies (0.16- $\mu$ m and 40-nm) are presented in this paper. Several devices from both technologies were extensively characterized at temperatures of 4 K and below. Based on a detailed understanding of the device physics at deepcryogenic temperatures, a compact model based on MOS11 and PSP was developed. In addition to reproducing the device DC characteristics, the accuracy and validity of the compact models are demonstrated by comparing time- and frequency-domain simulations of complex circuits, such as a ring oscillator and a low-noise amplifier (LNA), with the measurements at 4 K.

*Index Terms*—Cryogenic electronics, CMOS, cryogenic, cryo-CMOS, characterization, modeling, kink, 4 K, LNA.

#### I. INTRODUCTION

▼RYOGENIC electronics plays a fundamental role in several applications, such as spacecraft, high-energy physics experiments, metrology, superconductive astronomical detectors and, with the increased interest in quantum computing, the manipulation of quantum bits (qubits) [1]-[5]. Most qubits are placed in the coldest chamber of dilution refrigerators, where temperatures reach values in the range of 10-100 mK, in order to expose their quantum behavior and extend the lifetime of their quantum state. State-of-the-art quantum processors typically consist of a few qubits that are controlled and read out by general-purpose electronics operating at roomtemperature [6]–[8]. Only a few components, such as the first amplification stages, operate at cryogenic temperatures (1-4 K) in order to reduce their noise level [9], [10]. Nonetheless, future quantum computers would require millions of qubits to run any algorithm with practical applications, such as the simulation of a complex molecule [11]. Thus, an enormous amount of room-temperature electronics and, consequently,

R. M. Incandela and H. Homulle are with the Department of Quantum and Computer Engineering, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with QuTech and Kavli Institute of Nanoscience, 2628 CJ Delft, The Netherlands.

L. Song was with Delft University of Technology, 2628 CD Delft, The Netherlands, and now is with Analog Devices, Inc., Beijing 100192, China.

E. Charbon is with Kavli Institute of Nanoscience, 2628 CJ Delft, The Netherlands, with EPFL, 1015 Lausanne, Switzerland and also with Intel, Hillsboro, OR 97124 USA.

A. Vladimirescu is with the University of California at Berkeley, Berkeley, CA 94708 USA, and also with the Institut Supérieur d'Électronique de Paris, 75006 Paris, France.

F. Sebastiano is with the Department of Microelectronics and the Department of Quantum and Computer Engineering, Delft University of Technology, 2628 CD Delft, The Netherlands, and also with QuTech, 2628 CJ Delft, The Netherlands.

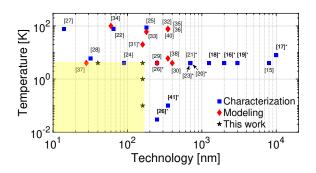

Fig. 1. Summary of CMOS technologies measured at cryogenic temperatures. The works on characterization are indicated by blue squares while attempts at modeling by red diamonds. The references with an asterisk showed kink.

an unpractical number of wires to connect such electronics to the qubits would be required. A viable alternative is to place the electronics much closer to the qubits [12]-[14]: a few circuits would operate at the qubit temperature (10-100 mK), while most of the electronics would be placed at 4 K, i.e. the lowest temperature at which existing dilution refrigerators can still provide a relatively large cooling power ( $\approx 1$  W). Among electronic technologies operating at those temperatures, only CMOS can provide the high level of integration required to reliably manipulate such a large number of qubits. However, although compact simulation models are crucial for the design of the high-performance circuits necessary for a large-scale quantum computer, the characterization and modeling of nanometer CMOS devices at cryogenic temperatures are not yet adequate. The use of nanometer CMOS nodes is particularly relevant to build lowpower circuits for quantum-computing applications, since the handling of high-frequency and large-bandwidth signals is required for qubit control. As shown in Fig. 1, several CMOS technologies have been characterized at temperatures below 77 K [15]–[41], but only [24], [37] and [39] address quantumcomputing needs, i.e. nanometer technologies (below 0.18  $\mu$ m) necessary for high-speed circuits (> 10 GHz), operating at 4 K or below where qubits can, in theory, still operate and the cooling power of state-of-the-art dilution refrigerator enables the placement of large integrated circuits. Furthermore, very few cryogenic models have been developed [29]-[39] with only [37] and [39] (of which this paper is an extension) recently focusing on the region of interest. In this paper,

2168-6734 (c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

TABLE I SUMMARY OF CHARACTERIZED DEVICES.

| Technology                  | SSMC        | 0.16 µm      | ST 40 nm    |             |  |

|-----------------------------|-------------|--------------|-------------|-------------|--|

| Oxide                       | Thick       | Thin         | Thick       | Thin        |  |

| Nominal V <sub>DD</sub> [V] | 3.3         | 1.8          | 2.5         | 1.1         |  |

| <b>W/L</b> [μm / μm]        | 2 / 1.61    | 2.32 / 1.6   | 1.6 / 1.35  | 1.2 / 0.4   |  |

|                             | 2 / 0.322   | 2.32 / 0.16  | 1.6 / 0.27  | 1.2 / 0.04  |  |

|                             | 0.4 / 1.61  | 0.232 / 1.6  | 0.32 / 1.35 | 0.12 / 0.4  |  |

|                             | 0.4 / 0.322 | 0.232 / 0.16 | 0.32 / 0.27 | 0.12 / 0.04 |  |

we present the characterization and SPICE modeling of two CMOS nanometer technologies (0.16- $\mu$ m and 40-nm bulk CMOS) at 4 K, and for 0.16- $\mu$ m devices also at 1 K and 100 mK [39]. Unlike prior works (see Fig. 1), we model, for the first time, the behavior of bulk CMOS devices at temperatures as low as 100 mK, and we validate the compact models at 4 K by comparing simulations and measurements of two complex circuits, namely a ring oscillator and a lownoise amplifier (LNA) for spin-qubit readout [42]. The paper is organized as follows: Section II describes the devices characterization; Section III discusses the cryogenic behavior and the related physics in detail; Section IV presents the modeling procedure and the resulting DC characteristics are compared to the measured ones; Section V presents the validation of the models with complex circuits and summarizes the effects of cryogenic cooling on technology parameters and on device figures of merit having an impact on future cryogenic-circuit designs; finally, conclusions are drawn in Section VI.

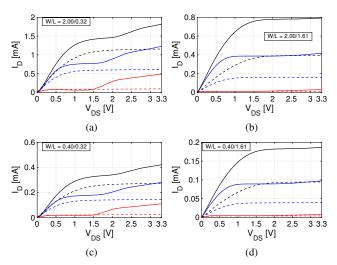

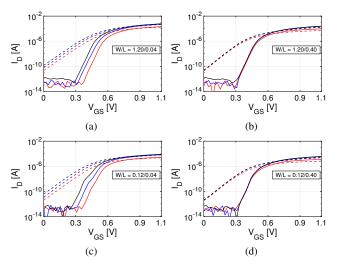

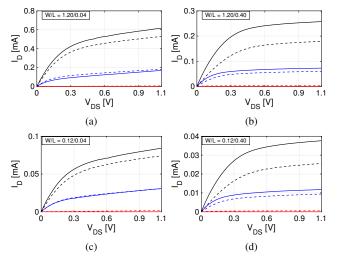

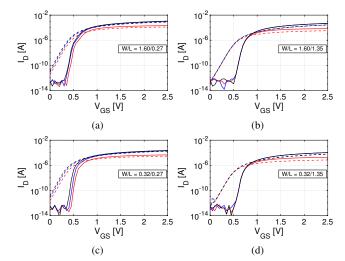

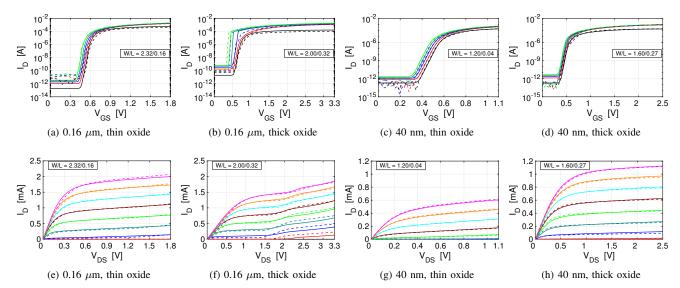

# II. CHARACTERIZATION

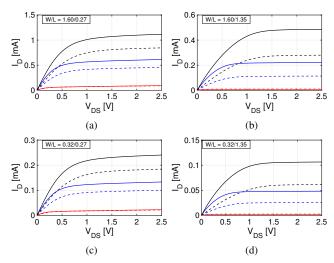

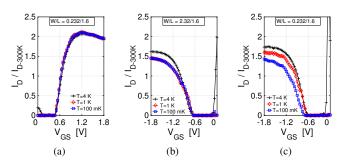

Several transistors with different dimensions and different oxide thickness from both technologies (SSMC 0.16  $\mu$ m, ST 40 nm) were tested at 4 K, as shown in Table I. Only a few 0.16- $\mu$ m devices were cooled down to 1 K and 100 mK, namely one NMOS (W/L = 0.232/1.6) and two PMOS (W/L = 2.32/1.6 and W/L = 0.232/1.6), since other devices did not outlive the bonding required in the sub-Kelvin setup. An ST-500 probe station by Janis Research was used for 300 K and 4 K testing, while a CF-CS81 dilution refrigerator by Leiden Cryogenics was used for sub-Kelvin characterization.  $I_D(V_{GS})$  and  $I_D(V_{DS})$  characteristics are shown in Fig. 2, 3, 4, 5, Fig. 6, 7, 8, 9 and Fig. 10 for the two technologies.

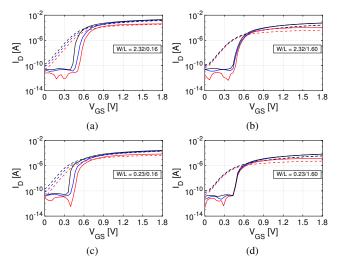

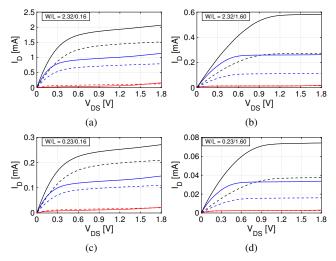

As mentioned in Section I, mature CMOS processes have been characterized at cryogenic temperatures and the physics underlying several cryogenic effects has been explained. Our measurements closely match to previous observations for several aspects. A general increase in mobility ( $\approx 2\times$ ), clearly visible in the long-channel devices of Fig. 3b-d and Fig. 7b-d, and threshold voltage ( $\approx 30\%$ ) is observed. The former is due to an overall decrease in electron scattering, while the latter to an increase in ionization energy [43]. From 300 K to 4 K, the subthreshold slope (*SS*) improved by 3.8× for the 0.16- $\mu$ m NMOS (Fig. 2) and 3.2× for the 40-nm NMOS (Fig. 6), thanks to the intrinsic temperature dependence of the diffusion current.

Furthermore, a jump in drain current, which is typically referred to as *kink*, is observed in the 0.16- $\mu$ m thick-oxide short-channel NMOS in Fig. 5a-c. The voltage  $V_{DS}$  at which the kink occurs,  $V_{DS-kink}$  is close to  $V_{DD}/2$  and is bias

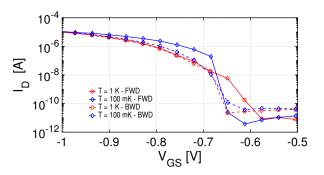

Fig. 2. Measured  $I_D(V_{GS})$  characteristics of thin-oxide NMOS in 0.16- $\mu$ m CMOS.  $V_{DS}$  = [0.1 V; 0.95 V; 1.8 V]. Solid line: 4 K; dashed line: 300 K.

Fig. 3. Measured  $I_D(V_{DS})$  characteristics of thin-oxide NMOS in 0.16- $\mu$ m CMOS.  $V_{GS}$  = [0.68 V; 1.24 V; 1.8 V]. Solid line: 4 K; dashed line: 300 K.

dependent, moving to higher values for larger  $V_{GS}$ . The kink also causes a very steep subthreshold slope, as shown in Fig. 4a-c for  $V_{DS} > 1.7$  V. This jump in current is not observed in all other PMOS and NMOS devices. Although no kink was measured in thin-oxide 0.16- $\mu$ m NMOS transistors, an onset of the substrate-current body effect (SCBE), common in nanometer CMOS transistors, is present and occurring at a lower  $V_{DS}$  at 4 K as compared to 300 K (Fig. 3a-c).

In addition, when cooled down to 100 mK, the  $0.16-\mu m$  devices showed proper operation, as shown in Fig. 10. In this case, mobility does not significantly change with respect to 4 K and the subthreshold slope improves by only  $2.3\times$  when reducing the temperature from 4 K to 100 mK.

Finally, few devices showed a difference in drain current in the subthreshold region when  $V_{GS}$  was swept from low to high or from high to low values. Such *hysteresis* will be discussed in Section III. For clarity, only the forward sweep is shown in Fig. 2, 3, 4, 5, Fig. 6, 7, 8, 9 and Fig. 10.

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2018.2821763, IEEE Journal of the Electron Devices Society

Fig. 4. Measured  $I_D(V_{GS})$  characteristics of thick-oxide NMOS in 0.16- $\mu$ m CMOS.  $V_{DS}$  = [0.1 V; 1.7 V; 3.3 V]. Solid line: 4 K; dashed line: 300 K.

Fig. 5. Measured  $I_D(V_{DS})$  characteristics of thick-oxide NMOS in 0.16- $\mu$ m CMOS.  $V_{GS}$  = [1.05 V; 2.17 V; 3.3 V]. Solid line: 4 K; dashed line: 300 K.

#### III. ANALYSIS OF THE CRYOGENIC BEHAVIOR

In this section, the differences between room-temperature and cryogenic behavior are discussed.

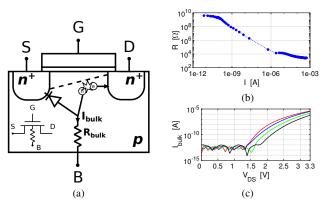

# A. Kink Effect

For bulk CMOS transistors at 4 K, the kink (see Fig. 5a-c) was first explained in [18]. At large  $V_{DS}$ , the generation of electron-hole pairs due to impact ionization leads to a multiplication current, flowing in part to the drain and the rest to the bulk ( $I_{bulk}$  in Fig. 11c). At the same time, an increase in the substrate resistance  $R_{bulk}$  is observed due to carrier freeze-out, which appears at temperatures below 70 K and is exemplified by the large resistance of the n-well resistor in Fig. 11b. The multiplication current flowing through  $R_{bulk}$  causes the bulk potential to raise, thus producing a threshold voltage drop and, consequently, the current jump measured in Fig. 5a-c. Nonetheless, after reaching the kink,

3

Fig. 6. Measured  $I_D(V_{GS})$  characteristics of thin-oxide NMOS in 40-nm CMOS.  $V_{DS}$  = [0.1 V; 0.6 V; 1.1 V]. Solid line: 4 K; dashed line: 300 K.

Fig. 7. Measured  $I_D(V_{DS})$  characteristics of thin-oxide NMOS in 40-nm CMOS.  $V_{GS}$  = [0.43 V; 0.76 V; 1.1 V]. Solid line: 4 K; dashed line: 300 K.

the current jump tends to flatten out as the drain-bulk-source lateral bipolar transistor starts conducting, with the bulksource junction equivalent to the forward-biased base-emitter junction, thus diverting most of the drain ionization current and leading to a gradual saturation of  $I_{bulk}$ , as can be seen in the bulk current plot of Fig. 11c. Furthermore, the voltage at which the kink occurs,  $V_{DS-kink}$ , shifts to higher  $V_{DS}$  for larger gate voltages  $V_{GS}$ . This can be explained by considering that a higher  $V_{GS}$  leads to a larger surface scattering and, hence, to a more pronounced mobility degradation, which mitigates the impact ionization and, consequently, the value of  $V_{DS}$  where the kink occurs.

It is important to note that the kink is observed only in two thick-oxide NMOS transistors, namely W/L = 2/0.322 and W/L = 0.4/0.322 in the 0.16- $\mu$ m CMOS technology. Prior works shown in Fig. 1 report the presence of the kink only in mature technologies, mostly for feature sizes larger than 0.35  $\mu$ m and at temperatures below 100 K. The reason for

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/JEDS.2018.2821763, IEEE Journal of the Electron Devices Society

Fig. 8. Measured  $I_D(V_{GS})$  characteristics of thick-oxide NMOS in 40-nm CMOS.  $V_{DS}$  = [0.1 V; 1.3 V; 2.5 V]. Solid line: 4 K; dashed line: 300 K.

Fig. 9. Measured  $I_D(V_{DS})$  characteristics of thick-oxide NMOS in 40-nm CMOS.  $V_{GS}$  = [0.85 V; 1.68 V; 2.5 V]. Solid line: 4 K; dashed line: 300 K.

Fig. 10. Measured characteristics of the three devices tested at 1 K and 100 mK compared to 4 K; (a) NMOS,  $V_{DS} = 1.8 V$ ; (b)-(c) PMOS,  $V_{DS} = -1.8 V$ . Every curve is normalized to 300 K to remove chip-to-chip spread since the 4 K measurements were done on a different chip placed in the probe station.

this technology dependence is strictly related to transistor scaling. Traditional scaling rules require thinner oxide thick-

4

Fig. 11. (a) Cross-Section and schematic representation of the cause of kink effect at 4 K; (b) N-well resistance versus current at 4 K; the resistance value at 300 K is 3.5 k $\Omega$ ; (c)  $I_{bulk}(V_{DS})$  of thick-oxide NMOS, W/L = 2.32/0.322 at 4 K.

ness to keep a constant vertical electric field. However, the vertical electric field in nanometer technologies has inevitably increased in spite of a proportional scaling of supply and gate insulator thickness, leading to higher mobility degradation (due to surface scattering, for example) that mitigates the impact ionization effect and, hence, the occurrence of the kink. Additionally, the substrate doping of nanometer technologies is considerably higher due to channel engineering, thresholdvoltage control, lightly doped drain (LDD) [20], pocket and deep retrograde implants, which help to reduce the drastic increase of the bulk resistance and, hence, the kink effect. Finally, supply voltages below 1.2 V inevitably prevent the kink from occurring because carriers cannot acquire enough energy through impact ionization to overcome the silicon bandgap. All these effects combined explain why we observe the kink only in thick-oxide short-channel 0.16- $\mu$ m NMOS devices. This type of transistor, in fact, closely resembles a 0.35- $\mu$ m-CMOS device and does not yet "benefit" from the scaling consequences explained above. Long-channel devices (Fig. 5b-d) do not show a kink because the longitudinal electric field never reaches the required critical electric field to trigger impact ionization. Finally, no kink is observed in 0.16- $\mu$ m thick-oxide PMOS because their intrinsic lower mobility suffices for the complete suppression of the kink.

#### B. Sub-Kelvin regime

Measurements at 100 mK<sup>\*</sup> showed proper transistor operation, as mentioned in Section II. Fig. 10 shows the  $I_D(V_{GS})$ characteristics at 4 K, 1 K and 100 mK of the three transistors listed in Section II normalized to the 300-K measurement to remove any chip-to-chip spread between the devices measured at 4 K in the probe station and those measured in the dilution refrigerator down to 100 mK. It can be observed that the three characteristics in Fig. 10 are almost overlapping for the three transistors, meaning that mobility and threshold voltage do not change significantly at temperatures below 4 K. For the PMOS, the current slightly diminishes below

\*The temperature was set to 40 mK but because of self-heating in the transistors, the temperature was around 100 mK for most of the measurement time.

5

4 K. The mobility degradation below 4 K is attributed to the strong contribution of carrier-to-carrier and neutral-impurity scattering, which increase at low temperature, as also observed in [44], [45]. Finally, the saturation in threshold voltage is most likely due to the fact that, once freeze-out is reached, the amount of ionized atoms does not significantly change and, hence, the threshold voltage  $V_T$  is not notably influenced.

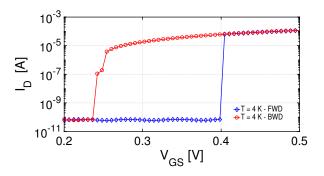

# C. Hysteresis

Although it has been a major concern in the past for several technologies operating at cryogenic temperatures [23], [46], [47], no significant hysteresis was observed in most of the tested devices, with the exception of those that showed a kink at 4 K and for the long-channel 0.16- $\mu$ m PMOS at 100 mK.

For the thick-oxide NMOS (W/L = 2/0.16), hysteresis occurs in the subthreshold region, as can be observed in Fig. 12 where a voltage shift in  $V_{GS}$  of around 0.15 V is measured. This happens only for  $V_{DS} > 1.7$  V, i.e. after the kink. This can be explained by considering that before  $V_{GS}$  overcomes the threshold voltage, negligible free charge is present at the surface, thus preventing significant impact ionization. As  $V_{GS}$ rises and the channel is being formed, the mechanism of avalanche due to impact ionization builds up as well. Once the channel is formed and the current is not negligible (at  $\approx$  0.4 V as shown in the forward-sweep curve in Fig. 12), the threshold voltage decreases due to the kink effect (see Section III-A), reaching the final value once the avalanche current is maximum, which happens when the channel is in strong inversion. When  $V_{GS}$  is swept in the other direction (red-circled line in Fig. 12), impact ionization is already occurring at large  $V_{GS}$  and, consequently, the threshold voltage  $V_T$  is already approximately 0.22 V. The  $V_{GS}$  must diminish below this value to completely turn off the transistor.

At sub-Kelvin temperature, a softer hysteresis can be seen in Fig. 13. However, although the temperature of the dilution refrigerator was set to 40 mK, the temperature of the sample varied between 40 mK and 100 mK due to self-heating. This could partially explain the presence of hysteresis in Fig. 13 as a measurement artifact. Further investigations are necessary though, to fully explain the cause of a possible hysteresis in the sub-Kelvin regime. In conclusion, we recognize that hysteresis is not a significant issue in nanometer nodes, since it emerged in very few tested devices.

### D. Subthreshold Slope

The subtreshold slope is expected to become steeper with decreasing temperature due to the exponential dependence of  $I_D$ ,

$$I_D \approx I_0 \cdot e^{\frac{q(V_{GS} - V_T)}{nk_B T}} \tag{1}$$

where  $I_0$  is the saturation current, q the electron charge,  $k_B$  the Boltzmann constant and T the temperature. The expression of the subthreshold slope results, therefore:

$$SS(T) = \left[\frac{\partial \log(I_D)}{\partial V_{GS}}\right]^{-1} = \ln(10)\frac{nk_BT}{q}$$

(2)

From the Eq. 2, it can be concluded that the subthreshold slope should be linearly dependent on T. However, according

Fig. 12. Forward (FWD) and backward (BWD) sweep of  $I_D(V_{GS})$  in subthreshold region for the thick-oxide NMOS (W/L = 2.32/0.16) at 4 K at  $V_{DS}$  = 3.3 V. Hysteresis causes a shift of  $\approx 0.15$  V.

Fig. 13. Forward (FWD) and backward (BWD) sweep of  $I_D(V_{GS})$  for the thin-oxide PMOS (2.32/1.6) at 1 K and 100 mK at  $V_{DS} = -1.8 V$ .

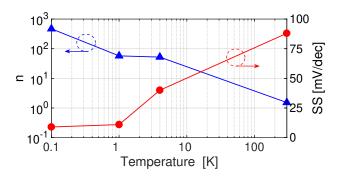

to the literature [15], the subthreshold slope follows the proportionality with the temperature down to  $\approx$  77 K, as predicted by Eq. 2, but it becomes strongly sub-linear at lower temperatures. The sub-linear trend matches our observation of the NMOS *SS* (Fig. 2), which improves by only  $\approx 3.8 \times$  from 300 K to 4 K. This can be attributed to the factor *n* and its dependence on *T*. As a proxy for the subthreshold slope, *n* is

$$n = 1 + \frac{C_{dep}}{C_{ox}} + \frac{C_{it}}{C_{ox}} \tag{3}$$

where  $C_{dep}$ ,  $C_{it}$  and  $C_{ox}$ , are the depletion, interface-states and oxide capacitances per device area, respectively. The temperature dependence of n can be explained by the nonnegligible increase of interface states at cryogenic temperatures, as reported in [48]. By extracting the value of n from the measurements at temperature  $T^*$  as

$$\frac{SS(300\ K)}{SS(T^*)} = \frac{n_{300K}}{n_{T^*}} \cdot \frac{300\ K}{T^*},\tag{4}$$

we obtain the plot of Fig. 14 for the 0.16- $\mu$ m PMOS (W/L = 2.32/1.6). In the figure, we can observe a drastic increase of *n* below 1 K, which is in agreement with the theory in [48]. In conclusion, a summary of subthreshold slope and *n* of a PMOS (W/L = 2.32/1.6) versus temperature is shown in Fig. 14.

#### IV. MODELING

No commercial compact model can predict the behavior of CMOS at cryogenic temperatures and hence, commercial

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 14. Subthreshold slope (SS) and extracted ideality factor n of the PMOS (W/L = 2.32/1.6) across temperature.

models cannot be used for the design of circuits operating at cryogenic temperatures. To overcome that limitation, we propose a model for cryogenic CMOS devices based on existing compact models. Our modeling effort aims at demonstrating the capability of standard compact models to cover cryogenic operation without significant modifications. More specifically, we adopted MOS11 [49] and PSP [50] for the 0.16- $\mu$ m and the 40-nm CMOS technology, respectively, since they were provided by the respective foundry for the standard temperature range. The development of PSP was inspired by MOS11 and therefore the modeling procedure could be mirrored, as will be presented below. Moreover, being MOS11 and PSP derived from surface-potential equations, they are possibly better suited to cover device behaviors in extreme conditions without trading off accuracy for model continuity.

As shown in Section II, the 40-nm CMOS technology did not show any specific cryogenic non-ideality. Therefore, the modeling procedure consisted in updating the parameters in the foundry-provided models with the new values extracted from the cryogenic characterization. On the contrary, some 0.16- $\mu$ m transistors showed strong non-idealities, such as the kink, which are not included in standard models for bulk CMOS. As a consequence, the modeling of those devices required the addition of extra electrical components to capture semiconductor physics at 4 K. In particular, a non-linear resistor was added in series to the bulk of the transistor to emulate freeze-out of the substrate (see Fig. 11) and, consequently, generate the kink at the appropriate  $V_{DS}$ . This, in addition to the extracted parameters, enabled the modeling of the DC characteristics at every bias point.

# A. Extraction and modeling procedure

To model the cryogenic behavior of the devices in Section II, we proceed in the following order: first, the temperature of the simulator was set to -200 °C in order to match the measured and simulated subthreshold slope. At the same time, the temperature-fitting parameters of the MOS11 model were zeroed to prevent the simulator from extrapolating meaningless values of mobility,  $V_T$  and other parameters at those temperatures. This was not necessary for the PSP. We then set the parameters related to the threshold voltage  $V_T$  (VFB for MOS11, DELVTO for PSP) and mobility  $\mu$  (BETSQ for MOS11, FACTUO for PSP), since they have the largest influence on  $I_D$ ,

TABLE II

LIST OF MODIFIED PARAMETERS FOR THE COMPACT MODEL AT 4 K.

6

| MOS11 parameters for 0.16- $\mu$ m CMOS |        |        |         |      |     |  |  |  |

|-----------------------------------------|--------|--------|---------|------|-----|--|--|--|

| BETSQR                                  | VFBR   | THESRR | SDIBLO  | ALPR | KOR |  |  |  |

| THESATR                                 | THERR  | A1R    | A2R     | A3R  |     |  |  |  |

| PSP parameters for 40-nm CMOS           |        |        |         |      |     |  |  |  |

| FACTUO                                  | DELVTO | THEMUO | THESATO | RSW1 | CFL |  |  |  |

| ALPL                                    | MUEO   | FBET1  |         |      |     |  |  |  |

as observed from the measurements. After this, the parameters that impact mobility degradation were modified; in particular, those related to surface scattering (THESRR for MOS11, THEMUO for PSP), and to velocity saturation (THESATR for MOS11, THESATO for PSP). This enabled us to match the curves at high  $V_{GS}$  where the characteristics are degraded by these effects. In combination to mobility degradation, impact ionization was enhanced through the parameters A1R, A2R and A3R for the 0.16- $\mu$ m technology in order to reproduce the kink or the onset of SCBE, while this was not necessary for the 40-nm technology. At this point, the relative error between simulation and measurement is below 20% for most of the curves. The remaining parameters listed in Table II but not mentioned above were modified to fine-tune the models, to compensate for other second-order effects (e.g. channel-length modulation) and, hence, to reduce the mismatch further below 10% in almost all the bias regions.

During the whole procedure, the bulk contact of the thickoxide 0.16- $\mu$ m NMOS transistor was connected to a highimpedance non-linear resistor implemented as a look-up table. The data of such look-up table were extracted from the measurement of the n-well resistor in Fig. 11b and scaled by a constant coefficient at the end of the modeling procedure to tune the magnitude of the current jump and  $V_{DS-kink}$ . The final implemented resistor has an impedance of 100 k $\Omega$  at  $I_{bulk} = 1$  nA.

The modeling of the devices at 100 mK followed the same procedure, proving that the models are scalable with temperature. It has to be noted that the parameters related to the dynamic behavior of the transistor were not modified and hysteresis was not modeled since the majority of the devices did not show this effect. Finally, although the extraction procedure described above has not yet been automated, we believe that, especially for the majority of the devices that do not show kink, the standard extraction procedure for the respective model can be adopted.

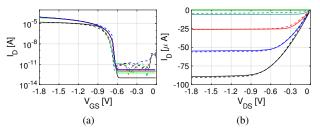

# B. Modeling results

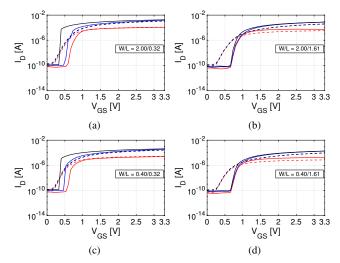

The results of this parameter-fitting procedure are shown in Fig. 15 and Fig. 16 where both 4 K and 100 mK measurements (dashed lines) and simulations based on the newly proposed models (solid lines) are superimposed. Good matching (relative error < 10%) of simulations and experimental data is obtained at every bias point, in both weak and strong inversion, with a single set of parameters for each device. However, the accuracy of the model is limited in the moderate-inversion region, e.g. in Fig. 15f for  $V_{GS} = 0.6 \text{ V} \rightarrow 1 \text{ V}$ , because both models employ a smoothing function to continuously merge the equations for weak and strong inversion, which was not modified in this work.

Fig. 15. Models (solid) and measurements (dashed) at 4 K; W/L in  $\mu$ m. (a,e)  $I_D(V_{GS})$  and  $I_D(V_{DS})$  of 0.16- $\mu$ m thin-oxide NMOS; (b,f)  $I_D(V_{GS})$  and  $I_D(V_{DS})$  of 0.16- $\mu$ m thick-oxide NMOS; (c,g)  $I_D(V_{GS})$  and  $I_D(V_{DS})$  of 40-nm thin-oxide NMOS; (d,h)  $I_D(V_{GS})$  and  $I_D(V_{DS})$  of 40-nm thick-oxide NMOS.

Fig. 16. Models (solid) and measurement (dashed) of  $0.16 + \mu m$  thin-oxide PMOS (W/L = 2.32/1.6) at 100 mK. (a)  $I_D(V_{GS})$ ,  $V_{DS} = -1.8 \rightarrow -0.09$  V; (b)  $I_D(V_{DS})$ ,  $V_{GS} = -0.3 \rightarrow -1.8$  V.

# V. MODEL VALIDATION

# A. Circuits at cryogenic temperature

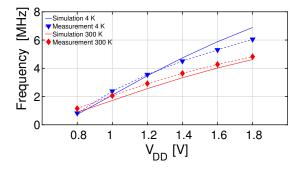

A 2703-stages ring oscillator in 0.16- $\mu$ m CMOS has been tested at 4 K. Its measured oscillation frequency is shown in Fig. 17 for both 300 K and 4 K for different supply voltages and compared to the simulation employing the proposed model. The higher driving capability reduces the gate delay by almost 30%. The simulation was performed on a different process corner with respect to the curves in Fig. 15, since the circuit was fabricated on a different die. The room-temperature measurements and simulation were firstly compared to calibrate the cryogenic model. After this calibration, the output frequency  $f_{osc}$  is in good agreement with simulation over a wide range of supply voltages. Faster saturation of the measured  $f_{osc}$  at high  $V_{DD}$  is observed at 4 K compared to simulation. This can be attributed to the increased poly depletion region, which leads to a smaller depletion capacitance in series with the thin-oxide and therefore a reduced effective gate-channel voltage (not included in our modeling procedure) [24]. This reduction in effective  $V_{GS}$  leads to  $I_D$ and, correspondingly,  $f_{osc}$  tapering off.

In order to further validate the model with a complex real-

Fig. 17. Ring oscillator frequency versus supply voltage  $(V_{DD})$  at 300 K and 4 K. Measurements (dotted lines) and simulations (solid lines) are compared with the compact model presented in Section IV.

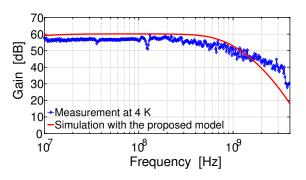

life circuit, a 0.16- $\mu$ m-CMOS low-noise amplifier based on the noise-canceling topology [51] was designed using the cryogenic models developed in this work. A comprehensive description of the circuit and its design flow together with extensive experimental characterization have been reported in [42]. Here, we focus our attention on the accuracy of the presented model by comparing the measured frequency response of the amplifier to the simulation employing the developed cryogenic models (Fig. 18). Only a 3-dB error can be observed in the DC gain, while the 3-dB bandwidth matches within a 10% margin. The observed discrepancy is well within the margin due to process spread, which has not been modeled in this work due to lack of the required cornerlot samples. In conclusion, both experiments above confirm the effectiveness of the parameter extraction and the modeling procedure presented above.

# B. Impact of cryogenic CMOS on circuit design

Device performance at 300 K and 4 K is compared and summarized in Table III for minimum-length devices for both technologies. The higher threshold voltage  $V_T$  combined

<sup>2168-6734 (</sup>c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Fig. 18. Frequency response of the cryogenic LNA: comparison between measurement at 4 K and simulation with the proposed model. Reproduced from [42].

with a steeper SS is beneficial to minimize leakage currents. However, a high  $V_T$  reduces the voltage headroom available for circuits, especially when operating at low supply voltages. This may force the adoption of low-voltage circuit topologies typically showing a lower energy efficiency [52]. This can be particularly detrimental in cryogenic applications, such as quantum-computing controllers, because of the tight power budget imposed by the cooling capabilities of dilution refrigerators.

The effect of the higher  $V_T$  is partially compensated by the increase in mobility, which results in an overall increase of the maximum drain current (see  $I_{on}$  in Table III) and, consequently, in a faster switching speed (see Fig. 17). The larger driving current and lower leakage bring an improved  $I_{on}/I_{off}$ ratio (better than  $100 \times$  for 40 nm), which is advantageous for the implementation of high-energy-efficiency digital logic. Table III also shows the transconductance efficiency in terms of  $g_m/I_D$  ratio in both weak and strong inversion, extracted from the measurements shown in Fig. 2, 3, 4, 5, Fig. 6, 7, 8, 9. A significant improvement ( $\approx 3\times$ ) is observed at 4 K in weak inversion while a slightly lower efficiency appears in strong inversion. This would lead to a major improvement in power efficiency for cryogenic circuits biased in weak inversion. Finally, a lower intrinsic gain is observed, due to the large increase in the channel-length modulation factor  $\lambda$ , in agreement to what was observed in [44].

## VI. CONCLUSIONS

This work presents the extensive DC characterization of transistors fabricated in 0.16- $\mu$ m and 40-nm CMOS technologies at deep-cryogenic temperatures (4 K, 1 K and 100 mK). A detailed understanding of the device physics at cryogenic temperatures was developed and captured in a compact model that was validated both via device DC characterization and through the design and testing of complex circuits.

It was demonstrated that nanometer bulk CMOS devices can operate reliably down to 100 mK and that, for the first time, their behavior can be modeled at such low temperature. Moreover, nanometer CMOS technologies are not affected by strong cryogenic non-idealities, such as kink, and several device figures of merit, such as  $I_{on}/I_{off}$  and  $g_m/I_D$ , significantly improve at 4 K, which is expected to enhance the

TABLE III

COMPARISON OF PERFORMANCE AT 300 K AND 4 K.

8

| Technology                           |                    | 0.16 µm                                 |                        | 40 nm                  |                        |  |

|--------------------------------------|--------------------|-----------------------------------------|------------------------|------------------------|------------------------|--|

| Temperature                          |                    | 4 K                                     | 300 K                  | 4 K                    | 300 K                  |  |

| Device W/L                           | $[\mu m / \mu m]$  | 2.32 / 0.16                             |                        | 1.2 / 0.04             |                        |  |

| $V_T$                                | [V]                | 0.55                                    | 0.40                   | 0.50                   | 0.38                   |  |

| SS                                   | [mV/dec]           | 22.8                                    | 87.0                   | 27.7                   | 88.2                   |  |

| n                                    | [-]                | 28.7                                    | 1.5                    | 34.9                   | 1.5                    |  |

| Ion                                  | [A]                | $2 \cdot 10^{-3}$                       | $1.5 \cdot 10^{-3}$    | $6 \cdot 10^{-4}$      | $5.3 \cdot 10^{-4}$    |  |

| I <sub>off</sub> <sup>†</sup>        | [A]                | $< 3 \cdot 10^{-11}$                    | $< 1.6 \cdot 10^{-10}$ | $< 1.5 \cdot 10^{-12}$ | $< 1.4 \cdot 10^{-10}$ |  |

| I <sub>on</sub> /I <sub>off</sub>    | [A/A]              | $> 6.7 \cdot 10^{7}$                    | $> 9.4 \cdot 10^{6}$   | $> 4.0 \cdot 10^{8}$   | $> 3.8 \cdot 10^{6}$   |  |

| Gate delay <sup>‡</sup>              | [ps]               | 30.60                                   | 38.30                  | -                      | -                      |  |

| $\lambda^{\S}$                       | [V <sup>-1</sup> ] | 3.3                                     | 0.6                    | 4.0                    | 1.3                    |  |

|                                      |                    | Weak Inversion                          |                        |                        |                        |  |

| $g_m/I_D$ ¶                          | [V <sup>-1</sup> ] | 70                                      | 27                     | 92                     | 27                     |  |

| Intrinsic gain = $g_m/(\lambda I_D)$ | [V/V]              | 21.2                                    | 45.0                   | 23.0                   | 20.8                   |  |

|                                      |                    | Strong Inversion (at $V_{ov} = 0.2 V$ ) |                        |                        |                        |  |

| $g_m/I_D$                            | [V <sup>-1</sup> ] | 6                                       | 9                      | 9                      | 10                     |  |

| Intrinsic gain = $g_m/(\lambda I_D)$ | [V/V]              | 1.8                                     | 15.0                   | 2.2                    | 7.7                    |  |

$^*I_{off}$  for 0.16- $\mu$ m transistors is limited by leakage in the ESD of the samples and in 40 nm by the accuracy of the instrument.

<sup>†</sup>Gate delay is measured with  $V_{DD}$  of 1.1 V (40 nm), 1.8 V (0.16  $\mu$ m).

$^{\ddagger}\lambda$  is extracted at  $V_{GS} = 0.65 V$  (40 nm) and  $V_{GS} = 0.68 V$  (0.16  $\mu$ m).

$^{\$}$ The peak value for  $g_m/I_D$  is reported. At 4 K, this value is limited by the accuracy of the instrument in measuring small values of  $I_D$ .

performance of both analog and digital circuits at cryogenic temperatures.

Thus, the proposed models will enable the design and simulation of circuits in nanometer CMOS, which is a viable technology for the implementation of high-performance and power-efficient cryogenic circuits, as required in demanding applications such as quantum computing.

#### ACKNOWLEDGMENT

The authors would like to thank Intel Corp. for funding, NXP and ST Microelectronics for chip fabrication and dr. Leonardo DiCarlo for help in the 100-mK characterization.

#### REFERENCES

- T. Chen, C. Zhu, L. Najafizadeh, B. Jun, A. Ahmed, R. Diestelhorst, G. Espinel, and J. D. Cressler, "CMOS reliability issues for emerging cryogenic Lunar electronics applications," *Solid-State Electronics*, vol. 50, no. 6, pp. 959–963, May 2006, doi:10.1016/j.sse.2006.05.010.

- [2] F. Zocca, A. Pullia, S. Riboldi, A. D'Andragora, and C. Cattadori, "Setup of cryogenic front-end electronic systems for germanium detectors read-out," in *Proc. 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC)*, Oct. 2009, pp. 368–372, doi:10.1109/NSSMIC.2009.5401690.

- [3] C. L. Degen, F. Reinhard, and P. Cappellaro, "Quantum sensing," *Reviews of Modern Physics*, vol. 89, no. 3, p. 035002, Jul. 2017, doi:10.1103/RevModPhys.89.035002.

- [4] A. Endo, J. J. A. Baselmans, P. P. van der Werf, B. Knoors, S. M. H. Javadzadeh, S. J. C. Yates, D. J. Thoen, L. Ferrari, A. M. Baryshev, Y. J. Y. Lankwarden, P. J. de Visser, R. M. J. Janssen, and T. M. Klapwijk, "Development of DESHIMA: a redshift machine based on a superconducting on-chip filterbank," in *Proc. of SPIE*, W. S. Holland, Ed., no. September 2012, Sep. 2012, pp. 84 520X-1 84 520X-15, doi:10.1117/12.925637.

- [5] L. Gottardi, H. Akamatsu, J. van der Kuur, S. J. Smith, A. Kozorezov, and J. Chervenak, "Study of TES-Based Microcalorimeters of Different Size and Geometry Under AC Bias," *IEEE Transactions* on Applied Superconductivity, vol. 27, no. 4, pp. 1–4, Jun. 2017, doi:10.1109/TASC.2017.2655500.

- [6] T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, "A programmable two-qubit quantum processor in silicon," *Nature*, feb 2018, doi:10.1038/nature25766.

- [7] J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, "A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%," *Nature Nanotechnology*, vol. 13, no. 2, pp. 102–106, feb 2018, doi:10.1038/s41565-017-0014-x.

- [8] D. Ristè, S. Poletto, M. Z. Huang, A. Bruno, V. Vesterinen, O. P. Saira, and L. DiCarlo, "Detecting bit-flip errors in a logical qubit using stabilizer measurements," *Nature Communications*, vol. 6, 2015, doi:10.1038/ncomms7983.

- [9] L. A. Tracy, D. R. Luhman, S. M. Carr, N. C. Bishop, G. A. Ten Eyck, T. Pluym, J. R. Wendt, M. P. Lilly, and M. S. Carroll, "Single shot spin readout using a cryogenic high-electron-mobility transistor amplifier at sub-Kelvin temperatures," *Applied Physics Letters*, vol. 108, no. 6, pp. 063 101–1 – 063 101–5, Feb. 2016, doi:10.1063/1.4941421.

- [10] I. T. Vink, T. Nooitgedagt, R. N. Schouten, L. M. K. Vandersypen, and W. Wegscheider, "Cryogenic amplifier for fast real-time detection of single-electron tunneling," *Applied Physics Letters*, vol. 91, no. 12, pp. 12–15, 2007, doi:10.1063/1.2783265.

- [11] D. Wecker, B. Bauer, B. K. Clark, M. B. Hastings, and M. Troyer, "Gatecount estimates for performing quantum chemistry on small quantum computers," *Physical Review A*, vol. 90, no. 2, pp. 022 305–1–022 305– 13, Aug. 2014, doi:10.1103/PhysRevA.90.022305.

- [12] F. Sebastiano, H. Homulle, B. Patra, R. Incandela, J. van Dijk, L. Song, M. Babaie, A. Vladimirescu, and E. Charbon, "Cryo-CMOS Electronic Control for Scalable Quantum Computing," in *Proc. of the* 54th Annual Design Automation Conference 2017, 2017, pp. 1–6, doi:10.1145/3061639.3072948.

- [13] J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, D. J. Reilly, I. D. C. Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and Others, "Cryogenic control architecture for large-scale quantum computing," *Physical Review Applied*, vol. 3, no. 2, p. 24010, 2015, doi:10.1103/PhysRevApplied.3.024010.

- [14] D. J. Reilly, "Engineering the quantum-classical interface of solid-state qubits," *npj Quantum Information*, vol. 1, no. 1, p. 15011, Dec. 2015, doi:10.1038/npjqi.2015.11.

- [15] A. Kamgar, "Subthreshold behavior of silicon MOSFETs at 4.2 K," *Solid-State Electronics*, vol. 25, no. 7, pp. 537–539, Jul. 1982, doi:10.1016/0038-1101(82)90052-1.

- [16] H. Hanamura, M. Aoki, T. Masuhara, O. Minato, Y. Sakai, and T. Hayashida, "Operation of bulk CMOS devices at very low temperatures," *IEEE Journal of Solid-State Circuits*, vol. 21, no. 3, pp. 484–490, Jun. 1986, doi:10.1109/JSSC.1986.1052555.

- [17] F. Balestra, L. Audaire, and C. Lucas, "Influence of substrate freezeout on the characteristics of MOS transistors at very low temperatures," *Solid State Electronics*, vol. 30, no. 3, pp. 321–327, mar 1987, doi:10.1016/0038-1101(87)90190-0.

- [18] L. Deferm, E. Simoen, and C. Claeys, "The importance of the internal bulk-source potential on the low temperature kink in NMOSTs," *IEEE Transactions on Electron Devices*, vol. 38, no. 6, pp. 1459–1466, Jun. 1991, doi:10.1109/16.81639.

- [19] E. Simoen, B. Dierickx, and C. Claeys, "Low-frequency noise behavior of Si NMOSTs stressed at 4.2 K," *IEEE Transactions on Electron De*vices, vol. 40, no. 7, pp. 1296–1299, Jul. 1993, doi:10.1109/16.216435.

- [20] E. Simoen and C. Claeys, "Impact of CMOS processing steps on the drain current kink of NMOSFETs at liquid helium temperature," *IEEE Transactions on Electron Devices*, vol. 48, no. 6, pp. 1207–1215, 2001, doi:10.1109/16.925249.

- [21] E. Simoen, A. Mercha, Y. Creten, P. Merken, J. Putzeys, P. De Moor, C. Claeys, C. Van Hoof, A. Mohammadzadeh, and R. Nickson, "Impact of Irradiations Performed at Liquid Helium Temperatures on the Operation of 0.7 μm CMOS Devices and Read-Out Circuits," in *Proc. Radiation and its Effects on Components and Systems (RADECS)*, 2003, pp. 369–375.

- [22] G. Siligaris, A. Pailloncy, G. Delcourt, S. Valentin, R. Lepilliet, S. Danneville, F. Gloria, D. Dambrine, "High-Frequency and Noise Performances of 65-nm MOSFET at Liquid Nitrogen Temperature," *IEEE Transactions on Electron Devices*, vol. 53, no. 8, pp. 1902–1908, Aug. 2006, doi:10.1109/TED.2006.877872.

- [23] Y. Creten, P. Merken, W. Sansen, R. Mertens, and C. van Hoof, "A Cryogenic ADC operating Down to 4.2K," in *Proc. 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers*, Feb. 2007, pp. 468–616, doi:10.1109/ISSCC.2007.373497.

- [24] Y.-H. Hong, Seung-ho Choi, Gil-bok Baek, Rock-Hyun Kang, Hee-Sung Jung, Sung-Woo Jeong, "Low-Temperature Performance of Nanoscale MOSFET for Deep-Space RF Applications," *IEEE Electron Device Letters*, vol. 29, no. 7, pp. 775–777, Jul. 2008, doi:10.1109/LED.2008.2000614.

- [25] G. De Geronimo, A. D'Andragora, Shaorui Li, N. Nambiar, S. Rescia, E. Vernon, Hucheng Chen, F. Lanni, D. Makowiecki, V. Radeka, C. Thorn, and Bo Yu, "Front-end ASIC for a liquid argon TPC,"

in IEEE Nuclear Science Symposuim & Medical Imaging Conference, vol. 58, no. 3. IEEE, oct 2010, pp. 1658–1666, doi:10.1109/NSSMIC.2010.5874057.

9

- [26] S. R. Ekanayake, T. Lehmann, A. S. Dzurak, R. G. Clark, and A. Brawley, "Characterization of SOS-CMOS FETs at Low Temperatures for the Design of Integrated Circuits for Quantum Bit Control and Readout," *IEEE Transactions on Electron Devices*, vol. 57, no. 2, pp. 539–547, Feb. 2010, doi:10.1109/TED.2009.2037381.

- [27] M. Shin, M. Shi, M. Mouis, A. Cros, E. Josse, G. T. Kim, and G. Ghibaudo, "Low temperature characterization of 14nm FDSOI CMOS devices," in *Proc. 2014 11th International Workshop on Low Temperature Electronics (WOLTE)*, no. 1, Jul. 2014, pp. 29–32, doi:10.1109/WOLTE.2014.6881018.

- [28] A. Coskun and J. Bardin, "Cryogenic small-signal and noise performance of 32nm SOI CMOS," in *Proc. 2014 IEEE MTT-S International Microwave Symposium (IMS2014)*, Jun. 2014, pp. 1–4, doi:10.1109/MWSYM.2014.6848614.

- [29] Y. Feng, P. Zhou, H. Liu, J. Sun, and T. Jiang, "Characterization and modelling of MOSFET operating at cryogenic temperature for hybrid superconductor-CMOS circuits," *Semiconductor Science and Technol*ogy, vol. 19, no. 12, pp. 1381–1385, Dec. 2004, doi:10.1088/0268-1242/19/12/009.

- [30] A. Akturk, Others, M. Peckerar, M. Dornajafi, N. Goldsman, K. Eng, T. Gurrieri, and M. S. Carroll, "Impact ionization and freeze-out model for simulation of low gate bias kink effect in SOI-MOSFETs operating at liquid He temperature," in *Proc. 2009 Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, Sep. 2009, pp. 1–4, doi:10.1109/SISPAD.2009.5290227.

- [31] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar, and K. P. Cheung, "Compact and Distributed Modeling of Cryogenic Bulk MOSFET Operation," *IEEE Transactions on Electron Devices*, vol. 57, no. 6, pp. 1334–1342, Jun. 2010, doi:10.1109/TED.2010.2046458.

- [32] Z. Zhu, A. Kathuria, S. Krishna, M. Mojarradi, B. Jalali-Farahani, H. Barnaby, W. Wu, and G. Gildenblat, "Design applications of compact MOSFET model for extended temperature range (60 - 400 K)," *Electronics Letters*, vol. 47, no. 2, p. 141, 2011, doi:10.1049/el.2010.3468.

- [33] P. Martin, A. S. Royet, F. Guellec, and G. Ghibaudo, "MOSFET modeling for design of ultra-high performance infrared CMOS imagers working at cryogenic temperatures: Case of an analog/digital 0.18 μm CMOS process," *Solid-State Electronics*, vol. 62, no. 1, pp. 115–122, 2011, doi:10.1016/j.sse.2011.01.004.

- [34] Z. Chen, H. Wong, Y. Han, S. Dong, and B. Yang, "Temperature dependences of threshold voltage and drain-induced barrier lowering in 60 nm gate length MOS transistors," *Microelectronics Reliability*, vol. 54, no. 6-7, pp. 1109–1114, Jun. 2014, doi:10.1016/j.microrel.2013.12.005.

- [35] H. Zhao and X. Liu, "Modeling of a standard 0.35 μm CMOS technology operating from 77 K to 300 K," *Cryogenics*, vol. 59, pp. 49–59, Jan. 2014, doi:10.1016/j.cryogenics.2013.10.003.

- [36] G. S. Fonseca, L. B. de Sá, and A. C. Mesquita, "Extraction of static parameters to extend the EKV model to cryogenic temperatures," in *Proc. SPIE Defense+ Security*, B. F. Andresen, G. F. Fulop, C. M. Hanson, J. L. Miller, and P. R. Norton, Eds., May 2016, p. 98192B, doi:10.1117/12.2219734.

- [37] A. Beckers, F. Jazaeri, A. Ruffino, C. Bruschini, A. Baschirotto, and C. Enz, "Cryogenic characterization of 28 nm bulk CMOS technology for quantum computing," in *Proc. 2017 47th European Solid-State Device Research Conference (ESSDERC)*, Sep. 2017, pp. 62–65, doi:10.1109/ESSDERC.2017.8066592.

- [38] N. C. Dao, A. E. Kass, M. R. Azghadi, C. T. Jin, J. Scott, and P. H. Leong, "An enhanced MOSFET threshold voltage model for the 6–300 K temperature range," *Microelectronics Reliability*, vol. 69, pp. 36–39, Feb. 2017, doi:10.1016/j.microrel.2016.12.007.

- [39] R. M. Incandela, L. Song, H. A. Homulle, F. Sebastiano, E. Charbon, and A. Vladimirescu, "Nanometer CMOS characterization and compact modeling at deep-cryogenic temperatures," in *Proc. 2017 47th European Solid-State Device Research Conference (ESSDERC)*, Sep. 2017, pp. 58– 61, doi:10.1109/ESSDERC.2017.8066591.

- [40] L. Varizat, G. Sou, M. Mansour, D. Alison, and A. Rhouni, "A low temperature 0.35μm CMOS technology BSIM3.3 model for space instrumentation: Application to a voltage reference design," in *Proc. 2017 IEEE International Workshop on Metrology for AeroSpace (MetroAeroSpace)*. IEEE, Jun. 2017, pp. 74–78, doi:10.1109/MetroAeroSpace.2017.7999541.

- [41] A. Rhouni, O. Gevin, X. de la Broïse, J. Sauvageot, V. Revéret, and L. Rodriguez, "First-ever test and characterization of the AMS standard bulk 0.35 μm CMOS technology at sub-kelvin temperatures,"

2168-6734 (c) 2018 IEEE. Translations and content mining are permitted for academic research only. Personal use is also permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications/standards/publications/rights/index.html for more information. Journal of Physics: Conference Series, vol. 834, p. 012005, may 2017, doi:10.1088/1742-6596/834/1/012005.

- [42] B. Patra, R. M. Incandela, J. P. G. van Dijk, H. A. R. Homulle, L. Song, M. Shahmohammadi, R. B. Staszewski, A. Vladimirescu, M. Babaie, F. Sebastiano, and E. Charbon, "Cryo-CMOS Circuits and Systems for Quantum Computing Applications," *IEEE Journal* of Solid-State Circuits, vol. 53, no. 1, pp. 309–321, Jan. 2018, doi:10.1109/JSSC.2017.2737549.

- [43] F. Balestra and G. Ghibaudo, "Brief review of the MOS device physics for low temperature electronics," *Solid State Electronics*, vol. 37, no. 12, pp. 1967–1975, 1994, doi:10.1016/0038-1101(94)90064-7.

- [44] D. Antonio, H. Pastoriza, P. Julián, and P. Mandolesi, "Cryogenic transimpedance amplifier for micromechanical capacitive sensors," *Review of Scientific Instruments*, vol. 79, no. 8, p. 084703, Aug. 2008, doi:10.1063/1.2970944.

- [45] E. A. Gutiérrez-D., M. J. Deen, and C. Claeys, "Chapter 1 Physics of Silicon at Cryogenic Temperatures," in *Low Temperature Electronics*. San Diego: Academic Press, 2001, pp. 1 – 103, doi:10.1016/B978-012310675-9/50002-5.

- [46] B. Dierickx, L. Warmerdam, E. Simoen, J. Vermeiren, and C. Claeys, "Model for hysteresis and kink behavior of MOS transistors operating at 4.2 K," *IEEE Transactions on Electron Devices*, vol. 35, no. 7, pp. 1120–1125, Jul. 1988, doi:10.1109/16.3372.

- [47] E. Simoen and C. Claeys, "The hysteresis and transient behavior of Si metal–oxide–semiconductor transistors at 4.2 K. I. The kink–related counterclockwise hysteresis regime," *Journal of Applied Physics*, vol. 73, no. 6, pp. 3068–3073, Mar. 1993, doi:10.1063/1.352990.

- [48] I. M. Hafez, G. Ghibaudo, and F. Balestra, "Assessment of interface state density in silicon metal–oxide–semiconductor transistors at room, liquid–nitrogen, and liquid–helium temperatures," *Journal of Applied Physics*, vol. 67, no. 4, pp. 1950–1952, Feb. 1990, doi:10.1063/1.345572.

- [49] R. van Langevelde, A. J. Scholten, and D. B. M. Klaassen, "Physical background of MOS Model 11," Koninklijke Philips Electronics N.V., Tech. Rep., Apr. 2003.

- [50] X. Li, W. Wu, G. Gildenblat, G. D. J. Smit, A. J. Scholten, D. B. M. Klaassen, and R. van Langevelde, "PSP 102.3," NXP Semiconductors 2008, Tech. Rep., May 2008.

- [51] F. Bruccoleri, E. Klumperink, and B. Nauta, "Wide-Band CMOS Low-Noise Amplifier Exploiting Thermal Noise Canceling," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 2, pp. 275–282, Feb. 2004, doi:10.1109/JSSC.2003.821786.

- [52] R. Gonzalez, B. Gordon, and M. Horowitz, "Supply and threshold voltage scaling for low power CMOS," *IEEE Journal of Solid-State Circuits*, vol. 32, no. 8, pp. 1210–1216, Aug. 1997, doi:10.1109/4.604077.

Harald Homulle received the B.S. and M.S. degrees in electrical engineering from Delft University of Technology, The Netherlands, in 2012 and 2014, respectively. During the Master's project, he did an internship at EPFL, Lausanne, Switzerland, for the development of a multi-channel TDC on FPGA. In 2014 he joined the research group of Edoardo Charbon as a Ph.D. student on the topic of cryogenic electronics, with the main focus on quantum computing applications in collaboration with other QuTech researchers.

Edoardo Charbon (SM'00–F'17) received the Diploma from ETH Zurich, the M.S. from the University of California at San Diego, and the Ph.D. from the University of California at Berkeley in 1988, 1991, and 1995, respectively, all in electrical engineering and EECS. He has consulted with numerous organizations, including Bosch, X-Fab, Texas Instruments, Maxim, Sony, Agilent, and the Carlyle Group. He was with Cadence Design Systems from 1995 to 2000, where he was the Architect of the company's initiative on information hiding

for intellectual property protection. In 2000, he joined Canesta Inc., as the Chief Architect, where he led the development of wireless 3-D CMOS image sensors. Since 2002 he has been a member of the faculty of EPFL, where is a full professor since 2015. From 2008 to 2016 he was with Delft University of Technology's as Chair of VLSI design. He has been the driving force behind the creation of deep-submicron CMOS SPAD technology, which is mass-produced since 2015 and is present in telemeters, proximity sensors, and medical diagnostics tools. His interests span from 3-D vision, FLIM, FCS, NIROT to super-resolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for quantum computing. He has authored or co-authored over 250 papers and two books, and he holds 20 patents. Dr. Charbon is a distinguished visiting scholar of the W. M. Keck Institute for Space at Caltech, a fellow of the Kavli Institute of Nanoscience Delft, a distinguished lecturer of IEEE Photonics Society, and a fellow of the IEEE.

**Rosario M. Incandela** (S'17) was born in Trapani, Italy in 1992. He received the B.Sc. in Electronics Engineering from Politecnico di Milano, Italy and the M.Sc (cum laude) in Microelectronics from Delft University of Technology, The Netherlands, in 2014 and 2016, respectively. In 2016, he started the Ph.D. in cryogenic electronics for quantum applications at Delft University of Technology. His main research interests include low-noise cryogenic CMOS readout of spin qubits and modeling of CMOS technologies at cryogenic temperature.

Andrei Vladimirescu (F'17) received the M.S. and Ph.D. degrees in EECS from the University of California, Berkeley, where he was a key contributor to the SPICE simulator, releasing the SPICE2G6 production-level SW in 1981. He pioneered electrical simulation on parallel computers with the CLASSIE simulator as part of his PhD. He is the author of "The SPICE Book" published by J. Wiley and Sons.

For many years Andrei was R&D director leading the design and implementation of innovative

software and hardware Electronic Design Automation products for Analog Devices Inc., Daisy Systems, Analog Design Tools, Valid Logic and Cadence.

Currently he is Professor involved in research projects at the University of California at Berkeley, Delft University of Technology and the Institut Supérieur d'Électronique de Paris, ISEP, as well as consultant to industry. His research activities are in the areas of ultra-low-voltage (ULV) CMOS, design, simulation and modeling of circuits with new devices and circuits for quantum computing.

Andrei is an IEEE Fellow.

Lin Song received the B.S., M.S. degrees in electrical engineering from Tsinghua University, Beijing, China and Delft University of Technology, Delft, the Netherlands, in 2014 and 2016, respectively. He is currently an analog designer with Analog Devices Inc., in Beijing design office, Beijing, China.

11

Fabio Sebastiano (S'09–M'10–SM'17) was born in Teramo, Italy in 1981. He received the B.Sc. (cum laude) and M.Sc. (cum laude) degrees in electrical engineering from University of Pisa, Italy, in 2003 and 2005, respectively, the M.Sc. degree (cum laude) from Sant'Anna school of Advanced Studies, Pisa, Italy, in 2006 and the Ph.D. degree from Delft University of Technology, The Netherlands, in 2011. From 2006 to 2013, he was with NXP Semicon-

ductors Research in Eindhoven, The Netherlands, where he conducted research on fully integrated

CMOS frequency references, deep-submicron temperature sensors and areaefficient interfaces for magnetic sensors. In 2013, he joined Delft University of Technology, where he is currently an Assistant Professor. He has authored or co-authored one book, nine patents, and over 40 technical publications. His main research interests are sensor read-outs, fully-integrated frequency references, and cryogenic electronics for quantum applications.