### Purdue University Purdue e-Pubs

Birck and NCN Publications

Birck Nanotechnology Center

5-15-2009

# Characterization and Modeling of Subfemotofarad Nanowire Capacitance Using the CBCM Technique

Hui Zhao Purdue University - Main Campus

Raseong Kim Purdue University - Main Campus

Abhijeet Paul Purdue University - Main Campus

Mathieu Luisier Purdue University - Main Campus

Gerhard Klimeck Purdue University - Main Campus, gekco@purdue.edu

See next page for additional authors

Follow this and additional works at: https://docs.lib.purdue.edu/nanopub

Zhao, Hui; Kim, Raseong; Paul, Abhijeet; Luisier, Mathieu; Klimeck, Gerhard; Ma, Fa-Jun; Rustagi, Subhash C.; Samudra, Ganesh S.; Singh, Navab; Lo, Guo-Qiang; and Kwong, Dim-Lee, "Characterization and Modeling of Subfemotofarad Nanowire Capacitance Using the CBCM Technique" (2009). *Birck and NCN Publications*. Paper 430. https://docs.lib.purdue.edu/nanopub/430

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

### Authors

Hui Zhao, Raseong Kim, Abhijeet Paul, Mathieu Luisier, Gerhard Klimeck, Fa-Jun Ma, Subhash C. Rustagi, Ganesh S. Samudra, Navab Singh, Guo-Qiang Lo, and Dim-Lee Kwong

# Characterization and Modeling of Subfemtofarad Nanowire Capacitance Using the CBCM Technique

Hui Zhao, Raseong Kim, Abhijeet Paul, Mathieu Luisier, Gerhard Klimeck, Fa-Jun Ma, Subhash C. Rustagi, Ganesh S. Samudra, Navab Singh, Guo-Qiang Lo, and Dim-Lee Kwong

Abstract—The experimental characterization of gate capacitance in nanoscale devices is challenging. We report an application of the charge-based capacitance measurement (CBCM) technique to measure the gate capacitance of a single-channel nanowire transistor. The measurement results are validated by 3-D electrostatic computations for parasitic estimation and 2-D self-consistent  $sp^3s^*d^5$  tight-binding computations for intrinsic gate capacitance calculations. The device simulation domains were constructed based on SEM and TEM images of the experimental device. The carefully designed CBCM technique thus emerges as a useful technique for measuring the capacitance and characterizing the transport in nanoscale devices.

Index Terms—Charge-based capacitance measurement (CBCM), nanowire MOSFETs, self-consistent C-V modeling, subfemtofarad-capacitance measurement.

#### I. INTRODUCTION

W ITH the rapid scaling of CMOS device technology, conventional bulk CMOS devices will soon reach their physical limits on the account of short-channel effects. Threedimensional (3-D) multiple-gate device structures, such as FinFETs and nanowire and nanotube FETs, have been proposed for next-generation nanoscale technology for their superior

H. Zhao and F.-J. Ma are with the Institute of Microelectronics, Agency for Science, Technology and Research (A\*STAR), Singapore 117685, and also with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 117576.

R. Kim, A. Paul, M. Luisier, and G. Klimeck are with the Network for Computational Nanotechnology, Purdue University, West Lafayette, IN 47907 USA (e-mail: kim369@purdue.edu).

S. C. Rustagi, N. Singh, G.-Q. Lo, and D.-L. Kwong are with the Institute of Microelectronics, Agency for Science, Technology and Research (A\*STAR), Singapore 117685 (e-mail: subhash@ime.a-star.edu.sg).

G. S. Samudra is with the Silicon Nano Device Laboratory, Department of Electrical and Computer Engineering, National University of Singapore, Singapore 117576 (e-mail: eleshanr@nus.edu.sg).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2009.2015588

subthreshold performance and, hence, lower leakage currents. The experimental characterization of the channel transport in these devices has been hampered due to the difficulty in measuring the capacitance that is typically below the femtofarad scale. The 3-D nature of these devices makes it impossible to have a large-area device for channel charge characterization, as is the case with bulk CMOS technology. Currently, characterization and modeling rely mostly on atomistic simulations and/or experimental capacitance data obtained from a large number of nanowires [1], [2] connected in parallel. However, enhancing the capacitance to a measurable level by connecting many devices in parallel masks the inherent variability at the nanoscale and is therefore undesirable. Tu et al. [3] reported the capacitance measurement of single nanowire channel at low temperature (150 K) using a conventional C-V meter. However, the method still suffers from high noise level due to the limited resolution of the instrument and large background capacitance.

In this letter, we report the measurement of gate capacitance on a single Si nanowire (SiNW) device using a carefully designed and calibrated charge-based capacitance measurement (CBCM) technique. We construct a realistic TCAD model with dimensions acquired from the SEM and TEM images of the structure of the characterized device after completing the electrical measurements and use COMSOL multiphysics [4] and the self-consistent  $sp^3s^*d^5$  tight-binding model [5]–[7] to obtain the simulated capacitance for validation. This letter is perhaps the first one to present a comparison of the measured C-V data with the carefully constructed simulation model of a singlechannel SiNW transistor. The results are of vital importance for characterizing the transport and variability in emerging research devices.

## II. CBCM TEST-KEY DESIGN, FABRICATION, AND CHARACTERIZATION

A few different circuit schematics have been proposed for on-chip implementation of the CBCM technique [8]–[10]. The accuracy of the three main variants of these was evaluated in [11] based on TCAD simulations. In this letter, we follow the charge-injection-induced error-free scheme proposed by Chang *et al.* [9], which measures two charging/discharging currents from exactly the same branch, eliminating the mismatch in the load. This is particularly important in our measurements since the pseudoinverter drivers are also nanoscale devices, and any mismatch of device dimension in the reference and device-under-test (DUT) branches can introduce significant

0741-3106/\$25.00 © 2009 IEEE

Manuscript received December 5, 2008; revised January 29, 2009. First published April 10, 2009; current version published April 28, 2009. This work was supported in part by a research collaboration agreement between IME, Singapore, and Purdue University, West Lafayette, IN. The work of R. Kim was supported by the National Science Foundation (NSF) under Grant ECS-0609282. The work of A. Paul and M. Luisier was supported in part by Semiconductor Research Corporation (SRC), by Microelectronics Advanced Research Corporation (MARCO) and its Focus Center on Materials, Structures and Devices (MSD), by the NSF under a research grant for petascale computing (OCI-0749140), by the Network for Computational Nanotechnology through nanoHUB.org computational resources funded by the NSF under Grants EEC-0228390 and EEC-0634750, and by the Midwest Institute for Nanoelectronics Discovery (MIND) funded by the Nanoelectronics Research Initiative (NRI) and by Purdue University. The review of this letter was arranged by Editor K. De Meyer.

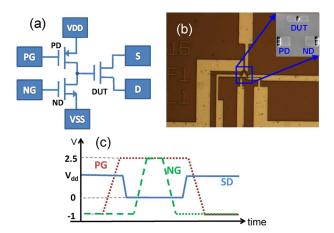

Fig. 1. (a) CBCM test key comprising a pseudoinverter, a DUT, and six input/output terminals. (b) Micrograph image of the fabricated test key. The inset shows the SEM image of the channels of the P driver, N driver, and single-finger DUT immediately after the local release of the SiNW. (c) Pulse inputs to PG, NG, S, and D terminals for the CBCM measurement of N-type SiNW DUT.

error in capacitance extraction. Measuring the two currents on a single branch with the same capacitance combination also helps reduce the error introduced by charge injection [11]. CBCM test keys with six input/output terminals were designed and fabricated, as shown in Fig. 1(a) and (b).

For fabrication, we modified the process flow in [12] by introducing the "local release" of the SiNW [as shown in the inset of Fig. 1(b)] to prevent the formation of a "gate poly-Si stringer" [13] around the source/drain (S/D) region. This significantly reduces the gate-to-source/drain parasitic capacitance. Single- and multiple-finger SiNWs are integrated as DUT in the CBCM test key. The drivers are SiNW devices with a gate length of 0.35  $\mu$ m and a larger diameter (around ~50 nm) to efficiently source/sink the charging/discharging current. The DUT has a gate length of 0.85  $\mu$ m and a rounded triangular cross section with base of ~22-nm length and ~7-nm height. The gate oxide thickness is ~9 nm, as seen from the TEM images.

The nonoverlapping pulses and voltages applied to terminals PG, NG, D, and S are shown in Fig. 1(c). The charging (or discharging) currents  $I_{1,\text{VDD}}$  and  $I_{2,\text{VDD}}$  through the VDD pad are monitored. A dc voltage is applied to the S/D pads for  $I_{1,\text{VDD}}$ , while a third nonoverlapping pulse [SD in Fig. 1(c)] is applied for measuring  $I_{2,\text{VDD}}$  [9]. The bias-dependent gate capacitance of the DUT is then given by

$$C_{\rm DUT} = \frac{d(Q_{1,\rm VDD} - Q_{2,\rm VDD})}{dV_{\rm DD}} = \frac{d(I_{1,\rm VDD} - I_{2,\rm VDD})}{dV_{\rm DD}} \frac{1}{f}.$$

(1)

The measurement scheme was verified by comparing the gate capacitance of a 100-finger SiNW device measured with CBCM and LCR meter (HP4284). The test key had an additional small pad connected to the DUT gate for this purpose. A constant voltage of 0.75 V was applied to the S/D terminals, and the voltage at the VDD pad was varied between 0.1 and 1.85 V in steps of 10 mV, yielding a range of gate biases for DUT capacitance from -0.65 to 1.10 V. The frequency for the three nonoverlapping pulses was chosen to be 1 MHz

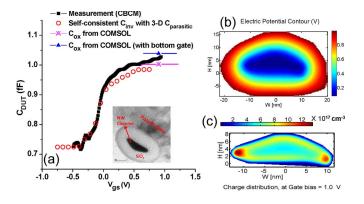

Fig. 2. (a)  $C_{\rm DUT} - V_{\rm gs}$  curves of the single-channel SiNW transistor measured by the CBCM technique and self-consistent intrinsic SiNW gate capacitance simulated with the  $s^3s^*d^5$  tight-binding model added with the 3-D electrostatic capacitance without considering NW in COMSOL [4]. The inset shows the TEM cross section of the SiNW channel. (b) and (c) Potential (in volts) and electron density (in units per cubic centimeter) in the channel obtained by self-consistent computation, respectively.

for all measurements. The Agilent 4156C was used for the measurement of currents  $I_{1,\text{VDD}}$  and  $I_{2,\text{VDD}}$ . Each current was measured 16 times, and their average value, after removing the outliers using Pierce's criteria [14], was used in (1). Furthermore, noise-free numerical derivatives were calculated following the algorithm by Savitzky and Golay [15]. The C-V curves derived from the CBCM technique for a 100-finger SINW transistor were found to agree well with the measurements from the LCR meter. For this purpose, we averaged 16 sets of LCR meter measurements to filter the noise for improved accuracy.

### III. C–V MODELING OF SINGLE-CHANNEL SiNW TRANSISTOR

The gate capacitance  $C_{\rm DUT}$  of the single-channel SiNW transistor measured by CBCM is shown in Fig. 2(a), along with the TEM cross section of the channel in the inset. As the S/D contacts are n-type, we do not expect any significant capacitance on the accumulation side ( $-\text{ve }V_{\rm gs}$ ). However, a capacitance floor of ~0.72 fF can be seen in the  $C_{\rm DUT}-V_{\rm gs}$  curve. We further observed that the minimum capacitance increases linearly with the length of the S/D region (not shown here), suggesting that the origin of this minimum capacitance is parasitic related to the contact pads of the S/D regions.

To investigate this further at a reasonable level of complexity, we simulated the structure in two parts. For the first part, to get the intrinsic gate capacitance, the Schrödinger and Poisson equations were solved self-consistently for the exact cross section of the SiNW based on the TEM image using the  $sp^3s^*d^5$  tight-binding model [5]–[7] for density-of-state calculations. Fig. 2(b) and (c) shows the potential distribution and the electron distribution in the cross section of the structure. Significant crowding of electrons can be seen clearly at the corners of the rounded-triangle shape. Low electron concentration at silicon oxide interfaces is due to the quantum effect considered in the simulation.

Next, a 3-D device model was constructed in COMSOL multiphysics [4] based on the TEM and SEM images and layout

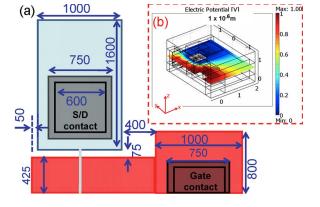

Fig. 3. (a) Top view of the simulation domain with dimensions for COMSOL multiphysics simulations (in nanometers; not to scale). (b) Potential distribution in the device structure (in micrometers) in the plane parallel to the wafer surface.

details of the DUT. Fig. 3(a) shows the simulation domain seen from the top (half of the device structure was considered taking advantage of the symmetry). Potential distribution plots in the planes parallel to the wafer surface are shown in Fig. 3(b). As expected, the potential changes sharply near the corners of the poly-silicon gate facing the S/D region, as well as in the narrow space separating the poly-Si gate contact region and the edge of the S/D region. The parasitic capacitance was estimated to be ~0.71 fF, which is very close to the measured minimum capacitance for the single-finger device of the same gate length.

Fig. 2(a) shows very good agreement of the measured  $C_{\rm DUT}$  with the sum of the simulated intrinsic and parasitic capacitances. The simulated gate capacitance in inversion (~0.261 fF) from the self-consistent simulation is about 90% of the measured value (~0.29 fF, measured from the minimum), and the sum of the self-consistent and parasitic capacitances is about 95.8% of the measured capacitance. A little larger value of the measured inversion capacitance is inferred to be due to the bottom-gated portion of the channel that extends from the gate-all-around region by 75 nm to both source and drain contact regions. The oxide capacitance increases by 3.6% when the bottom gate is considered in 3-D electrostatic simulations, as seen in Fig. 2(a).

### **IV. CONCLUSION**

In this letter, we reported the design, fabrication, and characterization of a CBCM test key with SiNW transistors as DUT and drivers to measure the voltage-dependent capacitance at the subfemtofarad level from a single-channel SiNW device. The CBCM method was carefully verified by conventional LCR meter measurement on a DUT with large number of NW channels connected in parallel. Furthermore, the measured C-Vcharacteristics have been validated by the 2-D self-consistent solution of the Schrödinger and Poisson equations and 3-D electrostatic calculation using the exact TEM cross sections and layout information. We conclude that the CBCM technique is capable of reliably measuring the capacitance in the hundredsof-attofarad range for emerging 3-D CMOS devices such as FinFETs and nanowire and nanotube transistors.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. M. S. Lundstrom at Purdue University, West Lafayette, IN, and Prof. G. Baccarani at the University of Bologna, Bologna, Italy, for the helpful discussions. The authors would also like to thank the staff of the SPT Laboratory, IME, Singapore, for the support in fabricating the devices.

#### REFERENCES

- [1] J. Chen, T. Saraya, K. Miyaji, K. Shimizu, and T. Hiramoto, "Experimental study of mobility in [110]- and [100]-directed multiple silicon nanowire GAA MOSFETs on (100) SOI," in VLSI Symp. Tech. Dig., 2008, pp. 32–33.

- [2] S. D. Suk, M. Li, Y. Y. Yeoh, K. H. Yeo, K. H. Cho, I. K. Ku, H. Cho, W. J. Jang, D.-W. Kim, D. Park, and W.-S. Lee, "Investigation of nanowire size dependency on TSNWFET," in *IEDM Tech. Dig.*, 2007, pp. 891–894.

- [3] R. Tu, L. Zhang, Y. Nishi, and H. Dai, "Measuring the capacitance of individual semiconductor nanowires for carrier mobility assessment," *Nano Lett.*, vol. 7, no. 6, pp. 1561–1565, Jun. 2007.

- [4] COMSOL Multiphysics. [Online]. Available: http://www.comsol.com

- [5] G. Klimeck, F. Oyafuso, T. B. Boykin, R. C. Bowen, and P. von Allmen, "Development of a nanoelectronic 3-D (NEMO 3-D) simulator for multimillion atom simulations and its application to alloyed quantum dots," *Comput. Model. Eng. Sci. (CMES)*, vol. 3, no. 5, pp. 601–642, 2002. (invited).

- [6] A. Paul, M. Luisier, N. Neophytou, R. Kim, M. McLennan, M. Lundstrom, and G. Klimeck, *Band Structure Lab*, 2006.

- [7] N. Neophytou, A. Paul, M. S. Lundstrom, and G. Klimeck, "Bandstructure effects in silicon nanowire electron transport," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1286–1297, Jun. 2008.

- [8] J. C. Chen, B. W. McGaughy, D. Sylvester, and C. Hu, "An on-chip, attofarad interconnect charge-based capacitance measurement (CBCM) technique," in *IEDM Tech. Dig.*, 1996, pp. 69–72.

- [9] Y.-W. Chang, H.-W. Chang, T.-C. Lu, Y.-C. King, W. Ting, Y.-H. J. Ku, and C.-Y. Lu, "Charge-based capacitance measurement for bias-dependent capacitance," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 390–392, May 2006.

- [10] L. Vendrame, L. Bortesi, and A. Bogliolo, "Accuracy assessment and improvement of on-chip charge-based capacitance measurements," in *Proc. 7th IEEE SPI Workshop*, 2003, pp. 117–120.

- [11] H. Zhao, S. C. Rustagi, F. Ma, G. S. Samudra, N. Singh, G. Q. Lo, and D.-L. Kwong, "Accuracy assessment of charge-based capacitance measurement for nanoscale MOSFET devices," in *Proc. SSDM*, 2008, pp. 886–887.

- [12] N. Singh, F. Y. Lim, W. W. Fang, S. C. Rustagi, L. K. Bera, A. Agarwal, C. H. Tung, K. M. Hoe, S. R. Omampuliyur, D. Tripathi, A. O. Adeyeye, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, "Ultra-narrow silicon nanowire gate-all-around CMOS devices: Impact of diameter, channelorientation and low temperature on device performance," in *IEDM Tech. Dig.*, 2006, pp. 548–551.

- [13] F. Daugé, J. Pretet, S. Cristoloveanu, A. Vandooren, L. Mathew, J. Jomaah, and B.-Y. Nguyen, "Coupling effects and channels separation in FinFETs," *Solid State Electron.*, vol. 48, no. 4, pp. 535–542, Apr. 2004.

- [14] B. Peirce, "Criterion for the rejection of doubtful observations," Astron. J., vol. II, no. 45, pp. 161–163, Jul. 1852.

- [15] A. Savitzky and M. Golay, "Smoothing and differentiation of data by simplified least squares procedures," *Anal. Chem.*, vol. 36, no. 8, pp. 1627–1639, Jul. 1964.