# Characterization of 9T SRAM Cell at Various Process Corners at Deep Sub-micron Technology for Multimedia Applications

R. K. Singh, Shilpi Birla, Member, IACSIT, and Manisha Pattanaik

Abstract—In the past decades CMOS IC technologies have been constantly scaled down and at present they aggressively entered in the nanometer regime. Amongst the wide-ranging variety of circuit applications, integrated memories especially the SRAM cell layout has been significantly reduced. As it is very well know the reduction of size of CMOS involves an increase in physical parameters variation, this is a factor which has a direct impact on SRAM cell stability. Polysilicon and diffusion critical dimensions (CD) together with implant variations are the main causes of mismatch in SRAM cells. SRAM memory cells have always been designed to occupy the minimum amount of silicon area consistent with the performance and reliability required. Today's system on Chip (SoC) trends result in a major percentage of the total die area being dedicated to memory blocks, consequently making SRAM parameter variations dominate the overall circuit parameter characteristics, including leakage, process variation effects, etc. The reliability is usually measured by static noise margin, SNM [1], and write trip point simulations and measurements. In this paper we have analyzed the stability of the 9T SRAM cell at SS, FF, TT, FS, SF corners. The simulations have been done at 45nm technology.

*Index Terms*—SOCs, Embedded SRAM, Scaling, Deep submicron level.

# I. INTRODUCTION

Subthreshold leakage and gate current are not the only issues that have to be deal at a functional level, but at the same time the power management issues of chips for high-performance circuits such as microprocessors, digital signal processors, and graphics processing units are also necessary. Power management is also a challenge in mobile/multimedia applications. Device variations causing device mismatch for several reasons make the memory more sensitive in terms of stability. For stable read and write, the memory cells must be able to keep the stored state when accessed for reading but quickly change state when accessed for writing. These conflicting needs are even more difficult to achieve with the process variations of sub-100 nm processes.

As the lithography shrinks, the device variations are becoming an ever increasing concern. With the sub-100 nm processes, statistical variations need to be included in the SRAM cell and SRAM block analysis to attain circuit designs with sufficient yield and performance within a

Manuscript received September 26, 2011; revised November 17, 2011. R. K. Singh is with BTKIT, Uttarakhand, India.

Shilpi Birla is with SPSU, Udaipur, India. (Email: shilpibirla@gmail.com)

Manisha Pattanaik is with ABV-IIITM Gwalior, India.

defined limited area and power budget.

On the contrary, the transistor and SRAM bit cell size reduction driven by the technology scaling has also made it even more challenging to maintain a sufficient cell stability margin while keeping the same scaling pace of access time and cell size as the mismatching of threshold voltage (Vt) between cross-coupled MOSFET pairs becomes larger and larger [1],[2],[3]. To maintain sufficient margins for read and write stability and read cell current has become challenging as Vdd has to be scaled down in order not only to meet the requirements for device scaling and power savings but also to keep the logic operating voltage compatibility. The Vdd scaling has quickly become one of the most critical challenges because of its strong dependency on the SRAM stability margins for read and write since the invention of 65 nm process node.

In this paper, we have analyzed the stability issues at various process corners of the proposed SRAM cell[14]. This 9T SRAM cell has better stability from the earlier publications. In Section II the conventional SRAM along with its limitations has been discussed. In Section III working of the SRAM cell which has been proposed in given. In Section IV the analysis of the cell at various process corners is included in which stability measures like SNM, write margin, read current and leakage has been analyzed and finally the conclusion.

# II. CONVENTIONAL SRAM CELL

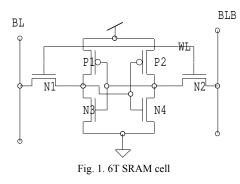

The mainstream six-transistor (6T) CMOS SRAM cell is shown in Fig.1 Similarly to one of the implementations of an SR latch, it consists of six transistors. Four transistors (P1, P2, N3, and N4) comprise cross-coupled CMOS inverters and two NMOS transistors, the pass gate transistors or the access transistors N1 and N2 provide read and write access to the cell. Upon the activation of the word line, the access transistors connect the two internal nodes of the cell to the true (BL) and the complementary (BLB) bit lines. A 6T CMOS SRAM cell is the most popular SRAM cell due to its superior robustness, low power and low-voltage operation. Therefore, we will discuss its operation and design in greater detail. An SRAM cell must be designed such that it provides a non-destructive read operation and a reliable write operation. These two requirements impose contradicting requirements on SRAM cell transistor sizing. SRAM cell transistor ratios that must be observed for successful read and write operations are discussed in the following sections.

In the traditional 6T-SRAM (Fig. 1), the cells must be both

stable (during a read event) and writeable (during a write event) ignoring redundancy; such functionality must be preserved for each cell under worst-case variation. At the cell level, transistor strength ratios must be chosen such that cell static noise margin and write margin are both maintained, which presents conflicting constraints on the cell transistor strengths.

For the cell stability during a read operation, it is desirable to strengthen the storage inverters and weaken the pass-gates. The opposite is desired for cell write ability a weak storage inverter and strong pass-gates. This delicate balance of transistor strength ratios can be severely impacted by device variation, which dramatically degrades stability and write margins, especially in scaled technologies. Low supply voltages further exacerbate the problem as threshold voltage variation consumes a larger fraction of these voltage margins. Variability can thus limit the minimum operating voltage of SRAM. [4]

In a 6T cell, variability tolerances are compromised by the conflicting needs of cell read stability and write ability. Because the same pass-gate devices are used to both read and write the cell, it is inevitable that the two conditions cannot be simultaneously optimized. The 6T SRAM cell stability problems also arise during a write operation to an unselected column when the word line is activated while both bit lines are held high [4],[5]. A situation that produces equivalent bias conditions to a read operation. So, different topologies of SRAM cell have been implemented at various technologies to improve the data stability and leakage power consumption.

## III. ANALYSIS OF THE 9T SRAM CELL

Many new cell topologies have been proposed for stability improvement like 7T, 8T, 9T, 10T, 11T.Although each has some advantages and disadvantages along with them. Various topologies of SRAM cell has been introduced, 7T SRAM cell in which a read static noise margin is achieved by cutting off a pull down path during read operation but has limited write capability due to single end write operations [6], [7].8T SRAM cell which is one of the popular topology which increases the stability but has its own limitation. In this paper the limitation of 8T has been removed and alternative topologies have been discussed to increase the stability.

A 7T cell [34] achieves read-static-noise-margin-free by cutting off a pull-down path during read operations, but has limited write capability due to single-end write operations. A read-decoupled (RD) 8T cell [8], [9], [10], [11], which isolates its read-port from the storage node, is a popular

solution for many low-VDD chips because of its superior read stability. However, RD-8T cells do not significantly increase the write margin (WM), and still suffer from half-select stability failure during a write operation. Divided wordline schemes prevent disturbance at half-select cells, but do not solve write failures.

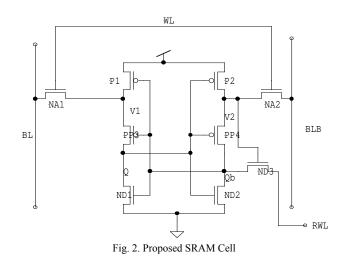

In this section, we describe our cell design in Fig. 2. As mentioned previously, it is composed of two cross coupled P-P-N inverters, and data is stored in node Q and node Qb in a complementary manner. Transistors P1, PP3, and ND1 form a P-P-N inverter and P1, PP4, ND2 form another.[12]

ND1 provides the read current path for discharging a bitline (BL) or its complementary (BLB), depending on the stored values of Q and Qb, respectively. The source terminal of this transistor is connected to the VGND pin, which connects to the ground voltage only during the read operation. Anytime else, it stays high to curb unnecessary leakage current.V1 and V2 are located between the two cascaded P-MOS transistors forming the P-P-N inverter. Q and Qb are the storage nodes .BL and BLB are bitlines while WL is the word line as in conventional 6T SRAM cell.[12]

# IV. PROCESS CORNER ANALYSIS

A process corner is an example of a design-of-experiments (DoE) technique that refers to a variation of fabrication parameters used in applying an integrated circuit design to a semiconductor wafer. Process corners represent the extremes of these parameter variations within which a circuit that has been etched onto the wafer must function correctly. A circuit running on devices fabricated at these process corners may run slower or faster than specified and at lower or higher temperatures and voltages, but if the circuit does not function at all at any of these process extremes the design is considered to have inadequate design margin.

There are therefore five possible corners: typical-typical (TT) (not really a corner of an n vs. p mobility graphs, but called a corner, anyway), fast-fast (FF), slow-slow (SS), fast-slow (FS), and slow-fast (SF). The first three corners (TT, FF, SS) are called even corners, because both types of devices are affected evenly, and generally do not adversely affect the logical correctness of the circuit. The resulting devices can function at slower or faster clock frequencies, and are often binned as such. The last two corners (FS, SF)

are called "skewed" corners, and are cause for concern.

The most common measure of checking the stability is the butterfly curve from which we can get the Static Noise Margin which is the amount of maximum tolerable DC noise voltage without disturbing the output [13]. Other alternate stability methods have also been reported in [14], [15] which is N curve .The N curve is used to get the read stability and write stability but here we have used the conventional method for finding the stability measures.

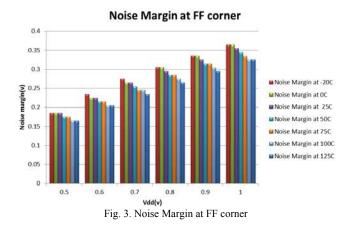

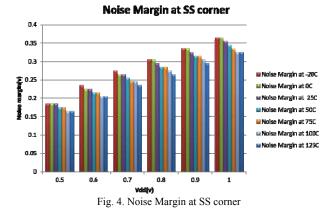

## A. SNM at Various Process Corners

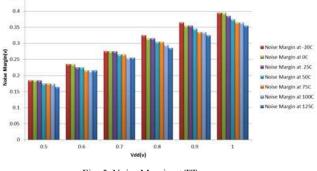

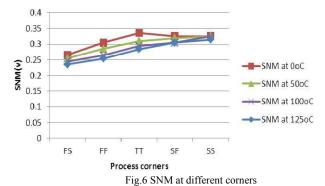

We have analyzed the SNM at different process corners .We have vary the voltages and temperature as in Fig.3 so that we can analyze the effects of voltage and temperature also on the stability. From Fig.3, Fig.4, Fig.5 we can observe that as Vdd is scaled down the SNM also decreases. From Fig.6 we can see that the Noise Margin decreases as temperature increases and the circuit observed the SNM at all the corners.

Noise Margin at TT corner

0.45

Fig. 5. Noise Margin at TT corner

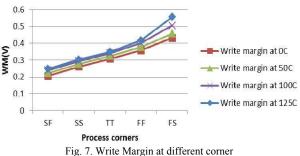

## B. Write Margin at Various Process Corners

The write margin (WRM) is defined as the rest of potential difference between the BL level at which the data is flipped and the end-point (e.g., GND).

Write margin is also analyzed at various process corners and we have taken Vdd=0.8V and analyzed the effect of temperature and process corners on write margin. The SNM decreases with the temperature but in case of write margin it is just reverse here increase in the temperature decreases the Write Margin. As in the Fig.7 we can see that the minimum write margin is observed in case of SF corner and the maximum write margin at FS corner. The cell operates in all the corners.

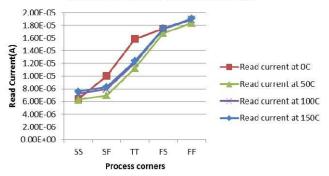

## C. Read Current

For minimum read delay the widths of both devices should therefore be as wide as possible. While SNM evaluate cell functionality, the cell read current, 'Iread' is a major component in designing array access time. Read current is also a measure of the stability and we have analyzed the read current at Vdd=0.8V at different temperatures and process corners as shown in Fig.8. The V DD scaling has quickly become one of the most critical challenges because of its strong dependency on the SRAM stability margins for read and writes stability. Temperature affects the read current inversely with respect to write margin. It decreases with increase in the temperature; it has maximum value at FF corner.

# SNM at 0.8 Vdd at different corners

Read Current at 0.8V at different corners

Fig. 8. Read current at different corners.

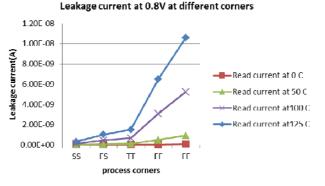

#### D. Leakage Current

Power consumption is one of the most important factors in multimedia applications as the requirement is of ultra-low power consumption. As the temperature increases the leakage also increases and we can see that at FF corner the leakage is highest as in Fig.9. The current measurement is done at Vdd =0.8V.The worst case leakage was 7.49nA.

Fig.9 Leakage current at different corners

#### V. CONCLUSION

In this paper we have analyzed the 9T SRAM cell which has been proposed in [14]. The cell has been analyzed at various process corners to check the read and write stability. We have taken Vdd=0.8V.On analyzing the the various corners we see that the highest SNM is at TT corner and the highest Write Margin is at FS and Read Current is at FF corner. But the cell has highest leakage at FF corner so the process corner. But the cell has operation at all the process corners and it shows good response at TT and FS and FF corners which is required for measuring the cell stability. SNM of the cell is 0.33V, Write Margin is 0.35 V and Read current is 14 $\mu$ A at Vdd=0.8V and temperature is 50°C. These values are better in respect to other published SRAM 9T Cell and the cell area is 1.85x 1.02  $\mu$ m<sup>2</sup>.

#### ACKNOWLEDGMENT

The authors are very grateful to their respective organizations for encouraging them to complete this work

#### REFERENCES

- Evelyn Grossar, Michele Stucchi, Karen Maex," Read Stability and Write-Ability Analysis of SRAM Cells for Nanometer Technologies", Solid-State Circuits, IEEE Journal ,vol. 41, no. 11, Nov.2006, pp.2577-2588.

- [2] Benton H. Calhoun Anantha P. Chandrakasan "Static Noise Margin Variation for Sub-threshold SRAM in 65 nm CMOS", Solid-State Circuits, IEEE Journal vol. 41, Jan.2006, Issue 7, pp.1673-1679.

- [3] Yeonbae Chung, Seung-Ho Song, "Implementation of low-voltage static RAM with enhanced data stability and circuit speed", Microelectronics Journal vol. 40, Issue 6, June 2009, pp. 944-951.

- [4] Shilpi Birla, Manisha Pattanaik, R.K.Singh "Static Noise Margin Analysis of Various SRAM Topologies", IACSIT International Journal of Engineering and Technology, Vol.3, No.3, June 2011,pp-304-309

- [5] Shilpi Birla, Neeraj Kr. Shukla, Manisha Pattanaik, R.K.Singh, "Device and Circuit Design Challenges for Low Leakage SRAM for Ultra Low Power Applications", Canadian Journal on Electrical & Electronics Engineering Vol. 1, No. 7, December 2010.

- [6] Y. H. Chen, W. M. Chan, S. Y. Chou, H. J. Liao, H. Y. Pan, J. J. Wu, C. H. Lee, S. M. Yang, Y. C. Liu, H. Yamauchi, "A 0.6 V 45 nm Adaptive Dual-rail SRAM Compiler Circuit Design for Lower VDD min VLSIs 21.3" IEEE 2008 Symposium on VLSI Circuits.

- [7] Sinangil M., Naveen Verma, A.P.Chandrakasan, "A Reconfigurable 8T Ultra – Dynamic Voltage Scalable(U-DVS) SRAM in 65nm CMOS", Solid-State Circuits, *IEEE Journal*, vol. 44, no. 11,Nov.2009, pp.3163-3173.

- [8] Koichi Takeda et al, "A Read Static Noise Margin Free SRAM cell for Low Vdd and HighSpeed Applications", Solidvol. 41, Jan.2006, Issue 1, pp.113-121.

- [9] Aly, R.E. Bayoumi, M.A., "Low-Power Cache Design Using 7T SRAM Cell" Circuits and Systems II: Express Briefs, IEEE Transactions, vol. 54 April 2007, Issue: 4, pp. 318-322

- [10] Zhiyu Liu and Volkan Kursun, "Characterization of a Novel Nine-Transistor SRAM cell", IEEE Transaction of Very large Scale Integration Systems, vol. 16, NO. 4, April 2008,pp.488-492

- [11] Sheng Lin, Yong-Bin Kim, Fabrizio Lombardi., "Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability" *Integration the VLSI Journal*, vol. 43 ,January 2010, pp. 176-187.

- [12] .Shilpi Birla, Rakesh Kumar Singh, Manisha Pattanaik, "Stability and Leakage Analysis of a Novel PP Based 9T SRAM Cell Using N Curve at Deep Submicron Technology for Multimedia Applications", Circuits & Systems, 2011, Vo.4, pp.274-280.

- [13] E. Seevinck et al., "Static-noise margin analysis of MOS SRAM cells,"IEEE J. Solid-State Circuits, vol. SC-22, no. 5, pp. 748–754, Oct. 1987.

- [14] Zheng Guo, Andrew Carlson, Liang-Teck Pang, Kenneth Duong, Tsu-Jae King Liu, Borivoje Nikolic, "Large-Scale Read/Write Margin Measurement in 45nm CMOS SRAM Arrays", IEEE Symposium on VLSI Circuits Digest of Technical Papers 2008,pp-42-43.

- [15] Jiajing Wang, Satyanand Nalam, and Benton H. Calhoun, "Analyzing Static and Dynamic Write Margin for Nanometer SRAMs", ISPLED 2008,pp.129-134.

**R.K. Singh** (IAENG, ACEEE, IE, ISTE), Professor in the Department of Electronics & Communication Engineering, Bipin Tripathi Kumaon Institute of Technology, Dwarahat, Almora (UK) India. He is being honored with the Ph.D. in Electronics Engineering in the Year 2003 from the University of Allahabad, Allahabad (Uttar Pradesh), India. He has received his M.E. (Electronics & Control

Engineering) in 1992 from BITS, Pilani and B.E. (Electronics & Communication Engineering) in 1990 from Marathawada University, India. He has authored several text-books in the field of VLSI Design, Basic Electronics, and Opto-Electronics. He has worked at various capacities as, the Principle, Kumaon Engineering College, Dwarahat in the year 2003-04, Director (O), Directorate of Technical Education, Uttaranchal in the year 2005, and Joint Director, State Project Facilitation Unit, Dehradun for the World Bank TEQIP Project. He is also the recipient of couple of prestigious awards, e.g., Rastriya Samman Puruskar, Jewel of India Award, Rastriya Ekta Award, Life Time Achievement Award, and Arch of Excellence Award. His current areas of interest are VLSI Design, Opto-Electronics and its applications.

# IACSIT International Journal of Engineering and Technology, Vol. 3, No. 6, December 2011

Shilpi Birla, Ph.D. Scholar at the UK Technical University, Dehradun (Uttarakhand) India. She's an Asst. Professor in the Department of Electronics & Communication Engineering, Sir Padampat Singhania University, Udaipur (Rajasthan) India. She has received her M.Tech. (VLSI Design) and B.E. (Electronics & Communication Engineering) Degrees from the University of Rajasthan, Jaipur

(Rajasthan) India and MITS University, Laxmangarh, (Rajasthan) India, respectively. Her main research interests are in Low-Power VLSI Design and its Multimedia Applications, RF-SiP, and Low-Power CMOS Circuit Design.

Manisha Pattanaik (WSEAS, IE, ISTE) She received the M.E. degree in Electronics Systems and Communication from National Institute of Technology, Rourkela, India in 1997. She received the Ph.D. degree in Electronics and Electrical Communication Engineering from the Indian Institute of Technology, Kharagpur, India in 2005. In 2007, she joined the Information and Communication Technology Faculty at ABV-Indian Institute of

Information Technology and Management, Gwalior, India and is currently an Associate Professor. She has authored and coauthored over 40 papers in journals and conference proceedings in various areas of VLSI design. Her research interests include leakage power reduction of Nano-scale CMOS circuits, low power and low voltage static and dynamic logic circuit techniques for high performance digital and analog VLSI applications, low power SRAM circuits, and CAD of analog and mixed signal integrated circuits.