# CHARACTERIZATION OF DOUBLE-LAYER CAPACITORS FOR POWER ELECTRONICS APPLICATIONS

BY

#### LUIS EDUARDO ZUBIETA BERNAL

A THESIS SUBMITTED IN CONFORMITY WITH THE REQUIREMENTS FOR THE

DEGREE OF MASTER OF APPLIED SCIENCE

GRADUATE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

UNIVERSITY OF TORONTO

© COPYRIGHT BY LUIS EDUARDO ZUBIETA 1997

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre reférence

Our file Notre référence

The author has granted a non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-28861-7

# CHARACTERIZATION OF DOUBLE-LAYER CAPACITORS FOR POWER ELECTRONICS APPLICATIONS

MASTER OF APPLIED SCIENCE 1997

LUIS EDUARDO ZUBIETA BERNAL

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

UNIVERSITY OF TORONTO

#### ABSTRACT

A new kind of capacitor, with large capacitance and high energy density, has become available in the last few years. These high energy capacitors are based on the double-layer technology. They have higher power handling capability and energy density compared to electrolytic power capacitors.

So far, almost no research has been published with respect to the use of these capacitors; in addition, the information supplied by the manufacturer is not enough to establish an accurate model and to understand the operation of the capacitors.

This thesis deals with the selection, identification and verification of a simple and accurate model for the double-layer capacitors. The model is based on the terminal behavior of the double-layer capacitors; therefore, the identification is given by a specific and repetitive process based on electrical measurements.

#### ACKNOWLEDGMENTS

I would like to thank the "UNIVERSIDAD EXPERIMENTAL POLITECNICA ANTONIO JOSE DE SUCRE" and the "CONSEJO NACIONAL DE INVESTIGACIONES CIENTIFICAS Y TECNOLOGICAS" in Venezuela for their economic support during my studies.

I was extremely fortunate to work with Professor Richard Bonert who has given me valuable guidance and advice in all aspects related to this research.

Special thanks to my wife for her understanding, patience and help during the development of this thesis. I would also like to express my gratitude to my parents for their many years of encouragement and support.

My sincere thanks to the professors and students from the group of Power and Systems at the University of Toronto for their comments, discussions and ideas. In addition, I thank Ms. Martine Johnson from the International Student Centre of the University of Toronto for helping me with the writing corrections to the thesis.

# TABLE OF CONTENTS

| 1 | INTROD  | UCTION.                                                | 1  |

|---|---------|--------------------------------------------------------|----|

|   | 1.1     | THESIS OBJECTIVES.                                     | 3  |

|   |         | 1.1.1 MODELING OF DOUBLE-LAYER CAPACITORS.             | 3  |

|   |         | 1.1.2 ENERGY CONSIDERATIONS.                           | 6  |

|   |         | 1.1.3 SERIES CONNECTION.                               | 6  |

|   | 1.2     | THESIS OUTLINE.                                        | 7  |

|   |         |                                                        |    |

| 2 | BACKGR  | DUND OF DOUBLE-LAYER CAPACITORS.                       | 9  |

|   | 2.1     | ELECTRICAL DOUBLE-LAYER TECHNOLOGY.                    | 10 |

|   | 2.2     | DOUBLE-LAYER CAPACITORS DEVELOPMENT.                   | 18 |

|   | 2.3     | DOUBLE-LAYER CAPACITOR CONSTRUCTION.                   | 18 |

|   | 2.4     | COMPARISON BETWEEN DOUBLE-LAYER AND ELECTROLYTIC POWER | 3. |

|   |         | CAPACITORS.                                            | 22 |

|   | 2.5     | DOUBLE-LAYER CAPACITORS APPLICATIONS.                  | 23 |

|   |         | 2.5.1 ELECTRIC AND HYBRID VEHICLE APPLICATIONS.        | 23 |

|   |         | 2.5.2 ELECTRICALLY HEATED CATALYST.                    | 24 |

|   |         | 2.5.3 VEHICLE ACCESSORIES.                             | 25 |

|   |         | 2.5.4 UNINTERRUPTIBLE POWER SUPPLIES.                  | 25 |

|   |         | 2.5.5 OTHER APPLICATIONS.                              | 26 |

|   |         |                                                        |    |

|   |         |                                                        |    |

| 3 | EQUIVAI | ENT MODEL PROPOSAL.                                    | 27 |

|   | 3.1     | PHYSICAL FACTS LEADING TO THE MODEL.                   | 27 |

|   |         | 3 1 1 TIME BEHAVITOR OF THE DOUBLE TAVER CARACTTORS    | 27 |

|   |         | 3.1.2 DEPENDENCE OF THE CAPACITANCE ON THE POTENTIAL   |    |

|---|---------|--------------------------------------------------------|----|

|   |         | DIFFERENCE.                                            | 29 |

|   |         | 3.1.3 DOUBLE-LAYER LEAKAGE.                            | 30 |

|   |         | 3.1.4 INDUCTIVE EFFECT IN THE CAPACITOR.               | 31 |

|   | 3.2     | PRACTICAL CONSIDERATIONS.                              | 32 |

|   |         |                                                        |    |

| 4 | IDENTI  | FICATION OF EQUIVALENT MODEL PARAMETERS.               | 35 |

|   | 4.1     | IDENTIFICATION OF IMMEDIATE BRANCH PARAMETERS.         | 37 |

|   | 4.2     | IDENTIFICATION OF DELAYED BRANCH PARAMETERS.           | 39 |

|   | 4.3     | IDENTIFICATION OF LONG TERM BRANCH PARAMETERS.         | 44 |

|   | 4.4     | IDENTIFICATION OF LEAKAGE RESISTANCE.                  | 45 |

|   | 4.5     | IDENTIFICATION OF DOUBLE-LAYER CAPACITOR INDUCTANCE.   | 47 |

|   |         |                                                        |    |

| 5 | MEASURE | EMENT OF EQUIVALENT MODEL PARAMETERS.                  | 49 |

|   | 5.1     | TEST AND MEASUREMENT FACILITIES.                       | 49 |

|   | 5.2     | MEASUREMENT TECHNIQUES.                                | 54 |

|   |         | 5.2.1 CONTROL OF THE CHARGE IN THE CAPACITOR.          | 54 |

|   |         | 5.2.2 AUTOMATED MEASUREMENT PROCEDURES.                | 55 |

|   |         | 5.2.3 DOUBLE-LAYER CAPACITOR INITIAL CONDITIONS.       | 57 |

|   | 5.3     | PARAMETERS MEASUREMENTS.                               | 65 |

|   | 5.4     | DISCUSSION OF MEASUREMENTS.                            | 67 |

|   |         |                                                        |    |

| 6 | EQUIVAL | LENT MODEL VERIFICATION.                               | 69 |

|   | 6.1     | EQUIVALENT MODEL MATHEMATICAL REPRESENTATION.          | 70 |

|   | 6.2     | VERIFICATION OF EQUIVALENT MODEL ASSUMPTIONS.          | 72 |

|   |         | 6.2.1 EXPERIMENTAL DEPENDENCE OF C AS FUNCTION OF V.   | 73 |

|   |         | 6.2.2 DISTINCT TIME BEHAVIOR OF THE BRANCHES.          | 73 |

|   | 6.3     | COMPARISON BETWEEN EXPERIMENTAL AND SIMULATED RESULTS. | 76 |

| 7   | ENERGY   | CONSIDERATIONS                                        | 85  |

|-----|----------|-------------------------------------------------------|-----|

|     | 7.1      | DOUBLE-LAYER CAPACITOR LOSSES                         | 85  |

|     | 7.2      | ENERGY IN THE IMMEDIATE BRANCH OF THE DOUBLE-LAYE     | R   |

|     |          | CAPACITOR                                             | 91  |

|     | 7.3      | ENERGY INTERCHANGE DEFINITION                         | 94  |

| 8   | SERIES   | CONNECTION PERFORMANCE                                | 98  |

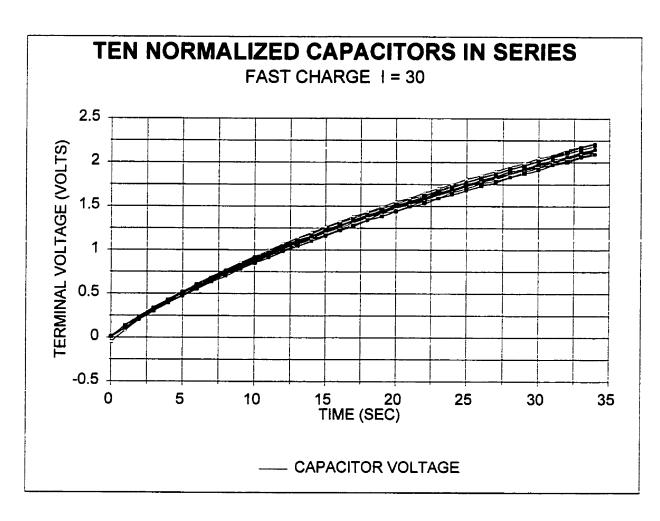

|     | 8.1      | FAST CHARGE TEST                                      | 98  |

|     | 8.2      | TEN CONSECUTIVE CYCLES TEST                           | 99  |

|     | 8.3      | FIVE HUNDRED CONSECUTIVE CYCLES TEST                  | 101 |

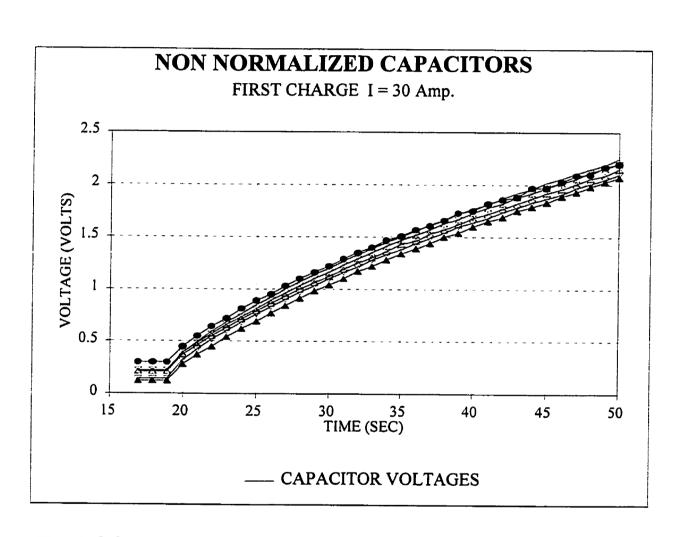

|     | 8.4      | SERIES CONNECTION OF NON-NORMALIZED CAPACITORS        | 104 |

|     | 8.5      | SERIES CONNECTION SELF-CHARGE DISTRIBUTION TEST       | 104 |

|     |          |                                                       |     |

| 9   | CONCLUS  | IONS                                                  | 107 |

| API | PENDIX A | PANASONIC DOUBLE-LAYER CAPACITORS DATA SHEET          | 112 |

| API | PENDIX B | S SOFTWARE AND HARDWARE DESIGN DETAILS                | 113 |

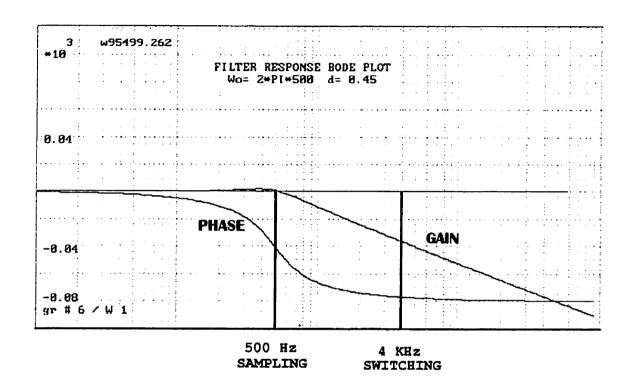

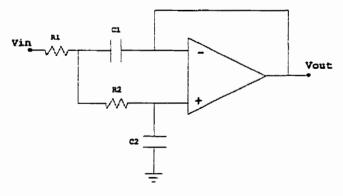

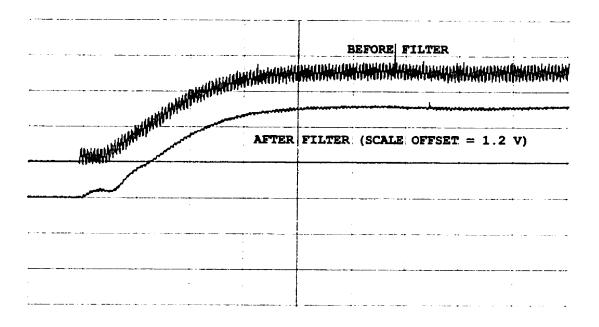

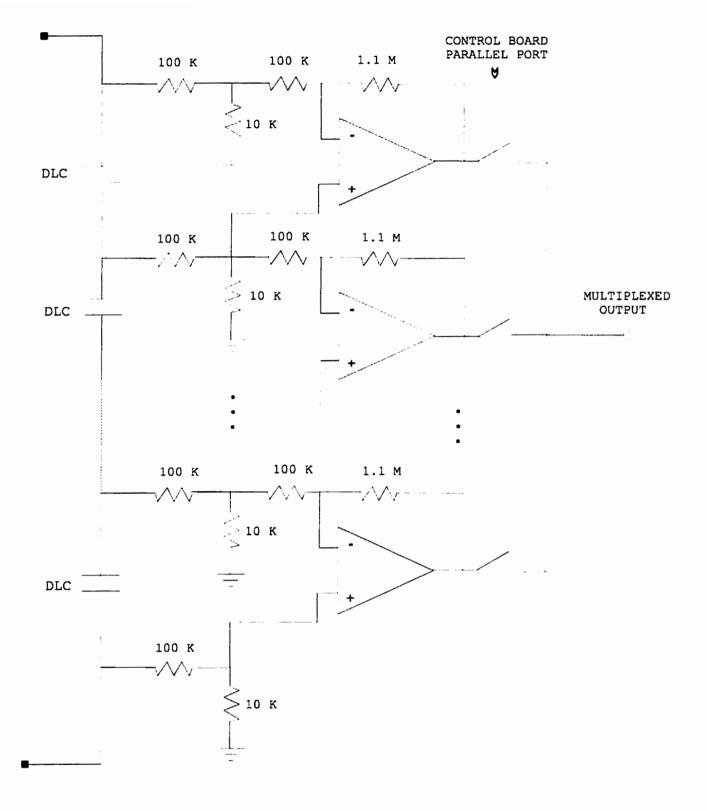

|     | B.1      | FILTER DESIGN                                         | 113 |

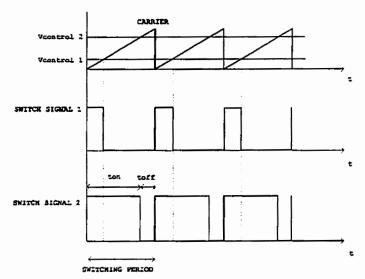

|     | B.2      | CURRENT CONTROL                                       | 114 |

|     | в.3      | DATA ACQUISITION SOFTWARE                             | 118 |

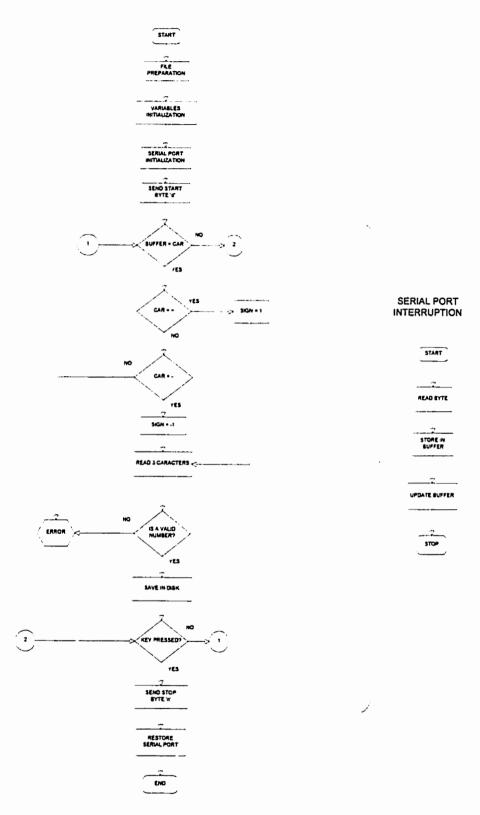

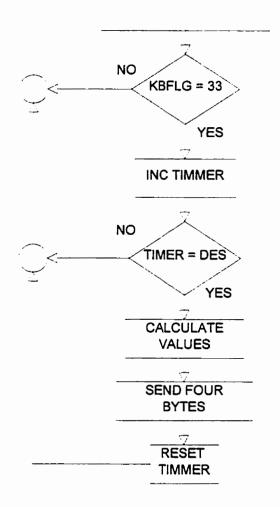

|     |          | B.3.1 PC DATA COLLECTION PROGRAM                      | 118 |

|     |          | B.3.2 DATA TRANSMISSION ROUTINE                       | 120 |

|     | B.4      | SERIES CONNECTION SOFTWARE AND HARDWARE MODIFICATIONS | 122 |

|     |          |                                                       |     |

| API | PENDIX C | LIST OF PROGRAMS                                      | 125 |

|     | C 1      | CENEDAL CADACIMOD WEST BROCKAM                        | 125 |

| C.2        | SERIES CONNECTION TEST PROGRAM            | 145 |

|------------|-------------------------------------------|-----|

| C.3        | PASCAL PROGRAM FOR DATA ACQUISITION       | 159 |

| C.4        | PROGRAM FOR SIMULATION UNDER SAM4         | 162 |

| C.5        | PROGRAM FOR ENERGY AND LOSSES SIMULATIONS | 165 |

|            |                                           |     |

| APPENDIX D | ADDITIONAL PRACTICAL CONSIDERATIONS       | 166 |

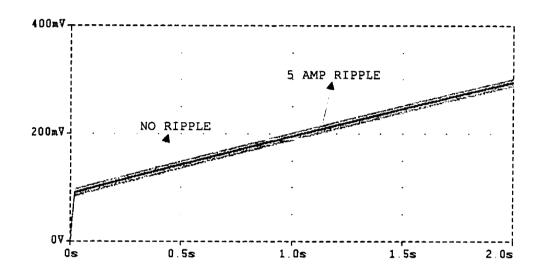

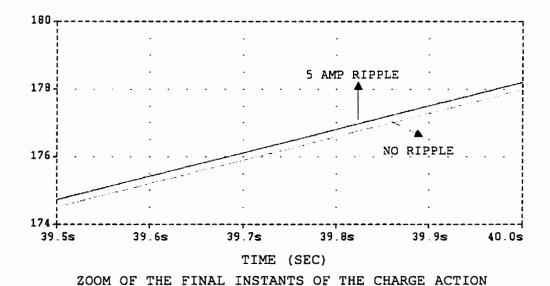

| D.1        | CURRENT RIPPLE EFFECT                     | 166 |

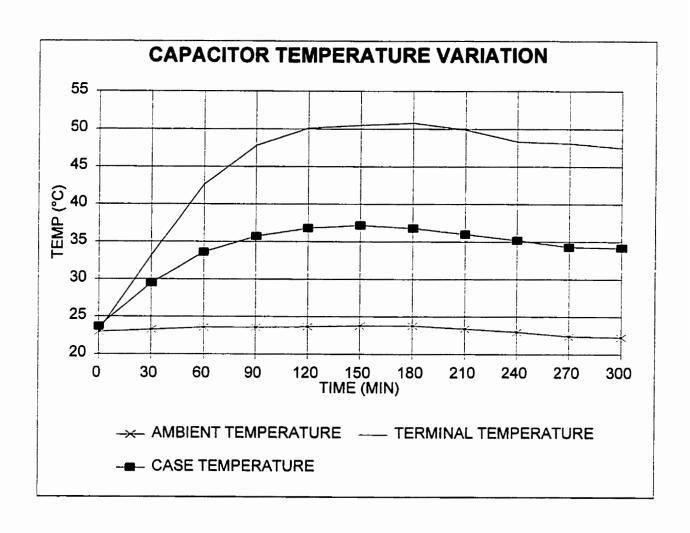

| D.2        | TEMPERATURE EFFECT IN THE PARAMETERS      | 170 |

| D.3        | CASE TEMPERATURE VARIATION                | 171 |

# LIST OF FIGURES

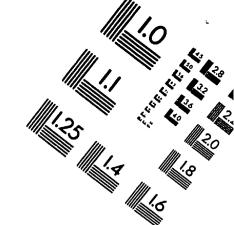

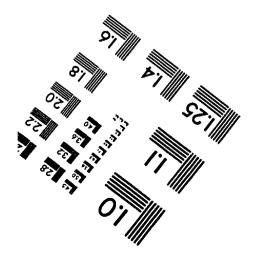

| FIGURE | 1.1 | INSUFFICIENCY OF THE SIMPLE RC MODELING                | 4  |

|--------|-----|--------------------------------------------------------|----|

| FIGURE | 2.1 | DOUBLE-LAYER FORMATION                                 | 11 |

| FIGURE | 2.2 | POTENTIAL OF THE DOUBLE-LAYER CHARGE DISTRIBUTION      | 12 |

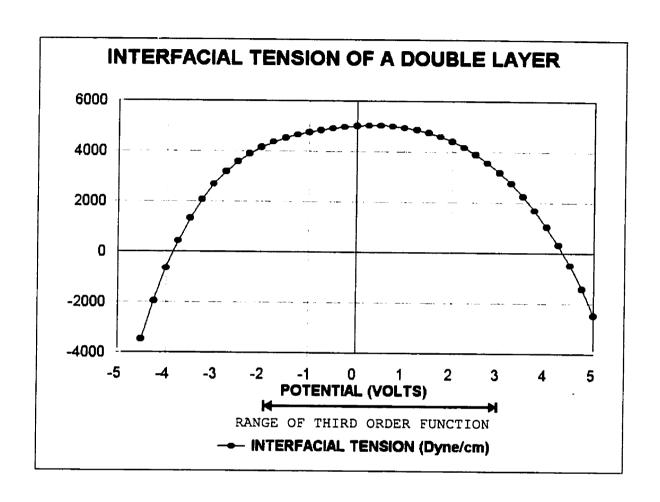

| FIGURE | 2.3 | TYPICAL ELECTROCAPILLARITY CURVE                       | 14 |

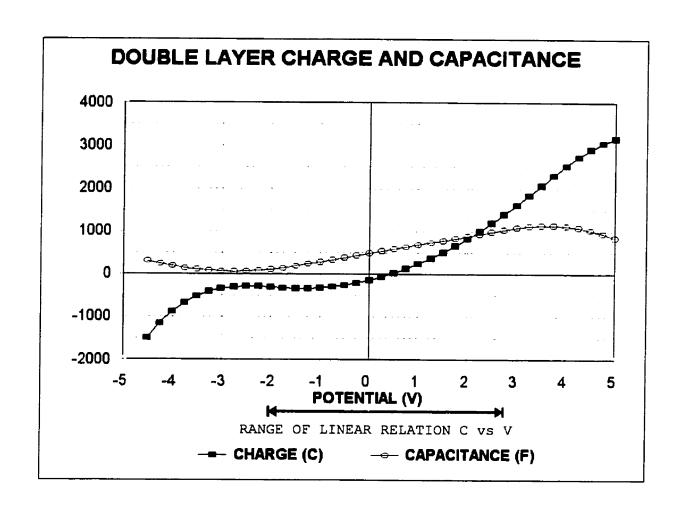

| FIGURE | 2.4 | TYPICAL DOUBLE-LAYER CHARGE AND CAPACITANCE CURVE      | 17 |

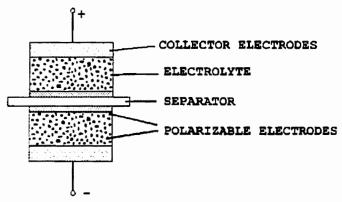

| FIGURE | 2.5 | ELECTRIC DOUBLE-LAYER CELL STRUCTURE                   | 19 |

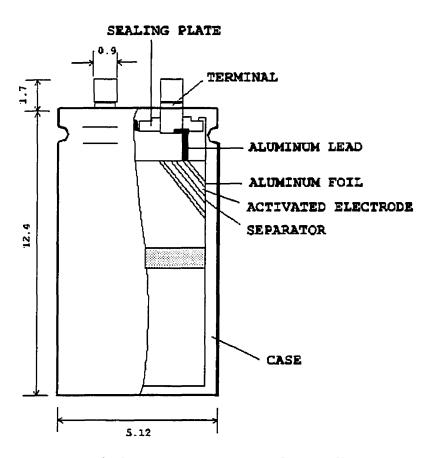

| FIGURE | 2.6 | PANASONIC DOUBLE-LAYER CAPACITOR CONSTRUCTION          | 20 |

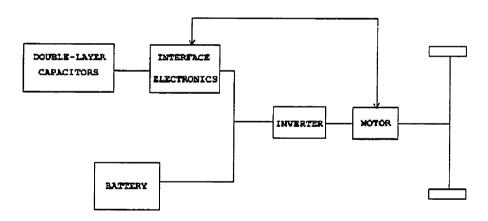

| FIGURE | 2.7 | ELECTRIC VEHICLE APPLICATION                           | 24 |

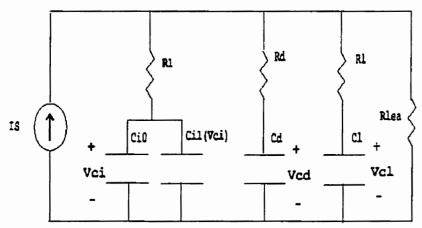

| FIGURE | 3.1 | GENERAL DOUBLE-LAYER CAPACITANCE MODEL                 | 28 |

| FIGURE | 3.2 | PROPOSED MODEL STRUCTURE                               | 31 |

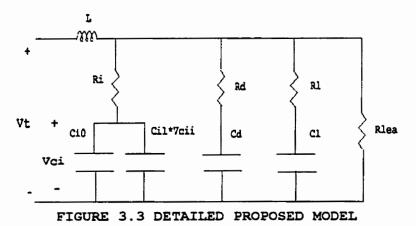

| FIGURE | 3.3 | DETAILED PROPOSED MODEL                                | 34 |

| FIGURE | 4.1 | IDENTIFICATION OF IMMEDIATE BRANCH PARAMETERS          | 40 |

| FIGURE | 4.2 | CHARGE REDISTRIBUTION EQUIVALENT CIRCUIT               | 41 |

| FIGURE | 4.3 | dV/dt CALCULATION                                      | 43 |

| FIGURE | 4.4 | EQUIVALENT CIRCUIT FOR CHARGE DISTRIBUTION TO THE LONG | G  |

|        |     | TERM BRANCH                                            | 44 |

| FIGURE | 4.5 | CAPACITOR INDUCTANCE IDENTIFICATION                    | 47 |

| FIGURE | 5.1 | DOUBLE-LAYER CAPACITOR TEST FACILITY                   | 50 |

| FIGURE | 5.2 | FILTER RESPONSE BODE PLOT                              | 53 |

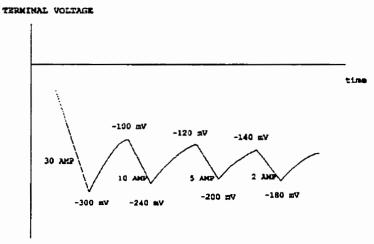

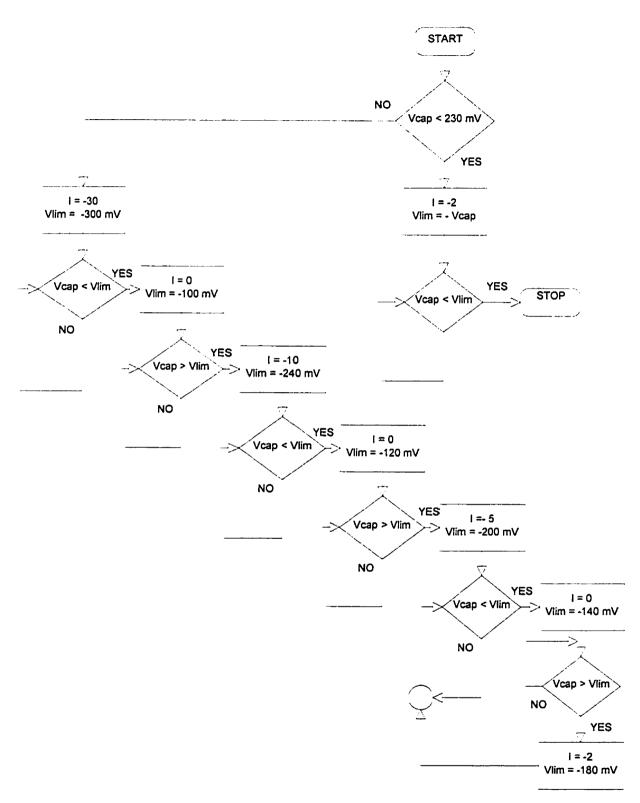

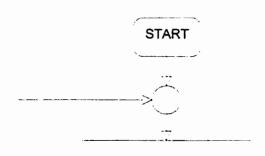

| FIGURE | 5.3 | FLOW CHART FOR AUTOMATIC PARAMETER MEASUREMENTS        | 58 |

| FIGURE | 5.4 | DISCHARGE CYCLES DURING NORMALIZATION                  | 62 |

| FIGURE | 5.5 | NORMALIZATION PROCESS FLOW CHART                       | 64 |

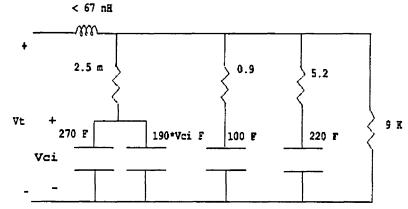

| FIGURE | 5.6 | MEASURED EQUIVALENT MODEL FOR THE 470 F CAPACITOR      | 66 |

| FIGURE | 6.1 | EQUIVALENT MODEL FOR SIMULATIONS                       | 70 |

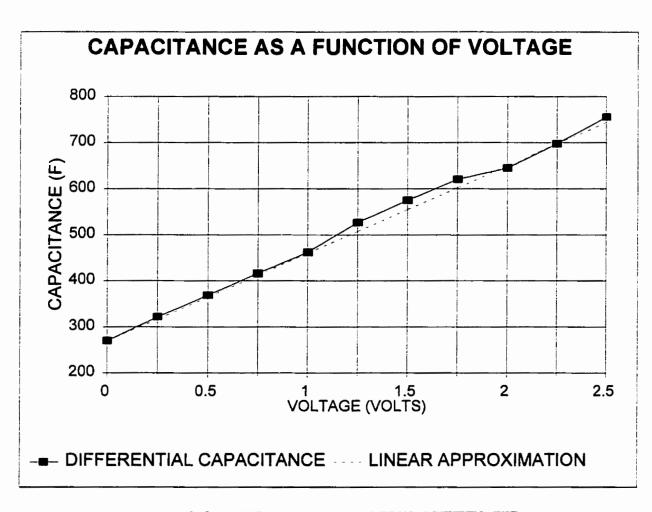

| FIGURE | 6.2 | EXPERIMENTAL RELATION BETWEEN CAPACITANCE AND VOLTAGE  | 74  |

|--------|-----|--------------------------------------------------------|-----|

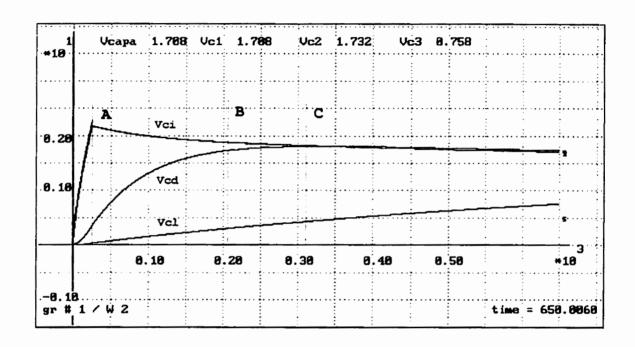

| FIGURE | 6.3 | VERIFICATION OF THE IDENTIFICATION ASSUMPTIONS         | 75  |

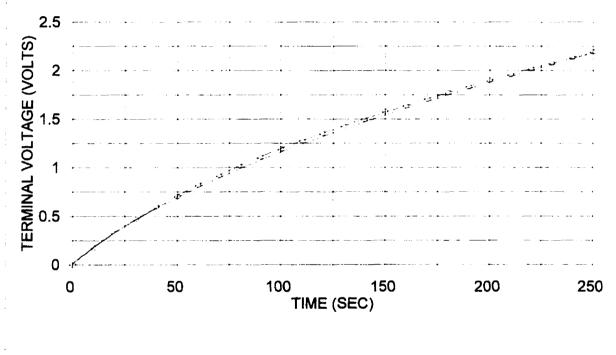

| FIGURE | 6.4 | IMMEDIATE AND DELAYED BRANCHES VERIFICATION            | 79  |

| FIGURE | 6.5 | LONG TERM BRANCH VERIFICATION                          | 80  |

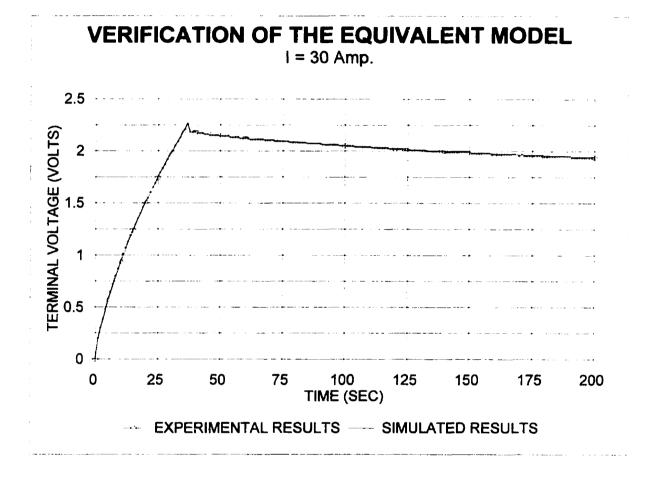

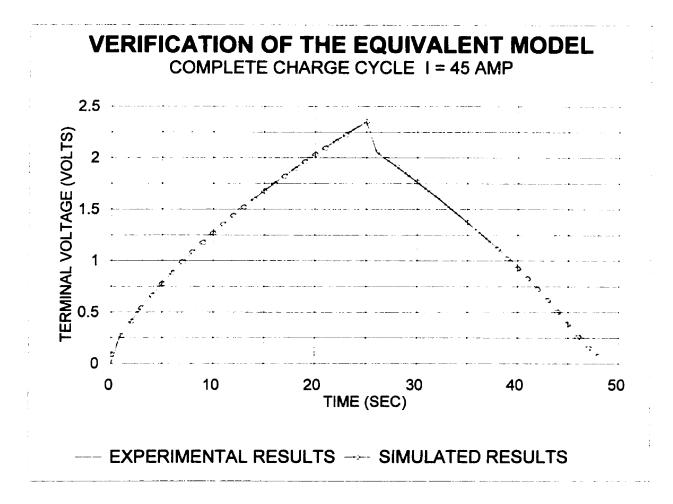

| FIGURE | 6.6 | VERIFICATION OF THE EQUIVALENT MODEL.                  | 81  |

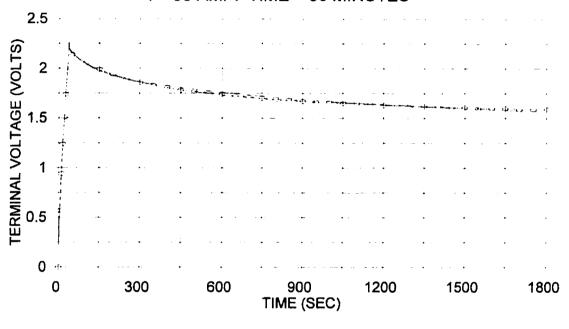

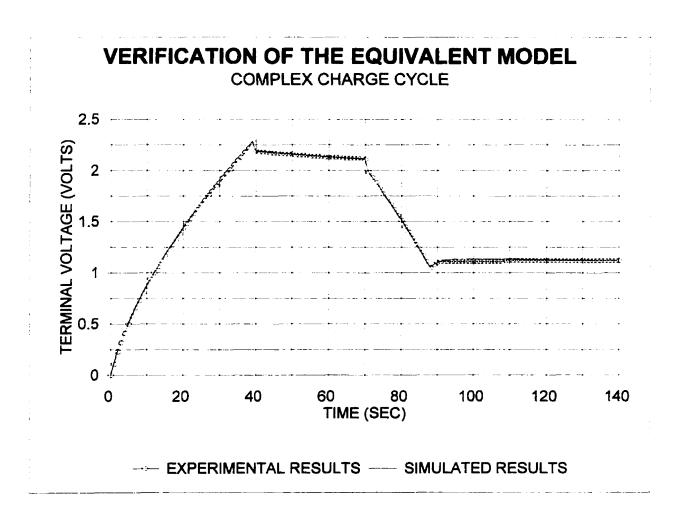

| FIGURE | 6.7 | VERIFICATION OF THE EQUIVALENT MODEL.                  | 82  |

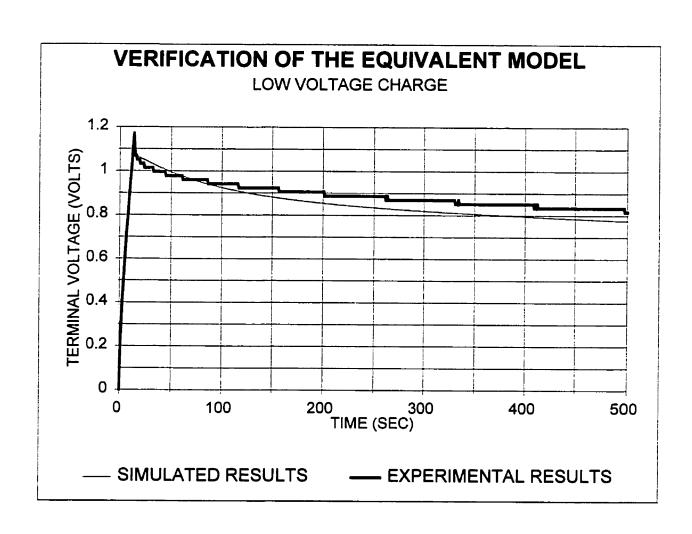

| FIGURE | 6.8 | VERIFICATION OF THE EQUIVALENT MODEL.                  | 83  |

| FIGURE | 6.9 | VERIFICATION OF THE EQUIVALENT MODEL.                  | 84  |

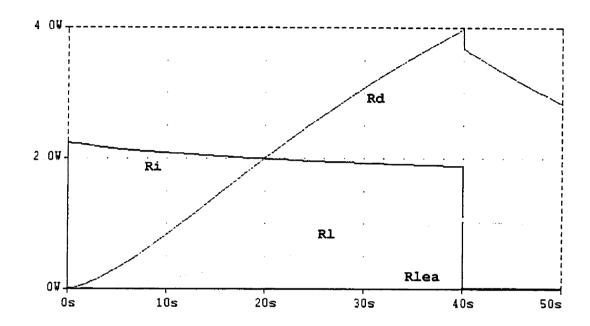

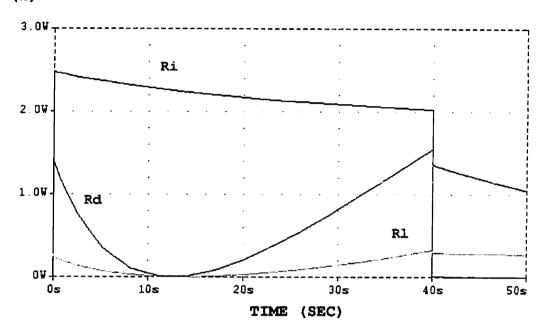

| FIGURE | 7.1 | LOSSES PER BRANCH. CAPACITOR NORMALIZED                | 87  |

| FIGURE | 7.2 | LOSSES PER BRANCH. CAPACITOR PRECHARGED                | 89  |

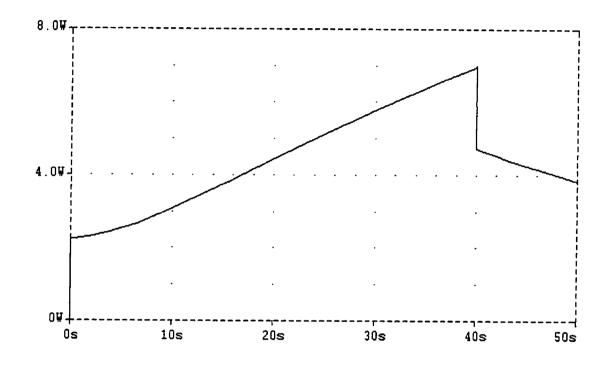

| FIGURE | 7.3 | TOTAL LOSSES IN A SINGLE CHARGE                        | 90  |

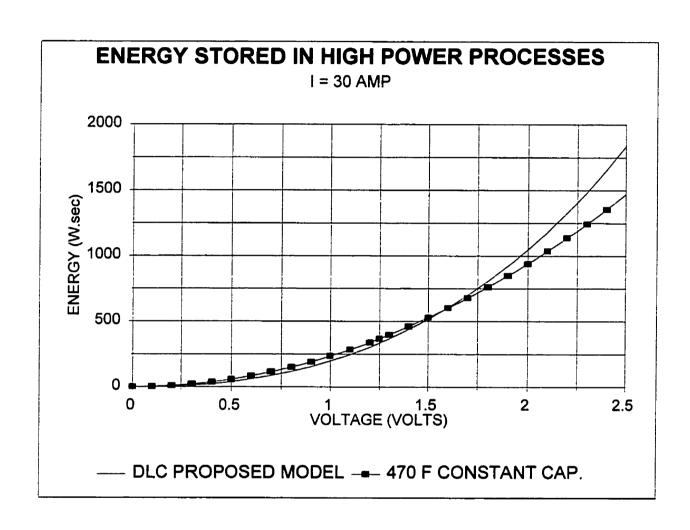

| FIGURE | 7.4 | ENERGY STORED IN HIGH POWER ACTIONS                    | 93  |

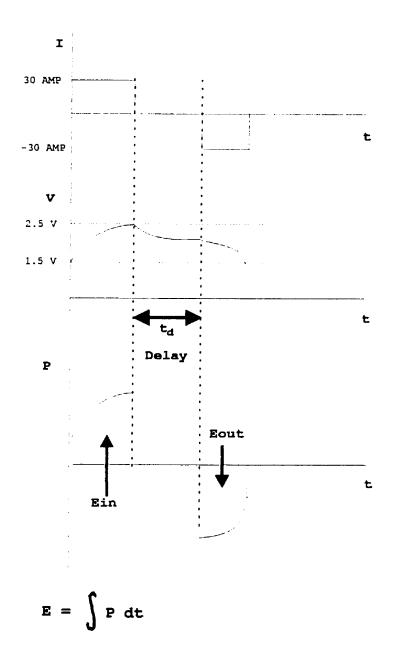

| FIGURE | 7.5 | ENERGY INTERCHANGE DEFINITION                          | 96  |

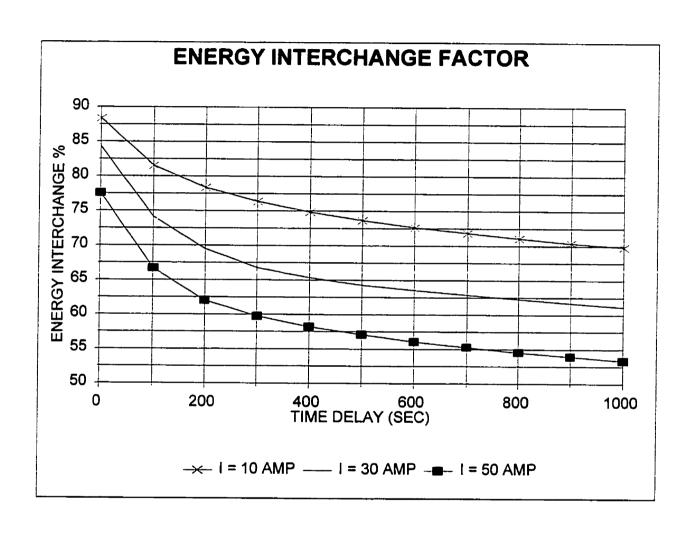

| FIGURE | 7.6 | ENERGY INTERCHANGE FACTOR VS TIME DELAY                | 97  |

| FIGURE | 8.1 | VOLTAGE DRIFT AMONG NORMALIZED CAPACITORS IN SERIES    | 100 |

| FIGURE | 8.2 | VOLTAGE DRIFT AMONG NON-NORMALIZED CAPACITORS          | 105 |

| FIGURE | B.1 | FILTER SCHEMATIC                                       | 113 |

| FIGURE | B.2 | CHARGE CURRENT BEFORE AND AFTER THE FILTER             | 115 |

| FIGURE | B.3 | PULSE WIDTH MODULATION                                 | 116 |

| FIGURE | B.4 | PC DATA ACQUISITION PROGRAM FLOW CHART                 | 119 |

| FIGURE | B.5 | CONTROLLER BOARD DATA ACQUISITION RESPONSE             | 121 |

| FIGURE | в.6 | MULTIPLEXER SYSTEM                                     | 123 |

| FIGURE | D.1 | CURRENT RIPPLE EFFECT IN THE TERMINAL VOLTAGE          | 168 |

| FIGURE | D.2 | CURRENT RIPPLE EFFECT IN THE CAPACITOR LOSSES          | 169 |

| FIGURE | D.3 | CAPACITOR TEMPERATURE VARIATION DURING CONTINUOUS CHAP | RGE |

|        |     | AND DISCHARGE ACTIONS                                  | 172 |

## CHAPTER 1

#### INTRODUCTION

The fast, reliable and efficient storage and recovery of energy is an important requirement in many power electronics applications. The batteries, which have been the traditional storage devices, should not only be able to store large amounts of energy, but also to draw that energy at high rates. However, the fast advance in the electronic devices and systems has not been accompanied by the same rate of improvement in the batteries' performance. Further, the battery performance is the main obstacle in many designs and applications.

The development of a new kind of capacitor, with larger value of capacitance and higher energy density, may open a wide range of possible applications in the power electronics field, not only as an energy storage element, but also as a fast energy delivery device.

Several kinds of power capacitors with different construction technologies have been developed since 1989. Most of them are still in the laboratory research stage. The PANASONIC power capacitor is one of the first carbon-based double-layer capacitors available commercially, and several prototypes are available at the University of Toronto for experimental testing; therefore, this device will be the object of this research.

The PANASONIC capacitors are based on the electrical double-layer principle. They are available in two ratings; 470 F and 1500 F. The double-layer capacitors present several characteristics which are very attractive to the power electronics field; among them are high power, energy density more than ten times greater than that of the

electrolytic capacitors, low internal resistance and very high capacitance.

Modeling the double-layer capacitors with a single resistive capacitive circuit is insufficient to describe the device behavior. Furthermore, so far, almost no research regarding the use of the double-layer capacitors has been published, and the information supplied by the manufacturer is not enough to develop a more accurate model and to understand the operation of the capacitors. Moreover, the first experimental results have shown inconsistent results that suggest the study of those devices is not a simple task.

The general objective of this research is the characterization of the double-layer capacitors through the development of an equivalent model that should be based on the terminal behavior of the device. This objective includes the selection of an adequate model, the determination of a procedure for calculating the model parameters, and in general, the understanding of the double-layer capacitors terminal performance. The presence of extremely long transient phenomena inside the double-layer capacitors makes it very difficult to conduct repeatable experiments; therefore, the development of a standard procedure to secure the same known initial conditions in every experiment is required.

The characterization will be completed by studying the losses and energy inside the double-layer capacitor and the performance of the capacitors connected in series.

This research is the fundamental starting point for future research and one important reference for the utilization of the double-layer capacitors in power electronics applications.

In the next section, a brief description of the main research

goals is presented. The main objective of the thesis is explained in detail, and the contribution of this research is emphasized. In addition, other goals that complete the understanding of the double-layer capacitors are presented and described.

#### 1.1 THESIS OBJECTIVES

#### 1.1.1 Modeling of Double-Layer Capacitors

One of the ways to obtain a better understanding of the performance and characteristics of new systems or devices is to model the system under study. The use of simple and well-known elements to represent a more complex device enables any engineer or scientist to become familiar in a short time with the properties of the device. In addition, the equivalent model makes possible the use of conventional mathematical techniques and simulation tools to study the device and its applications.

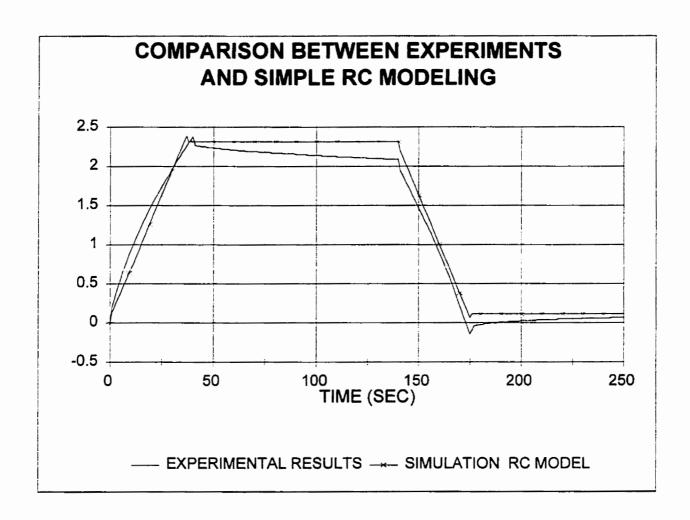

Modeling the double-layer capacitors using a single resistance and a single capacitance is insufficient to represent adequately the electrical behavior of the devices. Figure 1.1 shows the comparison between the experimental and simulated results of the terminal voltage when a simple RC series circuit is used to model the DLC. In this experiment a constant current of thirty amperes was used to charge the DLC; then, one hundred seconds pass without current application, and finally, the capacitor was discharged using a constant current of thirty amperes.

The deviation between the simulation and experiment demonstrates the presence of a more complex response and internal transients and therefore the inadequacy of this elementary model.

The main general objective of this research is the development

FIGURE 1.1 SIMPLE RC MODELING.

of an equivalent model for the DLC that should be based on two criteria: First, the model should be as simple as possible but describing the terminal behavior, over a time span of 30 minutes, accurately enough for design and application purposes. Second, the model parameters should be calculated based on the results of a series of measurements at the device terminals in a repeatable and clear procedure. Although there are equivalent models based on the physics of the double-layer, those models are not convenient for the design and analysis of double-layer capacitors applications in power electronics applications.

An equivalent model based on measurable electrical terminal parameters has several advantages:

First, the model parameters can be easily measured and verified several times using a simple experimental setup.

Second, because the fast advance of the technology makes almost certain the appearance of new improved devices, the proposed measurable model approach may be extended easily to future devices similar to those studied here.

Third, as the model uses typical electrical devices in its structure, that model is much easier to understand and analyze by engineers. Therefore, an accurate equivalent model provides the designer with the tools sufficient to integrate the DLC's in future designs.

Fourth, the availability of an equivalent model makes it possible to use simulation tools in order to anticipate the performance of the double-layer capacitors in specific applications, thus saving time and money.

#### 1.1.2 Energy Considerations

The general utilization of the double-layer capacitors in commercial applications depends on the adequate utilization of the energy by the devices. In this direction, a study of the energetic needs, losses, and efficiency is fundamental in order to complete the characterization.

The study includes the calculation of the losses in the doublelayer capacitor when it is subject to charge and discharge sequences. The energy study uses the proposed equivalent model and it is performed using simulation tools.

In addition, a study of the efficiency of the capacitor, based on the amount of energy that can be taken out of the capacitor with respect to the energy stored previously, is presented. Because of the long time constant present in the DLC response, the definition of efficiency is not a simple relation, and it will be a function of the time, so that it is necessary to define a cycle of charge in time that is the base for the efficiency study. In fact, the study should be defined as an energy interchange study for power electronics applications more than a traditional efficiency analysis.

#### 1.1.3 Series Connection

Because the rated voltage of the PANASONIC double-layer capacitors is only 2.3 V., the series connection study should be included as one necessary action in order to reach the voltage needed in most applications. In traditional capacitor banks, a resistance or another electronic device is placed externally in parallel with each capacitor in order to maintain a voltage balance among the capacitors. However, due to the DLC's high capacitance, which leads to long time

constants, and to the frequent current source applications in the power electronics field, the connection of external devices to balance the voltages in each capacitor is not useful.

Therefore, it is fundamental to study the performance of capacitors connected in series, giving special attention to the voltage drift when the capacitors are subject of several charge and discharge actions in sequence. The performance of the capacitors in the series test will show if it is necessary to design a more complicated system in order to balance the voltages and use the double-layer capacitors in series.

#### 1.2 THESIS OUTLINE

After the brief introduction and the clear definition and justification of the thesis objectives presented in the first part of this chapter, it is necessary to define the structure of the following chapters.

Chapter two presents a review of the double-layer background and double-layer capacitor construction. Furthermore, some possible applications for the double-layer capacitors are presented.

Chapter three introduces the selected double-layer capacitor equivalent model. First, the theoretical concepts and practical observations on which the selection of the model was based are discussed. Then, the different sections and elements of the model are defined and justified.

Chapter four introduces the procedure proposed for the identification of the equivalent model parameters.

Chapter five deals with the measurement of the equivalent model parameters. First, the general features of the experimental setup are

presented. Second, the measurement techniques needed in order to get trustworthy and accurate results are defined; this section includes the introduction of the automated test programs and the necessary normalization procedure. Third, the measurement results are presented. Finally, a discussion of the results is offered.

Chapter six uses the equivalent model and simulation tools in order to compare the model performance with the experimental results for several different tests. The simulations use the program SAM4 developed at the University of Toronto.

Chapter seven is a study of the losses and energy interchange inside the capacitor. This study uses the simulation software PSPICE and the verified equivalent model.

Chapter eight presents the results of an experimental study on the DLC series connection. Voltage drift among the capacitors, total capacitance, and the performance in short and long tests are the main points considered under research.

Chapter nine concludes with the results of the thesis and gives an overview of possible future research in this field.

## CHAPTER 2

# BACKGROUND OF DOUBLE-LAYER CAPACITORS

The electric double-layer phenomenon, described initially by H. von Helmholtz in 1879, was the starting point that led, almost one century later, to the development of large energy density capacitors. The electric double-layer capacitor was developed initially by Boss in 1971; since then, this kind of capacitor has been studied and developed by several corporations reaching capacitance and energy density levels which open a wide range of possible applications in power electronics, not only as energy storage device, but mostly as a fast energy delivery element. Although the double-layer capacitors have lower energy density than batteries, they can release that energy at high power level because of their low internal resistance.

Electric double-layer capacitors can be cycled many times, can operate over a wide temperature range, and are expected to reduce their cost as the manufacturing technology improves. On the other hand, the engineering information available is not enough to encourage the massive use of these devices in applications.

Several different names have been given to the high energy density capacitors; among them are: Supercapacitors, Pseudocapacitors, and Ultracapacitors. The more general name of double-layer capacitors (DLC's) will be used during this report with reference to the high energy density capacitors.

The initial point of interest is to obtain a good understanding of the technology upon which the DLC's are based. This aspect will be introduced in the next section.

#### 2.1 ELECTRICAL DOUBLE-LAYER TECHNOLOGY

A double-layer charge distribution is formed when two different phases, solid/liquid in the DLC's case, are in contact, and charge separation occurs at the boundary. The formation of the double-layer can be explained in the following way: when two phases are brought into contact, ions, which are assumed to be positively charged, migrate from one phase, in which the escaping tendency is larger, to the other phase. Because of this ionic migration, one phase becomes positively charged and the other negatively charged producing a double-layer charge distribution structure [1].

The reason for this chemical process, in which ions migrate from one phase to the other, is the difference in the inner potential between the two phases. When the superficial contact is established, the inner potential difference produces a force which transfers the particles across the interface.

The double-layer charge distribution generates an electric field, and subsequently an interface's potential. That electric field will hinder further migration of the ions as it compensates for the inner potential difference between the phases. Therefore, after a certain number of ions have migrated, a state of equilibrium is reached.

The double-layer effect behaves like an electric capacitor in that it is capable of storing energy. If a comparison with a parallel plate capacitor is done, the charge is stored in the double-layer formed across the interface. However, in this case, the distance between the plates (phases) is very small producing a device with high specific capacitance [2].

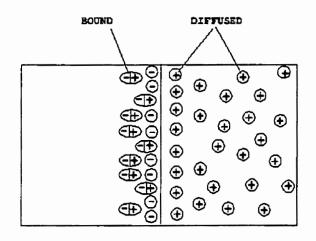

When the electric charge distributes itself throughout one of the phases, as occurs in the liquid, the double-layer is called

"diffused". As the solid structure does not allow much of a charge distribution, the charge produced in the solid phase is a surface charge. The surface charge at the solid phase generate a dipole orientation which generates another effect called "bound" double-layer. This bound double-layer is extremely thin, probably one molecule thick, and can be said to form a molecular capacitor. In the bound double-layer the charges neither move nor separate from the surface [1]. The capacitances of the two kinds of double-layer mentioned can be assumed to be in series, and they will produce the capacitor effect used in the double-layer capacitors.

Figure 2.1 represents the double-layer effect resultant in the interface between a liquid and a solid.

SOLID PHASE LIQUID PHASE

FIGURE 2.1 DOUBLE-LAYER FORMATION

If an external voltage is applied to the double-layer, the potential difference between the phases is increased or decreased depending on the sign of the applied voltage and the number of charges needed to establish the equilibrium is modified. The relation between the charge stored in the double-layer and the external voltage will

define the capacitance for the double-layer interface.

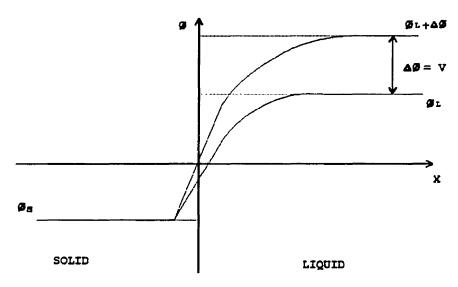

Figure 2.2 presents the potential curve at the interface including the effect that the external potential applied has on the charge stored at the double-layer. In the figure  $\phi$ s is the inner potential at the solid,  $\phi$ L is the inner potential at the liquid, X is the position and V is the external voltage applied. A positive external voltage increases the space charge at the interface. Also note in the right section of figure 2.2 the effect of the diffused double-layer that produces a curve in the potential characteristic.

FIGURE 2.2 POTENTIAL OF THE DOUBLE-LAYER CHARGE DISTRIBUTION

Previous studies in interfacial electrochemistry reported that the interface can never be represented simply by a parallel plate capacitor [1],[2],[3]. The more complex representation of the double-layer capacitor is mainly due to the following factors: First, all double-layer capacitors can be self discharged by electrochemical reactions taking place across the interface. Second, the charge held by the capacitor is not a linear function of the potential across it.

Third, the double-layer capacitance was found to depend not only on the composition of the solution but also on the concentration of the electrolyte in a given system [2].

The second factor introduced in the previous paragraph establishes that the total charge stored in the two layers is not linearly related to the potential difference between the layers; therefore, the capacitance of the double-layer is not a constant but depends on the potential difference.

The capacitance is generally defined as the ratio between the charge and the voltage. Because of the non-constant capacitance in the double-layer distribution, the previous definition is insufficient to represent appropriately the double-layer capacitance; therefore, a more adequate definition is used:

The differential capacitance  $(C_{\text{diff}})$  is defined as the derivative of the charge with respect to the potential difference between the phases:

$$C_{diff} = \frac{dQ}{dE} \quad (2.1)$$

The double-layer charge distribution is physically studied through the so called interfacial tension. The interfacial tension is developed at the contact surface between phases and it is given by the force per unit of length at the interface; this quantity is also a function of the potential difference. Based on the interfacial tension definition, the curve of interfacial tension vs potential difference has been measured using different solutes and electrolytes in the formation of the double-layer [1],[2],[4]. This curve is called the electrocapillarity curve and the results have been concordant with the fact that the capillarity curve can be modelled,

FIGURE 2.3 TYPICAL ELECTROCAPILLARITY CURVE.

at least for potential differences close to zero volts, as a third order function. Using different non ionic solutes, the location of the curve may be affected but not its general shape.

Figure 2.3 represents the general form of the capillarity curve and the approximate range of voltage used in the double-layer capacitors.

Based on the capillarity curve, the so-called capillarity equation is developed. In the capillarity equation, the interfacial tension  $(\gamma)$  is related to the electric potential difference across the phases (E) and to the surface charge  $(\sigma)$ .

A number of more or less equivalent derivations of the electrocapillarity equation have been given [2]. One of the simplest is the Lippmann derivation which is based on the supposition that the interface is analogous to a parallel plate condenser, so that the reversible work dG, associated with changes in area and in charge, is given by:

$$dG = \gamma dA + \Delta \phi dq \quad (2.2)$$

where q is the total charge and  $\Delta \varphi$  is the difference in potential. The second term on the right gives the work needed to increase the charge in a condenser. Integration of the last equation keeping  $\gamma$  and  $\Delta \varphi$  constants gives:

$$G = \gamma A + \Delta \Phi q \quad (2.3)$$

The last equation may now be redifferentiated with respect to different variables ( $\gamma$  and  $\Delta \phi$ ):

$$0 = Ad\gamma + qd(\Delta \phi) \qquad (2.4)$$

It should be noted that E in the electrocapillarity equation

refers to the externally measured potential difference, while  $\Delta \varphi$  in the deduced equation is the difference in potential between the two phases in question. These two quantities are not the same, but generally they differ by some constant involving the nature of the electrodes and other junctions in the system; so that changes in both are equal, and dE may be substituted for  $d(\Delta \varphi)$ . Substituting  $d(\Delta \varphi)$  and using the charge density  $(\sigma = q/A)$  instead of the total charge (q), the last equation represents the electrocapillarity equation:

$$\left(\frac{d\mathbf{\hat{\gamma}}}{dE}\right)_{\mu} = -\sigma \quad (2.5)$$

where the parameter  $\mu$  is the called electrochemical potential which depends on the solution composition, and it is constant for the same capacitor materials.

A more detailed study of the electrocapillarity equation is presented by Adamson [4].

Using the defined differential capacitance presented in equation 2.1 and the capillarity equation (2.5), the capacitance of the double-layer is related to the interfacial tension through the following equation:

$$C_{diff} = \left(\frac{dQ}{dE}\right) = K \frac{d}{dE} \left(\frac{dY}{dE}\right)$$

(2.6)

As the capillarity curve can be represented by a third order equation in the region close to zero volts, the differential capacitance expected in this region results in a linear function of the potential difference after the double differentiation indicated in equation 2.6. Figure 2.4 presents the double-layer charge and double-layer capacitance calculated from figure 2.3. The region of interest for the double-layer capacitors is again indicated.

FIGURE 2.4 TYPICAL DOUBLE-LAYER CHARGE AND CAPACITANCE CURVE.

#### 2.2 DOUBLE-LAYER CAPACITORS DEVELOPMENT

The first group of double-layer capacitors, developed in the eighties, was mostly the result of the increasing demand for miniaturization of devices used in the backup of memories and microcomputers. In general, they had capacitance values lower than 1 F, and very small dimensions as was dictated by the desired application [5].

Since then, several studies have been carried out to improve the capacitor characteristics by modifying the material of the polarizable electrodes, pore size distribution, packaging, and electrolyte material. In the early nineties, the development of a very high capacitance and low DC resistance capacitor was reported [6]. That capacitor, with greater dimensions, suitable for charging and discharging at high current levels, and with higher energy density, was the base in which PANASONIC developed and commercialized a double-layer capacitor which is rated 2.3 volts and 470 F. or 1500 F. These PANASONIC devices are the objects of study in this research.

Recently, other large capacitance devices with values up to 1000 F. and 5.5 volts using several cells in series have been reported [7]. Those devices, not available commercially, show the fast improvement in the characteristics of the double-layer capacitors, and give a good perspective into the future use of these devices in power applications.

#### 2.3 DOUBLE-LAYER CAPACITOR CONSTRUCTION

The basic general structure of the double-layer capacitor consists of a pair of polarizable electrodes. The electrodes are

formed by solid colloids suspended in an electrolytic solution, a separator between the electrodes, two collector electrodes as solid contacts, and a pair of leads used to charge and discharge the capacitor [6],[8].

Figure 2.5 shows the basic structure of a double-layer cell.

FIGURE 2.5 STRUCTURE OF THE ELECTRIC DOUBLE-LAYER CELL

The PANASONIC double-layer capacitor employs aluminum coils as collector electrodes, activated carbons as polarizable electrodes, binding material in the aluminum foils, and polypropylene separators. A mixture of activated carbons with particle size of 10µm, the organic binder and the solvent were coated on an aluminum foil. After removal of the solvent, a pair of aluminum foils with activated carbon layers were wound in spiral with polypropylene separators. The electrode wounds were immersed in an electrolytic solution, and then, the final compound was assembled in an aluminum case to form the capacitor [6].

The electrolytic solution is a mixture of tetraethyl-ammonium, tetrafluoroborate and propylene carbonate. Aluminum rods were used as connection terminals in order to support high current and obtain low resistance [6].

The reason for using activated carbons as polarizable electrodes

is the high specific surface area and high chemical stability of the carbon particles. As was explained, the capacitor effect is produced by the interface between two different phases, so that the surface of the carbon particles gives the possibility of obtaining greater value of capacitance per volume unit. In addition, the activated carbon electrodes have features of low sheet resistance and high density of carbon particles, which help to improve the characteristics of the device.

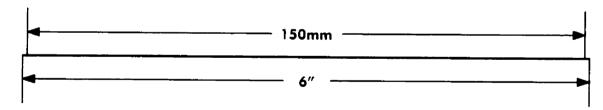

Figure 2.6 represents the structure and dimensions in centimetres of the PANASONIC 470 F double-layer capacitor.

FIGURE 2.6 CONSTRUCTION OF THE PANASONIC DOUBLE-LAYER CAPACITOR

Among the main features of the 470 F. capacitor given by the manufacturer are the following:

- High values of capacitance.

- Small temperature dependence of the capacitance value.

- Small internal resistance of the device.

- High energy density.

- Large values of current are supported by the device.

Table 2.1 shows quantitative and structural characteristics of the 470 F device given by the manufacturer.

| RATED VOLTAGE     | 2.3 V                                 |

|-------------------|---------------------------------------|

| RATED CAPACITANCE | 470 F                                 |

| DIAMETER          | 5.12 cm                               |

| LENGTH            | 12.4 cm                               |

| VOLUME            | 255 cm <sup>3</sup>                   |

| WEIGHT            | 330 gm                                |

| ENERGY DENSITY    | 1.05 Wh/kg or 1.35 Wh/l               |

| ENERGY STORED     | 1241 W.sec                            |

| TECHNOLOGY        | SINGLE SPIRAL CELL                    |

| MATERIALS         | CARBON BASED, NON AQUEOUS ELECTROLYTE |

TABLE 2.1

The data sheet given by the manufacturer in reference to the double-layer capacitors that are the objects of this research is presented in Appendix A.

# 2.4 COMPARISON BETWEEN DOUBLE-LAYER AND ELECTROLYTIC POWER CAPACITORS

The innovation that the double-layer capacitors may represent in the electronics field may be visualized in a better way if their rated characteristics are compared with a classical electrolytic capacitor used in many power electronics applications. Table 2.2 compare the manufacturer information of the 1500 F double-layer capacitor with an electrolytic power capacitor of similar physical dimensions.

| PARAMETER      | D-L CAPACITOR       | ELECTROLYTIC CAP. |

|----------------|---------------------|-------------------|

| RATED VOLTAGE  | 2.3 V               | 350 V             |

| CAPACITANCE    | 1500 F              | 4800 μF           |

| VOLUME         | 610 cm <sup>3</sup> | 885 cm³           |

| WEIGHT         | 800 gm              | 1000 gm           |

| ENERGY DENSITY | 1.39 Wh/kg          | 0.081 Wh/kg       |

| ENERGY STORED  | 4000 W.sec          | 294 W.sec         |

TABLE 2.2

The table 2.1 shows the notorious advantages of the DLC's in energy stored, device weight, volume and mainly in energy density.

It should be especially noted that the energy density of the DLC's is seventeen times higher than that of the electrolytic capacitor. In addition, an increase in the energy density of the double-layer capacitors by a factor of at least two is expected in the near future [9].

The only rating in which the electrolytic capacitor surpasses the double-layer capacitor is in the rated voltage. No appreciable improvements in the double-layer capacitor rated voltage are expected. That is because the use of higher voltage in this kind of device would produce irreversible chemical reactions, in particular the dissociation of the electrolyte solution.

The last condition makes it necessary to study in detail the double-layer capacitors connected in series. The connection of several double-layer capacitor cells in series inside the same case has already been reported [7].

#### 2.5 DOUBLE-LAYER CAPACITORS APPLICATIONS

There is a large spectrum of possible applications for the DLC's. Most of them depend on the increase in the knowledge about the characteristics and performance of the devices. In the next pages, some of the potential applications that in the short term are of interest are presented.

# 2.5.1 Electric and Hybrid Vehicle Applications

The average power that must be supplied by the battery in an all electric vehicle is relatively low depending on the driving mode and grade[9]. However, the peak power pulses during some periods are much higher due to the sudden acceleration and passing actions. Some studies have shown that the ratio between the peak power and the average power could be 16:1 or more [9]. If only a battery is used to supply the instant energy to the vehicle, the battery should be rated for the peak values increasing its weight, size, and cost.

The use of double-layer capacitors gives the possibility of

decoupling the peak power requirements from the average power. In this direction, the DLC's would meet the peak power requirements and the battery would supply the average power. Figure 2.7 shows the possible use of DLC's in an electric vehicle.

In addition, a study for the use of double-layer capacitors as energy source in hybrid vehicles instead of a battery has been reported [10]. In this study, the ratings with regard to the energy content and capacity needed to use the DLC's in hybrid vehicles are determined.

The main improvement needed to fulfill the requirements for this application is the increase in the energy density of the capacitor, up to at least 5 Wh/kg, in order to limit the space occupied by the double-layer capacitors [9],[10].

FIGURE 2.6 ELECTRIC VEHICLE APPLICATION

## 2.5.2 Electrically Heated Catalyst

A catalyst can be used in order to reduce the emissions from traditional vehicles. It has been reported that much higher levels of emission occur during the engine start and in the early stages; that is, when the system is still cold [9].

Using the energy stored in the DLC's, the catalyst could be heated up just prior to or during the engine start. The levels of power required to heat the catalyst are high but the amount of energy is relatively small, therefore, this appears to be a potential example for the use of double-layer capacitors.

# 2.5.3 Vehicle Accessories

Some automotive accessories, such as power steering and power brakes, require intermittent high power levels for their operation. Currently, these accessories utilize a hydraulically actuated or a vacuum actuated drive and accumulators for the energy supply. Double-layer capacitors would be adequate to supply the peak power and reduce the stress on the battery during periods of great demand.

#### 2.5.4 Uninterruptible Power Supplies

The objective of an electric supply is to provide a wide range and variety of customers with electrical energy. In practice, it is totally impossible to safeguard the electricity supply network against sporadic system failures.

However, there are many systems with critical loads which should have permanent power in order to protect the equipment involved. In addition, the presence of sensitive loads, typically computers, which may be seriously affected by relatively small disturbances, makes it necessary to maintain the quality of the power supply during disturbances[11].

Therefore, it is necessary not only to provide standby power in the event of supply failure, but also to make certain that the electrical input is pure, clean, and continuous.

Uninterruptible power supplies are designed and implemented in order to fulfill the previous conditions. They usually use a source of stored energy such as a battery which will give the energy during the main power failure.

Many of the power interruptions or disturbances only last a few seconds; in those cases, the energy required is relatively small but the power requirements may be high and that increases the size and cost of the battery.

The DLC's may be an adequate and reliable source of energy for these short backup power needs. They should reduce the size, increase the efficiency, and eventually reduce the cost of the UPS system.

# 2.5.5 Other Applications

There are unlimited possible applications for the double-layer capacitors: in medical equipment, in some military applications, in soldering equipment, in industrial electrical drives, as a memory backup for computers and other digital equipment, etc.

Not all of the applications mentioned earlier require and are adequate for the 470 F. PANASONIC capacitor. Some of them require lower levels of energy and capacitance but also make possible the use of smaller device sizes. In this direction, several other double-layer capacitors with different ratings and sizes are being developed by several corporations around the world [5],[8],[12].

# CHAPTER 3

# EQUIVALENT MODEL PROPOSAL

This chapter deals with the selection of an equivalent model which satisfies the general objectives of the thesis; that is, based on the double-layer capacitor terminal behavior and composed of general electrical components such as resistors, capacitors and inductors.

The selection of the equivalent model is based on two criteria: physical reasons related to the double-layer and the DLC construction and practical considerations resulting from the terminal model objective. The physical arguments are introduced in the following section.

#### 3.1 PHYSICAL FACTS LEADING TO THE MODEL

## 3.1.1 Time Behavior of the Double-Layer Capacitors

Chapter one presented the fact that electrical charge is stored in the double-layer when external voltage is applied. The flow of charges across the interface is not an instantaneous process. It depends on the ion mobility, environmental conditions and several other factors. In addition, the cross of electrical charges is followed by a series of charge distribution processes, and dipole orientations which take a considerably long time.

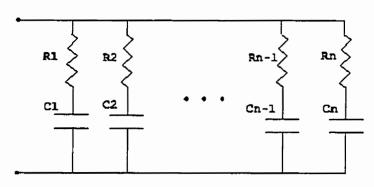

Based on the last factor, the capacitance of the double-layer is physically represented by a model which consists of an infinite number of parallel branches each one composed of a resistor and a capacitor in series. The time constant of each branch is longer with respect to

the previous one producing a general device with a complicate internal behavior.

Figure 3.1 presents the general model for the double-layer capacitance.

#### R1 C1< R2 C2 < ...< Rn-1 Cn-1 < Rn Cn

FIGURE 3.1 GENERAL DOUBLE-LAYER CAPACITANCE MODEL

This model as a representation of the double-layer has several factors favorable to the objective of this research:

- Use of simple electrical components to describe the doublelayer (Resistors and Capacitors).

- Representation of the double-layer as a terminal device.

Unfortunately, this representation of the DLC is not adequate for the characterization due to the following reasons:

- The presence of an infinite number or even a very large number of branches makes the model too complex for practical use and excessive effort is necessary to represent the model mathematically.

- The parameter calculation of so many branches based on

current and voltage measurements is difficult, arbitrary and inaccurate. In addition, physical data for the parameters values of the above equivalent model is not available.

Based on the previous considerations, the selected model will use the RC structure of the model in figure 3.1 but with a finite number of branches. The number of branches should be the smallest number possible keeping a good level of accuracy when the capacitor performance is simulated.

# 3.1.2 <u>Dependence of the Capacitance on the Potential</u> Difference

In chapter one, the study of the physics of the double-layer showed that the capacitance of the double-layer is not a constant but depends on the potential difference. This has to be included in the equivalent model in order to get accurate results.

The conclusion reached in Chapter two after the physical study of the double-layer is that the differential capacitance is linearly dependent on the potential. Therefore, the capacitance of the DLC model will include a fixed capacitor Co in parallel with a variable capacitor  $(C_1)$  linearly dependent on the voltage.

$$C_{diff}(V) = Co + C_1 * V$$

(3.1)

Based on the differential capacitance, an integral capacitance  $C_\kappa$  may be defined as the ratio between the total charge delivered to the capacitor to the voltage across the capacitor terminals.

$$C_K = \frac{Q_{tot}}{V_c} \quad (3.2)$$

Note that this definition uses the total charge referred to the zero voltage condition and it cannot be calculated from a different initial charge. The integral capacitance may be calculated from the differential capacitance in the following way:

$$C_{K} = \frac{1}{V} \int_{0}^{V} C_{diff} \ dV \quad (3.3)$$

In terms of Co and  $C_1$  the integral capacitance can be expressed as:

$$C_K = Co + \frac{C_1}{2} V$$

(3.4)

Although the integral capacitance appears to be the definition used in the specification of the capacitor value for the PANASONIC double-layer capacitor, the differential capacitance ( $C_{\rm diff}$ ) of the DLC will be the definition used in the modeling of the double-layer capacitors. That is because the differential capacitance defines the "instantaneous" capacitance of the DLC during any charge action independently of the previous charge cycles applied.

# 3.1.3 Double-Layer Leakage

Another characteristic of the double-layer mentioned in chapter one is the self discharge process present in the capacitor as a result of electrochemical reactions occurring across the interface when charge separation is present. This self-discharge or leakage means that part of the charge stored in the double-layer is lost internally and may not be recovered.

The leakage effect is represented in the equivalent model by a resistance in parallel with the resistance-capacitance branches already mentioned in the previous two sections. This resistance from now will be called  $R_{\rm cap}$ .

## 3.1.4 Inductive Effect in the Capacitor

Although specific details of the DLC construction are not available, the general construction process explained in chapter one mentioned that the aluminum foils are wound in spiral. Thus, it is possible to have some inductance inside the device which may affect the slew rate performance of the device. Therefore, a series inductance is included in the equivalent model.

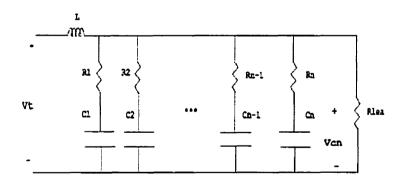

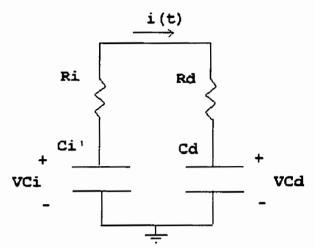

Based on the previous physical reasoning, the general structure of the equivalent model as shown in figure 3.2 is now proposed. Further properties of the proposed model are based on extensive experimentation and the conclusions of this experimentation will be presented in the next section.

FIGURE 3.2 PROPOSED MODEL STRUCTURE

#### 3.2 PRACTICAL CONSIDERATIONS

With the general structure of the equivalent model selected, the question about the number of branches needed to represent accurately the double-layer capacitor should be answered. For a practical model, the number of branches should be limited to the smallest number possible. The use of three branches to represent the DLC behavior is proposed.

Extensive experimental observations have influenced the selection of the number of branches of the equivalent model and in the model structure; these observations are commented on next:

- 1) Charging a fully discharged capacitor (all the equivalent internal capacitances with zero voltage) with controlled constant current up to the rated voltage and measuring the time required to this charge allow to calculate an integral capacitance of the device. The integral capacitance measured hardly changes if currents in the ratio of 1 to 10 are used for charging. This result indicates that the fastest branch may be assumed to have a very short time constant compared to further branches. The selection of a much bigger time constant for one branch in respect to the previous one makes the identification and calculation of the parameters simpler.

- 2) Although the internal time behavior of the double-layer capacitor may include processes with time constants of hours, the interest in power electronics is restricted to relatively short time or high power applications; so that the model selected should follow with greater accuracy the capacitor response thirty minutes after the start of a charge or discharge process.

- 3) The physical model composed by an infinite number of branches with different time constants gives a clear impression that reactions

with time constants between a few seconds and several hours occur inside the device. Observing the terminal voltage after a charge cycle confirms the previous impression and indicates that the charge is redistributed among the different branches. This distribution over the time of interest (30 minutes) should be represented in the model by the response of additional branches. One branch is insufficient to match the capacitor behavior in this wide time span; therefore, two branches with different time constant are proposed to represent the internal charge distribution. The second branch has a time constant in the order of few minutes and the third branch has a time constant in the order of tens of minutes.

4) The selection of the three voltage dependant branches increases the complexity of the parameter identification. In addition, extensive measurements of the internal charge distribution process at different voltages indicate that the assumption of only one branch voltage dependant does not introduces an appreciable error if the capacitor voltage is kept over 1.5 volts. As in the power applications the DLC's will not be discharged to very low voltages the dependence of the capacitance with the voltage is assigned to the first branch only.

Based on the previous physical and experimental observations, the proposed model consists of three branches in parallel each one composed of the connection in series of a resistor and a capacitor. In addition, the model includes a leakage resistor in parallel with the three branches and a series inductor in the input. The capacitance of the first branch is divided in a fixed part and a voltage dependant part.

The first branch has the smallest time constant. The time constant will be given by the capacitor response to a fast charge process, in other words a charge action with high current. Using the rated values given by the manufacturer, the time constant expected for this branch is in the order of few seconds. From this point the first branch and its components (R and C) will be named "immediate" and denoted with the letter 'i'. The name "immediate" is given because this branch will respond immediately to the charge action.

The second branch has a medium time constant. The time constant selected for this branch is between one and five minutes. That means that the time constant for the second branch is at least ten times larger than the time constant for the immediate branch. From this point the second branch will be named "delayed" branch and its elements denoted with the letter 'd'.

The third branch will be named "long term" branch and denoted with the letter 'l'. This branch has a time constant of more than 10 minutes which makes it much slower than the delayed branch.

Figure 3.3 presents the detailed proposed model of the carbon-based double-layer capacitor.

# CHAPTER 4

# IDENTIFICATION OF EQUIVALENT MODEL

## PARAMETERS

This chapter presents the principles on which the identification of the equivalent model parameters is based. With the principles clearly defined, the detailed parameter identification procedure is explained.

The measurement procedure is based on a test facility that consists of a controlled current source and a voltage measurement system. The test facility and the techniques used in the measurement of the parameters are presented in chapter five. However, it is convenient to indicate now that the current source has a very short maximum rise time compared with the typical charge times for the double-layer capacitors. Furthermore, the current source can be turned on or off at precise intervals in time, by mean of the controller board timing, or by the instant at which the double-layer capacitor terminals reach some pre-fixed value.

The identification of nine model parameters using only two measurable variables (terminal voltage and input current) has an infinite number of possible solutions, and therefore is in general arbitrary. However, based on the justified assumption of three branches with distinct time constants the principles of the parameter identification process are now proposed:

- The double-layer capacitor to be modeled should be in a fully discharged state; that is, all the equivalent internal capacitances have zero voltage. To achieve this state of full

discharge, a "normalization" process was developed and is presented in chapter five.

- The capacitances to be assigned to the equivalent model are given by the differential definition presented in chapter three. This definition gives the possibility to know the instantaneous capacitance of the device at any moment of any test sequence.

- The identification of the immediate branch equivalent model parameters is based on the charge of the capacitor up to the rated voltage with high current and the continuous measurement of the terminal voltage. The use of high current reduces the effect of the other two branches in the measurements.

- When the terminal voltage reaches the rated value, the current source is turned off and an internal charge distribution process among the different branches begins. Continuous voltage measurement during that charge distribution is used to identify the delayed and long term equivalent circuit parameters.

- The leakage resistance is identified using a capacitor whose voltage is equal across all the internal equivalent capacitances. In other words, no charge distribution process is occurring inside the device. Under this condition, the change in terminal voltage is only a result of the equivalent model leakage resistance.

- The DLC input inductance is calculated using the slope of the current transient at the instant that a fully charged capacitor is suddenly short-circuited.

In the above paragraphs only the general principles used in the identification were presented. A detailed description of the identification of each parameter is given in the following pages.

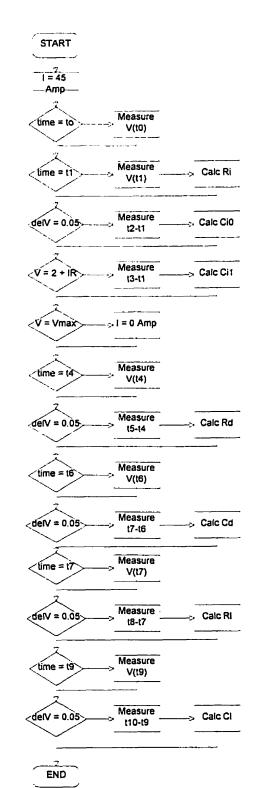

#### 4.1 IDENTIFICATION OF IMMEDIATE BRANCH PARAMETERS

The immediate branch parameters are measured by applying a fast charge to the capacitor. The higher the value of current the lower the charge introduced into the delayed and long term branches; therefore, the current should be as high as possible; however, the devices available for the experimental facility are limited to fifty amperes. For these reasons, the current was selected as 5% of the rated short circuit current of the double-layer capacitor or 45 Amp. The rated short circuit current is defined as the ratio between the rated voltage and the rated internal resistance of the capacitor.

The resistance of the immediate branch is determined from the voltage drop produced at the terminals when the current is applied to the capacitor. The DLC terminal voltage is measured at the time t0 before the application of the current. At some time t1 after the turn on of the current source, the terminal voltage is measured again. The time t1 is equal to the maximum rise time of the current source, which is also greater than the di/dt of the device; at this time, the current has reached the desired value but the energy stored in the equivalent capacitance is very low. Therefore, the measured voltage step ( $\Delta V$ ) is due to the equivalent resistance of the immediate branch and the value of the resistance is calculated using equation 4.1. In equation 4.1, I is the controlled current applied,  $R_{\rm i}$  is the immediate branch resistance and  $\Delta V$  is the difference between the voltage measured at t1 and the voltage measured at t0:

$$R_i = \frac{\Delta V}{I} \quad (4.1)$$

The voltage measured at the time t1 is used as a starting point

for the capacitance calculation. The fixed part of the immediate capacitance  $(C_{10})$  is measured based on the defined differential capacitance at the start of the charge action according to the following equation:

$$C_{i0} = \frac{dQ}{dV} \mid_{Vci=0} = \frac{I \ dt}{dV} \mid_{Vci=0} = \frac{I}{dV/dt} \mid_{Vci=0} (4.2)$$

As the current magnitude is constant, the voltage drop across the immediate resistance is constant; therefore, the dv/dt of the terminal voltage curve as a function of the time is equal to the dv/dt of the voltage curve at the immediate branch capacitance. The slope of the terminal voltage versus time curve is measured at the first instants after the current has been established. This value is used in conjunction with the known value of the current and  $C_{10}$  is determined.

The slope of the curve (dV/dt) is measured in the following form: The terminal voltage is measured continuously. When the terminal voltage has increased a value  $\Delta V$  with respect to the voltage measured at t1, the time t2 is measured. The time change  $\Delta t$  corresponding to this  $\Delta V$  is equal to t2-t1. In this form the dv/dt of the terminal voltage curve in time is measured and its value is used in equation 4.2. The size of the voltage step  $\Delta V$  is selected to provide good resolution in the calculation.

The voltage dependant immediate capacitance  $(C_{ii})$  may be calculated using the definition of differential capacitance or integral capacitance. As the integral capacitance definition does not need to measure the slope of the terminal voltage curve, this method is more accurate and will be implemented. The time t3 at which the capacitor reaches the rated value is measured. At this time the

equivalent integral capacitance of the immediate branch is given by the following relation:

$$C_K = \frac{Q_{tot}}{\Delta V} = \frac{I(t3-t1)}{V_{(t3)}-V_{(t2)}}$$

(4.3)

where t1 is the time at the start of the charge already mentioned in the calculations of Ri and  $C_{\text{io}}$ , and  $V_{\text{(in)}}$  represents the terminal voltage at the time tn.

With the value of the integral capacitance calculated, equation 3.4 is used to relate the integral capacitance with the differential capacitance. Using equation 3.4 the value of  $C_{ii}$  is calculated:

$$C_{i1} = \frac{2(C_K - C_{i0})}{V_{i1} - V_{i1}} \qquad (4.4)$$

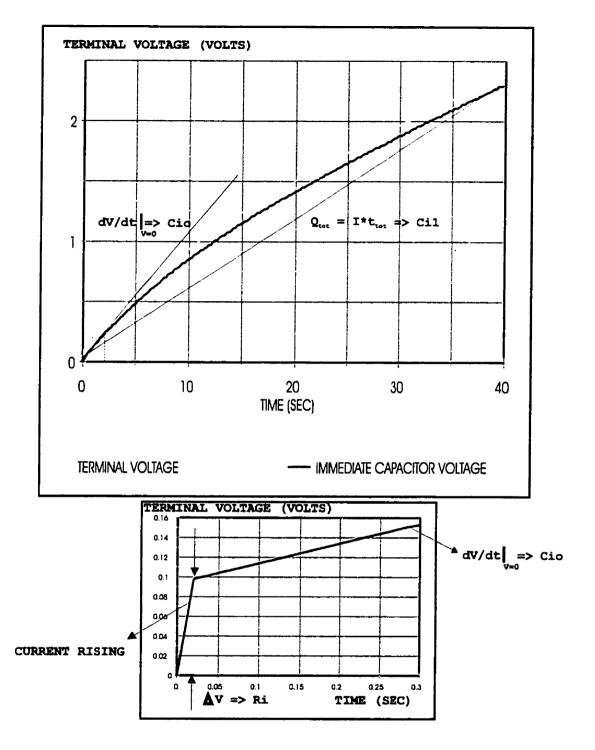

Figure 4.1 presents a typical curve of voltage vs time for a simple charge action with constant current. This figure summarizes the calculation of the immediate branch parameters.

## 4.2 IDENTIFICATION OF DELAYED BRANCH PARAMETERS

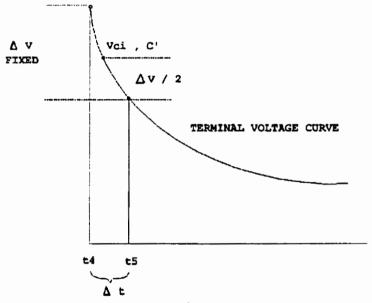

When the terminal voltage reaches the rated value, the current source is turned off and the redistribution of charge between the immediate and the delayed branch is the predominant action inside the capacitor. At this point the calculation of the delayed branch parameters begins.

The assumption made for the calculation is that the voltage at the delayed branch is zero volts when the current is removed; in other words, the time constant of the delayed branch is much higher than the

INITIAL INSTANTS SCALE ZOOM

FIGURE 4.1 IDENTIFICATION OF IMMEDIATE BRANCH PARAMETERS

charge time of the immediate branch.

The equivalent circuit in figure 4.2 represents the capacitor during that redistribution process

FIGURE 4.2 CHARGE REDISTRIBUTION EQUIVALENT CIRCUIT

In this figure, Ci' is the value of the immediate branch capacitance at the corresponding voltage, and Ri is the immediate branch resistance. The initial current flowing through the circuit when the current falls to zero and Vcd is zero (t4), is given by:

$$i_{(c4)} = \frac{VCi}{Ri + Rd} \qquad (4.5)$$

In addition, the following relation between the capacitor current and its voltage is valid at this instant:

$$i_{(td)} = C' \frac{dVCi}{dt} \quad (4.6)$$

The time t4, accordingly to the current source characteristics, is equal to the time during which the current source was turned off plus the maximum fall time of the current. The terminal voltage at t4

is measured, and then the voltage is continuously measured until it has dropped a fixed value  $\Delta V$ . This point determines the instant t5. With these two points of time and voltage the value of  $dV/dt = \Delta V/\Delta t$  is determined.

Assuming Rd >> Ri, Vci is approximately equal to the terminal voltage. Therefore, measuring the terminal voltage and dVci/dt, Rd can be calculated through the following equation deduced from 4.5 and 4.6:

$$Rd = \frac{Vci}{C' * dVci/dt} \qquad (4.7)$$

The value of Vci and C' used in the calculation of Rd is the terminal voltage and the immediate branch capacitance at the medium point of the dV/dt calculation. (See figure 4.3)

Using the same equivalent circuit shown in figure 4.2 at some instant (t6) where Vcd is different from zero, the value of Cd can be calculated. As the delayed branch was selected to represent the capacitor behavior up to five minutes after the charge action, the calculation of the delayed branch capacitance is done three minutes after the end of the charge action (t6 = 180 sec + t3).

At this instant the current flowing from the immediate to the delayed branch is given by:

$$i(t6) = C' \frac{dVci}{dt} \quad (4.8)$$

Furthermore, the total charge equilibrium equation that represents the interchange of charge between Ci and Cd is given by:

$$\Delta Q = Vci(t4) * C_K(t4) - Vci(t6) * C_K(t6) = Vd(t6) * Cd \qquad (4.9)$$

The integral capacitance value, needed in the previous equation, may be easily calculated from the differential capacitance as

explained in chapter three. The value of Vcd at t=t6 is calculated from figure 4.2 as:

$$Vci(t6) = i(Rd+Ri) + Vcd(t6)$$

(4.10)

Using equations 4.8 to 4.10 the value of Cd is calculated:

$$Cd = \frac{\Delta Q}{Vci(t6) - C' * \frac{dVci}{dt}|_{t6} * (Ri + Rd)}$$

(4.11)

FIGURE 4.3 dV/dt CALCULATION

A second proposal for the delayed branch capacitance calculation based only in the charge equilibrium is now presented. In this second possible identification, the time constant for the delayed branch is previously assumed. After three time constants of the delayed branch, the voltages across the immediate and delayed branches are practically equal, and the equation 4.9 for the charge equilibrium is applied with Vcd = Vci. This procedure has the advantage to save the calculation of dv/dt which is in general inaccurate. On the other hand, this

second proposal needs more time for the computation of the parameter Cd because the calculation is done when the voltages in both branches are considered equal.

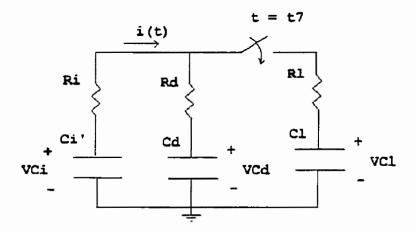

#### 4.3 IDENTIFICATION OF LONG TERM BRANCH PARAMETERS

The long term branch parameters' calculation follows similar steps to those for the delayed branch. In this case, the delayed capacitance is assumed with equal voltage to the immediate branch and the long term capacitance is assumed fully discharged. To make these assumptions valid, the start time for the calculation of the long term branch should be at least three times the delayed branch time constant. This criterion assures that the delayed voltage is within 95% of the immediate branch voltage.

The equivalent circuit for the charge transfer to the long term branch is shown in figure 4.4.

FIGURE 4.4 EQUIVALENT CIRCUIT FOR CHARGE DISTRIBUTION TO CL

The switch S1 is closed at the instant t7 in which the voltages at the immediate and delayed branches are almost equal. In this instant most of the charge transference occurs between the immediate branch and the long term branch because the value of Ri is much lower than Rd. Therefore, Rl is calculated using equation 4.7 three delayed branch time constants after the instant at which the current was turned off. The calculation of the dV/dt used in equation 4.7 is done in the same form explained for the delayed branch.

The capacitance Cl is calculated using the same procedure explained for the delayed branch but now the capacitance C' in equations 4.8 to 4.11 is equal to the capacitance of the immediate branch in parallel with the capacitance of the delayed branch. The instant of calculation for Cl is thirty minutes after the termination of the current source.

As was done for the delayed branch, the dv/dt of the terminal voltage versus time curve is measured and the equations mentioned for the case of the delayed branch are applied to the results.

In the calculation of the long term branch capacitance it is also possible to use a second identification procedure. In this method, the time constant for the long term branch is previously assumed and the equation for the charge equilibrium is applied after three times the selected time constant. This method saves the calculation of dV/dt that for this case is very difficult because the transient is very slow. However, the time needed to calculate the parameter is longer.

#### 4.4 IDENTIFICATION OF LEAKAGE RESISTANCE

The leakage resistance is identified by measuring the decrease

in the capacitor terminal voltage over a period of 24 hours. The capacitor used for the leakage resistance determination was previously normalized to 2 volts. After the normalization, it is expected that all the internal capacitances in the equivalent model are charged to the same voltage and the voltage decrease as function of time can be attributed to the equivalent leakage resistance. The duration of the test (24 hours) is much greater than the time constants of the three equivalent model branches; therefore, the capacitor is assumed as the parallel equivalent of the three branches and the resultant circuit is an RC circuit. The analysis of a simple RC circuit gives:

$$Vc(t) = Vo e^{-t/R_{los}Ct}$$

(4.12)

where Ct is the parallel equivalent capacitance, Vc is the double-layer capacitor terminal voltage and Vo is the initial voltage for the discharge, or in other words the terminal voltage after the normalization. In the previous equation the value of the leakage resistance is assumed to be much larger than the resistance of the three branches. Using the series approximation for the previous equation with t << Rlea\*Ct gives:

$$VC(t) = Vo(1-t/RpC_{leg}) \qquad (4.13)$$

Defining  $\Delta$ Vc as the decrease in terminal voltage after the 24 hours test, the following relation is produced

$$R_{lea} = \frac{Vo \Delta t}{\Delta Vc Ct} \qquad (4.14)$$

In the previous relation Vo is two volts,  $\Delta$ Vc is measured after 24 hours, Ct is known from the previous identification of the internal capacitances and  $\Delta$ t is equal to 24 hours.

#### 4.5 IDENTIFICATION OF DOUBLE-LAYER CAPACITOR

#### INDUCTANCE

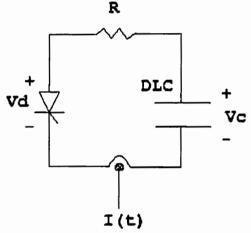

The measurement of the capacitor inductance will be done with a DLC precharged to the rated voltage. The precharged DLC is then connected as is shown in figure 4.5. In this figure R is the total loop resistance and Vd is the on state voltage drop of a PN junction. Then, a trigger pulse of 10 msec is applied to the switch and the current waveform in the circuit is measured.

FIGURE 4.5 IDENTIFICATION OF CAPACITOR INDUCTANCE

The voltage Vc may be assumed as constant during the transient because of the long time constant involved in its variation, the final current after the transient results in:

$$I(\infty) = \frac{Vc - Vd}{R} \qquad (4.15)$$

The analysis of the circuit gives:

The solution of the previous differential equation is:

$$L\frac{di}{dt} + iR = Vc - Vd \quad (4.16)$$

$$i(t) = I(\infty) (1-e^{-t/\tau})$$

(4.17)

where  $\tau$ = L/R. If the slope of the curve of i vs t is measured, the final value of I (I( $\infty$ )) is calculated, and the current for some time t' during the transient is known, then L could be calculated.

This measured inductance includes all the inductance in the loop; therefore, the inductance of the other components should be estimated and then subtracted from the total inductance calculated. The result of the identification is only an approximation.

# CHAPTER 5

# MEASUREMENT OF EQUIVALENT MODEL

## **PARAMETERS**

In this chapter, the experimental techniques used in the measurements and calculations are presented; these techniques assure that all the factors that may affect the accuracy of the measurements are controlled. In addition, results of the parameters measurements are presented and a brief discussion of these results is given. First, it is important to introduce the test facilities used in the double-layer capacitor test and in the parameters measurements.

#### 5.1 TEST AND MEASUREMENT FACILITIES

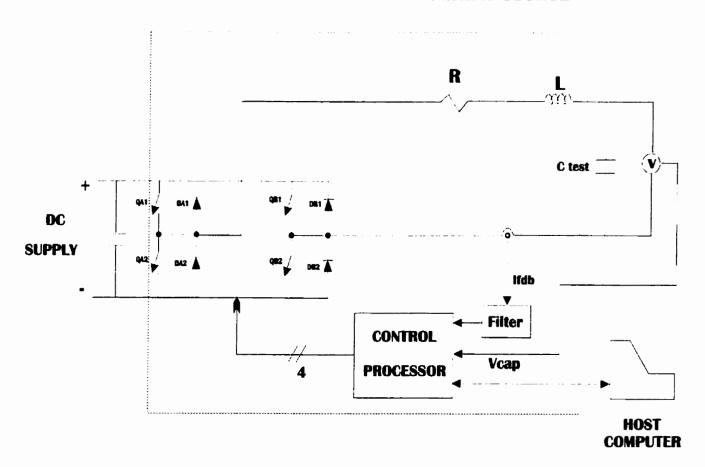

Chapter 4 presented the procedure for the identification of the equivalent model parameters. The identification of the immediate branch parameters is based on the application of a controlled current source. The main function of the experimental setup is the generation of the controlled current source. Figure 5.1 shows the experimental setup used in the DLC test and the following pages include a brief explanation of the main functions of each element in the experimental setup.

The host computer is an IBM compatible system running under WINDOWS that is used to facilitate the user interface during the tests. The main functions of the computer are: programming of the controller, adjusting of the settings used in the different tests, and data processing. The computer is connected through the serial port to the control processor. Continuous interchange of data between the

# **CURRENT SOURCE**

FIGURE 5.1 DLC TEST FACILITY

computer and the control processor is possible.

The control processor, a general purpose controller board for real time control, is the platform used for the control of the DC/DC converter, and for the different tests of the DLC's. The board is based on the microcontroller MC68332, which uses the 68020 CPU. Beside having the typical microcontroller features, the M68332 includes a time processing unit, which has many independently timed pulse channels. Those channels are used to control the state of the DC/DC converter switches.

The use of the microcontroller mounted in a business computer card makes it possible to use the system connected to a terminal or host computer. Therefore, the processor is programmed in C language on the host computer, compiled, and then the resultant file is transferred to the control board. Eight analog inputs and eight analog outputs are available for the signal feedback and monitoring as well as a 16-bit parallel port.