# Clemson University **TigerPrints**

All Theses Theses

5-2017

# Characterization of Polymer Hermetic Sealed Tantalum Capacitors Using Thin-film Devices

Shiva Kumar Chinnam Clemson University, shivakumar.chinnam@gmail.com

Follow this and additional works at: https://tigerprints.clemson.edu/all theses

# Recommended Citation

Chinnam, Shiva Kumar, "Characterization of Polymer Hermetic Sealed Tantalum Capacitors Using Thin-film Devices" (2017). All Theses. 2610.

https://tigerprints.clemson.edu/all\_theses/2610

This Thesis is brought to you for free and open access by the Theses at TigerPrints. It has been accepted for inclusion in All Theses by an authorized administrator of TigerPrints. For more information, please contact <a href="kokeefe@clemson.edu">kokeefe@clemson.edu</a>.

# CHARACTERIZATION OF POLYMER HERMETIC SEALED TANTALUM CAPACITORS USING THIN-FILM DEVICES

A Thesis

Presented to

the Graduate School of

Clemson University

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

Electrical Engineering

by

Shiva Kumar Chinnam

May 2017

Accepted by:

Dr. William R. Harrell, Committee Chair

Dr. Yuri Freeman

Dr. Goutam Koley

### ABSTRACT

Polymer Hermetic Sealed (PHS) capacitors are advanced polymer capacitors with a hermetic seal enclosing the materials inside a metal enclosure. Their primary features include leakage current stability, high volumetric efficiency, and low weight compared to both wet and solid-state polymer tantalum capacitors. However, Life Tests performed on these capacitors have revealed a failure to withstand their rated voltage in a working temperature range over the long-term. There are also other interesting properties which have been observed such as Breakdown voltage (BDV) exceeding the Formation Voltage ( $V_f$ ), anomalous transient currents, and a larger than expected capacitance dependence on temperature, C(T).

A primary goal in this research is to understand whether the observed characteristics of PHS capacitors are a result of their complex structure or due more to the nature of interactions between the organic and inorganic material layers present. C(T) and BDV measurements were performed on thin-film MIS capacitors representing the material layers of PHS capacitors. Measurements were performed in the voltage range (0V-100V), a temperature range (-55°C to 125°C), with varying frequency (20-10kHz), under both humid and dry conditions. Furthermore, one sample went through a curing process referred to as "Heat Treatment", which is thought to improve device stability. Results from these measurements show that thin-film devices can be reasonable representatives of discrete PHS capacitors, and the properties observed in PHS capacitors are significantly dependent on the material layers in the capacitors. Thus, the thin-film MIS capacitor is shown to be a useful test structures for investigating physical phenomena observed in the more complex polymer Ta capacitor structure.

# DEDICATION

To my brother, Srinivas Chinnam, for constantly inspiring me be to a better person and encouraging me all along.

### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. William R. Harrell for his guidance while conducting this research and writing this thesis. I would also like to thank Dr. Yuri Freeman for his assistance and KEMET Electronics Corporation for supporting this project financially. I would also like express my gratitude to Dr. Goutam Koley for reviewing my thesis and serving on my committee. I am grateful to Dr. Ruslan Burtovyy and Mr. Daniel B. Cutshall for their assistance in equipment setup for the measurements. Thanks also goes to Ms. Sudheera Bommakanti and Mr. Deep Shah for proof reading this thesis. My special thanks to Ms. Susmitha Siddula for being the strong motivator to finish this work.

A part of this thesis was submitted for a journal publication: William Harrell, Yuri Freeman, Igor Luzinov, Ruslan Burtovyy, Philip Lessner, Shiva Chinnam, and Javaid Qazi "Capacitance Stability in Polymer Tantalum Capacitors with PEDOT Counter Electrodes," ECS Journal of Solid State Science and Technology.

# TABLE OF CONTENTS

|                                                                                                                                                                                                                            | Page                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ΓΙΤLE PAGE                                                                                                                                                                                                                 | i                    |

| ABSTRACT                                                                                                                                                                                                                   | ii                   |

| DEDICATION                                                                                                                                                                                                                 | iii                  |

| ACKNOWLEDGMENTS                                                                                                                                                                                                            | iv                   |

| LIST OF TABLES                                                                                                                                                                                                             | vii                  |

| LIST OF FIGURES                                                                                                                                                                                                            | viii                 |

| CHAPTER                                                                                                                                                                                                                    |                      |

| I. INTRODUCTION                                                                                                                                                                                                            | 1                    |

| 1.1 PHS Tantalum Capacitors                                                                                                                                                                                                |                      |

| II. REVIEW OF CAPACITOR THEORY AND EVOLUTION OF TANTALUM CAPACITORS                                                                                                                                                        | 5                    |

| Capacitor Theory  Electrolytic Capacitors  Tantalum Capacitors  Construction  Failure Mechanism of Ta-Ta2O3¬-MnO2¬ Capacitors  Conclusion                                                                                  | 7<br>9<br>10<br>12   |

| III. POLYMER TANTALUM CAPACITORS                                                                                                                                                                                           | 16                   |

| Intrinsically Conducting Polymers  Polymer As Substitute For MnO <sub>2</sub> Insitu and Prepolymerized PEDOT Ta Capacitors.  MIS Model for Polymer Ta Capacitors  Polymer Hermetic Sealed (PHS) Ta Capacitors  Conclusion | 18<br>19<br>21<br>22 |

| IV. CHARACTERIZATION OF PHS TANTALUM CAPACITORS                                                                                                                                                                            | 25                   |

| Background                                                                                                                                                                                                                 |                      |

# Table of Contents (Continued)

| V.  | UNDERSTANDING PHS CAPACITORS USING FLAT SAMPLES | 4 |

|-----|-------------------------------------------------|---|

|     | Motivation for Thin-film Samples                | 4 |

|     | Fabrication of thin-film devices                |   |

|     | Experimental Procedure                          | 4 |

|     | Results                                         |   |

|     | Conclusion                                      | 6 |

| VI. | DISCUSSION AND CONCLUSIONS                      |   |

|     | Summary                                         | 6 |

|     | Conclusions                                     | 7 |

# LIST OF TABLES

| Table |                                                               | Page |

|-------|---------------------------------------------------------------|------|

| 5.1   | Capacitors with their corresponding BDV. FS2 is heat treated. |      |

|       | Measured at humid condition.                                  | 66   |

# LIST OF FIGURES

| Figure | Page                                                                               |

|--------|------------------------------------------------------------------------------------|

| 1.1    | PHS Tantalum Capacitors, an advanced solid Ta capacitor used in space applications |

| 2.1    | An illustration of a parallel plate capacitor6                                     |

| 2.2    | Parasitic elements of a capacitor                                                  |

| 2.3    | Electrolytic Capacitor                                                             |

| 2.4    | Structure of solid Ta capacitor with MnO <sub>2</sub> cathode11                    |

| 2.5    | Finished surface-mount Ta capacitor                                                |

| 2.6    | MnO <sub>2</sub> as contributing force to cracks                                   |

| 2.7    | Self-healing property of MnO <sub>2</sub>                                          |

| 2.8    | Theoretical ignition failure sequence                                              |

| 3.1    | Sigma and Pi bonds between adjacent carbon atoms                                   |

| 3.2    | Delocalized electron cloud. Charge transport in the                                |

|        | polymer chain takes placethrough hopping in the electron cloud                     |

| 3.3    | Self-Healing property of Ta capacitor with polymer cathode                         |

| 3.4    | Maximum working voltage of Ta capacitors                                           |

| 3.5    | I-V characteristics of polymer Ta capacitors with in                               |

|        | situ and prepolymerized PEDOT cathodes at $T = 300 \text{ K}$ .                    |

|        | Anodic oxide film thickness was 200 nm                                             |

| 3.6    | Simplified Ta capacitor structure for analysis                                     |

| 3.7    | Breakdown test for PHS Ta Capacitor with $V_f = 28V$                               |

| Figure | Page                                                                 |

|--------|----------------------------------------------------------------------|

| 4.1    | DC Leakage measured during Life Test. DCL after 500                  |

|        | hours in 80% of capacitors is less than 10µA, while                  |

|        | in remaining 20 % it reached 100mA                                   |

| 4.2    | ESR of all capacitors remained less than 10hm                        |

|        | after 500hrs even when 20% of these capacitors                       |

|        | showed high DCL current                                              |

| 4.3    | I-time measurement performed for one-hour to observe current decay30 |

| 4.4    | Automated system setup to measure voltage across                     |

|        | the resistors, which was the used to measure DC                      |

|        | leakage current through the capacitors                               |

| 4.5    | A vacuum chamber is created with this setup using                    |

|        | glass closing and removing the air using vacuum pump                 |

| 4.6    | Flexible heater is place below the test board soldered               |

|        | with capacitors. During the measurements, another                    |

|        | flex heater is placed over the test board                            |

| 4.7    | I-t of Good Sample-1 @Room Temperature for a range of voltages34     |

| 4.8    | I-V of all three Good Samples derived from I-time                    |

|        | curves shown in Figure 4.7                                           |

| 4.9    | I-time of Good Sample-1 @85°C at different voltages                  |

| 4.10   | I-V of all Good Samples at 85°C. Current for                         |

|        | capacitor-3 reached milliamp range and not shown here36              |

| Figure | Page                                                                      |

|--------|---------------------------------------------------------------------------|

| 4.11   | I-t of Good Sample-1 @125C. Current                                       |

|        | magnitude is irregular, and less than a micro-amp                         |

| 4.12   | I-time of Good Capacitor-1 in Liquid Nitrogen.                            |

|        | Current is in nanoamp range and irregular                                 |

| 4.13   | I-t of Good Sample-3 at 125°C. Current                                    |

|        | pattern is irregular and in a milliamp range                              |

| 4.14   | I-t of Good Sample-3 in Liquid Nitrogen.                                  |

|        | Current pattern is irregular and in a milliamp range                      |

| 4.15   | I-time of Bad Sample-1 at Room Temperature.                               |

|        | Current all voltages is in milliamp range                                 |

| 4.16   | I-V of Bad Sample-1 at all temperatures. There                            |

|        | is a linear correlation between current and voltage40                     |

| 4.17   | I-V at all temperatures, Virgin Sample – 341                              |

| 4.18   | I-time of Good Sample-1 of set-4 at room temperature.                     |

|        | Current at 100V dropped to zero and remained zero amps                    |

| 4.19   | I-time of Good Sample-2 of Set-4 at Room                                  |

|        | Temperature. Dielectric breakdown occurred at                             |

|        | 100V conducting milliamps of current                                      |

| 5.1    | (a) Layers in the thin film device; (b)Dicing pattern for the Si wafers47 |

| 5.2    | Flat Sample -1 showing 4 capacitors and their capacitance                 |

| 5.3    | Flat Sample -1 showing 4 capacitors and their capacitance                 |

| Figure | Pa                                                                     | age |

|--------|------------------------------------------------------------------------|-----|

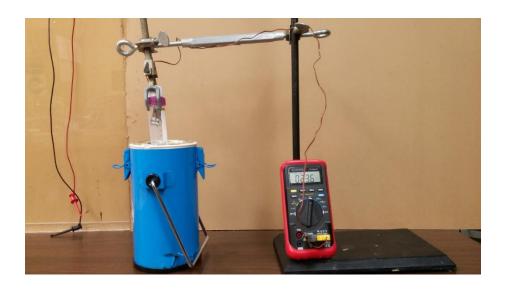

| 5.4    | Test tube used for high and low temperature                            |     |

|        | measurements. White rubber stopper through                             |     |

|        | the cap is used to maintain the temperature inside the tube            | 51  |

| 5.5    | High temperature measurement setup. The oven                           |     |

|        | is on the left, and the tube with the flat sample is                   |     |

|        | inserted into the oven                                                 | 51  |

| 5.6    | Low temperature measurement setup.                                     |     |

|        | Chemical mixture is prepared in the blue flask on the left             | 53  |

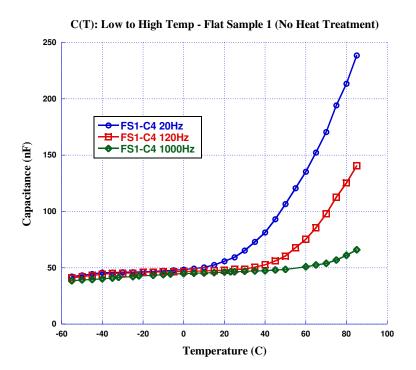

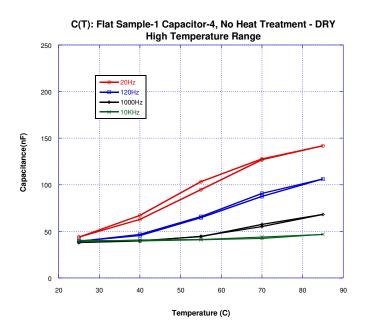

| 5.7    | C(T) of capacitor-4 in Flat Sample-1.                                  | 54  |

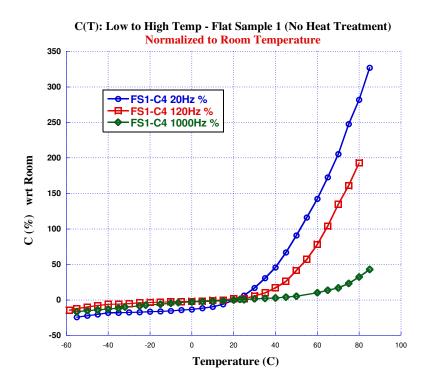

| 5.8    | %C vs Temperature for capacitor-4 in Flat Sample-1                     | 55  |

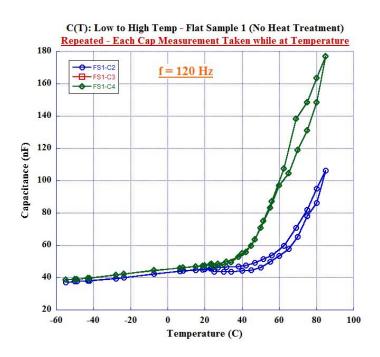

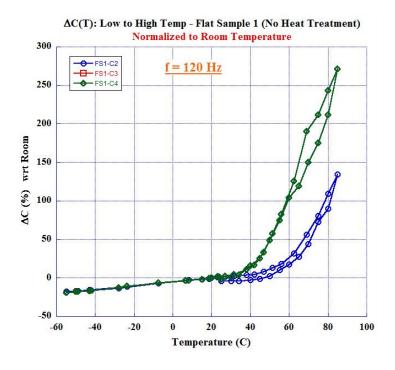

| 5.9    | C(T) of –Flat Sample 1, repeated measurements                          | 57  |

| 5.10   | $\Delta C(T)$ : Low to High Temp, Flat Sample 1, repeated measurements | 57  |

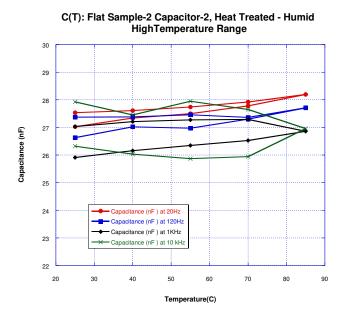

| 5.11   | C(T) of FS2-C2 at High Temperature. Change in                          |     |

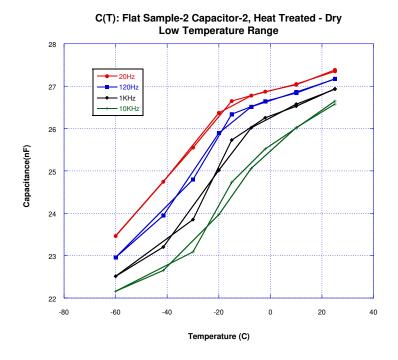

|        | capacitance is less than 20%                                           | 59  |

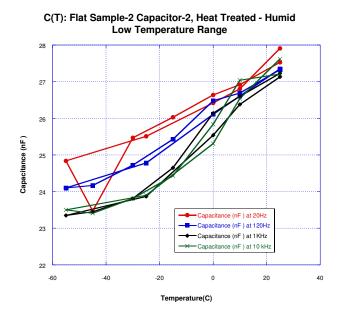

| 5.12   | C(T) of FS2-C2 at Low Temperature. Change in                           |     |

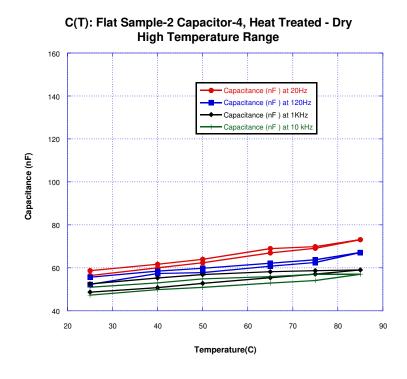

|        | capacitance is less than 20%                                           | 59  |

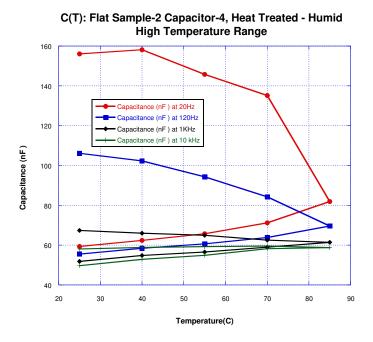

| 5.13   | C(T) of FS2-C4 at high temperature. Capacitance at                     |     |

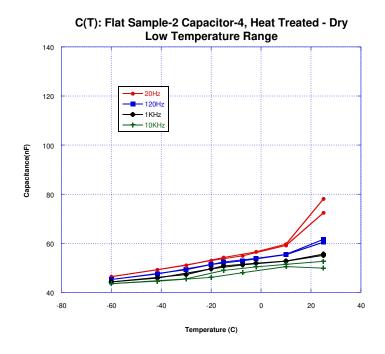

|        | 20Hz is very high                                                      | 60  |

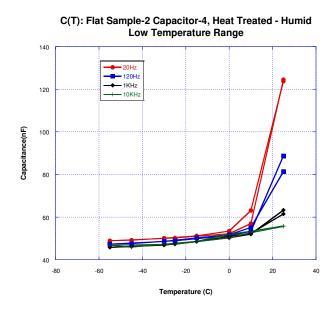

| 5.14   | C(T) of FS2-C4 in low temperature range.                               |     |

|        | The unusually high capacitance at 20Hz                                 |     |

|        | disappeared after drying the sample                                    | 60  |

| Figure | Page                                                      |

|--------|-----------------------------------------------------------|

| 5.15   | C(T) of FS1-C4 in the high temperature range with drying  |

| 5.16   | C(T) of FS2-C2 in the high temperature range after drying |

| 5.17   | C(T) of FS2-C4 in high temperature range after drying     |

| 5.18   | C(T) of FS2-C2 in low temperature range after drying      |

| 5.19   | C(T) of FS2-C4 in low temperature range after drying      |

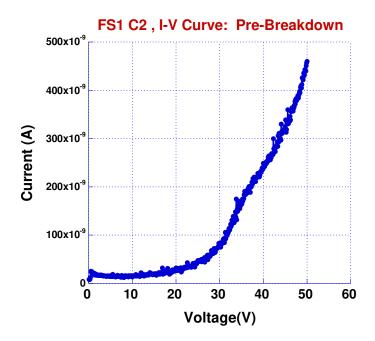

| 5.20   | Pre-breakdown current in FS1-C2, no heat treatment, Humid |

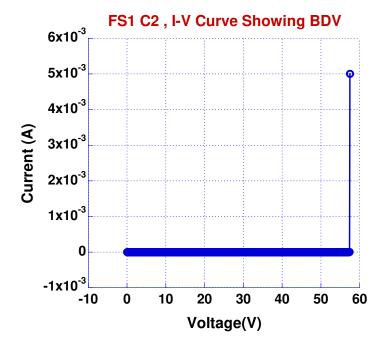

| 5.21   | I-V plot showing the breakdown at 57.5V in FS1-C2,        |

|        | no heat treatment, Humid                                  |

### CHAPTER 1

#### INTRODUCTION

### **PHS Tantalum Capacitors**

Polymer Hermetic Sealed (PHS) Tantalum(Ta) capacitors are advanced solid Tantalum capacitors with a Ta anode, tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) dielectric, and a conducting polymer as the cathode. These capacitors are hermetically sealed to maintain the humidity inside the metal enclosure. A picture of a PHS Ta capacitor is shown in the Figure 1.1. PHS capacitors have superior properties compared to traditional Ta capacitors with liquid electrolytic cathodes, referred to as wet Ta capacitors. PHS capacitors possess a high volumetric efficiency of capacitance, weigh less, and exhibit an improved capacitance retention at low temperature (below 0°C) and high frequency (10Khz), compared to wet Ta capacitors [1]. Moisture retention in the PHS capacitors, achieved by forming hermetic seal, has contributed to stabilization of leakage current in polymer Ta capacitors. Owing to these advantages, PHS Ta capacitors are primarily used in space applications such as satellites and missiles.

Figure 1.1: Commercial grade PHS Tantalum Capacitor by KEMET electronics corporation [35].

Long term testing has revealed that these capacitors failed to withstand their rated voltage and working temperature range. Also, recently KEMET discovered a new property in a variant of PHS capacitor which was never observed before, where the Breakdown Voltage(BDV) of these capacitors exceeded their Formation voltage( $V_f$ ). Phenomenon of BDV >  $V_f$  is possible and previously observed in Wet Ta capacitors and Polymer Ta capacitors due to extension of dielectric[28]. Though, in such cases the capacitance loss is observed due to an increase in dielectric thickness and more capacitors are used in the applications to compensate the capacitance loss. This combination of BDV> $V_f$  without capacitance loss and open failure mode is critical for the applications where there is a limitation on space and number of capacitors and where short circuit current can prove to be costly. But there is a lack of understanding of this high breakdown voltage phenomenon. To fully exploit this phenomenon and to improve long term stability it is necessary to investigate the properties of Polymer Ta capacitors through their characterization.

These PHS Ta capacitors represent a complex structure made from special flawless technology anodes [2], coarse tantalum powder, thin dielectrics, and pre-polymerized PEDOT cathodes sealed with internal humidity. Here the primary question is to understand whether the characteristics of PHS capacitors are a result of the special manufacturing process and the resulting complex structure involved or if it is primarily due to the nature of interactions between the organic and inorganic material layers present. If it is due to the nature of interactions between the materials involved, then the capacitor properties can best understood by preparing thin-film representations of these PHS capacitors with varying specifications and then find ways to improve PHS Ta capacitors. Otherwise, it can be concluded that the complex structure and the technology used to fabricate these capacitors is the primary contributor to the observed properties. In either case, fabricating thin-film devices similar to PHS capacitors and comparing the properties with properties discrete PHS capacitors will be helpful to understand and ultimately improve the performance and applications of PHS Ta capacitors.

# **Summary of Chapters**

In Chapter 2, we review basic capacitor theory and review the evolution of Ta capacitors from wet Ta capacitors to solid Ta capacitors.

In Chapter 3, intrinsically conducting polymers will be introduced and the history of how they came to replace MnO<sub>2</sub> in solid Ta capacitors will be reviewed. We will also review the advancements made in polymer Ta capacitors in the form of the transition from in-situ to prepolymerized Ta capacitors. PHS Ta capacitors will be introduced towards the end of this chapter, concluding with discussion of the motivation for studying these capacitors.

In Chapter 4, the measurement procedures performed on PHS capacitors will be presented thoroughly along with some background on the particular capacitors used for these measurements. The detailed measurement procedures, reasoning behind this procedure, and the detailed setup used for these measurements will be presented. The experimental results obtained will be discussed and analyzed in order to lay out the next steps for understanding the results. Chapter 4 is concluded with a discussion on the motivation to perform measurements on thin-film devices replicating the structure of polymer Ta capacitors.

In Chapter 5, experimental investigations on thin-film devices will be presented starting with the structure of these devices, followed by a description of the procedures for fabrication of the thin-film devices. The measurement setup and the procedures followed are then explained in detail. Finally, the results of the measurements are presented and discussed in detail.

In Chapter 6, the results of the measurements performed on the thin-film devices are discussed. Analysis of these results will be used to improve our understanding of the behavior of

PHS capacitors. This chapter will be concluded with the major observations and conclusions obtained from this research along with ideas for further research in this area.

#### **CHAPTER TWO**

# REVIEW OF CAPACITOR THEORY AND THE EVOLUTION OF TANTALUM CAPACITORS

# **Capacitor Theory**

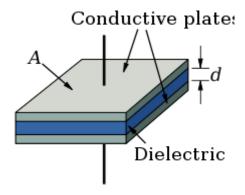

A capacitor is a two terminal device which can temporarily store charge. In its simplest form, it has two electrical plates or electrodes separated by an insulator (dielectric). The positively charged plate is called the anode and the negatively charged plate, the cathode. An illustration of parallel plate capacitor is shown in Figure 2.1[4]. Two parallel conducting plates of area 'A' are separated by a dielectric of thickness 'd'. While one conducting plate serves as cathode, the other serves as the anode. An increase in the electric field across a dielectric increases the charge accumulated on the plates in-turn increasing the potential difference between the plates. The ability of the capacitor to store the charge is described by its capacitance. Capacitance is given by the ratio of the magnitude of charge to the magnitude of the potential difference between the plates. Capacitance is proportional to the area (A) of the conductors and the electrical permittivity of the dielectric obtained by the product of electrical permittivity ('\varepsilon') of free space and the dielectric constant ('k') of the insulating material. It is inversely proportional to the distance (d) between the plates [2, 3]. Capacitance of a parallel plate capacitor is thus given by equation 2.1.

$$C = \frac{\varepsilon \cdot k \cdot A}{d} \tag{2.1}$$

Figure 2.1: An illustration of parallel plate capacitor [4]

Energy(E) stored in a capacitor due to an electric field is given by

$$E = 0.5 \cdot C \cdot V^2 \tag{2.2}$$

It implies energy storage is dependent on area and dielectric thickness. Sometimes more charge or energy must be stored in capacitors of very small size, a quality measured in terms of energy stored per unit volume, defined as Energy density. High energy density is achieved by increasing surface area, improving dielectric quality, or decreasing dielectric thickness.

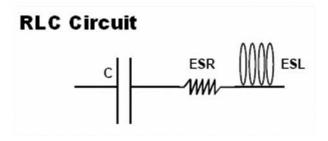

All manufactured capacitors have certain parasitic elements. An Equivalent Series Resistance (ESR) exists in capacitors because the conducting plates are not perfect conductors and because of the loss associated with the dielectric. An Equivalent series inductance (ESL) is created when current is restricted to follow a defined physical path. The current must be crowded into the available paths, and greater restriction over a longer path increases the ESL. The general electrical performance of a capacitor can be defined as a series arrangement of these elements with the ideal capacitor as shown in Figure 2.2[6]. These parasitic elements are influenced by type, quality, type of processing, and packaging that goes into the fabrication of these capacitors. [6]

Figure 2.2: Parasitic elements of a capacitor [6]

Ideally, capacitors should not conduct DC current. Since the capacitors are not perfect some DC current always flows through the capacitor, which is defined as Leakage Current. The amount of this DC leakage current depends on the quality and thickness of the dielectric, anode and cathode material. When the DC voltage across the capacitor is sufficiently high, very high leakage current flows through the capacitor which can damage the dielectric. The voltage at which this breakdown occurs is defined as the breakdown voltage of that capacitor (BDV). This BDV indicates the upper limit of the operation for a capacitor. Under normal circumstances, devices are operated well below the BDV, but within a range specified by the manufacturer referred to as the Working Voltage range. A capacitor is expected to operate at its intended level of performance within this range [5].

### **Electrolytic Capacitors**

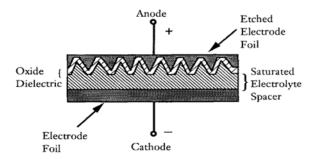

Electrolytic capacitors are a very common type of capacitor used in certain applications where there is a need for high capacitance in a very small volume. They are called electrolytic due to the fact that either or both of their conductive plates is an electrolyte. An electrolyte is typically a solution that conducts electricity via the ions present in the solution, and the dielectric is formed by inserting the anode in an electrolytic bath and having current pass through the system [5]. Here

the electrolytic bath acts as a cathode. Due to the oxidation process, a thin layer of metal oxide is formed on the surface of the anode, which will serve as the dielectric [6]. The voltage at which this oxidation of the anode (referred to as Anodization) takes place is called the Formation Voltage (V<sub>f</sub>) of that capacitor. Dielectrics formed this way are thin, rough and perfectly conforming to the surface of the metal anode. While keeping the size of the electrode the same, the surface area of the dielectric can be increased by starting with an anode with an uneven surface. Since the cathode is a liquid electrolyte it easily conforms to the uneven surface of the dielectric resulting in a higher capacitance. We can see a clear difference between a standard parallel plate capacitor in Figure 2.1 and an electrolytic capacitor with a larger dielectric contact area in Figure 1.3[7]. In electrolytic the capacitor the anode is etched with an uneven surface, whereas the anode (A) in parallel plate has smooth surface. As seen in the Figure 2.3 this uneven surface in electrolytic capacitor results in large surface area in contact with dielectric. One benefit from using a liquid electrolyte is that ionic current through the electrolyte helps to maintain the integrity of dielectric. It helps by healing any dc leakage damage sites through reformation of the dielectric (healing) in a fashion similar to how it was originally formed [2].

Figure 2.3: Electrolytic capacitor showing a large anode surface area [7]

# **Tantalum Capacitors**

Historically, aluminum was used in electrolytic capacitors for the anode. However, Tantalum gained prominence owing to the significant improvements in terms of the range of operating temperature and chemical stability of the metal and its anode [8]. Despite these improvements, there were still limitations associated with all wet electrolytic capacitors, such as large volume, low temperature limitations resulting from solidification of the electrolyte, and a limited shelf life [6,8]. Another drawback is due to the use of a caustic solution, which generates gases and cannot withstand thermal cycles of a surface mount assembly [9].

Then came a breakthrough in the form of manganese dioxide, MnO<sub>2</sub>, acting as a cathode. MnO<sub>2</sub> is a semiconducting solid with good electrical conductivity and long-term stability to act as a cathode. The main advantage of MnO<sub>2</sub> is that it can be applied as a Manganese Nitrate solution to anodized tantalum by a series of dips with drying cycles in between. The chemical equation showing the formation of solid Manganese dioxide from Manganese nitrate using pyrolysis carried out at 250 to 350°C, is shown below [9]: MnO<sub>2</sub> as a cathode is solid, occupies much less volume, has better temperature characteristics and shelf life, but still conforms to the surface of the dielectric much like a liquid electrolyte [9].

$$Mn(NO3)2.6H2O \rightarrow MnO2 + 2NO2 + 6H2O$$

(2.3)

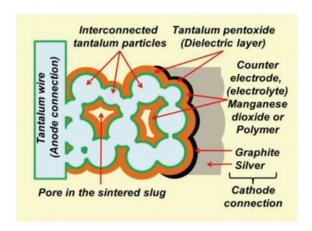

## Construction

Construction of solid Ta capacitors starts with fine tantalum powder in the form of spherical grains. Technical advancements in tantalum powder move towards shrinking the diameter of the grains which increases the surface area or capacitance per unit volume. The anode is formed by pressing the powder into a pellet, a compact collection of tantalum powder grains, around a tantalum wire. Within the pellet, as particles are pressed together they form an electrical contact, though there is still a large amount of open volume. The tantalum wire serves as a common electrical contact for all particles in the pellet [11].

To increase the contact area between the grains in the pellet and the tantalum wire, the anode (pellet +Ta wire) is sintered in vacuum at  $1350\,^{0}$ C for 10 minutes[12]. This sintering process also helps to drive out any contamination that was introduced during the pressing process. The result is a pure porous Tantalum pellet with large amounts of surface area within a confined volume [9,11]. In the next step the oxide layer is formed on the pellet by submerging it in an electrolytic bath and passing current through it. Liquid electrolyte enters all voids and channels and makes contact with the Tantalum particles and Tantalum wire. Oxygen from the electrolyte combines with Ta when the current is passed through the system to form the dielectric,  $Ta_2O_5$ . The thickness and consistency of the dielectric depends on the formation voltage,  $V_f$ , the current, and the time for which these are applied.

The cathode material applied is in a liquid form so that it penetrates the porous anode structure. MnHNO<sub>3</sub> is a liquid in which the Ta pellet is dipped, and then heated to dry. MnHNO<sub>3</sub> is converted to solid MnO<sub>2</sub> in the drying process. This dip and dry process is continued until the desired cathode thickness is achieved. MnO<sub>2</sub> thus penetrates into the porous Ta and covers the outside surface. On top of MnO<sub>2</sub> a graphite layer followed by silver paint is applied to achieve a

low resistance interface. The structure of a capacitor with all the above-mentioned components is illustrated in Figure 2.4[13]. On the left end is the Tantalum wire to which electrically continuous spherical Tantalum particles are connected. Other layers are labeled accordingly in Figure 2.4. The last step before encasing the capacitor is to connect a lead frame to the silver paint with conductive epoxy in order to make an external cathode connection, while the Ta wire serves as the anode [11]. Figure 2.5[14] shows an illustration of a completed chip-type tantalum capacitor.

Figure 2.4: Structure of solid Ta capacitor with MnO<sub>2</sub> cathode [13]

Figure 2.5: Finished surface-mount Tantalum capacitor [14].

# Failure Mechanism of Ta-Ta2O3¬-MnO2¬ Capacitors

Manufacturers of Ta capacitors often recommend de-rating of 50% for these devices. So, even if the capacitor is rated to work at a specific operating voltage it is still recommended to operate below 50% of that voltage. This cautionary measure is recommended to limit the high turn-on and infant mortality rates observed in solid Tantalum capacitors.

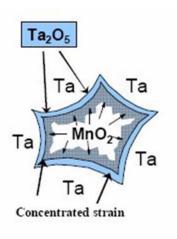

According to one theory, the reason for these failures is the stress-induced defects in the dielectric. During the dip and dry process of the Ta anode, liquid Manganese nitrate enters small channels and openings in the Ta pellet. This process involves dipping the pellet in manganese nitrate at room temperature and then heating at 270°C to dry. This process is repeated several times to achieve full coverage. As three materials of different coefficients of thermal expansion are involved (Ta, Ta<sub>2</sub>O<sub>5</sub>, and MnO<sub>2</sub>), repeated cycles of heating can create mechanical stress and ultimately lead to cracks in the dielectric. Figure 1.6 is an image of a constricted channel inside a porous anode where MnO<sub>2</sub> is contributing to stress on the dielectric layer [15].

Figure 2.6: MnO<sub>2</sub> as contributing force to cracks [15]

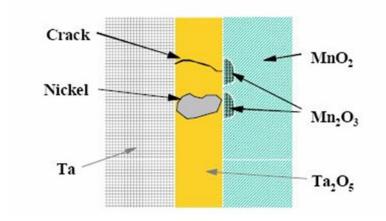

It is impossible to create a perfect and continuous dielectric because of impurities that will be present even in the purest of Tantalum metal and electrolyte solutions available [16]. These impurities along with stressed areas created during the processing create weakened sites in the dielectric. When subjected to high voltage these sites collapse and create a path for leakage current [11]. Due to this current, MnO<sub>2</sub> present at the leakage sites will start heating up. Eventually, this heat will increase and reach temperatures sufficiently high to cause conversion of MnO<sub>2</sub> to its other oxide form of Mn<sub>2</sub>O<sub>3</sub>. This lower oxide form of Manganese has very high resistance and thus will close the current path. This process is called Self-healing in Ta-MnO2 capacitors, though the dielectric is not actually healed [6,11]. This self-healing process is illustrated in Figure 1.7[6].

Figure 2.7: Self-healing property of MnO<sub>2</sub> [6]

All the manufactured solid Ta capacitors have defects in their dielectric. Before selling, these capacitors are stressed to a high voltage to activate the above self-healing mechanism. This process, referred to as aging of the capacitors, will remove many fault sites and reduce leakage current. This process of healing will continue long after the aging process as the application life increases [11].

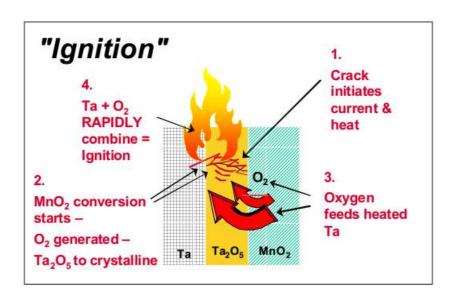

In the self-healing process, at a temperature slightly higher than that required for self-healing, the dielectric itself will start heating up and convert from an amorphous to a crystalline structure. However, the crystalline form of this oxide is almost 1000 times more conductive than the amorphous structure. So, this crystallization process eventually results in an increase in the leakage current. On the other hand, the cathode material MnO2 is going through a reduction process because of the same heat. This reduction process generates free oxygen which can act as fuel to the heat. More heat generated will help spread the crystallization to the whole dielectric. Eventually, oxygen and heat cause ignition of the whole device. This mechanism is illustrated in figure 1.8. [6,11,16]

Figure 2.8: Theoretical ignition failure sequence [6].

This ignition reaction causes the capacitors to fail visibly with fire. The self-healing property of MnO2 is the reason for wide use of solid Ta capacitors. However, the excess oxygen in MnO2 readily serves as a source of failure in these capacitors. Also, high ESR of Tantalum

capacitors is also due to MnO2. So, for further improvement in performance of Solid Ta capacitors there was a need to find a substitute for MnO<sub>2</sub>.

# Conclusion

This chapter explains the basic capacitor theory, electrolytic capacitors, Tantalum capacitors with liquid electrolyte, and finally solid Ta capacitors. The disadvantages of Solid Ta capacitors with MnO<sub>2</sub> along with the growing demand for smaller and better performing capacitors has led to the next level of innovation in Tantalum capacitors. In the next stage, MnO<sub>2</sub> will be replaced by intrinsically conducting Polymers (ICP).

#### CHAPTER THREE

#### POLYMER TANTALUM CAPACITORS

## **Intrinsically Conducting Polymers**

Intrinsically conducting polymers have conducting properties, unlike traditional polymers, with conductivity ranging between metals and insulators. These polymers have a conjugated structure, meaning alternate double and single bonds in the polymer chain, which are responsible for charge carrier conduction. Some examples of conducting polymers are Polyaniline, Polypyrrole, Polythiophene, Polyethylenedioxythiophene (PEDOT), Poly(p-phenylene ethylene)s [17].

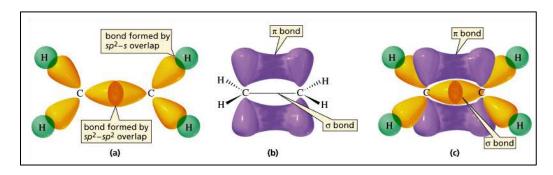

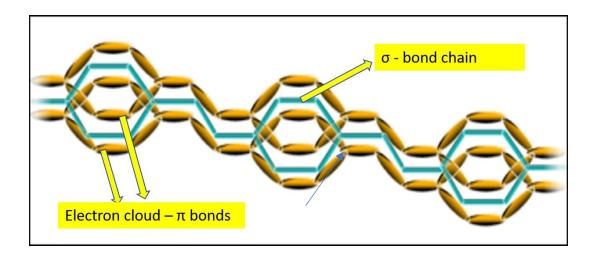

Compared to inorganic semiconductors, these polymers have significantly different mechanisms for conduction. Carbon atoms in the polymer chain have SP<sub>2</sub>-Pz hybridized orbitals and there two types of bonds involved in the polymer chain. Figure 3.1(a) [18] shows top view of two carbon atoms forming a sigma bond between their SP<sub>2</sub> hybrid orbitals. Three SP<sub>2</sub> orbitals of each carbon in the chain form sigma bonds with three adjacent carbon atoms. Figure 3.1(b) shows Pz orbitals involved in a  $\pi$  bond with an adjacent carbon atom and one carbon atom can form a  $\pi$  bond with only one atom at any instance. The  $\pi$  bonds shown in Figure 3.1 are present between adjacent atoms throughout the polymer molecule to form a delocalized electron cloud as shown in the Figure 3.2[19]. Solid blue line in the picture represents the polymer chain, with Carbon atom at each corner, and every carbon atom is bonded to the adjacent carbon atom with a sigma( $\sigma$ ) bond. Pi( $\pi$ ) bonds between the atoms throughout the molecule forms an electronic cloud represented by the yellow chain of ellipses above and below the carbon atom chain. Charge transport in this electron cloud takes place by a mechanism called hopping where the electrons hop from orbital of one atom to orbital of adjacent atom.

Figure 3.1: Sigma and Pi bonds between adjacent carbon atoms [18].

Figure 3.2: Delocalized electron cloud. Charge transport in the polymer chain takes place through hopping in the electron cloud. [19].

Conjugated polymers in their undoped or pristine state are semiconductors or insulators. Undoped conjugated polymer, such as polythiophene or polyacetylene, has a conductivity of around 10<sup>-10</sup> to 10<sup>-8</sup> S/cm. Upon doping, there is a rapid increase in electrical conductivity of several orders of magnitude up to values of around 10<sup>-1</sup> S/cm, even at a very low level of doping such as < 1 % of polymer weight. Further doping of the conducting polymers result in a saturation of the

conductivity at values around 100-10,000 S/cm for different polymers. The highest values reported to date are for the conductivity of stretch oriented polyacetylene, with confirmed values of around 80,000 S/cm[20]. Considering the fact that the traditional polymers are insulators, the discovery and development of conducting polymers came as a major breakthrough for which three scientists A.J. Heeger, A.G. MacDiarmid and H. Shirakawa were awarded Noble Prize in 2000 [21].

## Polymer as a Substitute For MnO<sub>2</sub>

Though many advancements have been made to produce Ta caps with low ESR, MnO<sub>2</sub> remained the primary reason for high ESR. It has a resistivity of 2 to 6 Ohm-cm. Conducting polymers, which showed properties of high conductivity, looked promising to replace MnO<sub>2</sub> as cathode in Ta Capacitors. Poly (3,4-ethylenedioxythiophene), or PEDOT, is a well-known conducting polymer with high conductivity up to 500 S/cm and electrochemical stability. A water dispersion of PEDOT (typically at 1-3% wt. solids) doped with poly(styrenesulfonate) (PSS) to increase conductivity of PEDOT, is commercially available and considered for used in Polymer Ta capacitors [22]. PEDOT Polymer Ta capacitors showed much lower ESR over a range of frequencies (10kHz to 1000kHz) compared to Ta-MnO<sub>2</sub> capacitors[23].

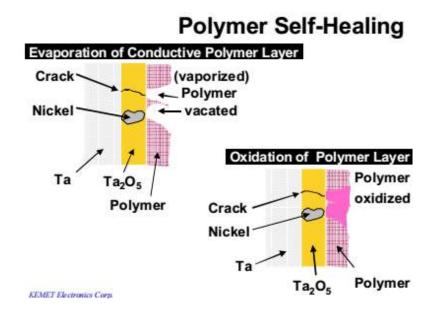

PEDOT in polymer Ta capacitors also exhibits the self-healing effect, which is responsible for reformation of dielectric in electrolytic capacitors. There are two possible explanations for self-healing in polymer Ta capacitors, illustrated in Figure 3.3 [24]: (1) Evaporation of conductive polymer layer: Heat generated at the fault site causes evaporation of polymer layer, thus vacating the fault area and preventing further leakage current and dielectric damage; or (2) Oxidation of polymer layer: The heat generated near dielectric leakage paths causes a change of oxygen levels in the polymer resulting in an oxidized polymer with higher resistivity[24]. In either case a fault

correction mechanism is present in the polymer which served as another reason to replace  $MnO_2$  with polymer as cathode in Ta capacitors. Thus, polymer began to replace  $MnO_2$  as cathode.

Figure 3.3: Self-Healing property of Ta capacitor with polymer cathode [24]

## In-situ and Prepolymerized PEDOT Ta Capacitors

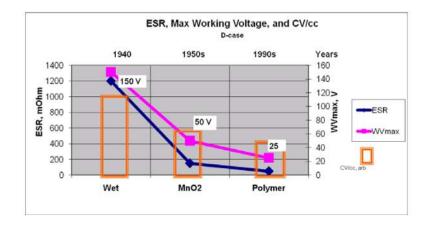

Traditionally, PEDOT is deposited by polymerization of 3,4-ethylene-dioxy-thiophene in the presence of iron III toluenesulfonate. Ta capacitors with the polymer deposited in this process are referred to as In-situ Ta polymer capacitors. As shown in Figure 3.4 [24], maximum working voltage of wet Ta capacitors was at 150V and MnO<sub>2</sub> based solid tantalum capacitors at 50V with the least working voltage belonging to in-situ Ta polymer capacitors was at 25V. As mentioned in Construction of Ta capacitors in Chapter 2, increasing the Formation Voltage should increase thickness of dielectric, which in turn should increase Breakdown Voltage. However, increasing the formation voltage in polymer Ta capacitors did not improve their breakdown voltage. BDV levelled off around 50V despite an increase in dielectric thickness [26]. This levelling of breakdown voltage

limited the working voltage, since the working voltage cannot be more than 50% of BDV in order to provide long-term stability and reliability [16].

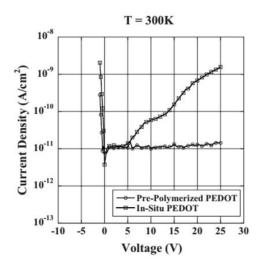

Figure 3.4: Maximum working voltage of Ta capacitors [24].

Eventually, this problem was solved by using a different polymerization technique. In this method, the PEDOT is polymerized before it is applied to the Ta pellets through a dip and dry process. This technique, referred to a pre-polymerization of PEDOT, resulted in a decrease in leakage current which in turn increases the BDV. Figure 3.5 shows the leakage current density in Pre-polymerized capacitors that remained low compared to current in In-situ Polymer Ta capacitors, which increased with bias. The pre-polymerization process possibly eliminated the stressing of the anode through repeated polymerization cycles as in the In-situ process, and this evidently increased the BDV [25]. Alternatively, since the particle size of polymer in pre-polymerized PEDOT is greater than in In-situ PEDOT pre-polymerization prevents penetration of PEDOT into dielectric macro defects [27].

Figure 3.5: I-V characteristics of polymer Ta capacitors with in situ and prepolymerized PEDOT cathodes at T = 300 K. Anodic oxide film thickness was 200 nm [26].

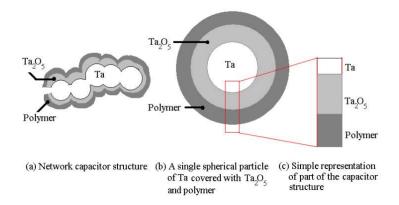

# MIS Model for Polymer Ta Capacitors

As discussed previously, several attempts have been made to explain the difference between In-situ and Prepolymerized Ta capacitors at a fundamental level [25,26]. At the material level, Ta capacitors essentially consist of numerous spherical Ta particles covered with oxide and then with PEDOT. That is; a metal anodized with an amorphous oxide which is then covered with a semiconducting polymer. This structure is well illustrated in Figure 3.6 where the capacitor is shown as combination of numerous spherical particles in 3.6(a), the detail of each spherical particle and the layers of metal (Ta), insulator (Ta<sub>2</sub>O<sub>5</sub>) and semiconductor (polymer) respectively shown in 3.6(b) & 3.6(c). This concept of the Metal-Insulator-Semiconductor (MIS) structure, as illustrated in Figure 3.6(c) is new to the capacitor industry, although it is familiar and well characterized in the microelectronics industry. This structure is similar to MOS capacitor structure studied in microelectronics, where gate is metal, SiO<sub>2</sub> is oxide and n or p-doped silicon serves as

semiconductor. Conducting C-V measurements on polymer Ta capacitors also concluded that these function essentially as MIS devices and also helped explain the better performance of prepolymerized a capacitor compared to in-situ Ta capacitors [26].

Figure 3.6: Simplified Ta capacitor structure for analysis [12]

### Polymer Hermetic Sealed (PHS) Ta Capacitors

After Prepolymerized PEDOT, the next big leap in technological development came in the form of Polymer Hermetic Sealed (PHS) Ta capacitors. PHS capacitors are polymer tantalum capacitors with moisture sealed inside capacitor via hermetically sealing the device inside a package. After applying carbon and silver layers over the PEDOT layer, the capacitors go through a humidification process at a temperature of 85°C and 85% relative humidity. This hermetic seal helps in maintaining the moisture inside the capacitor for long-term use. Retaining moisture inside the capacitor has also improved properties of DC leakage, ESR and stability [1].

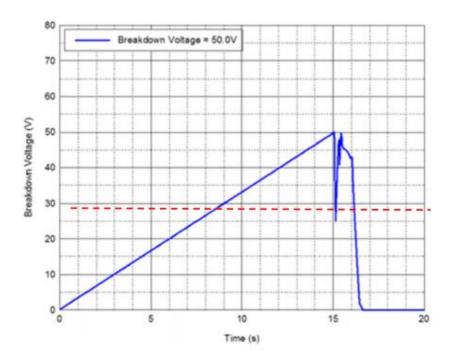

A variant of PHS capacitors, referred to as low voltage PHS Ta capacitors, are formed at low formation voltage with thinner dielectric, uses finer tantalum powder and a hybrid polymerization technique involving both in-situ and pre-polymerization. Recently, KEMET discovered a new property of low voltage PHS Ta capacitors which was never seen before. This

property is Breakdown Voltage exceeding the Formation Voltage. Figure 3.7[1] shows breakdown test results of PHS capacitor formed at 28V, shown in red dotted line, and breakdown occurred at 50V. Such a phenomenon was never observed before in the 75 years of manufacturing and testing of Ta capacitors. BDV of a capacitor is directly dependent on thickness of dielectric among other factors, with BDV increasing with dielectric thickness. Since the dielectric thickness is proportional to Formation voltage, in theory, breakdown voltage is always less than formation voltage

Figure 3.7: Breakdown test for PHS Ta Capacitor with  $V_f = 28V$  [1]

Phenomenon of BDV >  $V_f$  is possible and previously observed in Wet Ta capacitors and Polymer Ta capacitors due to extension of dielectric[28]. Though, in such cases the capacitance loss is observed due to an increase in dielectric thickness and more capacitors are used in the applications to compensate the capacitance loss. In the low voltage PHS Ta capacitors, even after breakdown the resistance of the capacitor was in the range of 0.1-1Mohms, an open failure mode

of capacitors in which current through the capacitor is cutoff unlike in a shorted failure where the current potentially destroys other components in the circuit. This combination of  $BDV>V_f$  without capacitance loss and open failure mode is critical for the applications where there is a limitation on space and number of capacitors and where short circuit current can prove to be costly.

## Conclusion

Conducing polymer was reviewed in this chapter, detailing the advantages associated with replacing MnO<sub>2</sub> with PEDOT polymer. Advances in polymer capacitors and the analogy between polymer Ta capacitors and MIS devices was discussed. PHS capacitors was introduced along with some interesting aspects associated with these capacitors. In the next chapter we shall start with the reasoning for this research on PHS Ta capacitors and move onto measurements on capacitors provided by KEMET Electronics Corporation.

#### CHAPTER FOUR

#### CHARACTERIZATION OF PHS TANTALUM CAPACITORS

#### Background

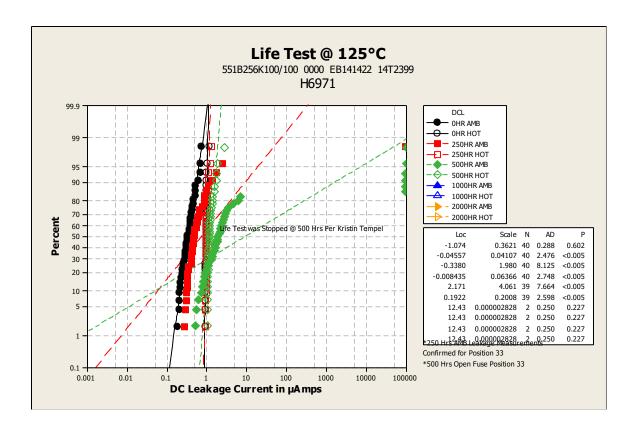

As discussed in Chapter 3, Polymer Hermetic Sealed (PHS) Tantalum capacitors are the best Polymer Ta capacitors available today. PHS capacitors are being commercially produced and available in the market [29]. One of the crucial characterization methods used on PHS Capacitors, known in the industry as "Life Tests", are often performed on a random sample of capacitors to test their long-term operational stability and reliability under typical application conditions. Life Tests conducted in KEMET typically consists of subjecting the capacitors to their working voltage at 125°C for 2000hrs. They are monitored and DC leakage current along with ESR were recorded at regular time intervals. Results are represented in the form of plots showing percentage of capacitors against the current or the ESR. For example, a point at (30%,10mA) on the plot represents that 30% of the capacitors have leakage current less than 10mA in the given set of capacitors. Results of the Life Test conducted in KEMET on one random sample of PHS Tantalum capacitors are illustrated in Figure 4.1 & Figure 4.2. Figure 4.1 shows the DCL characteristics of the capacitors, with a legend on the right side of plot detailing the icons for representing different stages at which leakage current was measured and the corresponding temperature. Current was measured before the experiment, after 250 hours, 500 hours, 1000 hours and 2000 hours. HOT stands for DC leakage measured at 125°C and AMB stands for measurement at ambient temperature. Per the plot in Figure 4.1 after 500 hours, at ambient temperature 80% of the capacitors have a DCL current of 10μA or less and the remaining 20% reached 100mA. This high current indicates a dielectric breakdown and capacitor damage. From here the capacitors among this 20% will be referred to as capacitors which failed Life Test or failed capacitors.

Figure 4.1: DC Leakage measured during Life Test. DCL after 500 hours in 80% of capacitors is less than  $10\mu A$ , while in remaining 20 % it reached 100mA [Provided by KEMET]

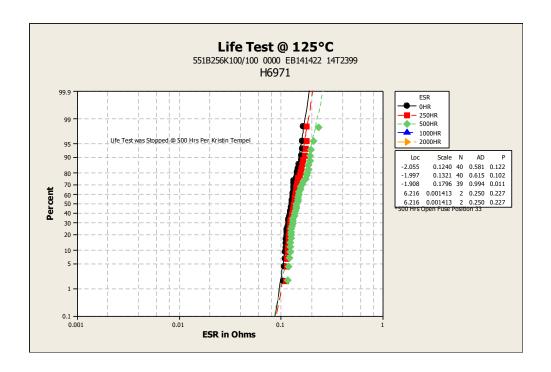

In Figure 4.2 we see the ESR results of the same Life Test. The ESR in all capacitors remained less than one ohm even when the DC leakage current increased significantly. This type of capacitor failure with high DC leakage current and low ESR is called high-leakage/short failure mode in capacitors. It implies that whenever these capacitors see a dielectric breakdown, the anode and cathode terminals will get shorted and act as a path for high current. This uncontrolled high current has the potential to damage other components in the circuit and thus undesirable.

Figure 4.2: ESR of all capacitors remained less than 10hm after 500hrs even when 20% of these capacitors showed high DCL current. [Provided by KEMET]

This 20% failure rate shown in Figure 4.1 is considered very high by industry standards. To investigate this failure rate, a further study of these capacitors was considered necessary. The point of interest is to perform certain measurements to determine whether the capacitors which did not fail the test will still meet their specifications after the Life Test and if the failed capacitors behaviour was temporary or if they are damaged for sure. Results of these measurements are then compared with results from same measurements performed on Virgin samples, samples which did not go through Life Test, to determine if there are any inherent failure mechanisms present even before the Life Test was performed. Measurements at different temperatures with applied voltage will test the ability of dielectric in resisting breakdown failure and studying DC leakage at these

conditions would help understanding failure mechanisms. For this purpose, a plan was created to investigate current-voltage characteristics of these capacitors at different temperatures.

### Measurement Procedure

Three sets of capacitors were provided by KEMET:

Set 1 : Capacitor samples which passed life test – "Good Samples".

Set 2 : Capacitor samples which failed life test – "Bad Samples".

Set 3 : Capacitor samples without life test – "Virgin Samples".

A measurement plan was created for the above three sets of capacitors at their rated voltage and at different temperatures. Rated voltage( $U_R$ ) is the "labelled" voltage of the device (capacitor), and it is defined as the maximum voltage at which the device can be safely operated at the rated temperature. As a standard industrial practice, Ta capacitors are usually operated at 50% of the rated voltage, a practice called as derating, to improve the long-term reliability and initial power on performance of the devices. The Rated temperature( $T_R$ ) is the temperature at which the device is expected to normally operate without lowering the voltage rating on the device. The device can also operate at temperatures higher than the rated temperature; however, in this case the capacitor voltage rating must be lower than the Rated Voltage. The maximum recommended operating temperature of a device is defined as the Category Temperature(CT), devices at this temperature must be operated by lowering the voltage rating than the Rated Voltage [30]. Maximum voltage the capacitor can be subjected to, at Category Temperature, is referred to as Category Voltage. The Category Temperature of the capacitors from KEMET is  $125^{\circ}$ C, and Rated Temperature is  $85^{\circ}$ C, the Rated voltage is 100V and the Category Voltage is 67V. The lower end of operating temperature

is -55°C for these samples. All three sets of samples received from KEMET were measured at the full voltage and temperature range in the following manner:

- 1. 0-100V at Room temperature.

- 2. 0-100V at 85°C.

- 3. 0-67V at 125°C.

- 4. 0-100V in Liquid Nitrogen (LN2).

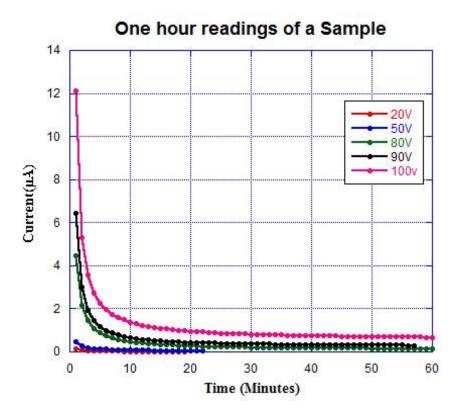

The focus is to obtain I-V characteristics of the capacitors under the conditions stated above. Leakage current in the capacitors in the range of milliamps would imply significant damage, and the devices would be classified as failures. I-V characteristics cannot be obtained by using the standard voltage sweep because in capacitors, at any voltage, when the voltage is changed the current will decay with time before reaching a steady state value, and so we must allow the current to stabilize before determining the DC leakage current. When the current stops decaying significantly with time, the capacitor system is assumed to have reached steady state. Time to reach steady state must be experimentally determined using an I-time(I-t) measurement, during which a constant voltage is maintained across the capacitor. The I-t characteristics taken for one hour for one of the samples measured at five different voltages was obtained and is shown in Figure 4.3. In Figure 4.3, current is decaying exponentially with time at a constant voltage following the standard relation between current and time in capacitors given by  $I \alpha e^{-t/RC}$ . To strike a balance between the measurement time required and the accuracy of the steady-state current, a delay of 600 seconds was selected for performing the measurements. So, at each voltage, the current was allowed to stabilize for 600 seconds before recording the current. Then, I-V characteristics of the devices were plotted.

Figure 4.3: I-time measurement performed for one-hour to observe current decay.

### Process automation

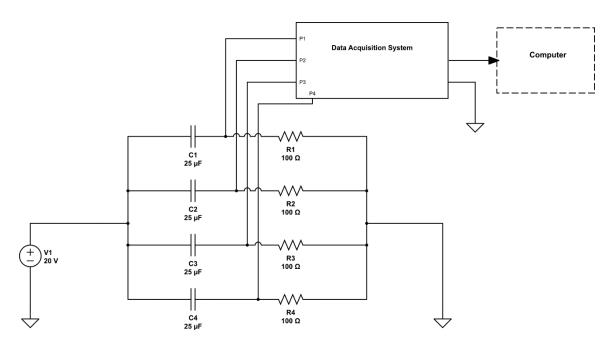

Since multiple capacitors needed to be characterized, which is a very time-consuming process, an automated system was used to collect the data. Schematic representation of the complete system is shown in Figure 4.4. As shown in Figure 4.4, capacitors were connected in parallel and a  $100\Omega$  resistor was placed in series with each capacitor to limit the current flowing through the capacitor. To implement this automated plan, capacitors were soldered onto a test board, resistors were soldered onto a separate perf-board and both connected in series. They are soldered on separate boards to keep the circuit board compact and have flexibility to transfer

capacitors to high temperature or low temperature setup. By using the Data Acquisition System(DAQ) - HP 3421A [31] it is easy to automate measuring voltage across several discrete components, for example, resistors. So, the voltage across each resistor, in series with each capacitor, was recorded by connecting the DAQ to a PC. The voltage measured across the resistor is then divided by resistance to obtain the current through the respective capacitor in series. Figure 4.4 illustrates the setup used to measure the voltage across resistors. Capacitor(C1) & resistor (R1) are in series, voltage across R1 is measured by connecting a line to port(P1) of the DAQ. Similarly, voltage across resistor in other capacitor-resistor combinations is measured by connecting to remaining ports of DAQ. This voltage data is transmitted to computer where the current in each branch is computed and stored to a text file. This data is then plotted by importing the data into the graphics tool, KaleidaGraph [32].

Figure 4.4: Automated system setup to measure voltage across the resistors, which was the used to measure DC leakage current through the capacitors.

## High-Temperature Measurements:

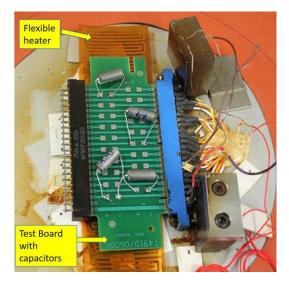

High-temperature measurements were performed by placing flexible heaters insulated with polyimide film [33] above and below the test board in a vacuum container. Figure 4.5 shows the setup where a glass closing is placed on a platform, air is sucked from this closing using a vacuum pump through a hole in the platform. The temperature was controlled using the voltage applied to these heaters and temperature was monitored using a direct contact surface thermometer scale [34]. Figure 4.6 shows the test board with PHS capacitors soldered on them and a flex heater below it. Another flex heater will be placed over the test board during the experiment.

Figure 4.5: A vacuum chamber is created with this setup using glass closing and removing the air using vacuum pump.

Figure 4.6: Flexible heater is place below the test board soldered with capacitors. During the measurements, another flex heater is placed over the test board.

## Low-temperature measurements:

Low temperature measurements are similar to high temperature measurements except that the test board with capacitors placed in vacuum chamber was placed in liquid nitrogen. Liquid nitrogen was taken in a flask and the test board with capacitors was completely immersed in Liquid Nitrogen to expose capacitors to the low temperature. The temperature of the liquid nitrogen was monitored using a thermocouple. Voltage across the resistors and thus current through capacitors was then measured using the setup illustrated in Figure 4.4.

### Results

I-V measurements were performed first on Set-1(Good Samples) followed by Set-2(Bad Samples) &3(Virgin Samples). Each set consisted of 3 capacitors which will be referred to as samples from now. Measurements were started under conditions where the scope for damaging the samples is minimal towards the more stressing conditions. Room temperature measurements will be performed first and last to compare and understand the effect of measurements on capacitors. The steps followed in the order are:

- 1. I-V measurements from 0 to 100V at Room temperature.

- 2. I-V measurements from 0 to 100V in LN2.

- 3. I-V measurements from 0 to 100V at 85°C.

- 4. I-V measurements from 0 to 67V at 125°C.

- 5. I-V measurements from 0 to 100V at Room temperature.

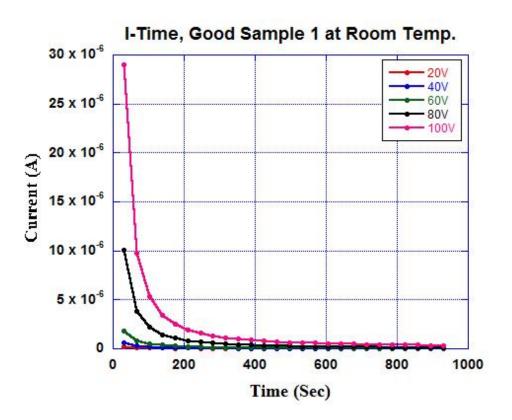

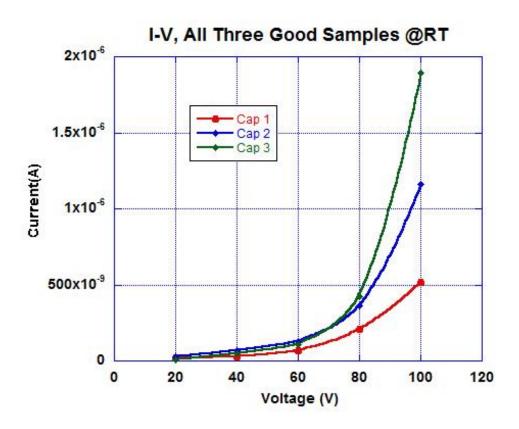

I-V measurements were performed at room temperature on Good Samples and the result of the measurement on Good Sample -1 is shown in Figures 4.7 & 4.8. In Figure 4.7, we see that the current reached a steady state after approximately 600 seconds. For each input voltage – 20V, 40V, 60, 80V & 100V, the corresponding current is recorded and then the corresponding I-V curve was plotted. The I-V plot for all three Good Samples is shown in Figure 4.8 and shows the current increased with the applied voltage. This is in line with a normal capacitor behaviour and this result imply that at room temperature Good Samples are in good working condition. The difference between the three capacitors is owing to differences in individual variations and the stress they have gone through during Life Test.

Figure 4.7: I-t of Good Sample-1 at Room Temperature for at different voltages.

Figure 4.8: I-V of all Good Samples derived from I-time curves shown in Figure 4.7.

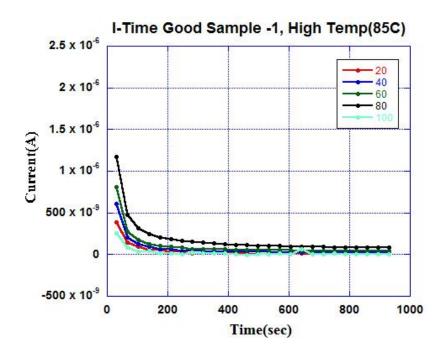

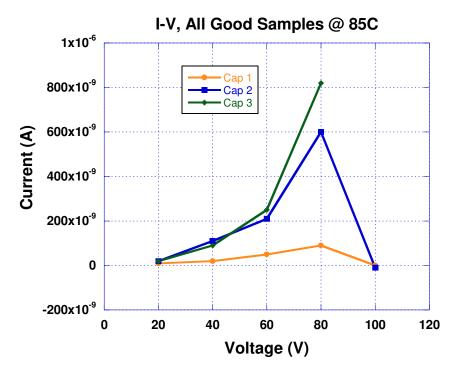

After the measurements at room temperature, the same I-time and I-V measurements were performed at 85C. The plots for these measurements are shown in Figure 4.9 and Figure 4.10. Plotting I-time measurements at 85C was expected to give exponential decaying curves as at room temperature similar to the plot in Figure 4.7 and obtained the same as shown in Figure 4.8. However, in Figure 4.9 notice that current at 100V in Capacitors 1 & 2 went down after 80V and in capacitor-3 the current at 100V reached the milliamp range and showing that point in plot would change the scale of plot and make the other curves difficult to interpret. The reason for current in Samples 1&2 at 100Vwas unknown at this stage but later figured out, it will be explained by the end of this chapter.

Figure 4.9: I-time of Good Sample-1 at 85°C at different voltages.

Figure 4.10: I-V of all Good Samples at 85°C. Current for capacitor-3 reached milliamp range and not shown here.

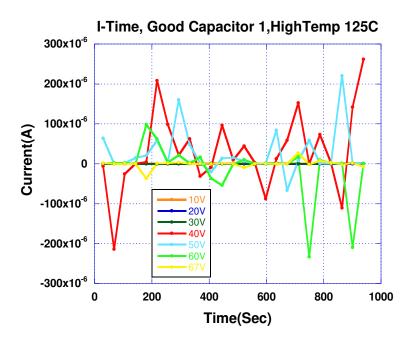

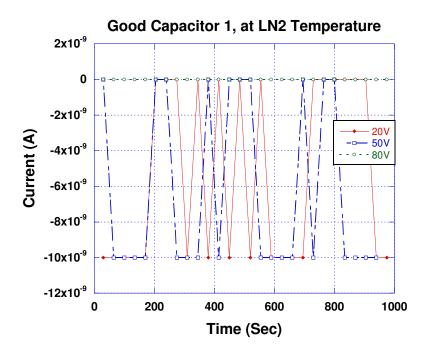

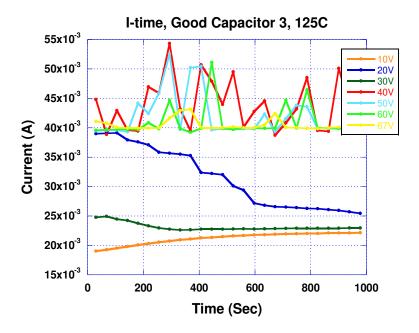

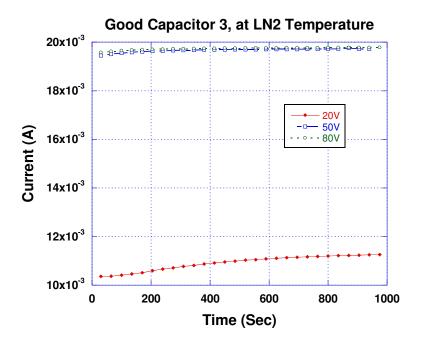

I-time plots for Capacitor -1 at 125°C and in Liquid Nitrogen are shown in Figure 4.11 and Figure 4.12 respectively. These results also represent of results for Capacitor – 2. At both temperatures, current remained below a milliamp. However, the current in Capacitor -3 continued to be in the milliamp range as can be seen in Figure 4.13 and Figure 4.14 for 125°C and Liquid Nitrogen respectively. While the behaviour of Capacitors 1& 2 is not understood, leakage current in capacitor implies a dielectric breakdown. All these results will be later understood by end of this chapter.

Figure 4.11: I-t of Good Sample-1 @125C. Current magnitude is irregular, and less than a micro-amp.

Figure 4.12: I-time of Good Capacitor-1 in Liquid Nitrogen. Current is in nanoamp range and irregular.

Figure 4.13: I-t of Good Sample-3 at 125°C. Current pattern is irregular and in a milliamp range.

Figure 4.14: I-t of Good Sample-3 in Liquid Nitrogen. Current pattern is irregular and in a milliamp range.

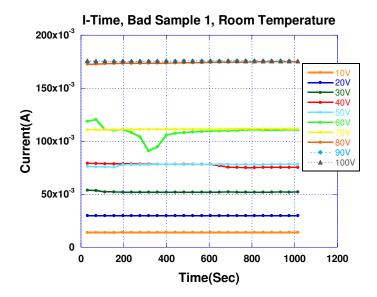

### Set 2

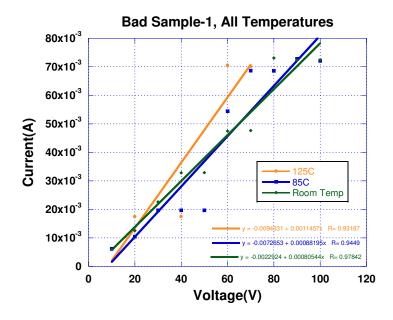

Measurements like the above were conducted on Set 2 - Bad Samples. Figure 4.15 shows I-t plot of Bad Sample-1 at Room Temperature. Unlike the typical exponential decay, current remained constant at any given voltage but increased with voltage. Similar behaviour was observed in other two capacitors in this set and at 85°C and 125°C. Plotting the current against the voltage and trying to correlate the current and voltage by using curve fitting in KaleidaGraph gave a correlation factor of more than 90%. This results shows the current and voltage are linearly correlated, an Ohmic behaviour like a resistor. The resulting plot is shown in Figure 4.16. Also, the current in all three capacitors is in milliamp range, indicating a dielectric breakdown. All these results of measurements on Bad Samples indicate that Bad Samples were definitely damaged during the Life Test and the impact of Life Test was not temporary.

Figure 4.15: I-time of Bad Sample-1 at Room Temperature. Current all voltages is in milliamp range.

Figure 4.16: I-V of Bad Sample-1 at all temperatures. There is a linear correlation between current and voltage

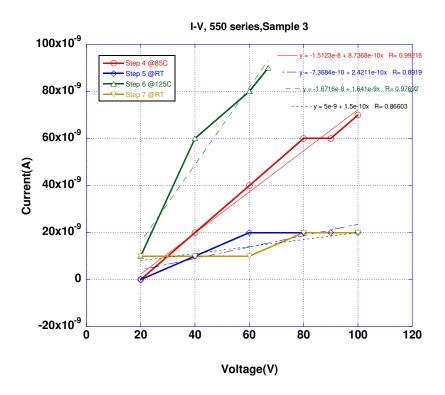

This set of capacitors are Virgin samples which did not go through life test. Performing electrical measurements at Room Temperature, 85°C, 125°C and in Liquid Nitrogen, an exponential current decay was observed in the I-t measurements. The corresponding I-V curves at each temperature are shown in Figure 4.16. Leakage current is very low, in nanoamp range, indicating a reliable operation in a circuit. The non-exponential I-V curve is possibly influenced by noise associated with very low leakage current, and the sensitivity of the setup involved in measuring this leakage current.

Figure 4.17: I-V at all temperatures, Virgin Sample -3

#### Set - 4

Since the behaviour in Set 1 was not clearly understood, another set of Good capacitors which went through life test but did not fail the test were obtained and retested. This set will be referred to as Set 4. Number of steps in the measurements were increased to include room temperature measurements after every different temperature condition to understand the effect of previous step. Changes include taking readings not only when increasing voltage from 20V to 100V, but also from 100V to 20V to observe any hysteresis. Sequence of steps followed for the measurements are:

Step 1: Room temperature. Step 5: At room temperature.

Step 2: In Liquid Nitrogen. Step 6: At 125°C.

Step 3: Room temperature. Step 7: Room temperature.

Step 4: At 85°C.

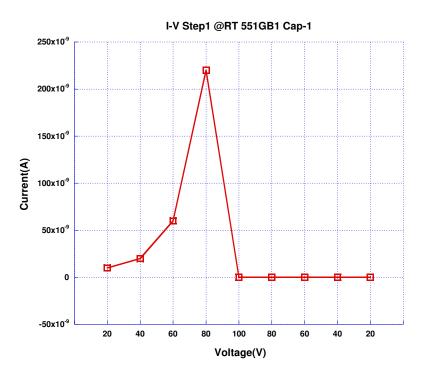

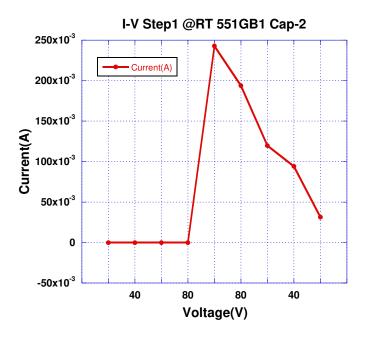

Figure 4.17 shows the result of Step 1 for sample 1. It's clear that the current increased with increasing voltage until 100V, however, there was a sudden drop in current after that. In Figure 4.18, at the same 100V, sample 2 current increased dramatically into milliamps range. The sudden increase in current in Sample 2 is because of dielectric breakdown. Both samples showed a sudden change in current at the same voltage. Close examination of the circuit revealed that the parallel connection of the capacitors in Figure 4.4 is the reason for the behaviour. At 100V when capacitor 2 got damaged (dielectric breakdown) it started drawing all the current serving as a short path to current in the circuit. So, the current in other samples dramatically decreased. When sample-2 was removed from test board to test the other samples, Sample-1 once again exhibited leakage current in nano-amp range. This explanation also helps understand the behaviour of capacitors in Set-1. In Figure 4.10 Capacitor 3 got damaged and shorted the circuit drawing all the current from remaining

two capacitors. All subsequent steps were influenced by capacitor-3 and current through remaining capacitor can be considered noise in the setup. In this set-4 all the samples got damaged in the subsequent steps revealing that even the good capacitors were effected by Life Test negatively.

Figure 4.18: I-time of Good Sample-1 of set-4 at room temperature. Current at 100V dropped to zero and remained zero amps.

Figure 4.19: I-time of Good Sample-2 of Set-4 at Room Temperature. Dielectric breakdown occurred at 100V conducting milliamps of current.

# Conclusion

The outcome of the measurements on 4 sets of Life tested PHS Ta capacitors is that bad samples are damaged for sure, and even the good samples that did not fail life test were negatively affected by Life Test. All the capacitors go through aging procedure to remove any manufacturing induced faults in the capacitor. By this aging, it is expected that the capacitors will have a long lifetime and operate at varied temperatures. However, even after aging process, the above samples failed during or after Life Test. It emphasizes the fact that a study of the fundamental structure of these capacitors is necessary.

#### **CHAPTER FIVE**

#### CHARECTARIZAION OF THIN-FILM SAMPLES

## Motivation for Investigating Thin-Film Samples

By end of Chapter Four it was concluded that PHS Ta Capacitors, provided by KEMET, failed after going through Life Test to withstand their rated voltage over the temperature range under consideration. This emphasizes the need for improvement in fabricating these capacitors. Also, the high BDV of PHS Ta capacitors, as seen in Chapter 3, is an extraordinary phenomenon and has many practical applications, such as over-voltage capability without capacitance loss and open failure mode. But there is a lack of understanding of this high breakdown voltage phenomenon. To fully exploit this phenomenon and to further understand the observations from Chapter 4, it is necessary investigate the properties of Polymer Ta capacitors through their characterization.

First order modeling, such as depletion layer thickness near the IS (Insulator-Semiconductor) interface observed in MIS devices as a function of applied bias, is insufficient to understand this behavior [26]. These pre-polymerized PHS Ta capacitors represent a complex structure made from special F-tech anodes [36], coarse tantalum powder, thin dielectrics, and pre-polymerized PEDOT cathodes sealed with internal humidity. The primary question is to understand whether the characteristics of PHS capacitors are a result of the special manufacturing process and the resulting complex structure involved, or if it is primarily due to the nature of interactions between the organic and inorganic material layers present. If it is primarily due to the nature of interactions between the materials involved, then the properties of PHS capacitors can best understood by preparing thin-film representations of these PHS capacitors; and recreating the

material interactions without involving the complex structure. Otherwise, it can be concluded that the complex structure and the technology used to fabricate these capacitors is the primary contributor to the observed properties. In either case, the results from thin-film devices will be will be helpful to understand and ultimately improve the performance and applications of PHS Ta capacitors.

## Fabrication of thin film devices

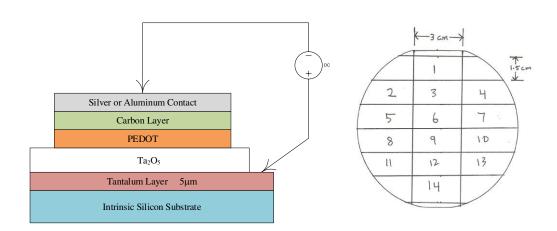

The stacking of material layers in the thin-film device should represent the real PHS capacitors as closely as possible. The structure of the thin-film device is shown in Figure 5.1(a). All the material layers are formed on a silicon wafer which essentially is the mechanical support for the devices. The starting material is a silicon substrate, and Ta is sputtered on its surface to serve as the anode. Subsequent layers of Tantalum oxide and polymer will be formed and finally a silver or aluminum contact over carbon surface will serve as the cathode, as shown in Figure 5.1(a).

4-inch intrinsic silicon wafers were purchased from University Wafer and forwarded to Georgia Tech for metal deposition. Tantalum was sputtered onto these Silicon wafers which were then diced into rectangular samples as shown in the Figure 5.1(b) at Institute of Electronics and Nanotechnology at Georgia Tech. Two sections of a 4 inch silicon wafer, which will be referred to as Flat Samples, were used for the current research. Both the flat samples, referred to as Flat Sample-1(FS1) and Flat Sample-2(FS2), were subjected to anodization in sulphuric acid at 85°C with a 44V Formation Voltage(V<sub>f</sub>). The formation voltage of 44V resulted in forming a dielectric of thickness 88nm at the rate of 2nm/Volt. After anodization, FS2 was subjected to heat treatment a procedure involving heating the samples at a predefined temperature for a fixed amount of time specified by KEMET Electronics Corporation. Later, PEDOT solution was deposited on both the

flat samples at four locations on each sample surface in the form of drops using a dropper and allowed to dry at room temperature for 24 hours. The four dots of PEDOT on each sample effectively form four capacitors with a common Tantalum metal anode. Carbon and silver layers were deposited by using a dropper to enhance the conductivity at the interface and to create a low resistance contact with external copper wires respectively. Flat samples were then heated to a temperature specified by KEMET. Capacitance of each capacitor on Flat samples was measured using an Agilent E4980A LCR meter and compared to the capacitance calculated using the known parameters.

Figure 5.1: (a) Layers in the thin film device; (b)Dicing pattern for the Si wafers.

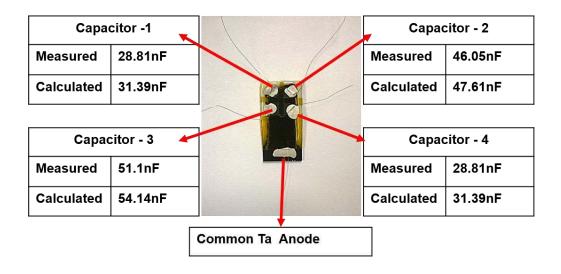

Figure 5.2 is photograph of Flat Sample – 1(FS1) with the four capacitors labeled along with their measured and calculated capacitances. The four capacitors are the four silver dots visible on the upper half of the flat sample. The other silver dot is the common anode. Kapton tape was used to separate the capacitors before applying the PEDOT preventing any contact between capacitors and to surround the epoxy cover the edges of the sample. Epoxy was used to prevent any

moisture come in contact with edges of the sample near the capacitors. We will adopt a convenient labeling such that, Capacitor-1 on Flat Sample -1 will be referred to as FS1-C1 and others are referred to similarly as FS1-C2, FS1-C3, and FS1-C4. The measured capacitance in the figure is measured at 120Hz using an Agilent E4980A Precision LCR meter. Calculated capacitance is estimated with the parallel plate model equation given by Equation 5.1, where  $\varepsilon = 8.854 \times 10^{-12}$  F/m is the permittivity of free space - the dielectric constant is k = 26, the oxide thickness is d=88nm at 2nm/V<sub>f</sub>, and areas are A1 =  $0.207 \times 10^{-4}$  m<sup>2</sup>, A2 =  $0.12 \times 10^{-4}$  m<sup>2</sup>, A3 =  $0.182 \times 10^{-4}$  m<sup>2</sup>, and A4 =  $0.193 \times 10^{-4}$  m<sup>2</sup> for capacitors C1, C2, C3 & C4 respectively. Areas were approximated by measuring the diameter of dots using a microscope and by assuming the dots are in circular shape. While C2, C3 and C4 showed consisted capacitance values with repeated measurement, the capacitance of C1 was not consistent. So FS1-C1 was not considered for any measurements.

$$C = \frac{\varepsilon * k * A}{d} \tag{5.1}$$

Figure 5.2: Flat Sample -1 showing 4 capacitors and their capacitance.

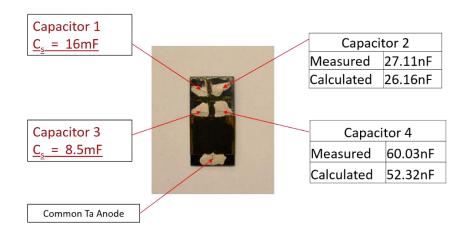

Figure 5.3 shows Flat Sample-2 (FS2) along with measured, and calculated capacitance values of each capacitor – FS2-C1, FS2-C2, FS2-C3 and FS2-C4. This flat sample, FS2, has gone through heat treatment similar to discrete commercial capacitors in KEMET facility. For FS2, only C2 and C4 showed consistent capacitance values upon repeated measurement, so all the measurements were performed only on these two capacitors. Approximate area of  $0.2*10^{-4}$ m<sup>2</sup> for each capacitor was used for calculating capacitance.

Figure 5.3: Flat Sample -1 showing 4 capacitors and their capacitance.

### **Experimental Procedure**

The primary goal for this part of the research is to observe the behavior of these thin-film capacitors over the temperature, -55°C to 85°C, and voltage range, 0V to breakdown voltage of that capacitor. To protect the samples from damage, the order of measurements will be arranged to start with the procedure which will most likely cause the least amount of stress. I-V measurements drive current through the dielectric of the capacitor, and therefore have potential to cause dielectric

breakdown. Since the breakdown voltage is unknown in these virgin devices and experimental measurements could lead to dielectric breakdown, I-V measurements were performed last. Measurements of capacitance change with temperature was performed first. Capacitance was measured at 20Hz, 120Hz, and 1Khz both in low temperature range (Room temperature to -55°C) and high temperature range (Room temperature to 85°C). The results from both high temperature and low temperature measurements were normalized to room temperature and plotted as C(T) curves.

## High Temperature Measurement Procedure