## Charging dynamics of a floating gate transistor with site-controlled quantum dots

P. Maier, F. Hartmann, M. Emmerling, C. Schneider, S. Höfling, M. Kamp, and L. Worschech

Citation: Applied Physics Letters **105**, 053502 (2014); doi: 10.1063/1.4892355

View online: http://dx.doi.org/10.1063/1.4892355

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/105/5?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Cavity-enhanced single photon emission from site-controlled In(Ga)As quantum dots fabricated using nanoimprint lithography

Appl. Phys. Lett. 104, 213104 (2014); 10.1063/1.4879845

Charge storage properties of InP quantum dots in GaAs metal-oxide-semiconductor based nonvolatile flash memory devices

Appl. Phys. Lett. 101, 212108 (2012); 10.1063/1.4767522

Size evolution of site-controlled InAs quantum dots grown by molecular beam epitaxy on prepatterned GaAs substrates

J. Vac. Sci. Technol. B 24, 1523 (2006); 10.1116/1.2190674

Trench-type InGaAs quantum-wire field effect transistor with negative differential conductance fabricated by hydrogen-assisted molecular beam epitaxy

J. Vac. Sci. Technol. B 20, 1192 (2002); 10.1116/1.1456519

Patterned growth on GaAs (311)A substrates: Dependence on mesa misalignment and sidewall slope and its application to coupled wire-dot arrays

J. Appl. Phys. 85, 3576 (1999); 10.1063/1.369717

Journal of Applied Physics is pleased to announce André Anders as its new Editor-in-Chief

## Charging dynamics of a floating gate transistor with site-controlled quantum dots

P. Maier, <sup>a)</sup> F. Hartmann, M. Emmerling, C. Schneider, S. Höfling, <sup>b)</sup> M. Kamp, and L. Worschech

Technische Physik, Physikalisches Institut, Wilhelm Conrad Röntgen Research Center for Complex Material Systems, Universität Würzburg, Am Hubland, D-97074 Würzburg, Germany

(Received 16 May 2014; accepted 20 July 2014; published online 4 August 2014)

A quantum dot memory based on a GaAs/AlGaAs quantum wire with site-controlled InAs quantum dots was realized by means of molecular beam epitaxy and etching techniques. By sampling of different gate voltage sweeps for the determination of charging and discharging thresholds, it was found that discharging takes place at short time scales of  $\mu$ s, whereas several seconds of waiting times within a distinct negative gate voltage range were needed to charge the quantum dots. Such quantum dot structures have thus the potential to implement logic functions comprising charge and time dependent ingredients such as counting of signals or learning rules. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4892355]

Quantum dots (QDs) located in close vicinity of transistor channels can induce significant threshold voltage shifts, which depend on the number of QD localized charges, the capacitive coupling, and the electrochemical properties. <sup>1-3</sup> The floating gate function of QDs has been demonstrated in different material systems such as lithography defined and self-assembled QDs and down to the quantum limit of one electron. <sup>1,8,9</sup> Since self-assembled QDs are randomly distributed, charges on several QDs contribute to the threshold voltage shift. Thus, ensembles of QDs are typically not practical for the study of single electron properties. Therefore, an accurate control of the number of QDs and their relative distances to the gates is necessary.

Here, we report on the realization of a QD flash memory based on a modulation doped GaAs/AlGaAs heterostructure with site-controlled InAs QDs located in the center of a quantum wire. The central QD becomes charged at negative gate voltages. By sampling different gate voltage sweeps with variations in the minimum gate voltage and waiting time, the charge occupation number of the QDs can be controlled in a wide range. A maximal hysteresis width of 6.2 V is found. Time resolved measurements show QD charging times of several seconds.

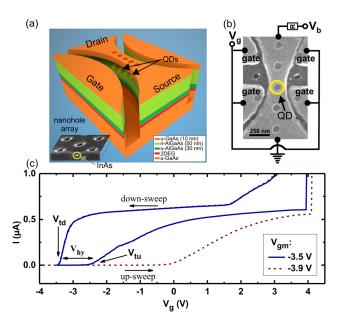

A sketch of the device is shown in Fig. 1(a). The QD floating gate transistor was grown by molecular beam epitaxy in two steps. Starting with an undoped GaAs substrate, 30 nm of undoped Al<sub>0.2</sub>Ga<sub>0.8</sub>As followed by 50 nm of n-doped Al<sub>0.2</sub>Ga<sub>0.8</sub>As were grown in the first growth process. On top of the heterostructure, a 10 nm thick and undoped GaAs layer was deposited. Afterwards, nanohole arrays were processed by electron beam lithography and soft dry chemical etching with a period of 300 nm and a hole diameter of around 100 nm. The depth of the nanoholes is around 50 nm. This results in a 40 nm thick Al<sub>0.2</sub>Ga<sub>0.8</sub>As layer between the

An electron microscope image of the device together with the circuit diagram is shown in Fig. 1(b). The device consists of a transport channel, four laterally defined side gates and site-controlled QDs above the channel. The gate voltage  $V_{\rm g}$ and the bias voltage  $V_{\rm b}$  were applied to the side gates and the top contact, respectively, with the bottom contact serving as common ground. The current was measured as voltage drop across a series resistor with  $R = 10 \,\mathrm{k}\Omega$ . All measurements were conducted at 4.2 K in the dark. The channel width at the smallest constriction is around  $w \approx 210$  nm. The position of the central site-controlled QD is highlighted by a yellow circle. In Fig. 1(c), two current-gate voltage traces  $I(V_g)$  are shown. The gate voltage was swept from a minimum gate voltage  $V_g = V_{gm} = -3.5$  (solid) or -3.9 V (dashed) to  $V_g = 4.5$  V (upsweep direction) and back (down-sweep direction) for a constant bias voltage  $V_{\rm b} = 0.1 \, \rm V$ . The arrows indicate the gate voltage sweep cycle directions and the corresponding threshold voltages  $V_{\rm tu}$  for the up- and  $V_{\rm td}$  for the down-sweep. Starting with a pinched-off channel at  $V_{\rm g} = V_{\rm gm} = -3.5 \, \text{V}$ , the channel opens when the gate voltage passes the threshold voltage  $V_{\mathrm{tu}}$ .

nanohole and the two-dimensional electron gas (2DEG). The diameter of 100 nm was selected because of optimal fabrication parameters, e.g., e-beam lithography resolution and InAs quantum dot formation. In the second growth process, InAs was deposited on the structure, which leads to InAs QDs in the holes. <sup>10</sup> Finally, the InAs QDs were capped with GaAs. A detailed description of the growth technique is given in Refs. 2 and 11. The inset of Fig. 1(a) shows an electron microscope image conducted from a tilted angle of the structure right after the InAs growth. The sample was etched in such a way that the front cuts through a nanohole. The bright spot inside the nanohole corresponds to InAs. After the growth procedure, a Hallbar was realized by optical lithography, wet chemical etching, and alloying of Ni/AuGe/Ni/Au contacts. Finally, the QD floating gate transistor was defined by electron beam lithography in combination with a soft dry chemical etching technique. Dry chemical etching was performed to isolate the gate from the channel area via trenches with a depth of 150 nm.

a) Author to whom correspondence should be addressed. Electronic mail: patrick.maier@physik.uni-wuerzburg.de.

b) Present address: SUPA, School of Physics and Astronomy, University of St. Andrews, North Haugh, KY16 9SS St. Andrews, United Kingdom.

FIG. 1. (a) Scheme of the QD floating gate transistor. It is composed of a 2DEG transport channel, site-controlled InAs QDs, and laterally defined side gates. Inset: An electron microscope image taken from a tilted angle shows a cross section through a nanohole. The bright spot corresponds to InAs. (b) Electron microscope image together with electrical setup of the device. The gate voltage  $V_{\rm g}$  was applied to the four side gates. The bias voltage  $V_{\rm b}$  was applied to the top contact and the bottom contact was used as common ground. The QD located in the smallest constriction of the channel is highlighted by a yellow circle. (c) Current-gate voltage traces  $I(V_{\rm g})$  for  $V_{\rm gm} = -3.5$  (solid) and  $-3.9\,{\rm V}$  (dashed) up to  $V_{\rm g} = 4.5\,{\rm V}$ . The arrows indicate the up- and down-sweep directions with corresponding threshold voltages  $V_{\rm tu}$  and  $V_{\rm td}$  as well as the hysteresis width  $V_{\rm hy}$ .

The current increases monotonically up to about  $V_{\rm g} \approx 4\,{\rm V}$ , at which an almost instantaneous jump of the current occurs. For the down-sweep, the current decreases slightly until it drops to zero when the gate voltage passes  $V_{\rm td}$ . A hysteresis between  $V_{\rm td}$  and  $V_{\rm tu}$  is evident with a hysteresis width of  $V_{\rm hy} = V_{\rm tu} - V_{\rm td} = 0.9\,{\rm V}$ . At  $V_{\rm g} = -2.86\,{\rm V}$ , the current is  $I_{\rm h} = 0.5\,\mu{\rm A}$  in the down-sweep and  $I_{\rm l} = 500\,{\rm pA}$  in the up-sweep. Thus, the onoff current ratio  $I_{\rm h}/I_{\rm l}$  is 1000. One can see when the minimum gate voltage is reduced to  $V_{\rm gm} = -3.9\,{\rm V}$ , that the down-sweep

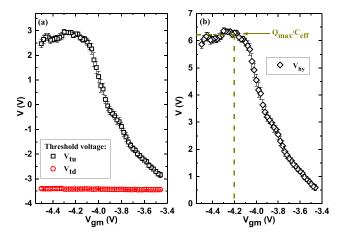

FIG. 2. (a) Threshold voltages  $V_{\rm tu}$  and  $V_{\rm td}$  versus minimum gate voltage  $V_{\rm gm}$ .  $V_{\rm td}$  is independent of  $V_{\rm gm}$ .  $V_{\rm tu}$  shifts from -2.8 to +2.8 V when  $V_{\rm gm}$  is reduced from -3.46 to -4.50 V and saturates below  $V_{\rm gm}=-4.2$  V. (b) Hysteresis width  $V_{\rm hy}$  versus minimum gate voltage  $V_{\rm gm}$ .  $V_{\rm hy}$  reaches a maximum of  $V_{\rm hy}=6.2$  V below  $V_{\rm gm}=-4.2$  V with a maximum charge occupation  $Q_{\rm max}$  on the QD. For  $V_{\rm gm}=-3.46$  V, the width of the hysteresis is still 0.6 V.

trace remains almost unaltered with a similar value  $V_{\rm td}$ , while the up-sweep trace differs significantly.  $V_{\rm tu}$  shifts to higher gate voltages with  $V_{\rm tu}(V_{\rm gm}=-3.9\,{\rm V})=3.3\,{\rm V}>V_{\rm tu}(V_{\rm gm}=-3.5\,{\rm V})$ .

Experimentally determined dependencies of  $V_{\rm td}$  and  $V_{\rm tu}$  on  $V_{\rm gm}$  are shown in Fig. 2(a). The measurements were conducted in the following way.  $V_{\rm gm}$  was first set to a constant value, e.g.,  $-3.46\,\rm V$ . Then, the gate voltage was swept at a constant sweep rate of  $\Delta V_{\rm g}/\Delta t = 0.2\,\rm V/s$  from  $V_{\rm gm}$  to  $V_{\rm g} = 4.5\,\rm V$  and back to  $V_{\rm gm}$ .  $V_{\rm tu}$  and  $V_{\rm td}$  were determined. Such measurements were repeated several times. Each data point in Fig. 2(a) represents the average value of forty closed gate voltage cycles. This procedure was performed for  $V_{\rm gm}$  from  $-3.46\,\rm to$   $-4.50\,\rm V$ . As depicted in Fig. 2(a),  $V_{\rm tu}$  increases from  $-2.8\,\rm to$   $+2.8\,\rm V$  when  $V_{\rm gm}$  is lowered but saturates below  $V_{\rm gm} \approx -4.2\,\rm V$ . In contrast  $V_{\rm td}$  remains constant and is independent of  $V_{\rm gm}$ .

The shift of the threshold voltage  $\Delta V_{\rm tu}$  to higher values for a reduction of  $V_{\rm gm}$  is explained by the charging of the central QD with  $\Delta V_{\rm tu} = \Delta Q/C_{\rm eff}$ . The capacitance  $C_{\rm eff}$ describes the Coulomb coupling between the gate, the QD, and the channel for a given amount of QD localized charge Q = nq. Here, q is the elementary charge and n is the number of electrons. Thus, the  $V_{\rm tu}(V_{\rm gm})$  curve shows that a reduction of  $V_{\rm gm}$  corresponds to an increased amount of electrons on the QD with  $Q \propto V_{\rm gm}$ . Interestingly, the charging process of the QD occurs when the quantum wire is depleted for gate voltages smaller than  $V_{\rm td}$ . We emphasize that the observed charging process at negative gate voltages is in contrast to the typical floating gate function of transistors with a top gate structure, in which charging is observed for positive gate voltages. 1,12,13 The negative charging voltages are attributed to the side-gate geometry. Here, the in-plane gates result in a more efficient shift of the electrostatic channel potential compared to the potential change of the floatinggate. Thus, at negative gate voltages, the electrostatic channel potential exceeds the one of the quantum dot so that the QD becomes charged.

Since  $V_{\rm td}$  is independent of  $V_{\rm gm}$ , the charge on the centered QD remains constant during the down-sweep. The instantaneous jump of the current at the gate voltage  $V_{\rm g} \approx 4\,{\rm V}$  (see Fig. 1(c)) thus corresponds to a pronounced discharging of the QD. Time-resolved measurements show that the discharging process occurs in the  $\mu{\rm s}$  range.

Fig. 2(b) displays the width of the hysteresis  $V_{\rm hy} = V_{\rm tu}$  versus the minimum gate voltage  $V_{\rm gm}$  as obtained from the data depicted in Fig. 2(a). Since  $V_{\rm td}$  is independent of  $V_{\rm gm}$ ,  $V_{\rm hy}$  follows the threshold voltage  $V_{\rm tu}$  of the upsweep. The maximum hysteresis width is  $V_{\rm th} \approx 6.2\,\rm V$  for  $V_{\rm gm}$  smaller than  $-4.2\,\rm V$  and a maximal QD charge occupation  $Q_{\rm max}$  is reached. For  $V_{\rm gm} = -3.46\,\rm V$ , the hysteresis still has a value of  $V_{\rm hy} \approx 0.6\,\rm V$  and the QD is partially charged even for  $V_{\rm gm} \approx V_{\rm td}$ . In contrast to the discharging, which results in the steep current increase, the charging of the QD occurs for a pinched-off channel. Thus, the charging time cannot be extracted directly from the I- $V_{\rm g}$  characteristic.

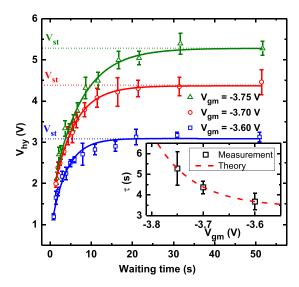

Fig. 3 depicts the waiting time dependence of  $V_{\rm hy}$  for  $V_{\rm gm}=-3.60,\,-3.70,\,{\rm and}\,-3.75\,{\rm V}$ . The waiting time measurements were conducted in the following way. At  $t=0\,{\rm s},\,V_{\rm gm}$  was set and kept constant for a given waiting time. Then, the gate voltage was swept from  $V_{\rm gm}$  to  $V_{\rm g}=4.5\,{\rm V}$

FIG. 3. Waiting time dependence of  $V_{\rm hy}$  for  $V_{\rm gm}=-3.60, -3.70$ , and -3.75 V. For constant  $V_{\rm gm}$  and increasing waiting time,  $V_{\rm hy}$  growths until the saturation voltage  $V_{\rm st}$  is reached. For waiting times of 50 s,  $V_{\rm st}$  increases when the minimum gate voltage is reduced. The solid lines are exponential fit functions according to Eq. (1). Inset: The charging time  $\tau$  decays exponentially with increasing  $V_{\rm gm}$ .

(and back) at a constant sweep rate with  $\Delta V_{\rm g}/\Delta t=0.2~{\rm V/s}$ . For each sweep cycle,  $V_{\rm td}$ ,  $V_{\rm tu}$ , and  $V_{\rm hy}$  were obtained and each data point in Fig. 3 corresponds to the average of five sweep cycles. When the waiting time is varied from 0 to 50 s for  $V_{\rm gm}=-3.60~{\rm V}$ ,  $V_{\rm hy}$  increases from 1.19 V until it saturates at  $V_{\rm hy}(t=50~{\rm s})=V_{\rm st}=3.10~{\rm V}$ . For a reduction of  $V_{\rm gm}$ , the  $V_{\rm hy}$ -waiting time curves behave qualitatively similar but  $V_{\rm st}$  increases to 4.37 ( $V_{\rm gm}=-3.70~{\rm V}$ ) and 5.27 V ( $V_{\rm gm}=-3.75~{\rm V}$ ).

We interpret the time evolution of  $V_{\rm hy}$  in the following way. By setting  $V_{\rm gm}$  at  $t=0\,\rm s$ , the electrochemical potentials of the QD  $\mu_{\rm q}$  and the source contact  $\mu_{\rm s}$  differ with  $\mu_{\rm s}>\mu_{\rm q}$ . The electrochemical potentials then start to align by charging of the QD via electron tunneling from the source contact until  $\mu_{\rm s}=\mu_{\rm q}$ . Fig. 3 thus resembles the time resolved charging of a capacitor and the time evolution of  $V_{\rm hy}$  for each  $V_{\rm gm}$  can be described by <sup>15</sup>

$$V_{hy} = (V_{st} - V_0) \left[ 1 - \exp\left(\frac{-t}{\tau}\right) \right] + V_0, \tag{1}$$

where  $\tau$  is the charging or RC time constant given by the capacitance C and resistance R.  $V_{\rm st}$  is the saturation threshold voltage and  $V_0$  considers dynamic effects of charging. The fit functions of the data from Fig. 3 with Eq. (1) lead to charging times of  $(5.3\pm0.8)$ ,  $(4.4\pm0.3)$ , and  $(3.6\pm0.4)$  s for  $V_{\rm gm}=-3.75$ , -3.70, and -3.60 V, respectively. Remarkably,  $\tau$  is in the order of a few seconds.  $\tau$  versus  $V_{\rm gm}$  is shown in the inset of Fig. 3. One can estimate the tunneling resistance R by  $\tau=RC$ . The capacitance C of the QD is approximated by a planar disk with diameter d=100 nm. With the dielectric constant of AlGaAs  $\varepsilon_{\rm r}=12.3\times\varepsilon_0$  ( $\varepsilon_0$  is the vacuum permittivity) we obtain  $C=4\varepsilon_{\rm r}d=43$  aF.  $^{1.6}$  The corresponding resistances R are 1.2, 1.0, and  $0.8\times10^{17}$   $\Omega$  for  $V_{\rm gm}=-3.75$ , -3.70, and -3.60 V, respectively. According to our observations an increase of the QD diameter would lead to larger capacitances, which in turn increases the charging times. We associated the

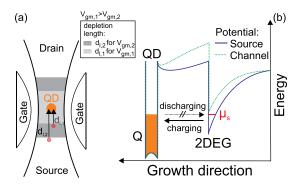

FIG. 4. Schemes of the charging time-gate voltage relation for  $V_{\rm gm,1} > V_{\rm gm,2}$ . (a) The central QD is charged when the 2DEG below the QD is depleted by the applied gate voltage. The electron tunneling distance from the source to the QD is enhanced with  $d_{1,2} > d_{1,1}$  when  $V_{\rm gm,1} > V_{\rm gm,2}$ . The QD is charged over a distance of several 100 nm from the source contact of the device. The discharging of the QD to the channel is blocked, because the electrostatic potential of the channel below the QD (b) is above the electrochemical potential of the QD. This results in a blockade for discharging the QD.

observed charging times  $\tau$  in the order of seconds with huge tunneling resistances. For clarity, Fig. 4 shows schemes of the device from the top (a) and conduction band profiles (b).

The top view image in Fig. 4(a) depicts the depletion region for two minimum gate voltages  $V_{gm,1}$  and  $V_{gm,2}$  with  $V_{\rm gm,1} > V_{\rm gm,2}$ . The depletion length  $d_{\rm l}$  from the center of the QD to the contacts of the wire increases from  $d_{1,1}$  to  $d_{1,2}$ when the gate voltage is reduced from  $V_{gm,1}$  to  $V_{gm,2}$ . We assume that the voltage dependent barrier width can be described by  $d_l = \alpha (V_{gm} - V_{td})$  for  $V_{gm} < V_{td}$  and  $\alpha < 0$ . We further assume that the charging can be explained by tunneling through a single barrier for which the tunneling resistance R is proportional to exp  $(2d\sqrt{2m*\Delta E}/\hbar)$ , <sup>14,17</sup> where d is the barrier thickness which equals  $\sqrt{d_I^2 + (40nm)^2}$ , m\* is the effective mass, and  $\hbar$  is the reduced Planck constant.  $\Delta E$ is the energetic difference between the top of the barrier and the electron energy. Thus, with  $\tau = RC$ , the charging time is proportional to exp  $(\beta(V_{gm} - V_{td}))$ .  $\beta$  accounts for the constants  $\alpha$ , m\*,  $\hbar$ , and  $\Delta E$ . This exponential dependence of  $\tau$  on the gate voltage is shown in the inset of Fig. 3.

In Fig. 4(b), schemes of the conduction band along the growth direction are shown for the source region and the channel below the central QD. The QD becomes charged with electrons from the source contact up to the electrochemical potential  $\mu_s$ . The electrochemical potential of the channel remains constant and thus no free electron states exist directly below the QD as the conduction band minimum is above  $\mu_s$ . Thus, increasing the gate voltage results in free electron states in the channel and the QD becomes discharged at  $V_g \approx 4 \text{ V}$ . At this gate voltage, electrons can overcome the AlGaAs/GaAs barrier at the interface which reduces the tunneling barrier to about 20 nm, which leads to a significantly faster discharging process compared to the charging process. This is reflected in the steep current increase in Fig. 1(c).

To summarize, we have fabricated and measured a QD floating gate transistor based on a modulation doped GaAs/AlGaAs heterostructure with site-controlled InAs QDs. The central QD becomes charged at negative and discharged at positive gate voltages. We observed charging times in the

order of several seconds when the gate voltage is in a critical range between -3.5 and -3.9 V. The presented single QD floating gate transistor may be used to realize low energy consuming memories or logic functions.

The authors gratefully acknowledge financial support from the European Union (FPVII (2007–2013) under Grant Agreement No. 318287 Landauer) as well as the state of Bavaria.

- <sup>1</sup>L. Guo, E. Leobandung, and S. Y. Chou, Science **275**, 649 (1997).

- <sup>2</sup>S. Göpfert, L. Worschech, S. Lingemann, C. Schneider, D. Press, S. Höfling, and A. Forchel, Appl. Phys. Lett. **97**, 222112 (2010).

- <sup>3</sup>C. R. Müller, L. Worschech, and A. Forchel, Phys. Rev. B **79**, 205307 (2009).

- <sup>4</sup>A. Marent, T. Nowozin, M. Geller, and D. Bimberg, Semicond. Sci. Technol. 26, 014026 (2011).

- <sup>5</sup>C. Balocco, A. M. Song, and M. Missous, Appl. Phys. Lett. 85, 5911 (2004).

<sup>6</sup>K. Koike, S. Sasa, M. Inoue, and M. Yano, J. Vac. Sci. Technol., B 21, 710 (2003).

- <sup>7</sup>T. Ohori, Y. Ohno, K. Maehashi, K. Inoue, Y. Hayashi, and K. Matsumoto, Appl. Phys. Lett. **98**, 223101 (2011).

- <sup>8</sup>A. Nakajima, T. Futatsugi, K. Kosemura, T. Fukano, and N. Yokoyama, Appl. Phys. Lett. **70**, 1742 (1997).

- <sup>9</sup>L. Guo, E. Leobandung, L. Zhuang, and S. Y. Chou, J. Vac. Sci. Technol., B **15**, 2840 (1997).

- <sup>10</sup>C. Schneider, M. Strauß, T. Sünner, A. Huggenberger, D. Wiener, S. Reitzenstein, M. Kamp, S. Höfling, and A. Forchel, Appl. Phys. Lett. 92, 183101 (2008).

- <sup>11</sup>C. Schneider, A. Huggenberger, T. Sünner, T. Heindel, M. Strauß, S. Göpfert, P. Weinmann, S. Reitzenstein, L. Worschech, M. Kamp, S. Höfling, and A. Forchel, Nanotechnology 20, 434012 (2009).

- <sup>12</sup>P.-F. Wang, X. Lin, L. Liu, Q.-Q. Sun, P. Zhou, X.-Y. Liu, W. Liu, Y. Gong, and D. W. Zhang, Science 341, 640 (2013).

- <sup>13</sup>B. Marquardt, M. Geller, A. Lorke, D. Reuter, and A. D. Wieck, Appl. Phys. Lett. **95**, 022113 (2009).

- <sup>14</sup>R. Waser, *Nanoelectronics and Information Technology*, 3rd ed. (Wiley, Weinheim, 2012), p. 626.

- <sup>15</sup>R. A. Serway, J. S. Faughn, C. Vuille, and C. A. Bennett, *Enhanced College Physics*, 7th ed. (Thomson Brooks/Cole, Belmont, 2006), p. 605.

- <sup>16</sup>J. D. Jackson, Classical Electrodynamics, 2nd ed. (John Wiley and Sons, New York, 1975), p. 133.

- <sup>17</sup>J. G. Simmons, J. Appl. Phys. **34**, 1793 (1963).