| [54] | CLIPPING POLYGON FACES THROUGH A POLYHEDRON OF VISION |                                                                           |  |  |  |  |

|------|-------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

| [75] | Inventors:                                            | Michel A. Rohner, San Jose; Judit K. Florence, Menlo Park, both of Calif. |  |  |  |  |

[73] Assignee: The Singer Company, Binghamton,

N.Y.

| [21] | Appl. No | o.: 940,818 |    |

|------|----------|-------------|----|

| [22] | Filed:   | Sen 11 1    | 97 |

[56] References Cited

# U.S. PATENT DOCUMENTS

| 3,639,736 | 2/1972  | Sutherland       | 364/723 |

|-----------|---------|------------------|---------|

| 3,816,726 | 6/1974  | Sutherland et al | 364/518 |

| 3,999,308 | 12/1976 | Peters           | 35/10.2 |

| 4,054,917 | 10/1977 | Race             | 35/10.2 |

| 4,152,766 | 5/1979  | Osofsky et al    | 364/515 |

|           |         |                  |         |

Primary Examiner—Felix D. Gruber Attorney, Agent, or Firm—Paul Hentzel; J. Dennis Moore; Jeff Rothenberg

#### [57] ABSTRACT

A flight simulator combines flight data and polygon face terrain data to provide a CRT display at each win-

dow of the simulated aircraft. The data base specifies the relative position of each vertex of each polygon face therein. Only those terrain faces currently appearing within the pyramid of vision defined by the pilots eye and the edges of the pilots window need be displayed at any given time. As the orientation of the pyramid of vision changes in response to flight data, the displayed faces are correspondingly displaced, eventually moving out of the pyramid of vision. Faces which are currently not visible (outside the pyramid of vision) are clipped from the data flow. In addition, faces which are only partially outside of pyramid of vision are reconstructed to eliminate the outside portion. Window coordinates are generated defining the distance between each vertex and each of the boundary planes forming the pyramid of vision. The sign bit of each window coordinate indicates whether the vertex is on the pyramid of vision side of the associated boundary panel (positive), or on the other side thereof (negative). The set of sign bits accompanying each vertex constitute the "outcode" of that vertex. The outcodes (O.C.) are systematically processed and examined to determine which faces are completely inside the pyramid of vision (Case A-all signs positive), which faces are completely outside (Case C-All signs negative) and which faces must be reconstructed (Case B-both positive and negative signs).

18 Claims, 33 Drawing Figures

Jun. 24, 1980

Jun. 24, 1980

Jun. 24, 1980

#### CLIPPING POLYGON FACES THROUGH A POLYHEDRON OF VISION

The invention described herein was made in the per- 5 formance of work under NASA Contract Number NAS9-14910 and is subject to the provisions of Section 305 of the National Aeronautics and Space Act of 1958 (72 Stat. 435; 42 U.S.C. 2457).

#### TABLE OF CONTENTS

BACKGROUND OF THE INVENTION SUMMARY OF THE INVENTION DESCRIPTION OF THE FIGURES GENERAL DESCRIPTION OF FLIGHT SIMU-**LATION SYSTEM 10** DETAILED DESCRIPTION OF INTERFACE CONTROLLER 46 AND THE DATA FORMAT DETAILED DESCRIPTION OF DIGITAL VI- 20 SUAL COMPUTER 12 IMAGE PROCESSOR 42 TRANSLATION STAGE 60 **ROTATION STAGE 62** CLIPPING STAGE 63 PROJECTION STAGE 64 **EDGE STAGE 65 CONTROL LOGIC 70 DISPLAY GENERATOR 44 CLIPPING LOGIC** CONCLUSION **CLAIMS**

#### BACKGROUND OF THE INVENTION

This invention relates to a flight or motion simulator display, and more particularly to continuously clipping 35 data which is currently not within the display area,

Heretofore, clipping of polygon faces outside pyramid of vision has been accomplished by continuously determining the distance or window coordinate between each pair of adjacent vertices within each 40 polygon face, and each boundary plane forming the pyramid of vision. The side of each plane outside the pyramid of vision was negative (non visible) and the side including the pyramid of vision was positive (possibly visible). The sign bits of each window coordinate 45 for each vertex were collected into a single data word-the "outcode". In the case of a square window, each outcode (O.C.) contained four sign bits. In a more recent approach, the clipping of the current face, the O.C. of each vertex was "tested" separately against each of 50 the four boundary plane. Testing is the process of determining whether a vertex is on the plus or minus side of a particular boundary plane, and is accomplished by examining the appropriate sign bit. The O.C. contains sufficient information to determine the visibility of the 55 corresponding vertex. If each bit of the O.C. is positive, then the vertex is within the pyramid of vision and visible. Testing is a procedure for gathering the visibility information. A four sided polygon face tested against a four sided pyramid of vision required 60  $4\times4+(4)=20$  separate tests or examinations. The number of testing steps remained the same for faces entirely within view (Case A) partially in view (Case B) or entirely out of view (Case C). There was no reduction in the number of testing steps for the simple case A and 65 case C±situations. However, more complex faces (and viewing volumes) required a proportionately greater number of tests.

In general case, the number of testing steps Tn required to clip a face was:

$Tn = (Vn) \times (Pn) + (closing tests)$

where

Vn is the number of vertices in the face, and

Pn is the number of clipping planes forming the pyramid of vision

10 This prior art-separate test clipping technique is shown in more detail in U.S. Pat. No. 3,639,736 and U.S. Pat. No. 3,816,726, both to Sutherland; and in an article by Sutherland and Hodgman entitled "Reentrant Polygon Clipping" appearing in "Graphics and Image Printing" (Communications of the ACM), January 1964, Volume

FIGS. 2-7, and 9 are identical to the corresponding Sections and Figures in U.S. patent application Ser. No. 869,210, filed 13 Jan., 1978, by Sullivan et al, entitled "Real-Time Simulation of a Polygon Face Object System as Viewed by a Moving Observer," and assigned to the present assignee.

#### SUMMARY OF THE INVENTION

It is therefore an object of this invention to provide a clipping system which is faster.

It is therefore another object of this invention to provide a face clipping circuit which requires fewer test 30 steps than the product of the number of vertices of the face times the number of boundary planes forming the clipping volume.

It is a further object of this invention to provide a clipping device in which the number of clipping steps is not directly related to the number of clipping planes.

It is yet another object of this invention to provide a clipping circuit which combines certain groups of vertex-plane tests into a single test.

It is another object of this invention to provide a clipping circuit to minimize the number of tests required to close the polygon faces.

It is a further object of this invention to provide a clipping circuit in which each polygon face is processed and closed without repeating the first vertex.

It is yet a further object of this invention to provide a clipping circuit which keeps track of all incompleted intersection point branches developed during the clipping process.

It is another object of this invention to provide a clipping circuit having sets of memory pointers and sign flags assigned to the window-coordinates to reduce the data handling requirements.

It is a further object of this invention to provide a clipping circuit in which the window coordinate memory locations are shared among the plane testing hardware for reducing the number of memory access periods per test to one.

#### DESCRIPTION OF THE FIGURES

Further objects and advantages of the present invention, and the operation of the clipping system, will become apparent from the following detailed description taken in conjunction with the accompanying drawings, in which:

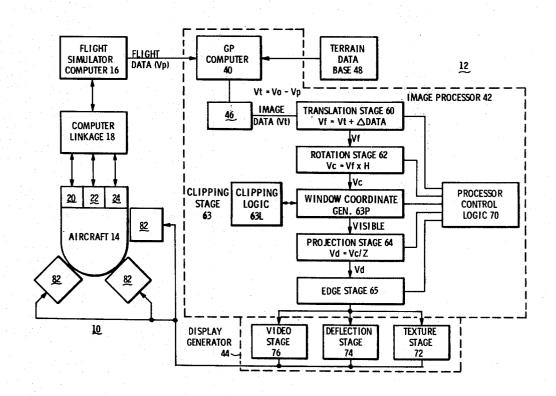

FIG. 1 is a block diagram of DIG visual system 10 and peripheral flight simulation equipment showing the data flow:

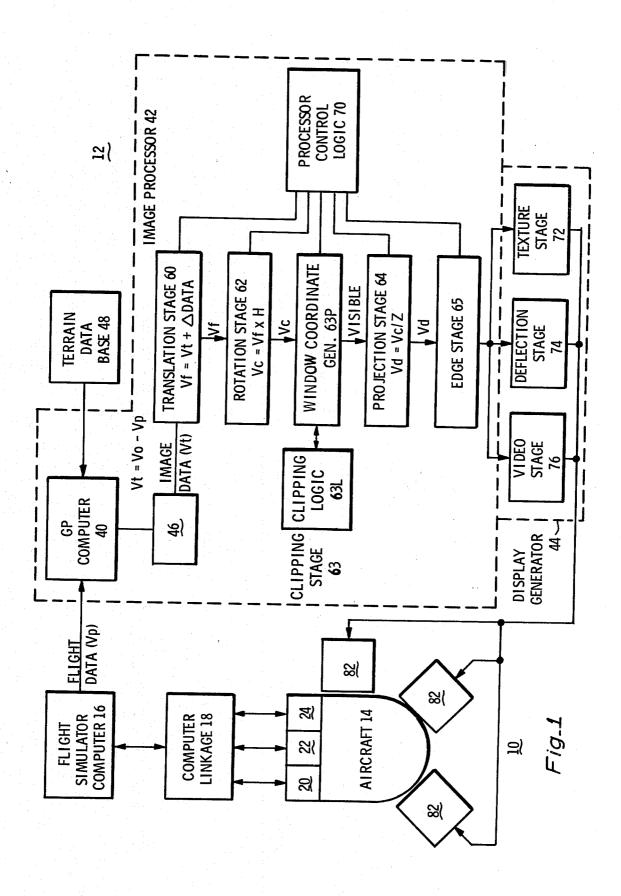

FIG. 2 comprising FIGS. 2A and 2B is a pictorial view of an aircraft and terrain features illustrating image vectors and O.C. regions;

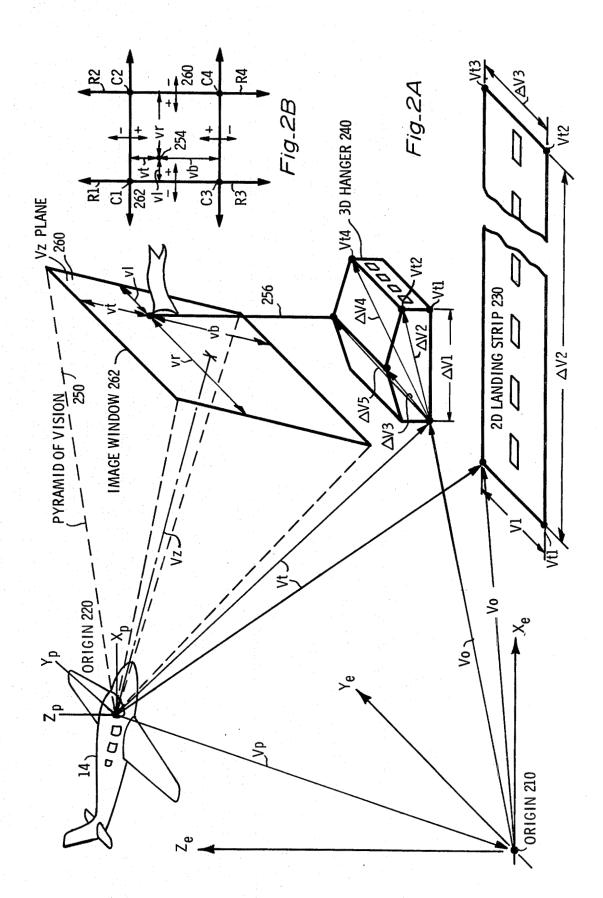

FIG. 3 is a block diagram of translation stage 60 wherein the delta data is translated into face vertex 5 vectors Vf;

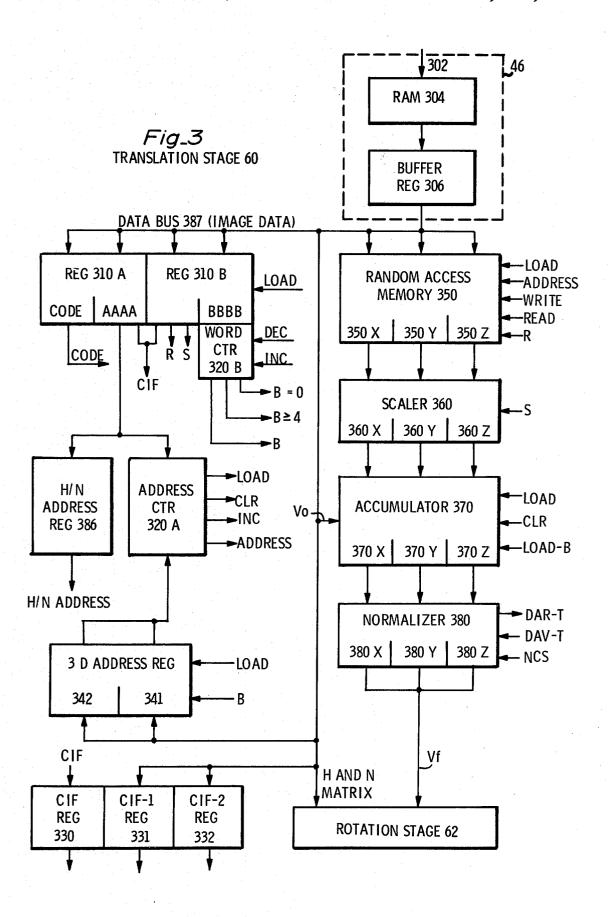

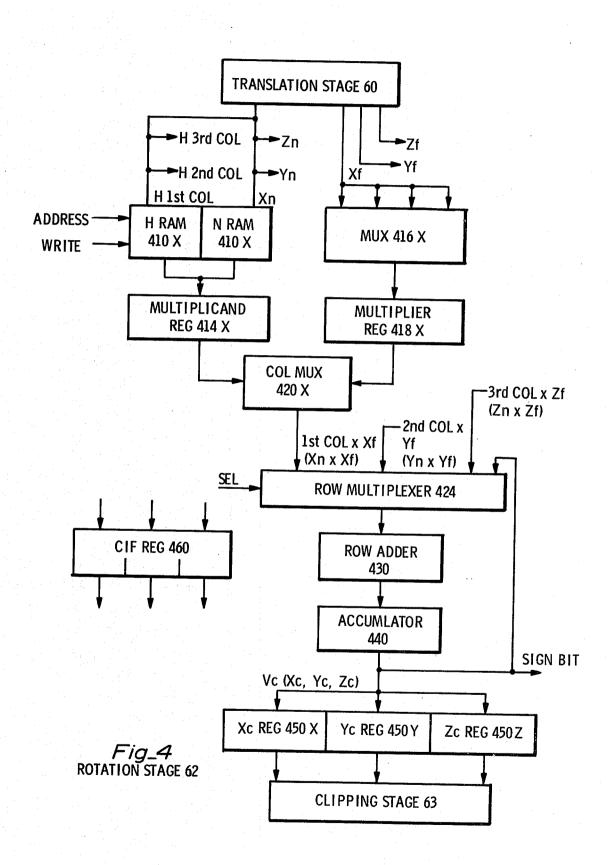

FIG. 4 is a block diagram of rotation state 62 wherein each Vf is multiplied by an H matrix:

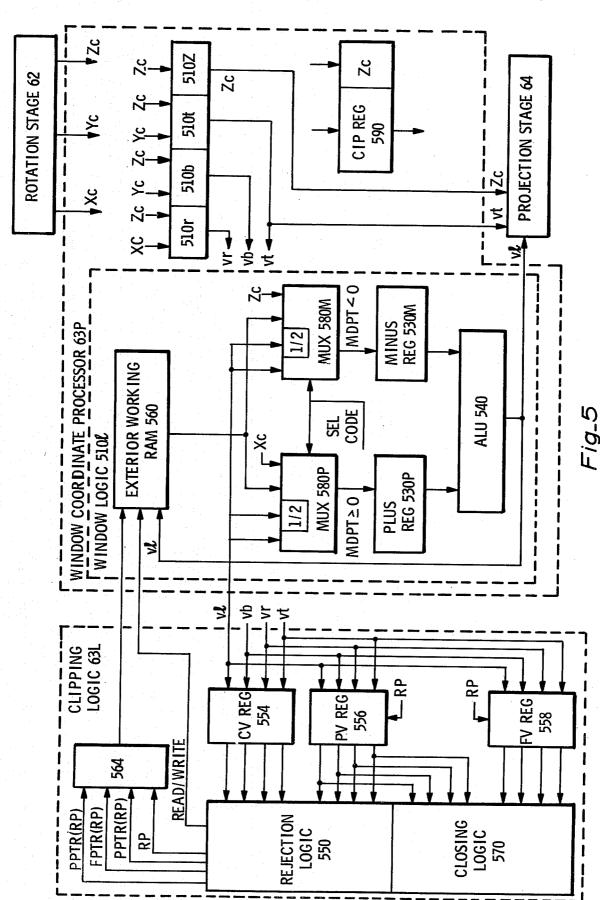

FIG. 5 is a block diagram of clipping stage 63 which eliminates image data outside the field of vision;

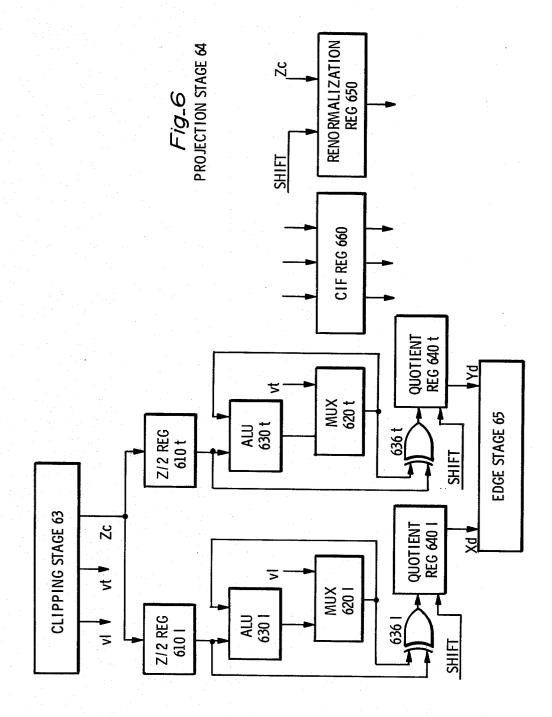

FIG. 6 is a block diagram of projection stage 64 wherein Xc and Yc are divided by Zc to project Vc into the display plane;

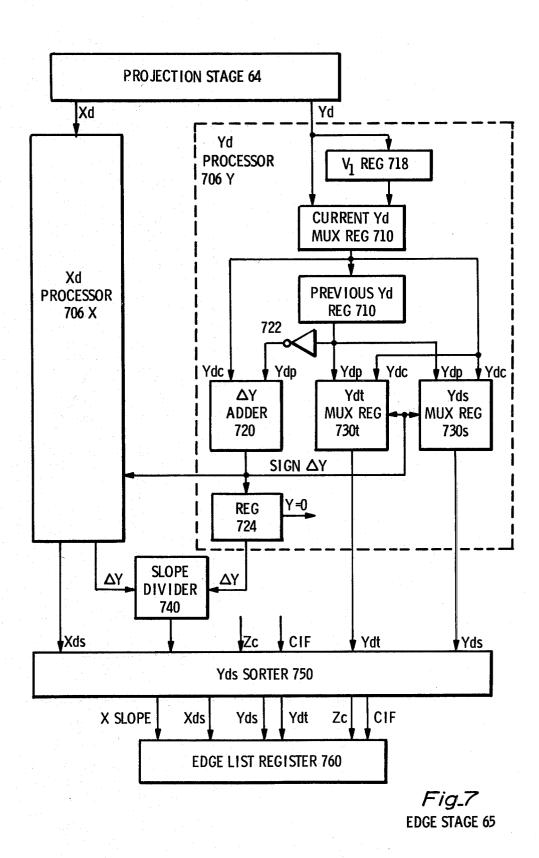

FIG. 7 is a block diagram of edge stage 65 which identifies the edges of each polygon face and the slopes 15 thereof:

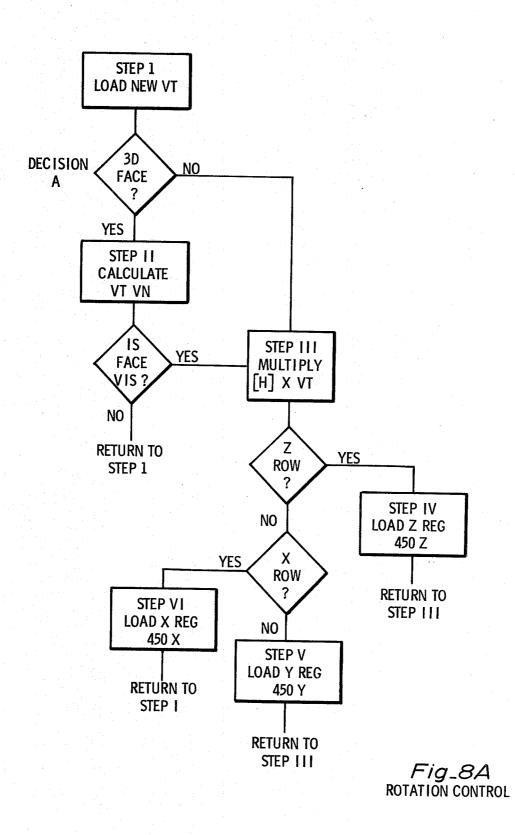

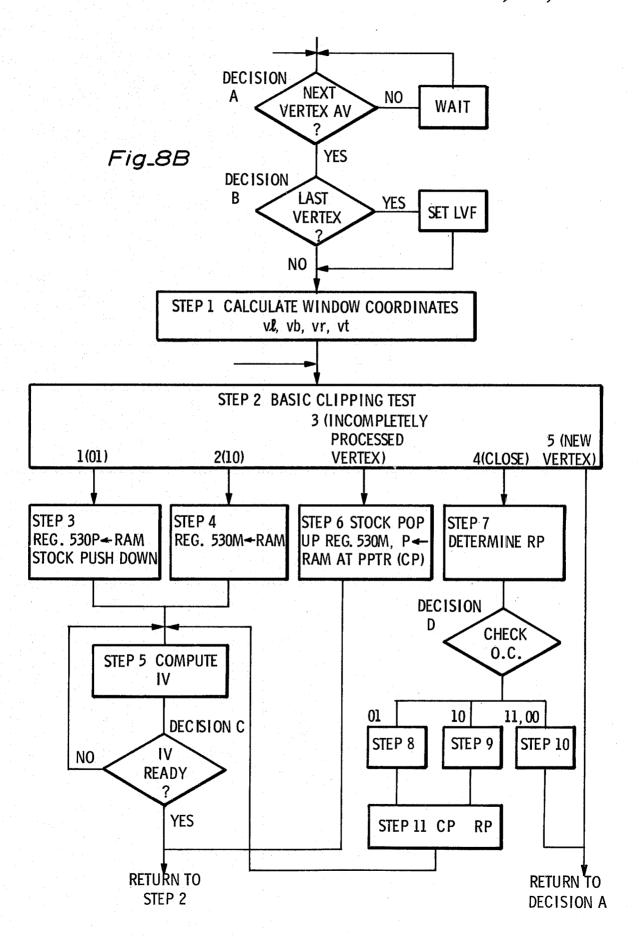

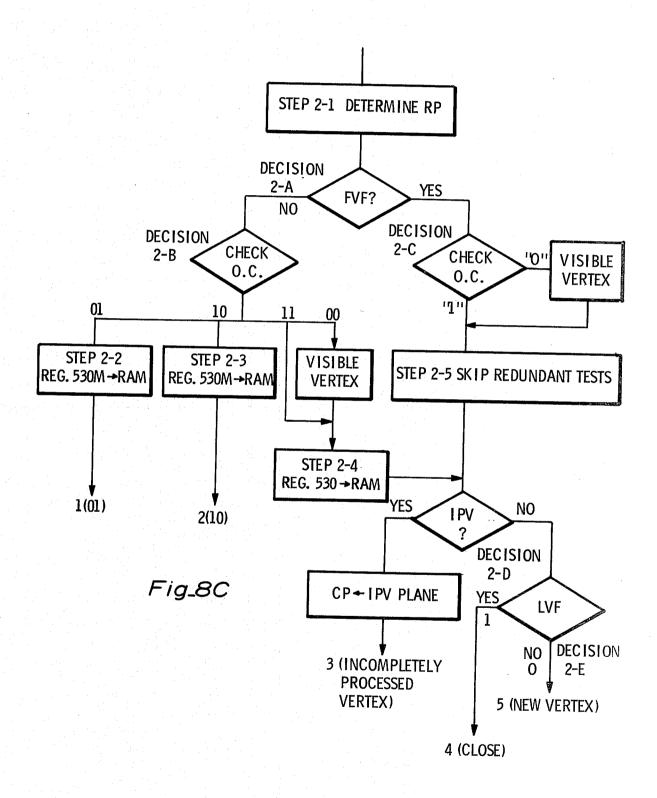

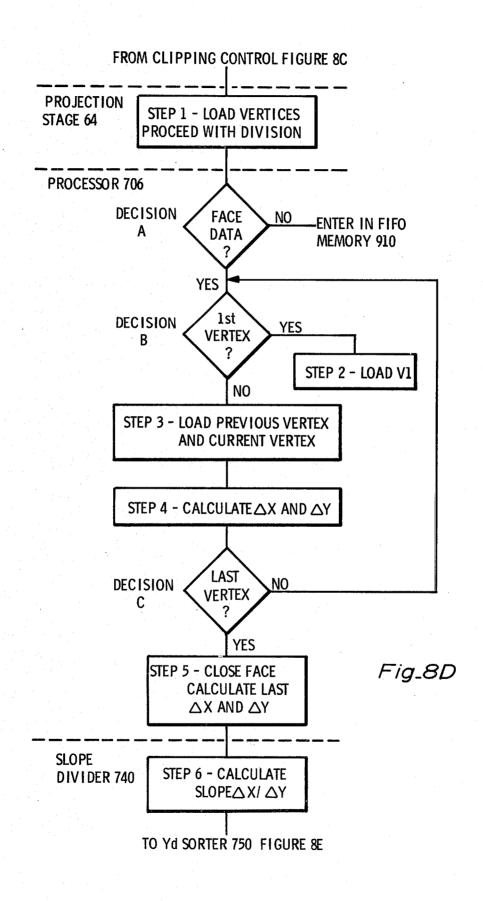

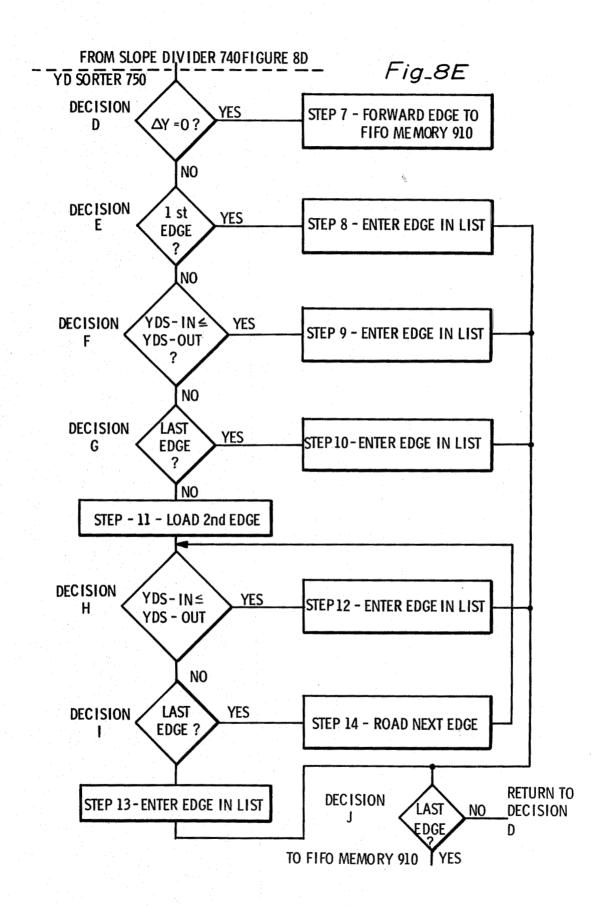

FIG. 8 comprising FIGS. 8A-8E is a logic diagram of processor control logic 70;

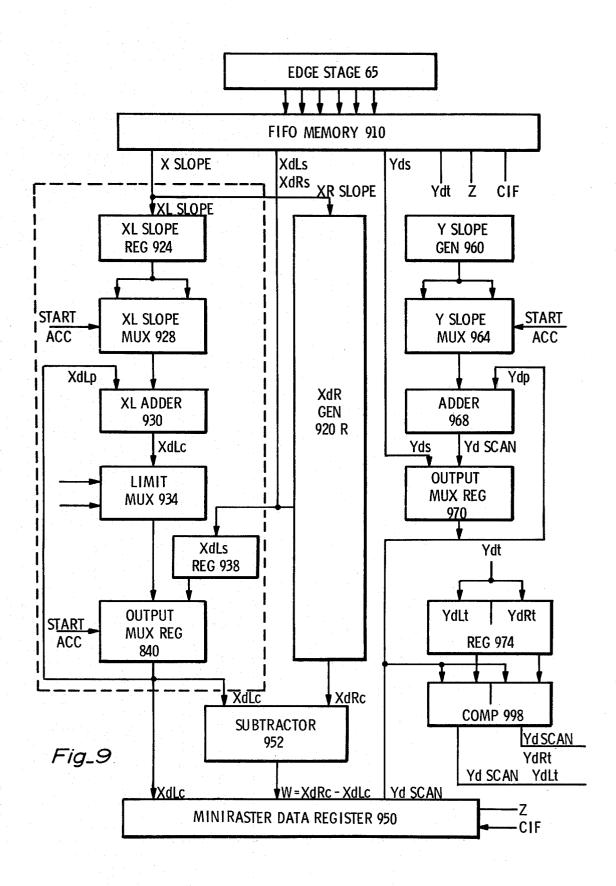

FIG. 9 is a block diagram of miniraster calculator 72 which provides the starting points and widths of each 20 scan line;

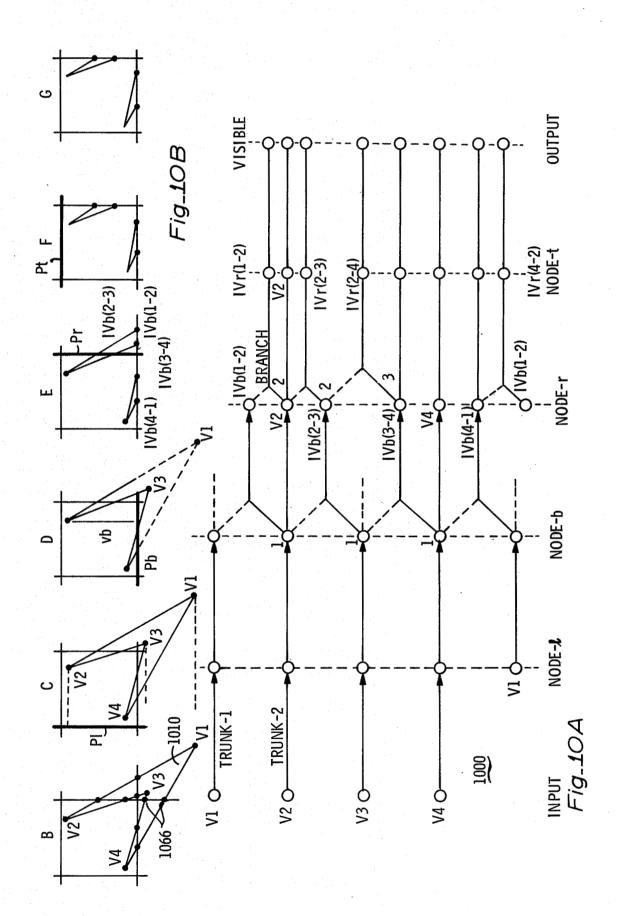

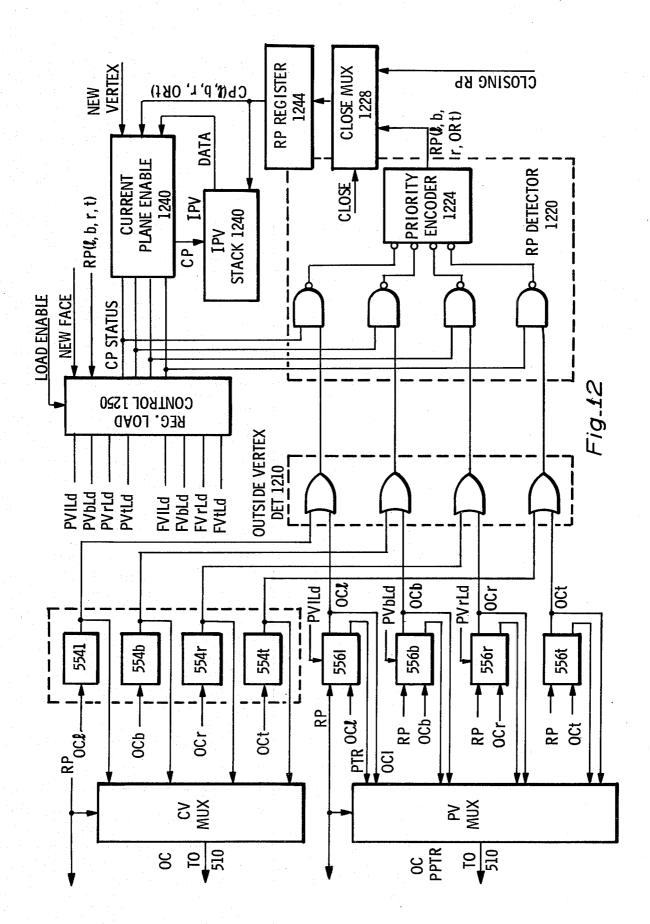

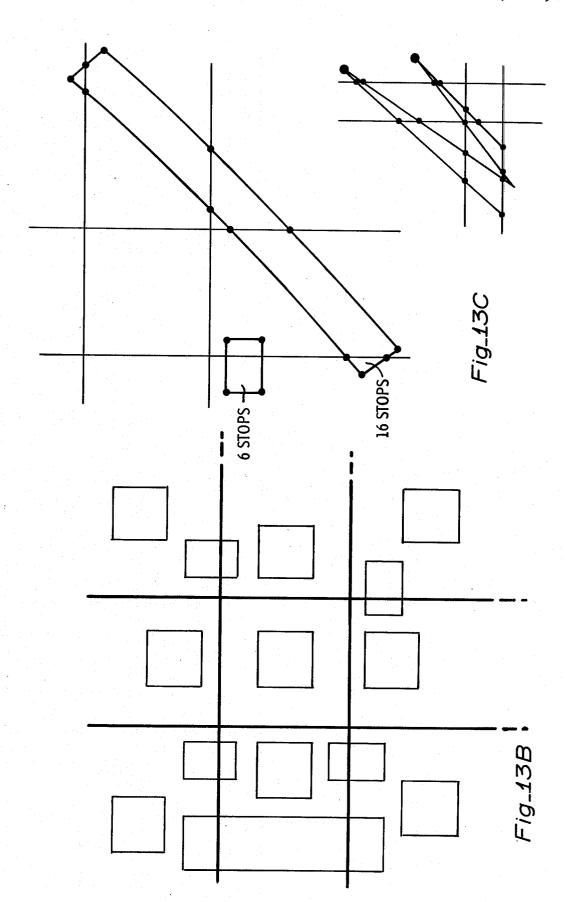

FIG. 10 comprising FIGS. 10A-10G is a clipping logic tree with accompanying face-outcode diagrams;

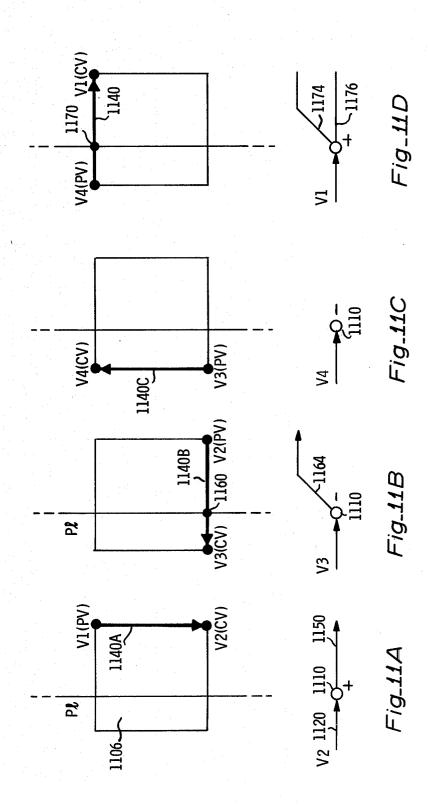

FIG. 11 comprising FIGS. 11A-11D is a diagram and a plane;

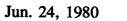

FIG. 12 is a block diagram of rejection logic 550 showing a plane testing circuitry; and

FIG. 13 comprising FIGS. 13A-13G is the logic tree of FIG. 10 showing each step of the clipping procedure. 30

#### GENERAL DESCRIPTION OF FLIGHT SIMULATION SYSTEM 10

FIG. 1 shows flight simulation system 10 with visual capabilities provided by a digital visual system 12. A 35 simulated aircraft 14 is linked to flight simulation computer 16 and visual system 12 through computer linkage 18. Flight computer 16 controls motion system 20 and instrument system 22 of aircraft 14 in response to the pilot's maneuvering action at aircraft controls 24. Vi- 40 sual system 12 is formed by general purpose computer 40 (such as Digital Equipment Corporation PDP 11/25) plus image processor 42, display generator 44. Interface controller 46, within image processor 42, is provided to process flight data from aircraft 14 to translation stage 45 60, and to control image data flow from GP computer 40 to image processor 42 via a data buffer.

GP computer 40 receives flight data, such as aircraft position Vp, aircraft roll, pitch, and yaw attitude (H matrix), etc., from computer 16. GP computer 40 addi- 50 tionally receives terrain data (both natural formations and cultural structures) from data base 48 such as runways, towers, hangers, roads, rivers, fields, moving objects, etc. In general visual system 12 may process and display terrain features consisting of points, lines 55 closed polygons, or combinations thereof. Preferably the aircraft position data is an aircraft position vector VP extending from the simulated position of aircraft 14 to the origin of the terrain coordinate system (see FIG. 2). In order to simplify conception and data organiza- 60 tion, the terrain origin is located proximate the touchdown area of the runway, and the x axis of the terrain coordinate system from data base 48 is coincident to the runway centerline. An updated Vp is supplied each frame period by flight simulation computer 16 as the 65 flight parameters of aircraft 14 change. The earth data also includes the position of certain landmark points (Vo) such as the first vertex of each face, and the rela-

tive position of the points forming other terrain feature (delta data). Translation stage 60 subtracts Vp from each Vo to form translated vectors (Vt=Vo-Vp). Translation stage 60 then combines the delta with the appropriate Vt to provide the remaining face vertex vector Vf for each face (Vf=Vt+delta data). Rotation stage 62 compensates each Vf for changes in aircraft 14 orientation (pitch, roll, and yaw) for each window (channel) and forwards Vc to clipping stage 63. Faces

which are not visible to the pilot because they are outside his field of vision are eliminated from the data flow within image processor 42 by clipping stage 63. In addition, clipping stage 63 reconstructs partially visible faces and forwards only the visible portion thereof to projection stage 64. Projection stages 64 projects the three-dimensional Vc into two-dimensional display coordinates or vectors Vd. Edge stage 65 provides a list of visible edges defined by the end points and the slope. The data flow through image processor 42 and the mode of operation thereof is controlled by processor control logic 70.

Texture stage 72 within display generator 44 receives the visible edge list for coordination with the display raster. Deflection stage 74 provides the required analog showing four possible clipping results between a line 25 deflection voltages to CRT display devices 82. Video stage 76 receives the color, intrinsic intensity and size portion of the data for controlling the CRT beam voltage, current and focus. The CRT in device 82 is preferably a beam penetration, random deflection tube which allows precise control of spot position, continuous control of spot focus and diameter, and provides at least two phosphors of different colors.

#### DETAILED DESCRIPTION OF INTERFACE CONTROLLER 46 AND THE DATA FORMAT

GP computer 40 has an in-core, buffer memory which accumulates blocks of image data required to form each display frame. The in-core buffer contains initialization points (Vo) and delta data from data base 48 plus each new position vector Vp and rotational matrix (H) as they are computed by flight computer 16.

The inage data accumulating in the in-core buffer is periodically transferred as a data block to hardware RAM buffer 304 in interface controller 46. Controller 46 processes the data words sequentially to image process or 42 while GP computer 40 simultaneously assembles the next data block in the in-core buffer for the next data handshake with RAM 304. The accumulation of data blocks in GP computer 16 and the handshake data transfer to RAM 304 is outlined in the following four operations:

#### Operatin I-Preflight Load-Data Base 48 to Core Memory

Prior to each training flight, the content of data base 48 is loaded into computer 40 core-memory. Image data from data base 40 includes sixteen control words (0000-1111) having bit formats as described hereinafter, initialization data Vo, delta data, etc.

#### Operation II-Aircraft Orientation Update

The in-core memory is updated periodically with the most recent aircraft orientation angles roll, pitch and yaw (H matrix data) from flight computer 16. Preferrably, this aircraft update occurs once each frame. The H matrix data is received by computer 40 as the sine and cosine of each of the three orientation angles—six items of data. The software of computer 40 responds to the

orientation data to form the rotational matrix H described in the specification (Section IX). The software merely calculates the proper sine-cosine products to form a  $3\times3$  matrix for each angle, and multiplies the three  $3\times3$  matrices together to generate the nine elements of the rotational matrix H. These nine elements are generated each frame and inserted into RAM 304 at the proper place. The nine elements of rotational matrix H preferrably occupy the lead position in the corememory because the rotational perspective must be developed by rotation stage 62 each frame prior to displaying any of the object faces on display 82.

#### Operation III-Aircraft Position Update

The core-memory update also includes the most recent aircraft position vector Vp which latter forms a series of initialization vectors Vo in translation stage 60.

# Operation IV—Handshake Between Core-Memory and RAM 304

As required the contents of the core-memory matrix are serially transferred to RAM 304 in interface controller 46, starting with the nine rotational elements.

The four above described operations involve simple software steps. Operations I, III, and IV are merely data transfer steps. Operation II involves forming a triple  $3\times3$  matrix product, a mathematical operation which is well understood. Subroutines are available to execute this systematic multiplication.

#### FORMAT SUMMARY

The data format is formed by groups of data words which describe the nature and position of each object feature, and spaced instruction words for identifying the type of data in the immediately subsequent group of data words. The MSB bits of each instruction word are coded to define the particular instruction contained in the word, and the remaining bits concern the subsequent data. In the embodiment shown, a sixteen bit 40 format is employed. The four MSB define the instruction and are decoded by processor control logic 70 to control the flow of data through image processor 42. The four LSB of each instruction word reveal the number of subsequent data words in the data word group to 45 be processed under that instruction word. Each instruction word is loaded into registers 310A and 310B by control logic 70 in due course, and the immediately subsequent group of data words is loaded into RAM

#### FIVE LOAD INSTRUCTIONS (0-4)

Each load instruction transfers point coordinates from buffer 306 into RAM 350 as follows:

# LDA (4) 0 1 0 0 A A A A R R B B B B

Load A instruction causes the subsequent group of B sets of X, Y, Z coordinates to be stored in RAM's 350X, 60 350Y, and 350Z, beginning at address A. The first coordinate (one of two sixteen bit words) is stored in the RAM 350X, the second in the RAM 350Y, and the third in the RAM 350Z. This sequence is repeated until B sets of coordinates have been loaded starting at address A. R 65 specifies the significance of the bits in the subsequent sixteen bit data words for coordinating the distribution thereof across the 24 bits of RAM's 350.

Normal 24 bit resolution (R=3) requires two subsequent data words. The first word provides the sixteen LSB to RAM's 350 and the second word provides the 8MSB to RAM's 350. Vp and Vo data require the full 24 bits and therefore are preceded by an LDA instruction word with R=3. The LSB of Vp preferably corresponds to \{\frac{3}{8}} of an inch to eliminate detectable jitter of the scene from frame to frame. A new Vp is calculated by FS computer 16 each frame, and the round-off error in the LSB of Vp causes the entire earth coordinate system to jump a ground distance equal to the LSB. This interframe displacement (motion resolution) is minimized and rendered indetectable to the pilot trainee by providing aircraft position vector (Vp) resolution at the 3 inch level. The LSB of Vo is preferably small in order to accurately position detailed structure within a terrain feature (positional resolution). In the embodiment shown, Vo LSB also equals § inch because image processor 42 is already required to handle the 3 inch bit in order to prevent interframe displacement. That is, the position resolution may have the same value as the motion resolution as in the embodiment shown; but it is not required that the two resolutions be equal. However, a 3 inch Vo position resolution permits moving objects such as other airplanes and ground vehicles to be viewed without interframe displacement. The MSB of both Vp and Vo is 262,144 feet forming a cubic gaming volume in data base 48 which is 262,144 feet on an 30 edge.

Fine 16 bit resolution (R=1) requires a single subsequent 16 bit data word of delta data which is entered into the 16LSB of 24 bit RAM's 350 (bits 16-23 are loaded with the sign bit 15). The MSB corresponds to 1024 feet (when  $LSB=\frac{3}{8}$  inch). The fine 16 bit resolution may be used to process the vertices of small terrain faces (largest dimension less than 1024 feet) which is associated with high resolution detailed structure.

Coarse 16 bit resolution (R=2) requires a single 16 bit subsequent data word of delta data which is entered into the 16 MSB of 24 bit RAM's 350 (bits 0-7 are loaded with "0"s). The MSB=262,144 feet and LSB=8 feet. The coarse 16 bit resolution may be used to process the vertices of large terrain faces in which the dimensions have been rounded off to multiples of eight feet. While the size resolution of these faces is eight feet, they are positioned with the same resolution as the associated Vo.

# LXY (3) 0 0 1 1 A A A A R R B B B B

Load XY instruction causes the subsequent group of B pairs of X and Y coordinates to be stored in the RAM 350X and RAM 350Y, beginning at address A. "O"s are stored in the corresponding addresses of the RAM 350Z. The data format is one or two 16 bit words of X data followed by one or two words of Y data. This 60 sequence is repeated until B pairs of X-Y coordinates have been loaded into RAM's 350X and 350Y. The R codes are the same as for LDA.

#### LDX (0) 0000AAAARR BBBB

Load X instruction causes the subsequent group of B X coordinates to be stored in the XT RAM 350X begin-

25

ning at address A. Zeros are stored in the corresponding addresses of RAM's 350Y and 350Z.

# LDY (1) 0 0 0 1 A3 A2 A1 A0 R R B3 B2 B1 B0

Load Y instruction is the same as LDX except that the data is stored in RAM 350Y and "0"s are stored in the corresponding addresses in RAM 350X and RAM 350Z.

#### LDZ (2) 0010 A A A A R R B B B B

Load Z instruction is the same as LDX except that the data is stored in the RAM 350Z and "0"s are stored in corresponding addresses of RAM's 350X and 350Y.

#### FIVE RECALL INSTRUCTIONS (5-9)

Recall instructions load the first vertice Vo of each face into RAM's 350 and initiates generation of the associated face.

# RCA (9) 1001AAAARSSSBBBBB

Recall A instruction causes the single subsequent set of coordinates for the first vertice of a face, which typically is also an initialization vector Vo, to be loaded into the first location of RAM 350X, RAM 350Y, and 350Z. The other vertices of the current face have already been entered into RAM's 350 in CCW order as 16 bit coarse or fine data under one of the load instructions (0-4). These other vertices B are now recalled in CCW order from RAM's 350 beginning with address A of RCA. Normal 24 bit resolution (R=3) and coarse 16 bit resolution (R=2) have been previously described. S is a scale factor. When S=7, the current face is displayed 40 full size. As S decreases the size of the current face is reduced by factors of 2.

#### RXY(8) 1000 A A A A R SSS BBBB

Recall XY instruction causes the single subsequent set of first vertice Vo coordinates to be loaded into the first address of RAM 350X and then the first address of RAM 310Y. RAM 350Z is unaffected. The face generation then proceeds as described under RCA.

#### RCX(5) 0101AAAARSSSBBBB;

Recall X instruction causes the single subsequent X coordinate of the first vertice Vo to be loaded into the first address of RAM 350X. RAM's 350Y and 350Z are unaffected.

# RCY(6) 0110 A A A A R SSS B B B B

Recall Y instruction causes the single subsequent Y 65 coordinate of the first vertice Vo to be loaded into the first address of RAM 350Y; RAM's 350X and 350Y are unaffected.

#### RCZ(7) 0111 A A A A R SSS B B B B

Recall Z instruction causes the single subsequent Z coordinate of the first vertice Vo to be loaded into the first address of RAM 310Z; RAM's 350X and 350Y are unaffected.

### RCL(10) 1010 A A A A S S B B B B;

Recall Load instruction does not load any new data into RAM's 350 but is the same as RCX in other respects. RCL is used to hold the previous Vo in order to construct another face contiguous with or proximate to the previous face using the previous Vo as the first vertice or a landmark point for establishing the position of the vertices of the contiguous face.

#### OTHER INSTRUCTIONS

Color Intensity Flag instruction is followed by B additional words, i.e.,

which define the visual characteristics of each data base feature (face, line, or point). The visual characteristic of certain cultural objects such as signal beacons and runway lamps are a function of viewing direction and require directional data. SEL AXIS identifies the viewing axis to which the CIF data pertains:

SEL AXIS=00: the color and intensity of the object is uniform in all directions—ordinary object.

SEL AXIS=01: the color of the object depends on the direction of viewing along the X axis—bidirectional object.

SEL AXIS=10: bidirectional along Y axis. SEL AXIS=11: birdirectional along Z axis.

S± (SIGN±) identifies the direction of view of the object along the axis identified by SEL AXIS. COLOR± identifies the color of the object when viewed from the S+ direction, and COLOR— identifies the color of the object when viewed from the S— direction. COL SEL permits ordinary non-direction features to be displayed in a color from COLOR+ (COL SEL=0) or from COLOR— (COL SEL=1). I (INTENSITY) determines the intensity of the data base feature. When only an intensity change is required to display the current object, only CIFO (B=0) is employed. OBJ CODE identifies the type of object to be

OBJ CODE = 000: 3 dimensional face (a face having a vertical component). Most 3D faces form part of a 3 dimensional object such as the side or top of a building.

= 001: Spare.

recalled:

= 010: Spare.

= 011: Face to line, such as runway stripes which narrow down to a line with distance.

#### -continued

| = 100: |                                   |  |

|--------|-----------------------------------|--|

| = 101: |                                   |  |

|        | Light point.                      |  |

| = 111: | 2 dimensional face, a completely  |  |

|        | horizontal face in the X-Y plane. |  |

The use of Recall instruction as illustrated in FIG. 2a is different for two dimensional faces on the X-Y ground plane (which always face the observer) and 10 faces of a 3 dimensional object (which are sometimes occluded), as illustrated in FIG. 2. Two dimensional faces are identified by a 2 D face object code in the previously loaded CIFI data. RCX computes the vertices of each face by starting with the X, Y, Z coordinates of Vo stored in the first address of RAM's 350 and combining additional vector coordinates from RAM's 350 starting at address A. B is the number of vertices in the face, and, since Vo is the first vertex, B-1 additional vectors (Delta V1, Delta V2, . . . Delta VB-1) are required to generate the other vertices. The vertices are always stored and retrieved in counter-clockwise order. Three dimensional faces are identified by a 3 D object code. Vo is not used as a vertex for 3 D faces, so that B additional vectors (Delta V1, Delta V2, ... Delta VB) are required to display a face having B vertices. The RAM addresses containing the additional vector coordinates for 3 D faces are provided by one or two data words 3DV1 and 3DV2 following the X data word or words. Each additional vector in 3 D recall describes the position of a vertex with respect to Vo as opposed to a 2 D recall, in which each additional vector describes the position of a vertex with respect to the previous vertex. The address format for additional 3 D vectors in **RAM 350 is**

|    | 15 | <u> </u> | VR |    | VR  |       | VR |    | VR 0 | 1 1 1 1 1   |   |

|----|----|----------|----|----|-----|-------|----|----|------|-------------|---|

| V1 | D  | D D      | D  | СС | СC  | ВВ    | BB | A  | AAA  | first word  |   |

| 1  | 5  | VR       |    |    | VR_ |       | VR |    | VR 0 |             |   |

| V2 | ΙH | нн       | G  | GG | GI  | 7 F I | F  | ΕĒ | EE   | second word | 1 |

If the face has four or fewer vertices, only the first word is used. The order in which the RAM 350 addresses are used to reverse alphabetical. For example, when recalling a face having five vertices, the first vertex will be computed using the vector stored at E. The last vertex is always stored at A. A in the RCX instruction is also the address of the normal vector stored in normal RAM 440N. The normal vector is used to test the visibility of a face and must have been previously loaded in normal RAM 440N using a LDN instruction (described hereinafter). Scale factor is the same for a 3 D face as for a 2 D face.

FB identifies data fed back for CRT correction to eliminate ballistic nonlinearities and provide a true display.

IOS identifies data displayed on the instructor's monitor 28 only.

VER RES determines the scan line density (vertical display resolution in horizontal lines per vertical scan).

| VER RE | ES | = 000: | 128 lines low resolution for rapidly                                                     |  |

|--------|----|--------|------------------------------------------------------------------------------------------|--|

|        |    |        | painting structureless large areas<br>such as the sky with a defocused<br>electron beam. |  |

|        |    | = 001: | 256                                                                                      |  |

|        |    | = 010: | 384                                                                                      |  |

|        | -contin       | uea                        |

|--------|---------------|----------------------------|

| = 011: | 512           |                            |

| = 100: | 640           |                            |

| = 101: | 768           |                            |

| = 110: | 896           |                            |

| = 111: | 1024 lines hi | gh resolution for painting |

# LCD(15) 15 12 11 87 0 | CCCCCCC

detailed objects

Load Correct Data instruction enters C vertices with corrected CRT coordinates.

# STG(12) II 100 A A A A CCCCCCCC

Control String instruction causes the display of string of C equally spaced lights or four-sided two dimensional faces, depending on the CIF1 OBJ CODE. The first light of a string is displayed at the Vo+A position and a spacing vector stored at A+1 is used to fix the position of the second light and all successive lights until C lights have been dislayed. The first vertex of the first face of a string of faces is displayed at the Vi+A position and the other three vertices are found successively adding the vectors stored at RAM's 350 addresses A+1, A+2, and A+3. The vector stored at A+4 locates the first vertex of the next face with respect to the last vertex of the current face.

Control Load H instruction loads the H rotation matrix on data bus 307 into RAM 410H in rotation stage 62. The elements of the rotation matrix are in 16 bit 2's complement form, and each address of RAM 410H will store three elements. The rotation matrix multiplies the translated X, Y, and Z coordinates in the following form:

$$\begin{bmatrix} h11 & h12 & h13 \\ h21 & h22 & h23 \\ h31 & h32 & h33 \end{bmatrix} \begin{bmatrix} XT \\ YT \\ ZT \end{bmatrix} \begin{bmatrix} XR \\ YR \\ ZR \end{bmatrix} = h11 & XT + h12 & 1/T + h13 & ZT \\ = h21 & XT + h22 & YT + h23 & ZT \\ = h31 & XT + h32 & YT + h33 & ZT \end{bmatrix}$$

The element data follows the LDH instruction in the following order:

h31, h32, h33, h21, h22, h23, h11, h12, h13.

The matrix is always stored in the first three addresses of RAM 410H, so A=0, the initial address and B=3, the number of matrix rows. C is the channel number associated with rotation matrix.

Control Load N instruction loads B face normal vectors on data bus 307 into normal vector RAM 440N in rotation stage 62, starting at address A. Each vector consists of three 16 bit data words in order Nx, Ny, Nz. The Control Load N will therefore always be followed by three B words of data. Each address in normal RAM 410N is associated with a three dimensional face of

identical address in RAM's 350. Both RAM's are addressed during the Control Recall of a 3 D face.

#### DETAILED DESCRIPTION OF DIGITAL VISUAL COMPUTER 12

Each stage of digital visual system 12 is shown in detail in FIGS. 3 through 9. Preferred embodiments are disclosured at the detailed logic level. Each component is described by function, input-output characters, or conventional nomenclature to enable one skilled in the 10 arts of simulation, digital design, and computer programming to practice the invention. The components are additionally designated by the manufacturer's IC type number from the following integrated circuits data books:

Texas Instruments Incorporated "The TTL Data Book of Design Engineers" First Editiion, Copyright 1973

National Semiconductor Corporation "Digital Integrated Circuits" January 1974

Advanced Micro Devices Inc. 1974

unless otherwise secified. Further, many inverters are employed throughout CDIG system 10 for buffering signals with multiple loads. These buffer inverters are 30 type 74S04 unless otherwise stated.

# TRANSLATION STAGE 60 **GENERAL OPERATION**

FIG. 3 shows translation stage 60 of image processor 35 42 and a portion of controller 46. Controller 46 receives image data in sequential order from computer 40 at input 302 of random access memory 304. The image data is arranged in data blocks M bits wide and N words long, which in the embodiment shown is  $16 \times 1024$ . 40 RAM 304 periodically handshakes with a core memory in GP computer 40 to reproduce each block of data. Image data is sequentially transferred from RAM 304 through a buffer register 306 to image data bus 307 in response to load pulses from interface controller 46.

Each instruction word on bus 307 is loaded into instruction registers 310 A and B which forwards the code bits (four MSB's) to control logic 70. Control logic 70 then selectively activates the remaining blocks of translation stage 60 for processing the subsequent B 50 words of data appropriately. Load instructions (0-4) cause control logic 70 to send WRITE to RAM's 350, which then writes the subsequent B data words starting at ADDRESS A. Counter 320A increments AD-DRESS A while counter 320B decrements down from 55 B. When the B count expires, B=0 is forwarded to logic 70 and the next instruction is loaded into instruction registers 310.

Vp is loaded into RAM's 350 by a Load A instruction (R=3) immediately after each handshake, and Vp is 60 always positioned at the same address (address 1). Next, B words of delta data vectors is entered by another load

Recall instructions (5-9) load the Vo associated with the previously loaded B words of delta data. Each Vo is 65 positioned at the same address in RAM 350 (address 0). The recall instruction causes control logic 70 to forward READ to RAM's 350, and the B words of delta

delta are recalled from RAM's 350 and processed through the remainder of translation stage 60.

CIF instruction causes control logic 70 to forward LOAD to CIF register 330 to receive SEL AXIS, SIGN±, and Intensity data from instruction registers 310. B subsequent data words are entered into CIF-1 register 331 an CIF-2 register 332 where the CIF data is temporarily held. The CIF data is advanced into corresponding CIF registers 460 in rotation stage 62 as Vf data enters rotation stage 62 from normalization register

Three dimensional vertex registers 341 and 342 receive the addresses of vertices of 3 D faces in RAM 350. The addresses in registers 341 and 342 address RAM's 350 via address counter 320A.

RAM's 350 write image data from interface controller 46 after load instructions and read image data after recall instructions. RAM's 350 temporarily store Vp 20 and delta V's until the associated Vo is entered permitting the faces to be generated.

Scalers 360 (X, Y, and Z) control the size of the displayed image by expanding or contracting the X, Y, and Z position coordinates by factors of two. S data from "Advanced Micro Devices Data Book" Copyright 25 register 310B shifts the binary decimal point to effect the scaling.

Accumulators 370 receive the X, Y, and Z position coordinates and perform the following translation computations (illustrated in FIG. 2):

basic translation: from the origin 210 of data base coordinate system to the origin 220 of aircraft 14 coordinate system

$V_p + V_o = V_t$

2 D translation: from initial vertex to the remaining vertices sequentually—cumulative (landing strip

Vt + Delta Vl = VtlVtl + Delta V2 = Vt2

Vtn + Delta (Vn + 1) = V(tn + 1)

3 D translation: from initial vertex to each remaining vertex separately-non cumulative (hanger 240)

Vt + Delta Vl = Vtl

Vt + Delta Vn = Vtn

Normalization registers 380 (X, Y, and Z) loads the translated vertices Vt, and left shifts leading zeros (or ones for negative Vt's) in response to control logic 70. The first difference between the MSB and the second MSB in any of the normalization registers 380 generates a normalization complete signal, (NCS), back to control logic 70. Normalization complete in any of the normalization registers 380 stops the normalization process of all the registers insuring that the normalized points maintain consistent dimension units and remain on the same line of vision as viewed on display 82. Normalization has the advantage of reducing the 24 bit input image data into bits of normalized image data by eliminating either leading zeros (or ones for negative numbers). The data load is reduced to 66% with negligible loss in position resolution.

#### **DETAILED DESCRIPTION**

RAM 304 may be formed by a 16 bit  $\times$  24 word RAM (sixteen 93415's, Fairchild) for holding the block of image data from GP computer 40.

Buffer register 306 may be formed by a 16 bit register (four 74S175's) followed by buffer inverters as required (74S04).

Register 310A may be an eight bit register (two 10 74S175's) for receiving four bits of code (4MSB) and four bits of RAM address (4LSB).

Register 310B and word counter 320B may be formed together by an eight bit down counter (two 74S163) for receiving the compliment of B and counting to 15. At B 15 compliment = 15, B = 0 appears on the carry out termi-

Address counter 320A may be a 2:1 inverting multiplexer (74S158) followed by a four bit up counter (one 74S163). During load and recall instructions, counter <sup>20</sup> 320A increments the start address AAAA to RAM's 350. While processing three dimensional faces counter 320A processes the face vertex addresses in three D registers 341 and 342.

CIF register 330 may be an eight bit register (two 74S175) for receiving eight bits of SEL AXIS,  $S \pm$  and Intensity Data from the CIF Load instruction.

CIF-1 and CIF-2 registers 331 and 332 may be 16 bit registers (four 74S174) for receiving two 16 bit words of 30 CIF data immediately following the CIF instruction.

Three dimensional registers 341 and 342 may be eight 4 bit tristate registers (eight 8551) preceded by a 3 line to 8 line decoder (one half 74S139) which enables one of the eight tristate registers in response to the three LSB's 35 of B from word counter 320B.

RAM 350X may be a 24 bit RAM (six 74S189's) to accomodate the 24 bits of X coordinate image data. The 24 bit RAM is preceded by a 2:1 8 bit multiplexer (two 74S158) between a pair of true compliment zero one elements (two 74H87's each). During 16 bit fine resolution (R=1) the right hand zero one element forwards the 8 LSB's of the image data to the 24 bit RAM, and the righthand zero one element enters all zeros (or all 45 ones depending on the sign of the image data). During 16 bit coarse resolution (R=2) the right hand zero one elements enters all zeros and the lefthand zero one element forwards the 8 MSB's.

Scaler 360x may be formed by a flow through right 50 shifter device (twelve 25S10's AMD) in response to S data from register 310B counter.

Accumulator 370x may be a 24 bit adder (six 74283's) for receiving data at the A input, followed by a 24 bit return register (six 74S175's) which outputs to the B 55 resulting Vc is forwarded to clipping stage 63. input. Vp is processed through the adder and return register, and returned to the B input. Vo is loaded at the A input and added to Vp to form Vt and returned to the B input. Delta data is then loaded at the A input and added to Vt to form the remaining vertice vectors Vfl-Vfn, which are advanced through the return register to a 24 bit buffer register (four 74S174's) where the Vf's are held until normalizer 380x is free.

Normalizer 380x may be formed by a 24 bit shift 65 where: register (three 74199) plus a Buffer register (four 74S174's) which holds the normalized Vf's until rotation stage 62 is free to handle the next Vf.

# **ROTATION STAGE 62** GENERAL-H MATRIX

FIG. 4 shows rotation stage 62 of image processor 42 which multiplies the translated point vectors Vfl-Vfn from translation stage 60 by the rotation matrix H provided on data bus 307 to produce a rotated or channel vectors Vc (XcYcZc):

Each channel corresponds to the perspective view from one window of aircraft 14.

The rotation matrix H is developed from yaw (Y, left), pitch (P, down), and roll (R, right) motions by flight simulator 16 using conventional software. The order of rotation is Y followed by P, and the matrices for the separate rotations from translated to rotated pilot eye or channel coordinates are as follows:

$$HY = \begin{bmatrix} \cos Y & \sin Y & 0 \\ -\sin Y & \cos Y & 0 \\ 0 & 0 & 1 \end{bmatrix}$$

$$HP = \begin{bmatrix} \cos P & 0 & -\sin P \\ 0 & 1 & 0 \\ \sin P & 0 & \cos P \end{bmatrix}$$

$$HR = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos R & \sin R \\ 0 & -\sin R & \cos R \end{bmatrix}$$

The composite matrix H describing this rotation is given by the matrix product:

[H] = [HR][HP][HY] = 3 columns  $\times 3$  rows matrix

The aircraft attitude matrix H is constant for each frame and is therefore computed only once per frame for each channel.

The three elements of the first column of the H matrix are entered into H RAM 410x by WRITE from control logic 70 immediately subsequent to the Load H instruction. The first column is then multiplied by the Xf coordinate of each of the translated vector series Vfl-Vfn in turn within column multiplier 420X. The three elements of the second and third columns of [H] are similarly entered into H RAM 410Y and 410Z (not shown). The nine products generated above are combined into Xc, Yc, and Zc by row multiplexer 424 and adder 430. The

#### **GENERAL-VISIBILITY TEST**

The rotation circuitry also provides the multiplication for the dot product visibility test for the faces which form three dimensional structures such as buildings:

$$Vt dot Vn = M cos P$$

Vt is the translated vector extending from aircraft 14 to the first vertex of the face being tested; and Vn is the vector normal to the face being tested.

When cos P is negative, P is greater than 90° and the face is visible—on the front or exposed side of the building. When cos P is positive, P is less than 90° and the face is invisible—on the back side of the building. The sign bit of the dot product is employed for back side 5 elimination—a simple occulting technique.

The Xn, Yn, and Zn coordinates of Vn are entered into NRAM's 410X, Y, and Z respectively immediately subsequent to the Load N instruction. Each coordinate is multiplied by the corresponding coordinate Xt, Yt, 10 and Zt of Vt in multipliers 420 and the sign bit of the resulting quantity is forwarded to control logic 70.

#### **DETAILED DESCRIPTION**

H RAM 410x may be a 16 word by 16 bit sequential  $^{15}$  access memory (four 74S189's) for holding the three words in the first column of the  $3\times3$  H matrix and providing 13 spare 16 bit addresses. WRITE and ADDRESS are provided by control logic 70.

N RAM 410x may be a 16 word by 16 bit random <sup>20</sup> access memory (four 74S189's) for holding up to sixteen words of Xn which accommodates a three dimensional complex structure with up to sixteen faces.

Multiplicand register 414x may be a 16 bit buffer register (four 74S175's) for holding the current output <sup>25</sup> of H and N RAM's 410x available to multiplexer 420x while the next address in RAM's 410x are accessed.

MUX 416x may be a 16 bit dual 4-1 multiplexer (three 74S153's) for providing four bits of output plus carry over bit.

Multiplier register 418x may be a 5 bit buffer register (one 74S174) for holding the output of MUX 416x available to multiplier 420x.

Column multiplier 420x may be formed by eight AM 25S05's (Advanced Micro Devices in 16 bit×4 bit configuration) followed by a buffer product register (three 74S175's) and operates as described in connection with Multiplier 330 in U.S. Pat. No. 3,996,672 which issued Dec. 14, 1976.

Row Multiplexer 424 may be a 20 bit 4 to 1 multiplexer (ten 74157's connected in parallel) which sequentially select the first row elements of each column for summing in row adder 430 to form Xc. The second and third row elements are likewise summed to provide Yc and Zc.

Row adder 430 may be a 20 bit adder (five 74783's) for summing the row products of the H matrix.

Accumulator 440 (three 74174's) returns intermediate sums to multiplexer 440 which are required in forming Vc. 50

Buffer registers 450 may be 18 bit registers (four 74175's) for holding Vc (Vx, Vy, Vz) prior to clipping. CIF register 460 may be a 40 bit register for holding the CIF data from CIF registers 330, 331, and 332.

#### **CLIPPING STAGE 63**

#### General

FIG. 5 shows window coordinate processor or generator 63G and clipping logic 63L which cooperate to 60 eliminate points outside the viewing volume or pyramid of vision 250 shown in FIG. 2a. Pyramid of vision 250 has its vertex at the eye of the pilot (origin 220). The viewing volume in the embodiment shown is bounded by four planes defined by the four sides of the aircraft 65 window. Non-square windows may be emloyed and would require a correspondingly different viewing volume configuration.

16

Clipping is accomplished at the object face level. Each face is defined by a CCW sequence of vertices. Pairs of adjacent vertices defining each face edge are processed in sequence through clipping stage 63 to determine whether the face is:

Case A—face completely within view,

Case B—face partially within view, or Case C—face completely out of view.

Faces which are only partially in view (Case B) are intercepted by the boundary planes of the pyramid of vision 250. In the process of clipping, Case B faces are modified by the addition of new vertices which define new edge coinciding with the intersection of the boundary planes. The result is a modified closed polygon face that is completely within pyramid 250.

The position of any point or vertex relative to pyramid of vision 250 is defined by the orthogonal distance across window plane 260 of that vertex from each of the four boundary planes of pyramid of vision 250. Referring to FIG. 2a, point 254 forming the top of the flag pole 256 is positionally defined by the four window coordinates vl, vr, vb, vt in Zc plane 260. These window coordinates are calculated as follows:

vl = Kl Z + X (distance to the left plane)

vr = Kr Z - X (distance to the right plane)

vb = Kb Z + Y (distance to the bottom plane)

vt = Kt Z - Y (distance to the top plane)

where the K's are constants associated with the vertex angles of pyramid 250. For a square pyramid of vision having equal vertex angles A, Kl=Kr=Kb=Kt=Tan (A/2). A point is inside the truncated pyramid of vision 250 if  $vl\ge0$ ,  $vr\ge0$ ,  $vb\ge0$ ,  $vt\ge0$ , and  $zc\ge0$ , that is, if all of the window coordinates have zero or positive values.

The above window coordinates are calculated from Vc by window logic 510-l, 510-r, 510-b, 510-t, and 510-z shown in FIG. 5 (only 510-l is shown in detail). Window circuit 510-l receives Xc and Zc from rotation stage 62 for temporary storage in interior working registers 530. ALU unit 540 performs the required addition or subtraction.

Clipping logic 63L determines which vertices are visible for each face, and determines when to compute the interception vertices where face edges intercept a boundary plane. Visibility is determined within rejection logic 550 by systematically advancing and comparing the sign of the window coordinates of each vertex with the sign of the corresponding window coordinates of the immediately previous vertex. The window coordinates of visible vertices are advanced to projection stage 64. All vertex coordinates must be saved in RAM 560 for calculation of possible intersection vertices and for closing. Rejection logic 550 provides separate PTRs for each plane saved.

The signs of the window coordinates for each vertex are combined in a single five-bit out-code (OC):

OC=sign l, sign r, sign b, sign t (and sign Z)

and are entered into current vertex (CV) register 554.

The sign of each window coordinate is "0" for positive and "1" for negative. The origin of each window coordinate is the corresponding boundary of image window 262 with the negative direction extending away from

image window 262 (see FIG. 2b, left for vl, right for vr, down for vb, and up for vt). The positive direction for each window coordinate is toward the center of image window 262. The four boundaries of pyramid 250 subdivide the Zc plus half-space in front of aircraft 14 into 5 nine regions. The out-code of each Vc identifies the region in which the point or vertex is located. The out-code for each region of the two-dimensional projection of pyramid 250 is shown in the following table:

| upper<br>left<br>region<br>1001 (0) | upper<br>region<br>0001 (0)                 | upper<br>right<br>region<br>0101 (0) |  |

|-------------------------------------|---------------------------------------------|--------------------------------------|--|

| left<br>region<br>1000 (0)          | visible<br>region<br>window 262<br>0000 (0) | right<br>region<br>0100 (0)          |  |

| lower<br>left<br>region<br>1010 (0) | lower<br>region<br>0010 (0)                 | lower<br>right<br>region<br>0110 (0) |  |

The relative position of any face edge to pyramid 250 can be found by comparing the out-codes of the end 25 points of the edge. The starting point O.C. is always in previous vertex (PV) register 556, and the terminal point O.C. is always in CV register 554.

Three sub-possibilities exist for the relative position of each face edge with respect to pyramid 250:

Case 1: Both vertices of the face edge are in view. No clipping is necessary:

C(P)=0000(0) and C(C)=0000(0).

Case 2: One vertex of the face edge is within view and the other is outside. The face edge intersects the pyramid 250:

OC(P) = 0000(0) and  $OC(C) \neq 0000(0)$ , or

OC(P) \neq 0000(0) and OC(C) = 0000(0).

Case 3: Both vertices are outside pyramid of vision 250:

$OC(P) \neq 0000(0)$  and  $OC(C) \neq 0000(0)$ .

In Case 3, definite decisions can be made only if the vertices points of the edge are either both to the right or both to the left, i.e., sign I(P)=sign I(C)=1 (negative) or 50 sign r(P)=sign r(C)=1 (negative). Furthermore, if  $OC(P)=OC(C)\neq 0000$ , both ends are outside, in the same region. In all these cases the face edge can be rejected. The rejection criteria of rejection logic 550 can be expressed as a Boolean function (R) of the two 55 out-codes. If R=0, none of the above rejection criteria are satisfied, and a part of the face edge boundary may go through image window 260.

Whenever Case 2 is determined by rejection logic 550, the intersection of each face edge and pyramid of 60 vision 250 is then calculated by window logic 510 using a binary search technique. The algorithm for the search is as follows:

- (A) Let the window coordinates of the vertex inside image window 260 be Vin and the outside coordinates be Vout (one is CV and the other is DV).

- (B) The midpoint between Vin and Vout is calculated by ALU 540.

- (C) If the midpoint is within pyramid 250, Vin is replaced by the midpoint.

- (D) If the midpoint is outside, Vout is replaced by the midpoint.

- (E) The process continues by returning each new midpoint to ALU 540 through multiplexers 580 until the distance of the midpoint from one side of pyramid 250 is less than the termination tolerance.

- (F) The last midpoint and Vin become the vertices (CV and PV) of the clipped edge just formed.

There remains the problem of modifying the edges of the clipped faces. In some situations the intersections of the face edges and the boundary planes of the pyramid of vision 250 define the new face edge. In other situations one or more corners of the window must be inserted into the sequence of vertices to complete the closed polygon face.

The out-code of the window coordinates for the first vertex of each face is stored in first vertex (FV) register 558 for comparison with the last vertex processed by window coordinate processor 63G. Closing logic 570 makes this comparison to complete the face.

#### DETAILED DESCRIPTION

Registers 530 P and M may be holding registers (74S194's) connected in cascade (with carry over) preferably with left and right shifting for facilitating midpoint computation.

ALU540 may be an arithmatic logic unit (841gl's) for adding, subtracting or passing data as required.

UV register 554 may be a 4 bit holding register (74174).

PV register 556 and PV register 558 may be 4 bit holding registers (74174's), one for each clipping plane, for storing 3 bits of pointer (2 bits for RP plus 1 bit for FVF) and 1 bit of O.C.

RAM 560 may be a 16 bit by 4 word random access memory (74S189's) for storing FV and PV window coordinates.

MUX 580 P and M may be 4:1 multiplexers (74153's) for selecting: (1) Xc and Zc during window coordinate calculation; (2) ALU output; (3) ALU output divided by 2 (right shift), and (4) RAM 560 for reading back the window coordinates of previous vertices during clipping testing.

MUX 564 may be a 4:1 multiplexer (74153's) for selecting RAM addresses RP, PPTR(RP), FPTR(RP) and PPTR(CP).

#### PROJECTION STAGE 64

#### General

FIG. 6 shows projection and clipping stage 64 of image processor 42 which projects three-dimensional window coordinates vl, vt, and Vz from clipping stage 63 into a two-dimensional vector Vd (Xd, Yd). The projected vectors Vd define the end points of each face edge for face generation stage 65. The projection is accomplished by dividing vl and vt by Zc through a binary division nonrestoring technique (described in "Digital Arithmetic-I" by Y. Chu pages 39-43). Z/2 registers 610-1 and 610-t load the divisor Zc/2, and MUX/Register 620-l and 620-t select and load the dividend v1/2 and vt/2 in response to control logic 70. The inputs to registers 610 and 620 are right-shifted by one digit to establish the division by two. Arithmetic logic unit ALU 630-1 and 630-t then receive the dividends through shift return loops 623-1 and 623-t, or subtract Zc/2 thereto in response to a  $\pm$  function from logic 70. The dividend  $\pm Zc/2$  term is loaded into MUX's 620, returned to ALU's 630, and then combined with another  $\pm Z/2$ . The output of ALU's is slew wired with respect to the input to MUX's 620 causing a division by 5 two right shift. The vI/Vz and vt/Vz quotients are generated one bit at a time, MSB first, by comparing the sign bit (MSB) of Zc with the sign bit of the partial remainders with MUX 620 through sign gates 636-1 and 636-t. The quotient bits individually enter quotient reg- 10 isters 640-l and 640-t, and are left-shifted by control logic 70. Zc on line 592 from range register 590 is loaded into renormalization register 650 and rightshifted by control logic 708 the same number of places as were left-shifted in normalizer 370 in translation stage 15 60. Color, intensity, and flat data on line 592 from CIF register 590 is loaded into CIF register 660 in response to control logic 70.

#### **DETAILED DESCRIPTION**

z12 register 610 may be a 24 bit register (four

MUX/Registers 620 may be 24 bit 2:1 multiplexers (five 74S298's) with storage.

logic units (four 74S181's + one 74S182).

Sign gates 636 may be exclusive OR gates (74S86). Quotient registers 640 may be 12 bit shift registers

(three 74164's) for receiving the projected data Xd and 30 Yd one bit at a time as it is generated by ALU's 630.

Zc register 650 may be a 24 bit shift register (six 74S195's).

CIF register 660 may be a series of 74S174's.

#### **EDGE STAGE 65**

#### General

FIG. 7 shows edge stage 65 having Xd processor 706X and Yd processor 706Y which receive projected face vertex coordinates (Xd and Yd) from projection 40 stage 64 and provides face edge lists to display generator 44. Each edge is defined by edge data including a starting point (Xds, Yds), the Y coordinate of the termination point (Ydt), plus the slope of the edge (delta

The Y coordinates of each set of face vertices (Xd and Yd) are loaded into current Y mux-register 710 and advanced to previous Y register 716 in CCW order as defined in data base 48. Each current Y coordinate (Ydc) and previous Y coordinate (Ydp) are forwarded 50 to adder 720 for calculating a delta Y for each face edge or pair of points (delta Y=Ydc-Ydp). Simultaneously, each Ydc and Ydp are entered into Y start multiplexer 730s and Y terminate multiplexer 730t. The starting Y scanned first on CRT 82; and the terminate Y coordinate Ydt is scanned last. In the embodiment shown, the conventional top to bottom scan is employed. Therefore, the start point Yds is always the smaller of the two adjacent points Ydc and Ydp. The sign bit of delta Y  $^{60}$ (SIGN  $\Delta Y$ ) defines which is smaller, Ydc or Ydp, as follows:

| for + delta Y              | for - delta Y              | 65 |

|----------------------------|----------------------------|----|

| Ydc = Ydt, and $Xdc = Xdt$ | Ydc = Yds, and $Xdc = Xds$ |    |

| Ydp = Yds, and $Xdp = Xds$ | Xdp = Xdt, and $Xdp = Xdt$ |    |

and activates multiplexers 730s and 730t accordingly. Slope divider 740 provides the slope of each edge face by computing delta X/delta Y for the corresponding pair of vertices.

The face edges are arranged in scan order by Yds sorter 750 according to the smallest YDs. Each edge data set is loaded into sorter 750 in CCW order and forwarded to image generator 44 in order of smallest Yds for accomodating the top to bottom scan.

#### DETAILED DESCRIPTION

Xd processor 706X has the same hardware as Yd processor 706Y, and is therefore now shown in detail.

Current Y mux-register 710 may be a 12 bit 2:1 muliplexer-register (three 74298's ) for the current vertex of each face as the vertices are received in CCW order from quotient registers 640-l and 640-t.

Previous Y register 716 may be a 12 bit storage register (two 74174's) for holding the vertex just preceding 20 the current vertex.

First vertex Y register 718 may be a 12 bit storage register (two 74174's) for holding the first vertex while the intermediate vertices are processed. The first vertex is loaded into current mux-register 710 as the last vertex ALU's 630 may be 16 bit flowthrough arithmetic 25 is advanced to previous vertex status to form the last edge of the face.

Adder 720 may be a 12 bit adder (three 74283's) for calculating delta Y=Ydc-Ydp, and forwarding SIGN Y to Y and X multiplexers-registers 730s and 730t.

Inverter 722 may be a 12 bit inverting buffer (two 74S04's) for inverting Ydp into -Ydp. The carry in on adder 720 is forced to 1 to complete the complement of Ydp.

Start point and terminate point multiplexer-register 35 730 may be 12 bit 2:1 multiplexer-registers (three 74298's each) for simultaneously holding both Ydc and Ydp available for selection as either Yds or Ydt.

Delta Y register 724 may be a 12 bit storage register (three 74S175's) for holding delta Yc while divider 740 forms the slope (delta Xp/delta Yp) for the previous edge. Additionally register 724 may include a zero detect circuit (one 74S30) for providing deltaY=0 to control 70 when the slope is horizontal and the edge may be omitted from further processing.

Divider 740 may be a 12 input bit-20 output bit binary division nonrestoring divider as described in projection stage 64, for calculating slope=delta X/delta Y. The dividend delta X may be right shifted into additional shift register (one 74166) for scaling down the resulting slope to accomodate a Y increment of one raster line. In the embodiment shown the right shift is nine places to accomodate a 1024 scan line, interlaced display (2 to the 9th = 512).

Sorter 750 may be a 12 bit key-96 bit non key sorter coordinate Yds is the end point of each face edge that is 55 for output edge data in order ascending of Yds, formed

- (a) a 16 word 12 bit key data RAM (three 74S189's) for receiving and storing the key data (Yds) in input order.

- (b) a 16 word 5 bit pointer RAM (two 74S189's) for storing the RAM pointers.

- (c) A three level pointer pushdown stock (two muxregisters 74298's—first level, one 74S174—second level, and one 74S174—third level) for manipulating pointers into sorted order each time a new key is received by the key data RAM.

- (d) address counter (one 74161) and smallest key pointer register (one 74S174) for generating RAM

addresses and storing the current smallest key RAM address.

(e) RAM address multiplexer (two 74S153's) and a pointer RAM input multiplexer (three 74S153's) which cooperates with the three level stack and 5 address counter for selecting RAM addresses and the pointer RAM input.

(f) an existing key register (three 74S175's) and comparator (three 74S85's) for determining where to insert the input key among the existing key in the 10 key data RAM. The existing key register also stores key data to be advanced to image generator 44

(g) non key data output register (twenty-four 74S175's) for storing non key data (Xds, slope, Ydt, Zc, and CIF) to be advanced to image generator 44

#### **CONTROL LOGIC**

Processor control logic 70 responds to instruction code and data flags contained in the data flow from data base 48 for processing the coordinate data through image processor 42. The flow tables described below disclose the logic involved in controlling each stage of image processor 42. Various hardware circuit configurations could incorporate this logic.

|         | TRANSLAT       | ION STAGE 60CONT         | TROL LOGIC FLOW                                       | TABLE                             |

|---------|----------------|--------------------------|-------------------------------------------------------|-----------------------------------|

| I.      | TRANSFER INSTR | UCTION WORD: CO          | NTROLLER 46 TO RI                                     | GISTER 310                        |

|         | STEP IA:       | (1) Maintain LO          | AD signal on instruction                              |                                   |

| 4.4.4.3 |                | register 310.            | atmostica Grain Luffan                                |                                   |

|         |                |                          | struction from buffer nto instruction regis-          |                                   |

|         |                | ter 310 (LOA             |                                                       |                                   |

|         | DECISION IA:   | Is image data availa     | ble to translation stage                              |                                   |

|         |                | 60 on data bus 307?      |                                                       |                                   |

| 1.0     | STEP IB:       |                          | NOSTEP IA<br>ulator 370 (CLR).                        |                                   |

|         | SIEFID.        |                          | data "S" from scale regi                              | S-                                |

|         |                | ter in scaler :          |                                                       |                                   |

|         |                |                          | s counter 320A (CLR).                                 |                                   |

|         |                |                          | m control logic 70, wait                              | for                               |

|         | DECISION IB:   |                          | nterface controller 46.<br>of instruction in register |                                   |

|         | DECISION IB.   |                          | e of sixteen instructions                             |                                   |

|         |                | (0–15).                  |                                                       |                                   |

| II.     | LOAD X INSTRUC | CTIONLDX (0)             |                                                       |                                   |

|         | STEP IIA:      |                          | s counter 320Å with fou                               | r bits                            |

|         |                | of address "A            |                                                       | (DEC)                             |

|         | DECISION IIA:  | (2) Unit decreme<br>DAV? | ent word counter 320B                                 | (DEC).                            |

|         | DDOIDION III.  | YES-DECISION I           | IB NO-DECISION                                        | I IIA                             |

|         | DECISION IIB:  | What is R?               | v. tra                                                |                                   |

|         |                | R=1                      | R=2                                                   | R=3                               |

|         |                | (fine 16 bit) 1. Load 16 | (coarse 16 bit) 1. Same as DE-                        | (normal 24 bit)<br>1. Load 16 LSB |

|         |                | LSB from bus             | CISION IIB                                            | from bus 307                      |

|         |                | 307 into RAM             | (R=1) 1 through                                       | into RAM 350X.                    |

|         |                | 350X.                    | 3 except load                                         | 2. Request DAR,                   |

|         |                | 2. Load zeros            | 16 MSB at 1.                                          | wait for DAV.                     |

|         |                | into RAMs 350            |                                                       | 3.Load 8 MSB                      |

|         |                |                          | •                                                     | 0.2000 0 1.102                    |

|         |                | Y and Z.                 | •                                                     | from bus 307                      |

|         |                | 2 - Tiula i-             | • • • • • • • • • • • • • • • • • • • •               | DAM 250V                          |

|         |                | 3.a. Unit in-            | •                                                     | into RAM 350X.                    |

|         |                | crement ad-              | •                                                     | 4. Load zeros                     |

|         |                |                          |                                                       |                                   |

|         |                | dress counter            | •                                                     | into RAMs 350                     |

|         |                | 220 A (TNIC)             | •                                                     | Y and Z.                          |

|         |                | 320A (INC).              |                                                       | I and Z.                          |

|         |                | 3.b. Unit de-            |                                                       | 5. Same as DE-                    |

|         |                |                          |                                                       |                                   |

|         |                | crement word             | •                                                     | CISION IIB                        |

|         |                | counter 320B             | •                                                     | (R=1)3.                           |

|         |                | Counter 520B             | •                                                     | (14-1)5.                          |

|         |                | (DEC).                   | •                                                     | •                                 |

|         |                |                          | •                                                     | •                                 |

|         |                | 3.c. Set DAR,            |                                                       | •                                 |

|         |                | wait for DAV.            | . •                                                   | •                                 |

|         |                | 4. DECISION              | 2. DECISION                                           | 6. DECISION                       |

|         |                | IIC.                     | IIC.                                                  | IIC.                              |

|         | DECISION IIC:  | Is word count in re      |                                                       |                                   |

| III.    | LOAD Y INSTRUC | YESSTEP IA               | NO-DECISION IIA                                       |                                   |

|         | STEP IIIA:     | Same as STEP IIA         |                                                       |                                   |

|         | DECISION IIIA: | DAV?                     | •                                                     |                                   |

|         |                | YESDECISION              | IIIB NO-DECISIO                                       | N IIIA                            |

|          | TRANSLATIO                   | ON STAGE 60CON                    | TROL LOGIC FLOW                 | TABLE                          |

|----------|------------------------------|-----------------------------------|---------------------------------|--------------------------------|

| -        | DECISION IIIB:               | What is R?                        |                                 |                                |

|          | And the second of the second | R=1                               | R=2                             | R=3                            |

|          |                              | 1. Load 16 LSB                    | 1. Same as DE-                  | 1. Load 16 LSB                 |

|          |                              | from bus 307                      | CISION IIIB                     | from bus 307                   |

|          |                              | into RAM 350Y.                    | (R=1)1 through                  | into RAM 350Y.                 |

|          |                              | 2. Load zeros                     | 3 except load                   | 2. Set DAR,                    |

|          |                              | into RAMs 350                     | 16 MSB at 1.                    | wait for DAV.                  |

|          |                              | X and Z.                          | •                               | 3. Load 8 MSB                  |

|          |                              | A allu Z.                         | •                               | J. LOZU 6 MISD                 |

|          |                              | 3. Same as DE-                    | •                               | from bus 307                   |

|          |                              |                                   |                                 | nom ous so,                    |

|          |                              | CISION IIB                        |                                 | into RAM 350X.                 |

|          |                              | the contract of                   | •                               |                                |

|          |                              | (R=1)3.                           | •                               | 4. Load zeros                  |

|          |                              | •                                 | •                               |                                |

|          |                              | •                                 | • .                             | into RAMs 350                  |

|          |                              | •                                 | •                               | X and Z.                       |

|          |                              |                                   | •                               | A and Z.                       |

|          |                              |                                   | •                               | 5. Same as DE-                 |

|          |                              |                                   |                                 |                                |

|          |                              | •                                 |                                 | CISION IIB                     |

|          |                              | •                                 | •                               |                                |

|          |                              |                                   |                                 | (R=1)3.                        |

|          |                              | 4. DECISION                       | 2. DECISION                     | 6. DECISION                    |

|          | DECISION IIIC                | IIIC.                             | IIIC.                           | IIIC.                          |

|          | DECISION IIIC:               | Is word count in re<br>YESSTEP IA | NO-DECISION IIIA                |                                |

| IV.      | LOAD Z INSTRUCT              |                                   | NO-DECISION IIIA                |                                |

| •••      | STEP IVA:                    | Same as STEP IIA                  |                                 |                                |

|          | DECISION IVA:                | DAV?                              | •                               |                                |

|          | DECISION IVA.                | YESDECISION                       | IIB NODECISION                  | TIVA                           |

|          | DECISION IVB:                | What is R?                        | IIB 140DECISION                 | IIVA                           |

|          |                              | R=1                               | R=2                             | R=3                            |

|          |                              | 1. Load 16 LSB                    | <ol> <li>Same as DE-</li> </ol> | 1. Load 16 LSB                 |

|          |                              | from bus 307                      | CISION IVB                      | from bus 307                   |

|          |                              | into RAM 350Z.                    | (R=1) 1                         | into RAM 350Z.                 |

|          |                              | 2. Load zeros                     | through 3, ex-                  | 2. Set DAR,                    |

|          |                              | into RAMs 350<br>X and Y.         | cept load 16                    | wait for DAV.                  |

|          |                              | A and Y.                          | MSB at 1.                       | 3. Load 8 MSB                  |

|          |                              | 3. Same as DE-                    | •                               | from bus 307                   |

|          |                              |                                   | ·                               | 110111 043 507                 |

|          |                              | CISION II                         |                                 | into RAM 350Z.                 |

|          |                              |                                   | •                               |                                |

|          |                              | (R=1) 3.                          | •                               | 4. Load zeros                  |

|          |                              | •                                 | •                               |                                |

|          |                              | •                                 | •                               | into RAMs 350                  |

|          |                              | • '                               | •                               | X and Y.                       |

|          |                              | •                                 | •                               | A and I.                       |

|          |                              |                                   |                                 | 5. Same as DE-                 |

|          |                              |                                   |                                 |                                |

|          |                              | •                                 |                                 | CISION IIB                     |