# **CMOS Circuit Design for Biomedical Telemetry**

#### Gudnason, Gunnar

*Publication date:* 2001

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Gudnason, G. (2001). *CMOS Circuit Design for Biomedical Telemetry*.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# CMOS CIRCUIT DESIGN FOR BIOMEDICAL TELEMETRY

**Gunnar Gudnason**

This thesis was submitted towards the Ph.D. degree at the Technical University of Denmark, Ørsted•DTU, on August 6, 2001.

Copyright © 2001 by Gunnar Guðnason

#### **Document version history**

Version 1: LATEX run August 4, 2001. Initial submission run. Times Roman, {oneside,12pt,a4paper} book class option.

Version 2: LATEX run October 25, 2001. First official print version with fewer typos and reduced page size. Times Roman, {twoside,l2pt,a4paper} book class option. Magnification factor \mag=800.

Version 3: LATEX run November 29, 2001. Second printing with typographical corrections and minor editing in response to the opponents' comments.

## ABSTRACT

Implanted electronics have a long history, reaching back over 40 years to the first totally implanted battery-powered pacemaker. During this time, electronic implants have become ever more commonplace, but the use of integrated circuit technology for such devices has only become prevalent during recent years.

This thesis presents the results of work done on the design of analog integrated circuits for use in biomedical telemetry systems, specifically for Functional Electrical Stimulation (FES) and for nerve signal sensor applications. The systems are powered by an externally generated electromagnetic field, and data communication to and from the implanted devices is made possible by modulating this field. While this type of telemetry link eliminates the need for wires to the implant or an implanted battery, it sets strict limitations on the power use of the device.

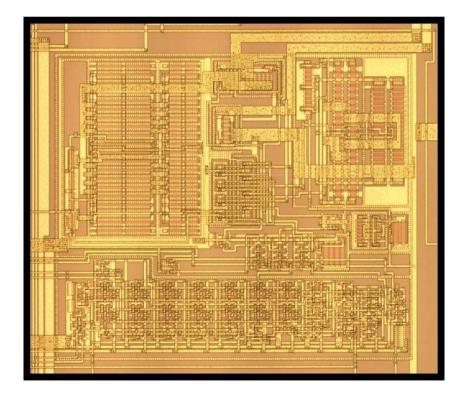

We have designed integrated circuit solutions for many of the problems associated with implanted devices, and present here circuits which improve in several ways over previously published designs, in functionality and level of integration. As an additional constraint, our designs are all implemented in plain CMOS technology, while most other designs rely at least partly on elements available in more specialized (and expensive) technologies. We have succeeded in implementing building blocks for a complete implanted transceiver IC which relies only on an absolute minimum of off-chip components.

The system blocks include circuits for the complete power supply path, including conversion of the RF carrier to a DC supply voltage, overvoltage protection and internal voltage regulation. In addition to being fully integrated in CMOS, these supply path blocks improve on previous designs in performance, functionality and/or power consumption. In addition to the power supply management, we have designed new receiver types which are adapted to the special requirements of mixed power/data transmission. Two complete implantable chips are presented, which highlight the design tradeoffs and optimizations applied to the design of CMOS implantable system chips.

# ÁGRIP

Igræddar rafrásir eiga sér tiltölulega langa sögu, þar sem meira en 40 ár eru liðin frá því að fyrsti rafhlöðuknúni hjartagangráðurinn var tekinn í notkun. Á þeim tíma sem liðinn er frá þeim atburði hafa ígrædd rafeindataæki orðið sífellt algengari lækningatæki, en notkun samrása til þessara tækja hefur ekki orðið almenn fyrr en á seinasta áratug.

Ritgerð þessi greinir frá niðurstöðum rannsókna sem framkvæmdar hafa verið varðandi hönnun hliðrænna samrása fyrir læknisfræðileg fjarkönnunartæki, nánar tiltekið fyrir það sem á ensku nefnist *Functional Electrical Stimulation* og fyrir fjarskynjun taugamerkja. Þessi ígræddu tæki fá alla raforku sína og stýrimerki með rafsegulbylgjum frá sendi sem liggur utan líkamans. Með þessari gerð sambands við ytri stjórnstöð er ekki þörf fyrir leiðslur í gegnum húðina, en kröfur til orkusparnaðar aukast jafnframt vegna lélegrar nýtni.

Hér verður greint frá lausnum sem fundist hafa á mörgum þeim vandamálum sem setja ígræddum raftækjum skorður, og sagt frá rásum sem eru að mörgu leyti eru betri en þær

sem áður hafa birst, meðal annars með tilliti til fjölhæfni og orkusparnaðar. Þar að auki hefur verið notuð einföld CMOS framleiðslutækni, andstætt fyrr birtum lausnum sem nota flóknari og dýrari framleiðslutækni. Tekist hefur að hanna rásarhluta sem hægt er að setja saman í fullkomið ígræðanlegt viðtæki, og sem jafnframt notar lágmarksfjölda íhluta utan kísilflögunnar.

Lýst er rásum fyrir öll þrep í meðferð raforkuflutnings frá ytri sendi, meðal annars rásum til að umbreyta orku á formi rafsegulbylgna við háa tíðni í nothæft form, rásum fyrir yfispennuvörn og fyrir spennureglun. Þessar rásir standa áður birtum lausnum að ýmsu leyti framar, meðal annars með tilliti til afkastagetu, fjölhæfni og orkunotkunar. Ennfremur er sagt frá hönnun viðtækja sem eru sérstaklega aðlöguð kröfum sem stafa frá því hvernig burðarbylgjan er notuð til að flytja bæði afl og upplýsingar. Að lokum eru teknar fyrir tvær kerfislausnir sem leggja áherslu á það hvernig megi hámarka afköst og nýtni ígræddra kerfisrása innan þeirra takmarka sem þeim sett eru.

# RÉSUMÉ

Implanteret elektronik har efterhånden en lang historie, der strækker sig over 40 år, fra den gang den første implanterbare batteridrevne pacemaker blev taget i brug. Elektroniske implantater har siden da vundet frem, og er i dag blevet ganske almindelige.

Denne afhandling præsenterer resultaterne af et udviklingsprojekt omfattende design af analoge kredsløb for biomedicinske telemetrisystemer, især systemer til Funktionel Elektrisk Stimulation (FES) og måling af nervesignaler. Disse systemer får deres energiforsyning fra et eksternt elektromagnetisk felt, og dataoverførsel foregår ved modulation af dette felt. Fordelen ved denne type telemetri er at elektriske ledninger ind og ud af kroppen undgås men den effekt der er til rådighed for implantatet bliver stærkt begrænset.

Vi har udviklet integrerede kredsløb der løser mange af problemstillingerne inden for implanteret elektronik, og der vises kredsløb der på adskillige måder udmærker sig i forhold til andre publicerede løsninger. Alle de heri viste kredsløb er implementeret i simpel CMOS teknologi, hvorimod de fleste andre løsninger baseres på brugen af avanceret procesteknologi. Vi har implementeret byggeblokke for en komplet implanterbar transceiver som støtter sig til et minimalt antal eksterne komponenter.

De forskellige systemblokke dækker over kredsløb der udfører alle opgaver inden for behandling af forsyningsspændingen, inklusiv konvertering af RF signalet til DC, overspændingsbeskyttelse og intern spændingsregulering. Foruden at være implementeret i CMOS har disse forsyningsblokke en bedre ydeevne og funktionalitet og et lavere effektforbrug end ældre løsninger. Ud over dem er der designet nye receivertyper der er specielt egnede til de forhold der opstår ved blandet effekt og data transmission. To komplette chipdesign gennemgås for at vise de forskellige optimeringer og kompromisser der indgår i design af implanterbare CMOS systemchips.

# CONTENTS

| 1                | Intr        | oductio | n                              | 1  |  |  |  |  |

|------------------|-------------|---------|--------------------------------|----|--|--|--|--|

| 2                | Link design |         |                                |    |  |  |  |  |

|                  | 2.1         | Circuit | t-level link description       | 6  |  |  |  |  |

|                  |             | 2.1.1   | Transformer model              | 7  |  |  |  |  |

|                  |             | 2.1.2   | Transfer functions             | 8  |  |  |  |  |

|                  |             | 2.1.3   | Range                          | 11 |  |  |  |  |

|                  | 2.2         | Electro | omagnetic view                 | 12 |  |  |  |  |

|                  |             | 2.2.1   | Field calculations             | 12 |  |  |  |  |

|                  |             | 2.2.2   | Radiated power                 | 14 |  |  |  |  |

|                  |             | 2.2.3   | Effect of geometry on coupling | 15 |  |  |  |  |

|                  |             | 2.2.4   | Induced voltages               | 17 |  |  |  |  |

|                  | 2.3         | Coil de | esign                          | 18 |  |  |  |  |

|                  |             | 2.3.1   | Area versus inductance         | 18 |  |  |  |  |

|                  |             | 2.3.2   | Planar inductors               | 18 |  |  |  |  |

|                  |             | 2.3.3   | Field simulations              | 20 |  |  |  |  |

|                  | 2.4         | Transn  | nitter design                  | 21 |  |  |  |  |

|                  |             | 2.4.1   | Architectures                  | 21 |  |  |  |  |

|                  |             | 2.4.2   | Implementations                | 25 |  |  |  |  |

|                  |             | 2.4.3   | Performance                    | 28 |  |  |  |  |

| 3                | Rece        | eivers  | :                              | 31 |  |  |  |  |

| 3.1 Requirements |             | Requir  | rements                        | 31 |  |  |  |  |

|                  |             | 3.1.1   |                                | 32 |  |  |  |  |

|                  |             | 3.1.2   | Frequency allocation           | 33 |  |  |  |  |

|                  |             | 3.1.3   |                                | 34 |  |  |  |  |

|                  | 3.2         | Basic s |                                | 37 |  |  |  |  |

|                  | 3.3         |         |                                | 39 |  |  |  |  |

|                  |             | 3.3.1   | Passive input network          | 39 |  |  |  |  |

|                  |             | 3.3.2   |                                | 40 |  |  |  |  |

|                  |             | 3.3.3   | Low-pass filter                | 41 |  |  |  |  |

|                  |             | 3.3.4   |                                | 43 |  |  |  |  |

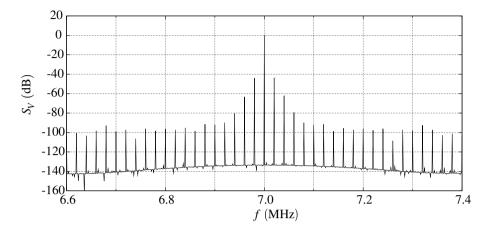

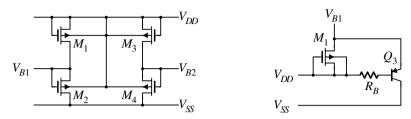

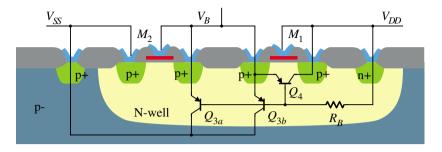

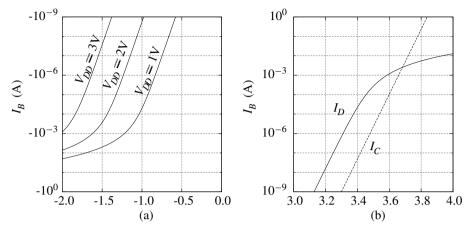

|                  |             | 3.3.5   | Experimental results           | 44 |  |  |  |  |

|   | Pow         | r supply management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47                                                                                     |

|---|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|   | 4.1         | Shunt regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48                                                                                     |

|   |             | 4.1.1 Regulator stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62                                                                                     |

|   | 4.2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66                                                                                     |

|   |             | 1 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                                                     |

|   |             | 5 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77                                                                                     |

|   |             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87                                                                                     |

|   | 4.3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90                                                                                     |

|   | т.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91<br>93                                                                               |

|   |             | ε                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 95<br>96                                                                               |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00                                                                                     |

|   |             | ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 01                                                                                     |

|   | 4.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 04                                                                                     |

|   |             | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 04                                                                                     |

|   |             | 4.4.2 Supply path functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 04                                                                                     |

| 5 | Refe        | rence circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 07                                                                                     |

|   | 5.1         | Bandgap references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 08                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 08                                                                                     |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

|   |             | 5.1.2 Design considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

|   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                     |

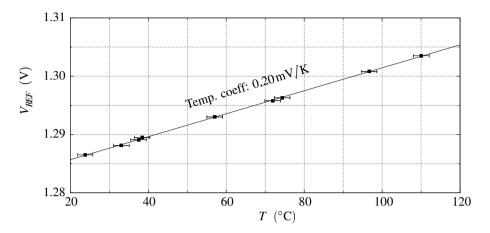

|   |             | 5.1.3 Measurement results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10<br>13                                                                               |

|   | 52          | 5.1.3         Measurement results         1           5.1.4         Output resistance         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10<br>13<br>14                                                                         |

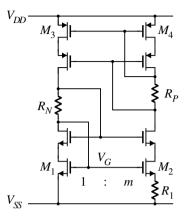

|   | 5.2         | 5.1.3 Measurement results15.1.4 Output resistance1Bias signal generation1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10<br>13<br>14<br>15                                                                   |

|   | 5.2         | 5.1.3Measurement results15.1.4Output resistance1Bias signal generation15.2.1Bias cells1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10<br>13<br>14<br>15<br>15                                                             |

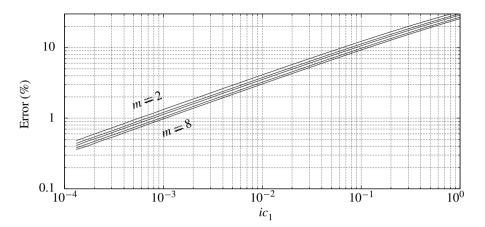

|   |             | 5.1.3Measurement results15.1.4Output resistance1Bias signal generation15.2.1Bias cells15.2.2Inversion limits for degenerate mirrors1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10<br>13<br>14<br>15<br>15<br>16                                                       |

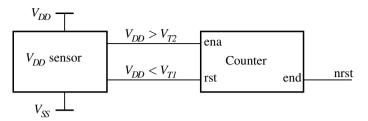

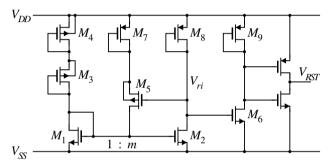

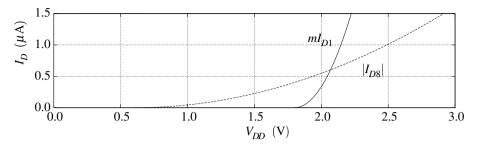

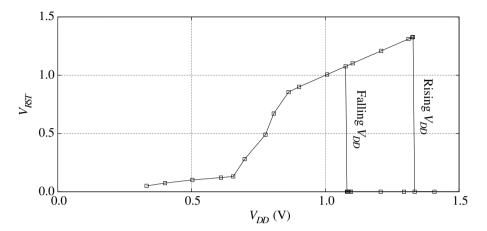

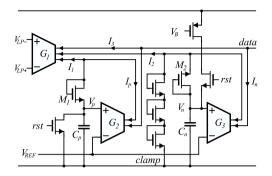

|   | 5.2<br>5.3  | 5.1.3 Measurement results15.1.4 Output resistance1Bias signal generation15.2.1 Bias cells15.2.2 Inversion limits for degenerate mirrors1Reset circuits1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10<br>13<br>14<br>15<br>15<br>16<br>18                                                 |

|   |             | 5.1.3 Measurement results15.1.4 Output resistance1Bias signal generation15.2.1 Bias cells15.2.2 Inversion limits for degenerate mirrors1Reset circuits15.3.1 Reset strategy1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18                                           |

|   |             | 5.1.3 Measurement results15.1.4 Output resistance1Bias signal generation15.2.1 Bias cells15.2.2 Inversion limits for degenerate mirrors1Reset circuits15.3.1 Reset strategy15.3.2 An effective low-power reset circuit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>19                                     |

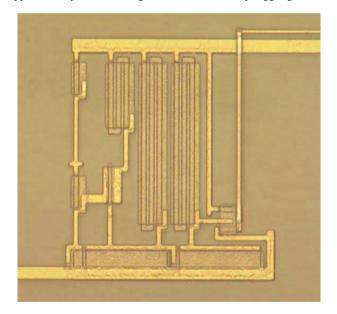

|   |             | 5.1.3Measurement results15.1.4Output resistance1Bias signal generation15.2.1Bias cells15.2.2Inversion limits for degenerate mirrors15.3.1Reset strategy15.3.2An effective low-power reset circuit15.3.3Measurements1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>18<br>19<br>21                         |

|   |             | 5.1.3 Measurement results15.1.4 Output resistance1Bias signal generation15.2.1 Bias cells15.2.2 Inversion limits for degenerate mirrors1Reset circuits15.3.1 Reset strategy15.3.2 An effective low-power reset circuit15.3.3 Measurements1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>19                                     |

| 6 | 5.3         | 5.1.3Measurement results15.1.4Output resistance1Bias signal generation15.2.1Bias cells15.2.2Inversion limits for degenerate mirrors15.2.3Reset strategy15.3.4Other circuits1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>18<br>19<br>21                         |

| 6 | 5.3         | 5.1.3       Measurement results       1         5.1.4       Output resistance       1         Bias signal generation       1         5.2.1       Bias cells       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         5.3.1       Reset strategy       1         5.3.2       An effective low-power reset circuit       1         5.3.3       Measurements       1         5.3.4       Other circuits       1         studies       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>19<br>21<br>22                         |

| 6 | 5.3<br>Case | 5.1.3       Measurement results       1         5.1.4       Output resistance       1         Bias signal generation       1         5.2.1       Bias cells       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         5.3.1       Reset strategy       1         5.3.2       An effective low-power reset circuit       1         5.3.3       Measurements       1         5.3.4       Other circuits       1         studies       1       1         Stimulator chip       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>19<br>21<br>22<br>22<br>25             |

| 6 | 5.3<br>Case | 5.1.3       Measurement results       1         5.1.4       Output resistance       1         Bias signal generation       1         5.2.1       Bias cells       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.3       Reset strategy       1         5.3.4       Other circuits       1         5.3.4       Other circuits       1         studies       1       1         Stimulator chip       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>18<br>19<br>21<br>22<br>25<br>25             |

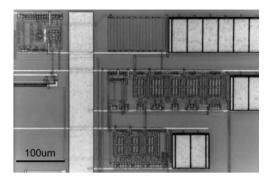

| 6 | 5.3<br>Case | 5.1.3Measurement results15.1.4Output resistance1Bias signal generation15.2.1Bias cells15.2.2Inversion limits for degenerate mirrors15.2.2Inversion limits for degenerate mirrors15.3.1Reset strategy15.3.2An effective low-power reset circuit15.3.3Measurements15.3.4Other circuits1studies1Stimulator chip16.1.1Packaging16.1.2Spatial arrangement1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>19<br>21<br>22<br>25<br>25<br>28<br>29       |

| 6 | 5.3<br>Case | 5.1.3       Measurement results       1         5.1.4       Output resistance       1         Bias signal generation       1         5.2.1       Bias cells       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.3       Reset strategy       1         5.3.4       Other circuits       1         5.3.4       Other circuits       1         studies       1       1         Stimulator chip       1       1         6.1.1       Packaging       1         6.1.3       Substrate design       1                                                                                                                                                                                                                                                                                                                                                     | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>19<br>21<br>22<br>25<br>28<br>29<br>31       |

| 6 | 5.3<br>Case | 5.1.3       Measurement results       1         5.1.4       Output resistance       1         Bias signal generation       1         5.2.1       Bias cells       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         7.2.2       Inversion limits for degenerate mirrors       1         7.3.1       Reset strategy       1         5.3.2       An effective low-power reset circuit       1         5.3.3       Measurements       1         5.3.4       Other circuits       1         5.3.4       Other circuits       1         studies       1       1         6.1.1       Packaging       1         6.1.2       Spatial arrangement       1         6.1.3       Substrate design       1         6.1.4       Coil fabrication results       1                                                                                                                                                                              | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>19<br>21<br>22<br>25<br>28<br>29<br>31<br>32 |

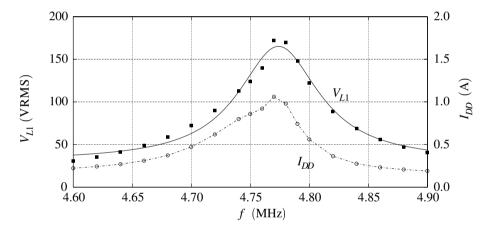

| 6 | 5.3<br>Case | 5.1.3       Measurement results       1         5.1.4       Output resistance       1         Bias signal generation       1         5.2.1       Bias cells       1         5.2.1       Bias cells       1         5.2.1       Bias cells       1         5.2.1       Bias cells       1         5.2.2       Inversion limits for degenerate mirrors       1         5.2.2       Inversion limits for degenerate mirrors       1         5.3.1       Reset strategy       1         5.3.1       Reset strategy       1         5.3.2       An effective low-power reset circuit       1         5.3.3       Measurements       1         5.3.4       Other circuits       1         5.3.4       Other circuits       1         studies       1       1         Stimulator chip       1       1         6.1.1       Packaging       1         6.1.2       Spatial arrangement       1         6.1.3       Substrate design       1         6.1.4       Coil fabrication results       1         6.1.5       Measurements       1 | 10<br>13<br>14<br>15<br>15<br>16<br>18<br>19<br>21<br>22<br>25<br>28<br>29<br>31       |

| CONTENTS |                             |                   |  |  |  |  |  |  |  |

|----------|-----------------------------|-------------------|--|--|--|--|--|--|--|

|          | 6.2.2<br>6.2.3              | Bus communication |  |  |  |  |  |  |  |

| Co       | Conclusion                  |                   |  |  |  |  |  |  |  |

| A        | A Field simulation software |                   |  |  |  |  |  |  |  |

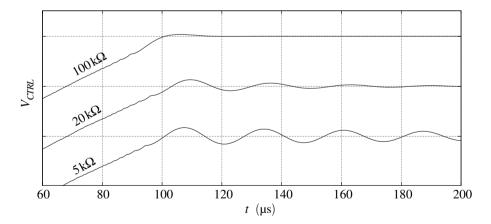

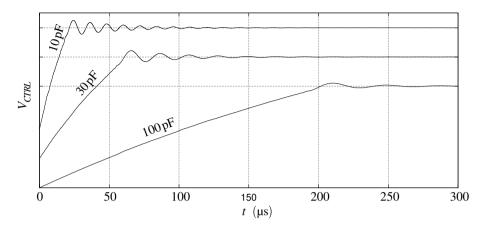

| B        | B PLL Simulation            |                   |  |  |  |  |  |  |  |

| Bib      | Bibliography                |                   |  |  |  |  |  |  |  |

| Pu       | Publications                |                   |  |  |  |  |  |  |  |

### CONTENTS

viii

# **1** INTRODUCTION

Electronic stimulation of human tissue for medical purposes has its roots in the first cardiac pacemakers. The exact date for the first use of a portable implanted pacemaker depends on the definitions of "portable" and "implanted", but some worthy candidates were taken into use around 1960. The art of neurostimulation, where electrical signals are applied to nerves in order to evoke a desired response, evolved in the early 1970s from pacemaker technology. For a long time, these were built from discrete electronics components, and later on, using general purpose integrated circuits. During the last decade or so, the focus has increasingly been on applications of custom integrated circuits for biomedical devices and all the new functionality they can provide. Microelectromechanical Systems (MEMS) have also found a plethora of applications in biomedical devices, but the focus has been aimed more at processing technology development than on circuit design.

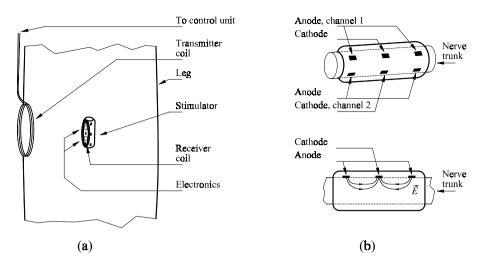

The research results presented here are the result of a cooperation between the Department of Information Technology (now Ørsted•DTU) at the Technical University of Denmark and the Center for Sensory-Motor Interaction (SMI) at Aalborg University. Much research has been carried out at SMI regarding the functioning of the nervous system, and the special discipline within the boundaries of this science which is relevant to this work is functional electrical stimulation (FES) or functional neural stimulation (FNS). The objective of FES is to generate artificial nerve signals, and by the correct application of these signals, restore functionality which has been lost due to accident or disease. Several neural stimulators have been built at SMI for stimulation of the motor system, and our work has benefited from the expertise gained in their development and use.

Space restrictions in an implanted device increase the effective cost of every additional component, in terms of usability and reliability. Every off-chip connection which must be added, because of a system function which cannot be integrated on the chip itself, contributes to the reduced reliability of the system. While circuits which reside completely on an IC die can be protected quite well against the harsh environment in the body, the connections to external components can be fragile. One of the main goals of this project has therefore been to find a way to integrate completely on silicon many of the common functions found in implants.

The requirements towards electronics in implants are quite severe in many ways, and many of them have traditionally been met by resorting to exotic IC technologies or external

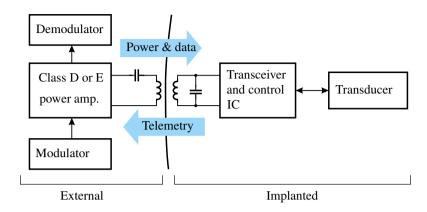

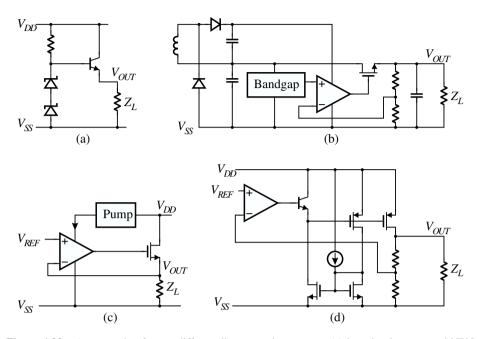

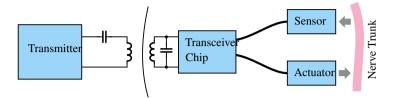

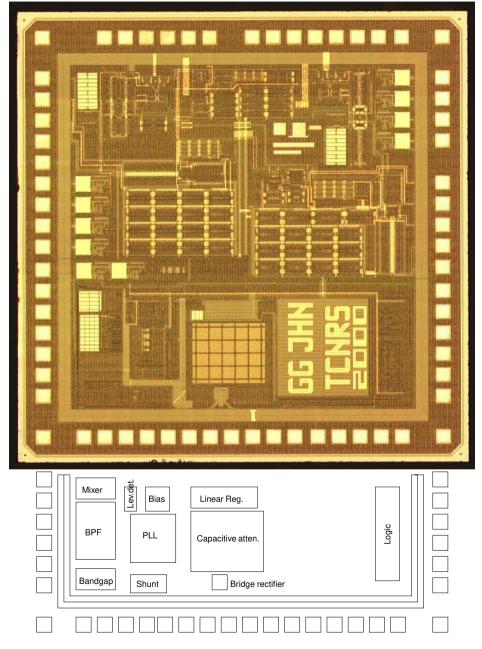

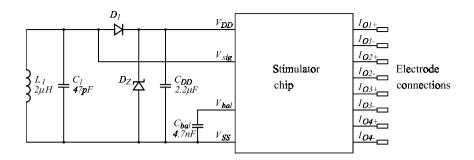

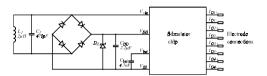

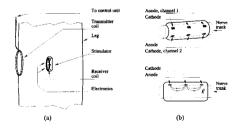

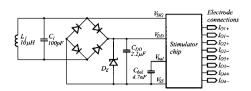

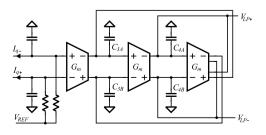

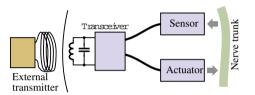

**Figure 1.1:** A block diagram showing the main part of an implanted stimulation/measurement system. The power and data is transmitted into the implant and telemetry data is extracted either by load modulating the external field or by active transmission.

components. There are however many things to be said for plain CMOS technology. The rapid development of CMOS processing technology, while driven mainly by the needs of the digital industry, helps the integration of complex biomedical systems on a single chip. The main disadvantage of the technology evolution is the ever decreasing supply voltage, but as long as the maximum voltage is at least a few threshold voltages, it is still possible to create reasonable mixed analog/digital systems. The second goal of this research has been to implement as much of as possible of the implant circuits in CMOS.

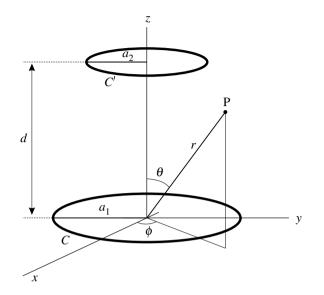

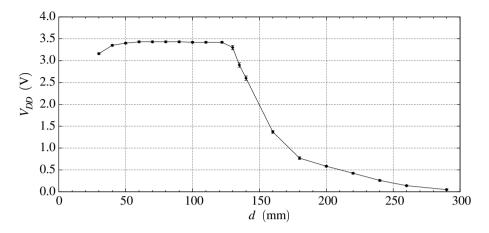

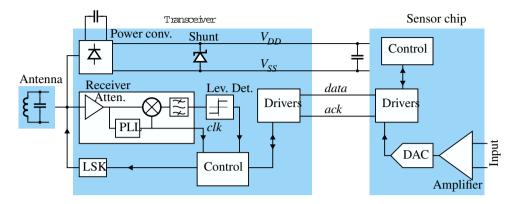

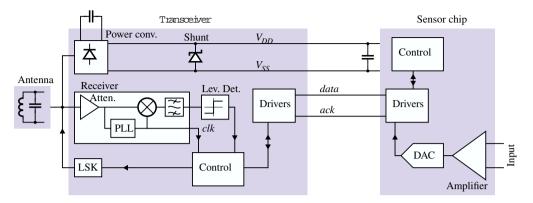

To avoid fixed electrical connections through the skin into the body, or as is the rule in pacemakers, implanted batteries which must be replaced periodically, the systems presented here are designed for use with wireless power and data transmission. The wireless power transmission is implemented in practice through the use of a so-called inductive link, which is basically a weakly coupled coreless transformer. A model of a typical arrangement is shown in figure 1.1. The primary winding of the transformer is driven by a power amplifier which induces a voltage on the implanted secondary. Typical operating frequencies are in the range 1–10MHz, but examples exist of systems which use higher or lower frequencies. The power supply for the implant is obtained by rectification and filtering of the received radio-frequency signal. The low power efficiency of this link is one of the main driving forces for low-power design in inductively coupled implants. Digital data transmission to the implant is made possible by modulating the RF carrier signal, and reverse transmission can be implemented by varying the load seen by the secondary of the transformer. This type of load shift keying (LSK) is however only possible if the coupling in the transformer is not too small.

The diagram shows two system components in the implanted part, the transceiver and control IC, and a transducer. This transducer can in principle be anything, and is not necessarily on a separate chip. In the case of electrical stimulation it would typically be an electrode connecting an on-chip current source to the nerve. In a nerve signal sensor system it could be a separate electrode and amplifier combination.

The inductive link is the subject of chapter 2. It is a key component of the system and

its characteristics influence most of the interface design of an implantable chip. The power conversion circuit, whose task it is to extract the system's supply power from the RF carrier, must be compatible with the receiver antenna design. The design of receiver circuits for a shared data/power link is also influenced to a large degree by the link.

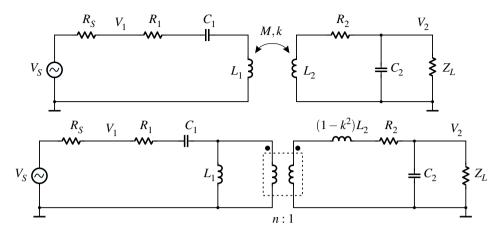

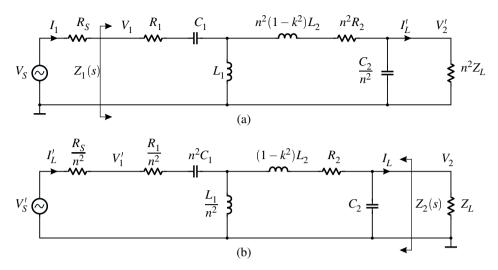

The link circuit is usually represented as a collection of lumped R, L and C elements, which is sufficiently accurate to describe the electrical circuit-level behavior. The connection between the external transmitter and the implanted system can then be described completely by a single coupling coefficient k. Such a circuit description does however have a severe disadvantage from the link designer's point of view, namely that there is no connection between the circuit description and the physical link realization. We have therefore developed in chapter 2 several expressions which provide a connection between the physical dimensions and the electrical behavior. These expressions are by necessity based on a few approximations, because of the complex dependence of mutual and self-inductances on the geometry. Experimental results did however prove that the expressions were quite accurate.

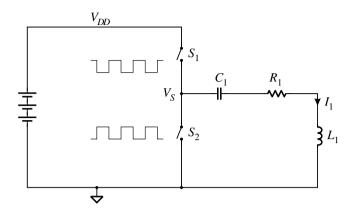

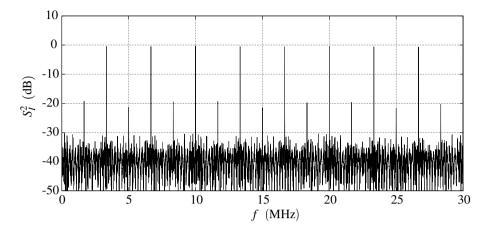

Several transmitters were designed in the course of this project, and chapter 2 also includes a description of transmitter architectures. A successful class D transmitter is described, and the influence of the transmitter design on efficiency and modulation methods is described.

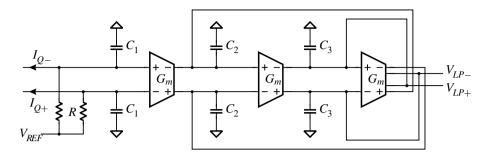

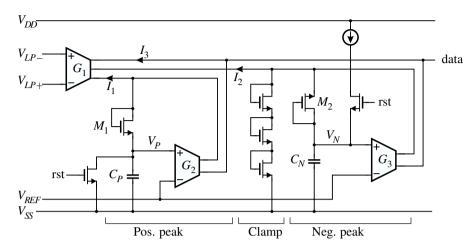

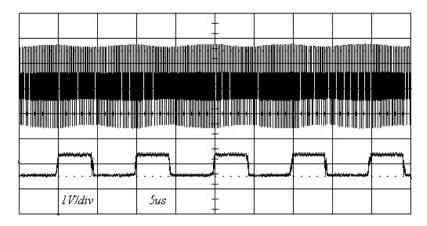

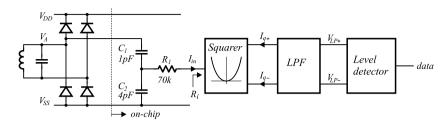

Chapter 3 treats the design of receivers for links which share data and power transmission. The design requirements for this type of link are unique in at least one respect, which is the input signal range. The input signal amplitude is similar to the supply voltage, and can actually exceed the supply range in the positive and negative directions. The option of using a separate receiver coil does exist but it should be avoided if possible because of the added interconnect complexity in the implant. The shared nature of the link means that the selected modulation method must take the power transfer into account. The best power transfer efficiency is obtained by sending a constant unmodulated carrier, but in order to transfer data, this carrier must obviously be modulated. A common method used to secure the power for the implant while still leaving room for data transfer is to send the data in bursts, with an unmodulated carrier in between. This places additional demands on the receiver design.

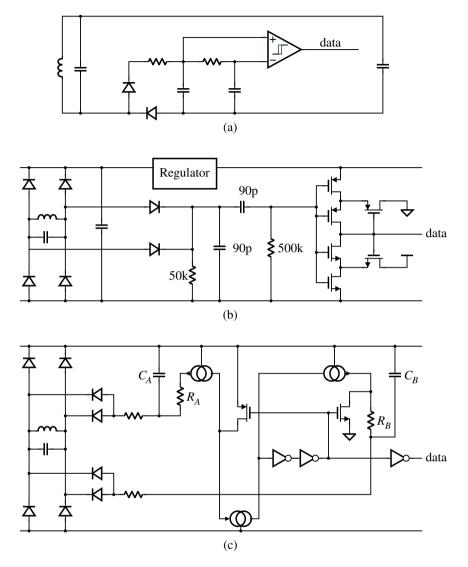

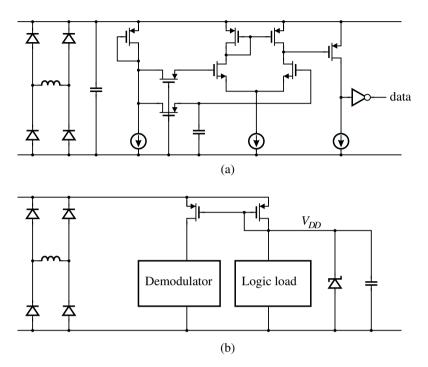

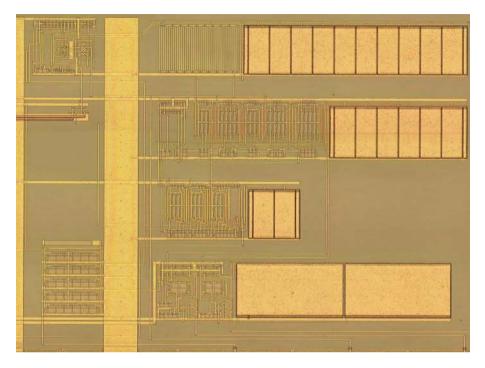

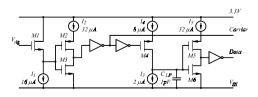

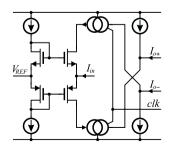

An overview of previous receiver designs is given in chapter 3, followed by new receiver designs developed by us. The design criteria were that the receivers should be compatible with burst mode data transfer, low modulation index amplitude shift keying (ASK) and adaptive detection levels. In addition, the receivers are designed for a minimum of supporting logic, especially without the DSP methods which characterize modern digital receiver designs. The omission of a DSP was justified partly because of the savings in supply current, but chiefly because the required design effort was too large for the available resources, and the research value of a traditional DSP solution is minimal.

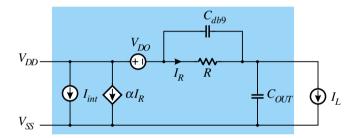

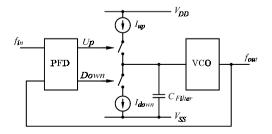

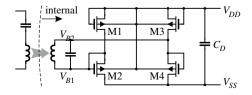

The on-chip power supply quality of implanted ICs is discussed in chapter 4, and several novel supply management circuits are presented. The supply voltage generation of inductively coupled systems is one area where external components or advanced processing steps have traditionally been used. This regards specifically the rectification of the RF carrier and overvoltage protection, which have previously been carried out on-chip by the use of floating p-n junctions and zener diodes. Since these circuit elements are not available in plain CMOS, we have developed active circuit solutions which can perform the same tasks, and are fully integrated in a CMOS technology. We present a CMOS bridge rectifier which does not suffer from parasitic effects and an active overvoltage protection circuit with a very large

shunt current range. In addition, we examine on-chip voltage regulators and their application in reducing power consumption and providing isolation between analog and digital parts of an integrated circuit.

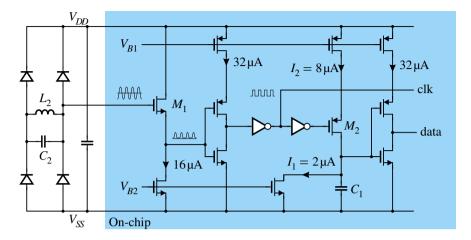

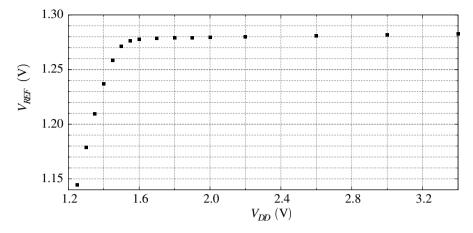

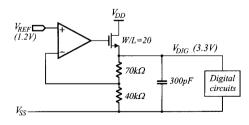

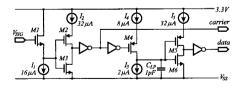

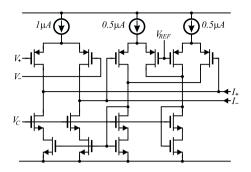

A self-contained system chip must also generate various support functions internally, such as reference voltages, bias signals and a digital power-on reset (POR). A bandgap voltage reference which can be implemented in a CMOS process is presented in chapter 5, and we show a new power-on reset circuit. The POR circuit uses very little static power, and can be implemented without any advanced analog process features, such as high-ohmic polysilicon. Design tradeoffs are also investigated for the degenerate current mirror structure, or constant- $g_m$  cell, which is often used in CMOS bandgap references and bias circuits.

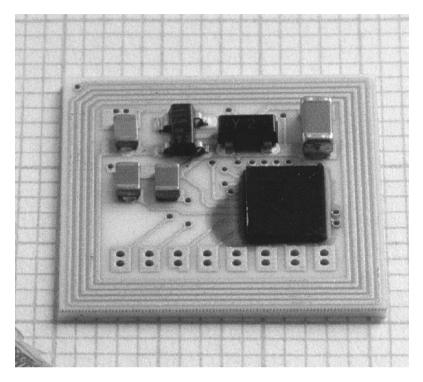

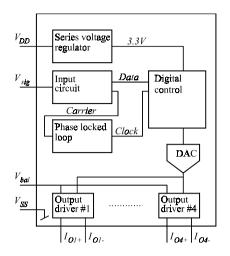

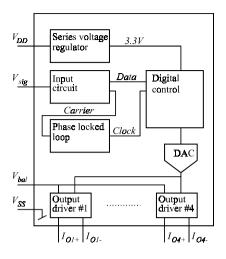

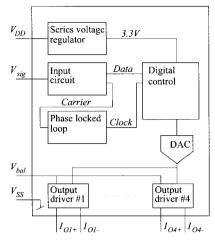

Chapter 6 shows two examples of system design for implantable devices, and emphasizes the system-level requirements which are specific to inductively coupled implants. These requirements relate mainly to the nature of the power supply, the characteristics of the data transmission and limitations in interconnect capabilities. The first example is an implantable neural stimulator chip, whose purpose is to generate stimulation pulses in response to commands transmitted by an external controller. The second example is a general transducer chip which can be used in conjunction with the generation or measurement of nerve signals. The main purpose of the transducer chip is to exploit the possibilities offered by the spatial separation of components in a neural implant.

# **2** Link design

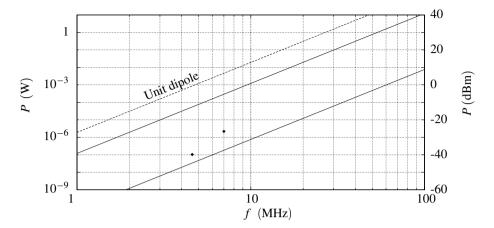

The design of the inductive link between an external transmitter and control unit and an implanted electronic device must be based on considerations of performance factors. One of these is the power consumption, which in a mobile system must be low enough that the battery change intervals are acceptable to the user. We can regard the power dissipation or loss as taking place in three locations, the transmitter power stage, the link air interface and inside the implant. No actual power dissipation takes place in the path between the transmitter and the receiver but since the unfocused power transfer and the weak coupling of the parts lead to a very low link efficiency, it must be included. The task of the transmitter is to set up at the location of the implant a modulated magnetic field which is strong enough to power the implant. Because of the inefficiency inherent in this arrangement the load placed by the implant upon the transmitter is much smaller than the other loss mechanisms in the system, the transmitter operated almost independently of the receiver. It is therefore useful to consider the transmitter as an isolated system and measure its performance by a yardstick which considers only efficiency in producing the remote field. The only real losses which need to be considered in the transmitter design are then the losses in the transmitter itself and the resistive losses in the primary LC circuit.

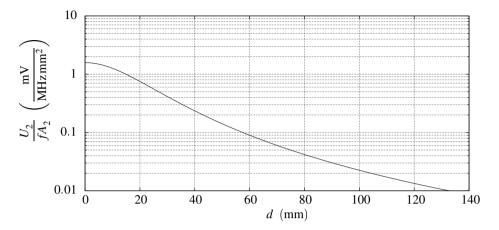

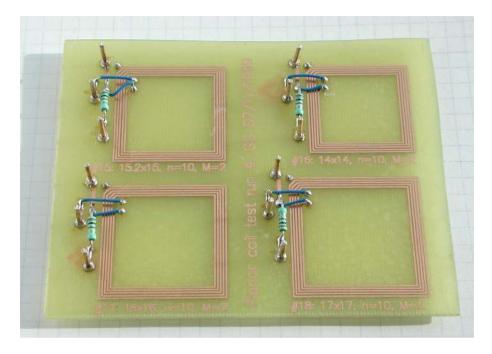

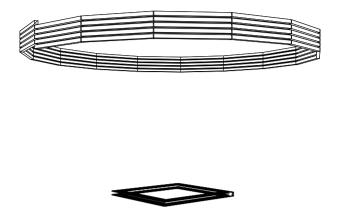

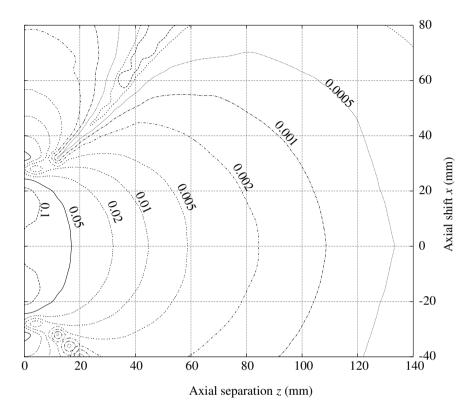

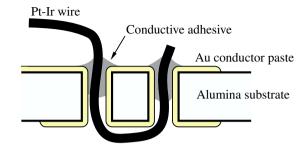

A large amount of work has been carried out on the design of coils for inductive links [37, 27], and the results of that work will not be repeated here. Much of that work has however focused on closely coupled links where the implanted device is relatively large and shallowly implanted. The coupling coefficients are therefore larger than we expect to obtain here and the loading of the primary by the secondary is more visible. A more realistic design goal is to maximize the transferred power subject to limitations in the size and quality of the implanted coil. A wide range of materials has been used in the construction of implanted coils, from hand-wound copper wire inductors to on-chip planar spiral coils made with standard metal layers [17, 44] or more exotic metallization layers [9]. We shall give an example of a planar substrate coil implemented with Au thick-film tracks on an alumina substrate.

Performance specifications of the link like power transfer, range and bandwidth are best calculated using a circuit-level description of the link. There are however a few circuit elements which can only be derived form a physical description of the system, namely the inductances of the coils and the mutual inductance or the coupling coefficient. Inductances can be calculated using analytical approximations or semi-empirical models, and we shall give

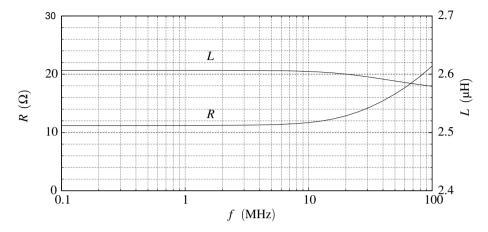

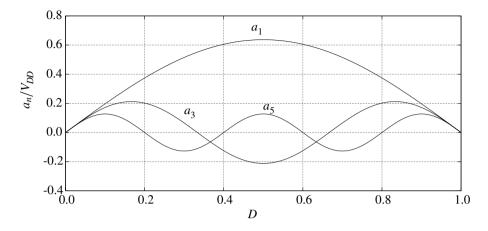

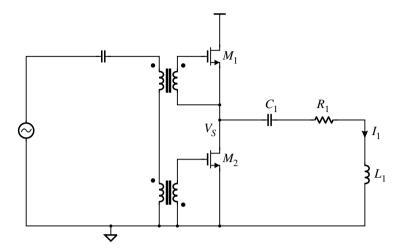

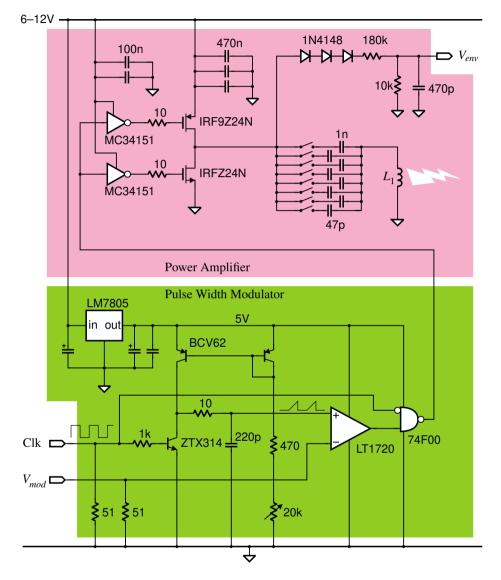

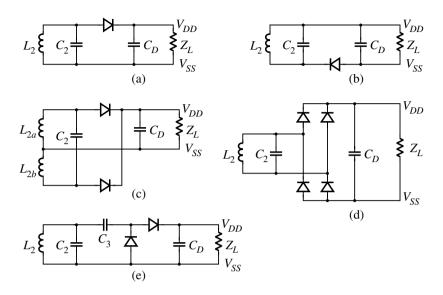

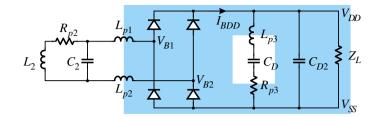

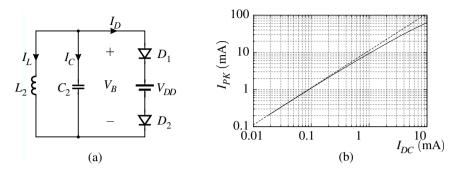

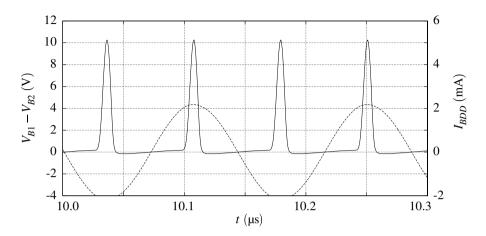

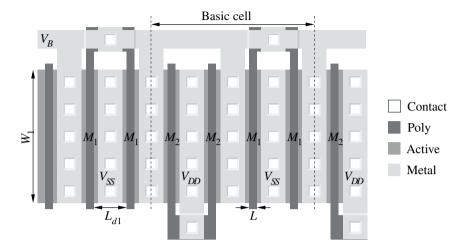

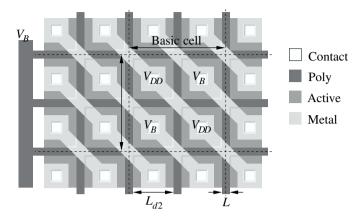

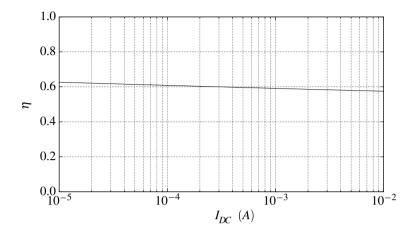

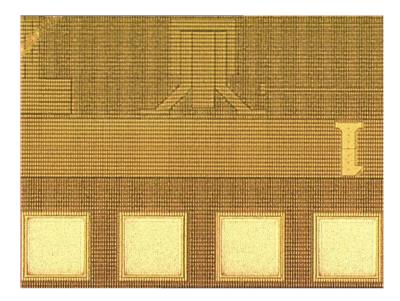

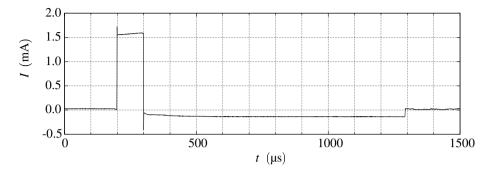

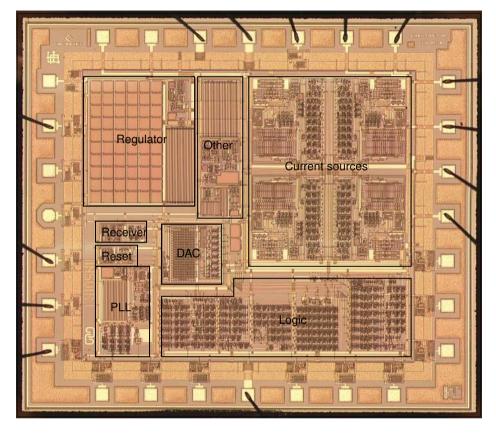

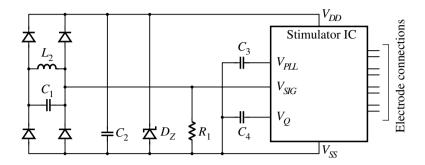

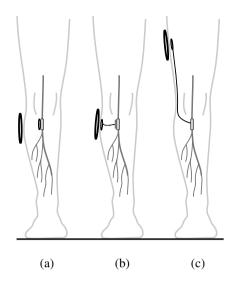

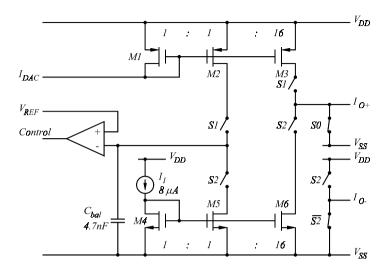

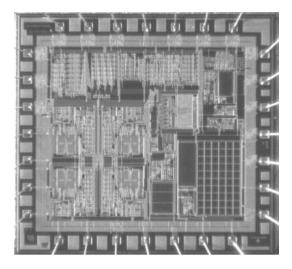

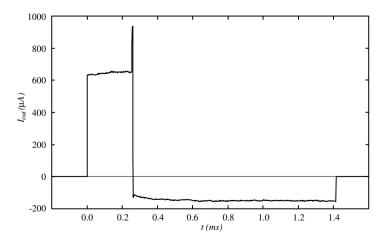

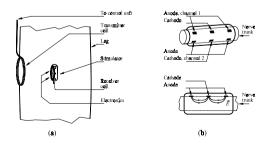

examples of those for some simple coil geometries. Another possible method is to simply build the coils and measure their inductance but this is only practical for wire coils. The fabrication of inductors on a substrate is usually too expensive and time-consuming for casual experimentation. The best option in that case is to use three-dimensional electromagnetic field simulators to obtain the inductances and loss factors for a given geometry. Most such tools can simulate inductances quite accurately, but their ability to calculate inductor losses is lacking, especially with respect to high-frequency losses in silicon substrates [74, 8]. Since the operating frequency of inductors, the losses are mostly due to bulk resistance and current crowding in the conductors. Various numerical tools can therefore be used to calculate the inductances and resistances with sufficient accuracy.