# CMOS-Compatible Surface-Micromachined Suspended-Spiral Inductors for Multi-GHz Silicon RF ICs

Jun-Bo Yoon, Member, IEEE, Yun-Seok Choi, Byeong-Il Kim, Yunseong Eo, and Euisik Yoon, Member, IEEE

Abstract—Fully CMOS-compatible, highly suspended spiral inductors have been designed and fabricated on standard silicon substrate (1 $\sim$ 30  $\Omega$ ·cm in resistivity) by surface micromachining technology (no substrate etch involved). The RF characteristics of the fabricated inductors have been measured and their equivalent circuit parameters have been extracted using a conventional lumped-element model. We have achieved a high peak Q-factor of 70 at 6 GHz with inductance of 1.38 nH (at 1 GHz) and a self-resonant frequency of over 20 GHz. To the best of our knowledge, this is the highest Q-factor ever reported on standard silicon substrate. This work has demonstrated that the proposed microelectromechanical systems (MEMS) inductors can be a viable technology option to meet the today's strong demands on high-Q on-chip inductors for multi-GHz silicon RF ICs.

Index Terms—High Q, microelectromechanical systems (MEMS) inductor, on-chip inductor, RF MEMS, silicon RF IC, surface micromachining, suspended spiral inductor.

## I. INTRODUCTION

S THE operating frequency of recent silicon RF ICs moves to the multi-GHz frequency range, it becomes difficult to achieve affordable Q-factors (>15) from on-chip inductors fabricated using conventional thin-film, planar IC processes. Recently, research has been actively carried out to find alternative technology options to address this issue including bulk micromachining [1]–[3], surface micromachining [4]–[12], and electrochemical processes [13]. Most recently, a couple of papers have reported nonconventional on-chip inductors successfully integrated with operational RF circuitries, such as a voltagecontrolled oscillator (VCO) [9], [10] and a power amplifier [11]. These on-chip inductors have been fabricated without any substrate etch, utilizing surface micromachining technology. Several variations of surface-micromachined inductors have been investigated including monolithic solenoid inductors [4], [7], [11], suspended spiral inductors [5], [6], [8], [10], and a vertical spiral inductor [12]. Among these, the suspended spiral inductors have shown higher Q-factors on silicon substrates so far [8].

Manuscript received June 19, 2002. This work was supported by a National Research Laboratory Grant from The Ministry of Science and Technology, Korea. The review of this letter was arranged by Editor S. Kawamura.

Digital Object Identifier 10.1109/LED.2002.803767.

TABLE I

(a) Physical Dimension With Major RF Performance and

(b) Lumped-Element Parameters of the Fabricated Inductors

| Device<br>Number | N<br>number<br>of turns | D (µm)<br>outmost<br>diameter | W<br>width<br>(μm) | pitch (µm)  | L (<br>lGI<br>(nI | Īz       |     | L<br>dicted*<br>nH) | Peak Q      | Peak-Q<br>frequency<br>(GHz) |

|------------------|-------------------------|-------------------------------|--------------------|-------------|-------------------|----------|-----|---------------------|-------------|------------------------------|

| 1                | 1.5                     | 330                           | 30                 | 80          | 1.3               | 1.38     |     | 1.32                | 70          | 6                            |

| 2                | 1.25                    | 430                           | 30                 | 80          | 1.8               | 1.86     |     | 1.56                | 49          | 3.4                          |

| 3                | 2.25                    | 430                           | 30                 | 80          | 2.5               | 2.59     |     | 2.44                | 38          | 2.6                          |

| 4                | 3.25                    | 430                           | 30                 | 50          | 4.1               | 4.10     |     | 3.74                | 32          | 2.2                          |

|                  |                         |                               |                    |             | (a)               |          |     |                     |             |                              |

| Device<br>Number | Ls<br>(nH)              | Rs (Ω)<br>f in GHz            | Cf<br>(fF)         | Ci1<br>(fF) | Rsi1<br>(Ω)       | Cs<br>(f |     | Ci2<br>(fF)         | Rsi2<br>(Ω) | Csi2<br>(fF)                 |

| 1                | 1.34                    | $0.27\sqrt{f}$                | 1.14               | 11.6        | 275               | 1        | .0  | 90.5                | 332         | 10.2                         |

| 2                | 1.77                    | $0.39\sqrt{f}$                | 0.82               | 20.2        | 193               | 27.6     |     | 92.2                | 222         | 21.2                         |

| 3                | 2.52                    | $0.64\sqrt{f}$                | 0                  | 25.8        | 230               | 34.4     |     | 160                 | 167         | 20.3                         |

| 4                | 3.90                    | $0.99\sqrt{f}$                | 0                  | 40.0        | 199               | 43       | 3.8 | 184                 | 148         | 16.7                         |

<sup>\*</sup>The predicted L is calculated from [15]

Other previous techniques for improving Q-factors were listed and compared in our earlier publication [7].

Recently, we have reported a new microelectromechanical systems (MEMS) fabrication process developed for RF and microwave applications [14]. This process allows the fabricating of arbitrary-shaped, highly suspended metal microstructures that are fully CMOS-compatible and manufacturable in terms of process stability and structural robustness. In this letter, we newly report the RF performance and model parameters of the suspended spiral inductors fabricated on the standard silicon substrate using our new fabrication technology.

## II. DESIGN AND FABRICATION

In order to evaluate and extract model parameters, various rectangular spiral inductors have been designed and fabricated. Table I lists their number of turns (N), outmost diameter (D), line pitch (P), and line width (W). These inductor structures are suspended by two signal posts of  $20~\mu\mathrm{m}$  in diameter without any additional mechanically supporting posts in order to minimize substrate coupling [8], sacrificing structural robustness. However, we have observed that even a 10~000- $\mu\mathrm{m}$ -long meander line is suspended well by only two signal posts without any structural deformation and instability after being fabricated by using all the standard routine processes such as dipping, rinsing, and blowing. The inductors have been suspended by  $50~\mu\mathrm{m}$  (based on the suggested height in [8]) over the  $1{\sim}30~\Omega$ -cm silicon substrate passivated by  $1{-}\mu\mathrm{m}$ -thick thermal oxide for electrical isolation. The inductors have been made of  $10{-}\mu\mathrm{m}$ -thick

J.-B. Yoon, Y.-S. Choi, B.-I. Kim, and E. Yoon are with the Division of Electrical Engineering, Department of Electrical Engineering and Computer Science, Korea Advanced Institute of Science and Technology (KAIST), Taejon 305-701, Korea (e-mail: jbyoon@ee.kaist.ac.kr).

Y. Eo is with the LG Electronics Institute of Technology, Seoul 137-724, Korea.

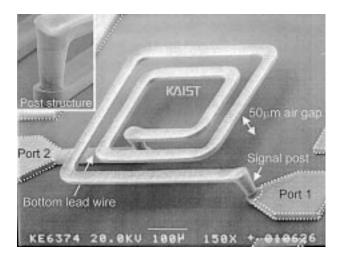

Fig. 1. SEM microphotograph of the highly suspended MEMS spiral inductor fabricated on standard silicon by using a new CMOS-compatible surface micromachining technology. The white dotted line illustrates the open-pad pattern utilized in de-embedding procedure.

electroplated copper in order to significantly minimize metal ohmic loss and ensure structural robustness. We observed that 5- $\mu$ m-thick copper inductors were occasionally deformed after the fabrication process.

The proposed fabrication process has utilized a special three-dimensional (3-D) photoresist mold, which is made of a single-coated positive-tone thick-photoresist layer (AZ9260) with a deep recess for signal posts and a shallow recess for suspended inductor structure, utilizing a double exposure (deep and shallow) and a single development [14]. The shallow exposure depth, which will determine the suspension height of the spiral inductor, has been controlled within  $\pm 10\%$  process variation, repeatedly. Once the 3-D photoresist mold has been fabricated, the two recess regions can be sequentially filled up with copper by a combination of electroplating, vacuum deposition, and mechanical polishing. Finally, the 3-D photoresist mold has been removed in acetone to release the air-suspended spiral inductor. The process variation in inductor thickness has been measured less than  $\pm 15\%$ , which might cause inductance variation of less than  $\pm 3\%$  [15]. The overall run-to-run inductance variation has been measured as less than  $\pm 5\%$ . All the processes have been completed at low temperature below 120 °C without any substrate etch, making the technology fully CMOS-compatible. More details about the fabrication process can be found in [14].

# III. RESULTS AND DISCUSSION

Fig. 1 shows the SEM microphotograph of the fabricated inductor, clearly revealing the flat and smooth surface of the suspended inductor together with robust post structure. Due to the excellent planarization capability of the sacrificial photoresist mold, the suspended structure has not shown any imprint of the bottom lead wire on the suspended metal lines, while these imprints can be found in the previous work [5]. For structural robustness, chip-dropping tests have been carried out and have shown no damage in the suspended structure from SEM inspection. Rigorous industrial reliability tests for shock and vibration are being undertaken and will be reported elsewhere.

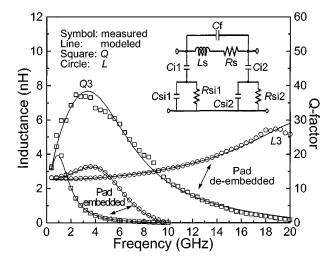

Fig. 2. Measured, de-embedded characteristics of inductance (L) and Q-factor (Q) of the fabricated inductors. The definitions of L and Q used in this work are also shown.

The on-wafer RF measurement has been performed from 0.2 GHz to 20 GHz using an HP 8510C network analyzer, coplanar GSG probes, a Cascade microwave probe station, and a CS-5 calibration substrate. The calibration has been performed up to the probe tips. The de-embedding of pad parasitics has been carried out with special care since the pads occupy large contact areas on the lossy silicon substrate. These pads are used only for inductor characterization and will not be included in the real on-chip integration. Fig. 1 also illustrates the open-pad pattern (white dotted line) employed in this work. Note that the open-pad pattern excludes the substrate-contact area of the posts and the bottom lead-wire, making the de-embedded data realistic. The pad de-embedding procedure has been done by subtracting measured two-port Y-parameters of the open-pad pattern from those of the pad-embedded inductor [16].

Fig. 2 shows the de-embedded inductance (L) and Q-factor (Q) characteristics of the four sample inductors accompanying with their definitions used in this work. Owing to the thick metal line and sufficient air gap from the lossy substrate, two major losses (ohmic and substrate) have been reduced remarkably. In consequence, we have achieved the highest peak Q-factor ever reported on the standard silicon substrate, which is 70 at 6 GHz with inductance of 1.38 nH (at 1 GHz) and a self-resonant frequency of over 20 GHz. The predicted inductance values listed in Table I has been calculated from [15]. As inductance increases, Q-factor decreases at a given frequency. This is because capacitive coupling increases between the substrate and the longer suspended metal lines, ultimately degrading both the peak Q value and peak-Q frequency simultaneously. All the inductors show fairly flat inductance and high Q-factor (>20) up to 5 GHz, which is a desirable characteristic required in today's multi-GHz silicon RF ICs.

The fabricated inductors have been modeled using a conventional on-chip inductor model [17], [18], as shown in Fig. 3. All the model parameters were extracted using HP-EEsof Libra and they are listed in Table I. In this model, Ls and Rs represent the series inductance and resistance, respectively. The metal skin-depth effect is taken into account in Rs. Cf models the

Fig. 3. Measured and modeled, pad-embedded and de-embedded characteristics of the fabricated inductor. The conventional lumped-element model used in this work is also shown.

overlap capacitance between the suspended spiral metal lines and the underlying bottom lead wire, which is negligible in this highly suspended structure as can be seen in Table I. Ci1 and Ci2 represent the air—gap capacitance between the spiral and the substrate, each of which increases as the length of the spiral increases. Note that Ci2 is fairly greater than Ci1 for the bottom lead wire. The silicon substrate losses are modeled by Rsi1, Csi1 and Rsi2, Csi2.

Fig. 3 shows both measured and modeled characteristics of the sample inductor as well as pad-embedded and de-embedded characteristics. As can be seen in Fig. 3, the conventional model represents L and Q characteristics of the fabricated MEMS inductors very well up to over 10 GHz, which is important for the fabricated MEMS inductors to be utilized in designing MEMS-integrated RF circuits in multi-GHz frequencies.

For a packaging issue, we have tested an encapsulation of the suspended inductor in a transparent silicone encapsulant, which has been spincoated into the finished and freestanding inductors. It is observed that the fabricated suspended structures maintain their original shape without any deformation after encapsulation. More substantial characteristic impact on Q-degradation due to the finite dielectric constant of the encapsulant is now being investigated.

# IV. CONCLUSION

Highly suspended MEMS spiral inductors have been fabricated and fully characterized with a conventional lumped-element model. The fabricated inductors have shown high Q-factors of up to 70 on standard silicon substrate in multi-GHz frequency ranges. The fabrication technology developed in this work is fully CMOS-compatible and does not involve any substrate etch. We believe the integration of these inductors onto the conventional RF circuits will lead a quantum leap for next-generation high-performance single-chip silicon RF ICs.

#### ACKNOWLEDGMENT

The authors would like to thank K. Han for initial RF measurement, I.-J. Cho for SEM pictures, and Prof. S. Hong for supporting HP-EEsof Libra.

#### REFERENCES

- R. P. Ribas, J. Lescot, J.-L. Leclercq, J. M. Karam, and F. Ndagijimana, "Micromachined microwave planar spiral inductors and transformers," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1326–1335, Aug. 2000

- [2] H. Jiang, Y. Wang, J.-L. A. Yeh, and N. C. Tien, "On-chip spiral inductors suspended over deep copper-lined cavities," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 2415–2423, Dec. 2000.

- [3] N. P. Pham, P. M. Sarro, K. T. Ng, and J. N. Burghartz, "IC-compatible two-level bulk micromachining process module for RF silicon technology," *IEEE Trans. Electron Devices*, vol. 48, pp. 1756–1764, Aug. 2001.

- [4] Y.-J. Kim and M. G. Allen, "Surface micromachined solenoid inductors for high frequency applications," *IEEE Trans. Comp., Packag., Manu*fact. Technol. C, vol. 21, pp. 26–33, Jan. 1998.

- [5] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "High-performance three-dimensional on-chip inductors fabricated by novel micromachining technology for RF MMIC," in *IEEE Int. Microwave Symp. Dig.*, June 1999, pp. 1523–1526.

- [6] J. Y. Park and M. G. Allen, "High Q spiral-type microinductors on silicon substrates," *IEEE Trans. Magn.*, vol. 35, pp. 3544–3546, Sept. 1999.

- [7] J.-B. Yoon, B.-K. Kim, C.-H. Han, E. Yoon, and C.-K. Kim, "Surface micromachined solenoid on-Si and on-glass inductors for RF applications," *IEEE Electron Device Lett.*, vol. 20, pp. 487–489, Sept. 1999.

- [8] J.-B. Yoon, C.-H. Han, E. Yoon, and C.-K. Kim, "Monolithic high-Q overhang inductors fabricated on silicon and glass substrates," in *IEDM Tech. Dig.*, Dec. 1999, pp. 753–756.

- [9] J. W. M. Rogers, V. Levenets, C. A. Pawlowicz, N. G. Tarr, T. J. Smy, and C. Plett, "Post-processed Cu inductors with application to a completely integrated 2-GHz VCO," *IEEE Trans. Electron Devices*, vol. 48, pp. 1284–1287, June 2001.

- [10] E.-C. Park, J.-B. Yoon, S. Hong, and E. Yoon, "A 2.6 GHz low phasenoise VCO monolithically integrated with high Q MEMS inductors," in 28th Eur. Solid-State Circuits Conf., Sept. 2002.

- [11] Y. E. Chen, Y. K. Yoon, J. Laskar, and M. Allen, "A 2.4 GHz integrated CMOS power amplifier with micromachined inductors," in *IEEE Int. Microwave Symp. Dig.*, June 2001, pp. 523–526.

- [12] J. Zou, J. G. Nickel, D. Trainor, C. Liu, and J. E. Schutt-Aine, "Development of vertical planar coil inductors using plastic deformation magnetic assembly (PDMA)," in *IEEE Int. Microwave Symp. Dig.*, June 2001, pp. 193–196.

- [13] H.-S. Kim, D. Zheng, A. J. Becker, and Y.-H. Xie, "Spiral inductors on Si p/p+ substrates with resonant frequency of 20GHz," *IEEE Electron Device Lett.*, vol. 22, pp. 275–277, June 2001.

- [14] J.-B. Yoon, B.-I. Kim, Y.-S. Choi, and E. Yoon, "3-D lithography and metal surface micromachining for RF and microwave MEMS," in *IEEE Int. MEMS Conf. Tech. Dig.*, Jan. 2002, pp. 673–676.

- [15] H. M. Greenhouse, "Design of planar rectangular microelectronic inductors," *IEEE Trans. Parts, Hybrids, Packag.*, vol. PHP-10, pp. 101–109, June 1974.

- [16] P. J. van Wijnen, H. R. Claessen, and E. A. Wolsheimer, "A new straight-forward calibration and correction procedure for 'on wafer' high frequency S-parameter measurements (45MHz–18GHz)," in IEEE Bipolar Circuits and Technology Meeting Tech. Dig., 1987, pp. 70–73.

- [17] K. B. Ashby, I. A. Koullias, W. C. Finley, J. J. Bastek, and S. Moinian, "High Q inductors for wireless applications in a complementary silicon bipolar process," *IEEE J. Solid-State Circuits*, vol. 31, pp. 4–9, Jan. 1996.

- [18] C. P. Yue, C. Ryu, J. Lau, T. H. Lee, and S. S. Wong, "A physical model for planar spiral inductors on silicon," in *IEDM Tech. Dig.*, Dec. 1996, pp. 155–158.