# CMOS-RC Colpitts Oscillator Design Using Floating Fractional-Order Inductance Simulator

KARTCI, A.; HERENCSÁR, N.; BRANČÍK, L.; SALAMA, K. N.

Proceedings of the 2018 61st IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 905-908

eISBN: 978-1-5386-7392-8

ISSN: 1558-3899

DOI: https://doi.org/10.1109/MWSCAS.2018.8623859

Accepted manuscript

©2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. KARTCI, A.; HERENCSÁR, N.; BRANČÍK, L.; SALAMA, K. N., " CMOS-RC Colpitts Oscillator Design Using Floating Fractional-Order Inductance Simulator ", Proceedings of the 2018 61st IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 905-908, 2019. DOI: 10.1109/MWSCAS.2018.8623859. Final version is available at https://ieeexplore.ieee.org/document/8623859

# CMOS-RC Colpitts Oscillator Design Using Floating Fractional-Order Inductance Simulator

Aslihan Kartci<sup>1,2</sup>, Norbert Herencsar<sup>1</sup>, Lubomir Brancik<sup>2</sup>, and Khaled N. Salama<sup>3</sup>

<sup>1</sup>Department of Telecommunications / <sup>2</sup>Department of Radio Electronics, Brno University of Technology, Brno, Czech Republic <sup>3</sup>Computer, Electrical and Mathematical Sciences & Engineering Division, King Abdullah University of Science and Technology, Thuwal, Saudi Arabia

Emails: {kartci; herencsn; brancik}@feec.vutbr.cz; khaled.salama@kaust.edu.sa

Abstract—This paper deals with CMOS fractional-order inductance (FoL) simulator design and its utilization in 2.75<sup>th</sup>order Colpitts oscillator providing high frequency of oscillation. The proposed floating FoL is composed of two unity-gain current followers (CF±s), two inverting voltage buffers, a transconductor, and a fractional-order capacitor (FoC) of order 0.75, while the input intrinsic resistance of CF± is used as design parameter instead of passive resistor. The resulting equivalent inductance value of the FoL can be adjusted via order of FoC, which was emulated via 5<sup>th</sup>-order Foster II RC network and values optimized using modified least squares quadratic method. In frequency range 138 kHz – 2.45 MHz the  $L_{\gamma}$  shows ±5 degree phase angle deviation. Theoretical results are verified by SPICE simulations using TSMC 0.18 µm level-7 LO EPI SCN018 CMOS process parameters with ±1 V supply voltages.

# Keywords—Colpitts oscillator; fractional-order capacitor; FoC; fractional-order inductor; FoL; fractional-order oscillator

## I. INTRODUCTION

At present, the number of applications of fractional calculus rapidly grows. It is due to the fact that this powerful mathematical tool allows us to describe and model a real-world phenomenon more accurately than via classical "integer" methods. In general, most of the real-world phenomena are of fractional origin, however, for many of them the fractionality is insignificant. Typical issues solved in fractional-order domain are the voltage-current relation of a semi-infinite lossy transmission line [1], oscillation of the linear/non-linear system, where the oscillation gives the ideal response [2], impedance response of the tissues especially in bioengineering [3], robustness of the systems in control theory [4], synchronization of nonlinear fractional-order chaotic systems [5], and many others [6] (and references cited therein). Unless integer-order inductors or their emulators [6], fractional-order ones are not commercially available and need to be emulated through active building blocks [7], [8] or resistor-inductor networks [9]. Two most popular high-frequency oscillators employing inductors are the Colpitts and Hartley oscillators [10], [11] and both were investigated under some of the following design conditions in integer-order cases: (i) power consumption, (ii) supply voltage, (iii) transistor current density, (iv) sizing (area, aspect ratio, finger width), (v) inductance, (vi) quality factor, and (vii) considering the full models of the transistors available within the process design kit. However, in open literature, recently few studies are reported on fractionalorder Hartley oscillator [12], while there is no available fractional-order Colpitts oscillator at present. The mathematical definitions of the fractional-order oscillation criteria are known and already investigated [13]. The implementation of such oscillators evidently require the use of a fractional-order capacitor (FoC), which brings to researchers several design features such as possibility of changing the frequency of oscillation (FO) and condition of oscillation (CO). Therefore, this study aims to investigate the fractional-order case of Colpitts oscillator employing a compact CMOS fractionalorder inductance (FoL) simulator, in which the FoC with 12 nF·s<sup>-0.25</sup> value is emulated via 5<sup>th</sup>-order Foster II RC network. The behavior of proposed FoL and Colpitts oscillator was verified by SPICE simulations.

# II. A FRACTIONAL-ORDER COLPITTS OSCILLATOR

### A. Introduction of the General Fractional Case

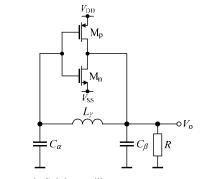

The Colpitts oscillator is an LC oscillator, which contains a tuned tank circuit consisting of one inductor and two capacitors; the two capacitors therein are making a capacitive voltage divider. Colpitts oscillator implemented using two CMOS-based transconductors is shown in Fig. 1, wherein the three terminal LC networks are connected in such a manner that between two nodes of the three terminal LC circuits, a transconductor of gain  $-g_m$  is connected, whereas the common node of the two capacitors  $C_i$  for  $i = \{\alpha, \beta\}$  with FoCs (i.e.  $C_{\alpha}$  and  $C_{\beta}$ ) having impedance  $Z_{\alpha}(s) = 1/(s^{\alpha}C_{\alpha})$ ,

Fig. 1. Voltage-mode Colpitts oscillator.

The article is based on work from the COST Action CA15225, a network supported by COST (European Cooperation in Science and Technology). Research described in this paper was financed by the National Sustainability Program under grant no. LO1401 and by the Czech Science Foundation under grant no. 16-06175S. For the research, infrastructure of the SIX Center was used.

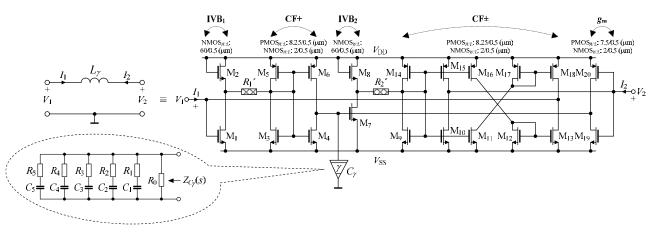

Fig. 2. Proposed CMOS fractional-order inductance simulator including RC network emulating fractional-order capacitor.

$Z_{\beta}(s) = 1/(s^{\beta}C_{\beta})$ , and FoL  $(L_{\gamma})$  with impedance of  $Z_{\gamma}(s) = s^{\gamma}L_{\gamma}$ , routine circuit analysis provides the following description of this fractional-order system [13]:

$$\begin{pmatrix} d^{\alpha}V_{C_{\alpha}}/dt^{\alpha} \\ d^{\beta}V_{C_{\beta}}/dt^{\beta} \\ d^{\gamma}I_{L_{\gamma}}/dt^{\gamma} \end{pmatrix} = \begin{pmatrix} 0 & 0 & 1/C_{\alpha} \\ -g_{m}/C_{\beta} & -1/RC_{\beta} & -1/C_{\beta} \\ -1/L_{\gamma} & 1/L_{\gamma} & 0 \end{pmatrix} \begin{pmatrix} V_{C_{\alpha}} \\ V_{C_{\beta}} \\ I_{L_{\gamma}} \end{pmatrix}.$$

(1)

Hence, the characteristic equation (CE) from (1) has the following general form:

CE:

$$s^{\alpha+\beta+\gamma}RC_{\alpha}C_{\beta}L_{\gamma} + s^{\alpha+\gamma}C_{\alpha}L_{\gamma} + s^{\alpha}RC_{\alpha} + s^{\beta}RC_{\beta} + Rg_{m} + 1 = 0.$$

<sup>(2)</sup>

An ideal third-order Colpitts oscillator corresponds to setting  $\alpha = \beta = \gamma = 1$ , which results in the well-known CO:  $g_m R = C_1/C_2$  and FO:  $\omega = \sqrt{1/(LC_{eff})}$ , where  $C_{eff} = C_1C_2/(C_1+C_2)$  and it can be proved from (1) and (2).

# B. Fractional-Order Inductor Case

Considering  $C_1$  and  $C_2$  as integer-order capacitors (i.e.  $C_{\alpha} \Rightarrow C_1$  and  $C_{\beta} \Rightarrow C_2$ ) and inductor  $L_{\gamma}$  remains as a fractional-order inductor, the general CE in (2) turns to:

$$CE_{\gamma}: s^{2+\gamma}RC_{1}C_{2}L_{\gamma} + s^{1+\gamma}C_{1}L_{\gamma} + sR(C_{1}+C_{2}) + Rg_{m} + 1 = 0, \quad (3)$$

and substituting  $s = j\omega$  therein, the derived CO<sub> $\gamma$ </sub> and FO<sub> $\gamma$ </sub> are respectively given by:

$$CO_{\gamma} : R = -\frac{1 + \omega^{1+\gamma} C_{1} L_{\gamma} \cos\left[0.5\pi(1+\gamma)\right]}{\omega^{2+\gamma} C_{1} C_{2} L_{\gamma} \cos\left[0.5\pi(2+\gamma)\right] + g_{m}} = -\frac{\omega^{1+\gamma} C_{1} L_{\gamma} \sin\left[0.5\pi(1+\gamma)\right]}{\omega^{2+\gamma} C_{1} C_{2} L_{\gamma} \sin\left[0.5\pi(2+\gamma)\right] + \omega(C_{1}+C_{2})},$$

(4)

$$FO_{\gamma} : \omega^{2+\gamma} C_{1}^{2} C_{2} L_{\gamma}^{2} - \omega C_{1} C_{2} L_{\gamma} \sin(0.5\pi\gamma) - \omega C_{1} L_{\gamma} (C_{1} + C_{2}) \cos(0.5\pi\gamma) + (5) + \omega^{-1} C_{1} L_{\gamma} g_{m} \sin(0.5\pi\gamma) - \omega^{-\gamma} (C_{1} + C_{2}) = 0.$$

As it is evident, the proposed oscillator offers independent tuning of the frequency and condition of oscillation.

#### III. REALIZATION OF PROPOSED CIRCUITS

In analog electronics, due to the large silicon area, cost, and lack of electronically tunability, CMOS-based inductance simulators are used [15]. The CMOS implementation of the proposed FoL simulator is shown in Fig. 2. It consists from two inverting voltage buffers (IVBs), two unity-gain current followers (CFs), and one simple transconductor. In brief, for example IVB<sub>1</sub> assuming that both NMOS work in saturation region,  $V_{\text{THN1}} = V_{\text{THN2}},$  $+V_{\rm DD} = -V_{\rm SS},$ and process transconductance parameters  $k_{\rm N1} = k_{\rm N2}$ , voltage transfer can be described simply as  $V_{\rm out} = -V_{\rm in}$ . Thus, it behaves as a linear IVB without DC offset. In order to keep the  $M_1$  in saturation region the condition  $V_{in} < V_{out} + V_{THN1}$  should be satisfied. Note that the M<sub>2</sub> always operates in saturation region since its drain and gate terminals are connected. Considering CF± structures used in Fig. 2, it can be observed that both were designed by superposition of top PMOS sourcing mirrors and bottom NMOS sinking mirrors. However, from another viewpoint this configuration may be seen as a cascade of two CMOS inverters with the first one having shorted input and output. In general, CF± can be described as  $V_{in} = R_{CF ink}I_{in}$  and  $I_{out\pm} = \pm I_{in}$  for  $k = \{1, 2\}$ . Here,  $R_{CF ink}$  denotes intrinsic input resistance, which can be set via supply voltages. Finally, the currentvoltage relationship of used transconductor is  $I_{out} = -g_m V_{in}$ . Detailed description of used active building blocks (ABBs) can be find in [16], while transistors main parameters obtained after re-design are listed in Table I.

Considering described ABBs, one capacitor, and assuming matching condition  $g_m = 1/R_{\text{CF}_in1}$ , while  $R_{\text{CF}_ink} \approx R_k'$ , routine circuit analysis yields the following short circuit admittance matrix  $[Y_L] = \frac{1}{r_m} \begin{bmatrix} +1 & -1 \\ -1 \end{bmatrix}$ , from which  $L_r = R_1 R_2 C_r$ . As it

natrix

$$[Y_{L_{\gamma}}] = \frac{1}{s^{\gamma} L_{\gamma}} \begin{bmatrix} +1 & -1 \\ -1 & +1 \end{bmatrix}$$

, from which  $L_{\gamma} = R_1' R_2' C_{\gamma}$ . As it

can be seen the equivalent inductance value is adjustable by order of the FoC (or phase). The Foster II structure has been used to realize the FoC with a fractional-order of  $\gamma = 0.75$ . Component values obtained via modified least squares quadratic (MLSQ) method. Parameters of both  $C_{0.75}$  and subsequently  $L_{0.75}$  emulators are summarized in Table II.

Fig. 3. Ideal and simulated (a) phase and (b) pseudo-capacitance responses of 0.75-order fractional-order capacitor.

#### IV. SIMULATION RESULTS

The behavior of the ABBs used in CMOS implementation of the FoL simulator and subsequently in Colpitts oscillator in Figs. 1 and 2 have been verified by SPICE simulations with DC power supply voltages  $+V_{DD} = -V_{SS} = 1$  V. In the design, transistors are modeled by the TSMC 0.18 µm level-7 LO EPI SCN018 CMOS process parameters ( $V_{THN} = 0.3725$  V,  $\mu_N = 259.5304$  cm<sup>2</sup>/(V·s),  $V_{THP} = -0.3948$  V,  $\mu_P = 109.9762$ cm<sup>2</sup>/(V·s),  $T_{OX} = 4.1$  nm) [17]. The aspect ratios of transistors in structures and their main parameters obtained with AC and DC analyses are listed in Table I. The equivalent intrinsic input resistance and the transconductance gain value are set  $g_m \approx (1/R_k' + 1/R_{IVB_out}) \approx 835 \mu A/V$  in order to fulfill the required parameter matching.

In order to verify the workability of the proposed Colpitts oscillator employing FoL simulator shown in Fig. 2, first of all the phase and pseudo-capacitance response of the FoC with an order  $\gamma = 0.75$  and value  $C_{\gamma} = 12 \text{ nF} \cdot \text{s}^{-0.25}$  (300 pF @ 407.5 kHz), emulated via 5<sup>th</sup>-order Foster II RC network, which has an admittance in following form:  $Y_{C_{\gamma}} = 1/Z_{C_{\gamma}} = 1/R_0 + \sum_{k=1}^{5} sC_k / [sR_kC_k + 1]$  and values optimized using MLSQ method, has to be evaluated. Fig. 3(a) shows that

using MLSQ method, has to be evaluated. Fig. 3(a) shows that the constant phase zone of the FoC is from 30 kHz to 30 MHz with -67.5 degrees, which is proven by the fitting equations as an inset of the figure. To estimate the equivalent order  $\gamma$  (or phase), the magnitude data simulated are fitted to the function

TABLE I. BEHAVIOR OF CMOS TRANSCONDUCTOR, IVB, AND CF±.

| Transconductor (                                                                                | g <sub>m</sub> )        |  |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------|--|--|--|

| Parameter                                                                                       | Value                   |  |  |  |

| Transconductance gain $g_{\rm m} I_{\rm out}/V_{\rm in}$ (µA/V)                                 | 835                     |  |  |  |

| Tracking error $\varepsilon_{gm}$ @ $g_o = 833 \mu A/V (-)$                                     | -0.002                  |  |  |  |

| <i>f</i> <sub>-3 dB</sub> @ g <sub>m</sub> (GHz)                                                | 7.195                   |  |  |  |

| DC linearity for $V_{in}(V)$                                                                    | ±0.535                  |  |  |  |

| $R_{\rm gm \ in} (\Omega)$                                                                      | $\cong \infty$          |  |  |  |

| $R_{\rm gm out}  ({\rm k}\Omega) \parallel C_{\rm gm out}  ({\rm fF})$                          | 64.44    6.42           |  |  |  |

| Inverting Voltage Buff                                                                          | er (IVB)                |  |  |  |

| Parameter                                                                                       | Value                   |  |  |  |

| Voltage gain $V_{out}/V_{in}$ gain ( $\beta_0$ )                                                | 0.972                   |  |  |  |

| Tracking error $\varepsilon_{\beta 0}$ (–)                                                      | 0.028                   |  |  |  |

| $f_{-3 \text{ dB}} @ V_{\text{out}}/V_{\text{in}} (\text{GHz})$                                 | 17.152                  |  |  |  |

| DC linearity $V_{out}/V_{in}$ (V)                                                               | $-1 \rightarrow +0.445$ |  |  |  |

| $R_{ m IVB}$ in $(\Omega)$                                                                      | $\cong \infty$          |  |  |  |

| $R_{\rm IVB out}(\Omega)$                                                                       | 80.6                    |  |  |  |

| Current Follower (                                                                              | CF±)                    |  |  |  |

| Parameter                                                                                       | Value                   |  |  |  |

| Current gains $I_{out+}/I_{in}$ ; $I_{out-}/I_{in}$ ( $\alpha_{oj}$ )                           | 0.982; 0.947            |  |  |  |

| Tracking errors $\varepsilon_{\alpha\alpha j}$ (–)                                              | 0.018; 0.053            |  |  |  |

| $f_{-3 \text{ dB}} @ I_{\text{out+}}/I_{\text{in}}; I_{\text{out-}}/I_{\text{in}} (\text{GHz})$ | 1.138; 0.871            |  |  |  |

| DC linearity $I_{out+}/I_{in}$ ; $I_{out-}/I_{in}$ ( $\mu$ A)                                   | ±944; ±333              |  |  |  |

| $R_{\rm CF \ in} \left( R_k' \right) \left( { m k} \Omega \right)$                              | 1.122                   |  |  |  |

| $R_{\rm CF out^+}({ m k}\Omega) \parallel C_{\rm CF out^+}({ m fF})$                            | 61.71    14.75          |  |  |  |

| $R_{\rm CF out-}({ m k}\Omega) \parallel C_{\rm CF out-}({ m fF})$                              | 61.71    20.94          |  |  |  |

TABLE II. PARAMETERS OF  $C_{0.75}$  and  $L_{0.75}$  Emulators in Fig. 2. (Note: " in 30 kHz - 30 MHz; <sup>‡</sup> in 130 kHz - 2.5 MHz Ranges )

| Component values (kΩ) / (pF)                                                                      |       |       |       |       |       |       |       |       |       |       |  |

|---------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| $R_0$                                                                                             | $R_1$ | $R_2$ | $R_3$ | $R_4$ | $R_5$ | $C_1$ | $C_2$ | $C_3$ | $C_4$ | $C_5$ |  |

| 51.1                                                                                              | 3.48  | 0.261 | 0.909 | 13.3  | 0.01  | 130   | 51    | 82    | 240   | 91    |  |

| Total resistance (kΩ) / capacitance (pF)                                                          |       |       |       |       |       |       |       |       |       |       |  |

| 69.06                                                                                             |       |       |       | 594   |       |       |       |       |       |       |  |

| Spread of resistance / capacitance                                                                |       |       |       |       |       |       |       |       |       |       |  |

| 5 110                                                                                             |       |       |       | 4.71  |       |       |       |       |       |       |  |

| <i>C</i> <sub>r</sub> Order (–) / phase (degree) / pseudo-capacitance (nF sec <sup>r-1</sup> )    |       |       |       |       |       |       |       |       |       |       |  |

| 0.75 / -67.5 / 12                                                                                 |       |       |       |       |       |       |       |       |       |       |  |

| $C_{r}$ : Phase angle deviation <sup>#</sup> (degree) / relative error <sup>#</sup> (%)           |       |       |       |       |       |       |       |       |       |       |  |

| $\pm 0.9 / -1.35 \rightarrow 0.6$                                                                 |       |       |       |       |       |       |       |       |       |       |  |

| $L_{\vec{r}}$ Order (–) / phase (degree) / pseudo-inductance (mH·sec <sup><math>r</math>1</sup> ) |       |       |       |       |       |       |       |       |       |       |  |

| 0.75 / 67.5 / 17.3                                                                                |       |       |       |       |       |       |       |       |       |       |  |

| $L_r$ : Phase angle deviation <sup>‡</sup> (degree) / relative error <sup>‡</sup> (%)             |       |       |       |       |       |       |       |       |       |       |  |

| $\pm 5 / 3.7 \rightarrow 8.7$                                                                     |       |       |       |       |       |       |       |       |       |       |  |

$\log Z = \gamma \log f + \log(2\pi j)^{\gamma} C_{\gamma}$ . Similarly, the pseudo-capacitance with stable  $C_{\gamma}$  is shown in Fig. 3(b). Note that the phase angle deviation in given range is only ±0.9 degree, while the corresponding relative pseudo-capacitance error in same range varies from -1.35% to +0.6%.

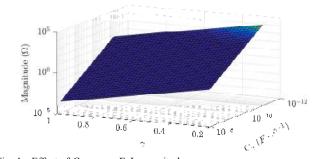

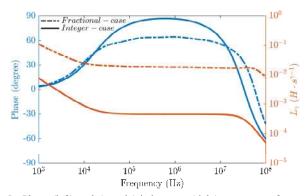

The performance of the proposed FoL simulator shown in Fig. 2 was also evaluated. Fig. 4 shows the effect of  $C_{\gamma}$  vs.  $\gamma$  on FoL magnitude. The simulated phase (pseudo)-inductance responses of 0.75 and integer-order inductance simulator are shown in Fig. 5. In this case the circuit was simulated with *C* and  $C_{\gamma}$  given above, which in fractional-order case theoretically resulted in  $L_{\gamma\_theor} = 17.3 \text{ mH} \cdot \text{s}^{-0.25}$  and the simulated one has a value  $L_{\gamma\_sim} = 18.4 \text{ mH} \cdot \text{s}^{-0.25}$ . Considering ±5 degree deviation in phase, the useful frequency range for  $L_{0.75}$  is about 138 kHz up to 2.45 MHz. Both 2.75<sup>th</sup> and 3<sup>rd</sup>-

Fig. 4. Effect of  $C_{\gamma}$  vs.  $\gamma$  on FoL magnitude.

Fig. 5. Phase (left) and (pseudo)-inductance (right) responses of proposed 0.75 and integer-order CMOS inductance simulator.

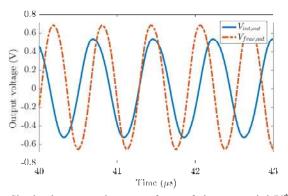

Fig. 6. Simulated output voltage waveforms of the proposed 2.75<sup>th</sup> and 3<sup>rd</sup>-order Colpitts oscillator.

order Colpitts oscillator were designed with CMOS transconductance given in Table I and capacitor values were selected as  $C_1 = C_2 = 61$  pF. The calculated oscillation start-up condition is  $R = 28.13 \text{ k}\Omega$  and the FO is  $f_{0 \text{ theor}\text{-fract}} = 1.3 \text{ MHz}$ , while the simulated CO is  $R = 30 \text{ k}\Omega$  and FO is 1.58 MHz. On the other hand, the CO is 1.8 k $\Omega$  and FO is 1.26 MHz in integer-order case. The steady-state output voltage waveforms of both cases are depicted in Fig. 6. For the output the generated peak-to-peak value is 1.34 V and 1.06 V for 2.75<sup>th</sup> and 3<sup>rd</sup>-order, respectively, while the total harmonic distortion (THD) at the outputs are about 4.1% and 5.3% for the fractional and integer cases, respectively.

### V. CONCLUSION

In this paper a fractional-order Colpitts oscillator design using a 0.75-order compact CMOS FoL simulator is presented. The  $C_{\gamma}$  with 12 nF·s<sup>-0.25</sup> value was emulated via 5<sup>th</sup>-order Foster II RC network and values optimized using MLSQ method. The resulted pseudo-inductance value of the proposed FoL is  $L_{\gamma} = 18.4 \text{ mH} \cdot \text{s}^{-0.25}$  and its behavior and performance in oscillator was verified using SPICE simulations. Future work will be focused on experimental verification of the oscillator.

#### REFERENCES

- [1] N. A. Z. R-Smith, A. Kartci, and L. Brancik, "Application of Numerical Inverse Laplace Transform Methods for Simulation of Distributed Systems with Fractional-Order Elements," Journal of Circuits, Systems and Computers, vol. 27, no. 11, pp. 1850172-1-1850172-25, 2018.

- [2] A. Kartci, N. Herencsar, J. Koton, L. Brancik, K. Vrba, G. Tsirimokou, and C. Psychalinos, "Fractional-order oscillator design using unity-gain voltage buffers and OTAs," In Proc. of the 2017 60th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Boston, USA, 2017. pp. 555-558.

- [3] R. E. Gutiérrez, J. M. Rosário, and J. T. Machado, "Fractional Order Calculus," Basic Concepts and Engineering, vol. 2010, article ID 375858, 19 pages, 2010.

- [4] I. Podlubny, I. Petras, B. Vinagre, P. O'Leary, and L. Dorcak, "Analogue realizations of fractional-order controllers," Nonlinear Dynamics, vol. 29, pp. 281-296, 2002.

- [5] I. N'Doye, K. N. Salama, and T. M. Laleg-Kirati, "Robust fractionalorder proportional-integral observer for synchronization of chaotic fractional-order systems," IEEE/CAA J. of Automatica Sinica, in print, pp. 1-10, 2018. DOI: 10.1109/JAS.2017.7510874

- [6] J. Jerabek, R. Sotner, R. Prokop, V. Kledrowetz, A. Kartci, and U. E. Ayten, "Inductance simulator based on dual controlled CMOS voltage differencing current conveyor," In Proc. of 2016 IEEE 59th Int. Midwest Symp. on Circuits and Systems (MWSCAS), Abu Dhabi, 2016, pp. 1-4.

- [7] G. Tsirimokou, A. Kartci, J. Koton, N. Herencsar, and C. Psychalinos, "Comparative study of discrete component realizations of fractionalorder capacitor and inductor active emulators," Journal of Circuits, Systems and Computers, vol. 27, no. 11, pp. 1850170, 2018.

- [8] A. Soltan, A. G. Radwan, and A. M. Soliman, "Fractional-order mutual inductance: analysis and design," International Journal of Circuit Theory and Applications, vol. 44, no. 1, pp. 85-97, 2016.

- [9] A. K. Gilmutdinov, P. A. Ushakov, and R. El-Khazali, Fractal Elements and their Applications, Springer, 2017.

- [10] R. Sotner, J. Jerabek, N. Herencsar, J. Petrzela, K. Vrba, and Z. Kincl, "Linearly tunable quadrature oscillator derived from LC Colpitts structure using voltage differencing transconductance amplifier and adjustable current amplifier," Analog Integrated Circuits and Signal Processing, vol. 81, pp. 121-136, 2014.

- [11] A. Kartci, U. E. Ayten, N. Herencsar, R. Sotner, J. Jerabek, and K. Vrba, "Floating capacitance multiplier simulator for grounded RC Colpitts oscillator design," In Proc. of the 2015 International Conference on Applied Electronics, Pilsen, Czech Republic, 2015, pp. 93-96.

- [12] A. S. Elwakil, A. Agambayev, A. Allagui, and K. N. Salama, "Experimental demonstration of fractional-order oscillators of orders 2.6 and 2.7," Chaos, Solitons and Fractals, vol. 96, pp. 160-164, 2017.

- [13] A. G. Radwan, A. S. Elwakil, and A. M. Soliman, "Fractional-order sinusoidal oscillators: Design procedure and practical examples," IEEE Trans. on Circuits and Systems I, vol. 55, pp. 2051-2063, 2008.

- [14] R. Senani, D. R. Bhaskar, V. K. Singh, and R. K Sharma, Sinusoidal Oscillators and Waveform Generators using Modern Electronic Circuit Building Blocks. Springer, 2016.

- [15] F. Yuan, CMOS Active Inductors and Transformers, Principle, Inplementation and Applications, Springer, 2008.

- [16] N. Herencsar, J. Koton, K. Vrba, and O. Cicekoglu, "Low-voltage fully cascadable resistorless transadmittance-mode all-pass filter," in Proc. of 2014 57th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), College Station, USA, 2014, pp. 185-188.

- [17] S. Minaei and E. Yuce, "Novel voltage-mode all-pass filter based on using DVCCs," Circuits, Systems, and Signal Processing, vol. 29, no. 3, pp. 391-402, 2010.