# CMOS Signal Synthesizers for Emerging RF-to-Optical Applications

#### Jahnavi Sharma

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

#### **ABSTRACT**

## CMOS Signal Synthesizers for Emerging RF-to-Optical Applications

#### Jahnavi Sharma

The need for clean and powerful signal generation is ubiquitous, with applications spanning the spectrum from RF to mm-Wave, to into and beyond the terahertz-gap. RF applications including mobile telephony and microprocessors have effectively harnessed mixed-signal integration in CMOS to realize robust on-chip signal sources calibrated against adverse ambient conditions. Combined with low cost and high yield, the CMOS component of hand-held devices costs a few cents per part per million parts. This low cost, and integrated digital processing, make CMOS an attractive option for applications like high-resolution imaging and ranging, and the emerging 5-G communication space. RADAR techniques when expanded to optical frequencies can enable micrometers of resolution for 3D imaging. These applications, however, impose upto 100x more exacting specifications on power and spectral purity at much higher frequencies than conventional RF synthesizers.

This generation of applications will present unconventional challenges for transistor technologies - whether it is to squeeze performance in the conventionally used spectrum, already wrung dry, or signal generation and system design in the relatively emptier mm-Wave to sub-mmWave spectrum, much of the latter falling in the "Terahertz Gap". Indeed, transistor scaling and innovative device physics leading to new transistor topologies have yielded higher cut-off frequencies in CMOS, though still lagging well behind SiGe and III-V semiconductors. To avoid multimodule solutions with functionality partitioned across different technologies, CMOS must be pushed out of its comfort zone, and technology scaling has to have accompanying breakthroughs in design approaches not only at the system but also at the block level. In this thesis, while not targeting a specific application, we seek to formulate the obstacles in synthesizing high frequency, high power and low noise signals in CMOS and construct a coherent design methodology to address them. Based on this, three novel prototypes to overcome the limiting factors in each case are presented.

The first half of this thesis deals with high frequency signal synthesis and power generation in CMOS. Outside the range of frequencies where the transistor has gain, frequency generation necessitates harmonic extraction either as harmonic oscillators or as frequency multipliers. We augment the traditional maximum oscillation frequency metric  $(f_{max})$ , which only accounts for transistor losses, with passive component loss to derive an effective  $f_{max}$  metric. We then present a methodology for building oscillators at this  $f_{max}$ , the Maximum Gain Ring Oscillator. Next, we explore generating large signals beyond  $f_{max}$  through harmonic extraction in multipliers. Applying concepts of waveform shaping, we demonstrate a Power Mixer that engineers transistor nonlinearity by manipulating the amplitudes and relative phase shifts of different device nodes to maximize performance at a specific harmonic beyond device cut-off.

The second half proposes a new architecture for an ultra-low noise phase-locked loop (PLL), the Reference-Sampling PLL. In conventional PLLs, a noisy buffer converts the slow, low-noise sine-wave reference signal to a jittery square-wave clock against which the phase of a noisy voltage-controlled oscillator (VCO) is corrected. We eliminate this reference buffer, and measure phase error by sampling the reference sine-wave with the 50x faster VCO waveform already available on chip, and selecting the relevant sample with voltage proportional to phase error. By avoiding the N-squared multiplication of the high-power reference buffer noise, and directly using voltage-mode phase error to control the VCO, we eliminate several noisy components in the controlling loop for ultra-low integrated jitter for a given power consumption. Further, isolation of the VCO tank from any varying load, unlike other contemporary divider-less PLL architectures, results in an architecture with record performance in the low-noise and low-spur space.

We conclude with work that brings together concepts developed for clean, high-power signal generation towards a hybrid CMOS-Optical approach to Frequency-Modulated Continuous-Wave (FMCW) Light-Detection-And-Ranging (LIDAR). Cost-effective tunable lasers are temperature-sensitive and have nonlinear tuning profiles, rendering precise frequency modulations or 'chirps' untenable. Locking them to an electronic reference through an electro-optic PLL, and electronically calibrating the control signal for nonlinearity and ambient sensitivity, can make such chirps possible. Approaches that build on the body of advances in electrical PLLs to control the performance, and ease the specification on the design of optical systems are proposed. Eventually, we seek to leverage the twin advantages of silicon-intensive integration and low-cost high-yield towards developing a

single-chip solution that uses on-chip signal processing and phased arrays to generate precise and robust chirps for an electronically-steerable fine LIDAR beam.

## Table of Contents

| Li           | st of | Figure          | es                                                  | v    |

|--------------|-------|-----------------|-----------------------------------------------------|------|

| Li           | st of | Tables          | S                                                   | xv   |

| $\mathbf{A}$ | cknov | wledge          | ement                                               | xvi  |

| D            | edica | tion            |                                                     | xvii |

| 1            | Intr  | oducti          | ion                                                 | 1    |

| <b>2</b>     | TH    | z Frequ         | uency Synthesis: Maximum Gain Ring Oscillator       | 9    |

|              | 2.1   | Techno          | ologies for high frequency signal generation        | 9    |

|              | 2.2   | $45\mathrm{nm}$ | SOI CMOS Technology Characterization                | 12   |

|              |       | 2.2.1           | Active Devices                                      | 12   |

|              |       | 2.2.2           | Transmission Line                                   | 15   |

|              |       | 2.2.3           | Capacitor (VNCAP)                                   | 16   |

|              | 2.3   | Maxin           | num Gain Ring Oscillator Topology                   | 17   |

|              |       | 2.3.1           | Accounting for Passive Element Loss                 | 21   |

|              |       | 2.3.2           | Determining the Matching Network                    | 24   |

|              |       | 2.3.3           | Circuit-Level Implementation                        | 26   |

|              | 2.4   | Harmo           | onic Power Extraction and Spurious Mode Suppression | 29   |

|              |       | 2.4.1           | Extracting the Kth harmonic                         | 29   |

|              |       | 2.4.2           | Increasing the Output Power                         | 31   |

|              |       | 2.4.3           | Maximizing the harmonic output power                | 33   |

|   |        | 2.4.4 Suppression of spurious modes                                   | 33 |

|---|--------|-----------------------------------------------------------------------|----|

|   | 2.5    | Oscillator Measurement                                                | 36 |

|   | 2.6    | Conclusion                                                            | 39 |

| 3 | $TH_2$ | z Power Generation: Frequency Multipliers                             | 42 |

|   | 3.1    | Scaling Trends in CMOS Multipliers                                    | 42 |

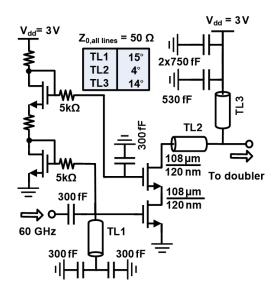

|   | 3.2    | A 134 GHz Doubler in 130 nm CMOS                                      | 47 |

|   | 3.3    | Conclusion                                                            | 49 |

| 4 | $TH_2$ | z Power Generation:Power Mixers                                       | 51 |

|   | 4.1    | Concept of Nonlinearity Engineering in beyond- $f_{max}$ Power Mixers | 53 |

|   |        | 4.1.1 Waveform shaping and output harmonic current                    | 54 |

|   |        | 4.1.2 Harmonic output power                                           | 58 |

|   |        | 4.1.3 Input power requirement                                         | 59 |

|   |        | 4.1.4 Effect of non-ideal input and output terminations               | 61 |

|   | 4.2    | $180-200\mathrm{GHz}$ 130 nm CMOS Power Mixer Implementation          | 64 |

|   |        | 4.2.1 130 nm CMOS 180 – 200 GHz Power Mixer                           | 65 |

|   |        | 4.2.2 130 nm CMOS 120 GHz Frequency Doubler                           | 67 |

|   |        | 4.2.3 130 nm CMOS Fundamental-frequency V-band PAs                    | 67 |

|   |        | 4.2.4 60 GHz Reflection-Type Phase Shifter (RTPS)                     | 69 |

|   |        | 4.2.5 60 GHz Variable Gain Amplifier                                  | 75 |

|   |        | 4.2.6 60 GHz Marchand Balun                                           | 77 |

|   | 4.3    | Measurement                                                           | 79 |

|   |        | 4.3.1 $60\mathrm{GHz}$ RTPS and VGA Breakout                          | 79 |

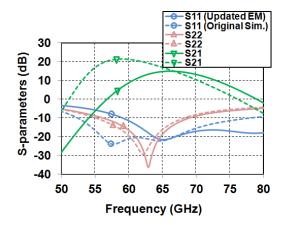

|   |        | 4.3.2 120 GHz Frequency Doubler Breakout                              | 81 |

|   |        | 4.3.3 $180 - 200 \mathrm{GHz}$ Power Mixer                            | 83 |

|   | 4.4    | Conclusion                                                            | 87 |

| 5 | Low    | Noise and Low Spur RF PLL: Reference-Sampling PLL                     | 91 |

|   | 5.1    | Review                                                                | 91 |

|   |        | 5.1.1 Conventional Type-II Second Order PLLs                          | 92 |

|     | 5.1.2  | Sub-sampling PLLs                                                         |

|-----|--------|---------------------------------------------------------------------------|

|     | 5.1.3  | Injection-Locked Clock Multipliers (ILCM)                                 |

| 5.2 | New S  | Sampled RF-PLL approach: Reference-Sampling Phase Locked Loop (RSPLL) 105 |

|     | 5.2.1  | Motivation: Low noise and Low Spur                                        |

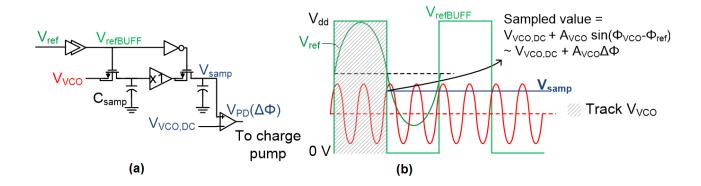

|     | 5.2.2  | Sampled Phase detector (PD)                                               |

|     | 5.2.3  | Sample Edge Selection Circuit (SESCi)                                     |

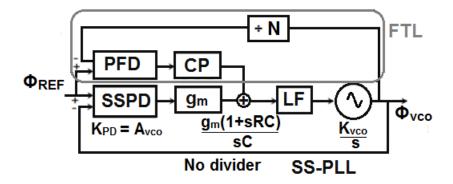

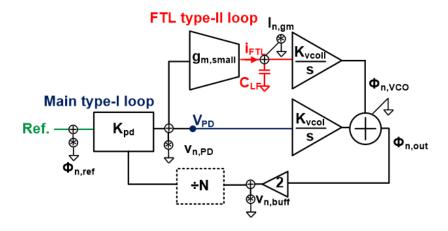

|     | 5.2.4  | Frequency Tracking Loop                                                   |

|     | 5.2.5  | Proposed PLL Architecture                                                 |

|     | 5.2.6  | Noise and Power Analysis                                                  |

|     | 5.2.7  | Effect of nonidealities                                                   |

| 5.3 | Propo  | sed Loop Implementation                                                   |

|     | 5.3.1  | Loop parameter selection                                                  |

|     | 5.3.2  | Switch size                                                               |

|     | 5.3.3  | SESCi                                                                     |

|     | 5.3.4  | Reference Buffer                                                          |

|     | 5.3.5  | LC-VCO Implementation                                                     |

|     | 5.3.6  | VCO Buffer                                                                |

|     | 5.3.7  | Frequency Tracking Loop                                                   |

|     | 5.3.8  | Output Test Buffer                                                        |

|     | 5.3.9  | Ground isolation and ESD protection                                       |

| 5.4 | Simul  | ated performance and Measurement                                          |

|     | 5.4.1  | Phase noise simulation                                                    |

|     | 5.4.2  | Measured Performances: VCO                                                |

|     | 5.4.3  | Measured Performances: RSPLL                                              |

| 5.5 | Comp   | arison                                                                    |

| 5.6 | Future | e work: Loop Bandwidth Modification                                       |

| Wie | le Ban | adwidth Electro-optic PLLs for FMCW LIDAR 152                             |

| 6.1 | Theor  | y of FMCW detection                                                       |

| 6.2 | Photo  | -electric interface                                                       |

| 6.3 | EO-P   | LL Basics                                                                 |

6

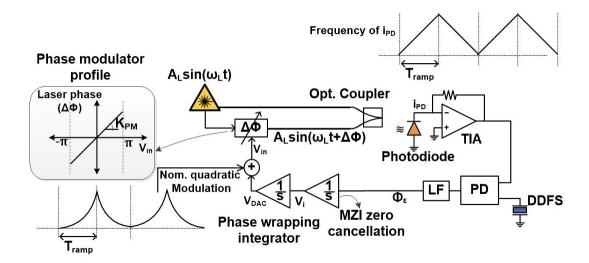

|    | 6.4                       | Propos   | sed EO-PLL for FMCW LIDAR                                  | . 162 |

|----|---------------------------|----------|------------------------------------------------------------|-------|

|    |                           | 6.4.1    | Motivation: Reduction in MZI delay and implementation area | . 162 |

|    |                           | 6.4.2    | Loop architecture                                          | . 164 |

|    |                           | 6.4.3    | Implementation                                             | . 164 |

|    |                           | 6.4.4    | Acquisition of mixer-based phase detector                  | . 170 |

|    |                           | 6.4.5    | Measured Perfomance                                        | . 170 |

|    | 6.5                       | Future   | e work                                                     | . 171 |

|    |                           | 6.5.1    | Mixer-based EO-PLL                                         | . 171 |

|    |                           | 6.5.2    | Conventional EO-PLL around a Laser Phase Shifter           | . 174 |

| 7  | Con                       | ıclusioı | n                                                          | 178   |

| Ι  | Bib                       | oliogra  | aphy                                                       | 181   |

| Bi | bliog                     | graphy   |                                                            | 182   |

| II | $\mathbf{A}_{\mathbf{l}}$ | ppend    | ices                                                       | 197   |

| A  | Effe                      | ect of C | Oscillator Non-ideality in OFDM                            | 198   |

|    | A.1                       | Inter-c  | carrier interference                                       | . 198 |

|    | A.2                       | Phase    | Noise                                                      | . 200 |

| B  | Rag                       | o Con    | ditions in Multi loop DLLs                                 | 203   |

## List of Figures

| 1.1 | Phase noise and $\text{FoM}_{PN} = \left(\frac{f_c}{\Delta f_c}\right)^2 / \left(L_{\Delta f_c} P_{DC,mW}\right)$ for state-of-the-art CMOS PLLs |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | for different carrier frequencies $f_c$ at different offsets $\Delta f_c$ . Maximum phase noise                                                  |    |

|     | limits for m-QAM at the OFDM-based standard's carrier spacing is shown for PLLs                                                                  |    |

|     | with loop bandwidth of $100\mathrm{kHz}$ . 3GPP to WiGig impose phase noise requirements                                                         |    |

|     | at increasing carrier spacing $\Delta f_c$ . Requirements for evolving OFDM-based standards                                                      |    |

|     | are met by CMOS for at least 64 QAM, but with poorer $FOM_{PN}$                                                                                  | 2  |

| 1.2 | Output power and efficiency roll-off in CMOS with increasing frequency                                                                           | 5  |

| 1.3 | (a) "Terahertz Gap" between Electronics and Photonics, [1] (b) Comparison of max-                                                                |    |

|     | imum oscillation frequency $(f_{max})$ across scaling technology nodes                                                                           | 5  |

| 2.1 | Layout of a BC NFET Device. This allows the gate to be doubly contacted in a                                                                     |    |

|     | symmetric fashion                                                                                                                                | 13 |

| 2.2 | The model for the NFET BC device. In, the FB version, there is no 'b' node and                                                                   |    |

|     | $r_{body}$ is absent. The FB node is $b_1$ ,                                                                                                     | 14 |

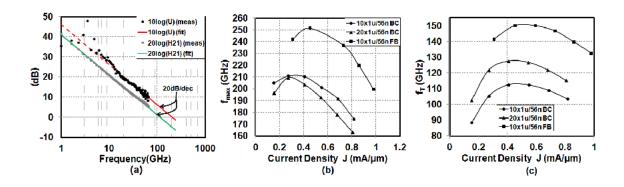

| 2.3 | (a) A line fitted by linear regression to the measured $U$ and $h_{21}$ plots of the 10 $\times$                                                 |    |

|     | $1\mu\mathrm{m}/56\mathrm{nm}$ BC device with a $J=0.56m\mathrm{A}/\mu\mathrm{m}$ . (b) Comparison of the $f_{max}$ across                       |    |

|     | $J$ from measurement for the $10\times1\mu\mathrm{m}/56\mathrm{nm}$ and $20\times1\mu\mathrm{m}/56\mathrm{nm}$ BC devices and                    |    |

|     | the $10 \times 1 \mu \text{m}/40 \text{nm}$ FB device. (c) Measured $f_T$ across $J$ for all three devices                                       | 14 |

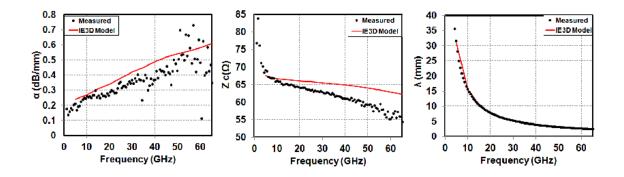

| 2.4 | Measured performance of a 70<br>$\!\Omega$ CPW in 45nm SOI CMOS. A comparison with the                                                           |    |

|     | simulated performance in IE3D is also shown                                                                                                      | 16 |

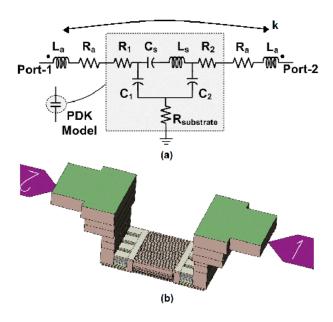

| 2.5 | (a) Model used for the VNCAP in 45nm SOI CMOS. $La$ and $Ra$ are added to capture                                                                |    |

|     | the via effect and the inductances on either plate are coupled. (b) IE3D VNCAP                                                                   |    |

|     | simulation setup                                                                                                                                 | 17 |

|     |                                                                                                                                                  |    |

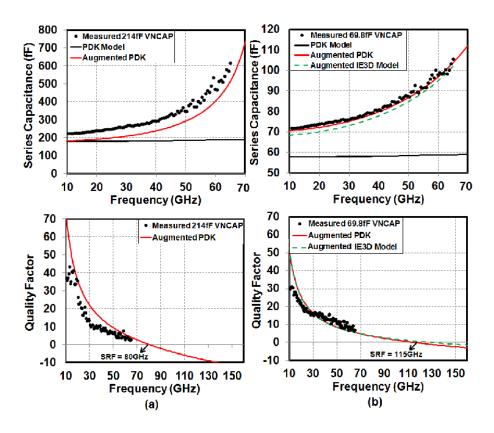

| 2.6  | Measured and simulated series capacitance $(=\frac{Imy_{11}}{\omega})$ and Quality Factor $(=\frac{Im(y_{11})}{Re(y_{11})})$ |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

|      | of (a) a 214fF and (b) a 70fF VNCAP in 45nm SOI CMOS                                                                         | 18 |

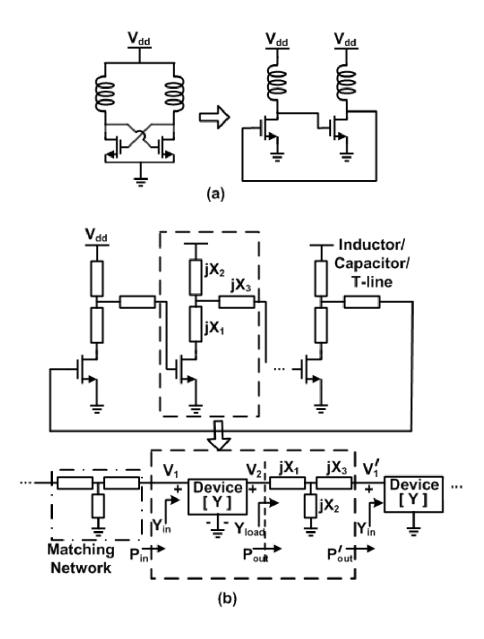

| 2.7  | (a) Cross-coupled oscillator as a two-stage tuned ring oscillator with a single inter-                                       |    |

|      | stage matching inductor. (b) MGRO concept                                                                                    | 19 |

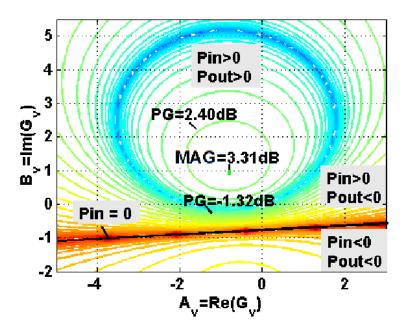

| 2.8  | Power gain $(PG)$ circles on the $G_v$ plane at 100GHz for a $10 \times 1 \mu \text{m}/56 \text{nm}$ body-                   |    |

|      | contacted NMOS device including estimated layout parasitics in a common source                                               |    |

|      | configuration. Current Density, $J=0.56 \mathrm{mA}/\mu\mathrm{m}.$                                                          | 21 |

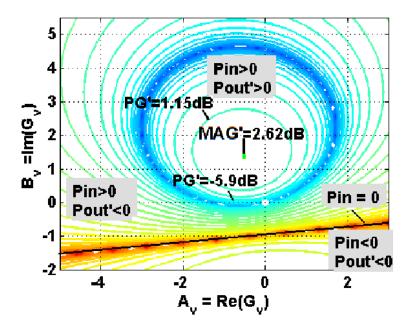

| 2.9  | Power gain $(PG')$ circles on the $G_v$ plane at 100GHz for the device in Fig. 3.8 with                                      |    |

|      | Inductor Quality Factor taken to be 14 at 100<br>GHz. Current Density, $J=0.56 {\rm mA}/\mu{\rm m}.$                         | 23 |

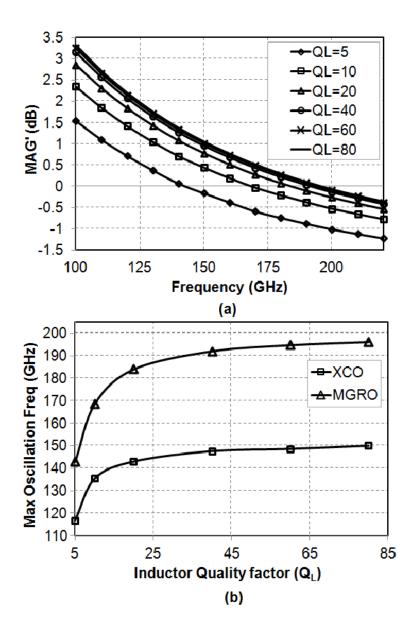

| 2.10 | (a) MAG' of the $10 \times 1 \mu \text{m}/56 \text{nm}$ body-contacted NMOS device versus frequency for                      |    |

|      | different $Q_L$ values. The annotated $Q_L$ values are for a frequency of 100GHz, and                                        |    |

|      | $Q_L$ is assumed to scale linearly with frequency. (b) Maximum oscillation frequencies                                       |    |

|      | of the device in the MGRO and XCO topologies as a function of $Q_L$                                                          | 25 |

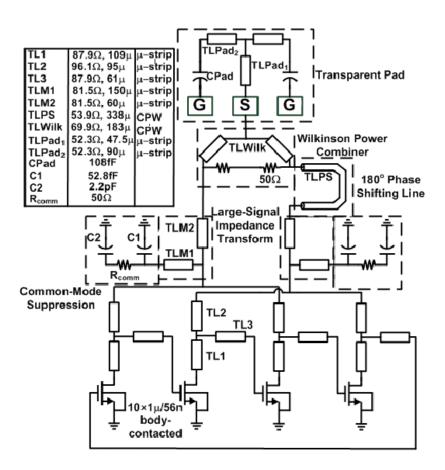

| 2.11 | Circuit diagram of the 216GHz signal source                                                                                  | 27 |

| 2.12 | Circuit diagram of the 316GHz signal source                                                                                  | 28 |

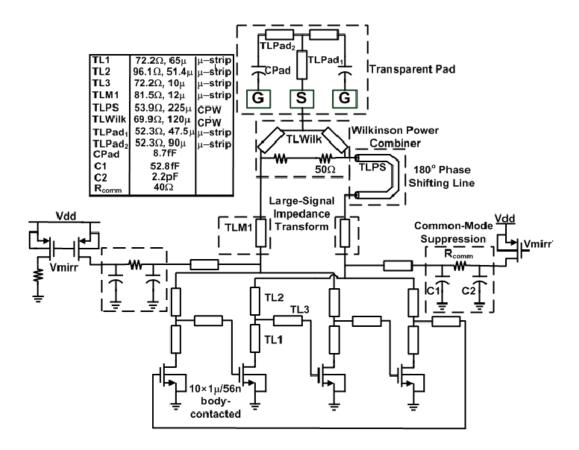

| 2.13 | Chip microphotographs of the (a) 216GHz and (b) 316GHz signal sources                                                        | 28 |

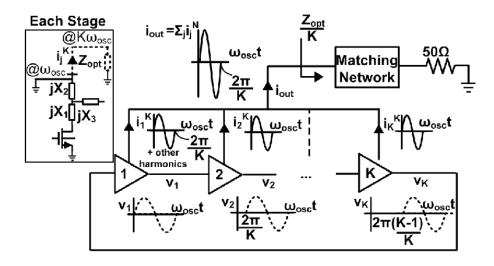

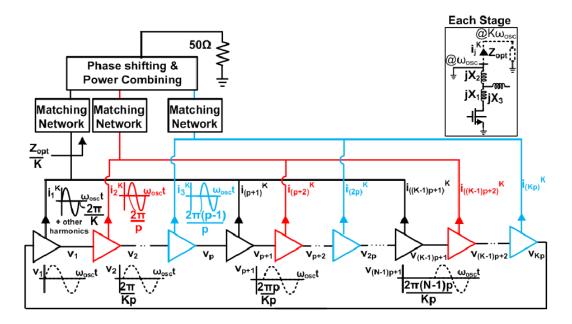

| 2.14 | Ring Oscillator with $K$ -stages to extract the $K$ th harmonic                                                              | 30 |

| 2.15 | Ring Oscillator with $K \times p$ -stages to extract the Kth harmonic. $\phi = \frac{2\pi}{K \times p}$ to ensure            |    |

|      | an inductive matching network                                                                                                | 30 |

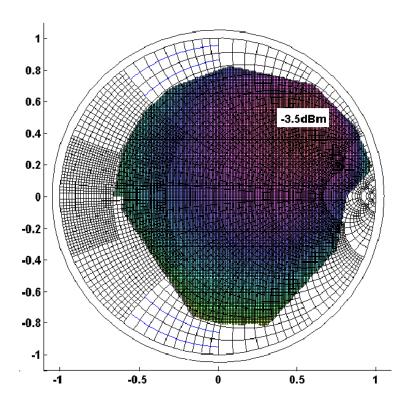

| 2.16 | Load-pull plot of the $K=2,p=2$ oscillator at 100<br>GHz                                                                     | 32 |

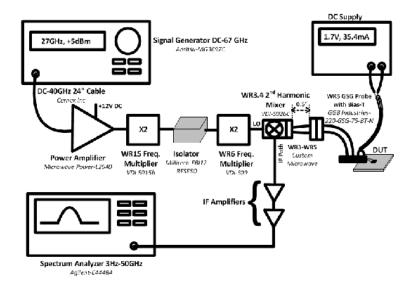

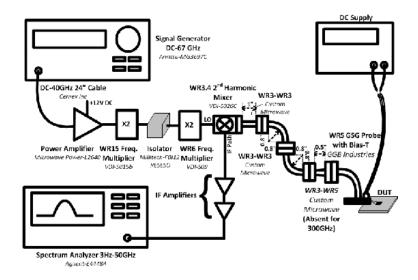

| 2.17 | 216GHz oscillator frequency and power measurement setup with WR-3 second-                                                    |    |

|      | harmonic mixer-downconverter (SHMD)                                                                                          | 34 |

| 2.18 | $216\mathrm{GHz}$ oscillator frequency and power measurement setup with WR-3 SHMD in-                                        |    |

|      | cluding two additional WR3 bends and one additional WR3 straight. This measure-                                              |    |

|      | ment is to measure the loss of the latter three components                                                                   | 34 |

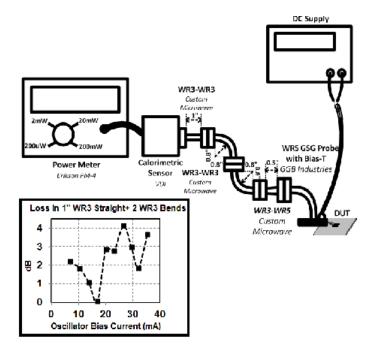

| 2.19 | Power meter measurement setup for the 216GHz oscillator. The inset shows the                                                 |    |

|      | measured loss of the additional two WR3 bends and the 1" WR3 straight. Details                                               |    |

|      | are provided in the text                                                                                                     | 35 |

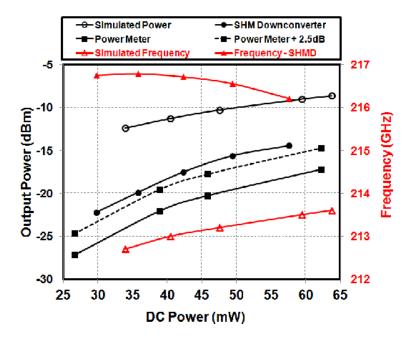

| 2.20 | $216\mathrm{GHz}$ oscillator frequency and power measured by a WR-3 SHMD and an Erickson                                     |    |

|      | PM4 power meter. Measurement details are in the text                                                                         | 37 |

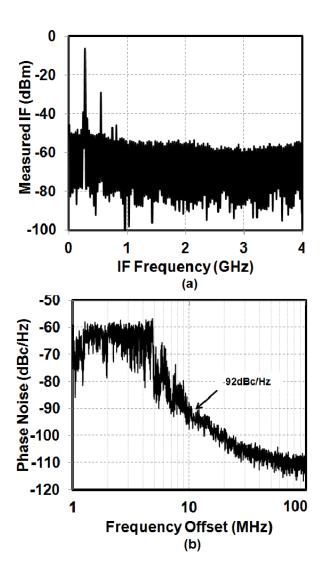

| 2.21 | (a) Measured downconverted spectrum of the 216GHz source for a DC power of                    |    |

|------|-----------------------------------------------------------------------------------------------|----|

|      | $57.5 \mathrm{mW},$ output frequency of 216.2<br>GHz and calibrated output power of -14.4dBm. |    |

|      | (b) Measured phase noise                                                                      | 38 |

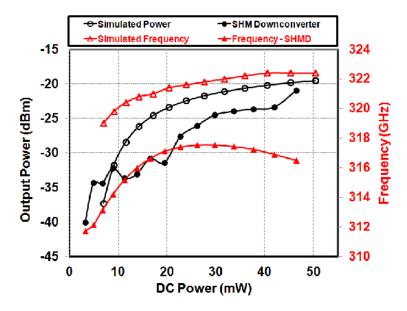

| 2.22 | $316\mathrm{GHz}$ oscillator frequency and output power measured using the WR3 SHMD           | 39 |

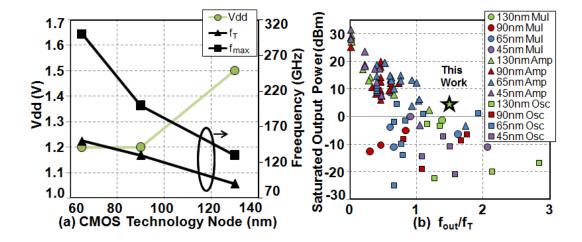

| 3.1  | (a) Scaling of supply voltage and cutoff frequency $(f_T)$ across CMOS nodes. (b)             |    |

|      | Comparison of this work with state-of-the-art CMOS sources across output frequency            |    |

|      | normalized to technology $f_T$                                                                | 43 |

| 3.2  | Circuit diagram of a simple balanced CMOS frequency doubler                                   | 44 |

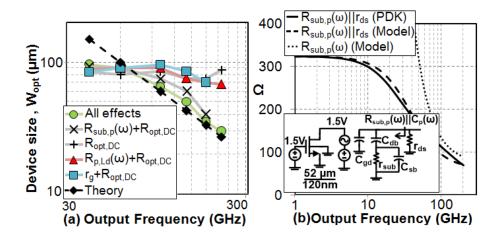

| 3.3  | (a) Device size needed to deliver maximum power to a 50 $\Omega$ load in a 130 nm CMOS        |    |

|      | balanced doubler. (b) Frequency dependence of $R_{sub,p}$                                     | 45 |

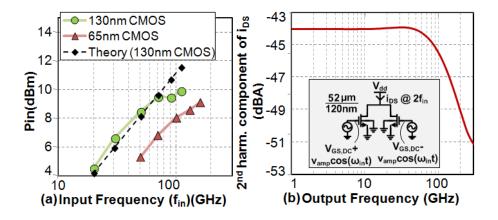

| 3.4  | (a) $P_{in}$ of optimal doubler driving $50\Omega$ across frequency. (b) Frequency dependence |    |

|      | of $2^{nd}$ harmonic current due to NQS effect in $130\mathrm{nm}$                            | 45 |

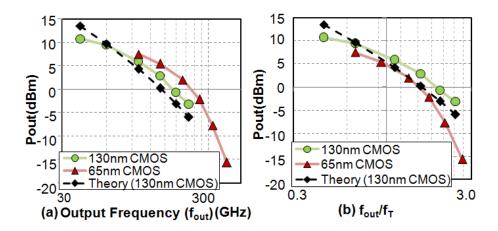

| 3.5  | Simulated output power for optimal doublers driving 50 $\Omega$ in 130 nm and 65 nm           |    |

|      | CMOS across (a) absolute $f_{out}$ , (b) $f_{out}$ normalized to $f_T$                        | 46 |

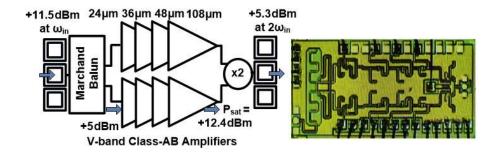

| 3.6  | Block diagram and chip photo of the 130 nm CMOS F-band doubler. The annotated                 |    |

|      | values are at 67 GHz after post-layout simulations                                            | 47 |

| 3.7  | (a) First V-band amplifier stage and, (b) the F-band balanced doubler                         | 48 |

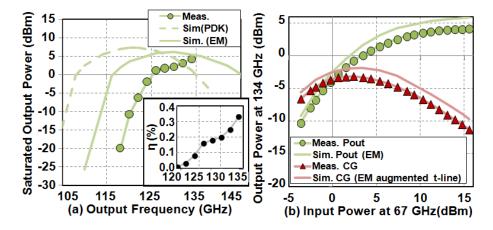

| 3.8  | (a) Measured and simulated saturated output power and efficiency. (b) Output                  |    |

|      | power and conversion gain at 134 GHz                                                          | 48 |

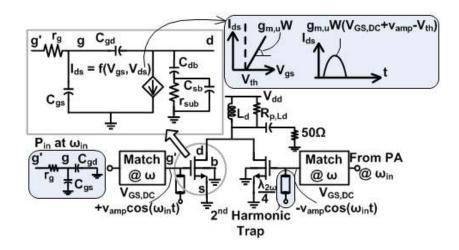

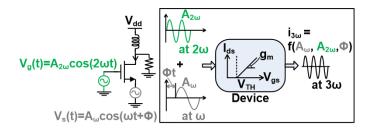

| 4.1  | Power mixer technique mixes the first and the second harmonic to generate the                 |    |

|      | third harmonic current. The third harmonic output power can be optimized by                   |    |

|      | controlling the amplitudes and relative phase shifts of the input fundamental and             |    |

|      | second harmonic signals                                                                       | 52 |

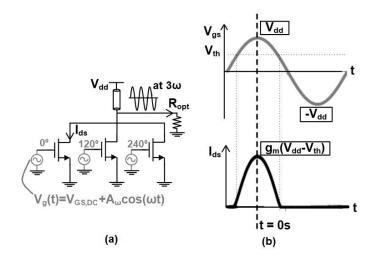

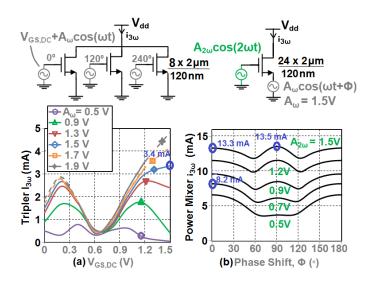

| 4.2  | (a) Conventional three phase frequency tripler. (b) Device nonlinearity clips the             |    |

|      | input fundamental sine wave, resulting in a clipped drain current waveform                    | 53 |

| 4.3  | Third harmonic current generated by a device when it is configured as (a) frequency           |    |

|      | tripler (the dashed portion of a curve indicates when the input amplitude violates            |    |

|      | long-term reliability guidelines), and (b) power mixer.                                       | 55 |

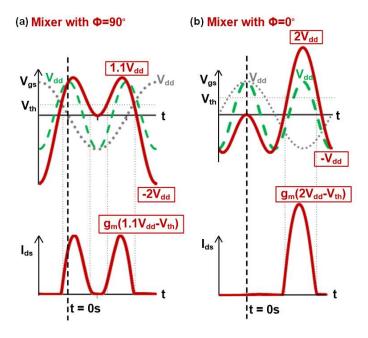

| 4.4  | Gate-source voltage shape and the resultant output current waveforms for the power                             |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | mixer with $A_{\omega}=A_{2\omega}=V_{dd}=1.5\mathrm{V}$ and a relative phase shift $\phi$ of (a) 90°, (b) 0°. | 56 |

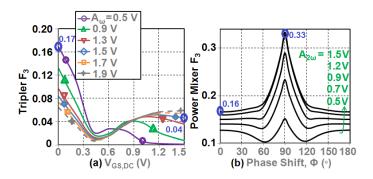

| 4.5  | Ratio of third harmonic current to peak current, $F_3 = \frac{i_{3\omega}}{i_{peak}}$ , generated by a device  |    |

|      | when it is configured as (a) a frequency tripler, and (b) a power mixer $(A_{\omega} = 1.5 \mathrm{V})$ .      | 57 |

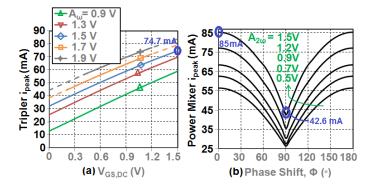

| 4.6  | Peak of output current waveform, $i_{peak}$ , generated by a device when it is configured                      |    |

|      | as (a) a frequency tripler, and (b) a power mixer $(A_{\omega} = 1.5 \mathrm{V})$                              | 57 |

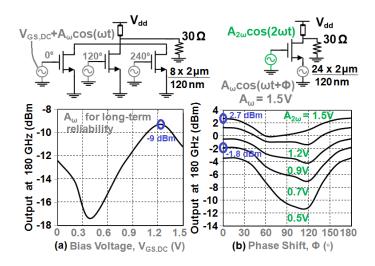

| 4.7  | Output power delivered to the optimal $30\Omega$ load by the device as a (a) frequency                         |    |

|      | tripler, (and b) power mixer with $A_{\omega} = 1.5 \mathrm{V}.$                                               | 58 |

| 4.8  | Fundamental input power required to generate third harmonic when the device is                                 |    |

|      | configured as (a) a frequency tripler, and (b) a power mixer with $A_{\omega}=1.5\mathrm{V}.$ In the           |    |

|      | power mixer case, the second harmonic is assumed to be generated by a balanced                                 |    |

|      | doubler with a conversion loss of 5 dB                                                                         | 59 |

| 4.9  | Fundamental to third harmonic conversion loss when the device is configured as (a)                             |    |

|      | a frequency tripler, and (b) a power mixer with $A_{\omega}=1.5\mathrm{V}.$ In the power mixer                 |    |

|      | case, the second harmonic is assumed to be generated by a balanced doubler with a                              |    |

|      | conversion loss of 5 dB                                                                                        | 60 |

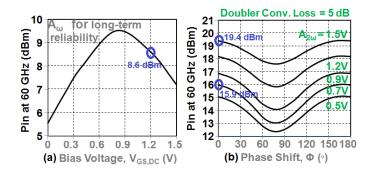

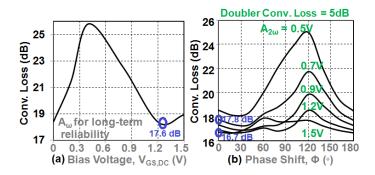

| 4.10 | Effect of non-ideal input and output terminations on the output power of the (a) a                             |    |

|      | frequency tripler, and (b) a power mixer with $A_{\omega}=1.5\mathrm{V.}$                                      | 61 |

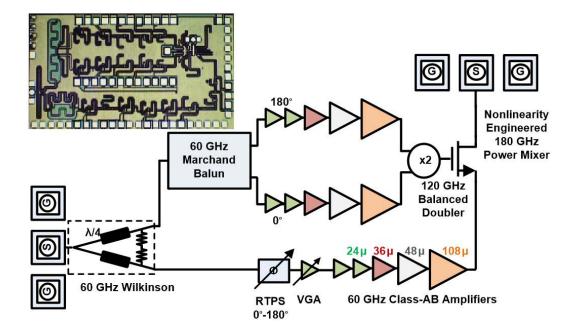

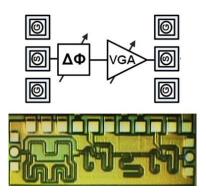

| 4.11 | Block diagram and chip photograph of the implemented 2.4 mm $\times$ 1.1 mm 180 $-$                            |    |

|      | 200 GHz power mixer in 130 nm CMOS with $f_{max} \approx 135$ GHz                                              | 62 |

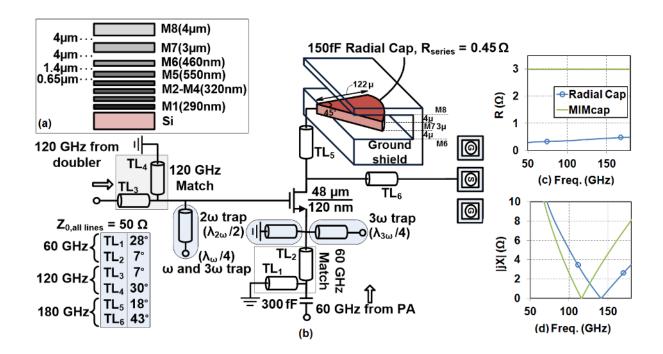

| 4.12 | (a) BEOL cross-section of the $130\mathrm{nm}$ CMOS process. (b) Circuit diagram of the                        |    |

|      | implemented $180-200\mathrm{GHz}$ power mixer. (c) Series resistance, $R$ ( $\Omega$ ), and (d)                |    |

|      | reactance, $ jX $ ( $\Omega$ ), of the 150 fF radial capacitance compared with that of the PDK                 |    |

|      | model of the $8.5\mu\mathrm{m}$ × $8.5\mu\mathrm{m}$ MIMcap                                                    | 64 |

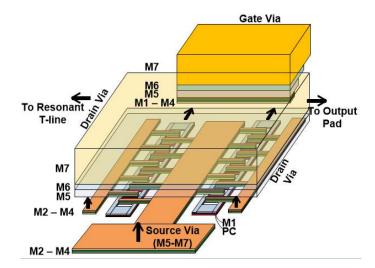

| 4.13 | Layout of the power mixer device. The source via is pulled to one side in $M2\text{-}M4$                       |    |

|      | and then built up<br>to $M7$ (not shown). The substrate connection is not shown                                | 65 |

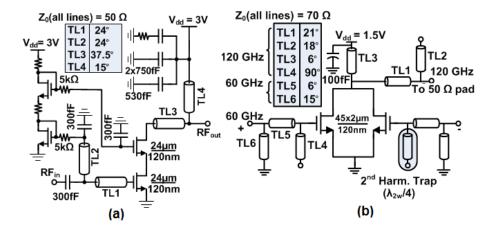

| 4.14 | Circuit diagram of the implemented 120GHz frequency doubler [2]                                                | 67 |

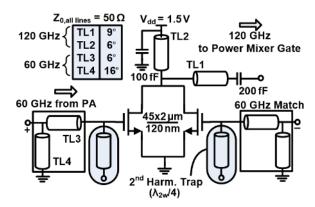

| 4.15 | Circuit diagram of the last stage of the implemented V-band amplifier chain                                    | 68 |

| 4.16 | Simulated S-parameter performance of the $60\mathrm{GHz}$ fundamental amplifier chain in                       |    |

|      | the source path of the power mixer.                                                                            | 69 |

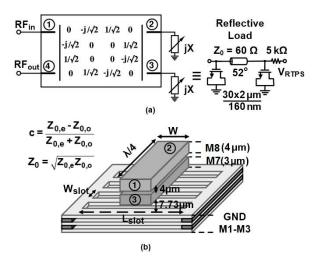

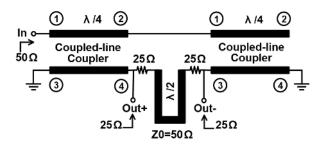

| 4.17 | (a) Circuit diagram of the RTPS. It uses a broadside coupled line 3 dB coupler and        |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | CLC reflective terminations. (b) Cross-section of the coupled line 3 dB coupler. A        |    |

|      | slow-wave technique has been used for achieving high even mode impedance as well          |    |

|      | as simplifying the design procedure                                                       | 70 |

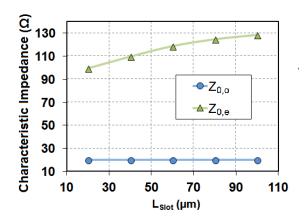

| 4.18 | Simulated characteristic impedance of the coupler in the even and odd modes. $W =$        |    |

|      | $12 \mu\mathrm{m},  W_{slot} = 10 \mu\mathrm{m}$ and $L_{slot}$ is varied                 | 70 |

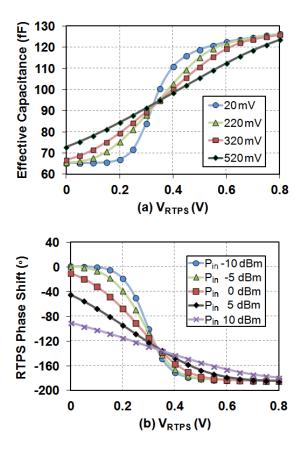

| 4.19 | (a) Simulated effective varactor capacitance for different signal amplitudes showing      |    |

|      | large signal effects. Larger signal amplitude across the varactor causes a reduction      |    |

|      | in capacitance range and tuning ratio (b) Simulated phase shift of the RTPS under         |    |

|      | large signal operation for different input power levels                                   | 73 |

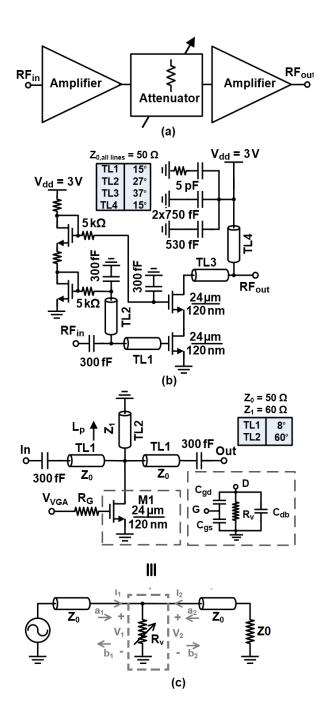

| 4.20 | (a) Block diagram of the variable gain amplifier. (b) Circuit diagram of the ampli-       |    |

|      | fiers. (c) Circuit diagram of the variable attenuator                                     | 76 |

| 4.21 | Circuit diagram of the impedance transforming Marchand Balun with a passive               |    |

|      | cancellation network between the balanced outputs. The passive network improves           |    |

|      | the output return losses and the isolation between output ports. $\dots$                  | 77 |

| 4.22 | Simulated performance of the Marchand Balun including (a) input and output return         |    |

|      | losses and insertion loss, and (b) phase and amplitude imbalance                          | 78 |

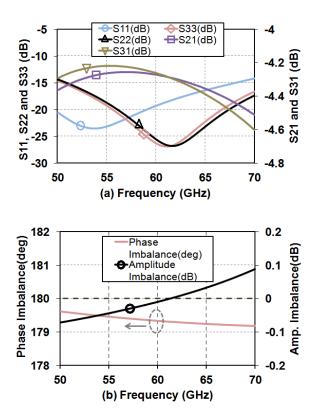

| 4.23 | Die photo of the test structure implemented to characterize the $60\mathrm{GHz}$ RTPS and |    |

|      | VGA cascade                                                                               | 79 |

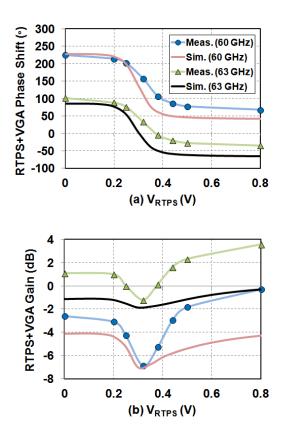

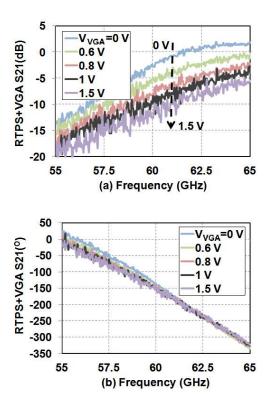

| 4.24 | Insertion (a) phase shift and (b) gain of the RTPS-VGA breakout versus RTPS               |    |

|      | control voltage at 60 and 63 GHz. The VGA has been set to maximum gain ( $V_{VGA} =$      |    |

|      | 0 V)                                                                                      | 80 |

| 4.25 | Insertion (a) gain and (b) phase-shift of the RTPS-VGA breakout versus VGA control        |    |

|      | voltage. For these measurements, $V_{RTPS} = 0  \text{V}.  \dots  \dots  \dots  \dots$    | 81 |

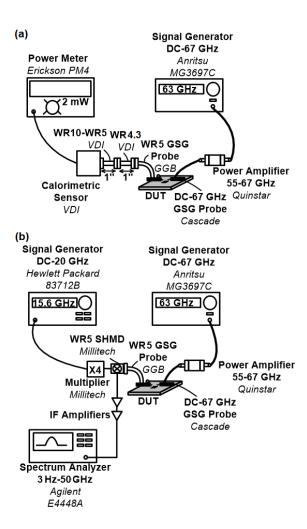

| 4.26 | Measurement setup of the power mixer prototype with (a) an Erickson power meter           |    |

|      | and (b) a second harmonic mixer downconverter (SHMD)                                      | 82 |

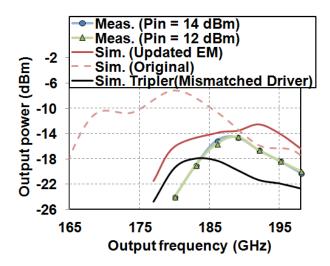

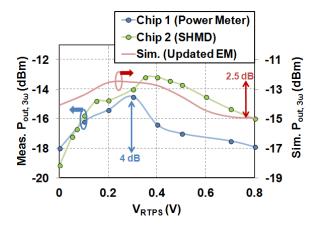

| 4.27 | Third harmonic output power of the implemented power mixer vs. output frequency                       |    |

|------|-------------------------------------------------------------------------------------------------------|----|

|      | measured with the power meter setup. The output power is plotted for the optimal                      |    |

|      | input phase at each frequency with the VGA set to maximum gain. The original                          |    |

|      | power mixer simulation, and the simulation with updated amplifier models that                         |    |

|      | capture the degradation in fundamental power available to the mixer are shown. For                    |    |

|      | comparison, a simulation of a frequency tripler driven by amplifiers with a frequency                 |    |

|      | mismatch similar to the power mixer implementation is also shown. The annotated                       |    |

|      | input power is at the fundamental frequency.                                                          | 83 |

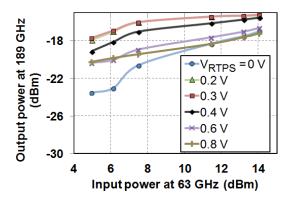

| 4.28 | Output power at $189\mathrm{GHz}$ vs. input power at $63\mathrm{GHz}$ for different input phase shift |    |

|      | (varying $V_{RTPS}$ ) measured with the power mixer setup. The VGA is set to maximum                  |    |

|      | gain                                                                                                  | 84 |

| 4.29 | Variation in output power of the power mixer at 189 GHz as the relative phase shift                   |    |

|      | between the input is changed by varying $V_{RTPS}$ . $V_{VGA}$ is adjusted to compensate              |    |

|      | for the RTPS gain variation across $V_{RTPS}$ settings. For these measurements, the                   |    |

|      | calibrated fundamental input power at the probe tip is $+12\mathrm{dBm.}$                             | 85 |

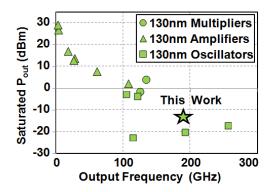

| 4.30 | Comparison of the output power of the $180-200\mathrm{GHz}$ power mixer with other $130\mathrm{nm}$   |    |

|      | CMOS signal sources at the same CMOS technology node                                                  | 87 |

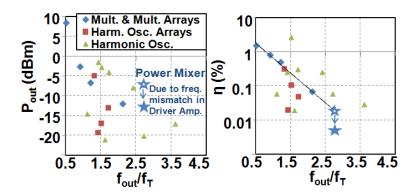

| 4.31 | Visual summary of Table 5.1. Even with frequency mismatch in the driver, the power                    |    |

|      | mixer has one of the highest power across technology nodes for $f_{out}/f_T > 2$ amongst              |    |

|      | mulitpliers and oscillator-arrays (per-element power). Mismatch can be corrected in a                 |    |

|      | re-spin by using updated EM models for drivers to achieve an efficiency comparable                    |    |

|      | to the multiplier and multiplier-arrays trend in efficiency.                                          | 90 |

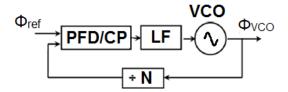

| 5.1  | Conventional Type-II Second Order PLL                                                                 | 92 |

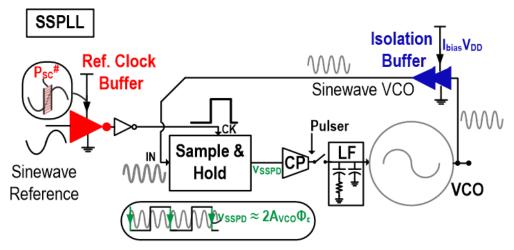

| 5.2  | (a) Sub-sampling phase detector. (b) Timing Diagram                                                   | 94 |

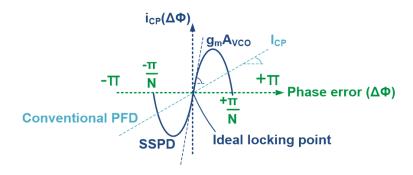

| 5.3  | Sub-sampling phase detector + charge pump profile and comparison with conven-                         |    |

|      | tional PFD+ charge pump. SSPD has higher gain and restricted monotonicity                             | 95 |

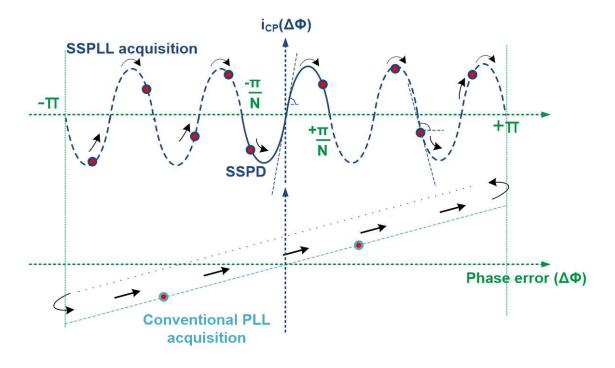

| 5.4  | Sub-sampling PLL architecture with acquisition aid                                                    | 96 |

| 5.5  | Acquisition process in SSPLL and conventional PLL. The red dot denoting the in-        |

|------|----------------------------------------------------------------------------------------|

|      | stantaneous phase error drifts across the phase-detector profile as the VCO frequency  |

|      | varies. Without a separate acquisition loop, the sign of feedback changes repeatedly   |

|      | in an SSPLL, while it remains the same for the conventional PLL 96 $$                  |

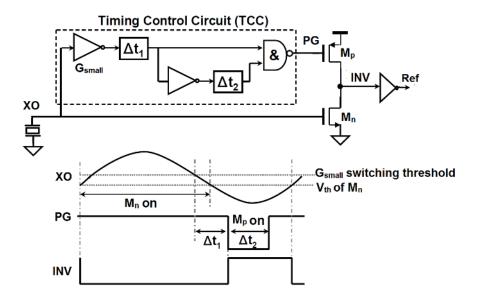

| 5.6  | Reference buffer power consumption reduction [3]. The on time of $M_n$ and $M_p$ are   |

|      | offset to reduce short circuit current                                                 |

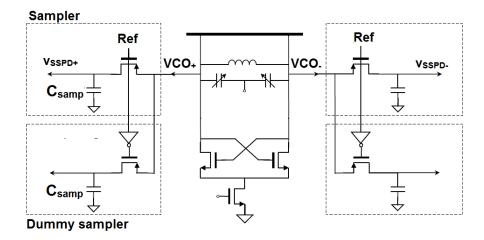

| 5.7  | Spur reduction technique [3]. Dummy switch and load for the VCO tank to prevent        |

|      | changing tank impedance during sampling                                                |

| 5.8  | Spur reduction technique [3]. To prevent spurs from periodic charge injection from     |

|      | the sampler into the VCO, there should be no difference in steady state between        |

|      | the VCO voltage at the start of the tracking phase and the sampled value stored on     |

|      | the capacitor. For this, the other reference edge is locked to a VCO zero crossing     |

|      | through a DLL. The noise on this edge is immaterial, so it can be generated using      |

|      | the low power short-circuit eliminating circuit of Fig. 6.6                            |

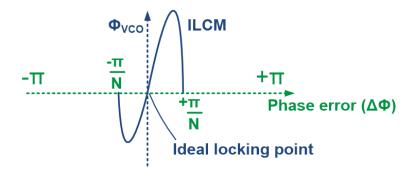

| 5.9  | Profile of equivalent phase detector in ILCM. This is taken from the simulated profile |

|      | under large thick pulse injection from [4]                                             |

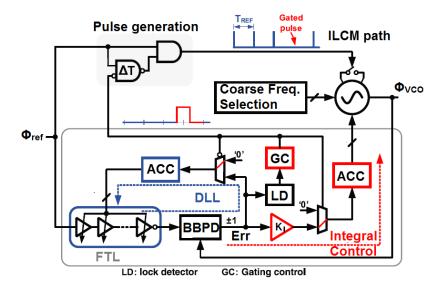

| 5.10 | From [4]. The injection locking path and the DLL are on simultaenously (blue time      |

|      | period). While the Type-I path works, the DLL matches the reference edges of the       |

|      | injection path and the integral path. When the injection path is gated (red time       |

|      | period), the paths in red are connected, and the accumulated phase error due to        |

|      | frequency drift alone is corrected                                                     |

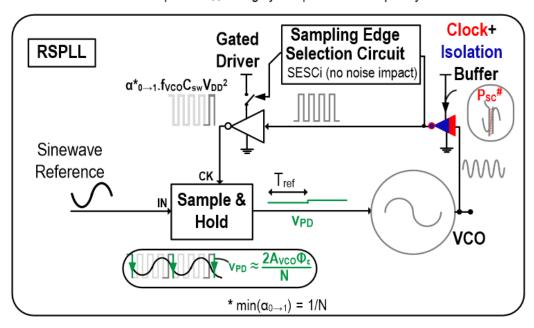

| 5.11 | Basic concept of the Reference-Sampling PLL. It combines the functionality of the      |

|      | power-hungry clock and isolation buffers to eliminate the dual noise penalty of two    |

|      | separate buffers. This helps realize very low jitter for a given power consumption     |

|      | while demonstrating low spur                                                           |

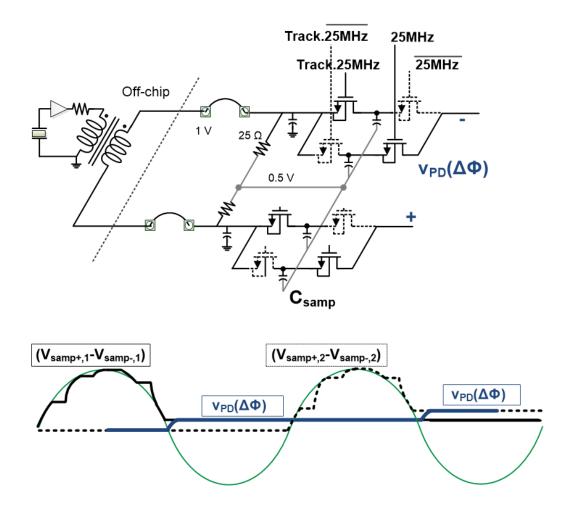

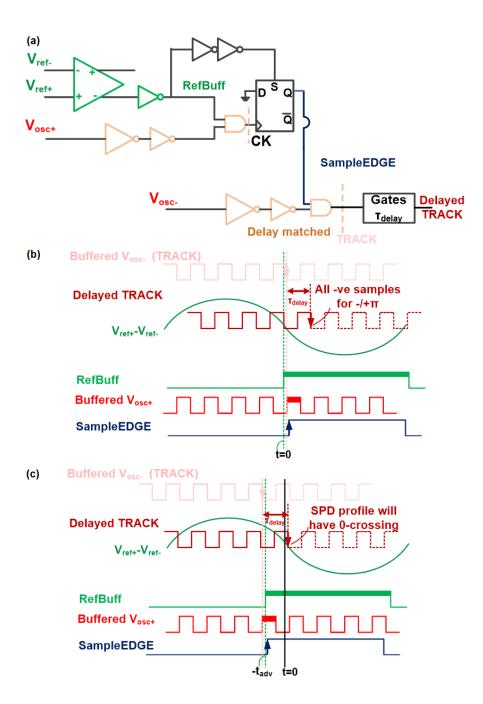

| 5.12 | Proposed sampled phase detector and timing diagram. The VCO is used to evaluate        |

|      | phase error in the loop by sampling voltages on the reference sinewave. The relevant   |

|      | sample pertaining to the phase error is selected using the Sample Edge Selection       |

|      | Circuit (SESCi). The noise of SESCi does not affect the sampled value 109              |

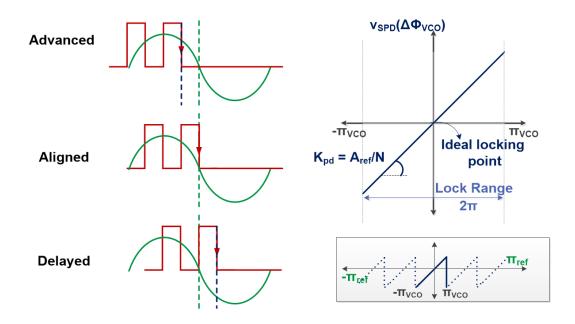

| 5.13 | Profile of proposed sampled phase detector. The profile is montonic over $\pm \pi_{VCO}$    |

|------|---------------------------------------------------------------------------------------------|

|      | unlike ILCM and SSPD which are only monotonic over $0.5 \pm \pi_{VCO}$ 110                  |

| 5.14 | Half rate multiplexing of samples in each differential path. This scheme reduces the        |

|      | area for sample and hold capacitances                                                       |

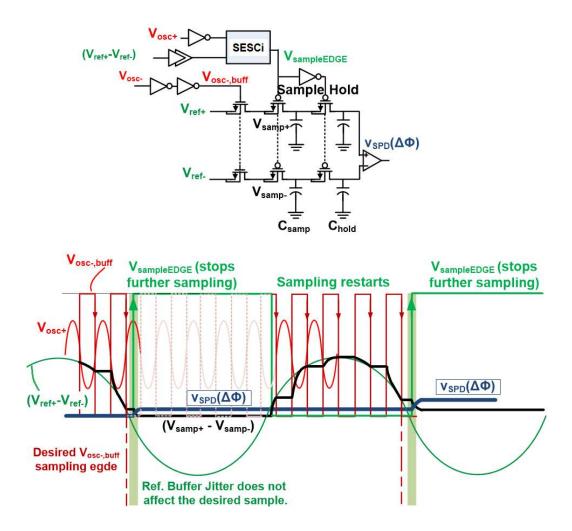

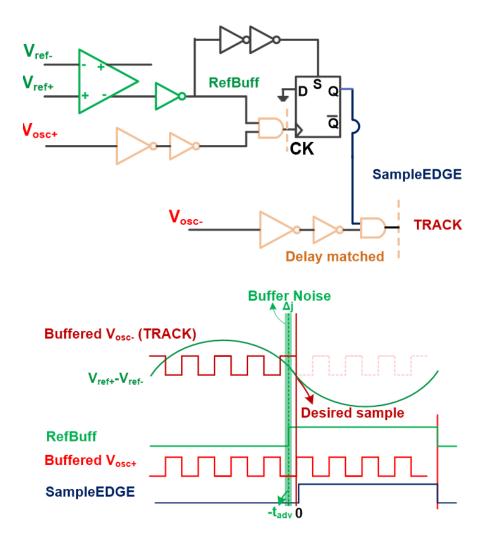

| 5.15 | Sample Edge Selection Circuit (SESCi) selects the sample relevant to estimating the         |

|      | VCO phase error. The timing diagram shows that the reference buffer edge RefBuff            |

|      | in the SESCi does not contribute noise to the $TRACK$ signal                                |

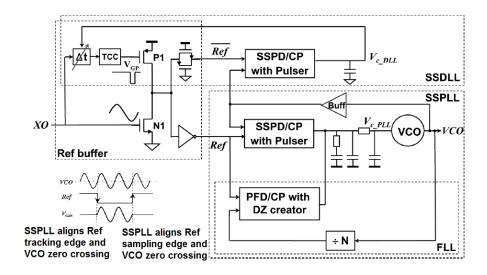

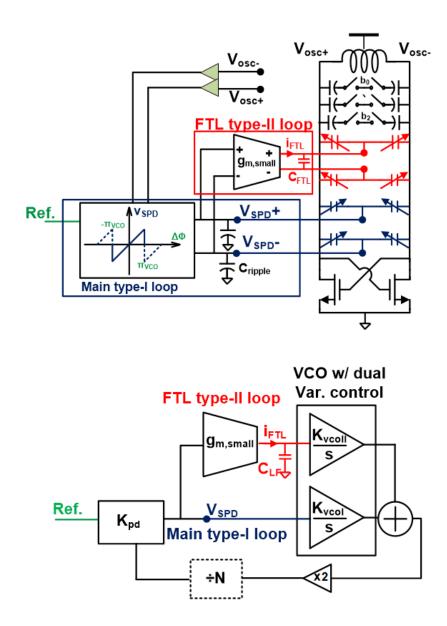

| 5.16 | Architecture and block diagram of proposed PLL                                              |

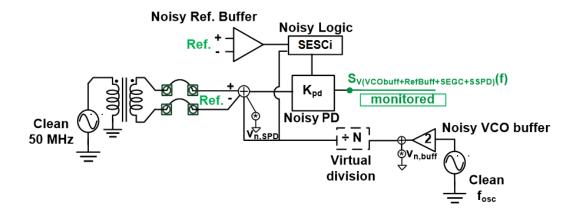

| 5.17 | Different sources of noise in the proposed architecture                                     |

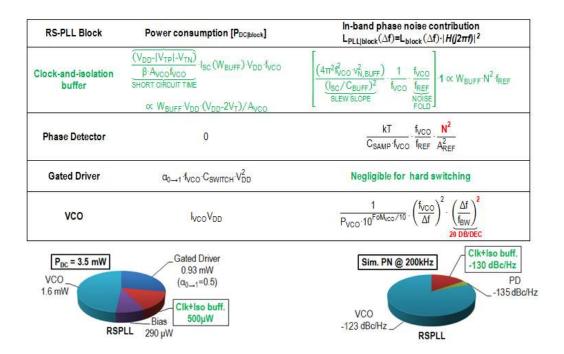

| 5.18 | A detailed analysis of noise contributions and power consumption in the RSPLL               |

|      | normalized to 2.21 GHz                                                                      |

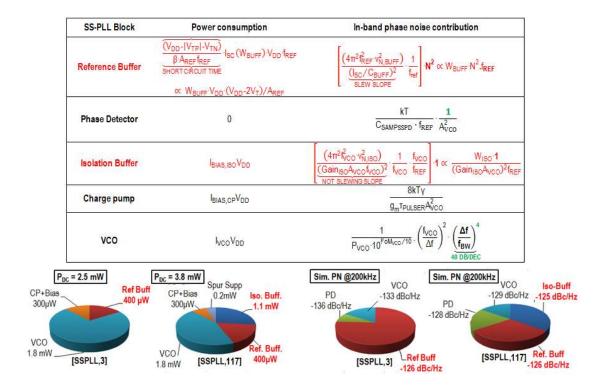

| 5.19 | A detailed analysis of noise contributions and power consumption in the SSPLL               |

|      | normalized to 2.21 GHz                                                                      |

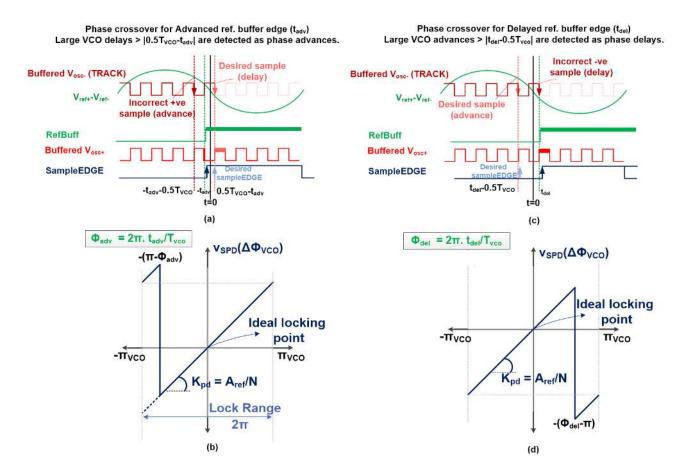

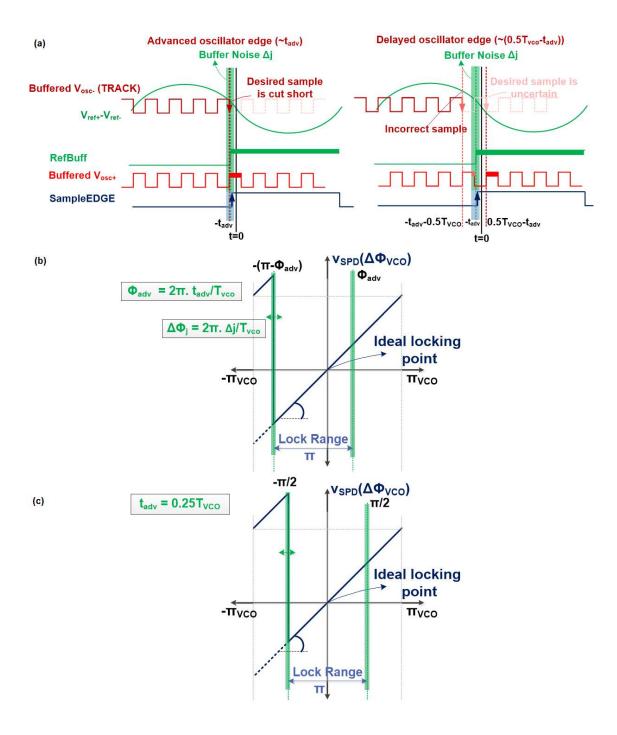

| 5.20 | (a) When reference buffer generates an advanced edge with respect to reference              |

|      | sinewave zero-crossing, the PD resolves large VCO edge delays as advances. (b)              |

|      | Phase detector profile remains monotonic with advanced reference buffer edge. (a)           |

|      | Delayed reference buffer edge resolves advances as delays (b) Phase detector profile        |

|      | with delayed reference buffer edge is also monotonic                                        |

| 5.21 | (a) Delay due to gates after $TRACK$ is generated results in sampling due to $DelayedTRACK$ |

|      | (b) Timing diagram when $RefBuff$ is at $t=0$ . All samples are -ve and there is            |

|      | no steady state solution for the feedback loop. (c) By advancing $RefBuff$ we can           |

|      | compensate for $\tau_{delay}$ ensure a solution to the feedback loop                        |

| 5.22 | Effect of reference buffer noise on the PD profile creates two zones of uncertain           |

|      | samples $\pi$ apart. The timing diagram is shown for noise on an advanced $RefBuff$         |

|      | edge. By tuning $RefBuff$ position, we can position the zones of uncertainty for            |

|      | higher robustness and place the ideal locking point in the center of the range $129$        |

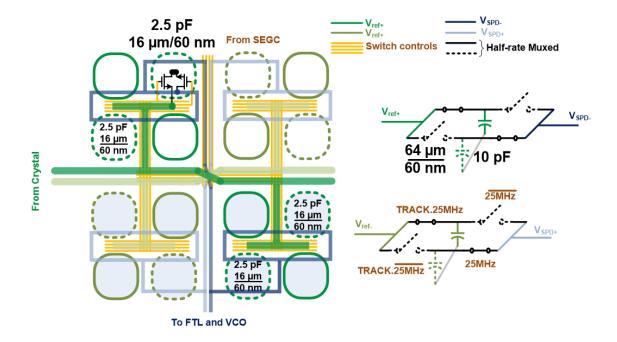

| 5.23 | Common centroid layout of differential Sampling Phase Detector                              |

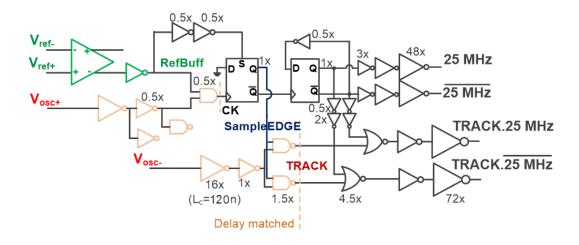

| 5.24 | SESCi component sizing and circuit diagram                                                  |

| 5.25 | Reference buffer with tunable delay                                                         |

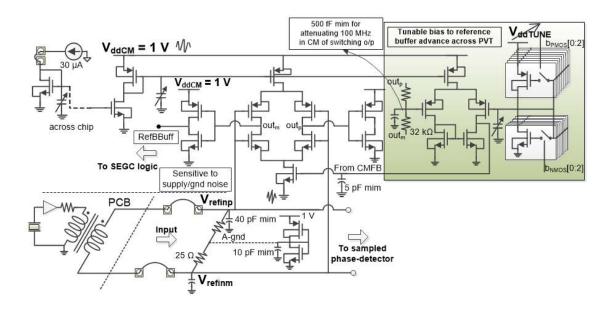

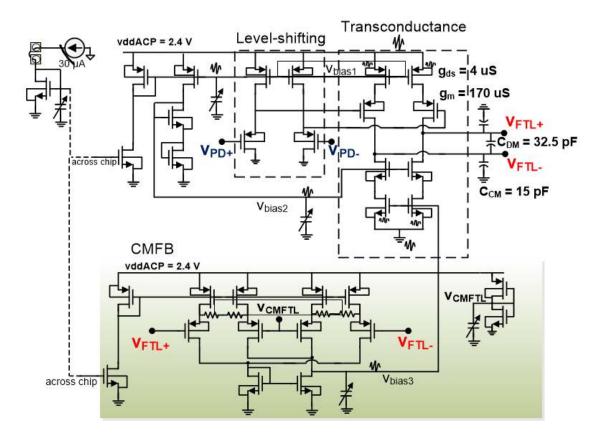

| 5.26 | Circuit diagram of Frequency Tracking Loop (FTL) with CMFB                                  |

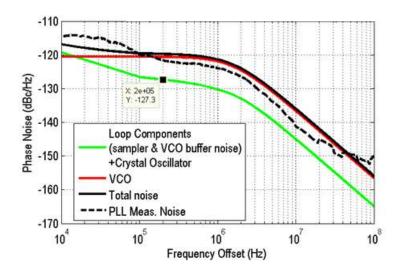

| 5.27 | Simulation setup for loop noise                                                                         | 41 |

|------|---------------------------------------------------------------------------------------------------------|----|

| 5.28 | Comparison of simulated PLL noise with measured performance at 2.55 GHz 1                               | 42 |

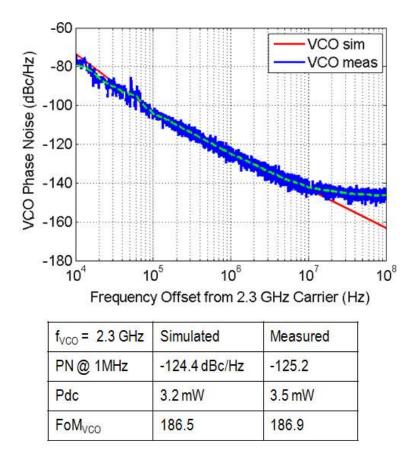

| 5.29 | Phase noise corresponding to the best measured FoM $_{VCO}$ at 2.3 GHz ( $P_{dc}=3.26mW$ ,              |    |

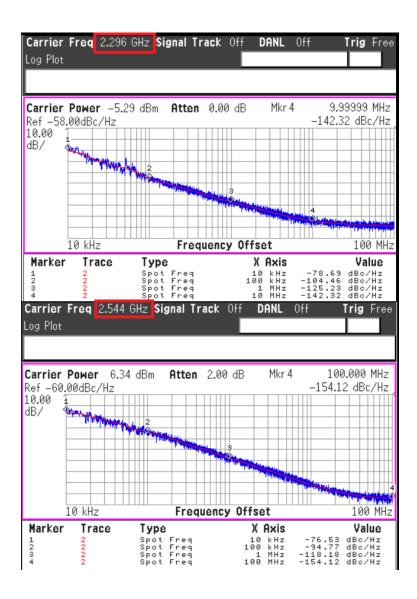

|      | $\text{FoM}_{VCO,1MHz} = 186.7$ ) and 2.55 GHz ( $P_{dc} = 1.6mW$ , $\text{FoM}_{VCO,1MHz} = 184.2$ ) 1 | 43 |

| 5.30 | Comparison of measured VCO performance with simulated phase noise at $2.3~\mathrm{GHz.}$ . $1$          | 44 |

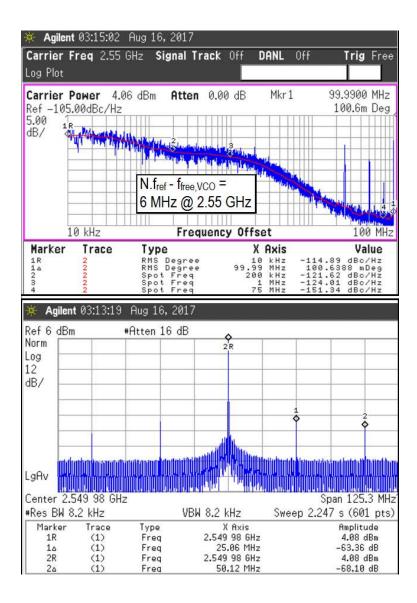

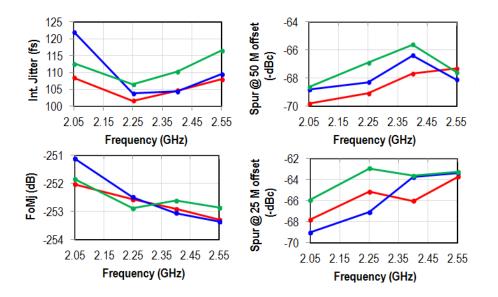

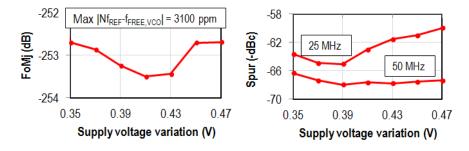

| 5.31 | Measured performance of the RSPLL at 2.55 GHz. The RSPLL shows a record $\mathrm{FoM}_j$                |    |

|      | of $-253.5\mathrm{dB}$ amongst explicit PLLs, with the lowest reference spur of $-67\mathrm{dBc}$ for   |    |

|      | such a low jitter-power figure-of-merit. The $25\mathrm{MHz}$ spur is a result of half-rate             |    |

|      | multiplexing, and is not intrinsic to the RSPLL architecture                                            | 46 |

| 5.32 | Measured performance across carrier frequency across three different samples $1$                        | 47 |

| 5.33 | Measured performance across VCO supply voltage variation. The desired lock fre-                         |    |

|      | quency is 2.55 GHz                                                                                      | 48 |

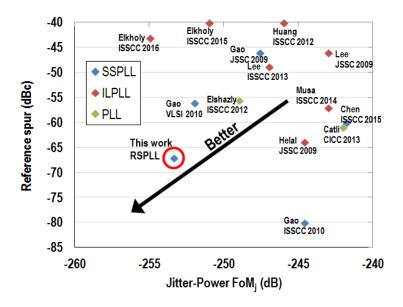

| 5.34 | The RSPLL architecture combines the best aspects of subsampling PLL and ILCM                            |    |

|      | architectures to show significant improvement in the jitter versus spur performance                     |    |

|      | space                                                                                                   | 48 |

| 5.35 | Possible approach to modifying loop bandwidth without changing area (total sam-                         |    |

|      | pling cap size remains same), power consumption (total switch size remains same)                        |    |

|      | or output noise                                                                                         | 49 |

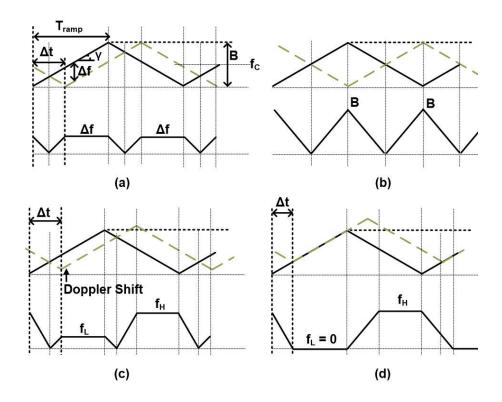

| 6.1  | FMCW with triangular chirp. (a) Stationary object. (b) Max. range for stationary                        |    |

|      | object. (c) Moving object and doppler shift. (d) Max. velocity for moving object at                     |    |

|      | a given distance                                                                                        | 54 |

| 6.2  | EO-PLL photoelectric interface                                                                          | 57 |

| 6.3  | EO-PLL block diagram                                                                                    | 59 |

| 6.4  | Proposed EO-PLL architecture with mixer-based phase detector                                            | 64 |

| 6.5  | Alcatel A1905LMI laser tuning curve                                                                     | 65 |

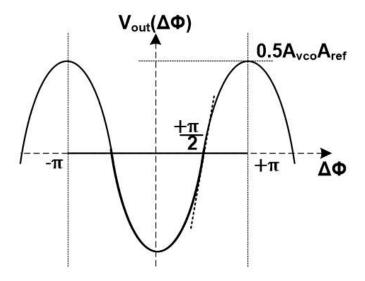

| 6.6  | Mixer-based phase detector profile with limited monotonicity                                            | 66 |

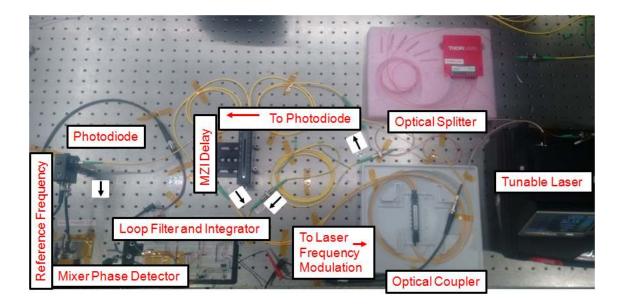

| 6.7  | Photograph of measurement setup to verify performance of mixer based continuous                         |    |

|      | analog correction loop with bandwidth equal to reference frequency                                      | 71 |

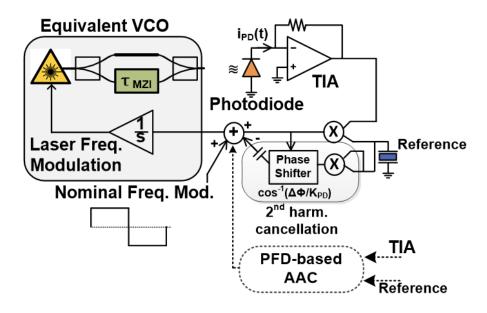

| 6.8  | Second harmonic cancellation in mixer-based EO-PLL                                                      | 73 |

| 6.9  | EO-PLL around laser phase shifter with electronic phase-domain integrator 1                             | 75 |

| 6.10 | EO-PLL around laser phase shifter with downconverted ramp locked by conventional             |

|------|----------------------------------------------------------------------------------------------|

|      | electronic FMCW PLL techniques                                                               |

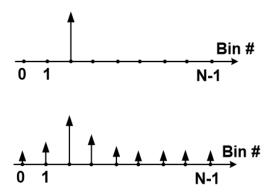

| A.1  | Single carrier (a) up- and down- converted by matched LO (b) leaking into the other          |

|      | bins when up-converted and down- converted by mismatched LO 199                              |

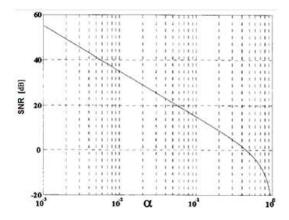

| A.2  | SNR from Inter Carrier Interference (ICI) due to Carrier Frequency Offset (CFO).             |

|      | CFO is represented on the x-axis as a fraction $\alpha$ of the inter-carrier spacing [5] 199 |

| A.3  | The limit on LO phase noise is calculated assuming that the OFDM data is just                |

|      | carriers                                                                                     |

### List of Tables

| 2.1 | Comparison of Reported CMOS-Based Sources Operating Above 200 GHz          | 40  |

|-----|----------------------------------------------------------------------------|-----|

| 3.1 | Recent CMOS Multipliers beyond 100 GHz                                     | 49  |

| 4.1 | Recent CMOS and SiGe Sources beyond 150 GHz                                | 89  |

| 4.2 | Recent CMOS and SiGe Sources beyond 150 GHz (continued)                    | 90  |

| 5.1 | Comparison of RSPLL with state-of-the-art integer-N frequency synthesizers | 151 |

#### ACKOWLEDGMENT

This thesis has been a long time coming, and it wouldn't be here without the support and encouragement, both academic and interpersonal, of my advisor Dr. Harish Krishnaswamy. Not many advisors would have the patience he has had for my particular brand of maladjustment, and I will always be grateful to him for providing an environment in which I could experiment with ideas, and individuality. I am also grateful for the stability he provided when the waters were tempestuous. Thank you for helping me develop as a researcher, for teaching me, and for leading by example on how to surmount fearsome challenges.

As they say, it takes a village. My mentors at IBM - Alberto Valdes Garcia, Mark Ferriss, and Bodhi Sadhu, and at Bell Labs, Mike Zierdt - thank you for giving me an opportunity to work with you and to learn from you. I am deeply grateful to Mark for all of the time he has spent in discussions with me, and for the intuitive insights he helped reveal.

The foundation all that is decent and worthwhile in me - my mum, my dad, my brother, my grandparents, and Babaji. They were there for every crisis of faith, when I thought the thread slipped through my fingers in the dark. My aunts Tanuja and Anupa, and the two people who raised me - Mini Ma and Jija, for their love and affection and concern. And though they will probably not read this, Mekhala, Mayu, Shinjini, Anshuman, Lorna Aunty, David Uncle and Susan.

My wonderful, loving and dear friends Karthik Swaminathan and Nandhini Chandramoorthy, and the Hobbes to my Calvin, Markus Nussbaum. They were my family away from home, and made life so much more equitable and importantly, happy.

Thanks are due to my labmates for all that they have helped me learn, in particular Jeffrey Chuang, Anandaroop Chakrabarti, Negar Reiskarimian and Mahmood Dastjerdi. Tolga Dinc deserves a special mention, for the long hours spent taping out with two weeks to go, and bonding the most stubborn chips with two days to go. Sohail Ahsan, though new to the lab, has been great fun to work with on the recent photonics research, and I wish him the best of luck.

To Ma, Papa, Dadda, my grandparents and Baba

#### Chapter 1

#### Introduction

The need for clean and powerful signal generation is ubiquitous, with applications spanning the spectrum from RF to mm-Wave, to into and beyond the terahertz-gap. RF applications including mobile telephony and microprocessors have effectively harnessed mixed-signal integration in CMOS to realize robust on-chip signal sources calibrated against adverse ambient conditions. Combined with low cost and high yield, the CMOS component of hand-held devices costs a few cents per part per million parts. This low cost, and integrated digital processing, make CMOS an attractive option for applications like high-resolution imaging and ranging, spectroscopy and the emerging 5G communication space. However, these applications are expected to impose far more exacting specifications on power and spectral purity at much higher frequencies than conventional RF synthesizers.

RF-based detection and ranging (RADAR) techniques when expanded to mmWave and even sub-mmWave frequencies can enable centimeters to millimeters of resolution, which prove useful in navigation systems and satellite imaging. mm-Wave and sub-mmWave systems can leverage windows in the absorption spectrum at 94 GHz, 140 GHz and 220 GHz for imaging in poor visibility conditions [6, 7]. 24 GHz and 77 GHz systems have found use in automotive radars for parking assistance and automatic cruise control [8]. Fine resolution ranging applications can require very clean signals to minimize reciprocal mixing between the transmitted and received signal, while long range applications require powerful beams.

Expanding ranging techniques to the optical domain can yield very fine angular and distance resolution. Apart from automotive applications, this finds particular use in 3-D imaging. How-

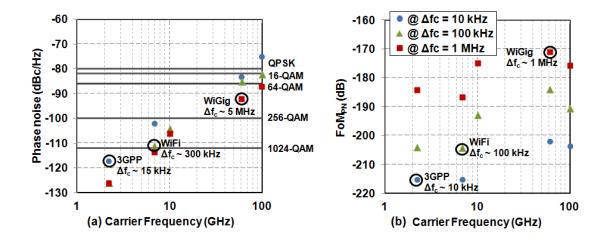

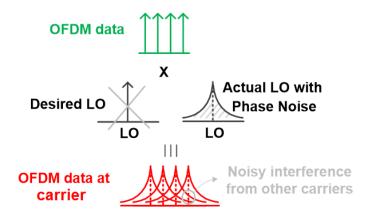

Figure 1.1: Phase noise and  $\text{FoM}_{PN} = \left(\frac{f_c}{\Delta f_c}\right)^2 / (L_{\Delta f_c} P_{DC,mW})$  for state-of-the-art CMOS PLLs for different carrier frequencies  $f_c$  at different offsets  $\Delta f_c$ . Maximum phase noise limits for m-QAM at the OFDM-based standard's carrier spacing is shown for PLLs with loop bandwidth of 100 kHz. 3GPP to WiGig impose phase noise requirements at increasing carrier spacing  $\Delta f_c$ . Requirements for evolving OFDM-based standards are met by CMOS for at least 64 QAM, but with poorer  $\text{FOM}_{PN}$ .

ever, cost-effective tunable optical sources are temperature-sensitive and have nonlinear tuning profiles, rendering precise frequency modulations or 'chirps' untenable. Locking them to an electronic reference through an electro-optical PLL, and electronically calibrating the control signal for nonlinearity and ambient sensitivity, can make such chirps possible. To avoid high-cost modular implementations, we seek to leverage the twin advantages of silicon-intensive integration and low-cost high-yield towards developing a single-chip solution that uses on-chip signal processing and phased arrays to generate precise and robust chirps for an electronically-steerable fine LIDAR beam.

For next generation communication networks that promise increased connectivity through improved accessibility, lower latency and better reliability, innovations at the network layer and in signal processing will require concomitant advances in hardware. A shift to higher frequencies will bring with it the advantages of higher bandwidth and new mobile networks are expected to incorporate a large mm-Wave component. Even in current network deployments, point-to-point highly directional mm-wave links, implemented through small form-factor phased arrays, are used

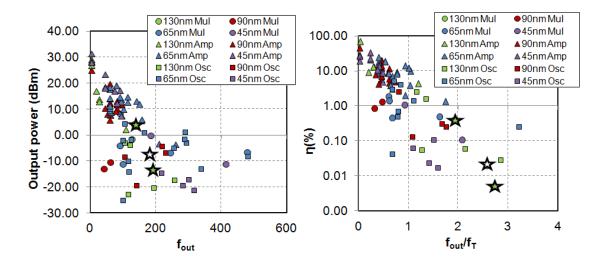

Figure 1.2: Output power and efficiency roll-off in CMOS with increasing frequency.

as part of the wireless backhaul of data, augmenting or even replacing wireline links where fiber is hard to route. This has led to a vast research effort in recent years in mm-Wave communication systems, peppered with innovations at the system level and in transciever chain building blocks such as power amplifiers, power combiners, low-noise amplifiers, mixers and of course synthesizers, much of which will be leveraged in the coming 5-G network evolution. For widespread adoption it is necessary that such technology is developed in a low cost, reliable process like CMOS that enables integrated mixed signal processing. Fig. 1.1 shows the phase noise requirement of different m-QAM constellations on a multi-carrier scheme like OFDM, along with the best reported phase noise of CMOS synthesizers for different carrier frequencies. For any m-QAM in OFDM, the integrated noise satisfying EVM is proportional to the in-band noise at carrier spacing  $\Delta f_c$  in the standard, and the loop bandwidth. For a detailed derivation, see Appendix A. CMOS has been able to keep up with the tighter demands for phase noise for different standards though with reducing margin. The figure also means that 5-G, with its push towards 100x end-user data rates, is expected to need even cleaner sources that enable transmission of dense modulation on powerful high frequency carriers.

A consequence of expanding connectivity in future networks will be high rates of data transfer between devices and the need for large throughput in processing this data. Wide bandwidth wireless chip-to-chip interconnects have been proposed as a replacement for wired connections to enable high density implementations which can pack in intensive functionality in a small foot print. In addition to communication applications, high bandwidth chip-to-chip interconnects can also prove very useful for fast data transfer inside data centers and in dense and powerful computing infrastructure. Owing to the short distance and controlled environment in which these links operate it is possible that these interconnects may even be implemented at sub-mmWave frequencies. With relation to CMOS, power generation in CMOS at sub-mmWave frequencies is very challenging as this frequency range is beyond the transistor cut-off frequency and relies on weak nonlinearities for harmonic generation. While the short wavelength leads to small antenna size and signal can be boosted through integrated phased arrays, the weak individual transmitting element remains a bottleneck. The latter can drive up the number of elements needed in an array presenting serious on-chip signal routing and distribution issues. Fig. 1.2 shows output power and efficiencies in recent sub-mmWave CMOS sources. Although not the focus of this thesis, receiver design for high sensitivity and efficiency also remain open research problems. Fully integrated CMOS centimeter range wireless communication links at 135 GHz and 260 GHz with an energy efficiency of 10pJ/bit [9] and 30 pJ/bit [10] have been demonstrated. While promising, this is still short of state-of-the-art energy efficiencies of 4 pJ/bit in on-chip RF interconnects ( $\leq 1$  cm) and optical interconnects ( $\geq 10 \text{ cm}$ ) [11]..

Another application in the sub-mmWave range is spectroscopy. [12–16]. Certain molecules have resonances in the 100-300 GHz spectrum, and development of clean, wideband synthesizers will find applications in medical screening such as skin cancer detection, defensive technology such as the detection of poisonous gases like sarin and methyl chloride, product evaluation such as non-destructive pharmaceutical testing and as a useful investigative tool for material scientists, and perhaps even a "tricorder" in the decades to come [17], [18]. Indeed development in CMOS, where both sample excitation and data processing can be performed in a miniaturized area, could inform a drastic improvement in the portability and affordability of such technology across healthcare and industry.

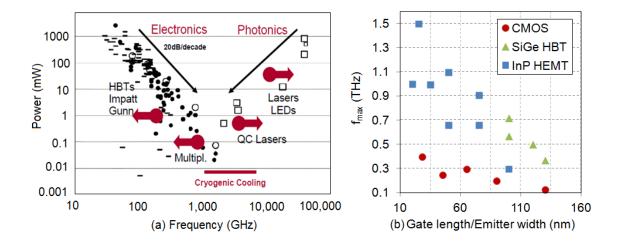

All this is to say that the coming generation of applications will present unconventional challenges for transistor technologies - whether it is to squeeze more performance in the conventionally used spectrum, already wrung dry, or signal generation and system design in the relatively emptier mm-Wave to sub-mmWave spectrum, most of the latter falling in the so-called "Terahertz Gap" shown in Fig. 1.3 [1]. Indeed, transistor scaling and innovative device physics leading to

Figure 1.3: (a) "Terahertz Gap" between Electronics and Photonics, [1] (b) Comparison of maximum oscillation frequency  $(f_{max})$  across scaling technology nodes.

new transistor topologies have yielded higher cut-off frequencies in CMOS, as in Fig. 1.3, though still lagging well behind SiGe and III-V semiconductors. Similarly the noise in CMOS remains high compared to bipolar SiGe technology. Quick roll-off in the gain and reducing power supply can be formidable obstacles for performance at mm-Wave to sub-mmWave frequencies. To avoid multimodule solutions with functionality partitioned across different technologies, CMOS must be pushed out of its comfort zone, and technology scaling has to have accompanying breakthroughs in design approaches not only at the system but also at the block level. In this thesis, while not targeting a specific application, we seek to formulate the obstacles in synthesizing high frequency, high power and low noise signals in CMOS and construct a coherent design methodology to address them.

The first half of this thesis deals with signal synthesis and power generation in CMOS in the so-called Terahertz Gap. This region lies outside the range of frequencies where the MOS transistor has gain, and necessitates frequency generation through harmonic extraction either as harmonic oscillators or as frequency multipliers.

Chapter 2 presents a technique to implement an oscillator operating at the maximum oscillation frequency of a given technology, hereby denoted as  $f_{max}$ . The conventional definition of  $f_{max}$  includes only the limit defined by device gain falling to one as a result of internal losses in a transistor. As such oscillators cannot startup beyond technology  $f_{max}$ . Due to the high loss in

passive components, especially with increasing frequency, the actual achievable maximum fundamental frequency for oscillators is lower. Interestingly, the presented design methodology results in a closed form expression relating the actual achievable maximum oscillation frequency or effective  $f_{max}$  (denoted as  $f_{max,eff}$ ) of a technology to the transistor loss as well as the quality factor of the passives in the BEOL irrespective of the specific topology of passives used in the resonant network. This chapter also forays into harmonic generation for signals beyond technology  $f_{max}$  and dwells on determining the optimal load for maximizing harmonic power transfer from the oscillator under large signal conditions. Using the discussed techniques two oscillators generating second harmonic outputs at 200 GHz and 300 GHz are demonstrated in a 45 nm SOI-CMOS technology with  $f_{max}$  of 200 GHz.

In Chapter 3, we study the alternate approach of harmonic generation through frequency multipliers. Harmonic power from multipliers is a product of the harmonic current generated by the transistor, and the load to which it is delivered. The most common harmonic current generation technique in frequency multipliers is through a MOS device biased such that the voltage swing of the input fundamental frequency sinusoid at the gate generates a clipped sinusoidal current. Most recent works focus on finding the input bias that yields an optimal duty cycle of the clipped sinusoid to maximize content at a desired harmonic. The optimal load is then usually obtained by a large signal load pull simulation. Several factors can limit the output load such as the I-V conduction loss, output matching network loss, gate resistance and substrate loss. We investigate the dominant factor that affects the output load and derive a scaling trend for output harmonic power generated from conventional frequency multipliers. A 135 GHz frequency doubler generating +4 dBm output power at 1.1  $\times$  technology  $f_{max}$  is implemented in 130 nm CMOS to verify the presented theoretical formulation. This study is also useful because it shows that substrate loss is the limiting loss mechanism for output load. Therefore, short of techniques that can circumvent substrate loss, increase in harmonic power from a given device size will only be got from increasing harmonic current generated through the device transconductance. This necessitates using transistor nonlinearity more effectively than simple sinusoidal clipping and duty cycle optimization, and forms the basis of the work in the next chapter.

In Chapter 4, we present a power mixer topology that generates the third harmonic current by mixing the first and second harmonic signals by feeding them to a MOS transistor at the source and gate respectively. By controlling the amplitudes and relative phase shifts of the input signals we optimize how the device moves through various regions of operation so that it generates waveforms with more third harmonic content than the conventional frequency multipliers. This nonlinearity engineering technique is shown to generate three times more current than a frequency tripler for the same fundamental swing. Given that the optimal load is limited by substrate loss in both cases translates to nine times higher output power. This chapter also does a rigorous comparative study of the two approaches in terms of conversion gain and long term reliability, the latter is especially important in decreasing supply voltages of scaled CMOS processes. A 180 GHz power mixer generating -13.5 dBm at  $1.5 \times$  technology  $f_{max}$  is demonstrated in a 130 nm CMOS process.

The second part of this thesis is devoted to low noise phase locked loops (PLLs) at RF frequencies, and to electro-optic PLLs (EO-PLLs) in developing robust Light-Detection-And-Ranging (LIDAR) systems.

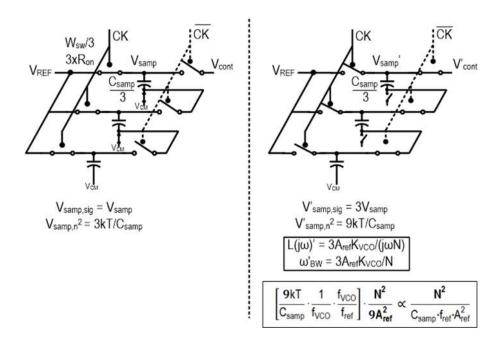

Chapter 6 reviews state-of-the-art techniques for low jitter FoM CMOS PLLs based on LC-VCOs including subsampling PLLs (SSPLL) and injection locked clock multipliers (ILCM) with high-multiplication ratio. The SSPLL greatly attenuates the noise from the phase detector and charge pump by removing the N<sup>2</sup> multiplication of the phase noise from these blocks. In ILCMs, these blocks are altogether eliminated. The dominant source of noise in these two techniques is the in-band reference buffer, the noise of which is still multiplied by N<sup>2</sup>, and the out-band VCO noise. These two blocks also consume the most power. In recent work, several LC-VCOs topologies with phase-noise-and-power FoM close to theoretical achievable limit have been demonstrated, and the reference logic remains the last hurdle. A new type-I RF PLL approach, the reference-sampling PLL (RSPLL) is presented which eliminates the reference buffer and samples the reference sinewave using the fast VCO waveform. Of the multiple samples generated, the relevant sample is selected every N VCO cycles through a very low noise and low power selection logic. Further, the isolation of the VCO tank from any varying loads helps simultaneously achiever low spur without additional circuitry. Using this approach, a 2.05-2.55 GHz RSPLL achieves a record FoM<sub>i</sub> of -253.5dB among explicit PLLs and reference spur <-67 dBc. This work achieves record numbers across architectures in the low-jitter versus low-spur performance space.

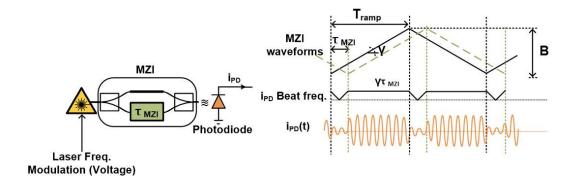

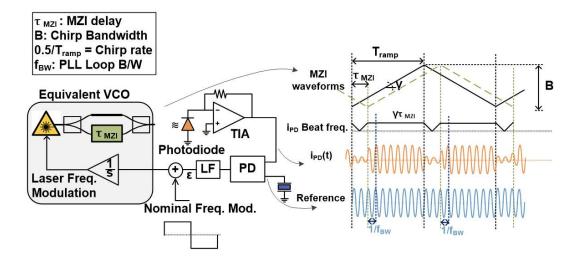

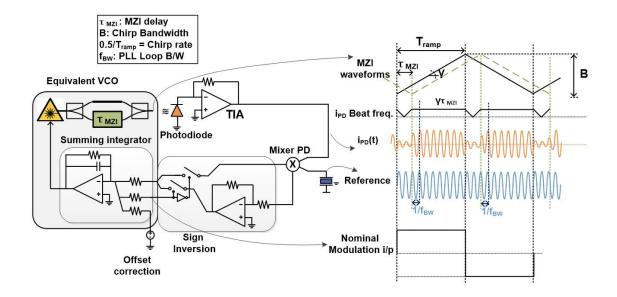

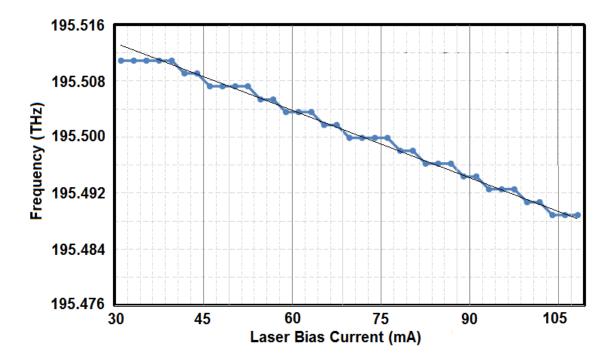

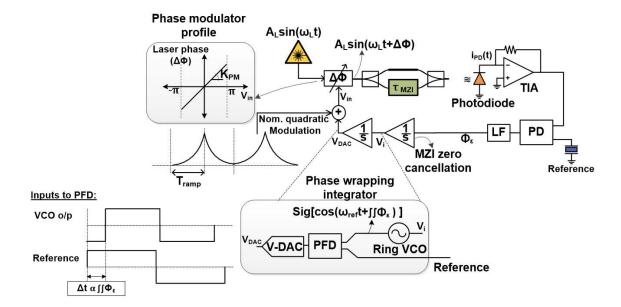

Chapter 6 discusses ongoing work that brings together concepts developed for signal generation towards a hybrid CMOS-Optical approach to Frequency-Modulated Continuous-Wave (FMCW)

LIDAR. In any electro-optic PLL (EO-PLL), a Mach-Zender Interferometer (MZI) is used as a delay discriminator to generate low frequency signals with information about optical performance. The low frequency signal can be processed by the electrical component of the loop to provide corrective behavior to the optical component. In the case of FMCW LIDAR, the photodiode generates a low frequency signal with frequency proportional to the modulation slope and the discriminator delay which can then be locked to an electrical reference. Based on the settling behavior of the triangular frequency chirp, very high reference frequencies may be required. For the photodiode output to match the reference for a given modulation slope, this yields impractically large optical delays in the MZI. We break the tradeoff of settling behavior and on-chip optical delay by proposing a novel PLL architecture which provides continuous error correction and has a bandwidth (settling) equal to reference, rather than a factor of ten lower as in conventional PLLs. This allows us to reduce MZI form factor by ten times. A discrete implementation of the proposed PLL is demonstrated. The chapter concludes by proposing future work on several new architectures for EO-PLLs that address different challenges in EO-PLL implementations.

Chapter 8 concludes the dissertation with a summary of the academic contributions of the thesis.

#### Chapter 2

# THz Frequency Synthesis: Maximum Gain Ring Oscillator

#### 2.1 Technologies for high frequency signal generation

Sub-mmWave signals have been dominantly generated using III-V compound semiconductors, [19–26]. In [19], using a 250nm InP HBT technology with a maximum frequency of oscillation  $f_{max} > 800 \text{GHz}$ , the authors have demonstrated fundamental oscillators at 573GHz and 412.9GHz with -19 dBm and -5.6 dBm of output power respectively. Signal generation in the high-mmWave/sub-mmWave range has also been successfully demonstrated using heterostructure barrier varactor (HBV) multipliers [27–31]. Most recently, the authors of [30] have demonstrated an HBV quintupler generating 60mW of power at 175GHz. Signal sources based on GaAs Schottky diode multipliers have also been constructed [32–34]. The authors in [32] generate more than 0dBm of power in the 840-900 GHz range using a frequency multiplier chain. The authors in [33] have shown -17.5 dBm of output power at 2.58 THz.

SiGe technologies have also become an active avenue for signal generation in the mmWave and sub-mmWave regimes, [35–40]. The authors in [37] construct a push-push oscillator generating -4.5dBm at 190GHz in a SiGe:C bipolar technology with an  $f_{max}$  of 275GHz. A 278GHz push-push oscillator in the same technology has been shown in [40]. Recently, in a 250nm SiGe BiCMOS process ( $f_{max}$ =435GHz), the authors in [35] have shown a spatially power combined array of four frequency multipliers generating an EIRP of -17dBm at 820GHz.

Modern CMOS technology nodes have an  $f_{max}$  of about 150-300GHz (130nm-65nm CMOS). Loss in passive components is also quite high at these frequencies, and consequently these technologies cannot provide amplification in the sub-mmave/THz region. Current research focuses on building oscillators close to and below  $f_{max}$  (typically below 200GHz), and extracting harmonics to extend the output frequency  $(f_{out})$  beyond  $f_{max}$ . The authors in [41] use the push-push technique with a cross-coupled oscillator (XCO) in 45nm CMOS to generate a second harmonic at 410 GHz with -49dBm power. The authors in [42] feed the four 90° out-of-phase outputs of a quadrature XCO to a rectification circuit that feeds the fourth harmonic to an external 50 $\Omega$  load. This shifts the burden of generating harmonic power from the oscillator core to the rectification circuit. A -46dBm signal at 324GHz is shown in 90nm CMOS. In [43], the authors combine the fourth harmonic current at the source node of the coupling transistors of a quadrature XCO to generate a -36.6dBm 553GHz signal in 45nm CMOS. They include a matching network between the common source node and the antenna to increase the fourth harmonic power transmitted. In [44], the inductance of a regular XCO is split between the core and the buffer stage. This mutually couples back the signal from the buffer to the core to improve the oscillator loop gain and thus improve the fundamental oscillation frequency to 300.5GHz in 65nm CMOS. The authors of [45] have designed a travelling wave-oscillator with a 300GHz second harmonic output in 45nm SOI CMOS. The geometry of the oscillator and the ground plane is such that the structure is radiative at the second harmonic. They mutually lock and spatially combine such distributed active radiators to improve the total radiated power. The total radiated power of a  $2 \times 1$  array is -19dBm, and that of a  $2 \times 2$  array is -10.9dBm. In [46], the same authors show a 282GHz  $4 \times 4$  beam-steering array of distributed active radiators in 45nm SOI CMOS with 80° electronic beam-scanning in each of the orthogonal axes in 2D space. A total power of -7.2dBm is radiated broadside with an EIRP of 9.4dBm while consuming around 800mW of DC power. A tuning range of 3.2% has been shown around 280GHz. Finally, the authors of [47] attempt to maximize  $f_{osc}$  by increasing the small-signal startup gain of a ring oscillator. They do so by maximizing the small-signal power added per stage. They have shown a 256GHz third harmonic oscillator with -17dBm output power in 130nm CMOS and a 482GHz third harmonic oscillator with -7.9dBm output power in 65nm CMOS. It should be noted that in these works, the output is at the center of the ring oscillator and the on chip routing losses of a practical implementation are not included. In [48], the authors show a VCO in a 65nm CMOS process with a fourth-harmonic output power of about -1.2 dBm at 292GHz. It has a tuning range of 4.5% around 290GHz using variable coupling between injection locked oscillators. In [49] the authors use a 90nm CMOS process and generate -6.5 dBm of power at 228GHz by extracting the third harmonic from a differential VCO in a Colpitts configuration. They show a tuning range of 7%. Finally, the authors of [50] have shown a doubler in 45nm SOI CMOS generating -3 to 0dBm of output power in the 170 - 195GHz range with a conversion gain between -2 to -1dB.

This brief overview suggests that while CMOS based oscillators and sources are now able to operate in the high mmWave/THz regime, additional research needs to be done to produce output frequencies and power comparable to compound semiconductor technologies. Our work introduces a topology that maximizes the frequency of oscillation achievable in a given technology through a ring oscillator configuration with appropriately-designed passive matching networks. There have been many works in the microwave community that lend significant insight into maximizing oscillation frequency and output power. The author in [51] discusses the existence of a specific voltage ratio between the drain and the gate terminal that maximizes the power gain from the gate to the drain, thus improving small-signal loop gain. Our work improves on this by standardizing the methodology of arriving at the passive network to achieve this gain. Our work also explicitly accounts for passive loss in a closed form fashion, and allows for any phase shift per stage for a multi-stage ring oscillator with arbitrary number of stages. This in turn allows power combining of different number of stages for larger output power. The authors in [52] similarly attempt to improve loop gain of a ring oscillator but maximize added power from the gate to the drain. Other works of interest that work on maximizing power gain across a ring oscillator include [53].

This chapter is organized as follows. Section 2.2 discusses the modeling of the IBM 45nm SOI CMOS active and passive devices. Section 2.3 deals with the MGRO concept. Section 2.4 discusses the design and optimization of networks that extract harmonic output power from the MGRO. It also discusses the possibility of spurious-mode oscillations which must be suppressed. Section 2.5 discusses the measurement setup and the performance of the fabricated chips. Section 2.6 concludes the chapter.

#### 2.2 45nm SOI CMOS Technology Characterization

#### 2.2.1 Active Devices

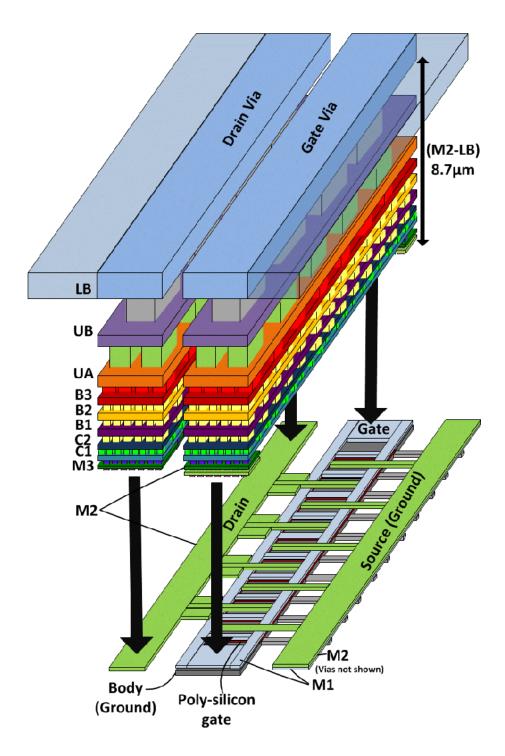

The IBM 45nm SOI CMOS technology offers floating-body (FB) devices with a channel length of 40nm and body-contacted (BC) devices with a channel length of 56nm. The BC devices are slower than their FB counterparts due to their longer channel length and the additional capacitive parasitics introduced by the body contact. We have measured a  $10 \times 1\mu\text{m}/56\text{nm}$  BC, a  $20 \times 1\mu\text{m}/56\text{nm}$  BC, and a  $10 \times 1\mu\text{m}/40\text{nm}$  FB device. The gate-over-device layout used in this work is shown in Fig. 2.1 for a BC device. For the FB device, the body-contact notches, [54], are absent. The thick via walls for the gate and the drain reduce wiring resistance. The layout allows a symmetric doubly contacted gate. The concern of capacitance between the gate and drain via walls is mitigated by placing them sufficiently far apart, while a possible increase in drain resistance is reduced by using the winged structures in  $M_2$  as shown. The fringing capactance from the wings to gate does not add to the gate-drain via capacitance.

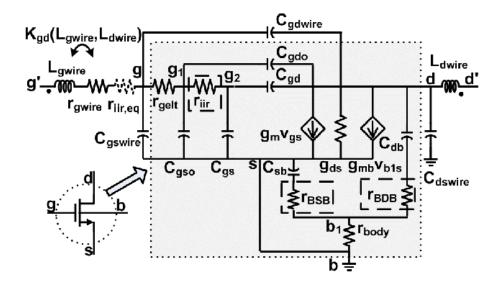

Fig. 2.2 shows a simplified BSIMSOI 4.x model (inside the dotted box [55]) to demonstrate some of the important components that model high-frequency effects. The components that are absent in the PDK model, namely the non-quasi static gate resistance  $r_{iir}$ , and  $r_{BDB}$  and  $r_{BSB}$  in the body resistance network, have been marked in dashed boxes. Wiring self-  $(L_{gwire}, L_{dwire})$  and mutual-  $(K_{gd})$  inductances, resistance  $(r_{gwire})$  and capacitances  $(C_{gswire}, C_{gdwire})$  are located outside the dotted box containing the BSIMSOI model, and are also not included in the PDK. The mutual inductance is primarily from the coupling between the drain and gate vias. Wiring parasitics are determined through parasitic extraction using the Calibre extraction tool and through EM simulations using the IE3D field solver [56].

Open-Short Deembedding, [57], was used to deembed the pad and feedlines from the device test structures that were measured. The sufficiency of Open-Short Deembedding up to 67GHz has been verified by EM simulations, which confirm that the pad and the feedline can be treated as lumped components at these frequencies. The deembedding is done up to a reference plane located at the top of the gate and drain vias. The measured Mason's Unilateral Gain (U) and  $h_{21}$  for the  $10 \times 1 \mu \text{m}/56 \text{nm}$  BC device at a current density  $J = 0.56 \text{mA}/\mu \text{m}$  is shown in Fig. 2.3(a). To determine  $f_{max}$  and cut-off frequency  $f_T$ , a 20dB per decade line is extrapolated from the measured

Figure 2.1: Layout of a BC NFET Device. This allows the gate to be doubly contacted in a symmetric fashion.

Figure 2.2: The model for the NFET BC device. In, the FB version, there is no 'b' node and  $r_{body}$  is absent. The FB node is ' $b_1$ '