### CO-SYNTHESIS OF HARDWARE AND SOFTWARE FOR DIGITAL EMBEDDED SYSTEMS

A DISSERTATION SUBMITTED TO THE DEPARIMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENIS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> By Rajesh Kumar Gupta December 10, 1993

© Copyright 1994 by Rajesh Kumar Gupta I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

> Giovanni De Micheli (Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Michael J. Flynn

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Krishna Saraswat

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Kunle Olukotun

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and in quality, as a dissertation for the degree of Doctor of Philosophy.

Dr. Martin Freeman, Philips Research Labs.

Approved for the University Committee on Graduate Studies:

Dean of Graduate Studies & Research

### Abstract

As the complexity of systems being subject to computer-aided synthesis and optimization techniques increases, so does the need to find ways to incorporate *predesigned* components into the final system implementation. In this context, a general-purpose microprocessor provides a sophisticated low-cost component that can be tailored to realize most system functions through appropriate software. This approach is particularly useful in the design of embedded systems that have a relatively simple target architecture, when compared to general-purpose computing systems such as workstations. In embedded systems the processor is used as a resource dedicated to implement specific functions. However, the design issues in embedded systems are complicated since most of these systems operate in a time-constrained environment. Recent advances in chip-level synthesis have made it possible to synthesize application-specific circuits under strict timing constraints. This dissertation formulates the problem of computer-aided design of embedded systems using both application-specific as well as general-purpose reprogrammable components under timing constraints.

Given a specification of system functionality and constraints in a hardware description language, we model the system as a set of bilogic flow graphs, and formulate the co-synthesis problem as a partitioning problem under constraints. Timing constraints are used to determine the parts of the system functionality that are delegated to applicationspecific hardware and the software that runs on the processor. The software component of such a 'mixed' system poses an interesting problem due to its interaction with concurrently operating hardware. We address this problem by generating software as a set of concurrent fixed-latency serialized operations called threads. The satisfaction of the imposed performance constraints is then ensured by exploiting concurrency between program threads, achieved by an inter-leaved execution on a single processor system.

This co-synthesis of hardware and software from behavioral specifications makes it possible to build time-constrained embedded systems by using off-the-shelf parts and application-specific circuitry. Due to the reduction in size of application-specific hardware needed compared to an all-hardware solution, the needed hardware component can be easily mapped to semicustom VLSI such as gate arrays, thus shortening the design time. In addition, the ability to perform a detailed analysis of timing performance provides an opportunity to improve the system definition by creating better prototypes. The algorithms and techniques described have been implemented in a framework called *Vulcan*, which is integrated with the Stanford Olympus Synthesis System and provides a path from chip-level synthesis to system-level synthesis.

## Dedication

This thesis is dedicated to a very special person in my life, my wife Anne Usha.

### Acknowledgements

My deepest gratitude is to Professor Giovanni De Micheli for giving me the opportunity to explore new grounds in the computer-aided design of electronic systems without getting lost in the process. His constant encouragement, support and guidance were key to bringing this project to a fruitful completion. I am grateful to him for the training to carry out productive and directed research and for his friendship.

I would like to thank my associate advisor, Professor Michael J. Flynn for devoting precious time to monitor the progress of this research, and in reading this dissertation. Professor Krishna Saraswat has been very generous with his time to serve as chairperson for both my oral defense and the reading committees. I have also benefited from discussions with Professor Kunle Olukotun, who served on the defense and reading committees.

My sincerest thanks to my mentor Dr. Martin Freeman of Philips Research, Palo Alto for his constant guidance and a diligent reading of this dissertation. Needless to say, that any remaining mistakes are my sole responsibility. I would like to thank Uzi Bar-Gadda and Joe Kostelec of Philips Research, and Prof. Rick Reis and Carmen Miraflor of the Center for Integrated Systems for the honor to have been supported by the Philips Fellowship for the years 1992 and 1993.

This research builds upon the prior work of many people. I would like to thank all the other people involved in the synthesis project at Stanford. Of particular mention are David Ku, Frederic Mailhot, and Thomas Truong for writing the Olympus Synthesis System upon which the project is based. Claudionor Coelho wrote the simulator and contributed in numerous ways to this research work.

Many thanks are due to past and present members of our research group at Stanford. I am thankful to my colleagues David Ku, Frederic Mailhot, Maurizio Damiani, Polly Siegel, Thomas Truong, Jerry Yang, David Filo and Claudionor Coelho for providing a supportive and productive environment during the course of my stay at Stanford. I would also like to take this opportunity to thank my friends outside our research group, Rohit Chandra and Kourosh Gharachorloo for many discussions and for providing the valuable 'non-CAD' feedback to this research. Many thanks are due to Ms. Lilian Betters for her valuable administrative support during the course of my stay at Stanford.

Many thanks to my colleague and one of the most critical examiners of this research, Dr. Mani Bhushan Srivastava of AT&T Bell Laboratories. I am greatly indebted to him for his ever sharp examination of the concepts and ideas presented in this dissertation. He has provided valuable and constructive feedback at every stage of this project that has enhanced the overall quality of the research work.

I would also like to thank Prof. Gaetano Borriello of University of Washington, Prof. Wayne Wolf of Princeton University and Prof. Daniel Gajski of University of California, Irvine for taking active interest in this research and providing a fertile environment to foster the growth of new ideas.

The time during which the ideas in this thesis were developed was an intense time for my family. It has all been made possible by the patience, love and support of my wife, Anne Usha, and the high spirits maintained by our son Anand. My regards to Atta and Mama for their family support and for giving me the most valuable companion in my life, my wife. Finally, my regards to my parents for their love and understanding, and to my brother Sanjay and sister Neena. They have all contributed in many ways to the person that I am today.

Financial support for this research was provided by a Fellowship provided by Philips and Center for Integrated Systems, and by NSF-ARPA under grant MIP 9115432.

## Contents

| Al | Abstract   |                                                 |      |  |

|----|------------|-------------------------------------------------|------|--|

| De | Dedication |                                                 |      |  |

| Ac | cknow      | ledgements                                      | viii |  |

| 1  | Intr       | oduction                                        | 1    |  |

|    | 1.1        | Design of Embedded Systems                      | 4    |  |

|    | 1.2        | Synthesis Solutions                             | 5    |  |

|    | 1.3        | Co-design and Co-synthesis                      | 7    |  |

|    | 1.4        | Motivations for Hardware-Software Co-synthesis  | 9    |  |

|    | 1.5        | Applications of Hardware-Software Co-synthesis  | 13   |  |

|    | 1.6        | The Opportunity of Co-synthesis                 | 14   |  |

|    | 1.7        | Architectures with Hardware-Software Components | 16   |  |

|    |            | 1.7.1 Target system architecture                | 17   |  |

|    | 1.8        | Scope and Contributions of Thesis               | 21   |  |

|    | 1.9        | Outline of the Dissertation                     | 22   |  |

| 2  | Rela       | ted Work                                        | 24   |  |

|    | 2.1        | CAD Systems for Hardware-Software Co-design     | 25   |  |

|    |            | 2.1.1 Ptolemy                                   | 26   |  |

|    |            | 2.1.2 CODES                                     | 28   |  |

|    |            | 2.1.3 Rapid prototyping using SIERRA            | 28   |  |

|    | 2.2        | CAD for Hardware-Software Co-synthesis          | 29   |  |

|   |      | 2.2.1             | COSYMA                                                       | 29  |

|---|------|-------------------|--------------------------------------------------------------|-----|

|   |      | 2.2.2             | Use of non-deterministic finite state machines for co-design | 30  |

|   |      | 2.2.3             | Co-synthesis from UNITY                                      | 33  |

|   |      | 2.2.4             | Interface co-synthesis                                       | 33  |

| 3 | Syst | em Mo             | deling                                                       | 35  |

|   | 3.1  | System            | n Specification using Procedural HDL                         | 36  |

|   | 3.2  | System            | n Model and its Representation                               | 41  |

|   | 3.3  | The Fl            | low Graph Model                                              | 43  |

|   |      | 3.3.1             | Representation and definitions                               | 43  |

|   |      | 3.3.2             | Hierarchy                                                    | 47  |

|   |      | 3.3.3             | Execution semantics                                          | 48  |

|   |      | 3.3.4             | Implementation attributes                                    | 50  |

|   | 3.4  | Interac           | ction Between System and its Environment                     | 59  |

|   |      | 3.4.1             | Ports and communication                                      | 59  |

|   |      | 3.4.2             | Non-determinism in flow graph models                         | 60  |

|   | 3.5  | $\mathcal{ND}, E$ | Execution Rate and Communication                             | 61  |

|   | 3.6  | Constr            | aints                                                        | 65  |

|   |      | 3.6.1             | Min/max delay constraints                                    | 66  |

|   |      | 3.6.2             | Execution rate constraints                                   | 67  |

|   |      | 3.6.3             | Specification of timing constraints                          | 69  |

|   | 3.7  | Summa             | ary                                                          | 69  |

| 4 | Con  | straint           | Analysis                                                     | 72  |

|   | 4.1  | Schedu            | uling of Operations                                          | 73  |

|   | 4.2  |                   | ninistic Analysis of Min/max Delay Constraints               | 79  |

|   | 4.3  | Detern            | ninistic Analysis of Execution Rate Constraints              | 81  |

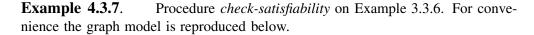

|   |      | 4.3.1             | Procedure                                                    | 96  |

|   | 4.4  | Min/m             | ax Constraints Across Graph Models                           | 99  |

|   | 4.5  |                   | Cycles in Constraint Graph                                   | 102 |

|   |      | 4.5.1             | Meaning of an $\mathcal{ND}$ cycle                           | 102 |

|   |      | 4.5.2             |                                                              | 105 |

|   |      |                   |                                                              |     |

|   |      | 4.5.3         | Use of buffers to extend bounds on loop index                |

|---|------|---------------|--------------------------------------------------------------|

|   | 4.6  | Probab        | bilistic Analysis of Min/max and Rate Constraints            |

|   |      | 4.6.1         | Meaning of constraint satisfiability                         |

|   |      | 4.6.2         | Index distribution and bounds on buffer depth                |

|   | 4.7  | Flow <b>(</b> | Graph as a Stochastic Process                                |

|   | 4.8  | Summ          | ary                                                          |

| 5 | Soft | ware ai       | nd Runtime Environment 126                                   |

|   | 5.1  | Proces        | sor Cost Model                                               |

|   | 5.2  | A Mo          | del for Software and Runtime System                          |

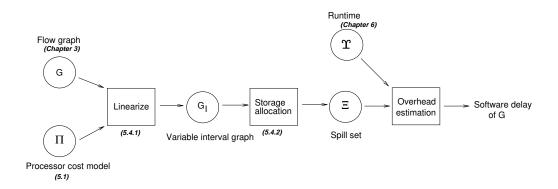

|   | 5.3  | Estima        | tion of Software Performance                                 |

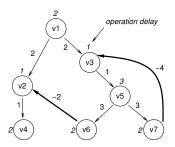

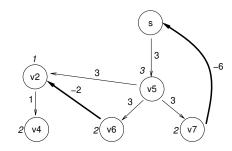

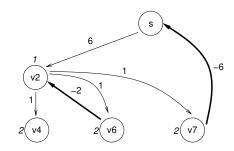

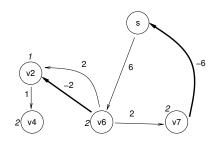

|   |      | 5.3.1         | Operation delay in a software implementation                 |

|   | 5.4  | Estima        | tion of Software Size                                        |

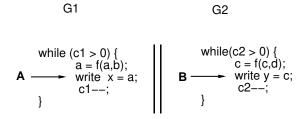

|   |      | 5.4.1         | Operation linearization                                      |

|   |      | 5.4.2         | Estimation of register, memory operations                    |

|   |      | 5.4.3         | Compiler effects                                             |

|   |      | 5.4.4         | Software data size and performance tradeoffs                 |

|   | 5.5  | Softwa        | are Synthesis                                                |

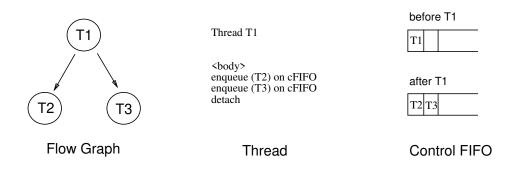

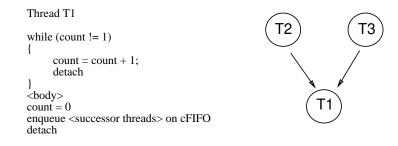

|   | 5.6  | Step I:       | Generation of Program Threads                                |

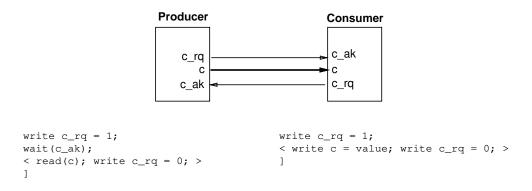

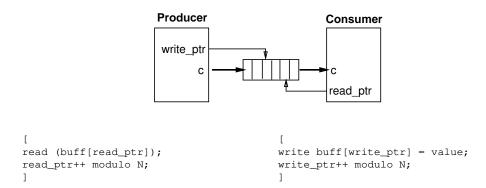

|   |      | 5.6.1         | Implementation of inter-thread buffers                       |

|   | 5.7  | Step II       | E: Generation of Program Routines                            |

|   |      | 5.7.1         | Concurrency in software through Interleaving: Coroutines 166 |

|   |      | 5.7.2         | Software implementation using description by cases 166       |

|   | 5.8  | Step II       | II: Code Synthesis                                           |

|   | 5.9  | Issue i       | n Code Synthesis from Program Routines                       |

|   |      | 5.9.1         | Memory allocation                                            |

|   |      | 5.9.2         | Data types                                                   |

|   |      | 5.9.3         | The C Standard Library                                       |

|   |      | 5.9.4         | Linking and loading compiled C-programs                      |

|   |      | 5.9.5         | Interface to assembly routines                               |

|   | 5.10 | Summ          | ary                                                          |

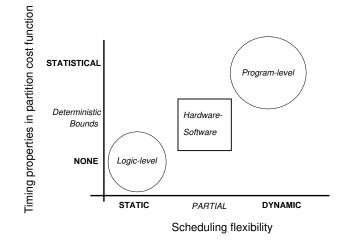

|   | 6.1  | Partition Cost Model                                                                      | 176 |

|---|------|-------------------------------------------------------------------------------------------|-----|

|   |      |                                                                                           | 1/0 |

|   | 6.2  | Local versus Global Properties                                                            | 181 |

|   | 6.3  | Partitioning Feasibility                                                                  | 183 |

|   |      | 6.3.1 Effect of runtime scheduler                                                         | 184 |

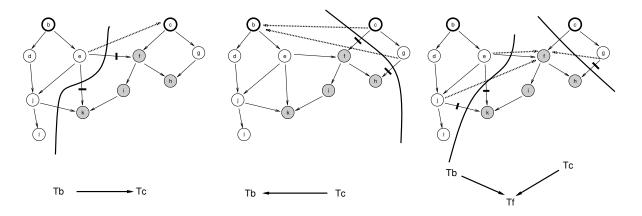

|   | 6.4  | Partitioning Based on Separation of Control and Execute Procedures                        | 188 |

|   | 6.5  | Partitioning Based on Division of $\mathcal{ND}$ Operations $\ldots \ldots \ldots \ldots$ | 189 |

|   | 6.6  | Partition Related Transformations                                                         | 193 |

|   | 6.7  | Summary                                                                                   | 194 |

| 7 | Syst | em Implementation                                                                         | 196 |

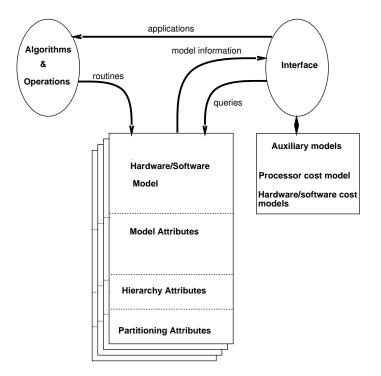

|   | 7.1  | Vulcan System Implementation                                                              | 196 |

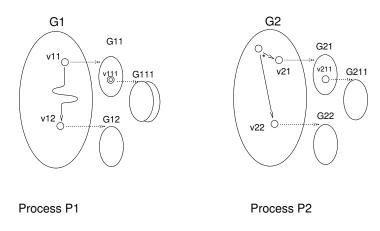

|   |      | 7.1.1 Data organization in Vulcan                                                         | 199 |

|   |      | 7.1.2 Command organization in Vulcan                                                      | 200 |

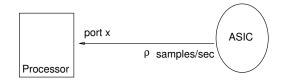

|   | 7.2  | Implementation of Target Architecture in Vulcan                                           | 203 |

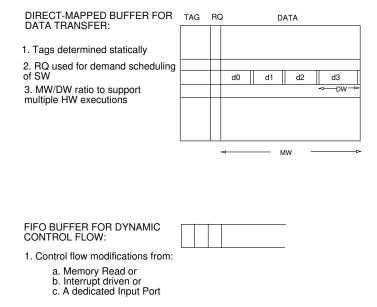

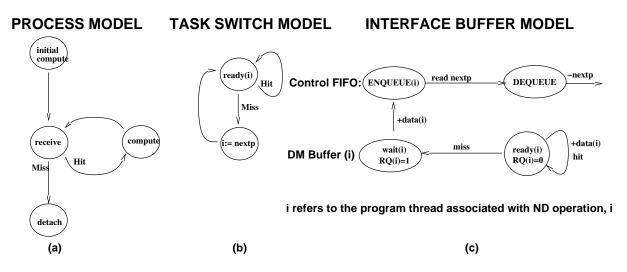

|   |      | 7.2.1 System synchronization                                                              | 203 |

|   |      | 7.2.2 Communication protocols                                                             | 207 |

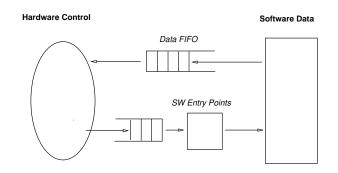

|   |      | 7.2.3 Hardware-software interface architecture                                            | 209 |

|   | 7.3  | Co-simulation Environment.                                                                | 211 |

|   | 7.4  | Summary                                                                                   | 217 |

| 8 | Exa  | amples and Results 21                                                                     |     |

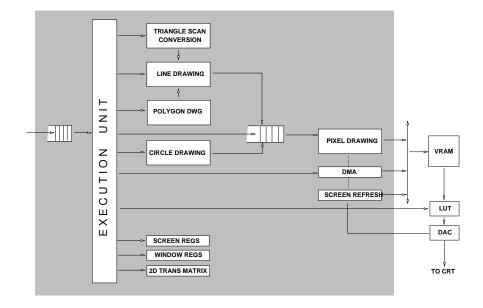

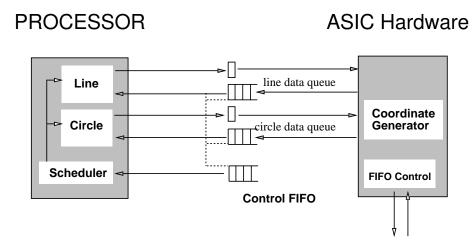

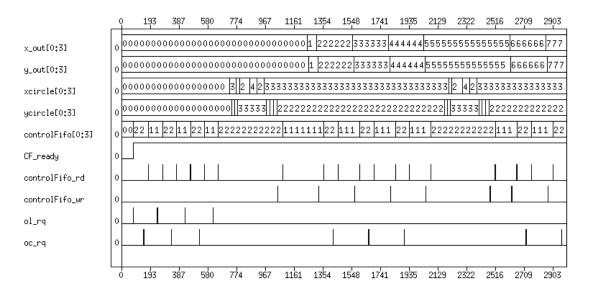

|   | 8.1  | Graphics Controller                                                                       | 219 |

|   |      | 8.1.1 Implementation                                                                      | 219 |

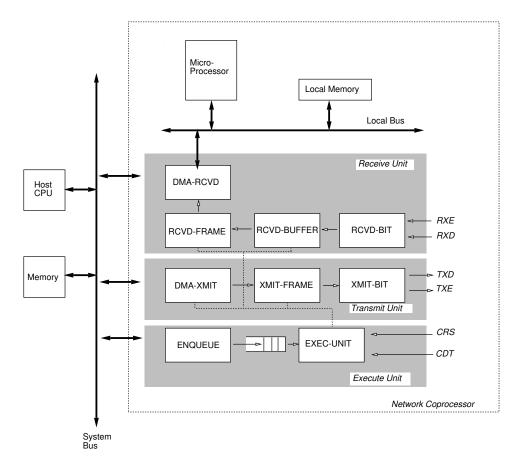

|   | 8.2  | Network Controller                                                                        | 225 |

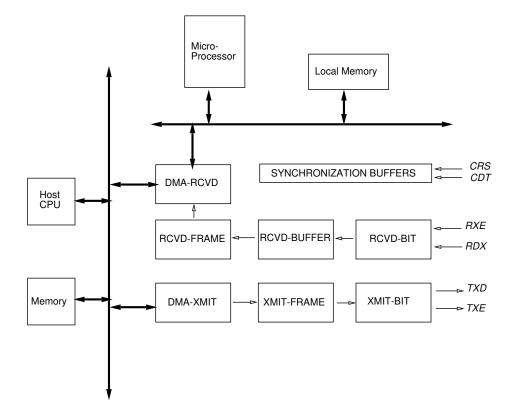

|   |      | 8.2.1 Host CPU-controller interface                                                       | 225 |

|   |      | 8.2.2 Controller operation                                                                | 225 |

|   |      | 8.2.3 Controller architecture                                                             | 227 |

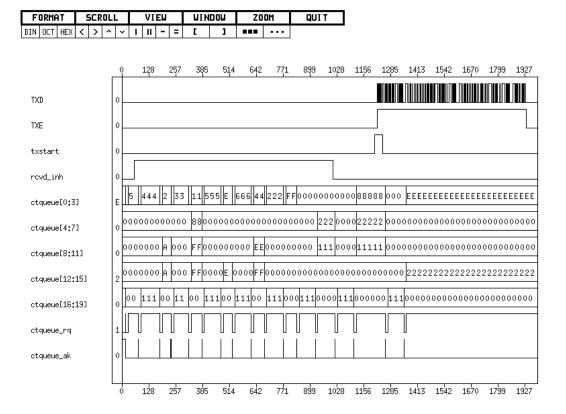

|   |      | 8.2.4 Network controller implementation results                                           | 228 |

| 9 | Sum  | mary, Conclusions and Future Work                                                         | 232 |

|   | 9.1  | Future Work                                                                               | 234 |

| Bibliography |                                      | 237 |

|--------------|--------------------------------------|-----|

| A            | A Note on HardwareC                  | 249 |

| B            | Bilogic Graphs                       | 251 |

| С            | Processor Characterization in Vulcan | 254 |

| D            | Runtime Scheduler Routines           | 256 |

| E            | Index of Notations                   | 259 |

## List of Tables

| 1  | Operation vertices in a flow graph                           |

|----|--------------------------------------------------------------|

| 2  | Link vertices in a hierarchical flow graph                   |

| 3  | Basic instruction set                                        |

| 4  | Addressing modes                                             |

| 5  | Variable types and storage                                   |

| 6  | Comparison of program thread implementation schemes          |

| 7  | Vulcan (Rev 0) subsystems and commands                       |

| 8  | A comparison of control FIFO implementation schemes          |

| 9  | Graphics controller implementations                          |

| 10 | Network controller instruction set                           |

| 11 | Network controller synthesis results using LSI library gates |

| 12 | Network controller synthesis results using Actel gates       |

| 13 | Network controller software component                        |

# **List of Figures**

| 1  | A design-oriented approach to system implementation.                    | 5  |

|----|-------------------------------------------------------------------------|----|

| 2  | A synthesis-oriented approach to system implementation                  | 7  |

| 3  | Proposed approach to system implementation.                             | 8  |

| 4  | Synthesis approach to embedded systems                                  | 9  |

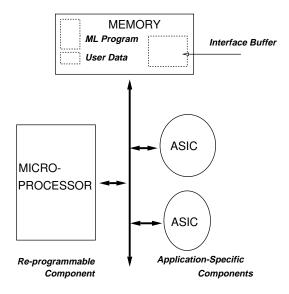

| 5  | Example of a mixed system implementation                                | 10 |

| 6  | DES Procedure                                                           | 11 |

| 7  | Bit permutations in DES Key Encryption                                  | 12 |

| 8  | System Classification Based on HW/SW Components                         | 17 |

| 9  | Target System Architecture                                              | 18 |

| 10 | Single chip realization of the target architecture                      | 20 |

| 11 | System Synthesis Procedure                                              | 23 |

| 12 | Objects in PTOLEMY                                                      | 7  |

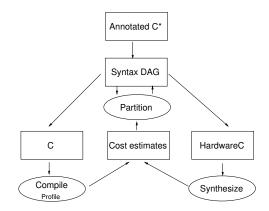

| 13 | Codesign flow in COSYMA                                                 | 30 |

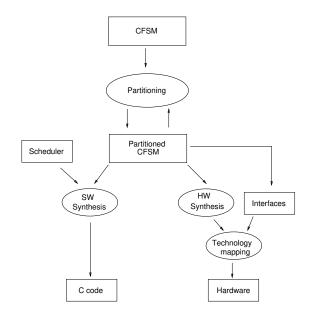

| 14 | Co-design from Finite State Machines                                    | 32 |

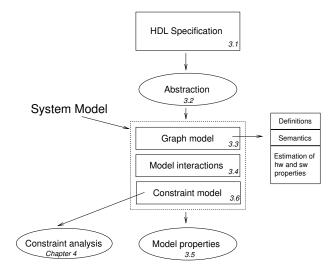

| 15 | Organization of Chapter 3                                               | 37 |

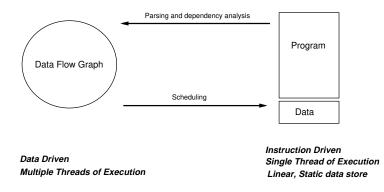

| 16 | Linear code versus data-flow graph representations                      | 38 |

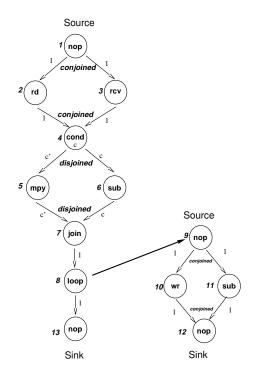

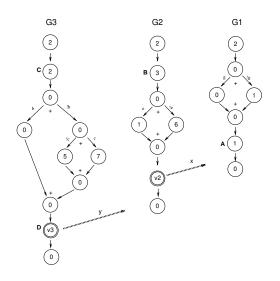

| 17 | Flow graph of process example                                           | 46 |

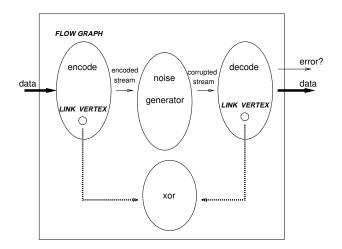

| 18 | Flow graph model for an error correction system.                        | 48 |

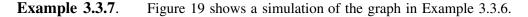

| 19 | Simulation of the graph model in Example 3.3.6                          | 57 |

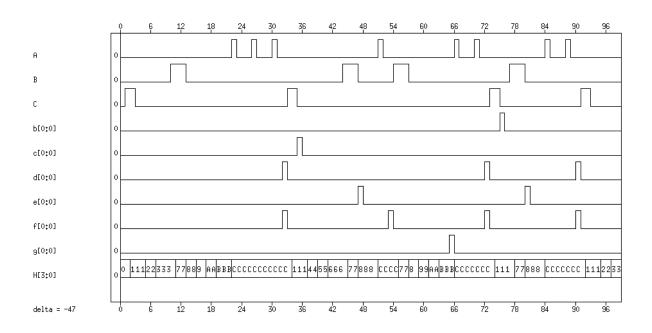

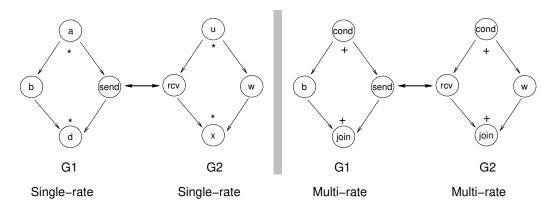

| 20 | Shared memory versus message passing communication                      | 59 |

| 21 | Graph model properties                                                  | 63 |

| 22 | Communication across models.                                            | 63 |

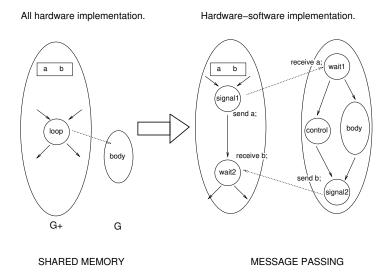

| 23 | Shared-memory versus message-passing implementations of loop operation. | 64 |

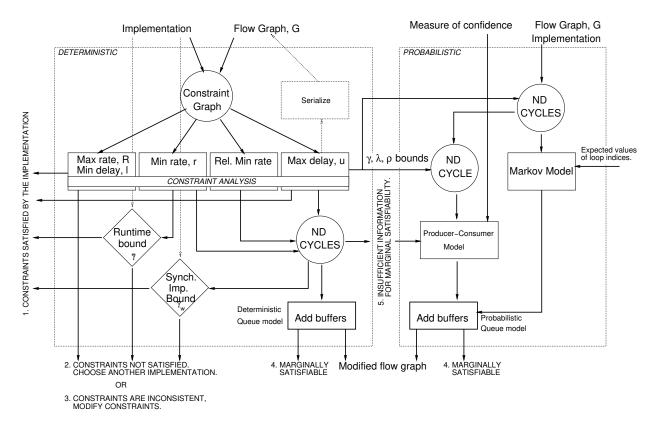

| 24 | General flow of constraint analysis                                                                                                                                                    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

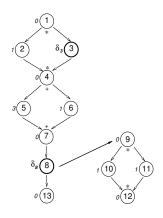

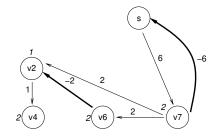

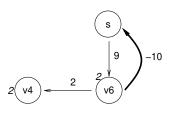

| 25 | Constraint Graph Model                                                                                                                                                                 |

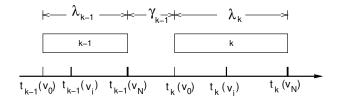

| 26 | Operation invocation interval                                                                                                                                                          |

| 27 | Consecutive executions of an operation corresponds to traversal of a path                                                                                                              |

|    | <i>in G</i>                                                                                                                                                                            |

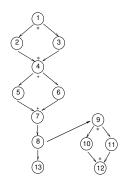

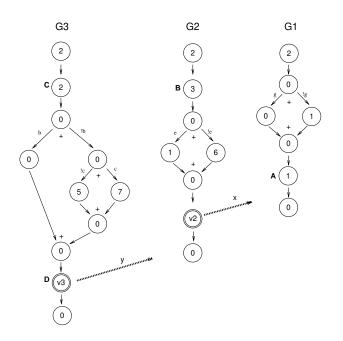

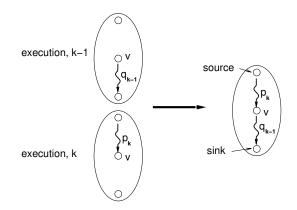

| 28 | Upward propagation of minimum execution rate                                                                                                                                           |

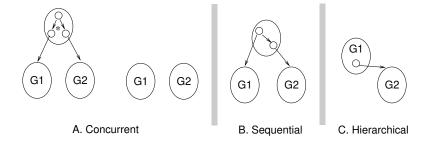

| 29 | Relationships between flow graphs                                                                                                                                                      |

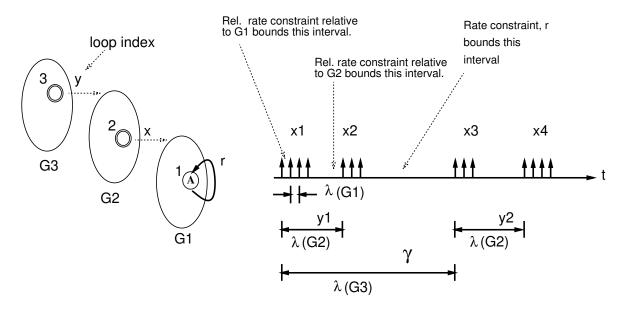

| 30 | Graph model hierarchy                                                                                                                                                                  |

| 31 | An $\mathcal{ND}$ cycle in the constraint graph $\ldots \ldots \ldots$ |

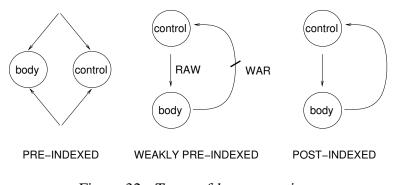

| 32 | Types of loop operations                                                                                                                                                               |

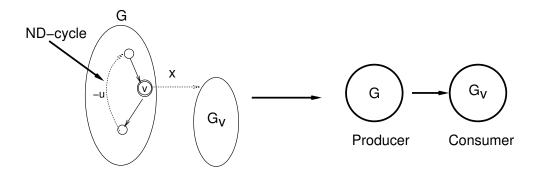

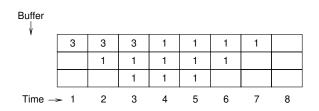

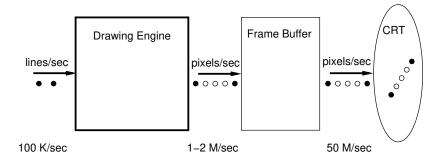

| 33 | Modeling an $\mathcal{ND}$ loop as a producer-consumer system                                                                                                                          |

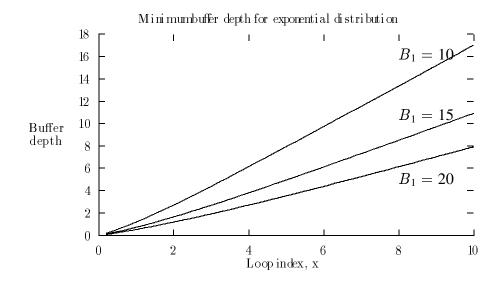

| 34 | Buffer depth for exponential distributions ( $\epsilon = 0.01\%$ )                                                                                                                     |

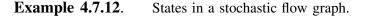

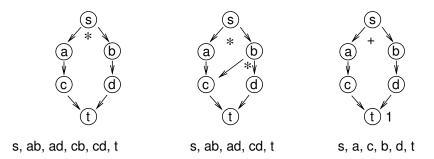

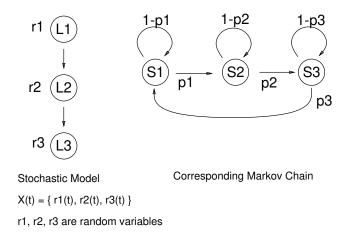

| 35 | States of stochastic flow graphs                                                                                                                                                       |

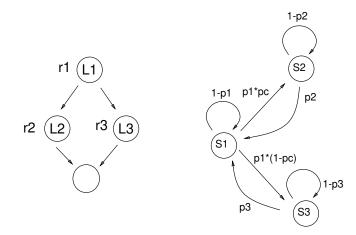

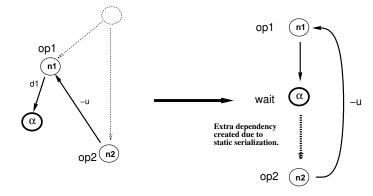

| 36 | Loops in a serialized model                                                                                                                                                            |

| 37 | Loops in a fork                                                                                                                                                                        |

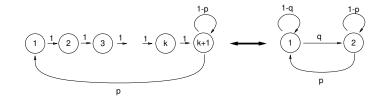

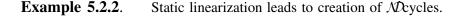

| 38 | Software model to avoid creation of $\mathcal{ND}$ cycles                                                                                                                              |

| 39 | Software delay estimation flow                                                                                                                                                         |

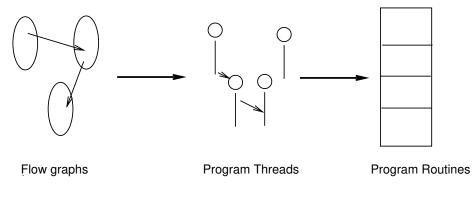

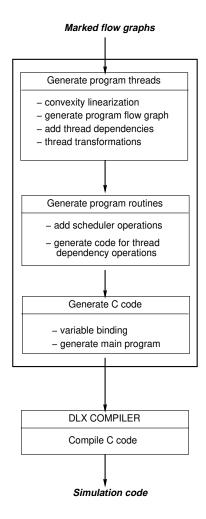

| 40 | Steps in generation of the software component                                                                                                                                          |

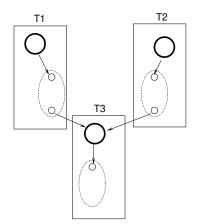

| 41 | Use of enabling condition to build inter-thread dependencies                                                                                                                           |

| 42 | Convexity serializations and possible thread implementations                                                                                                                           |

| 43 | Generating fixed addresses from C-programs                                                                                                                                             |

| 44 | Components of the partition cost model                                                                                                                                                 |

| 45 | Use of timing properties in partition cost function                                                                                                                                    |

| 46 | Partitioning into Hardware Control and Software Execute Processes 189                                                                                                                  |

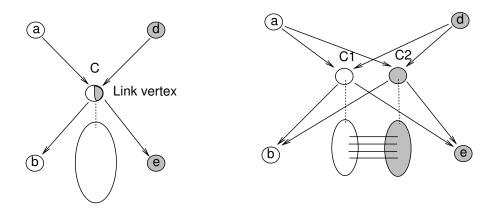

| 47 | Partition of link vertices                                                                                                                                                             |

| 48 | Co-synthesis flow                                                                                                                                                                      |

| 49 | Data Organization in VULCAN                                                                                                                                                            |

| 50 | Vulcan subsystems and the Olympus Synthesis System                                                                                                                                     |

| 51 | Flow of software synthesis in Vulcan                                                                                                                                                   |

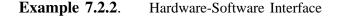

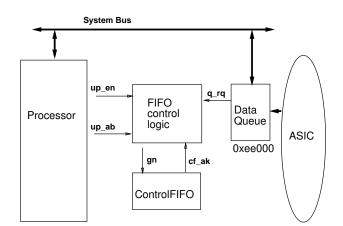

| 52 | Control FIFO schematic                                                                                                                                                                 |

| 53 | FIFO control state transition diagram                                                                                                                                                  |

| 54 | Hardware and Software Interface Architecture                           |

|----|------------------------------------------------------------------------|

| 55 | Hardware and Software Interface Model                                  |

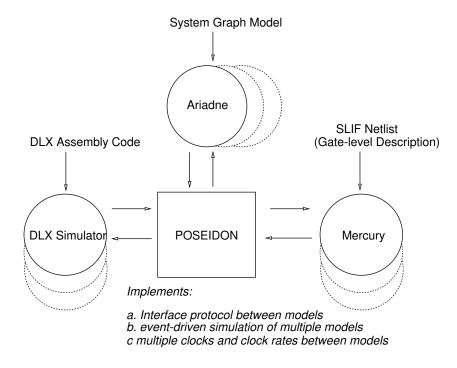

| 56 | Event-driven Simulation of a Mixed System Implementation               |

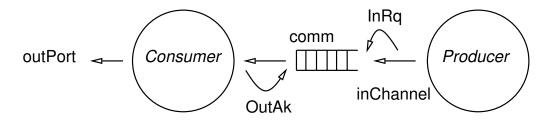

| 57 | Producer consumer system                                               |

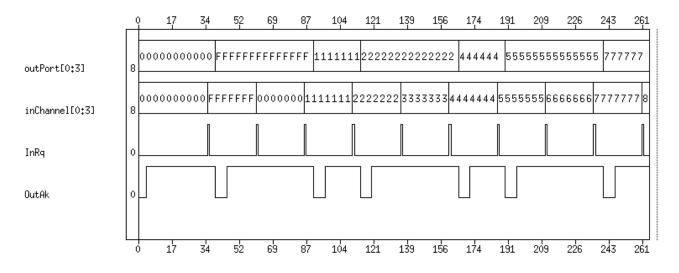

| 58 | Example simulation: software producer, hardware consumer               |

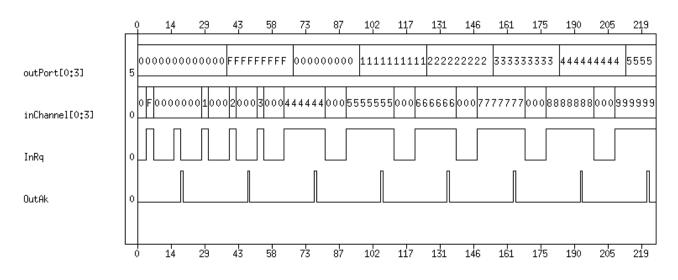

| 59 | Example simulation: software consumer, hardware producer               |

| 60 | Graphics controller block diagram                                      |

| 61 | Graphics controller implementation                                     |

| 62 | Graphics controller software component using hardware control FIFO 221 |

| 63 | Graphics controller software component using software control FIFO 222 |

| 64 | Graphics controller simulation                                         |

| 65 | Network controller block diagram                                       |

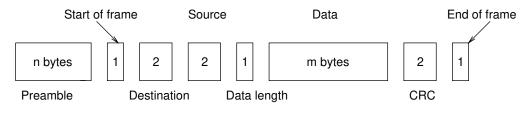

| 66 | Format of an ethernet frame                                            |

| 67 | Network controller implementation                                      |

| 68 | Network controller simulation                                          |

## Chapter 1

### Introduction

Recent years have seen remarkable growth in the design and use of digital systems in several application areas. Digital systems are designed for two major *classes* of applications: *general-purpose* and *application-specific* systems. General-purpose systems are not designed for any specific applications but can be *programmed* to run different applications. The most common use of general-purpose systems is in computing applications. Examples of these systems are computers such as workstations.

In contrast, *application-specific* systems are designed for dedicated applications. Examples of such systems can be found in medical instrumentation, process control, automated vehicles control, and networking and communication systems. As these systems are contained within a larger non-electronic environment, these are commonly referred to as **embedded systems**. Embedded computer systems have been applied to tasks erst-while handled by electronic or electro-mechanical *non-computing* systems. As a result, the volume of embedded electronics market has grown. For the year 1991, the industrial and medical electronics market alone accounted for \$31 billion compared to the general purpose computing systems market of \$46.5 billion [JJ93].

This growth has been fueled by the advent of microprocessors, the primary compute element in a system. Microcontrollers, a derivative of microprocessors, are now beginning to be used in many embedded systems. For the year 1991, the market for microcontrollers amounted to \$4.6 billion and has been rising at a 18% annual growth rate compared to a 10% annual growth rate of general-purpose systems [JJ93].

While there has been notable growth in the use and application of embedded systems, improvements in the design process for such systems have not kept pace, leading to a gap in the evolution of component technology and its application in embedded computing systems. While new processors and programmable/reprogrammable integrated circuits are announced every six months with an average performance boost of 50% per year, it may be several years before such components find use in embedded computer systems. This is in contrast to the design of general-purpose computing systems that have largely kept pace with advances in component technology related to processors, memory or integrated circuits. Currently, approximately 80% of the microcontrollers used in embedded systems are 4- and 8-bit processors of old generations [Bad93]. Of the total \$4.6 billion microcontroller market for 1991, 32-bit processors account for less than 4% or \$184 million, despite the fact that such processors have been commonplace since 1985 and almost all advances in processor.

Examining the cost analysis for semiconductor manufacturing, including package and testing, the total chip cost for a die size of 1x1 sq. cm. comes to an average of \$27 versus \$7 for a 0.25x0.25 sq. cm. die [HP90]. Thus, chip manufacturing cost is not always the dominant factor in overall chip pricing. Historically, it has been observed that the prices of single-chip processors stabilize to a certain level in the \$10-50 range regardless of the introduction price of the processor. This drop in price is more strongly related to the advancements on the technology learning and yield curves than to market dynamics. Typically this price stabilization occurs within two years of the introduction of a processor.

There are several reasons for this discrepancy in the advancement of embedded versus general-purpose systems. More often, the embedded system is not the most visible part of the application and, therefore, its implementation inefficiencies are often overlooked. Component prices and manufacturing/maintenance cost of such systems is often cited as reasons for relatively slow proliferation of advanced components in such systems. However, as explained, the cost/price stabilization for processors occurs much sooner than their proliferation in the embedded systems. Further, instead of using multiple 4-, 8- or 16-bit processors, the trend in embedded system design is to use 32-bit processors

*despite* increased system costs. The use of 32-bit controllers in embedded applications, though a tiny 4% of the total volume, is increasing at an annual rate of 52% as against the overall growth of 18% for the overall embedded controller market [JJ93].

In summary, even though there is a greatly recognized need for the use of advanced 32-bit processors in embedded applications, their proliferation in terms of total volume has been lagging behind the growth in the 32-bit processor market. Further, the price stabilization for these advanced processors occurs much earlier than their bulk use in embedded systems. Thus, the proliferation of advanced 32-bit processors in embedded systems does not appear to be limited by component cost considerations alone.

The chief reason for the slow proliferation of advanced components into embedded systems is **the long design time and high cost of design** of such systems. Since embedded systems are tailored to specific applications, the design cost per unit volume is higher for embedded systems. Therefore, such systems stand to gain most from advances in the design process that shortens the design time and improves performances by leveraging the use of newer and advanced components. Based on this hypothesis, this thesis examines the problems in system design and provides solutions to speed up the design process by developing *synthesis* techniques. The difference in design and synthesis techniques is discussed a little later in this chapter. But first we briefly examine some of the commonly used terms associated with the design of computer systems.

An electronic system consists of a set of *interacting* components. A digital electronic system implements its primary functions using components that react to and produce discrete objects. A component of a system may be a system in itself. At the lowest-level (leaf-level) components tend to be more functionally homogeneous than the systems that use these components. For example, a digital computer system consists of software, processor, memory and peripheral input/output components. For this reason, systems are often called *heterogenous systems*.

A component functionality is classified as either a *computation* or *communication*. As the terms suggest, a communication functionality relates to operations involving input and output operations, with the rest being computations. Both computation and communication functionalities can be implemented in a *synchronous* or an *asynchronous* manner. Synchronous communication refers to a *constant phase-relationship* between two or more input and/or output operations. Asynchronous communication, on the other hand, refers to input/output operations that have no or variable phase-relationships. A synchronous implementation uses a *global* mechanism such as a clock, whereas asynchronous computations are characterized by the absence of such *global synchronization* mechanisms.

This thesis is targeted at exploring the implementation of embedded digital systems with synchronous computation and communication components that are targeted for specific applications. In addition to being application-specific, such systems are also designed to respect constraints related to the relative timing of their actions, hence these systems are referred to as *real-time embedded systems*. The application-specific nature of these systems often requires custom hardware circuits and programs to run on a general-purpose processor hardware. This personalization is commonly referred to as programmability in **hardware** and **software** respectively. Since the components that can be *reprogrammed* to suit applications or changes and upgrades in an application.

#### **1.1 Design of Embedded Systems**

While there have been tremendous advancements in the design of the general purpose components of an embedded system, the design of the hardware and software components to achieve its programmability has not changed much over the years. Software programmability is achieved by manually writing software often in processor assembly language. Similarly, hardware programmability is achieved by manual design using gate-level circuits or low to medium-scale integration circuits.

There are several challenges in the design and the analysis of time-constrained embedded systems that prolong the design process. Important among these are the problems of performance estimation, selection of appropriate components and verification of such systems for functional and temporal properties. In practice, such systems are created using a **design-oriented** approach. The system is specified by a collection of its functionalities which are then implemented by a choice of appropriate components.

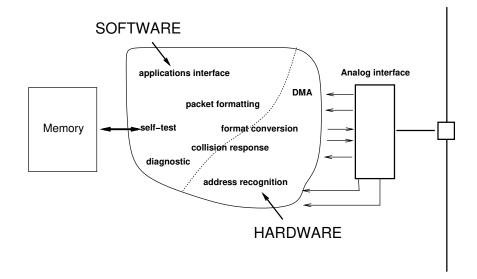

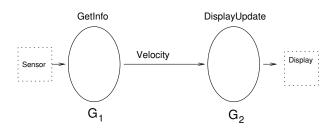

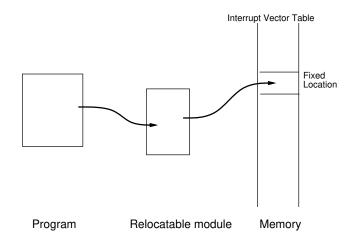

For instance, consider the design of a network controller shown in Figure 1. The controller is connected to a serial line and a memory. The purpose of the controller is to

Figure 1: A design-oriented approach to system implementation.

receive and send data over the serial line using a specific communication protocol (such as CS/CD protocol for ethernet links). The decision to map functionalities into dedicated hardware or implement them as programs on a processor is usually based on estimates of achievable performance and implementation cost of the respective parts.

There are several limitations to this approach. The division of functionality between components is based on the designer's experience and takes place early on in the design process. This often leads to portions of the design that are either under- or over-designed with respect to their required performance. More importantly, due to the ad-hoc nature of the overall design process, there is no guarantee that a given implementation meets the required system performance (except possibly by overdesigning).

#### **1.2** Synthesis Solutions

In contrast to design-oriented solutions, a methodical approach to system implementation can be formulated as a **synthesis-oriented** solution which has been enormously successful in the design of individual integrated circuit chips (*chip-level* synthesis). Instead of using a specification as a set of loosely-defined functionalities, a synthesis approach for hardware proceeds with systems described at the *behavioral level* by means of an

appropriate specification language. While the choice of finding a suitable specification language for digital systems is a subject of on-going research, the use of procedural *hardware description languages* (HDLs) to describe integrated circuits has been gaining wide acceptance in recent years.

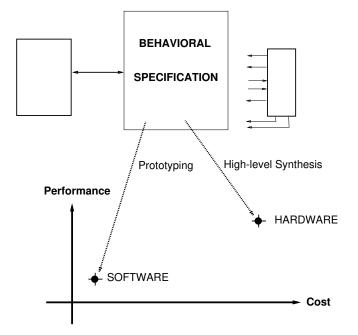

A synthesis-oriented approach to digital circuit design takes a behavioral description of circuit functionality and attempts to generate a gate-level implementation that can be characterized as a purely hardware implementation (Figure 2). Recent strides in high-level synthesis have made it possible to synthesize digital circuits from high-level specifications and several such systems are available from industry and academia [BCM<sup>+</sup>88, CR89, RMV<sup>+</sup>88, CPTR89, TLW<sup>+</sup>90, MKMT90, WTH<sup>+</sup>92]. The outcome of synthesis is a gate-level or geometric-level description that is implemented as a single chip or multiple chips.

An alternative to hardware synthesis of system prototypes would be to build a *software prototype* of the system functionality. Such implementations lie on the opposite end of the cost-performance spectrum (Figure 2). Here cost refers to system development cost and performance is the time-related performance of the prototype. A software prototype consists of a completely software specification based on a programming language that is sometimes enhanced to support the structural interconnection of language objects [BL90a, BL90b]. An example of a software prototyping system is the RAPI DE prototyping system [LVBA93]. Software prototypes are rather quick to build and are often used for verifying system functionality. Because the prototypes are primarily targeted for simulations, there is a limit to the resolution of time-scale of events that can be used. Therefore, the timing performance of software prototypes often falls short of what is desired for time-constrained system designs.

In summary, there are several limitations of existing synthesis-oriented solutions to system implementation. For synthesized hardware solutions, as the number of gates (or logic cells) increases, such implementations require the use of semi-custom or custom design technologies with their associated increases in cost and design turn-around time. Therefore, for large system designs, synthesized hardware solutions tend to be fairly expensive depending upon the choice of technology required for chip implementation. As mentioned earlier, software solutions on the other hand, often fail to meet constraints

Figure 2: A synthesis-oriented approach to system implementation.

on timing performance.

#### 1.3 Co-design and Co-synthesis

Synthesis-oriented approaches to system implementation provide systematic and rapid evaluation of implementation alternatives. System cost and performance tradeoffs dictate a choice between synthesized hardware solutions or software prototypes. But we do know from our practical experience that cost-effective designs use a mixture of hardware and software to accomplish their overall goals (Figure 1).

This provides sufficient motivation for attempting a system implementation that contains both hardware and software components. This is commonly referred to as the process of **hardware-software co-design** where both components are designed together. The input specification in co-design may consist of a single or a collection of *heterogenous* specifications.

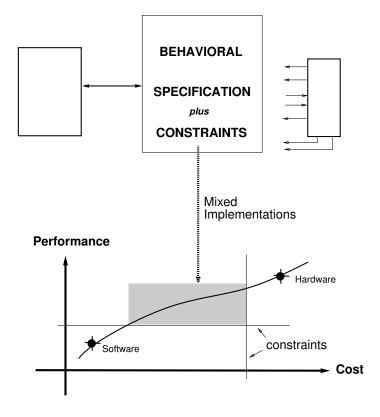

A further development in this direction would be a **co-synthesis** approach that attempts to provide mixed hardware-software implementations using synthesis techniques. Such

Figure 3: Proposed approach to system implementation.

an approach would benefit from a systematic analysis of design trade-offs that is common in synthesis, while at the same time creating systems that are cost-effective. One way to accomplish this task would be to specify constraints on the cost and the performance of the resulting implementation (Figure 3).

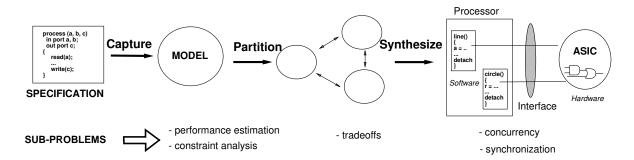

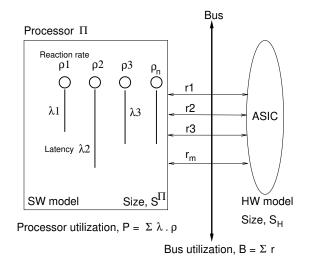

This thesis presents a synthesis approach to systematic exploration of system designs that is driven by the constraints. This work is built upon high-level synthesis techniques for digital hardware [MKMT90] by extending the concept of a resource needed for implementation. Figure 4 shows the essential aspects of this approach. A behavioral specification is captured into a system model that is partitioned for implementation into hardware and software. The partitioned model is then synthesized into interacting hardware and software components for the target architecture shown in Figure 9. The target architecture uses one processor and application-specific hardware. The target architecture is described in further detail in Section 1.7.1.

Figure 4: Synthesis approach to embedded systems.

#### **1.4 Motivations for Hardware-Software Co-synthesis**

Most digital functions can be implemented by software programs. The major reason for building dedicated application-specific hardware (ASICs) is the satisfaction of performance constraints. These performance constraints can be on the overall time (latency) to perform a given task, or more specifically on the timing to perform a subtask and/or on the ability to sustain specified input/output data rates over multiple executions of the system model. The hardware performance depends on the results of operation scheduling and on the performance characteristics of individual hardware resources. The software performance, defined as the number of cycles that it takes the processor to execute a routine, depends on the number of instructions the processor must execute and the cyclesper-instruction (CPI) metric of the processor. In general, application-specific hardware implementations tend to be faster since the underlying hardware is optimized for the specific set of tasks. However, in the absence of stringent performance constraints, for a given behavioral description of an ASIC machine, some parts (subroutines) of it may be well suited to a commonly available re-programmable processor (e.g., 6502, 68HC11, 8051, 8096 etc) while others may take too long to execute. For instance, most general purpose CPUs deal with byte-size operands whereas many ASIC controllers contain bit-oriented operations resulting in unnecessary overheads when the operations are implemented entirely in software. However, the software implementations do provide the ease and flexibility of reprogramming for the possible price of loss of performance.

**Example 1.4.1**. Data encryption controller.

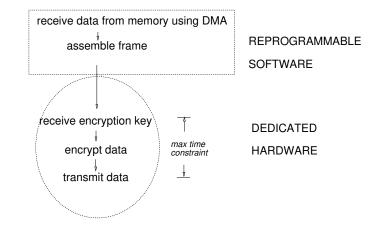

Figure 5: Example of a mixed system implementation

To be specific, consider the design of a data encryption/protocol controller chip, based on the DES (Data Encryption Standard) protocol used by commercial banks or the AES (Audio Engineering Society) protocol used for communication between digital audio devices and computers. In Figure 5, the DES transmitter takes data from memory using a DMA controller, assembles the frame for transmission, encrypts the data after it receives the key and transmits the encrypted data. The encryption protocol requires that the encrypted data be transmitted within a certain time duration of receiving the encryption key.

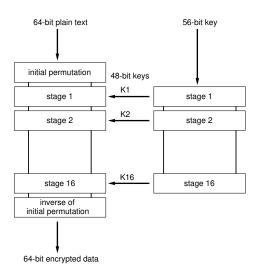

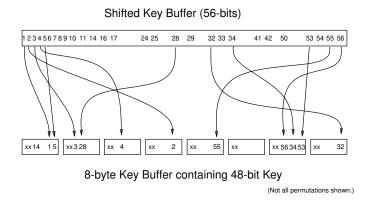

In the DES protocol, a 64-bit encryption key is used to transform 64 bits of 'plaintext' into 64 bits of encrypted text. Here we present only the relevant aspects of the encryption process. For details on the standard and algorithms the reader is referred to [oS88] [SB88]. The encryption key contains 8 parity bits which are removed before the encryption process thus deriving a 56-bit encryption key. As shown in Figure 6, the entire encryption process consists of 18 permutation stages including an initial and a final stage which do not require any key. The 16 intermediate steps are key-controlled. The first and last stages are simple permutations. The 16 48-bit keys required for intermediate stages are derived from the original 56-bit key. Thus there are two separate 16-stage operations: a) generation of the 48-bit encryption key, and b) use of encryption key to manipulate 64-bit data. Here we consider the first operation, that is the generation of the encryption key, though a similar argument can also be made for the data manipulation operations which consists of rotation, permutations, xor and table lookup.

The encryption key algorithm transforms the 56-bit input key buffer (known as shifted key buffer, SKB) into a 48-bit key which is organized as an 8-byte key buffer (KB) such that only 6 bits from each byte of the KB are used in the key.

Figure 6: DES Procedure

Thus each stage of the 16-stage key generation algorithm consists of 48 permutation operations on the shifted key buffer as illustrated by the algorithm below:

```

clear 64-bit key buffer

for i = 1 .. 48 do {

isolate bit i of the shifted keyed buffer

if (bit == 1)

set key buffer bit pc2(i) using permuted choice table, pc2

}

```

Software implementations of this encryption key algorithm vary from 300 to 3000 instructions depending on the level of bit-oriented operations supported. This is in sharp contrast to the hardware implementation in which each stage can be accomplished in a single cycle by building the permutation into an interconnection network as shown in Figure 7. Therefore, a hardware implementation of the algorithm would require 16 cycles.  $\Box$

Thus, hardware and software implementations vary widely in speed. For designs that are dominated by bit-oriented operations, dedicated hardware implementations are preferred, whereas it may take too long to execute these operations as a sequence of instructions on most processors, thus violating the constraints on timing performance of the controller. Whereas implementing the complete protocol controller on dedicated hardware may be too expensive, an implementation which uses a re-programmable component may satisfy performance requirements and at the same time provide the ease and flexibility of programming in software.

Figure 7: Bit permutations in DES Key Encryption

While bit-wise shifting and xor operations lead to slower software implementations, the implementation of byte-oriented data-intensive operations with the use of structured memory is considerably faster. Such implementations are often competitive with corresponding hardware implementations. Consider the following example.

**Example 1.4.2**. Cyclic redundancy code computation.

Consider a 16-bit CRC-CCITT computation using the polynomial  $x^{16} + x^{12} + x^5 + 1$ . With the addition of every byte of data, the new CRC is clearly a function of 8-bits of the old CRC and the new byte of data. This function is precomputed and stored in a 256-entry table. A byte-wise implementation using two 256-byte tables, as described by the following pseudo-code, when coded in assembly can achieve the 16-bit CRC computation in 7 instructions per byte.

> typedef byte char; byte Table\_low[256], Table\_high[256]; byte Temp, data, CRC\_low, CRC\_high; Temp = data xor CRC\_low; CRC\_low = Table\_low[Temp] xor CRC\_high; CRC\_high = Table\_high[Temp];

The actual latency of computation is strongly dependent on the instruction-set architecture (ISA) of the target processor. The best implementation of the above pseudo-code on an Intel 8086 processor computes 16-bit CRCs in 9 instructions, a Motorola 68K implementation in 11 instructions and a RISC-based implementation in 14 instructions.

In contrast to a table-driven software implementation, a hardware implementation of the CRC typically consists of a 16-bit shift register with xor taps at locations

dictated by the polynomial (i.e., positions 0, 5 and 12). Then the incoming bit stream is shifted from the right into the shift register by left shifting the register. Any time a 1 bit gets shifted off the left end of this register, the register contents are replaced by an xor with the polynomial (equivalent to a modulo-2 subtraction operation). This implementation results in a CRC computation rate of 8 cycles/byte.  $\Box$

#### **1.5** Applications of Hardware-Software Co-synthesis

The hardware-software co-synthesis techniques formulated in this thesis can be used for following applications.

- 1. **Design of cost-effective systems:** The overall *cost* of a system implementation can be reduced by the ability to use already available general purpose re-programmable components while reducing the number of application-specific components.

- 2. Rapid prototyping of complex system designs: A complete hardware prototype of a complex system is often too big to be implemented using field programmable gate-array (FPGA) technologies. For such systems a mask programmable or even a custom hardware realization is required. With the identification of the time critical hardware section, the total amount of hardware to be synthesized may be reduced significantly, thus making it feasible for rapid prototyping. A feasible partition that shifts the non performance-critical tasks to software programs can be used to quickly evaluate the design.

- 3. **Speedup of hardware emulation software:** During their development phase, many system designs are often modeled and emulated in software for test and debugging purposes. Such an emulation can be assisted by dedicated hardware components which provide a speedup on the emulation time.

Rapid prototyping and hardware emulation are two opposite ends of the system synthesis objective. Rapid prototyping attempts to minimize the application-specific component to reduce design time, whereas hardware emulation attempts to maximize the application-specific component to realize maximum speed-up.

#### **1.6 The Opportunity of Co-synthesis**

This thesis explores the opportunity of achieving hardware-software co-synthesis by formulating it as a problem of system partitioning into application-specific and reprogrammable components. We can also view it as an extension of high-level synthesis techniques to systems with generic re-programmable resources. Nevertheless, the overall problem is much more complex and it involves, among others, solving the following sub-problems:

1. Modeling the system functionality and performance constraints.

System modeling refers to the *specification* problem of capturing important aspects of system functionality and constraints to facilitate design implementation and evaluation. Most hardware description languages attempt to describe a system functionality as a set of computations performed by a computing element and as interactions among computing elements. Among the important issues relevant to mixed system designs are:

- explicit or implicit concurrency in specification

- model of communication shared memory versus message-passing

- control flow specification or *scheduling* information

There is a relationship between concurrency in specification and the *natural* partitions in the system descriptions. Typically, languages that contain explicit partitioning via control flow breaks, find it difficult to specify concurrency explicitly. Concurrency information is then obtained by performing a dependency analysis whose complexity depends on the model of communication used. We consider the relevant modeling issues in Chapter 3.

2. Choosing the granularity of the hardware-software partition.

The system functionality can be handled either at the functional abstraction level where a certain set of *high-level* operations is partitioned or at the process communication level where a system model composed of interacting process models is mapped onto either hardware or software. The former attempts fine grain partitioning while the latter attempts a *high-level library binding* through coarse-grain partitioning.

3. Determining the feasible partitions of application-specific and re-programmable components.

The so-called problem of *hardware-software partitioning*. This delineation is influenced by issues such as analog interfaces that require a specialized hardware interface. However, for operations that can be implemented either in hardware or in software, the problem requires a careful analysis of the flow of data and control in the system model.

- 4. Specifying and synthesizing the hardware-software interface.

- 5. Implementing software routines to provide real-time response to concurrently executing hardware modules.

- 6. Using synchronization mechanisms for software routines and synchronization between hardware and software portions of the system.

One important issue that needs to be resolved before addressing the co-synthesis subproblems is choice of a target system architecture. By target system architecture we mean general organization of its components. As with specification, target architectures for embedded systems are not universally defined or accepted. This is in sharp contrast with single-chip systems where a single synchronous data-path/controller chip organization is almost always implied unless otherwise mentioned.

The choice of a system architecture is not a trivial task due to the great impact of system organization on system cost and performance. Further, a target architecture is strongly influenced by the *specific application* to which the system is targeted. This issue, though important, is peripheral to the co-synthesis problem that this thesis seeks to address. Therefore, we choose an architecture that preserves essential features of mixed systems while leaving the specific details as a co-design problem that must be solved in the context of an application. In order to put it in proper perspective, we present

our target system architecture in the context of the organization of some of the familiar computer systems.

#### **1.7** Architectures with Hardware-Software Components

As mentioned earlier, most digital computer systems are either *general-purpose* or *embedded*. General-purpose computer systems contain some form of storage that can be altered (reprogrammed) by the user under software control. On the other hand, embedded systems are usually hard-wired for certain specific tasks such that the degree of 'reprogrammability' varies from none to the changing of parameters of some existing sequential control. An embedded system may have a dedicated controller (a sequencer) or a microcontroller programmed to sequence operations. Most of these systems contain storage (program or data) which is relatively small and cannot be easily altered. Microcontrollers are essentially general purpose microprocessors with on-board memory for program and data storage. The ability to reprogram a computer system is related to the versatility of its primitive operations, or the instruction-set of the microprocessor or a microcomputer used in the system. In our terminology, we refer to a microprocessor or a microcontroller as a *reprogrammable component* or simply as a *processor*. The specific sequence of instructions needed for a particular application to be executed by the reprogrammable component is referred to as the software component.

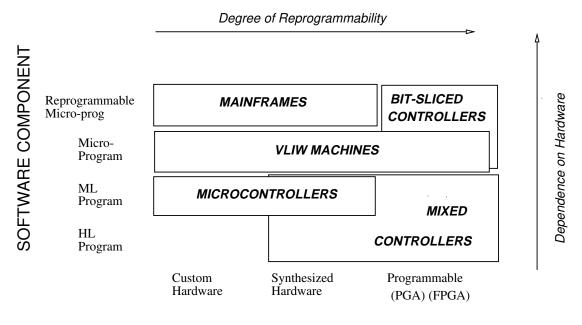

Thus, in broad terms, a digital system can be thought of as consisting of two components: *software* as a program in an on-board RAM or ROM and *hardware* as the underlying interconnection of special-purpose blocks. Based on this distinction, Figure 8 shows compositions of some familiar systems. The hardware component in a system design may be manually designed or synthesized automatically using a silicon compiler. The software component of a system may consist of microcoded routines, or machine-level programs used in embedded control systems or high-level programs used in special-purpose machines. Note that some system designs, most notably single-chip microprocessors, use microprogramming simply as a design technique for implementation of hardware control. This is different from the software *necessary* to achieve system functionality, as in microprogramming of functional algorithms in the case of mainframe

HARDWARE COMPONENT

Figure 8: System Classification Based on HW/SW Components

machines. Conventionally, machine-level and high-level programs manipulate user datastructures, while microprograms manipulate hardware resources. In the case of the mixed controller designs proposed in this dissertation, we use machine-level programs to perform both activities. The co-synthesis approach proposed in this work addresses the design problem of mixed controllers shown in Figure 8.

#### **1.7.1** Target system architecture

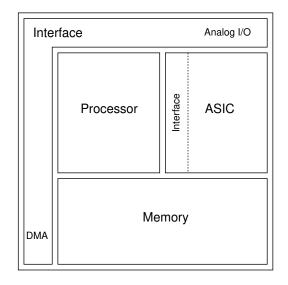

For the purposes of developing a co-synthesis approach, we choose the target architecture shown in Figure 9 that consists of a processor assisted by application-specific hardware components.

The application-specific hardware is not pipelined, for the sake of simplifying the synthesis and performance estimation task for the hardware component. Even with its relative simplicity, the target architecture is applicable to a wide class of applications in embedded systems used in medical instrumentation, process control, vehicular control,

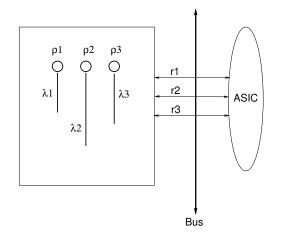

Figure 9: Target System Architecture

and communications. The following lists the assumptions relating to the target architecture. These assumptions are made in order to keep the relevant synthesis issues subject to a systematic approach, while at the same time retaining generality and effectiveness of the target architecture. Many of these assumptions can be dropped in a larger system co-design methodology without affecting the underlying co-synthesis approach developed here.

- We restrict ourselves to use of a *single re-programmable component*. We make this simplifying assumption in order to make the synthesis tasks manageable. The presence of multiple re-programmable components requires additional software synchronization and memory protection considerations to facilitate safe multiprocessing. Multiprocessor implementations also increase the system cost due to requirements for additional system bus bandwidth to facilitate inter-processor communications. These issues, though important, are not directly relevant to the focus on system co-synthesis problem addressed in this work.

- The memory used for program and data-storage may be on-board the processor. However, the interface buffer memory needs to be accessible to all of the hardware

modules directly. Because of the complexities associated with modeling hierarchical memory design, we consider only the case where all memory accesses are to a single level memory, i.e., outside the re-programmable component. The hardware modules are connected to the system address and data busses. Thus, all the communication between the processor and different hardware modules takes place over a shared medium.

- The re-programmable component is always the bus master. Almost all reprogrammable components come with facilities for bus control. The inclusion of such functionality on the application-specific component would greatly increase the total hardware cost.

- All the communication between the re-programmable component and the application-specific circuits is done over named channels whose width (i.e. number of bits) is the same as the corresponding port widths used by read and write instructions in the software component. The physical communication takes place over a shared bus.

- The re-programmable component contains a 'sufficient' number of maskable interrupt input signals. For the purpose of simplicity, we assume that these interrupts are unvectored and there exists a predefined destination address associated with each interrupt signal.

- The application-specific components have a well-defined *RESET* state that is achieved through a system initialization sequence.

Figure 10 shows a single chip realization of the target architecture. The processor in this realization refers to the processor *core* of a general-purpose microprocessor. Physical implementation of the ASIC may be achieved using standard cells or gate array circuits. The interface between the processor and the ASIC refers to the hardware portion of the interface circuitry (for details on this see Section 7.2.3). The memory consists of program ROM plus any RAM buffers need for the interface. Finally, the system interface may be composed of analog I/O circuits such as A/D and D/A converters, direct-memory access

Figure 10: Single chip realization of the target architecture

(DMA) circuits, and any possible data width conversion circuits (serial-to-parallel and parallel-to-serial).

It is important to note that the final system implementation may or may not be a single-chip system design, depending on availability of the re-programmable component either as a macro-cell or as a separate chip. Further, the approach outlined in this report can also be used for alternative target architectures.

The key concept in any realization of the target architecture is the fact that a (generalpurpose) processor is used as merely another **resource** to realize system functionality. The emphasis is not to build a system around a processor; instead the emphasis is to use a processor to reduce the size of the ASIC circuitry. At first glance, these two approaches may appear to lead to the same implementation. However, the difference is in the emphasis on the utilization of the processor to implement system functionality. For systems that are built around a given processor (or processors), the chief objective of system design is to exploit processor functionality and utilization to the fullest extent, as is the case in general-purpose computing systems. This often requires design decisions that are difficult, if not impossible, to capture in a synthesis-oriented solution. In contrast, when using the processor as another resource, the objective is to reduce the ASIC size while meeting constraints where actual utilization of the processor is of secondary importance. Due to the emphasis on devising a synthesis-oriented solution to achieve embedded system design, the resulting implementations have some limitations in their scope and applicability. These limitations are due to assumptions made on the runtime system and system interfaces in order to reduce the complexity of the embedded system design details. The assumptions and limitations are described in their context in corresponding chapters.

# **1.8 Scope and Contributions of Thesis**

The following lists the goals and contributions of this dissertation:

- Development of a model for capturing hardware and software properties. The model is based on a graph-based representation of operations and dependencies and on the relationship of computation rates to the associated communication mechanisms.

- Formulation of rate constraints for high-level synthesis purposes and analysis of feasible hardware-software partitions in the context of general timing constraints.

- Development of partitioning schemes that capture both spatial and temporal properties of the partitioned systems.

- Development of a runtime system software that is suitable for co-synthesis.

- Development of model transformations to meet rate constraints, in particular program transformations to improve latency and throughput.

- Design of a low-overhead hardware-software interface architecture.

- VILCAN a CAD tool for exploring system-level designs.

Part of the subject matter addressed in this thesis has been presented in following publications [GM90, GM91, GM92, GCM92b, GCM92a, GM93, GCM94].

# **1.9** Outline of the Dissertation

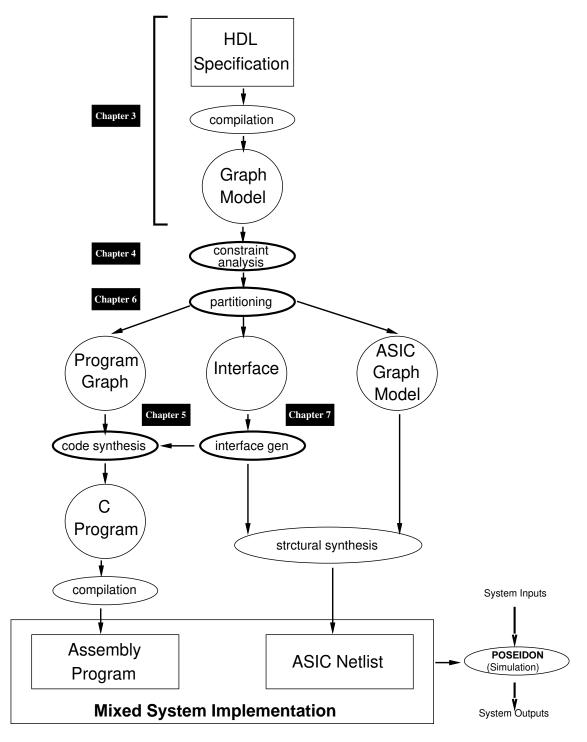

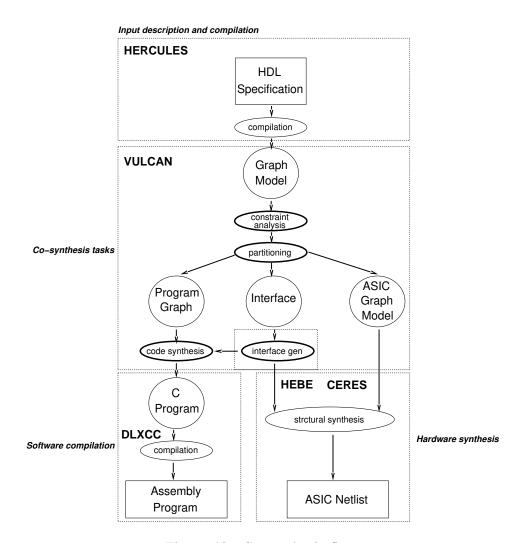

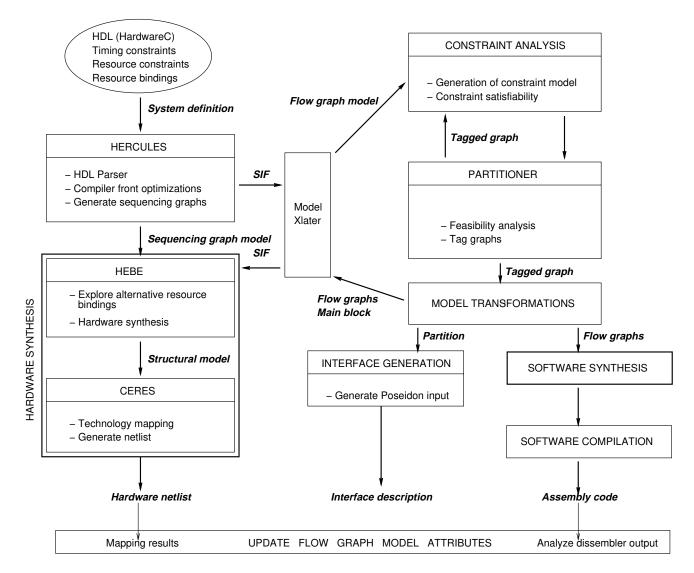

This thesis is organized according to the problem taxonomy described in Section 1.6. Chapter 2 briefly presents an overview of related work in system design and computeraided design techniques developed for system synthesis. The organization of the rest of thesis can be best explained by relating it to the organization of our co-synthesis CAD system, WLCAN shown in Figure 11. The input to our synthesis system is an algorithmic description of system functionality described in a hardware description language (HDL). The HDL description is compiled into a system graph model based on data-flow graphs. Chapter 3 describes the features and properties of our system model. Chapter 4 describes constraint modeling and analysis techniques to determine feasibility of hardware-software implementations.

In Chapter 5 we discuss issues and techniques in the generation of software and its associated runtime environment. We introduce the concept of a threaded software implementation which is shown to observe constraint satisfiability properties discussed in Chapter 4. In Chapter 6 we define the problem of system partitioning and present an approach to partitioning of systems for hardware-software co-synthesis. In Chapter 7 we discuss issues in system synchronization, how synchronization is achieved between heterogeneous components of a system design. Here we also present an overview of the VULCAN system. The resulting mixed system design consists of an assembly code for the software component, and a gate-level description of the hardware and hardware-software interface. This heterogenous description is simulated using the program POSEI DON that is described elsewhere [GCM92b].

Chapter 8 describes case studies in hardware-software co-synthesis and results. Chapter 9 presents conclusions and directions for future research.

Figure 11: System Synthesis Procedure

# Chapter 2

# **Related Work**

This chapter reviews important developments in the area of system design and synthesis. The issue of co-design of hardware and software often appears in the larger context of system design. Computer architects often tradeoff the implementation of an instruction in hardware versus its implementation in software as a sequence of available instructions. This flavor of the co-design problem addresses the issue of design of software and hardware *upon* which the software runs. This is clearly different from the notion of hardware and software defined in the previous chapter, where the software runs on a predesigned hardware. The idea of hardware-software co-design has even been applied to the *process* of system design [BV92].

We briefly review some of the novel architectures that consist of a mix of hardware and software. Programmable active memories, PAM [BRV89], use a network of basic cells which are programmed for specific applications. The Map-oriented Machine (MoM) [HHW89] belongs to a class of system architectures for implementing systolic algorithms. MoM's relevance to system co-design is highlighted by its reliance on reprogrammable technologies to achieve performance speedups. Indeed, its derivative work on *xputer*[HHR<sup>+</sup>91] attempts to use MoM architectural principles in prototype implementation of non-systolic algorithms. MoM is characterized by data-driven execution streams. This key advantage is achieved by replacing register and ALU combinations in sequential processors by a logic unit, called the problem-oriented logic unit, that uses RAMs, PLDs and other programmable hardware. QuickTurn [Wal90] and PiE systems use reprogrammable hardware to create system prototypes. The primary advantage of these systems is the short amount of time it takes to create and modify these prototypes that may not provide the intended system timing performance, but these prototypes are considerably faster than their equivalent software prototypes.

Another area where the co-design problem has been studied is in the design and analysis of 'real-time systems'. Real-time systems span a wide variety of applications and can be fairly complex. Performability analysis of real-time systems, defined as analysis of system performance metrics over finite time intervals, is one of the key analytical tools.

Work in the computer-aided approach to system design is relatively new. Recent interest in system synthesis has been stimulated by the relative success and maturity of chip-level synthesis tools, and emergence of synthesis approaches at levels of abstraction higher than logic-level and RTL-level circuit descriptions. CAD related work falls under two broad categories:

- Generic CAD for supporting hardware-software co-design. These approaches generally recognize the difficulty in addressing all parts of the system design problem in a unified framework. Therefore, these systems concentrate on providing a frame-work to support the process of system design.

- 2. Specific CAD for hardware-software co-synthesis. Work in this area concentrates on providing CAD solutions to specific synthesis sub-problems. Most of these solutions are devised under specific restrictions on system implementation.

# 2.1 CAD Systems for Hardware-Software Co-design

A CAD system refers to an integrated collection of tools that conform to an overlaying methodology usage of these tools. The overall goal of a CAD system is to improve the process of system analysis and design. In all these systems, trade-offs are made among the following metrics:

1. **Analyzability** - the ability to analyze a system design for its functional and performance properties,

- 2. Simulatability the ease in arriving at a complete system simulation,

- 3. **Implementability** the ability to implement (design or synthesize) a system from its specification.

### 2.1.1 Ptolemy

PIOLEMY [BHLMar] [KL93] is a framework for the simulation, prototyping and software synthesis of digital signal processing systems. Due to its application focus on the DSP domain, the reprogrammable components in system design are chosen from a set of general-purpose DSP processors (or equivalent cores), such as Motorola DSP56001, DSP96002. Hardware in PIOLEMY refers to custom data paths and discrete (or glue) logic components in addition to the processor.

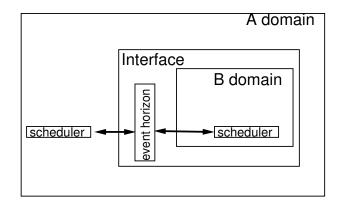

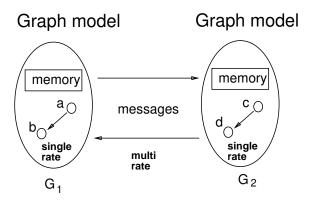

PIOLEMY's strength is its unified framework for the simulation of specifications as a set of heterogenous computation models. Specification in a particular model of computation is referred to as a design style that is encapsulated in objects called *domains*. A domain is comprised of blocks, targets and a scheduling discipline appropriate to its model of computation. In addition, *operational semantics* are embedded in blocks that govern their interaction with other blocks. Examples of supported domains are synchronous data flow (SDF), dynamic data flow (DDF), discrete event (DE) and signallevel digital hardware (Thor). A domain may embed another domain in its hierarchy. An embedded domain interacts with its parent domain by means of a procedures called the *event horizon*. Figure 12 explains the organization of domains and interface.

The event horizon is a key feature in PTOLEMY that makes it possible to interface event schedules from different domains. Domains can be classified into two categories: **timed** and **untimed** domains. A timed domain refers to a model of computation that produces events in the context of an associated time scale, for example, a discrete event domain. On the other hand, untimed domains do not have an absolute time association with their events, for example, data flow. When interfacing events across timed and untimed domains, there are several issues in event synchronization that must be worked out. In general, it would be hard, if not impossible, to provide a consistent simulation framework across concurrently independently active domains. However, due to embeddings

Figure 12: Objects in PIOLEMY

of these domains PTOLEMY makes it possible to carry out simulation under (conservative) restrictions. Stopping heuristics are used in domain simulations in order to make sure that inner timed domains do not temporally get ahead of the time in outer domains. Of course, inner untimed domains react in zero time. Outer untimed domains maintain timing attributes in order to set stop times for their inner domains. As an example, an event from an untimed domain causing an event into timed domain initiates a time scale on which to carry out further events in the timed domain until the inner domain has no more active events, thus making the timed domain appear like a functional block.

Despite the code generation abilities in its synchronous data flow (SDF) domain, PTOLEMY is primarily a simulation-oriented tool. Its specification language (for domains) is a procedural C++-type language. All models must be specified in this language which is extended to allow modeling of operators from various other languages (such as the '@' operator from Silage etc). Each model generates tokens. Models differ in values and timing interpretation of these tokens. Various models can be connected using a graphical schematic capture or a netlist language.

Even though semantically rich, PTOLEMN's syntax is awkward for specifying systems that are best captured in non-procedural languages. The use of a predefined library of a large number of models ameliorates this difficulty in specifying model functionalities.

The strength in heterogeneity by use of diverse computation models in PIOLEMY comes at the loss of an analytical handle on system properties. Further, it suffers in implementability of these models because of the necessity to specify these systems in