# Common-Mode DC-Bus Filter Design for Variable-Speed Drive System via Transfer Ratio Measurements

Dongsheng Zhao, Student Member, IEEE, J. A. Ferreira, Fellow, IEEE, Anne Roc'h, Student Member, IEEE, and Frank Leferink, Senior Member, IEEE

Abstract—Filters used in electromagnetic interference suppression are often described in literature on drive systems and have become a standard solution in industry. The effect of the commercial off-the-shelf filter depends significantly on how it is installed. A model that includes the installation parameters is made first and then the parameters of the model are extracted by transfer ratio measurements. One possibility is to include the filter on the dc-bus inside the converter. The differential mode dc-bus filter is well known, but the common-mode dc-bus filter has received little attention. Our model is used to show that the common-mode dc-bus filter can achieve the same or even better suppression of common-mode noise by careful design. The transfer ratio is used to evaluate the performance of filter design.

*Index Terms*—Electromagnetic compatibility, electromagnetic interference, filters, variable-speed drives.

### I. INTRODUCTION

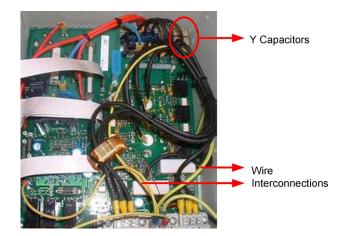

SING filters is a well-known solution to suppress the EMI of drive systems [1]–[3]. The filters should work efficiently according to the datasheets provided by filter manufacturers. However, the effect of filters may change significantly depending on how they are installed. Grounding methods or interconnection methods have large impact on the real attenuation provided by the filter. A node in a schematic diagram may be a wire or a mounting screw in the real application. For example, in one converter provided by the industry, the heat sink and the Y capacitors on printed circuit board are connected to the converter frame by 20-cm long wires (see Fig. 1). Although in some well-designed products, the long wires are replaced by shorter connections or mounting screws, the parasitic values still exist for the connections. These parasitic parameters affect the electromagnetic compatibility (EMC) performance of the drive system [4], [5].

Manuscript received May 30, 2008; revised August 11, 2008; accepted September 23, 2008. Current version published February 6, 2009. This work was supported by the Dutch Ministry of Economic Affairs under Innovative Research Project (IOP). Recommended for publication by Associate Editor P. Tenti.

D. Zhao and J. A. Ferreira are with the Faculty of EWI, Delft University of Technology, 2628CD Delft, The Netherlands (e-mail: dongsheng. zhao@gmail.com; j.a.ferreira@tudelft.nl).

A. Roc'h is with the Faculty of EWI, University of Twente, 7500AE Enschede, The Netherlands (e-mail: a.roch@utwente.nl).

F. Leferink is with the Faculty of EWI, University of Twente, 7500AE Enschede, The Netherlands, and also with Thales Netherlands, 7550 GD Hengelo, The Netherlands (e-mail: frank.leferink@utwente.nl).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2008.2007296

Fig. 1. Photo shows the real installation inside a converter.

The transfer ratio is defined in [6] as the ratio of the common mode (CM) current  $I_{CM1}$  on the line side to the CM current  $I_{CM2}$  on the motor side. It is used to indicate how efficiently the filter blocks the noise propagation. There are three reasons why the transfer ratio is defined in this way.

- The CM current can be easily measured with current probe because the electrical contact is not necessary. The transfer ratio can possibly be measured with low-cost current probes [7] even when the conversion factors of these lowcost current probes are unknown or not calibrated.

- 2) The installation methods, include the grounding configuration and interconnection methods, have little effect on the differential mode (DM) noise conversion. The DM noise is dominant in the low-frequency range, where the values of the discrete components are significant compare to that of the parasitic components. By contrast, CM noise is the main part that has been influenced.

- 3) CM currents may flow in any of the phases in the three phase lines [8], [9]. There are differential-mode components produced by CM currents when the CM currents are not evenly distributed in the three phases. For the same CM currents with different distributions in the three phases, LISN measurement in one particular phase gives an uncertainty up to 9.5 dB (= $20 \log_{10} 3$ ), because the LISN cannot distinguish between the CM components and the DM components. Using current measurement to measure the CM current can avoid the DM components by adding the currents in the three phase lines together.

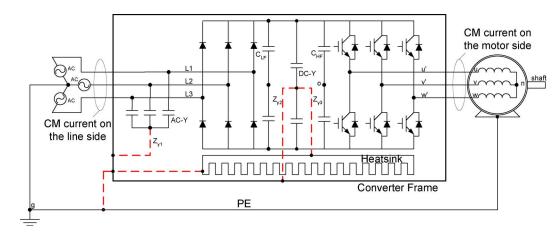

Fig. 2. Circuit diagram of the converter under test.

In this paper, the relationship between transfer ratio and parasitic parameters is derived by using a model. Therefore, the parameters can be extracted from significant points on the curve of transfer ratio measurement result. The suppression efficiencies when placing the Y capacitors at different places are also compared using the model. The transfer ratio is used to evaluate the suppression efficiency. A good solution is to connect the dc-Y capacitors between the dc-bus and the heat sink and to put the common mode choke (CMC) between the rectifier and the dc-Y capacitors. Comparisons are used to show the key design rules of CM dc-bus filter. Experimental results show that placing the dc-Y capacitors on dc-bus can achieve better suppression performance.

#### II. EXPERIMENTAL SETUP AND MODELING

#### A. Experimental Setup

A commercial pulsewidth modulation voltage source inverter with diode rectifiers is selected for the case study. Its power rating is 12 kW. An induction machine is fed with this converter. The measurements are made in unloaded condition. It is believed that the transfer ratio is determined by the passive components only; therefore, the ratio is not affected by the load condition.

Fig. 2 illustrates the whole experimental setup. In the original design, the ac-Y capacitors were placed between the ac line and the converter frame. The dashed lines represent the real installation wires that cannot be idealized in the model for EMC analysis. Also, in Fig. 2, it is proposed to connect the dc-Y capacitors between the dc-bus and the converter frame or the heat sink. Two circles indicate the positions where the CM currents are measured to derive the transfer ratio.

#### B. CM Equivalent Model

A frequency domain model is proposed in [10] to calculate the CM noise generated by switched power converter. Based on the CM equivalent circuit, the model is expanded by including the parasitic parameters brought by installation. Then, it is further simplified by applying reasonable assumptions. We assume that the parameters of the three inverter legs are the same. The arbitrary voltage noise sources can be treated as superimposed three

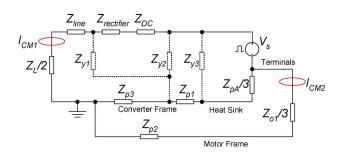

Fig. 3. CM equivalent circuit.

identical CM voltage sources and three DM voltage sources. The DM voltage sources will not produce a current flowing through ground. Therefore, they can be removed if we want to calculate the CM current. Three identical CM voltage sources can be further reduced to one CM voltage source after changing the CM impedance of load and stray impedance between the output terminal and the heat sink to one-third of their original value. The equivalent circuit used to calculate the transfer ratio is shown in Fig. 3.

The generated CM currents flow along the dc-bus to the line side. The CM current will be evenly distributed in positive and negative dc-bus bars after the high-frequency dc-link capacitors  $C_{\rm HF}$ . Therefore, the two dc-bus bars are considered as one node in the model.  $Z_{y1}$ ,  $Z_{y2}$ , and  $Z_{y3}$  represent the three possible places for placing the Y capacitors. They are identified by a dashed line in Fig. 3.  $Z_{y1}$  represents the ac-Y capacitors connected between ac line input and converter frame.  $Z_{y2}$  represents the dc-Y capacitors added between the dc-bus and the converter frame.  $Z_{y3}$  represents the dc-Y capacitors whose one terminal is connected to the heat sink instead of the converter frame. The impedance of the ac line, the rectifier, and the dc-bus are indicated as  $Z_{\rm line}$ ,  $Z_{\rm rectifier}$  and  $Z_{\rm dc}$ , respectively. Besides that, the following notations have been adopted.

- $Z_{p1}$  The impedance of the connection between the converter frame and the heat sink.

- $Z_{p2}$  The impedance of the connection between the motor frame and ground.

- $Z_{p3}$  The impedance of the connection between the converter frame and ground.

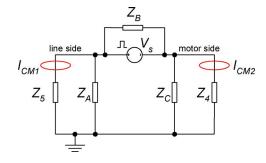

Fig. 4. CM equivalent circuit after Y- $\Delta$  conversion.

$Z_{o(1,2,3)}$  The CM impedance of the load, including the cable and the motor in the present example.  $Z_{p(A,B,C)}$  The impedance between output terminals of the converter legs and the heat sink.  $Z_L$  The impedance of the LISN.

# C. Model Parasitic Parameters Extraction From Transfer Ratio Measurements

The transfer ratio T is defined as the ratio of the CM current  $I_{\rm CM1}$  on the line side to the CM current  $I_{\rm CM2}$  on the motor side. For the conventional way, ac-Y capacitors are placed between ac line input and converter frame, as indicated by  $Z_{y1}$  in Fig. 3. This model can be further simplified by Y- $\Delta$  conversion because it is easy to apply the current divider rule. The simplified model is shown in Fig. 4, and the transfer ratio can be expressed in a concise form as

$$T = \left| \frac{I_{\rm CM1}}{I_{\rm CM2}} \right| = \left| \left( \frac{Z_A}{Z_5 + Z_A} \right) \left( \frac{Z_C + Z_4}{Z_C} \right) \right|.$$

(1)

In this equation

$$Z_4 = \left(\frac{Z_{o1}}{3} + Z_{p2}\right) \tag{2}$$

$$Z_5 = \left(\frac{Z_L}{2} + Z_{\rm line}\right) \tag{3}$$

$$Z_A = (Z_{y1} + Z_{p3}) + \frac{Z_{y1}Z_{p3}}{Z_{pA}/3 + Z_{p1}}$$

(4)

$$Z_C = \left(\frac{Z_{pA}}{3} + Z_{p1} + Z_{p3}\right) + \frac{(Z_{pA}/3 + Z_{p1})Z_{p3}}{Z_{y1}}.$$

(5)

The values of the parasitic parameters are not easy to obtain by direct measurement [11]. Therefore, a method to derive the parasitic parameters via the transfer ratio measured in some particular situations is introduced here.

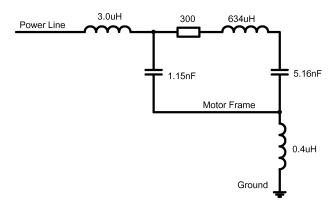

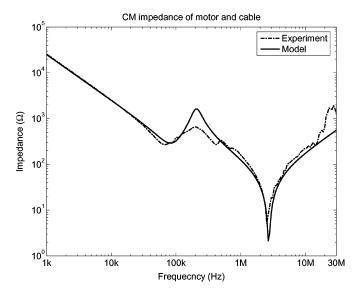

The high-frequency CM behavior of the motor and the cable is firstly modeled by the method introduced in [12] and [13]. It is illustrated in Fig. 5. This corresponds to the impedance of  $Z_{o1}/3$  and  $Z_{p2}$  in Fig. 3. Fig. 6 compares the simulation and measurement results.

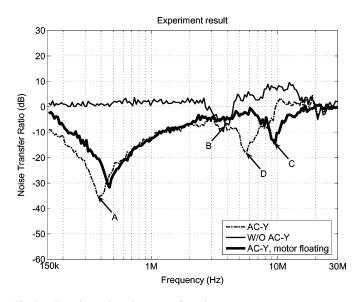

After that, the transfer ratio of the test setup is measured in three situations:

- 1) the ac-Y capacitors are installed at ac line input; (ac-Y);

- 2) the ac-Y capacitors are not installed. (W/O ac-Y);

Fig. 5. High-frequency CM model of the motor and the cable.

Fig. 6. Simulation versus measurement of the CM impedance of the motor and the cable.

3) the ac-Y capacitors are installed at ac line input and the motor is floating to ground; (ac-Y, motor floating).

The results are shown in Fig. 7. The next step involves how to derive the parameters of the model by the results. When applying (1), the transfer ratio apparently reaches its minimum point under two conditions, i.e., when  $Z_A$  or  $Z_C + Z_4$  reach their minimum. In the first situation, a minimum is found around 370 kHz (see Fig. 7, point A). That is because  $Z_A$  approaches its minimum as mentioned before. It can be approximated by the series resonance of  $Z_{y1} + Z_{p3}$ . The values of the ac-Y capacitors are already known to be 100 nF. Therefore, the stray inductance to produce the  $Z_{p3}$  is calculated by  $1/(4\pi^2 f 3C_Y)$ , i.e., 0.7  $\mu$ H. Although the impedances  $Z_4$  and  $Z_5$  may shift the resonance frequency slightly, it provides a method to determine the first guess of parasitic parameters of the model.

In the second situation, the Y capacitors are disconnected, which makes  $Z_{y1}$  quite large and  $Z_C + Z_4$  can be approximated as  $Z_{pA}/3 + Z_{p1} + Z_{p3} + Z_{o1}/3 + Z_{p2}$ . It determines the second minimum observed around 3.6 MHz (see Fig. 7, point B). The inductive part of impedance in this loop is 3.4  $\mu$ H + 0.7  $\mu$ H = 4.1  $\mu$ H, the capacitive part should be around 470 pF. In

Fig. 7. Experimental results on transfer ratio.

this frequency range, only  $C_{g1}$  (1.15 nF) dominates  $Z_{o1}/3$ . The  $Z_{pA}/3$  is calculated to be the capacitive impedance produced by 800 pF capacitor to get this resonance frequency.

In the measurement done in the third situation, the motor is floating, and the resonance moves to 10 MHz (see Fig. 7, point C). The reason is that the capacitive part in the loop is dominated by the parasitic capacitor between the motor frame and ground.  $Z_{p2}$  is replaced by a 100 pF capacitor to create the resonance.

Comparing the first and the third situation, points D and C in Fig. 7 are caused by the same resonance. The minimum point shifts slightly due to the variation of  $Z_{p2}$ . By fine adjustment of  $Z_{p1}$  and  $Z_{p3}$ , the resonance frequency can be matched to the measurement result very well. In the last step, some damping resistances are added to adjust the quality factor of the resonance. The ratio curves by calculation become even closer to the measurement results.

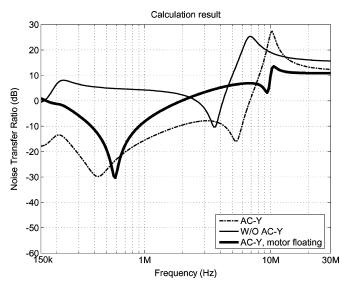

Up until now, the parameters for the proposed CM model were extracted by the transfer ratio measurement. They are listed in Table I. With the model, the transfer ratio calculated by the model shown in Fig. 8 shows a good agreement with the measurement result in Fig. 7. Because the calculation is done on frequency domain, it is an efficient way to calculate the transfer ratio even for a complex model [14].

#### D. DC-Bus Filter

In Fig. 2, three possible positions to place Y capacitors are shown. When the Y capacitors are connected to the dc-bus, as indicated by  $Z_{y2}$  or  $Z_{y3}$  in the figure, the way to calculate  $Z_5$ ,  $Z_A$ , and  $Z_C$  requires a change.

When the Y capacitors are placed at the position of  $Z_{y2}$  or  $Z_{y3}$ , (3) need to be changed to (6)

$$Z_5 = \left(\frac{Z_L}{2} + Z_{\text{line}} + Z_{\text{rectifier}} + Z_{\text{dc}}\right). \tag{6}$$

TABLE I Parameters in the Model

| $Z_L$           | 50Ω                               |

|-----------------|-----------------------------------|

| $Z_{y1}$        | $300$ nF+ $0.2\mu$ H              |

| $Z_{p1}$        | $0.2 \mu \mathrm{H}{+}6 \Omega$   |

| $Z_{p2}$        | $0.4 \mu \mathrm{H}{+}5 \Omega$   |

| $Z_{p3}$        | $0.5\mu\mathrm{H}$ + $0.8\Omega$  |

| $Z_{o1}/3$      | 3.0µH+1.15nF  (300Ω+634µH+5.16nF) |

| $Z_{pA}/3$      | 800pF                             |

| $Z_{rectifier}$ | ignored                           |

| $Z_{line}$      | ignored                           |

| $Z_{dc}$        | $0.5\mu\mathrm{H}$ +8 $\Omega$    |

Fig. 8. Transfer ratio as calculated with the model.

Especially, when the Y capacitors are placed at the position of  $Z_{y3}$ , (4) and (5) need to be changed to (7) and (8)

$$Z_A = (Z_{y1} + Z_{p1} + Z_{p3}) + \frac{Z_{y1}(Z_{p1} + Z_{p3})}{Z_{pA}/3}$$

(7)

$$Z_C = \left(\frac{Z_{pA}}{3} + Z_{p1} + Z_{p3}\right) + \frac{(Z_{pA}/3)(Z_{p1} + Z_{p3})}{Z_{y1}}.$$

(8)

These closed-form equations can be used to calculate the transfer ratio in frequency domain directly. Based on the established model, the noise suppression efficiency of the three possible methods can be compared. Some conclusions are drawn as follows:

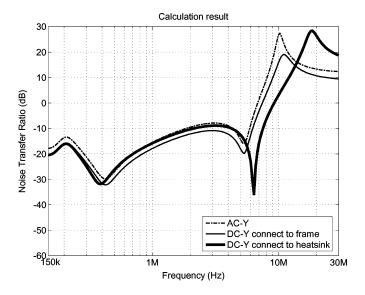

1) In Fig. 9, the transfer ratio is calculated by the built model. When the Y capacitors are placed at position  $Z_{y1}$  or  $Z_{y2}$ , the two connection methods are slightly different because of the small dc-bus impedance. For the third connection method, the dc-Y capacitors are connected to a heat sink.  $Z_A$  and  $Z_C$  are calculated using (7) and (8) instead of (4)

Fig. 9. Transfer ratio comparison by adding Y capacitors at different positions (calculation result).

Fig. 10. Transfer ratio comparison for the effect of dc-bus CM chokes after adding Y capacitors at different positions (calculation result).

and (5). It can be seen that the EMC performance becomes slightly worse in the low-frequency range and improves in the high-frequency range. For these three positions for placing Y capacitors, suppression effects are almost the same.

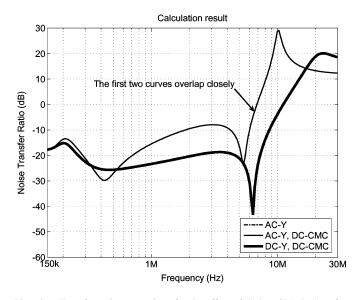

2) Compared to the ac-Y capacitors, the dc-Y capacitors are placed at positions  $Z_{y2}$  or  $Z_{y3}$ .  $Z_5$  is calculated by (6) instead of (3). The increasing value of  $Z_5$  can decrease the transfer ratio, which means by adding a CM choke between rectifier and dc-Y capacitors, the noise will be suppressed better. On the contrary, adding the CM choke on the dc-bus has no effect on the transfer ratio when ac-Y capacitors are connected in ac line input. In Fig. 10, the conclusion is proved by the calculated transfer ratio from the built model.

Fig. 11. Transfer ratio using dc-bus filter with very short interconnection (calculation result).

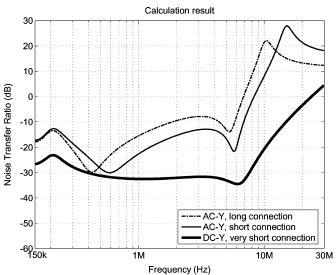

3) The connection between the heat sink and ground and the connection between Y capacitors and the heat sink are vital to the suppression efficiency. They must all be kept as short as possible. By decreasing the  $Z_{p1}$ ,  $Z_{p3}$  and inductive part of  $Z_{y1}$ , the suppression effect makes significant progress. In Fig. 11, the transfer ratio is first calculated assuming that the connection wires are two times shorter. The result shows that the transfer ratio gets 10 dB improvement around 1-6 MHz, where some EMC problems often come up. The calculation is also done assuming the parasitic components of the connection wires are reduced to one-tenth of the original values. This is possible when screw mounting is used instead of wire interconnection. Here, the Y capacitor is also increased three times although it contributes additional leakage current. Via this arrangement, 20 dB improvement is achieved around 1–6 MHz; there is also a 10 dB improvement in the low-frequency range.

It is worthwhile to mention here that the addition of the filter not only changes the transfer ratio but also changes the level of the noise source. The changes might be better or worse, and sometimes, in the reverse direction. These two effects can be considered separately and there is a compromise between them. The transfer ratio is affected by the passive components only, while the noise source level is determined by both the active and passive components. In this paper, we study the transfer ratio solely because we consider only the influence of installation methods.

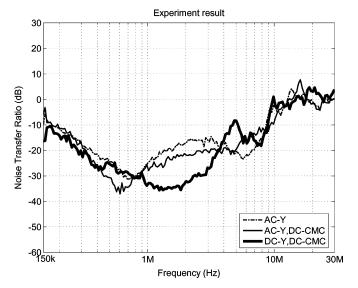

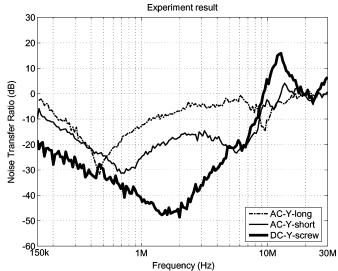

The experiment is done on the test setup to verify the model further and conclusions are drawn in the last section. The components employed in the experiments are listed in Table II. The first experiment is done to show the effect of adding a CM choke on the dc-bus. Compared with the transfer ratio of using ac-Y solely, adding the CM choke on the dc-bus does not make a big difference, which is consistent with the calculation. However,

| Qty. | Components | Specification                         |

|------|------------|---------------------------------------|

| 3    | AC-Y       | 100nF                                 |

| 2    | DC-Y       | 47nF                                  |

| 1    | DC-CMC     | Rasmi RS-OC/2, AL=12 $\mu$ H, 2 turns |

TABLE II Components Used in the Experiments

Fig. 12. Transfer ratio comparison for the effect of dc-bus CM chokes after adding Y capacitors at different positions (experimental result).

the combination of dc-Y and dc-CMC improves the suppression effect in the 1–4 MHz range, as shown in Fig. 12.

The second experiment shows the importance of short connections. The transfer ratios are compared between the test setup originally designed (20 cm), half-length connection (10 cm), and screw-mounted filter. The benefit is significant for a well-designed installation. Compared with the calculation results from Fig. 13, the trends are the same, and the minimum point moves toward a higher frequency as predicted, and the transfer ratio is lower after the resonance frequency. The transfer ratio does not improve so much beyond 10 MHz, it even becomes a positive value. That means that a new resonance loops occurs, because of the resonance of the dc-Y capacitors and the stray inductance of the dc-bus. Because the noise source level is much lower in this frequency range, even though the transfer ratio is increasing, it would not be a problem.

Comparing the experimental results of Figs. 12 and 13 to the calculation results of Figs. 10 and 11, the deviation exists. The deviation between the experimental results and the calculation results is due to the very simple model. In experimental results, the transfer ratio approaches 0 dB in the high-frequency range. This is because the noise measurements are close to the noise floor in the high-frequency range. The application of transfer ratio method is limited by the measurement in the high-frequency

Fig. 13. Transfer ratio using dc-bus filter with very short interconnection (experimental result).

range. More accurate measurements of transfer ratio can be achieved if a preamplifier is available to lower the noise floor.

## **III.** CONCLUSION

The transfer ratio is defined and can be measured by a lowcost current probe. The parasitic parameters of the model can be extracted based on the transfer ratio measurement results. Based on the established model, the benefit of using a dc-bus CM filter can be calculated efficiently in the frequency domain. The filter is installed inside the converter and the interconnection can be made very short. That can improve the suppression performance significantly. This avoids the tricky task of designing or selecting a filter afterward. The noises are suppressed partly inside the converter if the dc-bus filter is included in the design. For some critical requirements, the additional filter needed would be much smaller.

#### REFERENCES

- [1] F. Shih, D. Chen, Y. Wu, and Y. Chen, "A procedure for designing EMI filters for AC line applications," *IEEE Trans. Power Electron.*, vol. 11, no. 1, pp. 170–181, Jan. 1996.

- [2] N. Hanigovszki, J. Poulsen, and F. Blaabjerg, "A novel output filter topology to reduce motor overvoltage," *IEEE Trans. Ind. Appl.*, vol. 40, no. 3, pp. 845–852, May–Jun. 2004.

- [3] H. Akagi and T. Shimizu, "Attenuation of conducted EMI emissions from an inverter-driven motor," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 282–290, Jan. 2008.

- [4] G. Grandi, I. Montanari, and U. Reggiani, "Effects of power converter parasitic components on conducted EMI," in *Proc. Int. Symp. Electromagn. Compat. (EMC Zurich)*, 1997, pp. 499–504.

- [5] S. Wang, F. Lee, W. Odendaal, and J. van Wyk, "Improvement of EMI filter performance with parasitic coupling cancellation," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1221–1228, Sep. 2005.

- [6] D. Zhao, J. Ferreira, H. Polinder, A. Roc'h, and F. Leferink, "Using transfer ratio to evaluate EMC design adjustable speed drive systems," in *Proc. Eur. Int. Symp. Electromagn. Compat.*, 2006, pp. 140–145.

- [7] F. Ridao, J. Carrasco, E. Galván, and L. Franquelo, "Implementation of low cost current probes for conducted EMI interference measure in power systems," presented at the Eur. Conf. Power Electron. Appl. (EPE), Lausanne, Switzerland, 1999.

- [8] W. Shen, F. Wang, and D. Boroyevich, "Conducted EMI characteristic and its implications to filter design in 3-phase diode front-end converters," in *Proc. IEEE Ind. Appl. Soc. Conf. (IAS)*, 2004, vol. 3, pp. 1840–1846.

[9] J. Meng, W. Ma, L. Zhang, and Z. Zhao, "Identification of essential cou-

- [9] J. Meng, W. Ma, L. Zhang, and Z. Zhao, "Identification of essential coupling path models for conducted EMI prediction in switching power converters," in *Proc. IEEE Ind. Appl. Soc. Conf. (IAS)*, 2004, vol. 3, pp. 1832– 1839.

- [10] D. Gonzalez, J. Gago, and J. Balcells, "New simplified method for the simulation of conducted EMI generated by switched power converters," *IEEE Trans. Ind. Electron.*, vol. 50, no. 6, pp. 1078–1084, Dec. 2003.

- [11] H. Zhu, A. Hefner, Jr., and J. Lai, "Characterization of power electronics system interconnect parasitics using time domain reflectometry," *IEEE Trans. Power Electron.*, vol. 14, no. 4, pp. 622–628, Jul. 1999.

- [12] M. Schinkel, S. Weber, S. Guttowski, W. John, and H. Reichl, "Efficient HF modeling and model parameterization of induction machines for time and frequency domain simulations," in *Proc. IEEE Appl. Power Electron. Conf. Expo. (APEC)*, 2006, 6 pp.

- [13] A. Boglietti, A. Cavagnino, and M. Lazzari, "Experimental high-frequency parameter identification of AC electrical motors," *IEEE Trans. Ind. Appl.*, vol. 43, no. 1, pp. 23–29, Jan.–Feb. 2007.

- [14] L. Ran, S. Gokani, J. Clare, K. Bradley, and C. Christopoulos, "Conducted electromagnetic emissions in induction motor drive systems. II. Frequency domain models," *IEEE Trans. Power Electron.*, vol. 13, no. 4, pp. 768– 776, Jul. 1998.

**Dongsheng Zhao** (S'06) was born in Yining city, China, in 1975. He received the B.Sc degree in electronic engineering from Shanghai JiaoTong Univeristy, Shanghai, China, in 1993, and the Master's degree in electric engineering from the University of Twente, Enschede, The Netherlands, in 2004. He is currently working toward the Ph.D. degree at the Electrical Power Processing Group, Faculty of EWI, Delft University of Technology, Delft, The Netherlands.

He was with the industry for 9 years. His current research interests include electromagnetic compatibility issues in power electronic applications.

Netherlands.

**Anne Roc'h** (S'07) was born in Strasbourg, France, in 1981. She received the Diploma in electronics, telecommunication, and instrumentation engineering from the National Engineering School of Limoges, Limoges, France, in 2005.

Since 2005, she is a Ph.D. Research Assistant in the Telecommunication Engineering Group, Faculty of EWI, University of Twente, Enschede, The Netherlands, where she is engaged in researech on multidimensional optimization in power electronics. This work is performed in collaboration with Thales

**Frank Leferink** (M'92–SM'07) received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Twente, Enschede, The Netherlands, in 1992 and 2002, respectively.

He was in 1994 with Hollandse Signaalapparaten B.V., which is now part of the THALES Netherlands Group. He is currently the Technical Authority Electromagnetic Compatibility (EMC) of THALES Nederland, Manager of the Network of Excellence on EMC of the THALES Group, and since 2003, he also has been the Chair for EMC at the University of

Twente, The Netherlands, where he is engaged in research on EMC. He holds several patents on EMC measurements techniques and is the author or coauthor of more than 125 papers on EMC in journals and at conferences. His current research interests include electromagnetic interference due to power electronics and modeling of electromagnetic fields and EMC issues in semienclosed environments, as well as the favorite subjects EMC at printed circuit board and integrated circuit level and innovative EMC test techniques.

J. A. Ferreira (M'88–SM'01–F'05) received the B.Sc.Eng. (*cum laude*), M.Sc.Eng. (*cum laude*), and Ph.D. degrees in electrical engineering from the Rand Afrikaans University, Johannesburg, South Africa, in 1980, 1982, and 1988, respectively, all in electrical engineering.

In 1981, he was with the Institute of Power Electronics and Electric Drives, Technical University of Aachen, Aachen, Germany, and worked in industry at ESD (Pty) Ltd. from 1982 to 1985. From 1986 to 1997, he was on the Faculty of Engineering, Rand

Afrikaans University, where he held the Carl and Emily Fuchs Chair of Power Electronics. Since 1998, he has been a Professor at the Faculty of EWI, Delft University of Technology, Delft, The Netherlands.

Prof. Ferreira was a member of the IEEE PELS Adcom, and is, since 2005, the Treasurer of the IEEE PELS. He served as Chairman of the International Council on Large Electric Systems (CIGRE) SC14 National Committee of the Netherlands and was a member of the Executive Committee of the European Power Electronics Society. He was Chairman of the South African Section of the IEEE during 1993–1994. He was the Founding Chairman of the IEEE Joint Industrial Applications Society (IAS)/Power Electronics Society (PELS) Benelux Chapter in 1999. He served as the Transactions Review Chairman of the IEEE IAS Power Electronic Devices and Components Committee and is an Associate Editor of the TRANSACTIONS ON POWER ELECTRONICS.