# Compact Modeling of Organic Transistors with Multi-Finger Contacts

Afra Al Ruzaiqi<sup>1</sup>, Boyko Nikolov<sup>1</sup>, Lawrence R. Chen<sup>2</sup>, Helena Gleskova<sup>1</sup>

<sup>1</sup>Department of Electronic and Electrical Engineering, University of Strathclyde, Glasgow, UK <sup>2</sup>Department of Electrical and Computer Engineering, McGill University, Montreal, Canada afra.al-ruzaiqi@strath.ac.uk

# I. SUMMARY AND MOTIVATION

Organic thin-film transistors (OTFTs) with multi-finger contacts based on dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) exhibit near-zero turn-on voltage, hysteresisfree behavior, and high transconductance of 30-80  $\mu$ A at V<sub>DS</sub> =  $V_{\rm GS} = -2$  V. [1] In addition, common-source amplifiers based on such transistors deliver voltage gain even when the supply voltage is limited to 5 V, making them attractive for flexible/ wearable analog sensors. This paper presents the results of compact modeling, implemented in Matlab Simulink, applied to such transistors. The measured transistor transfer characteristics are used to extract the parameters for the semiempirical model. The model was validated in 3 ways on 8 OTFTs with varied geometries and substrates (glass or PEN). The validation included calculations of (a) transistor output characteristics, (b) a.c. drain currents for 1 Hz sinusoidal gate voltages, and (c) output voltages of the common-source amplifier, and their comparison to the measured data.

#### II. ADVANCES OVER PREVIOUS WORKS

The commercial success of thin-film transistors (TFTs) based on polycrystalline and hydrogenated amorphous silicon started the development of physical and/or semi-empirical transistor models to aid in the design of circuits and systems. [2] In the past 30 years such models have been extended to other TFT technologies, OTFTs including. Physical transistor models tend to be complex as a result of accurately capturing the physical behavior of the devices. If this requirement is relaxed, semi-empirical mathematical equations can be used to accurately describe the transistor drain current. Such models involve 'empirical', i.e., 'fitting' parameters, yet are able to predict with high accuracy the operating characteristics of the transistors while requiring shorter computation times.

To address particular principles and features of the OTFTs and/or adopt simplifications to provide an accessible analysis, various OTFT compact models were developed. [3-5] Examples include, a d.c. model considering Schottky barrier limitation on carrier injection in short channel transistors and a small signal a.c. non-quasi-static model addressing parasitic capacitances in printed devices which exhibit large process tolerances [6]. The aim of our semi-empirical model is to help with the design of flexible sensors and circuits implementing low-voltage OTFTs with multi-finger contacts based on DNTT and this paper represents the first step. The measured transistor transfer characteristics constitute the input data for the model that starts by producing the mathematical expression for the OTFT drain current as a function of the voltages applied on OTFT terminals. This drain current fitting procedure involves all transistor operating regimes including the subthreshold regime and the off-state. Afterwards one can model the drain current for d.c. and low-frequency a.c. conditions and output voltage of a common-source amplifier.

## III. RESULTS AND METHODOLOGY

A compact model proposed in [7] served as a foundation for the model used in this work. Similar to [7], the transistor dimensions contribute via W and L, with no special provisions made for the source/drain finger geometry. In addition, the following simplifications were performed: (a) the number of empirical/fitting parameters was reduced from 5 to 4, and (b) the source/drain contact resistance was neglected. The model developed in Matlab Simulink environment computes the OTFT drain current based on a set of measured transfer characteristics. Eq. (1) defines the modeled drain current  $I_D$

$$I_{D} = \frac{W}{L\left(1 - \frac{\Delta L}{L}\right)} \cdot \frac{\mu_{o}}{\left(\frac{V_{SS}}{2 + \gamma}\right)^{\gamma}} \cdot C \cdot \left[\frac{\left(\frac{V_{SS} \ln\left\{1 + \exp\left[\frac{V_{G} - V_{T} - V_{S} - (V_{G} - V_{S})\delta_{VT}}{V_{SS}}\right]\right\}}{\gamma + 2}\right]^{(\gamma + 2)}}{\gamma + 2} - \frac{\left(\frac{V_{SS} \ln\left\{1 + \exp\left[\frac{V_{G} - V_{T} - V_{D} - (V_{G} - V_{D})\delta_{VT}}{V_{SS}}\right]\right\}}{\gamma + 2}\right]}{\gamma + 2}\right]}{\gamma + 2}$$

(1)

where

$$\frac{\Delta L}{L} = \lambda (V_D - V_S) \cdot \frac{(V_D - V_S) + V_{GT\Delta L}}{2(V_D - V_S) + V_{GT\Delta L}} \ge 0$$

(2)

Here  $V_G$ ,  $V_D$ , and  $V_S$  are voltages on the gate, drain and source terminals, W is the channel width, L the channel length, C the gate dielectric capacitance and  $V_T$  the threshold voltage. The specific transistor determines W, L, C and  $V_T$ , as well as the transistor off-current. In addition,  $V_{GT\Delta L} = \max(V_G - V_T, 0.01 V)$  and  $\lambda = 0.02$ . The four empirical/fitting parameters are the subthreshold slope voltage  $V_{ss}$ , mobility enhancement factor  $\gamma$ , low-field mobility  $\mu_o$ , and threshold voltage bias sensitivity  $\delta_{VT}$ . To compute these parameters an objective function, defined as the mean squared error of the measured and fitted data, was minimized using a genetic algorithm.

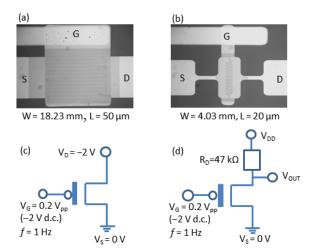

The OTFT data used to develop and test the model were taken from the prior experiments performed with two types of multi-finger OTFTs shown in Figs. 1(a) and 1(b). [1] These low-voltage bottom-gate, top-contact p-channel OTFTs based on DNTT were fabricated either on glass (Ossila) or PEN (Optfine, DuPont Teijin) substrates following the procedure described in [8]. The testing of the model was performed in 3 steps, each time producing a comparison with the measured data. Initially, the transistor transfer and output characteristics were simulated, next the a.c. drain currents for 1 Hz sinusoidal gate voltage were produced, and finally the output voltages of the common-source amplifier were modeled.

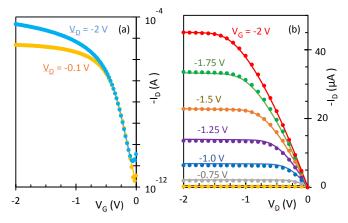

Figure 2 shows the measured and simulated transfer and output characteristics of a wide-gate transistor with W = 17.12 mm and  $L = 46.15 \mu$ m in linear and saturation regimes. As shown, the developed model is able to replicate the electrical performance of the transistor with high accuracy.

Fig. 1: Wide-gate (a) and narrow-gate (b) transistors, transconductance measurement (c), and transistor common-source amplifier (d).

Fig. 2: Transistor transfer (a) and output (b) characteristics. The points are the measured data and solid lines are the model.

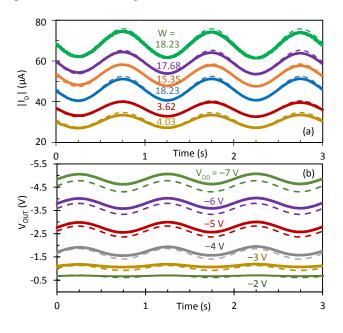

The a.c. transistor performance (Fig. 1(c)) and the output from the common-source amplifier (Fig. 1(d)) were simulated and the results are shown in Figs. 3(a) and 3(b) respectively. In addition, the peak-to-peak values of the measured and simulated drain current of six transistors with different W and L are summarized in Table I. The table also shows the comparison of the peak-to-peak output voltages of the transistor amplifier for different  $V_{DD}$ . Regarding the a.c.  $I_D$ , all simulated peak-to-peak values were slightly greater than the experimental values, resulting in error values ranging from 1.7% to 11.6%. Regarding the output voltage of Fig. 3(b) the error in the peak-to-peak voltage increased with decreasing  $V_{\rm DD}$ , resulting in the highest percentage error for  $V_{\rm DD} = -2$  V. Overall, the simulated peak-to-peak output voltages were slightly higher when compared to the measured ones. This may result from the fact that only transfer characteristics in saturation regime ( $V_{\rm DS} = -2$  V) were available for the simulations shown in Fig. 3, while transfer characteristics in both the linear ( $V_{\rm DS} = -0.1$  V) and saturation regimes ( $V_{\rm DS} = -2$  V) were available for the simulations in Fig. 2. Consequently, the error is increased when the transistor operates in the linear regime.

Fig. 3: A.c. drain current of Fig. 1(c) for transistors with various W (a) and output voltage of the transistor amplifier of Fig. 1(d) for various  $V_{DD}$  (b). The points correspond to the measured data and dashed lines to the model.

TABLE I.

PEAK-TO-PEAK VALUES AND ERROR OF MEASURED AND SIMULATED DATA IN FIGURE 3

|                              | Fig 3(a) |       |       |       |      |      |

|------------------------------|----------|-------|-------|-------|------|------|

| W (mm)                       | 18.23    | 17.68 | 15.35 | 18.23 | 3.62 | 4.03 |

| I <sub>Dpp</sub> meas (µA)   | 13.5     | 11.3  | 11.0  | 10.7  | 7.65 | 6.46 |

| I <sub>Dpp</sub> model (µA)  | 14.1     | 11.6  | 11.2  | 11.8  | 7.80 | 7.21 |

| Error (%)                    | 4.3      | 2.3   | 1.7   | 9.5   | 2.0  | 11.6 |

|                              | Fig 3(b) |       |       |       |      |      |

| $V_{DD}\left(V ight)$        | -2       | -3    | -4    | -5    | -6   | -7   |

| V <sub>OUTpp</sub> meas (V)  | 0.04     | 0.13  | 0.39  | 0.45  | 0.45 | 0.45 |

| V <sub>OUTpp</sub> model (V) | 0.10     | 0.21  | 0.44  | 0.47  | 0.47 | 0.48 |

| Error (%)                    | 148.8    | 63.0  | 13.4  | 3.7   | 4.1  | 5.5  |

In summary, compact modeling was successfully applied to multi-finger OTFTs with high transconductance. While the model reproduces the OTFT d.c. characteristics well, additional work is needed to improve the accuracy of the lowfrequency a.c. measurements in the future.

### ACKNOWLEDGMENT

This project has received funding from the European Union's Horizon 2020 research and innovation program under the Marie Skłodowska-Curie grant agreement No 734331

### References

- Al Ruzaiqi, A., Ishaku, A. A., Gleskova, H. (2018). Organic thin film transistors with multi-finger contacts as voltage amplifiers. *IEEE Access*, 6, 43770-43775.

- [2] Shur, M., Hack, M., Shaw, J. G. (1989). A new analytical model for amorphous silicon thin-film transistors, J. Appl. Phys., 66(7), 3371-3380.

- [3] Kim, C., Bonnassieux, Y., Horowitz, G. (2014). Compact DC modeling of organic field-effect transistors: Review and perspectives, *IEEE Trans. Electron Devices*, 61(2), 278-287.

- [4] Estrada, M., et al. (2010). Modeling the behavior of charge carrier mobility with temperature in thin-film polymeric transistors, *Microelectronic Engineering*, 87(12), 2565-2570.

- [5] Zaki, T., et al. (2014). Accurate capacitance modeling and characterization of organic thin-film transistors, *IEEE Transactions on Electron Devices*, 61(1), 98-104.

- [6] Valletta, A., et al. (2017). A DC and small signal AC model for organic thin film transistors including contact effects and non quasi static regime, *Organic Electronics*, 41, 345-354.

- [7] Marinov, O., Deen, M., Zschieschang, U., Klauk, H. (2009). Organic thin-film transistors: Part I - compact DC modeling. *IEEE Transactions* on Electron Devices, 56 (12), 2952-2961.

- [8] Hannah, S., et al. (2016). Interplay between vacuum-grown monolayers of alkylphosphonic acids and the performance of organic transistors based on dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene. ACS Appl. Mater. & Interfaces 8 (38), 25405-25414.