#### Compilation and Synthesis for Fault-Tolerant Digital Microfluidic Biochips

Alistar, Mirela

*Publication date:* 2014

Document Version Publisher's PDF, also known as Version of record

Link back to DTU Orbit

*Citation (APA):* Alistar, M. (2014). *Compilation and Synthesis for Fault-Tolerant Digital Microfluidic Biochips*. Technical University of Denmark. DTU Compute PHD-2014 No. 332

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

### Compilation and Synthesis for Fault-Tolerant Digital Microfluidic Biochips

Mirela Alistar

Kongens Lyngby 2014 IMM-PhD-2014-332

Technical University of Denmark Department of Applied Mathematics and Computer Science Matematiktorvet, building 303B, 2800 Kongens Lyngby, Denmark Phone +45 4525 3351 compute@compute.dtu.dk www.compute.dtu.dk IMM-PhD-2014-332

## Summary

Microfluidic-based biochips are replacing the conventional biochemical analyzers, by integrating all the necessary functions for biochemical analysis using microfluidics. The digital microfluidic biochips (DMBs) manipulate discrete amounts of fluids of nanoliter volume, named droplets, on an array of electrodes to perform operations such as dispensing, transport, mixing, split, dilution and detection.

Researchers have proposed compilation approaches, which, starting from a biochemical application and a biochip architecture, determine the allocation, resource binding, scheduling, placement and routing of the operations in the application. During the execution of a bioassay, operations could experience transient faults, thus impacting negatively the correctness of the application. We have proposed both offline (design time) and online (runtime) recovery strategies. The online recovery strategy decides the introduction of the redundancy required for fault-tolerance. We consider both time redundancy, i.e., re-executing erroneous operations, and space redundancy, i.e., creating redundant droplets for fault-tolerance. Error recovery is performed such that the number of transient faults tolerated is maximized and the timing constraints of the biochemical application are satisfied.

Previous work has assumed that the biochip architecture is given, and most approaches consider a rectangular shape for the electrode array, where operations execute on rectangular "modules" formed of electrodes. However, non-regular application-specific architectures are common in practice. Hence, we have proposed an approach to the synthesis of application-specific architectures, such that the cost is minimized and the timing constraints of the application are satisfied.

We propose an algorithm to build a library of non-regular modules for a given applicationspecific architecture, so that the area of a non-regular application-specific biochip can be used effectively. During fabrication, DMBs can be affected by permanent faults, which may lead to the failure of the application. Our approach introduces redundant electrodes to synthesize fault-tolerant architectures aiming at increasing the yield of DMBs. We also propose a method to estimate, at design time, the application completion time in case of permanent faults in order to verify if an application can be successfully run on the architecture.

The proposed approaches were evaluated using several real-life case studies and synthetic benchmarks.

## Resumé

Mikrofluidiske biochips erstatter i stigende grad konventionelle biokemiske analyser ved at integrere alle nødvendige operationer i den biokemiske analyse på en enkelt biochip. Digitale Mikrofluidiske Biochips (DMBs) manipulerer små diskrete mængder væske i størrelsesordnen nanoliter, kaldet dråber (eng., droplets), på et array af elektroder, for at udføre operationer så som: dosering, transport, blanding, opsplitning, fortynding og detektering.

Forskere har foreslået en samlet design proces, der startende fra en biokemisk applikation (bioassay) og en biochip arkitektur, fastsætter allokering, resurse binding, afviklings rækkefølge, placering og transport, af de i applikationen anvendte operationer. Under eksekveringen af bioassayet kan operationerne blive udsat for transiente fejl, hvilket kan påvirke nøjagtigheden af operationer og i værste fald betyde at applikationen leverer et forkert resultat. Vi har udviklet både offline (dvs. under design processen) og online (dvs. under eksekvering) fejlkorrektionsmetoder. Online fejlkorrigering beslutter den nødvendige redundans, der sikre tilstrækkelig fejltolerance. Vi håndterer både tids-redundans, dvs., genberegning af fejlende operationer, og fysisk-redundans, dvs., dublering af dråber. Fejlrettelse udføres således, at antallet af transiente fejl, der kan accepteres, maksimeres, samtidig med at tidskrav for den biokemiske applikation overholdes.

Tidligere arbejder har antaget, at biochip arkitekturen er givet på forhånd, og de fleste tilgange antager en rektangulær form af elektrodearrayet, hvor operationer afvikles inden for et rektangulært set af elektroder, kaldet et "modul". Dog forekommer irregulære applikationsspecifikke arkitekturer ofte i praksis. Derfor har vi foreslået en udviklingsmetode til applikationsspecifike arkitekturer, der sikre at prisen minimeres og tidskravene for applikationen overholdes.

Vi foreslår en algoritme til at opbygge et bibliotek af ikke-rektangulære moduler til en given applikationsspecifik arkitektur, således, at arealet af irregulære applikationsspecifikke biochip kan udnyttes effektivt. Under fabrikation kan DMBs være udsat for permanente fejl, hvilket kan lede til at bioassayet fejler. Vi foreslår også en metode der, i tilfælde af permanente fejl, kan estimere tiden for færdiggørelsen af applikationen, under selve designprocessen. Vi kan således verificere, at applikationen kan afvikles på den fejlbehæftede arkitektur.

Den udviklingsmetode er blevet evalueret på adskillige virkelige case-studier og syntetiske benchmarks.

### Preface

This thesis was prepared at the Department of Applied Mathematics and Computer Science, Technical University of Denmark in fulfillment of the requirements for acquiring the Ph.D. degree in computer engineering.

The thesis deals with optimization methods for the compilation and synthesis of fault-tolerant digital microfluidic biochips.

The work has been supervised by Associate Professor Paul Pop and co-supervised by Professor Jan Madsen.

Lyngby, 31 March 2014

Mirela Alistar

## Papers included in the thesis

- Mirela Alistar, Elena Maftei, Paul Pop, and Jan Madsen. Synthesis of biochemical applications on digital microfluidic biochips with operation variability. *Symposium on Design Test Integration and Packaging of MEMS/MOEMS*, pages 350– 357, 2010. Published.

- Mirela Alistar, Paul Pop, and Jan Madsen. Online synthesis for error recovery in digital microfluidic biochips with operation variability. *Symposium on Design Test Integration and Packaging of MEMS/MOEMS*, pages 53–58, 2012. Published.

- Mirela Alistar, Paul Pop, and Jan Madsen. Application-specific fault-tolerant architecture synthesis for digital microfluidic biochips. *Asia and South Pacific Design Automation Conference*, pages 794–800, 2013. Published.

- Mirela Alistar, Paul Pop, and Jan Madsen. Operation placement for applicationspecific digital microfluidic biochips. *Symposium on Design Test Integration and Packaging of MEMS/MOEMS*, pages 1–6, 2013. Published.

- Mirela Alistar, Paul Pop, and Jan Madsen. Biochemical application compilation and architecture synthesis for fault-tolerant digital microfluidic biochips. *Lab-on-a-Chip World Congress*, 2013. Poster presentation.

- Paul Pop, Jan Madsen, Kasper Understrup, Mirela Alistar, and Wajid Hassan Minhass. Programming language and tools for multipurpose lab-on-a-chip plat-forms. *Lab-on-a-Chip European Congress*, 2014. Poster presentation.

- Mirela Alistar, Paul Pop, and Jan Madsen. Compilation and synthesis for faulttolerant digital microfluidic biochips. *Design Automation and Test in Europe Conference*, 2014. Poster presentation at PhD Forum. **Best poster award**.

• Mirela Alistar, Paul Pop, and Jan Madsen. Redundancy optimization for error recovery in digital microfluidic biochips. Under review in *Journal of Design Automation for Embedded Systems*, 2014.

## Acknowledgements

I thank Paul Pop, my super supervisor, for his dedication and constant effort to make my PhD years both lucrative and a valuable life experience. I am extremely grateful for his guidance, 24/7 availability and unlimited patience. I also thank Jan Madsen, my co-supervisor, for helping my research with insightful feedback and creative ideas.

I thank my colleagues for having someone to share late working nights at university and great laughter during lunch breaks. My gratitude goes also to my family and friends that had to endure endless technical monologues. I thank them for supporting my enthusiasm, for encouraging me in troubled times and for being proud of me.

Lastly, I dedicate this thesis to Abi. Little one, always learn to be smarter than life!

<u>x</u>\_\_\_\_\_

\_

### Contents

| Su | ımma   | у                                                                   | i         |

|----|--------|---------------------------------------------------------------------|-----------|

| Re | esumé  |                                                                     | iii       |

| Pr | eface  |                                                                     | v         |

| Pa | pers   | ncluded in the thesis                                               | <b>ii</b> |

| Ac | eknov  | ledgements                                                          | ix        |

| Al | obrev  | ations xv                                                           | ii        |

| No | otatio | IS X                                                                | ix        |

| 1  | Intr   | duction                                                             | 1         |

|    | 1.1    | Related work                                                        | 3         |

|    | 1.2    | Contributions                                                       | 8         |

|    | 1.3    | Thesis overview                                                     | 10        |

| 2  | Syst   |                                                                     | 13        |

|    | 2.1    | Biochip architecture model                                          | 13        |

|    |        | 2.1.1 Fault models                                                  | 15        |

|    | 2.2    | Operation execution                                                 | 18        |

|    |        | 2.2.1 Circular-route module                                         | 19        |

|    |        | 2.2.2 Worst-case operation execution overhead in case of permanent  |           |

|    |        | faults                                                              | 22        |

|    |        | 2.2.3 Estimation of operation execution in case of permanent faults | 24        |

|    | 2.3    | Biochemical application model                                       | 26        |

|    | 2.4    | Transient faults and fault-tolerance models                         | 27        |

|    |                    | 2.4.1<br>2.4.2 | Fault-Tolerant Sequencing Graph       Generalized Fault-Tolerant Application model | 28<br>30        |

|----|--------------------|----------------|------------------------------------------------------------------------------------|-----------------|

| •  | ъ.                 |                | ••                                                                                 |                 |

| 3  | <b>Desi</b><br>3.1 |                | hodology for DMBs                                                                  | <b>39</b><br>41 |

|    | 5.1                | 3.1.1          | lation of biochemical applications                                                 | 41              |

|    |                    | 3.1.1          | Allocation       Placement of operations                                           | 42<br>43        |

|    |                    | 3.1.2          | Binding and scheduling                                                             | 43              |

|    |                    | 3.1.3          | Routing                                                                            | 45              |

|    | 3.2                |                | ng a library of circular-route modules                                             | 45<br>46        |

|    | 5.2                | 3.2.1          | Determining a circular-route module                                                | 40              |

| 4  | Con                | milatio        | n for Error Recovery                                                               | 51              |

| •  | 4.1                | -              | compilation for error recovery                                                     | 52              |

|    |                    | 4.1.1          | Problem formulation                                                                | 53              |

|    |                    | 4.1.2          | Fault-tolerant compilation                                                         | 56              |

|    | 4.2                |                | compilation for error recovery                                                     | 59              |

|    |                    | 4.2.1          | Problem formulation                                                                | 60              |

|    |                    | 4.2.2          | Online error recovery strategy                                                     | 63              |

|    |                    | 4.2.3          | Recovery strategy example                                                          | 65              |

|    |                    | 4.2.4          | Assignment of redundancy for error recovery                                        | 67              |

|    |                    | 4.2.5          | Error recovery strategy with a CCD detection system                                | 73              |

|    | 4.3                | Experi         | mental results                                                                     | 75              |

| 5  | Synt               |                | Application-Specific Architectures                                                 | 83              |

|    | 5.1                |                | m formulation                                                                      | 83              |

|    | 5.2                | Archite        | ecture evaluation                                                                  | 91              |

|    | 5.3                | SA-bas         | sed architecture synthesis                                                         | 93              |

|    |                    | 5.3.1          | Worst-case application completion time analysis                                    | 94              |

|    | 5.4                | TS-bas         | sed architecture synthesis                                                         | 95              |

|    |                    | 5.4.1          | Application completion time estimation                                             | 98              |

|    |                    | 5.4.2          | Incremental build of a CRM library                                                 | 101             |

|    | 5.5                | Experi         | mental results                                                                     | 105             |

| 6  | Con                |                | s and Future work                                                                  | 111             |

|    | 6.1                | Conclu         | isions                                                                             | 111             |

|    | 6.2                | Future         | work                                                                               | 113             |

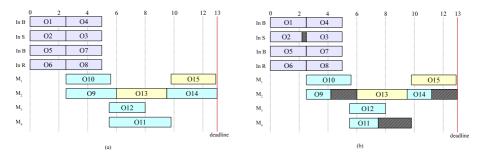

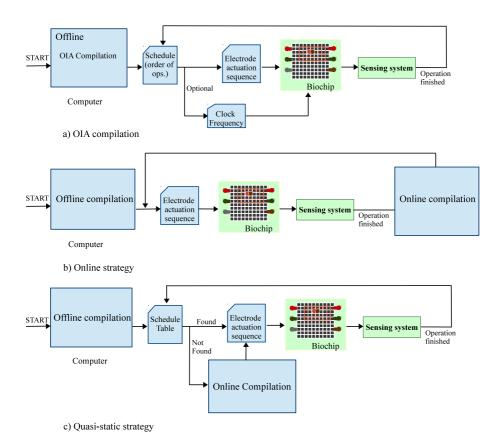

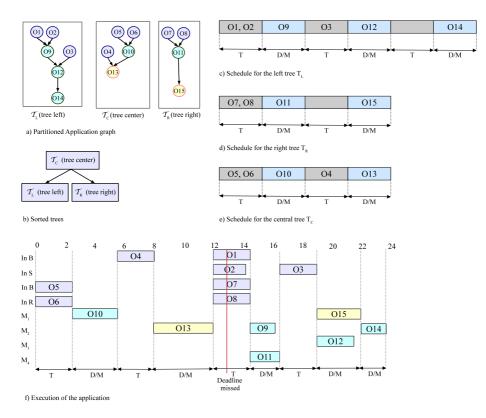

|    |                    | 6.2.1          | OIA strategy                                                                       | 116             |

|    |                    | 6.2.2          | Online compilation under execution time uncertainty                                | 119             |

|    |                    | 6.2.3          | Quasi-static scheduling                                                            | 120             |

| Bi | bliogi             | raphy          |                                                                                    | 123             |

# List of Figures

| 1.1  | Digital microfluidic biochip example [82]                          | 2  |

|------|--------------------------------------------------------------------|----|

| 1.2  | Example controller platform [7]                                    | 2  |

| 1.3  | Setup for running an application on a DMB                          | 3  |

| 1.4  | DMB for newborn screening [69]                                     | 7  |

| 1.5  | DMB for sample preparation [57]                                    | 7  |

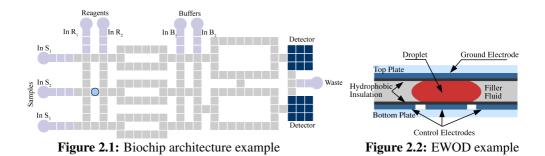

| 2.1  | Biochip architecture example                                       | 14 |

| 2.2  | EWOD example                                                       | 14 |

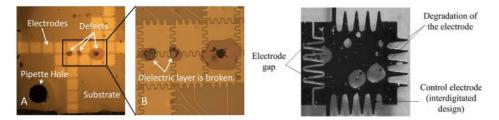

| 2.3  | Dielectric breakdown [34]                                          | 15 |

| 2.4  | Insulator degradation [83]                                         | 15 |

| 2.5  | Unbalanced split [20]                                              | 17 |

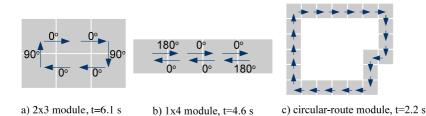

| 2.6  | Example of circular-route modules                                  | 20 |

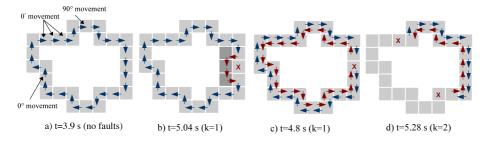

| 2.7  | Module decomposition approach for operation execution              | 21 |

| 2.8  | Worst-case operation execution time in case of permanent faults    | 23 |

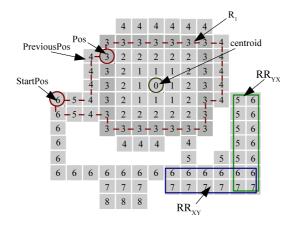

| 2.9  | Estimation of operation execution time in case of permanent faults | 24 |

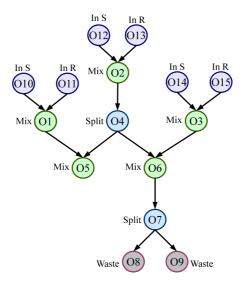

| 2.10 | Biochemical application graph $\mathcal{G}^0$                      | 27 |

| 2.11 | Fault-Tolerant Sequencing Graph                                    | 29 |

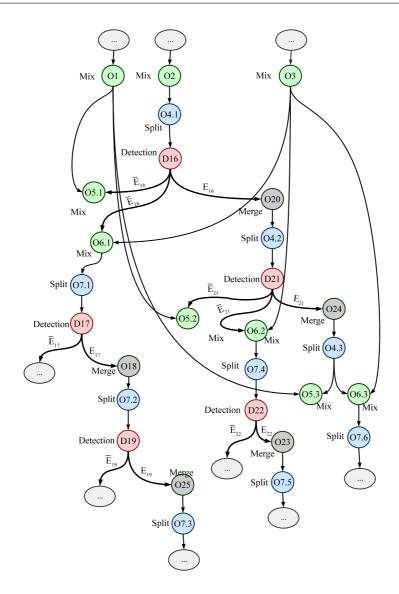

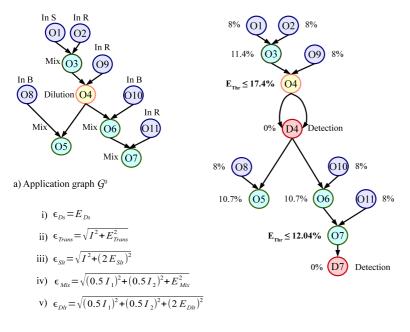

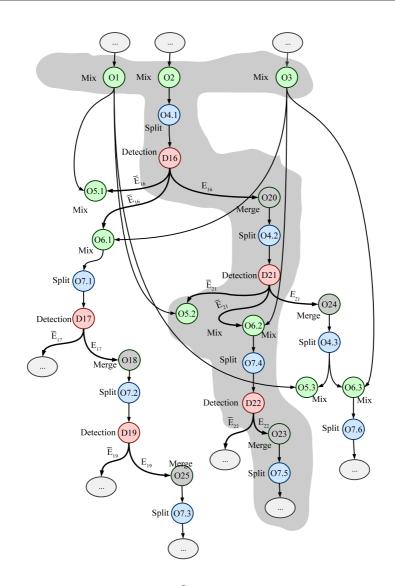

| 2.12 | Example application model, with error propagation and detection    | 32 |

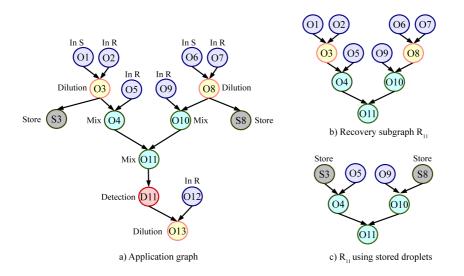

| 2.13 | Example of recovery subgraph                                       | 34 |

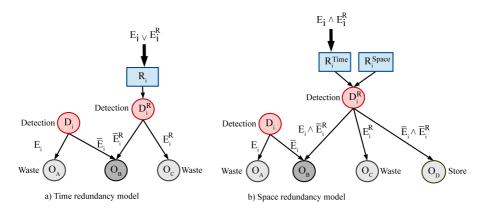

| 2.14 | Recovery using time vs. space redundancy                           | 35 |

| 2.15 | Example GFTA model for $\mathcal{G}^0$ in Fig. 4.11a               | 37 |

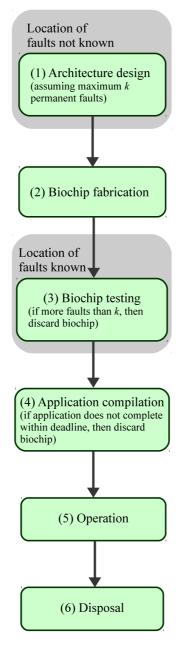

| 3.1  | Typical phases of a design methodology for DMBs                    | 40 |

| 3.2  | Example compilation task                                           | 42 |

| 3.3  | List Scheduling compilation                                        | 44 |

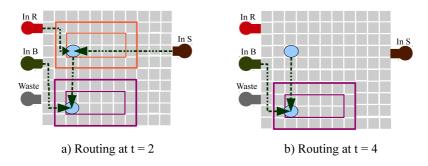

| 3.4  | Routing example                                                    | 45 |

| 3.5  | Algorithm for building a CRM library                               | 46 |

| 3.6  | Determining circular-route modules                                 | 47 |

| 3.7                                                                                                                   | Determine CRM algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

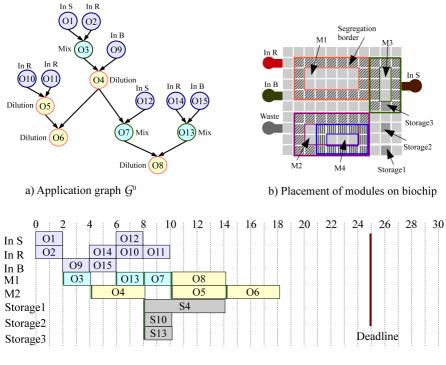

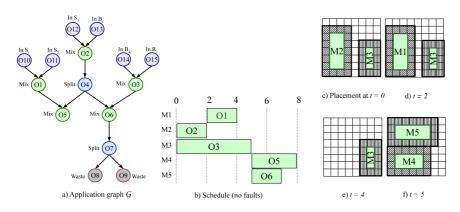

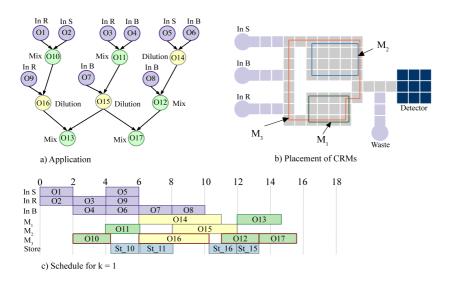

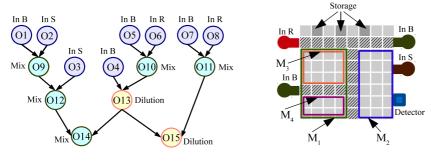

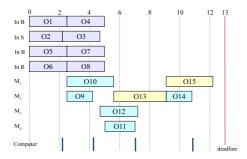

| 4.1                                                                                                                   | Compilation results (no faults)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                                                                                     |

| 4.2                                                                                                                   | SFS schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55                                                                                                     |

| 4.3                                                                                                                   | FTC schedule for faults in $O_4$ and $O_7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56                                                                                                     |

| 4.4                                                                                                                   | FTC schedule for faults in $O_7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 56                                                                                                     |

| 4.5                                                                                                                   | Fault-tolerant compilation example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57                                                                                                     |

| 4.6                                                                                                                   | FTSG $G^S$ for application in Fig. 4.1a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                                     |

| 4.7                                                                                                                   | Fault-tolerant scheduling algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 59                                                                                                     |

| 4.8                                                                                                                   | Motivational example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61                                                                                                     |

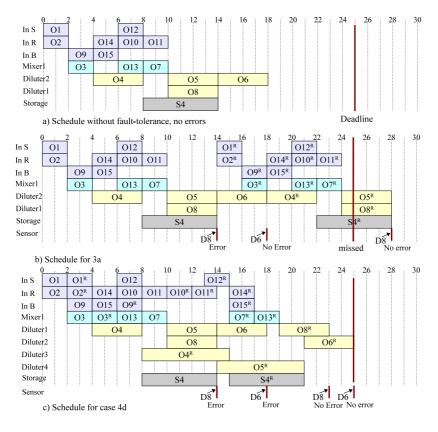

| 4.9                                                                                                                   | Schedules for various error scenarios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 63                                                                                                     |

| 4.10                                                                                                                  | Online error recovery strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                                                                     |

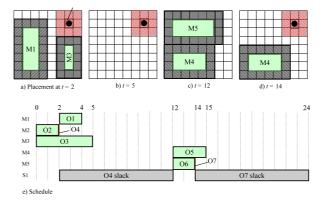

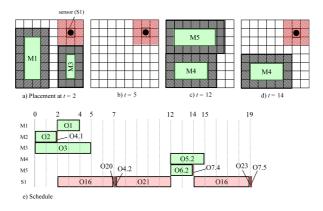

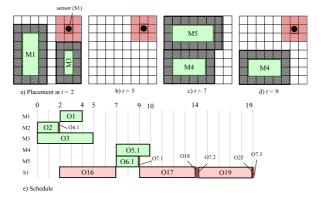

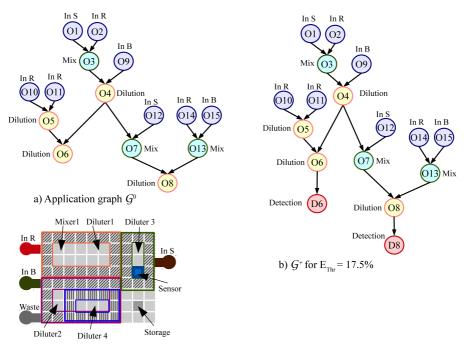

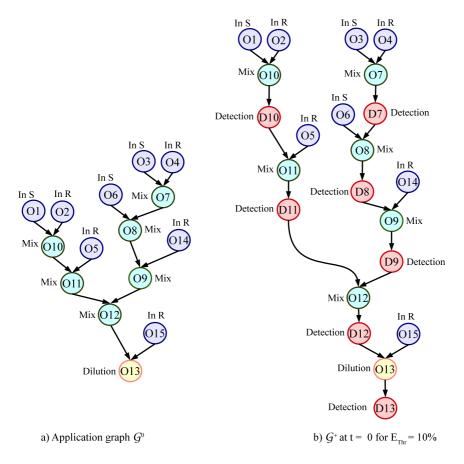

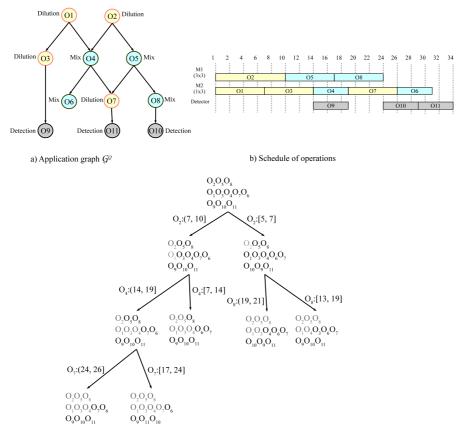

| 4.11                                                                                                                  | Initial offline redundancy assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                                                                                     |

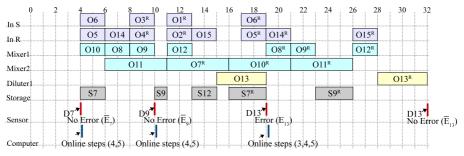

| 4.12                                                                                                                  | Schedules for execution of application from Fig. 4.11a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67                                                                                                     |

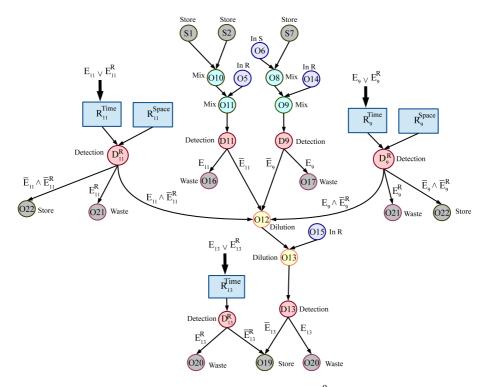

|                                                                                                                       | Redundancy Optimization Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68                                                                                                     |

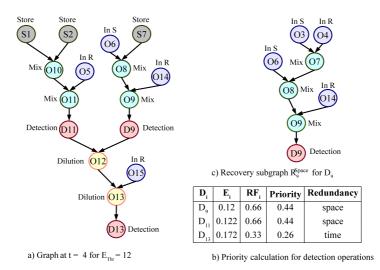

|                                                                                                                       | Online redundancy assignment at $t = 4$ for the application in Fig. 4.11a                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71                                                                                                     |

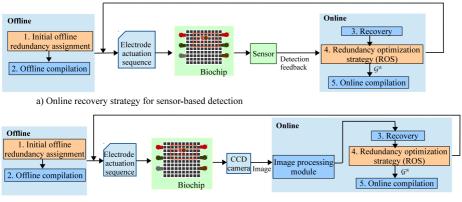

|                                                                                                                       | Determine recovery subgraph algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73                                                                                                     |

| 4.16                                                                                                                  | The execution of the application from Fig. 4.11a, with CCD detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                        |

|                                                                                                                       | system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 74                                                                                                     |

|                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                        |

| 5.1                                                                                                                   | Example application graph $G$ for architecture synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85                                                                                                     |

| 5.1<br>5.2                                                                                                            | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>85                                                                                               |

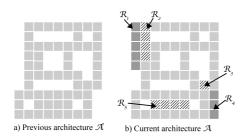

|                                                                                                                       | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                        |

| 5.2                                                                                                                   | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thickness                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85                                                                                                     |

| 5.2<br>5.3                                                                                                            | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thickness                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85<br>88                                                                                               |

| 5.2<br>5.3<br>5.4                                                                                                     | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89                                                                                         |

| 5.2<br>5.3<br>5.4<br>5.5                                                                                              | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and Routing                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89<br>91                                                                                   |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                       | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesis                                                                                                                                                                                                                                                                                                                                                                | 85<br>88<br>89<br>91<br>97                                                                             |

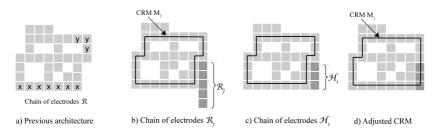

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and Routing                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89<br>91<br>97<br>99                                                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9                                                                  | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and RoutingCompilation example                                                                                                                                                                                                                                                                                                      | 85<br>88<br>89<br>91<br>97<br>99<br>100                                                                |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                  | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and RoutingCompilation exampleExample diversification moveIncremental Library Build algorithmAdjusting a CRM in case (1)                                                                                                                                                                                                            | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102                                                         |

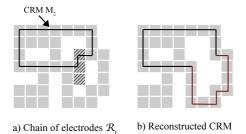

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                  | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and RoutingCompilation exampleExample diversification moveIncremental Library Build algorithmAdjusting a CRM in case (1)                                                                                                                                                                                                            | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103                                                  |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                                          | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and RoutingCompilation exampleExample diversification moveIncremental Library Build algorithmAdjusting a CRM in case (2)                                                                                                                                                                                                            | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103                                           |

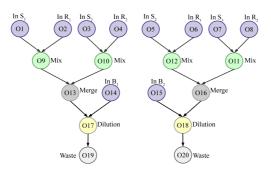

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>6.1                                   | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and RoutingCompilation exampleIncremental Library Build algorithmAdjusting a CRM in case (1)Reconstructing a CRM in case (2)Example application G                                                                                                                                                                                   | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103<br>104<br>114                             |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>6.1<br>6.2                            | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103<br>104<br>114<br>114                      |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>6.1                                   | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103<br>104<br>114<br>114<br>115               |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ $        | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103<br>104<br>114<br>114<br>115<br>116        |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ 6.5 \\ $ | Application-specific biochip architectureArchitecture synthesisRectangular routes of varying thicknessExample of neighboring architecturesTabu Search-based architecture synthesisFault-Aware List Scheduling and RoutingCompilation exampleExample diversification moveIncremental Library Build algorithmAdjusting a CRM in case (1)Reconstructing a CRM in case (2)Example application $\mathcal{G}$ Schedule using wcet values for operation executionSolutions to the problem of uncertainties in operation executionOIA compilation example | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103<br>104<br>114<br>114<br>115<br>116<br>118 |

| $5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\ 5.10 \\ 5.11 \\ 5.12 \\ 6.1 \\ 6.2 \\ 6.3 \\ 6.4 \\ $        | Application-specific biochip architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 85<br>88<br>89<br>91<br>97<br>99<br>100<br>102<br>103<br>103<br>104<br>114<br>114<br>115<br>116        |

xiv

### **List of Tables**

| 2.1  | Types of faults in DMBs [31]                                                                                                       | 16  |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Example module library $\mathcal{L}$ [76]                                                                                          | 19  |

| 2.3  | CRM library $\mathcal{L}$ for the architecture in Fig. 2.6a $\ldots \ldots \ldots \ldots$                                          | 20  |

| 4.1  | Module library $\mathcal{L}$ for FTC                                                                                               | 55  |

| 4.2  | Application completion times (for combinations of error scenarios and                                                              |     |

|      | redundancy scenarios)                                                                                                              | 62  |

| 4.3  | Comparison between SFS and FTC                                                                                                     | 76  |

| 4.4  | Results for IVD                                                                                                                    | 77  |

| 4.5  | Comparison between recovery techniques for PDNA                                                                                    | 77  |

| 4.6  | Comparison of dictionary-based error recovery [44] and ROS for CPA                                                                 | 78  |

| 4.7  | Comparison of dictionary-based error recovery [44] and ROS for IDP                                                                 | 79  |

| 4.8  | ROS results for $q = 1, 2$ and 3 faults (capacitive sensor)                                                                        | 80  |

| 4.9  | ROS results for $q = 1, 2$ and 3 faults (CCD detection)                                                                            | 80  |

| 5.1  | Example of component library $\mathcal{M}$ [7]                                                                                     | 84  |

| 5.2  | Fluidic library $\mathcal{F}$ for PCR [68]                                                                                         | 84  |

| 5.3  | Library $\mathcal{L}$ of rectangular modules $\ldots \ldots \ldots$ | 86  |

| 5.4  | Fault-tolerant CRM library $\mathcal{L}$ for the architecture in Fig. 5.8b                                                         | 101 |

| 5.5  | Component library                                                                                                                  | 105 |

| 5.6  | Fluidic library                                                                                                                    | 105 |

| 5.7  | Application-specific synthesis results obtained by SA                                                                              | 106 |

| 5.8  | Application-specific synthesis results obtained by TS                                                                              | 107 |

| 5.9  | Comparison between TS-based synthesis and SA-based synthesis                                                                       | 107 |

| 5.10 | Evaluation of the LSPR/FA-LSR compilations (no faults and rectangu-                                                                |     |

|      | lar architectures)                                                                                                                 | 108 |

| 5.11 | Increase in application completion time $(k = 0, 1, 2)$                                                                            | 108 |

|      | Evaluation of the CRM approach for compilation                                                                                     | 109 |

| 6.1 | Module library <i>L</i> with <i>wcet</i> values          | 115 |

|-----|----------------------------------------------------------|-----|

| 6.2 | Module library $\mathcal{L}$ for quasi-static scheduling | 120 |

# **Abbreviations**

| Abbreviation | Meaning                                     |

|--------------|---------------------------------------------|

| BFS          | Breadth-First Search                        |

| CCD          | Charged-Couple Device                       |

| CRM          | Circular-Route Module                       |

| CPA          | Colorimetric Protein Assay                  |

| DAG          | Directed Acyclic Graph                      |

| DMB          | Digital Microfluidic Biochip                |

| EWOD         | Electrowetting on Dielectric                |

| FA-LSR       | Fault-Aware List Scheduling and Routing     |

| FTC          | Fault-Tolerant Compilation                  |

| FTSG         | Fault-Tolerant Sequencing Graph             |

| GFTA         | Generalized Fault-Tolerant Application      |

| IDP          | Interpolation Dilution of a Protein         |

| ILB          | Incremental Library Build                   |

| IVD          | In-Vitro Diagnostics                        |

| LED          | Light-Emitting Diode                        |

| LS           | List Scheduling                             |

| LSPR         | List Scheduling, Placement and Routing      |

| OIA          | Operation-Interdependency-Aware compilation |

| PCR          | Polymerase Chain Reaction                   |

| PDNA         | sample preparation for Plasmid DNA          |

| ROS          | Redundancy Optimization Strategy            |

| RRT          | Rectangular Route of varying Thickness      |

| SA           | Simulated Annealing                         |

| SB           | Synthetic Benchmark                         |

| SFS          | Straighforward Scheduling                   |

| TS           | Tabu Search                                 |

xviii

# **Notations**

| Notation                                                    | Meaning                                                                 |

|-------------------------------------------------------------|-------------------------------------------------------------------------|

| q                                                           | number of transient faults in all types of operations                   |

| s                                                           | number of transient faults in split operations                          |

| k                                                           | number of permanent faults                                              |

| $\mathcal{G}^0, \mathcal{G}$                                | biochemical application graph without fault-tolerance                   |

| $\mathcal{G}^+$                                             | biochemical application graph $\mathcal{G}^0$ with the detection opera- |

|                                                             | tions                                                                   |

| $G^R$                                                       | biochemical application graph with redundancy                           |

| $\mathcal{G}^R \ \delta_\mathcal{G} \ \delta^s_\mathcal{G}$ | application completion time without fault-tolerance                     |

| $\delta_G^{\tilde{s}}$                                      | application completion time in case of <i>s</i> faults in split opera-  |

|                                                             | tions                                                                   |

| $\delta^k_{\mathcal{G}} \ p^1_{0^\circ}$                    | application completion time in case of k permanent faults               |

| $p_{0^{\circ}}^{f}$                                         | percentage towards operation completion for a forward                   |

|                                                             | movement of one electrode                                               |

| $p_{0^{\circ}}^{2}$                                         | percentage towards operation completion for a forward                   |

|                                                             | movement of at least two consecutive electrodes                         |

| $p_{180^\circ}$                                             | percentage towards operation completion for a backward                  |

|                                                             | movement                                                                |

| $p_{90^\circ}$                                              | percentage towards operation completion for a 90° turn                  |

| $p_{cycle}^0$                                               | percentage towards operation completion for a cycle when                |

|                                                             | there are no faults                                                     |

| $p_{cycle}^{f}$                                             | percentage towards operation completion for a cycle in case             |

| - cycle                                                     | of f permanent faults                                                   |

| Notation          | Meaning                                                    |

|-------------------|------------------------------------------------------------|

| $C_i$             | operation execution time without fault-tolerance           |

| $C_i^k$           | operation execution time in case of k permanent faults     |

| $O_i$             | operation                                                  |

| $O_{i,x}$         | the $x^{th}$ copy of the operation $O_i$                   |

| $O_i^R$           | redundant operation                                        |

| $D_i$             | detection operation                                        |

| $D_i^R$           | detection operation needed to detect an error during $R_i$ |

| $\vec{E_i}$       | condition of a fault occurrence                            |

| $\overline{E}_i$  | condition of a no fault occurrence                         |

| $E_{Mix}$         | intrinsic error limit for mixing operation                 |

| $E_{Ds}$          | intrinsic error limit for dispensing operation             |

| $E_{Slt}$         | intrinsic error limit for split operation                  |

| $E_{Trans}$       | intrinsic error limit for transport operation              |

| $E_{Dlt}$         | intrinsic error limit for dilution operation               |

| $I_i$             | input operation error limit                                |

| $E_{Thr}$         | error threshold                                            |

| $R_i$             | recovery subgraph for $O_i$                                |

| $R_i^{Space}$     | recovery subgraph for space redundancy                     |

| $R_i^{Time}$      | recovery subgraph for time redundancy                      |

| $M_i$             | circular-route module                                      |

| Ĺ                 | module library                                             |

| ${\mathcal A}$    | biochip architecture                                       |

| ${\mathcal F}$    | fluidic library                                            |

| ${\mathcal M}$    | component library                                          |

| 0                 | allocation                                                 |

| ${\mathcal B}$    | binding                                                    |

| $\mathscr{P}$     | placement                                                  |

| И                 | routing                                                    |

| S                 | schedule of operations                                     |

| In R              | dispensing reservoir for reagent                           |

| In S              | dispensing reservoir for sample                            |

| In B              | dispensing reservoir for buffer                            |

| n <sub>sns</sub>  | number of sensors                                          |

| $RF_i$            | reusability factor for operation $O_i$                     |

| $\mathcal{R}_{i}$ | chain of electrodes                                        |

| ${\mathcal E}$    | set of electrodes                                          |

| $e_i$             | electrode                                                  |

| TI                | initial temperature                                        |

| TL                | temperature length                                         |

| 3                 | cooling ratio                                              |

| W                 | penalty weight                                             |

### CHAPTER 1

## Introduction

Microfluidics, the study and handling of small volumes of fluids, is a well-established field, with over 10,000 papers published every year [56]. With the introduction at the beginning of 1990s of microfluidic components such as microvalves and micropumps, it was possible to realize "micro total analysis systems" ( $\mu$ TAS), also called "lab-on-a-chip" and "biochips", for the automation, miniaturization and integration of complex biochemical protocols [55].

The trend today is towards *microfluidic platforms*, which according to [55], provide "a set of fluidic unit operations, which are designed for easy combination within a well-defined fabrication technology", and offer a "generic and consistent way for minia-turization, integration, customization and parallelization of (bio-)chemical processes". Microfluidic platforms are used in many application areas, such as, *in vitro* diagnostics (point-of-care, self-testing), drug discovery (high-throughput screening, hit characterization), biotech (process monitoring, process development), ecology (agriculture, environment, homeland security) [14, 72].

Microfluidic platforms can be classified according to the liquid propulsion principle used for operation, e.g., capillary, pressure driven, centrifugal, electrokinetic or acoustic. In this thesis, we are interested in microfluidic platforms which manipulate the liquids as droplets, using electrokinetics, i.e., electrowetting-on-dielectric (EWOD) [60]. We call such platforms *digital microfluidic biochips* (DMBs).

Figure 1.1: Digital microfluidic biochip example [82]

Figure 1.2: Example controller platform [7]

DMBs integrate on-chip all the functions needed to complete biochemical applications such as bioassays, which measure the concentration of a specific constituent in a mixture (e.g., measuring the concentration of glucose in plasma, serum, urine and saliva [72]).

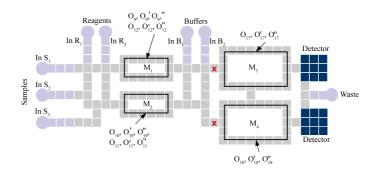

DMBs are typically modeled as an array of electrodes, where each electrode can hold a droplet, see Fig. 1.1 and 1.3 for example DMBs. Hence, DMBs are able to perform fluidic operations such as dispensing, transport, mixing, split, dilution and detection using droplets (discrete amount of fluid of nanoliters volume) [19, 22].

Immediate advantages of DMBs are *automation*—reducing the likelihood of human error, and *integration*—eliminating additional equipment for intermediate steps. Moreover, due to *miniaturization*, the reagent and sample consumption is lower and the bioassay time-to-result is shortened. By using smaller volumes of expensive reagents and hard-to-obtain samples, the costs are significantly reduced thus addressing an important concern of clinical laboratories. Moreover, faster reaction times are observed when using volumes at the microliter scale, making DMBs suitable for flash chemistry applications [89, 44]. The reduced size of DMBs contribute to their portability, making digital microfluidic platforms ideal candidates for near-patient and point-of-care testing [68].

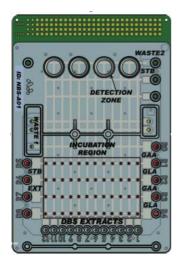

For example, digital microfluidic platforms have been proposed for newborn screening, a procedure that tests newborns for genetical diseases that can result in irreversible organ damage if not treated soon after birth. In order to screen for Pompe and Fabry diseases, a DMB needs a fraction of sample and reagents volumes required by standard methods [69]. The incubation time was reduced to less than 2 hours, resulting in a 10 times faster time-to-result than when using standard methods. Recently, Advanced Liquid Logic, Inc., proposed an advanced DMB that is able to screen 40 newborns at the same time [7].

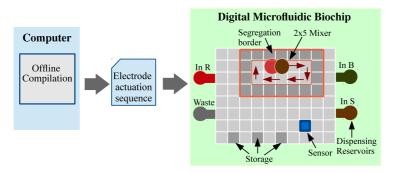

Figure 1.3: Setup for running an application on a DMB

In order to run a biochemical application, a DMB is typically used with a controller platform that has additional components such as sensing systems, charged-couple device camera-based detectors, magnetic bars, heaters, etc. [68]. The DMB is loaded with the input fluids (samples, reagents, buffers), then placed in the controller platform, which is connected to the computer.

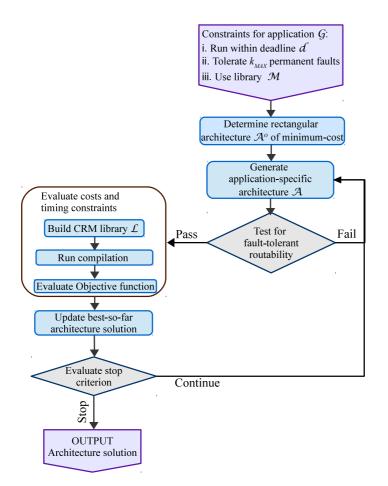

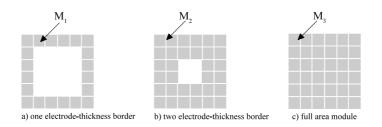

The flow of a biochemical application execution is schematically represented in Fig. 1.3. A control software that compiles the biochemical application is executed on the computer. The output of the control software is the "electrode actuation sequence", which controls the movement of droplets in order to run the biochemical application. The controller platform actuates the droplets and activates the additional components according to the electrode actuation sequence.

Fig. 1.2 shows the controller platform LSD100 developed by Advanced Liquid Logic, Inc., for Lysosomal Storage Enzyme Analysis [7]. Alternatively, the results of the control software can be stored on a flash drive which is plugged in the controller platform, thus increasing the portability of the system.

#### 1.1 Related work

Initially, bottom-up approaches have been used for the design of DMBs. However, due to the increase in the complexity of DMBs, top-down methodologies are more suitable, as they can easily scale for new designs [14]. There is a lot of research on methods for the design of biochips, see [13, 9] for surveys about this area. This section is not intended to give an overview of the research in this field. Instead, we mention only the research that is closely related to the methods proposed in the thesis.

Researchers have used the term "synthesis" to denote the tasks that determine the "electrode actuation sequence", which controls the movement of droplets to run the biochemical application. We will call these synthesis tasks *compilation*, to distinguish it from the architecture *synthesis*, which determines the biochip architecture for a specific biochemical application.

Researchers have initially assumed regular rectangular architectures and have focused on the compilation tasks. The compilation process is a NP-complete problem [14], which, consists of the following tasks: allocation, resource binding, scheduling, placement and routing, which are explained in the following. Biochemical applications can be modeled using programming languages such as BioCoder [8, 28]. However, most researchers have used sequencing graph models, where each node is an operation, and each edge represents a dependency [14]. Most of previous work has assumed that operations execute on predetermined areas of electrodes, named "modules", which are allocated from a given module library. Recently, [46] have proposed the use of additional equipment (e.g., sensing systems) to eliminate the need for characterizing a module library. As soon as the *binding* of operations to the allocated modules is decided, the scheduling algorithm determines the time duration for each bioassay operation, subject to resource constraints and precedence constraints imposed by the application. Next, the *placement* [90] of operations on the microfluidic array and the *routing* [15, 38] of droplets from one module to another have to be determined. In Chapter 3 we present examples of compilation.

Three of the compilation tasks are NP-complete problems: scheduling [79], placement [77] and routing [91]. Hence, in order to reduce the complexity of the compilation problem, researchers have initially separated the compilation tasks into "architecturallevel" compilation (i.e., modeling, allocation, binding and scheduling) and "physicallevel" compilation (i.e., placement and routing) [31].

At architectural-level, compilation approaches were proposed using Integer Linear Programing [73], modified List Scheduling algorithm [73] and metaheuristics such as Genetic Algorithms [73, 63]. At physical-level, [77, 74] proposed placement algorithms based on Simulated Annealing.

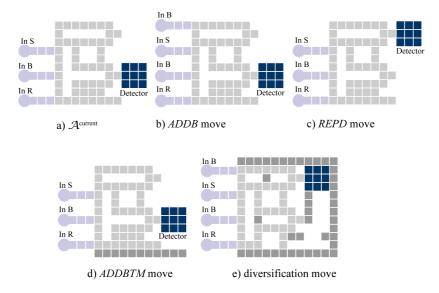

Next, researchers have considered unified approaches for the compilation of DMBs, which combine the architectural and physical levels. The integer linear programming formulation proposed in [54] derives optimal solutions for small applications. Near-optimal results in terms of application completion time were obtained by compilation implementations based on search metaheuristics such as Tabu Search [50] and Parallel Recombinative Simulated Annealing [14], which combines genetic algorithms and simulated annealing algorithms. List Scheduling-based compilations were proposed in [4, 45, 29, 27]. These compilations are faster and thus can be used to take decisions at runtime and to quickly evaluate an alternative architecture during architecture synthesis.

In related literature, several placement strategies have been proposed for rectangular architectures. In [77], a Simulated Annealing-based method is used to determine the placement of the operations on the biochip. A unified compilation and module placement, based on Parallel Recombinative Simulated Annealing, was proposed in [75]. Better results were obtained by using a T-Tree algorithm for placement [90] or by using a fast-template placement [10] integrated in a Tabu Search-based compilation [50]. A placement approach that minimizes droplet routing, when deciding the locations of the modules, is considered in [87]. Placement strategies based on virtual topology [27] were proposed for fast compilation approaches.

A lot of work has been done concerning the routing problem. [11] proposed a routing algorithm based on A\* search, which finds the optimal-length route, but works only when routing is possible. Hence, [80] proposed redoing the placement when routing fails and used modified Lee algorithm for routing. In [15], a "bypassibility" metric is proposed to assign droplet priorities such that deadlocks are avoided. However, in case of deadlock, "concession zones" are used to store the droplets and thus eliminate the deadlock.

A network-flow based routing algorithm was proposed in [91], which has two stages: (i) global routing, where a set of independent nets is determined and a rough routing path is generated for each droplet, and (ii) detailed routing, which routes each droplet using a negotiation-based algorithm. The routing strategy proposed in [36] determines a global routing track on which droplets prefer to move ordered by an entropy-based metrics. The routes were compacted in [36] using dynamic programming.

Cross-contamination is a frequent problem for the biochemical assays that use proteins [93]. To avoid cross-contamination, wash droplets are transported over the contaminated areas to clean the residues. Researchers have proposed methods to optimize the washing [92, 93] and routing algorithms to minimize the intersection of operations with contamination conflicts [37].

Several mixing and dilution techniques have been proposed for sample preparation [62, 65, 33], focusing on obtaining a desired concentration by using the byproduct droplets of operations already executed and thus reduce the waste. Researchers have also proposed techniques for fabrication [60, 25] and testing of DMBs [88, 81]. However, these topics (i.e., contamination, mixing/dilution algorithms, fabrication and testing) are orthogonal to the research work presented in this thesis.

Fault-tolerance to transient faults. During the execution of the bioassay, the volume of droplets can vary erroneously due to transient faults. The errors propagate throughout the entire application, affecting eventually the result of the bioassay. Biochemical applications have high accuracy requirements, determined by the acceptance range for the concentration of droplets. Example applications with accuracy requirements of less than  $\pm 10\%$  are drug discovery applications [64] and plasmid DNA preparation [41].

Past research has addressed the erroneous volume variation due to transient faults using re-execution and checkpointing as recovery techniques [1, 95]. The work in [95] addresses the volume variations in operations, by duplicating intermediate droplets of correct volumes and storing them at checkpoints. When an error is detected, the stored droplets are used in the recovery subroutine. The locations of the checkpoints and the recovery subroutines are determined offline and stored in a microcontroller memory. If an error is detected during runtime at a checkpoint, the microcontroller interrupts the bioassay, and transports the intermediate product droplets to the storage units; then the corresponding recovery subroutine is executed using a statically predetermined allocation and placement, which do not consider the current context. Consequently, the delays introduced by the recovery subroutines can lead to the application missing the deadline.

Hence, in [44] the authors propose a method to precompute and store a dictionary that contains recovery solutions for all combinations of errors. When an error is detected, the system looks in the dictionary for the corresponding recovery actuation sequence. Since the recovery solutions consider the current context, the delays due to recovery are minimized. However, taking into account all possible scenarios for any combinations of errors comes with high storage requirements. Hence, compression algorithms are needed to reduce the size of the dictionary in order to store it on the flash memory of the microcontroller.

In all mentioned approaches, the error recovery actions are determined *offline*, and are applied online when a fault is detected. Researchers have also proposed *online* approaches that determine the necessary recovery actions *during the execution of the biochemical application*, at the moment when an error is detected. Such online recovery approaches, some of which also perform online re-compilation to reconfigure the electrode actuation sequence, are possible because the biochemical application execution times are much slower compared to the control software execution.

The work in [32] addresses sample preparation and proposes dynamic error recovery to recreate online the desired target concentrations, using the stored intermediate droplets. A general approach, that compiles a new implementation containing the appropriate error recovery actions whenever errors are detected, is proposed in [45]. The online compilation re-computes the placement of operations and the droplets routes using a List-Scheduling based implementation.

In this thesis we propose both offline (design time) and online (runtime) recovery strategies. The online recovery strategy decides the introduction of the redundancy required for fault-tolerance. We consider both time redundancy, i.e., re-executing erroneous operations, and space redundancy, i.e., creating redundant droplets for fault-tolerance. Error recovery is performed such that the number of transient faults tolerated is maximized and the timing constraints of the biochemical application are satisfied.

Figure 1.4: DMB for newborn screening [69]

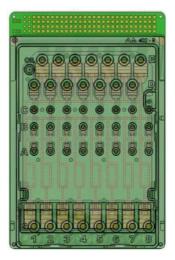

Figure 1.5: DMB for sample preparation [57]

Architecture synthesis. The physical architecture of a DMB consists of *physical* components, such as electrodes, sensors, detectors, heaters, actuators, reservoirs for dispensing and waste. Previous work assumes that the physical architecture of a DMB is given and focuses on the automation of the application execution.

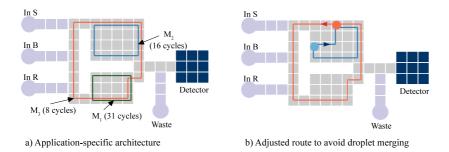

Moreover, most researchers use general-purpose architectures, which have a rectangular shape (Fig. 1.3). However, in practice, application-specific architectures which are non-regular (Fig. 1.1) are more common because they can significantly reduce the costs by including only the components that are necessary for the execution of the application.