#### Abstract

Title of dissertation:

COMPILER-DECIDED DYNAMIC

MEMORY ALLOCATION FOR SCRATCH-PAD

BASED EMBEDDED SYSTEMS

Sumesh Udayakumaran, Doctor of Philosophy, 2006

Dissertation directed by: Professor Rajeev Barua Department of Electrical and Computer Enginnering

In this research we propose a highly predictable, low overhead and yet dynamic, memory allocation strategy for embedded systems with scratch-pad memory. A *scratch-pad* is a fast compiler-managed SRAM memory that replaces the hardwaremanaged cache. It is motivated by its better real-time guarantees vs cache and by its significantly lower overheads in energy consumption, area and overall runtime, even with a simple allocation scheme.

Scratch-pad allocation methods primarily are of two types. First, softwarecaching schemes emulate the workings of a hardware cache in software. Instructions are inserted before each load/store to check the software-maintained cache tags. Such methods incur large overheads in runtime, code size, energy consumption and SRAM space for tags and deliver poor real-time guarantees, just like hardware caches. A second category of algorithms partitions variables at compile-time into the two banks. However, a drawback of such static allocation schemes is that they do not account for dynamic program behavior.

We propose a dynamic allocation methodology for global and stack data and program code that (i) accounts for changing program requirements at runtime (ii) has no software-caching tags (iii) requires no run-time checks (iv) has extremely low overheads, and (v) yields 100% predictable memory access times. In this method data that is about to be accessed frequently is copied into the scratch-pad using compiler-inserted code at fixed and infrequent points in the program. Earlier data is evicted if necessary. When compared to an existing static allocation scheme, results show that our scheme reduces runtime by up to 39.8% and energy by up to 31.3% on average for our benchmarks, depending on the SRAM size used. The actual gain depends on the SRAM size, but our results show that close to the maximum benefit in run-time and energy is achieved for a substantial range of small SRAM sizes commonly found in embedded systems. Our comparison with a direct mapped cache shows that our method performs roughly as well as a cached architecture in runtime and energy while delivering better real-time benefits.

## Compiler-Decided Dynamic Memory Allocation for Scratch-Pad Based Embedded Systems

by

Sumesh Udayakumaran

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy 2006

Advisory Committee:

Professor Rajeev Barua, Chair/Advisor Professor Donald Yeung Professor Shuvra Bhattacharrya Professor Peter Petrov Professor Chau Wen Tseng © Copyright by Sumesh Udayakumaran 2006 This dissertation is dedicated to my loved ones, without whose support I could not have completed this journey.

## ACKNOWLEDGMENTS

At times our own light goes out and is rekindled by a spark from another person. Each of us has cause to think with deep gratitude of those who have lighted the flame within us.

Albert Schweitzer

With these thoughts in mind, I embark on this humble duty to acknowledge different people who have contributed to that light in their own ways.

First and foremost, I acknowledge my parents, my brother and my sister-inlaw whose concern for my health and wellbeing, always drives me to work harder towards my goals.

I would also like to acknowledge those who have helped me to complete this dissertation. My advisor, Dr. Rajeev Barua, has been an outstanding motivator. I have learnt several important aspects of research from him, including technical writing and preparing presentations. But most of all, I am extremely indebted to him for all the valuable time he spent discussing my research and his help with various publications and presentations.

I would also like to thank my committee members who gave valuable feedback on my dissertation.

I also wish to thank several of my colleagues. I am most thankful to Angelo Dominguez, whose help with the infrastructure was extremely invaluable. I am grateful to Surupa Biswas, Tom Carley, Steve Haga, Bhuvan Midha, Nghi Nguyen, Mathew Simpson for their help with paper reviews and comments on my presentations. I am also indebted to several of my fellow PhD friends – Brinda Ganesh, Ankush Verma, Wanli liu, Sadagopan Srinivas – for their various inputs to my dissertation.

Doing my PhD has been a tremendous learning experience for me. The 4 years I have spent has given me the opportunity to learn and grow as a human being. The journey would not have been so joyful and enriching if not for my friends in and outside Maryland. I especially recognize the contribution of my friends – friends at Yoga classes, tennis/racquetball sessions and friends sharing thoughts on spirituality, politics and computer architecture – in keeping my spirits up through this journey.

Lastly, I believe the acknowledgement would be incomplete if I do not thank the light within all of us that leads and guides us to live constructively.

## TABLE OF CONTENTS

| 1        | Intr | oduction                                   | 1  |

|----------|------|--------------------------------------------|----|

|          | 1.1  | Our dynamic method for scratch-pad         |    |

|          |      | management                                 | 5  |

|          |      | 1.1.1 Scope and restrictions               | 7  |

|          |      | 1.1.2 Impact                               | 8  |

|          | 1.2  | Overview of thesis                         | 9  |

| <b>2</b> | Scra | atch-Pad Memory                            | 11 |

|          | 2.1  | Relevance of scratch-pad memory in         |    |

|          |      | embedded system design                     | 12 |

|          | 2.2  | Scratch-pad management                     | 15 |

|          |      | 2.2.1 Software caching                     | 16 |

|          |      | 2.2.2 Static allocation                    | 17 |

|          | 2.3  | Example architectures                      | 18 |

|          | 2.4  | Summary                                    | 20 |

| 3        | Dyr  | namic Allocation Overview                  | 21 |

|          | 3.1  | Designing a dynamic strategy               | 22 |

|          | 3.2  | Characteristics of our allocation strategy | 26 |

|          | 3.3  | Dynamic solution overview                  | 28 |

|          | 3.4  | Dynamic memory allocation parts            | 29 |

|          | 3.5  | Summary                                    | 31 |

| 4        | Dyr  | namic Allocation Algorithm                 | 32 |

|          | 4.1  | Deriving regions and timestamps            | 32 |

|          | 4.2  | Allocation of Global and Stack Objects     | 37 |

|          | 4.3  | Algorithm extension for code objects       | 47 |

| 5        | Har  | ndling Program Features                    | 52 |

|          | 5.1  | Join nodes                                 | 52 |

|          | 5.2  | Recursive functions                        | 55 |

|          | 5.3  | Goto statements                            | 55 |

| 6        | Lay  | out and Code Generation                    | 57 |

|          | 6.1  | Layout assignment                          | 57 |

|          | 6.2  | Code generation                            |    |

|    |      | 6.2.1 Code generation for accessing variable in scratch-pad        | 60  |

|----|------|--------------------------------------------------------------------|-----|

|    |      | 6.2.2 Memory transfer code                                         | 64  |

| 7  | Har  | ndling Pointers                                                    | 66  |

|    | 7.1  | Impact of invalid pointers on program                              |     |

|    |      | correctness                                                        | 67  |

|    |      | 7.1.1 Pointer translation                                          | 68  |

|    |      | 7.1.2 Address constraining                                         | 73  |

|    | 7.2  | Impact of function pointers on program                             |     |

|    |      | correctness                                                        | 75  |

|    | 7.3  | Impact of pointers on liveness                                     | 76  |

|    | 7.4  | Summary                                                            | 77  |

| 8  | Fra  | mework For Partial Variable Optimizations                          | 78  |

|    | 8.1  | Generating partial variables                                       |     |

|    |      | 8.1.1 Affine analysis for partial arrays                           |     |

|    |      | 8.1.2 Adapting structure splitting                                 |     |

|    |      | 8.1.3 Impact of loop transformations                               |     |

|    | 8.2  | Framework extensions                                               | 104 |

|    | 8.3  | Summary                                                            | 107 |

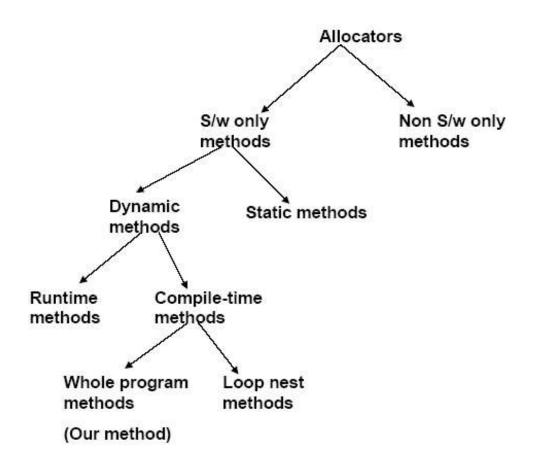

| 9  | Rel  | ated Work                                                          | 108 |

|    | 9.1  | Software methods                                                   | 109 |

|    |      | 9.1.1 Static methods                                               | 110 |

|    |      | 9.1.2 Dynamic methods                                              | 110 |

|    | 9.2  | Methods using hardware                                             | 121 |

| 10 | Res  | ults                                                               | 125 |

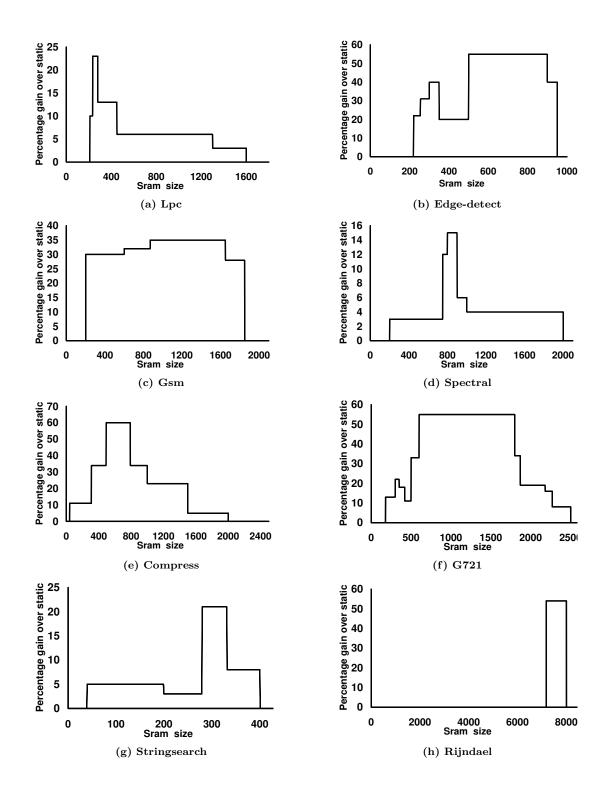

|    | 10.1 | Static method comparison                                           | 127 |

|    | 10.2 | Comparison with caches                                             | 148 |

|    | 10.3 | Results on dynamic method integrated with partial array handling . | 153 |

|    |      | Results on pointer handling                                        |     |

| 11 | Cor  | clusion and Future work                                            | 162 |

## LIST OF TABLES

| 10.1 | Application programs for comparison with static method                                              |

|------|-----------------------------------------------------------------------------------------------------|

| 10.2 | Useful range of dynamic method and run-time gain vs. static allocation.130                          |

| 10.3 | Program and region statistics                                                                       |

| 10.4 | Additional scratch-pad memory area required by static allocation to match runtime of dynamic method |

| 10.5 | Benchmark programs for our experiments on integrated algorithm 154                                  |

| 10.6 | Benchmarks and characteristics for testing pointer handling strategy. 159                           |

## LIST OF FIGURES

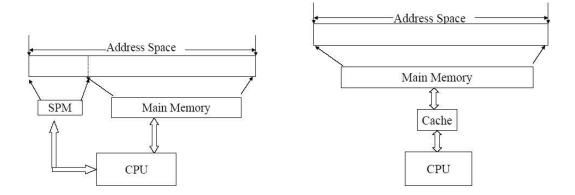

| 2.1 | Architecture with scratch-pad                                                                  | 12 |

|-----|------------------------------------------------------------------------------------------------|----|

| 2.2 | Architecture with cache                                                                        | 12 |

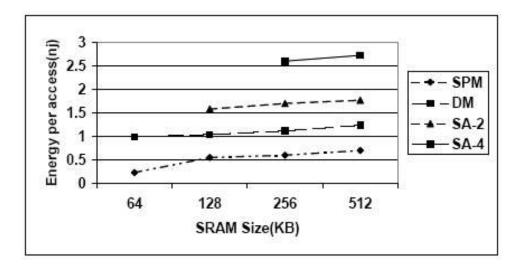

| 2.3 | Per-access energy comparison between scratch-pad memory and var-<br>ious cache configurations  | 14 |

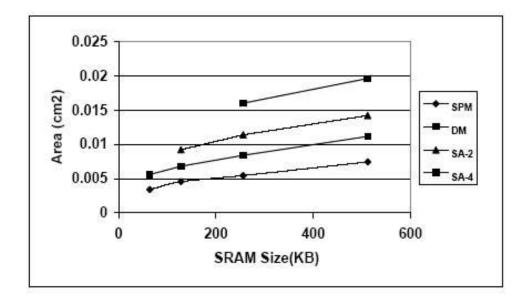

| 2.4 | Area comparison between scratch-pad memory and various cache con-<br>figurations.              | 14 |

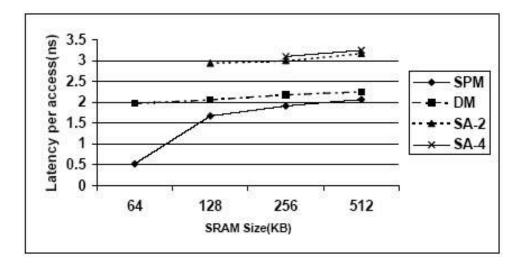

| 2.5 | Per-access latency comparison between scratch-pad memory and var-<br>ious cache configurations | 15 |

| 3.1 | Dynamic memory allocation methodology                                                          | 29 |

| 4.1 | Example showing a program outline                                                              | 34 |

| 4.2 | Example showing the DPRG showing nodes, edges & timestamps                                     | 35 |

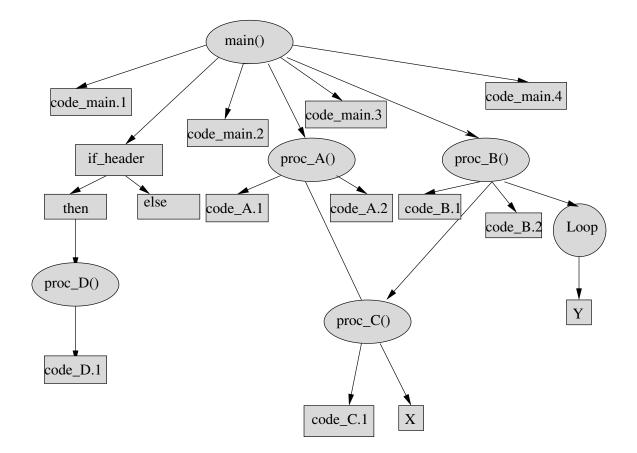

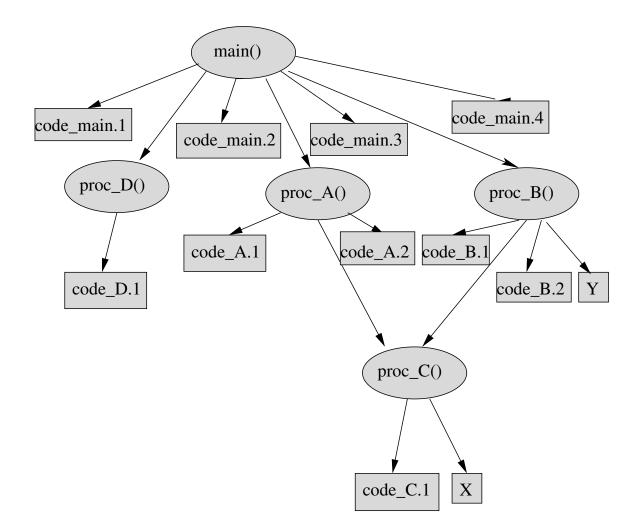

| 4.3 | Example DPRG with code nodes                                                                   | 49 |

| 4.4 | An example coalesced DPRG                                                                      | 50 |

| 7.1 | Code fragment with calls to the translate function for pointer p $\ldots$                      | 69 |

| 7.2 | Translation and retranslation function                                                         | 71 |

| 8.1 | Part of a DPRG with partial variables                                                          | 80 |

| 8.2 | An example loop with affine references                                                         | 91 |

| 8.3 | Example output of affine analysis phase                                                        | 92 |

| 8.4 | Structure splitting optimization                                                               | 98 |

| 9.1 Different kinds of scratch-pad allocators                                                                                                | )9 |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

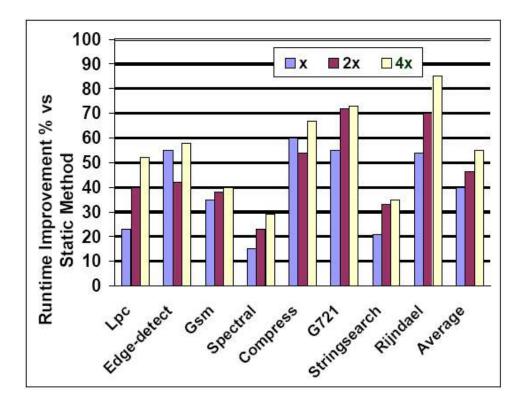

| 10.1 Runtime gain from our dynamic method vs. static method for differ-<br>ent SRAM sizes                                                    | 3  |

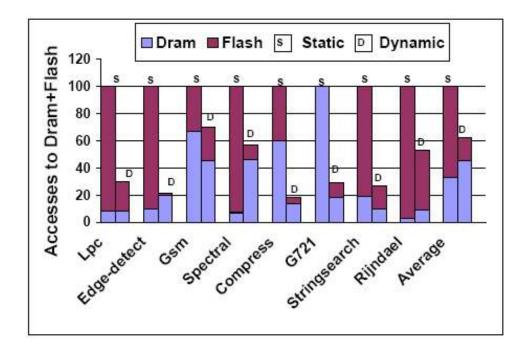

| 10.2 Percentage of memory accesses going to the DRAM and Flash for<br>each benchmark for the maximum benefit configuration                   | 35 |

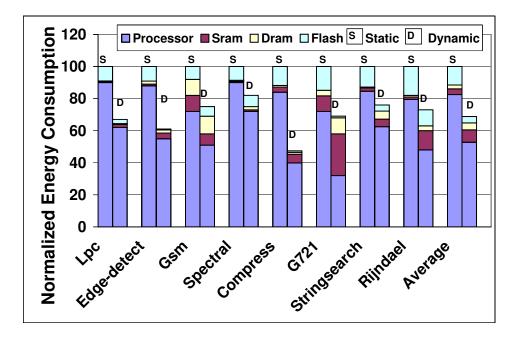

| 10.3 Reduction in energy consumption from dynamic method for the max-<br>imum benefit configuration                                          | 86 |

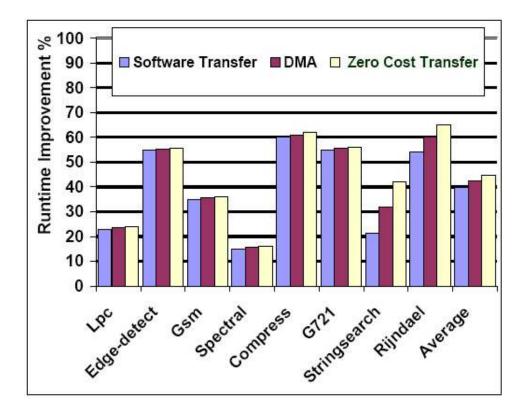

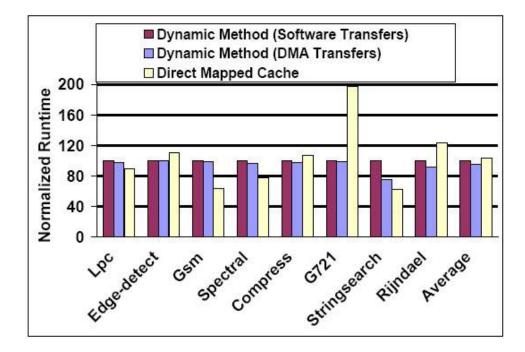

| 10.4 Run-time gain for different data-transfer methods for the maximum benefit configuration                                                 | 0  |

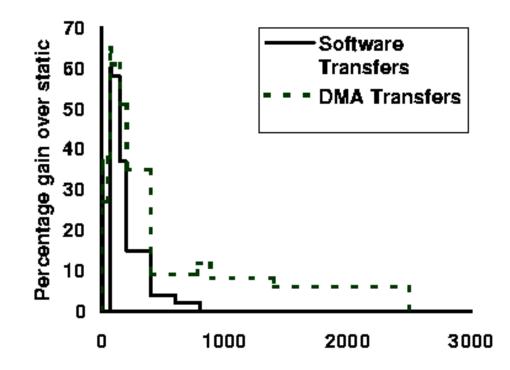

| 10.5 Run-time gain for different data-transfer methods $\ldots \ldots \ldots \ldots \ldots 14$                                               | 1  |

| 10.6 Effect of varying DRAM and Flash latencies on run-time gain from<br>our method for the maximum benefit configuration                    | 2  |

| 10.7 Comparison of our address assignment with perfect address assignment.14                                                                 | 5  |

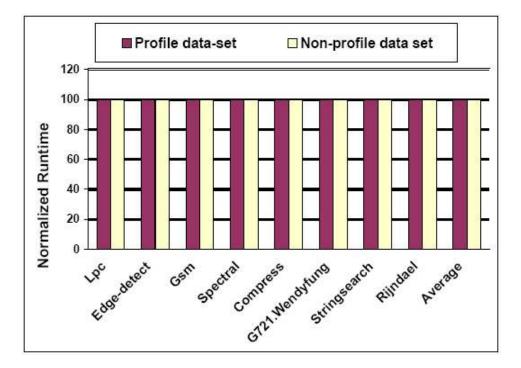

| 10.8 Runtime comparison of profiled data-set and non-profile data-sets 14                                                                    | 6  |

| 10.9 Normalized run time for a cache only and scratch-pad only architec-<br>ture measured for maximum benefit configuration                  | 17 |

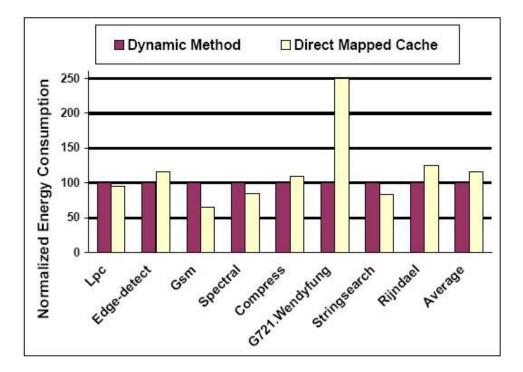

| 10.10Normalized energy consumption for a cache only and scratch-pad<br>memory only architecture measured for maximum benefit configuration14 | 8  |

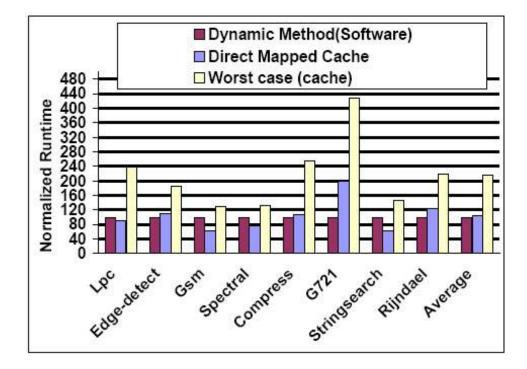

| 10.11Normalized runtime and worst-case runtime for cached architecture . 15                                                                  | 52 |

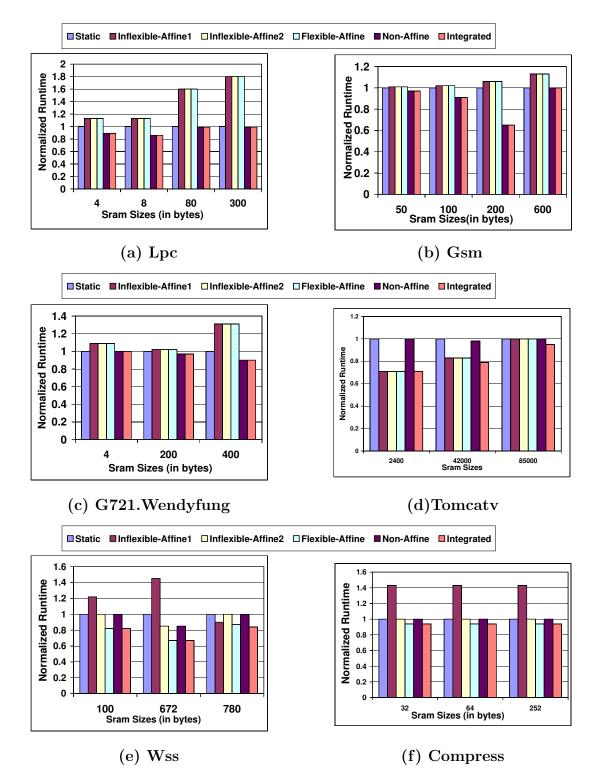

| 10.12Normalized runtime for our integrated method, different affine-only<br>methods, non-affine method and static method                     | 5  |

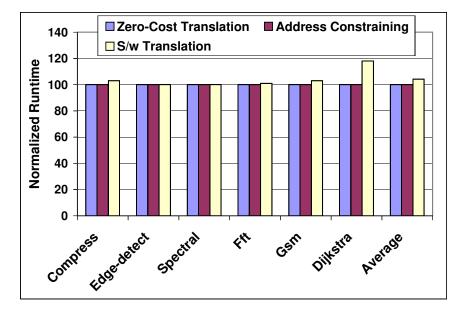

| 10.13Runtime overhead of pointer handling strategies                                                                                         | 59 |

## List of Algorithms

- 1 Algorithm for determining dynamic memory allocation . . . . . . . . 40

- 2 Algorithm to generate partial variables for affine references . . . . . 94

## Chapter 1

## Introduction

The growing use of computing power in different aspects of daily life has led to embedded systems becoming an important focus of computer architecture research today. In these systems, performance requirements are accompanied by other goals such as low power consumption and suitable form factor. Designers also often face the challenge of ensuring that the task finishes its execution within a specified time.

Performance also being an important requirement in embedded systems, the processor memory gap problem is also an issue in embedded systems. Towards bridging this gap, design of memory systems has received a lot of attention. Memory systems generally are organized using a variety of devices that serve different purposes. Devices like SRAM and flash memory are fast but expensive. On the other hand, devices like DRAM and magnetic disks are slower but being cheaper can be used to provide capacity. Designing a memory system therefore involves using small amounts of faster devices like SRAM along with slower devices like DRAM to obtain satisfactory performance while keeping a check on the overall dollar cost.

In desktops, the usual approach to adding SRAM is to configure it as a hard-

ware cache. The cache dynamically stores a subset of the frequently used data in on-chip memory. Caches have been a big success for desktops, a trend that is likely to continue in the future. Caching is essential in desktop systems for another reason. Using non-cached SRAM is usually not feasible for desktops; one reason is the lack of binary-code portability. Caching, due to its runtime nature, delivers an important benefit for desktop systems – that of transparency with respect to the cache parameters like the size and associativity. Allocations that are decided when the application is compiled require that the size of the on-chip memory be known; otherwise, they cannot reason about what variables will fit into it. This contrasts with cache allocation which is decided only at run-time; and hence does not require compile-time knowledge of the size of cache. Binary portability is valuable for desktops, where independently distributed binaries must work on any cache size.

Memory organization for embedded systems has other design constraints and issues. Apart from performance, memory organizations now also have to meet other embedded systems goals like real time guarantees, low power consumption and form factor restrictions. However, unlike in desktop systems allocation solutions do not have to provide binary portability. In embedded systems, software is configured along with the hardware in the factory and rarely changes thereafter. This means that embedded system designers can afford to customize the SRAM to a particular size to reap the additional cost savings from customization. This makes alternatives like deciding the allocation strategy at compile time possible. However, the appropriate allocation strategy depends on the environment and requirements of the embedded device. Thus, the choice of allocation strategy is an integral part of memory system design of en embedded system.

Runtime memory management strategies such as hardware caching are often not useful for embedded systems. Typically, embedded systems are used in resourceconstrained environments that places constraints like deterministic behavior, low power consumption and small form factor on them. Subsequently, for embedded systems the serious overheads of caches are less defensible. The extra tag hardware that accompanies a cache adds significant power, area and latency overhead; not to mention the non-deterministic behavior of the memory system in the presence of cache. A recent study [13] has shown that non-cached SRAM's use 34% lesser area and consume 40% lower power than a cache of the same capacity. These savings are significant since the on-chip cache typically consumes 25-50% of the processor's area and energy consumption, a fraction that is increasing with time [13]. Moreover, the cacti tool [24] shows that the access latency of caches is significantly lower than that of non-cached SRAM memory of the same capacity. So using a non-cached SRAM is an promising alternative for embedded systems. Such memory is also called scratch-pad memory. Given the power, cost, performance and real time advantages of scratch-pad, it is not surprising that scratch-pads are the most common form of on-chip SRAM in embedded CPUs today. Some examples of processors with scratchpad memory are the Intel IXP network processor, ARMv6 and ARM968E-S, IBM 440 and 405, Motorola's MCORE, 6812 and Dragonball, TI TMS-370, Hitachi's MS32R-32192 and SuperH-SH7050, Infineon XC166, Philips LPC2290, and Atmel AT91-C140; there are many others. Trends in recent embedded designs indicate that the dominance of scratch-pad will likely consolidate further in the future [13] [49].

Although many embedded processors with scratch-pad exist, using the scratchpad effectively has been a challenge. In contrast, caches have been effectively used in desktop systems for a long time. Central to the effectiveness of caches is their ability to maintain, at each time during program execution, the subset of data that is frequently used at that time in the fast memory. The contents of cache constantly change during runtime to reflect the changing working set of data across time. Unfortunately, two of the existing allocation approaches for scratch-pad – program annotations and the recent compiler-driven approaches [11, 12, 73] – are static allocators, *i.e.*, they do not change the contents of scratch-pad at runtime. This is a serious limitation. For example, consider the following thought experiment. Let a program consist of three successive loops, the first of which makes repeated references to array A; the second to B; and the third to C. If only one of the three arrays can fit within the scratch-pad, then any static allocation suffers DRAM accesses for two out of three loops. In contrast, a dynamic strategy can fit all three arrays in the scratch-pad at different times. Although this example is oversimplified, it intuitively illustrates the benefits of dynamic allocation.

In this thesis, we present a new compiler method for allocating three types of program objects – global variables, stack variables and program code – to scratchpad. The method's feature is that it is able to change the allocation at runtime while avoiding the overheads of runtime methods. The method (i) accounts for changing program requirements at runtime; (ii) has no tags like used by runtime methods; (iii) requires no run-time checks per load/store; (iv) has extremely low overheads; and (v) yields 100% predictable memory access times. In the rest of the chapter, we first outline our method. We then outline the layout of the thesis. Finally, we summarize the important contributions of the thesis.

## 1.1 Our dynamic method for scratch-pad

#### management

Our method is outlined as follows. The compiler analyzes the program to identify locations we call *program points* where it may be beneficial to insert code to copy a variable from DRAM into the scratch-pad. It is beneficial to copy a variable into scratch-pad if the latency gain from having it in scratch-pad rather than DRAM is greater than the cost of its transfer. A profile-driven cost model estimates these benefits and costs. The compiler ensures that the program data allocated to scratch-pad fits at all times by occasionally evicting existing variables in scratch-pad to make space for incoming variables. In other words, just like in a cache, data is moved back and forth between DRAM and scratch-pad, but under compiler control, and with no additional overhead.

Key components of our method are as follows. (i) To reason about the contents of scratch-pad across time, it helps to attach a concept of time to the above-defined program points. Towards this end, we introduce a new data structure called the *Data-Program Relationship Graph (DPRG)* which associates a *timestamp* with each program point. (ii) A detailed cost model is presented to estimate the runtime cost of any proposed data transfer at a program point. (iii) A compile-time heuristic is presented that uses the cost model to decide which transfers minimize the runtime.

**Program Code** Our base method can allocate global and stack objects. We also separately show how our method can also easily be extended to allocate program code objects. Although, code objects are accessed more heavily than data objects (one fetch per instruction), dynamic schemes like ours are not likely to be applicable in all cases for two reasons. First, compared to data caches the use of instruction caches is more feasible due to their effectiveness at much smaller sizes. So it is not uncommon to find instruction caches (but not data caches) especially in high end embedded systems like Motorola's STARCORE, MFC5xx and 68HC. Second, for low and medium end embedded systems code is typically stored in ROM/flash. An example of such a system is Motorola's MPC500. Unlike DRAM devices, ROM/flash devices have lower seek times (in the order of 75ns-120ns, 20 ns in burst/page mode) and power consumption. For low end embedded systems, this would mean an access latency of a cycle or two. For such low end embedded systems using ROM/Flash where cost is also a lot more important factor, speeding up accesses to code objects as compared to accesses to data objects in DRAM is not very attractive. Nevertheless, for high end systems, which store code in ROM/flash such as the Motorola MCORE and Motorola 6812, methods to speed up accesses to code can improve performance immensely. Our proposed extension for handling code would thus enable our dynamic method to be used for speeding up code accesses in such systems.

#### **1.1.1** Scope and restrictions

**Profile dependence** Our method is profile-dependent; that is, its improvements are dependent upon how representative the profile data set really is. *Indeed, all existing scratch-pad allocation methods, whether compiler-derived or programmer-specified, are inherently profile-dependent.* This cannot be avoided since they all need to predict which data will be frequently used. Further, our method does not require the profile data to be like the actual data in all respects; so long as the relative re-use trends between variables are similar in the profile and actual data, good allocation decisions will be made, even if the re-use factors are not identical. A regions gain may even be higher with non-profile data if its data re-use is more than in the profile data.

Heap data Our method does not allocate heap data in the program to the scratchpad. Programs with heap data still work; however, all heap data is allocated to DRAM and the global stack and program code can still use the scratch-pad using our method, but no SRAM acceleration is obtained for heaps. Heap data is difficult to allocate to the scratch-pad at compile-time because the total amount and lifetime of heap data is often data-dependent and therefore unknowable at compile-time. Software caching strategies [36, 59] can be used for heap, but they have significant overheads. Method for allocating heap data to scratch pad [32] can be easily integrated with our method; indeed that paper shows how.

#### 1.1.2 Impact

Here we briefly preview the benefits of adopting our method over both existing compile-time technologies like static allocation and hardware mechanisms like caching.

**Quantitative benefits** If adopted, the impact of this work will be a significant improvement in the cost, energy consumption, and runtime of embedded systems. Our results show up to 39.8% reduction in run-time for our method for global and stack data and code vs. an existing static allocation scheme. With hardware support for DMA, present in some commercial systems, the runtime gain increases to up to 42.3% respectively. The actual gain depends on the SRAM size, but our results show that close to the maximum benefit in run-time and energy is achieved for a substantial range of small SRAM sizes commonly found in embedded systems. Using an accurate power simulator, our method also shows up to 31.3% reduction in energy consumption vs. an existing static allocation scheme. Our method also does marginally better than a cached architecture both in runtime and energy consumption. Finally, integrating our method with optimizations for partial variable handling gives it ability to provide gains at much smaller SRAM sizes. At the same time, the method still remains generally applicable for a large variety of programs. The details of our results are provided in chapter 10.

**Real-time guarantees** Not only does our method improve run-time and energy consumption, it also improves the real-time guarantees of embedded code. Our method like all compiler-decided allocation methods, guarantees that the latency of

each memory instruction is known for sure. This translates into the behavior of the memory system becoming totally predictable, thus immensely aiding in obtaining a better WCET. Such real time benefits of scratch-pad have been observed before too [89]; by improving runtime our method aims to improve the WCET's more than the existing static methods.

## 1.2 Overview of thesis

This section gives an overview of the thesis. First, it summarizes the significant contributions of the thesis. Second, it gives an overview of the rest of the chapters.

**Contributions** Our thesis makes the following contributions.

- This research the first version of which was published in [83] represents the first solution to the problem of compile-time dynamic allocation of the scratch-pad memory using whole program analysis.

- To aid in a whole program analysis, the thesis introduces the notion of a timestamped representation of the program. Such a representation, we believe, can be useful in other region based optimizations.

- Towards making the solution comprehensive, the method can handle various program structures and data types like pointer variables.

- The thesis provides an extension of the base solution to also allocate code variables. This makes it a general solution capable of handling all non-heap variables.

- Further, the thesis extends the method to a framework that can incorporate a variety of optimizations that can create partial variables.

- To prove the effectiveness of the framework, the thesis presents an affine analysis based optimization that can exploit the presence of affine accesses to arrays in the code and create smaller partial variables.

- Finally, the method is implemented inside the gcc compiler as a proof of its implementation viability in a commercial compiler.

#### Organization

The rest of the thesis is organized as follows. Chapter 2 introduces scratch-pad memory and some aspects concerning its management. Chapter 3 overviews some basics of our method. Chapters 4 through chapter 6 describe the details of the method are described. Chapter 4 describes the precise method used to determine the memory transfers of global and stack variables at each program point. Chapter 5 describes how the algorithm is modified to correctly handle certain language features. Chapter 6 describes the layout of variables in scratch-pad and the process of code generation. Chapter 7 addresses how to handle programs with pointers. Chapter 8 extends the method to a framework that can use various partial-variable optimizations. It presents an example of how this can be done with the help of affine-analysis-based optimization. Chapter 9 overviews related work. Chapter 10 presents an evaluation of our methodology. Chapter 11 concludes and discusses some future direction.

## Chapter 2

## Scratch-Pad Memory

In this chapter, we discuss the concept of a scratch-pad memory. We further look at its benefits for embedded systems and importance of its management.

Scratch-pad memory refers to on-chip memory that has a separate address space as seen by the CPU. Such memory can be on chip SRAM or DRAM. The terminology, *perhaps*, owes its origin to the use of such memory by CPU in some superscalar processors for storing intermediate values or instructions, in other words used as a scratch-pad memory. They are also sometimes referred as on-chip memory or tightly coupled memory. The main characteristic of such memory is that it is an explicit part of the complete address space. In other words, while a cache memories address space is part or whole of the off-chip address space, a scratch-pad memory has an address space outside the off-chip memory. Figure 2.1 and Figure 2.2 illustrates this difference.

The rest of the chapter is organized as follows. Section 2.1 describes the benefits of using scratch-pad memory in an embedded device compared to using a hardware cache. Section 2.2 overviews the importance of appropriate scratch-pad

Figure 2.1: Architecture with scratch-pad. Figure 2.2: Architecture with cache.management technology with the help of two existing management technologies.Finally, section 2.3 illustrates a few architectures that use the scratch-pad.

# 2.1 Relevance of scratch-pad memory in embedded system design

Scratch-pad memories offer some inherent advantages that work towards making them a more favorable alternative in embedded system design. Banakar et al in [13] argued the case for use of scratch-pad in embedded systems. They reported significant area, energy and latency gains for scratch-pad based embedded systems. With the help of experiments similar to ones described by them, we show comparison between different cache configurations and scratch-pad memory in figures 2.3, 2.4 and 2.5. These figures respectively show how area, per-access energy cost and peraccess latency vary for different sizes and different associativities. The sizes vary from 64K to 512 K. The associativity is varied from direct mapped to associativity of 4. The cache line size is chosen as 8 words and the technology fixed at 0.5 micron. The numbers for the scratch-pad memory for a particular size is obtained from the numbers of a direct mapped cache for that size by subtracting the contribution of the tags.

From figure 2.3, we see that across all configurations, scratch-pad memory consumes the least energy per-access. Energy is an important criterion in embedded system design. Embedded systems are often battery powered. Due to weight, size and cost constraints, these systems have to carry batteries limited in their power availability. Power consumption also impacts the heat dissipation of the device, which is factor in the usability of the device. With a lower per-access energy cost, scratch-pad memory devices promise lower power consumption. The reduction in energy is further helped by the reduction in area. In figure 2.4, we see that scratchpad devices also use lesser area for the same SRAM size. Area reduction in turn leads to reduction in leakage current. Area reduction also means an improvement in the production efficiency of the chips.

Scratch-pad devices also have lower per-access latency. This is seen in figure 2.5. Although this by itself does not translate into overall performance benefit over caching, it offers the promise that good overall performance can be achieved.

These gains can be attributed to the absence of tags and other overhead bits in a scratch-pad memory. The lack of tags also means that the designer is free to choose his own memory management. Such a choice can be based on the specific needs of his system. This, as we will see, is very useful as allocation strategies can have significant impact on the constraints of an embedded system, particularly the predictability of the memory system. The predictability of the memory system is an important

Figure 2.3: Per-access energy comparison between scratch-pad memory and various cache configurations.

Figure 2.4: Area comparison between scratch-pad memory and various cache configurations.

Figure 2.5: Per-access latency comparison between scratch-pad memory and various cache configurations.

component in providing real time guarantees. A proper allocation strategy is also important in translating the inherent advantages of a scratch-pad memory to benefits for the system. The absence of tags positions scratch-pad based systems to better meet the goals of embedded systems compared to cached architectures.

## 2.2 Scratch-pad management

In order that the above said advantages of scratch-pad over cache translate into benefits for the system, the choice of scratch-pad allocation strategy is very important. Different strategies favor different criterion. We will now using two existing strategies, software caching and static allocation, see how a particular criterion is affected by allocation strategies.

#### 2.2.1 Software caching

Software caching [36, 59] represents a dynamic allocation strategy. This class of methods emulate the behavior of a hardware cache in software. In particular, a tag consisting of the high-order bits of the address is stored for each cache line in software. Before each load or a store, additional instructions are compiler-inserted to mask out the high-order bits of the address, access the tag, compare the tag with the high-order bits and then branch conditionally to hit or miss code. On a hit, in the hit code, using a mapping table the address is mapped to a new address in the scratch-pad where the data resides. Otherwise it is a cache miss and new data is brought into the scratch-pad. At that point, the index tables are updated to reflect the presence of this new data in the scratch-pad. Being a runtime strategy like caching, the strategy can adapt to runtime conditions. This makes it particularly suited for workloads whose runtime conditions continuously vary.

However, the use of the extra inserted instructions also leads to some drawbacks. Some methods are able to reduce the number of such inserted overhead instructions [59], but much of it remains, especially for non-scientific programs. Needless to say, the inserted code adds significant overhead, including (i) additional runtime; (ii) higher code size and dollar cost; (iii) higher data size and cost from tags; (iv) higher energy consumption; and (v) memory latency that is as unpredictable as hardware caches. Similar to a cache, it is hard to predict if the latency of a memory access would be that of a cache hit or a cache miss. Unpredictable memory latency makes such a scheme unsuitable for applications with hard real time deadlines.

#### 2.2.2 Static allocation

In static management of scratch-pad memory, the contents of the scratch-pad are decided at compile time itself. A simple way of doing this is based on programmer hints. Thus, the programmer provides annotations that tell if a variable is to be put into the scratch-pad address space or not. In such a scheme, it is the programmer responsibility to ensure that a particular variable fits completely inside the scratchpad address space. To make this process efficient, the selection strategy can be based on compiler analysis of the application. Examples of such static allocation strategies include [12, 13, 73, 77]. The advantage of a static scheme is that it does not involve any additional per-access overhead like that of software caching as no translation is required. So the inherent gains of a scratch-pad memory are still preserved. No translation gives scratch-pad memory yet another advantage that makes it suited for real time applications. For most memory memory access, its exact location is known and hence also known is its latency. This enables predicting the memory system behavior accurately.

A drawback of the static scheme is that being a static scheme, the allocation cannot adapt to changing runtime conditions. This makes it unsuitable for memory bound embedded applications where performance heavily depends on the program locality. Examples of such applications are high performance scientific and DSP applications. In spite of the drawback, researchers have shown for a limited set of benchmarks that the inherent advantages of a a scratch-pad over the cache can be translated to overall runtime, energy gains when compared to a cache [13].

17

## 2.3 Example architectures

Due to the numerous advantages offered by scratch-pad memory, it is dominant in embedded systems. The prevalence of scratch-pad memory in embedded systems is evident from the large variety of chips with scratch-pad memory available today in the market (*e.g.*, [1, 20, 41, 42, 60, 61, 81]).

A large number of systems exist that only use scratch-pad memory. Examples of such architectures include low-end chips such as the Motorola MPC500, Analog Devices ADSP-21XX, Motorola Coldfire 5206E; mid-grade chips such as the Analog Devices ADSP-21160m, Atmel AT91-C140, ARM 968E-S, Hitachi M32R-32192, Infineon XC166 and high-end chips such as Analog Devices ADSP-TS201S, Hitachi SuperH-SH7050, and Motorola Dragonball. However, sometimes in some high-end systems, scratch-pad memory is used in conjunction with either only Icache or Dcache or sometimes both. This is done with the objective of combining the benefits of both cache and scratch-pad memory. A majority of these systems also provide DMA hardware for fast data transfers. We now illustrate some representative processors with varying scratch-pad memory based memory systems. Apart from showing how scratch-pad memory is useful in these processors, these examples also point to how the scratch-pad memory fits into the overall architecture of the processor.

**ARM968E-S** The ARM968E-S [9], which belongs to ARM9E family, is targeted for embedded real-time applications. Its key characteristic is that it is small and low power. Its size and power advantages are partly contributed by separate

scratch-pad memories for instruction and data. The scratch-pad memory is also termed tightly coupled memory and has customizable sizes. The ARM968E-S has a dual-banked scratch-pad to store data and a DMA controller to share access to the scratch-pad memory. The DMA interface accesses the data scratch-pad (also called data tightly coupled memory or DTCM) through two separate ports, D0TCM and D1TCM. The processor and the DMA controller alternately access the D0TCM and D1TCM ports. This unique feature enables the DMA port to move external data blocks into the Data scratch-pad without stalling the processor access during the DMA block move. Some of the applications its particularly found use in are: networking systems, wireless devices, storage devices consumer devices like audio players.

**MPC565** The MPC565 [62] from Motorola belongs to the MPC500 family. The MPC500 family is targeted at a variety of Global Positioning Systems (GPS), ranging from high-velocity, fast acceleration aircraft applications to low-speed, high precision agriculture applications. Its memory sub-system consists of 1Mbyte of embedded Flash memory and 36 KB scratch-pad memory. The scratch-pad is useful in storing the data read by the sensors, while the embedded flash stores the code. The 1Mbyte of embedded Flash is divided into 2 blocks of 512 Kbytes. Because the memory is configured into two separate blocks, program code can be executed from one block of Flash while programming into the other.

**ADSP-21262** The ADSP-21262 [4] from Analog Devices belongs to the SHARC programmable DSPs. The ADSP-21261 chip is used in a range of processors such as high-quality audio and automotive entertainment systems, voice recognition, med-

ical appliances and measurement. The memory system of ADSP-21262 represents how scratch-pad memory can be combined with different devices to provide a sophisticated memory system. The memory system includes 256 KB of on-chip dual-ported scratch-pad memory, 512 KB of mask programmable ROM memory and an on-chip instruction cache of size 192 KB. The scratch-pad is dual-ported and enables sustained processor and I/O performance without the need for external memory. For fast delivery between the scratch-pad and the main memory, it has 22 zero-overhead Direct Memory Access (DMA) channels, thus avoiding processor intervention. The cache is used only when there is a conflict for the program memory bus between instruction fetches and data fetches. This cache allows full-speed execution of core and looped operations such as digital filter multiply-accumulates.

## 2.4 Summary

Scratch-pad memory offers several inherent advantages like lesser area, faster per-access time and lower per-access energy cost. The choice of the allocation strategy is important in not only translating these advantages to benefits for the system but also ensuring other requirements like real time guarantees. Due to these advantages, scratch-pad memory systems find use in many embedded systems in variety of ways.

## Chapter 3

## **Dynamic Allocation Overview**

In the absence of hardware that helps un runtime management of memory, ensuring good performance in the case of scratch-pad memory becomes the task of the allocation algorithm. The role of the allocation algorithm is crucial in preserving the advantages of a scratch-pad memory over a cache like lower per access energy consumption, lesser area. Allocation algorithms have their most influence on the behavior of the application – whether its memory system behaves deterministically or not. Totally dynamic allocation algorithms that modify the memory contents based on run-time conditions cannot provide good real time guarantees. Static allocation schemes, although they provide for deterministic memory behavior, do not adapt to runtime conditions; thus limiting their performance. So while the allocation being dynamic is good for performance, it conflicts with providing real time guarantees.

The motivation of this thesis is to explore a dynamic strategy that also offers good real time guarantees. With such a strategy we target embedded real time application that also require performance and low energy consumption. In this chapter we discuss some of the basic aspects of such a strategy. Section 3.1 defines some of the parameters of our solution strategy. Section 3.2 looks at some of the characteristics of our method, some of which manifest as challenges in the problem.

## 3.1 Designing a dynamic strategy

Our choice of these features is guided by the applications we have targeted – applications that have severe real time requirements. Additionally, we assume that these applications are run in resource constrained environment and hence are required to consume less power, have small memory footprint while also having a performance requirement.

#### Greedy versus non-greedy solutions

We first consider if the dynamic algorithm should be heuristic driven or otherwise. Towards that we prove that the problem is NP-hard.

**Theorem 1.** The dynamic memory allocation problem for Scratch-pad memory systems is NP-hard.

*Proof.* The dynamic allocation problem can be shown to NP-hard by reducing the problem from register allocation; register allocation has been proven NP-Complete [69].

Consider the problem of global register allocation with k registers; each register of size v words and an input variable set A. An equivalent dynamic memory allocation problem can be constructed by the following two steps. First, determine the scratch-pad size as  $k^*v$ . Second, enforce a alignment restriction of v bytes. Each of these steps is trivially done. Thus, from the NP-Completeness of register

The consequence of theorem 1 is that polynomial-time optimal solutions are highly unlikely. With that in mind, we develop a heuristic solution. Our heuristicdriven algorithm exploits several well known algorithm and program properties. First, we restrict our program points to only points those that are likely to be useful. Second, we use a divide-and-conquer approach to divide our problem into several subproblems. Each of these problems falls into variants of well-known classical problems namely the 0/1 knapsack problem and the bin packing problem that have good greedy solutions.

**Pseudo dynamic versus dynamic** Next we consider if the algorithm should be purely dynamic or not. The drawback of truly dynamic allocations is that the memory behavior is then non-deterministic, which then impacts the real time guarantees. On the other end, static allocations do not exploit the locality of the application and are hence likely to be inferior in runtime.

We choose a profile-guided pseudo-dynamic allocation strategy and hence avoid a purely dynamic strategy. Using the profile information we find a dynamic allocation at compile time. This involves using the compiler to insert code at different program points to change the contents of the scratch-pad memory at different points. While this can exploit the locality to some extent, the contents of the scratch-pad are known exactly at different program points. This leads to total predictability of latency for each memory access.

Number of allocations at a program point Due to the presence various

control structures, program execution can pass through a particular program point multiple times; some of the paths through the point may be different from the others. This leads to the following design question: how many different allocation should be associated with a particular program point. A purely dynamic solution can be considered one where allocation at any point is totally unconstrained. An example of such a strategy is software caching discussed earlier. However, software caching has drawbacks of non-determinism and per-access translation cost. A slightly less dynamic allocation could be one where at any point a set of allocations is determined for different execution paths through the point. We here consider if such alternative methods can be designed that avoid the per-access translation overhead and non determinism in truly dynamic allocations. We will see why two such approaches we speculate on are not likely to be successful<sup>1</sup>.

First, *cloning* makes a copy of each code region for each of its possible dynamic allocations. The program then checks runtime conditions and jumps to the most suitable of the cloned alternatives. In this way, the overhead is reduced from being per-access to per-region, making it manageable. Unfortunately such a solution has a serious drawback: the code growth can be exponential in the number of program variables in a region – for n variables, each in SRAM or DRAM, the number of possible allocations is  $2^n$ . In addition, selective cloning of a few variables is infeasible since a factor of  $2^n$  increase in code size is un-acceptable even for small n. Further,

<sup>&</sup>lt;sup>1</sup>These two hypothetical approaches are not used in any existing scratch-pad allocation method. Further, these are the only approaches *we* could imagine for truly dynamic allocations – that is not to say that others are not possible.

selectively cloning only a few time-critical regions is difficult. This is because allocation uncertainty in one region causes allocation uncertainty in subsequent regions, requiring more cloning.

A second method to reduce per-access overhead is *conditional allocation*. Here variables are accessed indirectly through conditionally assigned temporaries, eliminating cloning, but an exponential number of check cases is still needed per region to assign its temporaries. This is because the number of allocation possibilities is still exponential, and the allocation decisions for different variables are not independent since whether a variable fits in scratch-pad depends on the allocation of other variables. Further, the run-time overhead increases because of the access overhead from indirection through temporaries. Because of the large overheads and complexity of these alternatives, we do not believe these alternatives to be promising, and do not study them further. This leads us to the next design criterion for our algorithm-*we restrict the number of allocations at any program point to one*.

Need for Interprocedural Analysis Our next criterion is whether the algorithm should be interprocedural or not. The need for interprocedural analysis arises due to the large amount of data that a dynamic allocation strategy is likely to handle. Without a interprocedural mechanism, it would mean the scratch-pad is emptied at the boundaries of a procedure. In particular, if the function calls are present inside a loop, then transfers accumulated over the whole loop would be a significant fraction of the total runtime. Not only is this expensive, it is also unnecessary. Aggregate data types like arrays and structures often exhibit cross function reuse. Unnecessary eviction of such large data at the boundaries of function can severely degrade the overall runtime. In general, as will be shown by statistics in the results chapter 10, interprocedural analysis enables the same allocation to be retained with minimal transfers.

To summarize, our method is motivated by the following design goals.

- The strategy should be pseudo-dynamic and compiler-decided strategy so that it would provide real time guarantees while adapting to runtime conditions.

- The strategy should be heuristic-driven to efficiently explore the large design space.

- The strategy should have one allocation at every point to avoid unnecessary code growth.

- The allocation strategy should be interprocedural to avoid unnecessary transfers.

# 3.2 Characteristics of our allocation strategy

The choice of being a compiler-decided and dynamic scheme leads to several characteristics that are inherent to both compiler-decided and dynamic methods. Some of them are advantageous while there are some which a designer has to be careful about. We now look at some of these characteristics.

Compiler schemes have a unique set of advantages and disadvantages due to their view of memory that is different from how hardware schemes view memory. While compiler schemes view memory as made up of various data types, hardware schemes have a uniform view of memory made of bytes or words. Consequently, compiler schemes can utilize a lot of program information; this is not easy for hardware schemes. This difference can also work in favor of hardware schemes. Some of the differences and their impact is discussed below.

Data size While a compiler scheme can handle precisely only those addresses that belong to a particular variable, a hardware scheme handles all the addresses that belong to the cache lines it is fetching. This characteristic can work in the favor of hardware schemes as well. Hardware schemes can be totally oblivious of the size of the variable. In the case of compiler schemes, size of a variable is an important parameter that influences lot of decisions like if the variable would fit into the memory, what addresses to assign the incoming variable.

**Dead data** Similarly, while a compiler scheme can use program information to identify stale data in memory, hardware schemes cannot do so.

**Code generation** In the case of a hardware scheme, code can be generated independent of the underlying memory. Such binary portability is not possible in the case of compiler schemes. Information about the scratch-pad has to be taken into account while generating the code.

**Correctness issues** Issues pertaining to correctness of the program also arise because of the program view of memory. One such issue is due to the presence of pointers. Hardware schemes can be totally oblivious of the kind of programs run. In contrast, presence of pointers causes issues for compiler schemes. We elaborate on the issue of pointers in Chapter 7. Our method also has some characteristics due to being a dynamic scheme. Some of these are discussed below.

**Coherence issue** Due to dynamic nature of the algorithm, several versions of the same variable can exist in memory. For example, when a variable is copied from the DRAM to the SRAM, two versions of the variable exist. If then a new copy of the variable is created either from its copy in SRAM or from DRAM a third new version results. Hence, the allocation algorithm has to keep track of the latest copy of the variable to avoid coherence issues.

**Runtime adaptability** Being a dynamic scheme, our method has the ability to adapt changing runtime conditions.

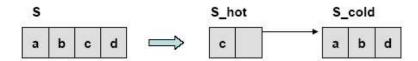

# 3.3 Dynamic solution overview

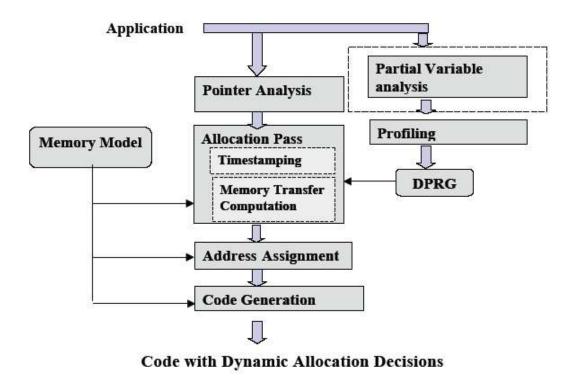

We next overview our method. The process flow of our method is illustrated in figure 3.1. A brief description of the entire flow follows. The figure shows two parallel paths of flow. The data inputs are shown in rounded rectangles. In the first path, profile information is collected and stored in the stucture called the DPRG. Depending on the application, the code can be optionally optimized and analyzed for partial variable references. The results of the partial variable analysis is also stored in the DPRG. The second path is the allocation strategy. The strategy is centered around three steps that form the core of our method. After pointer analysis is done, the main allocator takes in profile input and the memory model and outputs an allocation. This is followed by address assignment and code generation. The memory model provides memory device information like the latencies, energy model and sizes of the different memory devices.

Figure 3.1: Dynamic memory allocation methodology

# 3.4 Dynamic memory allocation parts

**Profiling** The objective of profiling is to find the relative use of different variables in different portions of the program. To achieve this, it proceeds in three steps. First, it partitions the program into regions where the start of each region is a *program point*. Then, instrumentation code is inserted at these program points. The instrumentation involves code to capture information like how many times variable around that point are accessed. Then when the instrumented code is run, profile

information is collected which is stored in the data structure called the DPRG. We discuss this structure elaborately in section 4.1.

#### Allocator

The allocator forms the central part of our method. The allocator can be further divided into two sub-parts. The first part takes the DPRG as input from the profiler and associates a timestamp with every program point such that (i) the timestamps form a partial order; and (ii) the program points are reached during runtime roughly in timestamp order. Timestamping is discussed in detail in section 4.1 The second sub-part determines the contents of the scratch-pad memory at different points. Changes in allocation are made only at program points by compiler-inserted code that copies data between the scratch-pad and the DRAM. The method visits these different points in a timestamped order and determines the variables to be transferred between memories at each program point by using the cost-model. The cost-model takes into account different factors like the current contents, possible transfer points (eg. just outside the different loops of a loop nest), transfer costs and parameters of the memory model. We discuss the algorithm and various aspects of it in detail in chapters 4 and chapter 5.

Address assignment In the next step, the allocator decides on the addresses of the scratch-pad memory variables in different regions. This involves deciding which available address range in the scratch-pad memory (free hole) to use to accommodate a variable allocated to the scratch-pad memory. To achieve this, the methods again visits the regions in timestamp order and attempts to fit the variables newly allocated to the scratch-pad memory into the available free holes in the scratch-pad memory in a best-fit manner. Since over time memory might get fragmented and consequently free holes of desired size might not be available, the method invokes a limited compaction mechanism when it runs out of adequate-sized holes. The details of this step are discussed in section 6.1

**Code generation** Code generation involves using new temporaries to access a variable allocated to the scratch-pad memory. A temporary represents a variable allocated to the scratch-pad memory at a specific address. Use of temporaries also implies that at any point multiple versions of a variable may exist, but with one latest version known to the compiler. Code generation also includes memory transfers inserted before and after regions to copy between the temporary and the original variable. The details of this step are discussed in section 6.2

**Optimizations and partial variable handling** Finally, optimizations can be integrated into the process flow to improve the allocation solutions. In chapter 8, we discuss how our method can be extended to incorporate partial-variable handling.

## 3.5 Summary

In this chapter, we overviewed some fundamental aspects of our algorithm. First, based on the requirements we wanted to meet, we fixed the different design choices for our method. The design choices decided several characteristics and challenges that our method would need to address. Finally, we briefly described the process flow of our solution.

### Chapter 4

# Dynamic Allocation Algorithm

This chapter describes the proposed algorithm for determining the memory transfers of global and stack variables at each program point.

An outline of the chapter follows. We first in section 4.1 discuss the data structure that is a key input to our algorithm. Then, we discuss our method that allocates global and stack variables in 4.2. In section 4.3, we show how this method can be extended to also allocate program code.

# 4.1 Deriving regions and timestamps

Our algorithm relies on identifying promising parts of the programs where certain variables can be allocated to the scratch-pad memory. So an essential task is identifying these parts. As the first task, the algorithm partitions the program into *regions* where the start of each region is a *program point*. Changes in allocation are made only at program points by compiler-inserted code that copies data between SRAM and DRAM. The allocation is fixed within a region. The choice of regions is discussed in the next paragraph. Then it associates a *timestamp* with every program point such that (i) the timestamps form a partial order; and (ii) the program points are reached during runtime in timestamp order. In general, it is not possible to assign timestamps with this property for all programs. Later in this section, however, we show a method that by restricting the set of program points and allowing multiple timestamps per program point, is able to define timestamps for all programs.

The choice of program points and therefore regions, is critical to our algorithm's success. Regions are the code between successive program points. Promising program points are (i) those after which the program has a significant change in locality behavior, and (ii) those whose dynamic frequency is less than the frequency of its following region, so that the cost of copying into SRAM can be recouped by data re-use from SRAM in the region. For example, sites just before the start of loops are promising program points since they are infrequently executed compared to the insides of loops. Moreover, the loop often re-uses data, justifying the cost of copying into SRAM. With the above two criteria in mind, we define program points as (i) the start and end of each procedure; (ii) just before and just after each loop (even inner loops of nested loops); (iii) the start and end of each if statement's then part and else part as well as the start and end of the entire if statement; and (iv) the start and end of each case in all **switch** statements in the program as well as the start and end of the entire **switch** statement. In this way, program points track most major control-flow constructs in the program. Program points are merely candidate sites for copying to and from SRAM – whether any copying code main () {

main () {

if (...) { proc-D()} else {...}

proc-A()

proc-B()

}

proc-B()

}

proc-A() {

proc-C() { X =...}

proc-C() { ...}

}

}

Figure 4.1: Example showing a program outline.

is actually inserted at those points is determined by a cost-model driven approach, described later in section 4.2.

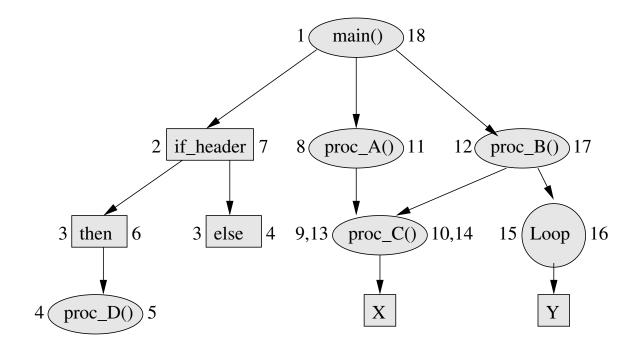

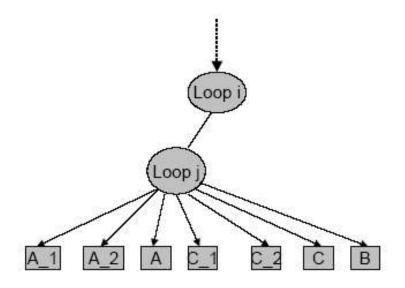

Figures 4.1 and 4.2 shows an example illustrating how a program is marked with timestamps at each program point. Figure 4.2 shows the program outline. It consists of five procedures, namely main(), proc-A(),proc-B(), proc-C() and proc-D(), one loop and one **if-then-else** construct. The only program constructs shown are loops, procedure declarations and calls, and **if** statements – other instructions are not. Accesses to two selected variables X and Y are also shown.

Figure 4.2 shows the Data-Program Relationship Graph (DPRG) for the pro-

Figure 4.2: Example showing the DPRG showing nodes, edges & timestamps.

gram in figure 4.1. The DPRG is a new data structure we introduce that helps in representing regions and reasoning about their time order. The DPRG is the program's call graph appended with new nodes for loops, if-then's and variables. In the DPRG shown in figure 4.2, there are five procedures, one loop, one if statement, and two variables represented by nodes. Separate nodes are shown for the entire **if** statement (called if-header) and for its **then** and **else** parts. On the figure, oval nodes represent procedures, circular nodes represent loops, rectangular nodes represent **if** statement nodes, and square nodes represent variables. Edges to procedure nodes represent calls; edges to loop and if nodes shows that the child is in its parent; and edges to variable nodes represent memory accesses to that variable from its parent. Continue and break statements are not modeled separately. The DPRG is usually a directed acyclic graph (DAG), except for recursive programs, where cycles occur.

Figure 4.2 also shows the timestamps (1-18) for all program points, namely the beginnings (shown on left of nodes) and ends (shown on right) of every *procedure*, *loop*, *if-header*, *then* and *else* node. The goal is to number timestamps in the order they are encountered during the execution. This numbering is computed at compiletime by the well-known depth-first-search (DFS) graph traversal algorithm. Our DFS marks program points in the order seen with successive timestamps. Our DFS is modified, however, in two ways. First, our DFS is modified to number *then* and else nodes of if statements starting with the same number since only one part is executed per invocation. For example, the start of the *then* and *else* nodes shown in the figure both are marked with timestamp 3. The numbering of the end of *if-header* node (marked 7 in the figure) follows the numbering of either the *then* and *else* parts, whichever consumes more timestamps. Second, it traverses and timestamps nodes every time they are seen, rather than only the first time. This still terminates since the DPRG is a DAG for non-recursive functions. Such repeated traversal results in nodes that have multiple paths to them from main() getting multiple timestamps. For example, node proc-c() gets timestamps 9 & 13 at its beginning, and 10 & 14 at its end.

Now we can see that the timestamps are a partial order rather than a total order. This is because timestamps should not be used to derive an order between two nodes such that one is a child of the *then* part of some *if-header* node, and the other is a child of the *else* part of the same *if-header*. Such nodes have no relative order.

Timestamps are useful since they reveal dynamic execution order: the run-

time order in which the program points are visited is roughly the order of their timestamps. The only exception is when a loop node has multiple timestamps as descendants. Here the descendants are visited in every iteration, repeating earlier timestamps, thus violating the timestamp order. Even then, we can predict the *common case time order* as the cyclic order, since the end-of-loop backward branch is usually taken. Thus we can use timestamps, at compile-time, to reason about dynamic execution order across the whole program. This is a useful property, and we speculate that timestamps may be useful for other compiler optimizations as well that need to reason about execution order, such as compiler-controlled prefetching [53], value prediction [48] and speculation [22].

Timestamps have their limitations in that they do not directly work for **goto** statements or the insides of recursive cycles; but we have work-arounds for both which are mentioned in chapter 5.

## 4.2 Allocation of Global and Stack Objects

Before running this algorithm, the DPRG is built to identify program points and mark the timestamps. Next, profile data is dynamically collected to measure the frequency of access to each variable separately for each region. This frequency represents the weight of the edge from a parent node to a child variable. Profiling also measures the average number of times a region is entered from a parent region. This represents the edge weight between two non-variable nodes. The edge weight between a variable and a non-variable represents the access frequency of the variable in the parent region. The total frequency of access of a variable is the product of all the edge weights along the execution path from the main() node to the variable.

An overview of the first part of our memory transfer algorithm is as follows. At each program point, the algorithm determines the following memory transfers: (i) the set of variables to copy from DRAM into the scratch-pad and (ii) the set of variables to evict from DRAM to the scratch-pad to make way for incoming variables. The algorithm computes the transfers by visiting each program point (and hence each region) once in an order that respects the partial order of the timestamps. For the first region in the program, variables are brought into the scratch-pad in decreasing order of frequency-per-byte of access. Thereafter for subsequent regions, variables currently in DRAM are considered for bringing into the scratch-pad in decreasing order of frequency-per-byte of access, but only if a *cost model* predicts that it is profitable to do so. Variables are preferentially brought into empty space if available, else into space evicted by variables that the compiler has proven to be dead at this point, or else by evicting live variables. Completing this process for all variables at all timestamps yields the complete set of all memory transfers.

The order in which different regions are visited by our method is guided roughly by the timestamps of the regions. It is important to note that such reliance on the timestamps does not have any correctness impact. Timestamps are used only as an indicator of the common-case ordering between regions. No assumption is made that the execution order at run-time is the same as the timestamp order. Moreover, since timestamps define a partial order and not a total order, no common-case ordering is assumed in the case of incomparable nodes For example, nodes such as ones under the *then* part of some *if-header* node, and the *else* part of the same *if-header* do not have any relative ordering. In such cases, our method derives allocation for each branch independent of the other branch. The details are discussed in chapter 5. Thus, using the timestamps to guide allocation does not have any correctness impact.

The cost model works as follows. Given a proposed incoming variable and oneor-more variables to evict for the incoming variable, the cost model determines if this proposed swap should actually take place. In particular, copying a variable into the scratch-pad may not be worthwhile unless the cost of the copying and the lost locality of evicted variables is overcome by its subsequent reuse from scratch-pad of the brought-in variable. The cost model we use models each of these components to derive if the swap should occur.

**Detailed algorithm** Algorithm 1 describes the above algorithm in pseudo-code form. A line-by-line description follows in the rest of this section.

Algorithm 1 begins by declaring several compiler variables. These include Vfast and V-slow to keep track of the set of application variables allocated to the scratch-pad and DRAM, respectively, at the current program point. Bring-in-set, Swap-out-set and Retain-in-fast-set store their obvious meaning at each program point. Dead-set refers to the set of variables in V-fast in the previous region whose lifetime has ended. The frequency-per-byte of access of a variable in a region, collected from the profile data, is stored in freq-per-byte[variable, region].

We now consider the top level function **Memory-allocator**. Line 12 is the main **for** loop that steps through all the subsequent program points in timestamp or-

#### Algorithm 1 Algorithm for determining dynamic memory allocation

| $\begin{array}{c} 1: \text{ Define} \qquad \triangleright \text{ The values of all of the quantities defined below change at each program point} \end{array}$ |                                                                                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| 2: Set V-slow                                                                                                                                                 | $\triangleright$ Set of variables in DRAM at this point                        |  |

| 3: Set V-fast                                                                                                                                                 | $\triangleright$ Set of variables in the scratch-pad at this point             |  |

| 4: Free space                                                                                                                                                 | $\triangleright$ Free space in scratch-pad memory                              |  |

| 5: Set Bring-in-set                                                                                                                                           | $\triangleright$ Variables to bring into the scratch-pad at this program point |  |

| 6: Set Swapout-set                                                                                                                                            | $\triangleright$ Set of variables for eviction to DRAM                         |  |

| 7: Set Retain-in-fast-set                                                                                                                                     | $\triangleright$ Set of variables to retain in the scratch-pad                 |  |

| 8: Set Dead-set                                                                                                                                               | $\triangleright$ Set of variables in V-fast whose lifetimes have ended         |  |

| 9: float freq-per-byte<br>[variable,region] $\triangleright$ Access frequency per byte of variable in region in profile                                       |                                                                                |  |

data

- 10: **procedure** Memory-allocator

- 11: initial-candidate-list  $\leftarrow$  Sort variables accessed in first region in decreasing order of freqper-byte[variable, first region

- 12: **for all** timestamped program points in the application visited in partial order of their timestamps, starting at second region **do**

- 13: Swapout-set  $\leftarrow$  NULL\_SET; Bring-in-set  $\leftarrow$  NULL\_SET; Retain-in-fast-set  $\leftarrow$  NULL\_SET

- 14: Free-space = Free-space + sizeof(Dead-set)

- 15: **for all** variables V accessed in this region in decreasing order of frequency-per-byte **do**

- 16: Consider-for-Vfast(V) ▷ Check if V can be allocated into scratch-pad. If so,

update various

40

```

17: end for

```

- 18: V-fast  $\leftarrow$  V-fast  $\bigcup$  Bring-in-set Swapout-set Dead-set

- 19: V-slow  $\leftarrow$  V-slow  $\bigcup$  Swapout-set Bring-in-set Dead-set

- 20: Store V-fast and V-slow for this region

- 21: Dead-set  $\leftarrow$  Variables which are no longer alive at this program point

- 22: **end for**

23:

- $\mathbf{return}$

- 24: end procedure

| 1:                                                               | 1: procedure Consider-for-Vfast(V)                                                                                                                                                                          |                                                  |  |  |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| 2:                                                               | 2: <b>if</b> $V \in V$ -slow <b>then</b>                                                                                                                                                                    |                                                  |  |  |

| 3:                                                               | $\mathbf{if} \ \mathrm{sizeof}(V) \leq \mathrm{Free-space} \ \mathbf{then} \qquad \qquad \triangleright \ V \ \mathrm{fits} \ \mathrm{no} \ \mathrm{need} \ \mathrm{to} \ \mathrm{swapout} \ \mathrm{vari}$ |                                                  |  |  |

| 4:                                                               | $Benefit\text{-of-bring-in-V} \leftarrow Find\text{-benefit}(V, NULL\_SET)$                                                                                                                                 |                                                  |  |  |

| 5:                                                               | if Benefit-of-bring-in- $V > 0$ then                                                                                                                                                                        |                                                  |  |  |

| 6:                                                               | Bring-in-set $\leftarrow$ Bring-in-set $\bigcup \{V\}$                                                                                                                                                      |                                                  |  |  |