#### **UCLA**

#### **UCLA Electronic Theses and Dissertations**

#### **Title**

Compiler Support for Customizable Domain-Specific Computing

#### **Permalink**

https://escholarship.org/uc/item/2s79r0jr

#### **Author**

Huang, Hui

#### **Publication Date**

2014

Peer reviewed|Thesis/dissertation

#### University of California

Los Angeles

# Compiler Support for Customizable Domain-Specific Computing

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

**Hui Huang**

© Copyright by

Hui Huang

2014

#### ABSTRACT OF THE DISSERTATION

# Compiler Support for Customizable Domain-Specific Computing

by

#### **Hui Huang**

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 2014

Professor Jason Cong, Chair

It is known that with the support of domain-specific customizable heterogeneous architecture, energy efficiency can be significantly improved by adapting architectures to match the requirements of a given application or application domain. One of the main challenges in this emerging trend is how to efficiently take the advantage of the *heterogeneity* and *customization* features in those architectures. This research investigates developing efficient compiler support to automate the platform mapping and code transformation process.

First, considering customizable computing engines, we have investigated both tightly-coupled and loosely-coupled computing elements. In terms of tightly-coupled computing engine customization, customizable vector ISA supports are explored to better exploit data-level parallelism in the high performance applications. We identify the needs

and opportunities to explore customized vector instructions and quantify their benefits. We build an automatic compilation flow in LLVM-2.7 compiler infrastructure to efficiently identify customized vector instructions from a given set of applications. The memory alignment overhead, which is known to be critical for vector processing efficiency, has been optimized in our customized vector ISA identification flow. To support efficient vector ISA customization, we design a composable vector unit (CVU), which can be used both separately and in a chained mode, to support a large number of virtualized custom vector instructions with minimal area overhead. The results show that our approach achieves an average 27% speedup over the state-of-art vector ISA.

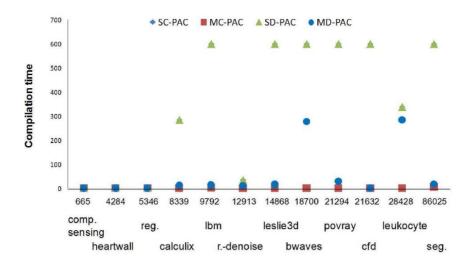

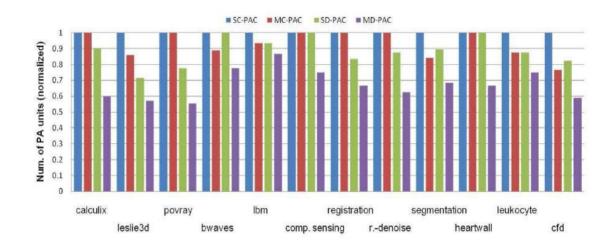

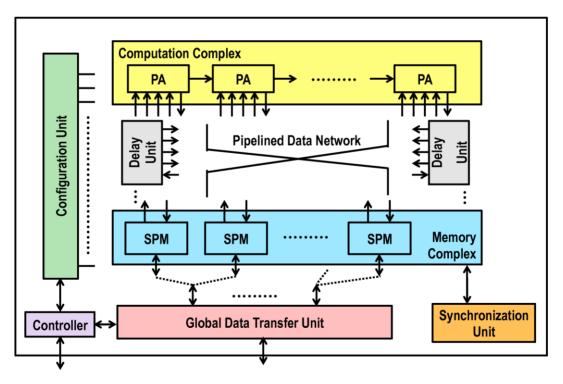

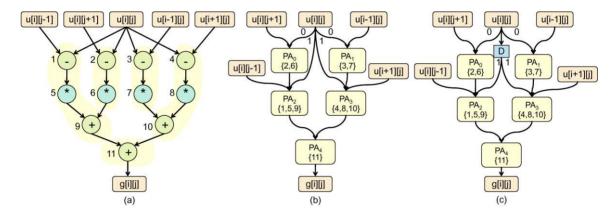

Second, in terms of loosely-coupled computing elements, it is known that on-chip accelerators are combined with general-purpose cores in an effort to amortize the cost of the design across many application domains. In recent days programmable accelerators (PA) are widely investigated in the design of domain-specific architectures to improve the system performance and power. Micro-architectures with a series of PAs have been explored to provide more general supports for customization. One important feature in the PA-rich systems is that the target computational kernels are compiled with a set of pre-defined PA templates and dynamically mapped to real PAs at runtime. This imposes a demanding challenge on the compiler side regarding how to generate high-quality PA mapping code. We present an efficient PA compilation flow, which is fairly scalable in mapping large computation kernels into PA-rich architectures and provides support for full pipelined execution to achieve the highest energy efficiency. A concept called maximal PA candidate is proposed to drastically reduce the number of input PA candidates in the mapping phase without influencing the overall mapping optimality. Efficient pre-selection and pruning techniques are employed to further speedup the maximal PA mapping process. Our experimental results show that for 12 computation-intensive standard benchmarks, the proposed approach achieves a significant improvement on the compilation time comparing to the state-of-art PA compilation approaches. The average mapping quality is improved by 23.8% and 32.5% for connected PA candidates and disjoint ones, respectively.

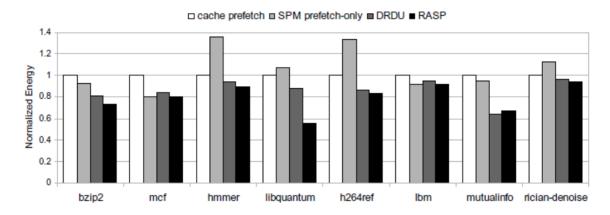

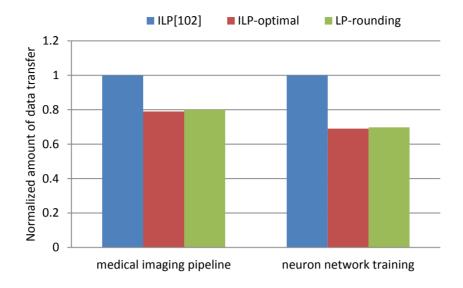

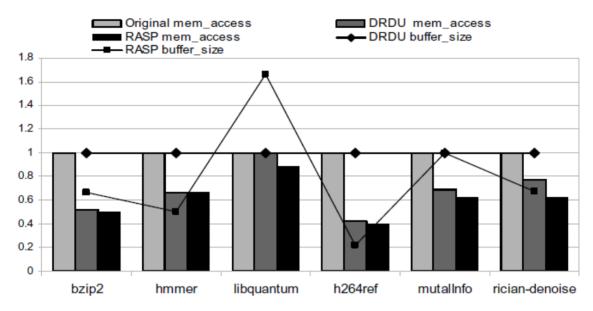

Third, in domain-specific computing multi-level software-controlled memories have been commonly used to better utilize domain-specific knowledge of particular applications and achieve high performance/energy efficiency. At the level of L1 memory, while conventional cache works well for general workloads, some recent works explore the idea of using a hybrid cache, which can be flexibly partitioned into a traditional cache and an SCM. In the hybrid cache architecture, first-level SCM has been utilized as prefetch buffer to hide memory access latency. We quantify the impact of data reuse on SCM prefetching efficiency and propose a reuse-aware SCM prefetching (RASP) scheme, which shows 31.2% performance gain over previous work. On the other hand, SCM has also been widely used in last level on-board memory to reduce the data movements between computing cores (i.e. host processor and accelerator cores), which is usually transferred through low-bandwidth bus and known to be one of the major performance bottlenecks in modern heterogeneous systems. To efficiently manage LL-SCM, we propose a task-level-reuse-graph (TLRM) based LL-SCM data movement scheme to minimize the amount of data transfers between heterogeneous computing cores through the slow PCIe bus. With the introduction of TLRM, the data movement optimization between host and accelerator cores can be approximated using a linear programming based solution, and an average 25% reduction of host-accelerator data transfers is observed from previous work.

The dissertation of Hui Huang is approved.

Jens Palsberg

Glenn Reinman

Lieven Vandenberghe

Jason Cong, Committee Chair

University of California, Los Angeles

2014

# TABLE OF CONTENTS

| 1 | In  | trodu | ction                                                      | 1  |

|---|-----|-------|------------------------------------------------------------|----|

|   | 1.1 | Cus   | tomizable Heterogeneous Architecture                       | 1  |

|   | 1.2 | Con   | npiler Support for Customizable Domain-Specific Computing  | 4  |

|   |     | 1.2.1 | Customizable Vector Unit                                   | 4  |

|   |     | 1.2.2 | Customizable Computing Accelerator                         | 6  |

|   |     | 1.2.3 | Customizable Memory                                        | 7  |

| 2 | Co  | mpile | r Support for Customizable Vector Instruction Extension    | 10 |

|   | 2.1 | Intr  | oduction                                                   | 10 |

|   | 2.2 | Mot   | tivational Example                                         | 14 |

|   | 2.3 | Cus   | tomized Vectorization Flow                                 | 16 |

|   |     | 2.3.1 | Vectorizable Code Region Extraction                        | 19 |

|   |     | 2.3.2 | Operation-based Vectorizability Checking                   | 21 |

|   |     | 2.3.3 | Vectorizable Data Flow Graph Expansion                     | 23 |

|   |     | 2.3.4 | Pattern-Based Customized Vector Instruction Identification | 27 |

|   | 2.4 | Exp   | eriment Results                                            | 29 |

|   |     | 2.4.1 | Evaluation Methodology                                     | 29 |

|   |     | 2.4.2 | Pattern Recognition Results                                | 30 |

|   |     | 2.4.3 | Alignment Optimization Results                             | 31 |

|   |     | 2.4.4 | Performance Comparison Results                             | 32 |

|   | 2.5 | Conclusion and Future Work                 | 33 |

|---|-----|--------------------------------------------|----|

| 3 | Con | npilation for Programmable Accelerators    | 35 |

|   | 3.1 | Introduction                               | 35 |

|   | 3.2 | Related Work                               | 39 |

|   | 3.3 | PA Compilation Example                     | 41 |

|   | 3.4 | Preliminaries and Problem Formulation      | 43 |

|   | 3.5 | Maximal PA Compilation Flow                | 47 |

|   | :   | 3.5.1 Maximal PA Candidates Identification | 47 |

|   |     | 3.5.2 Maximal PA Mapping                   | 48 |

|   | 3.6 | Experimental Results                       | 53 |

|   |     | 3.6.1 Experiment Setup                     | 53 |

|   |     | 3.6.2 Comparison Results                   | 53 |

|   | 3.7 | Algorithm Generalization                   | 58 |

|   | 3.8 | Conclusions                                | 59 |

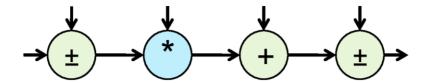

| 4 | Con | npilation for Fully Pipelined Accelerators | 60 |

|   | 4.1 | Introduction                               | 60 |

|   | 4.2 | Overview of Fully Pipelined PA             | 62 |

|   | 4.3 | Preliminaries                              | 64 |

|   | 4.4 | Throughput-Aware Path Balancing            | 65 |

|   | 4.5 | Pipelined PA Mapping                       | 68 |

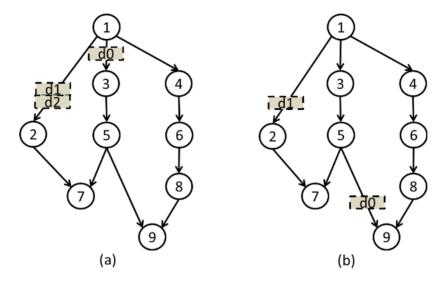

|   | 4   | 4.5.1 Delay Unit Insertion                 | 69 |

|   | 4   | 4.5.2 Balanced PA Mapping                  | 71 |

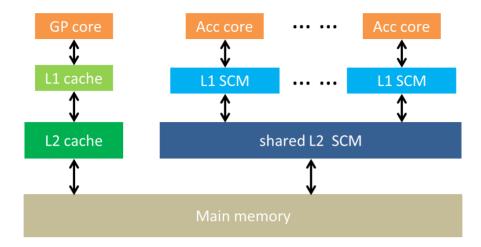

|   | 4.6 | Experimental Results                       | 74 |

|    |     | 4.6.1           | Experiment setup                                      | 74      |

|----|-----|-----------------|-------------------------------------------------------|---------|

|    |     | 4.6.2           | Comparison Results                                    | 74      |

|    | 4.7 | Cor             | nclusion                                              | 76      |

| 5  | Co  | mmu             | nication Optimization for Software-Controlled Men     | ories77 |

|    | 5.1 | Intr            | oduction                                              | 77      |

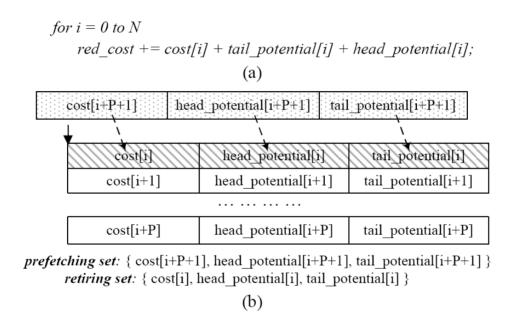

|    | 5.2 | L1-             | SCM Management                                        | 81      |

|    |     | 5.2.1           | Impact of Reuse Pattern on SCM Prefetching Efficiency | 81      |

|    |     | 5.2.2           | RASP: Reuse-Aware SCM Management                      | 83      |

|    | 5.3 | LL-             | -SCM Management                                       | 90      |

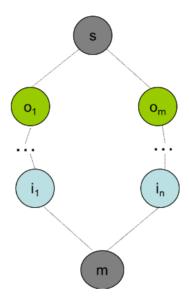

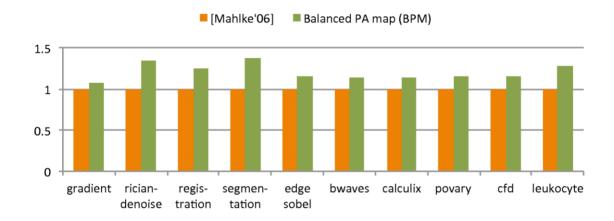

|    |     | 5.3.1           | Architecture Model                                    | 90      |

|    |     | 5.3.2           | Application Execution Model                           | 91      |

|    |     | 5.3.3           | Task-Level-Reuse-Graph Based LL-SCM Management        | 92      |

|    | 5.4 | Exp             | periment Results                                      | 98      |

|    |     | 5.4.1           | Experiment Setup                                      | 98      |

|    |     | 5.4.2           | Comparison Results                                    | 99      |

|    |     | 5.4.3           | Discussion of L1-SCM Utilization Efficiency           | 103     |

|    | 5.5 | Cor             | nclusions and Future Work                             | 104     |

| 6  | Co  | nclus           | ion Remarks                                           | 106     |

| D. | . C | 0 <b>12</b> 000 |                                                       | 107     |

# LIST OF FIGURES

| Figure 1-1. Customizable heterogeneous platform for domain-specific computing 3                |

|------------------------------------------------------------------------------------------------|

| Figure 2-1. (a) One example loop (b) Mis-aligned vector addition (c) Aligned vector            |

| addition                                                                                       |

| Figure 2-2. (a) Customized scalar instruction candidates (b) Customized vector                 |

| instruction candidates                                                                         |

| Figure 2-3 One kernel loop in <i>jacobi rician-denoise</i>                                     |

| Figure 2-4. Data flow graph of kernel loop in <i>jacobi rician-denoise</i>                     |

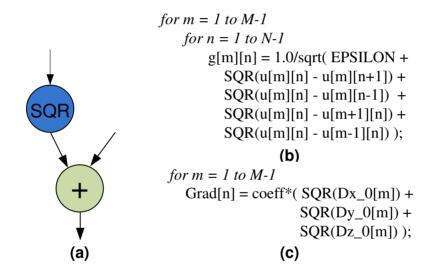

| Figure 2-5. (a) Data flow graph of SQR-accumulate (b) Kernel code piece in jacobi              |

| rician-denoise (c) Kernel code piece in level-set segmentation 16                              |

| Figure 2-6. Customized vector instruction identification flow                                  |

| Figure 2-7. Kernel code of gauss-seidel rician-denoise                                         |

| Figure 2-8. Data flow graph of gauss-seidel rician-denoise                                     |

| Figure 2-9. Complementary code elimination, vectorizability checking and alignment             |

| node insertion in the kernel code of gauss-seidel rician-denoise 20                            |

| Figure 2-10. (a) Original code (b) Transformed code                                            |

| Figure 2-11. (a) Shifting scheme 1 (b) Shifting scheme 2                                       |

| Figure 2-12. The CVU architecture                                                              |

| Figure 2-13. Normalized speedup.                                                               |

| Figure 3-1. Example of a CCA implementation [4]                                                |

| Figure 3-2. A sample PA template                                                               |

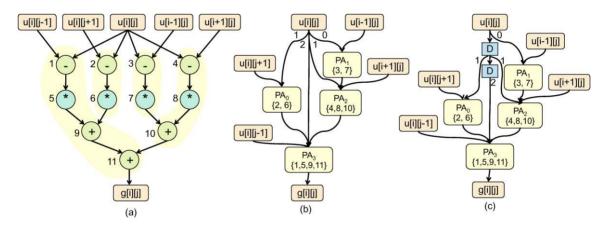

| Figure 3-3. (a) DFG of the kernel loop in <i>rician-denoise</i> . (b) One PA mapping solution. |

| (c) Runtime PA configuration of (b)                                                            |

| Figure 3-4. Two compatible maximal PA candidates                                               |

| Figure 3-5. Algorithm runtime vs. input problem size                                        |

|---------------------------------------------------------------------------------------------|

| Figure 3-6. Comparisons on PA compilation result                                            |

| Figure 4-1. Architecture of CHARM                                                           |

| Figure 4-2. A sample PA template                                                            |

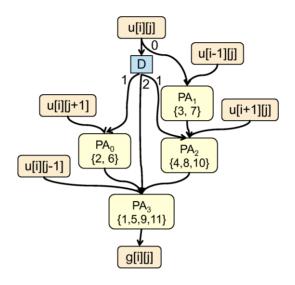

| Figure 4-3. (a) Mapping solution I of rician-denoise. (b) Mapping graph of (a). (c)         |

| Balanced mapping graph of (a)65                                                             |

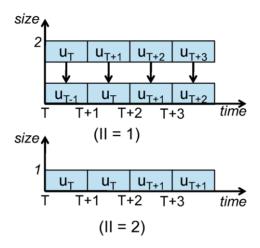

| Figure 4-4. Delay unit insertion (II = 2).                                                  |

| Figure 4-5. Delay propagation when II = 1 and 2                                             |

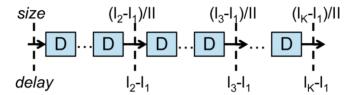

| Figure 4-6. Chained delay units for a target II                                             |

| Figure 4-7. (a) Mapping solution II of rician-denoise. (b) Mapping graph of (a). (c)        |

| Balanced mapping graph of (a)                                                               |

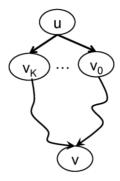

| Figure 4-8. An undirected cycle in a data flow graph                                        |

| Figure 4-9. (a) A greedy delay unit insertion scheme (b) An optimal delay unit              |

| insertion scheme                                                                            |

| Figure 4-10. A partial mapping graph. 72                                                    |

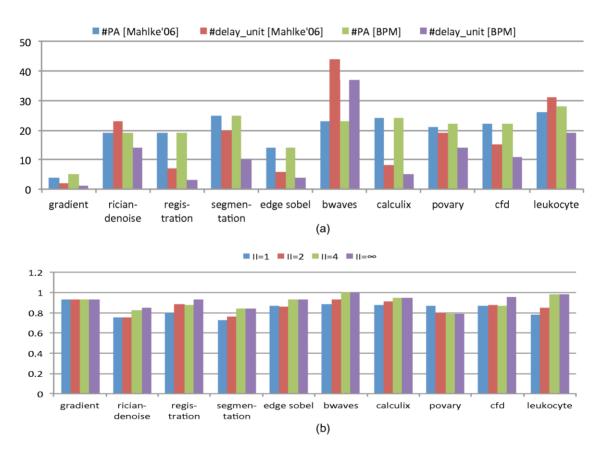

| Figure 4-11. (a) Mapping size comparison of BPM and [9] (II = 1) (b) Mapping size           |

| comparison of BPM under different II75                                                      |

| Figure 4-12. Performance comparison                                                         |

| Figure 5-1. Two-level SCM-based heterogeneous platform                                      |

| Figure 5-2. (a) Simplified kernel of 429.mcf. (b) SCM management of 429.mcf 82              |

| Figure 5-3. (a) Simplified kernel of 401.bzip2. (b) Prefetch-only SCM management of         |

| 401.bzip2. (c) Reuse-aware SCM prefetching scheme of 401.bzip2 83                           |

| Figure 5-4. (a) Normalized kernel loop of <i>rician-denoise</i> . (b) Reuse candidate graph |

| built on (a)                                                                                |

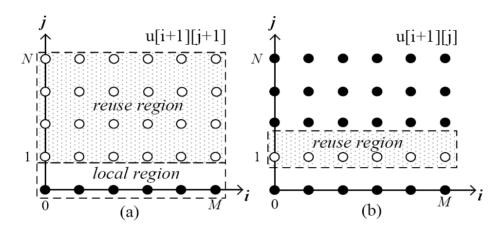

| Figure 5-5. (a) Iteration space partition of reference u[i+1][j+1]. (b) Iteration space |

|-----------------------------------------------------------------------------------------|

| partition of reference u[i+1][j]                                                        |

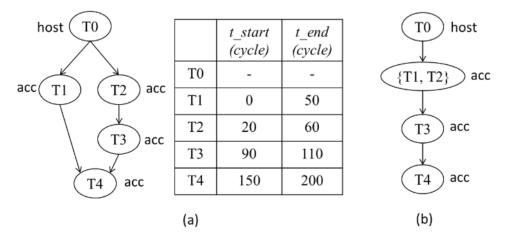

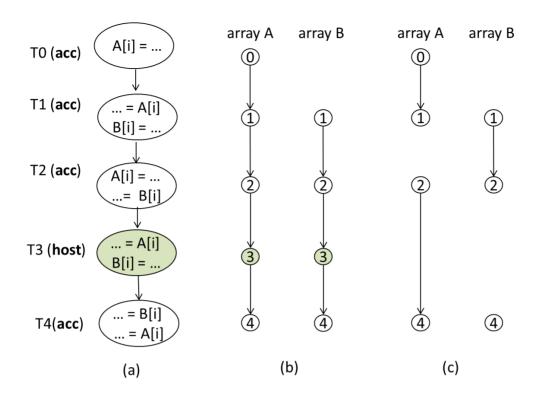

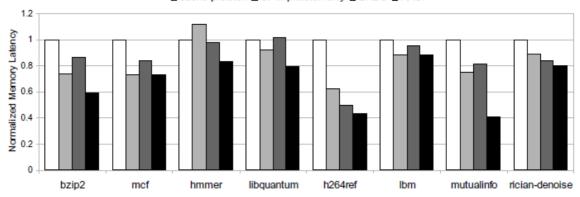

| Figure 5-6. (a) Example of task graph (b) Merged task graph                             |

| Figure 5-7. (a) Example task graph. (b) Task level data dependency graph for array A    |

| and B. (c) Task level reuse graph for array A and B                                     |

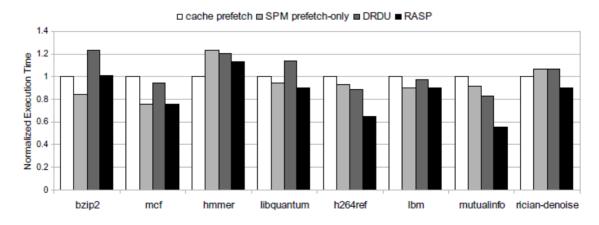

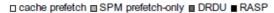

| Figure 5-8. Comparison of execution time                                                |

| Figure 5-9. Comparison of memory access latency                                         |

| Figure 5-10. Comparison of energy consumption                                           |

| Figure 5-11. Comparison of host-accelerator communication                               |

| Figure 5-12. Comparison of buffer size and SCM data transfers                           |

# LIST OF TABLES

| Table 2-1. Pattern recognition results on 9 computation-intensive benchmarks | and  |

|------------------------------------------------------------------------------|------|

| their synthesized area on ASIC.                                              | . 30 |

| Table 2-2. Comparison on overall shifting distance.                          | . 32 |

| Table 3-1. Comparisons on PA compilation time (sec)                          | . 56 |

| Table 3-2. Comparisons on the number of PA candidates                        | . 57 |

| Table 3-3. Kernel size reduction with <i>pre-selection</i>                   | . 57 |

| Table 5-1. Architecture parameters                                           | . 98 |

| Table 5-2. Comparison on problem size.                                       | 102  |

#### **ACKNOWLEDGMENTS**

I am deeply grateful to my advisor Professor Jason Cong for his guidance, support and vision throughout my Ph.D. study. During the past five years Jason offers persistent support, constructive suggestions, criticisms and encouragements when guide my graduate research, and has given me the valuable opportunity to turn research ideas into real products. Without his continuous guidance and support, this dissertation would not have been possible.

I would also like to express my appreciation to my doctoral committee members, Professor Jens Palsberg, Professor Glenn Reinman and Professor Lieven Vandenbergh. Their comments provides deep insight and greatly improve the quality of this dissertation.

In addition, I would like to thank all my colleagues in the UCLA VAST lab, especially Wei Jiang, Chunyue Liu, Yi Zou and Bin Liu. Their insight in research, optimistic life attitude and generous spirit largely encourage me to overcome the difficulties encountered from the beginning until the end of my Ph.D. study. I really appreciate and cherish the time working closely with these talented colleagues.

Finally, I would like to take this opportunity to thank my parents Hongmin Huang and Chunhua Zhao, my fiancé and best friend Maoqi Wang. Although the separation from them is painful, their love consistently support me to pursue the Ph.D. degree and higher goals in my life. I dedicate this dissertation to them.

This research was partially supported by the MARCO Gigascale System Research Center (GSRC) and the Center for Domain-Specific Computing (CDSC) funded by the NSF Expedition in Computing Award CCF-0926127 and the NSF grant CCF-0903541.

#### **VITA**

2004-2008 B.S. Department of Computer Science

Peking University, Beijing, P.R. China

#### **PUBLICATIONS**

Jason Cong, Hui Huang, Chiyuan Ma, Bingjun Xiao, and Peipei Zhou, "A Fully Pipelined and Dynamically Composable Architecture of CGRA", International Symposium on Field-Programmable Custom Computing Machines (FCCM 2014), pp. 9-16, May 2014.

Hui Huang, Taemin Kim and Yatin Hoskote, "Edit Distance Based Instruction Merging Technique to Improve Flexibility of Custom Instructions Toward Flexible Accelerator Design", Proceedings of the 19th Asia and South Pacific Design Automation Conference (ASP-DAC 2014), Jan. 2014.

Jason Cong, Mohammad Ali Ghodrat, Michael Gill, Beayna Grigorian, Hui Huang and Glenn Reinman, "Composable Accelerator-rich Microprocessor Enhanced for Adaptivity and Longevity", Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED 2013), pp. 305-310, Sep.2013.

Yu-Ting Chen, Jason Cong, Hui Huang, Chunyue Liu and Glenn Reinman, "Combined Static and Dynamic Optimizations for Hybrid SRAM and STT-RAM Caches", Proceedings of International Symposium on Low Power Electronics and Design (ISLPED 2012), August 2012.

Yu-Ting Chen, Jason Cong, Hui Huang, Chunyue Liu and Glenn Reinman, "Reconfigurable Hybrid Cache: An Energy-Efficient Last-Level Cache Design", Proceedings of Design, Automation and Test Europe (DATE 2012), March 2012.

Jason Cong, Mohammad Ali Ghodrat, Michael Gill, Hui Huang, Bin Liu, Raghu Prabhakar and Glenn Reinman, "Compilation and Architecture Support for Custom Vector Instruction Extension", Proceedings of the 17th Asia and South Pacific Design Automation Conference (ASPDAC 2012), pp. 652-657, Jan. 2012.

Jason Cong, Karthik Gururaj, Hui Huang, Chunyue Liu, Glenn Reinman and Yi Zou, "An Energy-Efficient Adaptive Hybrid Cache", in the Proceedings of International Symposium on Low Power Electronics and Design (ISLPED 2011), pp. 67-72, August 2011.

Jason Cong, Hui Huang, Chunyue Liu and Yi Zou, "A Reuse-Aware Prefetching Algorithm for Scratchpad Memory", in Proceedings of 48th Design Automation Conference (DAC 2011), pp. 960-965, June 2011.

Jason Cong, Hui Huang and Wei Jiang, "Pattern-Mining for Behavioral Synthesis", IEEE Transactions on Computer-Aided Design (TCAD 2011), Volume 30, Issue 6, pp. 939-944, June 2011.

Jason Cong, Hui Huang and Wei Jiang, "A Generalized Control-Flow-Aware Pattern Recognition Algorithm for Behavior Synthesis," in Proceedings of Design, Automation and Test Europe (DATE 2010), pp. 1255-1260, March 2010.

# **Chapter 1. Introduction**

## 1.1 Customizable Heterogeneous Architecture

As discussed in [2], in order to meet ever-increasing computing needs and overcome power density limitations, the computing industry has halted simple processor frequency scaling and entered the era of parallelization, with tens to hundreds of computing cores integrated in a single processor, and hundreds to thousands of computing servers connected in a warehouse-scale data center. However, such highly parallel, general-purpose computing systems still face serious challenges in terms of performance, power, heat dissipation, space, and cost. Recently the research focus has moved from parallelization to domain-specific customization in which computing engines and interconnects can be specialized to a particular application domain to gain significant improvement in power-performance efficiency comparing to general-purpose architecture.

The motivation of domain-specific customizable computing platform is derived on three observations:

1) Each user typically has a high computing demand only in one or a few selected application domains (e.g., graphics for game developers, circuit simulation for integrated circuit design houses, financial analytics for investment banks) [2], which makes developing a customizable computing platform where computing engines and memories can be specialized to a particular application domain possible. Taking the advantage of the domain-specific knowledge, these architectures normally can gain significant improvements in power-performance efficiency comparing to a general-purpose architecture.

- 2) The power-performance gap between a fully customized platform, such as application-specific integrated circuit (ASIC), and a general-purpose platform can be very large. A case study of the 128-bit key AES encryption algorithm is discussed in [2]. An ASIC implementation in 0.18um CMOS achieves 3.86Gbits/second at 350mW, while the same algorithm coded in Java and executed on an embedded SPARC processor yields 450bits/second at 120mW. This difference implies a performance/power efficiency gap of approximately 3 million Gbits/seconds/Watts.

- 3) It is very costly to implement a fully customized ASIC architecture for each application, due to the fact that the non-recurring engineering cost of an ASIC design at the current 45nm CMOS technology is over \$50M [3] and the design cycle can easily exceed a year. The large ASIC cost also imposes a strong need for an architecture platform to be efficiently customized to a wide range of applications in one domain or a set of domains, which can bridge the huge performance/power gap between ASICs and general-purpose processors with moderate hardware costs.

To realize the order-of-magnitude performance/power efficiency improvement via customization with reasonable cost, both industry and academia have been turning their attention on developing customizable heterogeneous platforms. For example, NVIDIA's Fermi GPU introduces memory customization capability, in which the shared memory space can be reconfigured into either cache or scratchpad memory with multiple possible sizes.

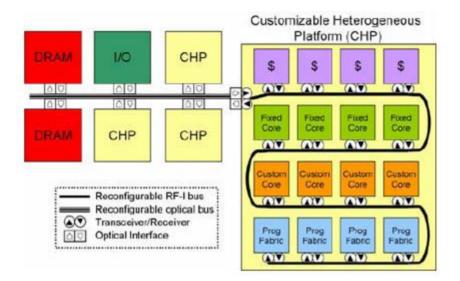

A more general customizable architecture is presented in [2], which includes: 1) integration of customizable cores and co-processors that will enable power-efficient performance tuned to the specific needs of an application domain; and 2) reconfigurable high-bandwidth and low-latency on- and off-chip interconnects, which can be customized to specific applications. Figure 1-1 illustrates an example of such customizable

domain-specific architecture, in which a set of fixed cores coexist with customizable cores, programmable fabric, and a set of distributed cache banks (\$).

Figure 1-1. Customizable heterogeneous platform for domain-specific computing.

As we know, fixed cores can vary dramatically in their energy efficiency, computational power, and area, but have limited reconfigurability. One example of this kind of architecture is the IBM Cell, with one general-purpose PPE core and the more numerous, but simpler, SPE cores. On the other hands, customizable cores provide coarse-grained adaptation to application demand, offering a number of discrete, tunable options that can be set, with flexibility somewhere between FPGAs and fixed cores. It is possible to design cores with a rich set of tunable characteristics to enable significant performance/power efficiency, such as customizable vectorization support or computing accelerator support.

With the emergency of the customizable domain-specific platform, one of the main challenges is how to efficiently take the advantage of the heterogeneity and customization features in those architectures.

This problem can be recapped as how to map one or a set of applications to a customizable heterogeneous platform with high performance/power efficiency. Considering that manual optimization is time-consuming and also not scalable as the design space increases, it is very important to develop efficient compiler support to automate this platform mapping.

# 1.2 Compiler Support for Customizable Domain-Specific Computing

As we discussed, with the support of customizable domain-specific platform, performance/power efficiency can be significantly improved by adapting architectures to match the requirements of a given application or application domain. On the other hand, this also imposes challenges on the compiler size to provide high-quality mapping solution on such reconfigurable architectures. The existence of heterogeneity greatly increases the complexity of its programming model. For example, the code executed on host processors cannot be directly used on hardware accelerators. In addition, explicit data transfers are required for host-accelerator communication. In this section, we will briefly look through three customizable heterogeneous platforms, including tightly-coupled customized vector unit and loosely-coupled programmable accelerators and customizable memories.

#### 1.2.1 Customizable Vector Unit

It has been discussed that customization can achieve significant power-performance efficiency improvement [21], and this is also the case with the vector or SIMD applications. Recently increasing attention has been given to customized vector ISA support from both academia and industry. For example, Convey system [39] supports application-specific vector instruction set, with which users are allowed to reconfigure the vector ISA to match different application features. The authors of [16] propose a

SystemC-based support for customized vector instruction. The work in [15] introduces a customized vector instruction set for multimedia applications and the work in [36] explores customized SIMD units with high-level synthesis techniques.

This trend presents new challenges to both compiler and architecture designs to provide efficient customized vector ISA support. At compiler side, the challenge will be how to efficiently identify application/domain-specific vector instruction and perform automatic customized vectorization.

A crucial step to achieve high performance in a customized vector design is the identification of frequently executed instructions. There already exist extensive work on customized *scalar* instruction exploration [12][17][38]. However, a naïve employment of the existing techniques without considering the vector features will result in inefficient customized vector instruction generation. For example, one important feature of vector processing is the existence of memory alignment. For example, AltiVec requires memory accesses to be aligned at a 16-byte boundary and it cannot handle unaligned vector loads and stores; In AVX mis-aligned memory accesses are supported with a large performance penalty.

We introduce an automatic LLVM-based compilation flow to extract customized vector instructions from one or a set of applications. Pattern recognition approaches have been used here to identify frequently appeared customized vector instruction candidates and an optimal alignment insertion scheme has been developed to reduce the memory alignment overhead. This flow is tested on the composable vector processing units (CVUs), which can be chained together to create customized vector instructions. This design allows programmable customized vector extensions and can achieve up to 52% speedup over standard vector ISA and 14.6X area gain over the dedicated ASIC-based design.

#### 1.2.2 Customizable Computing Accelerator

Programmable accelerator (*PA*) has been proposed to enable varying degrees of customization together with general-purpose cores [51] [54] [55] [56] [57]. In a standard PA architecture, a programmable accelerator template is implemented inside each PA unit to support a selected set of computation tasks with reasonable hardware design costs. The entire pre-defined PA template may support a relatively complicated computation task, while it can be reconfigured dynamically to perform a set of simpler but more general sub-tasks. Therefore, each accelerator unit in a PA-rich system can be customized to computation tasks with different granularity, which enables efficient switching among varying degrees of customization at runtime.

With more flexible customization support, the PA-rich design has been raised as a promising solution to improve the system performance-power efficiency. However, this design trend imposes a demanding challenge on the compiler side – how to generate high-quality PA mapping code which can efficiently utilize the programmable execution units existing in a PA-rich architecture.

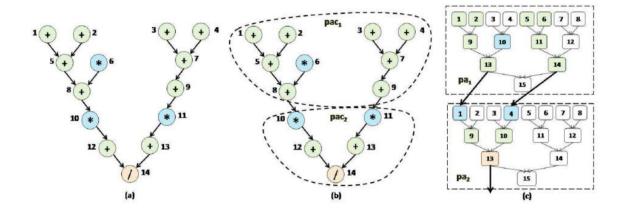

In general, the PA compilation flow can be divided into two phases - PA candidate identification and PA template mapping. Given the data flow graph (DFG) of application kernels, the PA candidate identification phase extracts all the data flow subgraphs which are executable on the PA units. To decide whether a subgraph is executable on PA units, subgraph isomorphism checking is performed between the subgraph and the PA templates. After that, the identified candidates will be fed into the mapping phase, in which a subset of candidates will be mapped to PA templates to accelerate the target kernels.

As discussed in [60], since the PA candidates identification and PA mapping problems are both difficult to solve, scalability has been considered as a main problem in the existing PA compilation flows. Considering that the number of PA candidates grows exponentially with the size of input DFG and PA template, the mapping problem may become

intractable for large DFG blocks. When disjoint PA candidates are considered, the mapping problem size is even larger after including all the legal combinations of connected PA candidates.

The other challenge comes with the pipelined PA execution. In a fully pipelined PA design, input data comes in at every clock cycles, buffers or dummy PAs [99] need to be inserted to guarantee the correctness of pipeline behavior. This serves as a new demanding resource requirement, which is not considered in previous work.

Targeting scalable PA compilation of fully pipelined execution, we build an automatic PA compilation flow, which supports both connected and disjoint PA candidates. Delay units are inserted in the PA mapping graph to balance the path delays in a pipelined execution. Comparing to the scalable PA compilation approaches proposed in [60] and [55], our approach achieves a significant reduction on the overall compilation time. The corresponding mapping quality has been improved by 23.8% and 32.5% on average for mapping the connected-only and disjoint PA candidates, respectively. We also investigate the impact of a given throughput target on resource usage in accelerator pipelines. Here resource usage includes not only PAs, but also delay units required to balance path delay. An optimal PA mapping algorithm is used to efficiently map on-chip accelerator resources to a pipelined execution. Compared to the PA compilation approaches proposed in [60], our approach achieves a significant reduction on mapping size and up to 33.8% improvement on system performance.

#### 1.2.3 Customizable Memory

Modern high performance processors are known to be abundant in processing elements, e.g. general-purpose cores or customized hardware accelerators (FPGA, GPU, etc.). Memory accesses become an increasing performance bottleneck, preventing applications from fully exploiting the computing power. To alleviate the memory bottleneck, communication optimizations, including memory latency reduction and efficient

bandwidth utilization, turns out to be crucial for system performance and energy efficiency. Traditional hardware-controlled cache suffers from 'blind' data movement decisions, which are made independent with program behavior. As an alternative, software-controlled memories (SCM) have been employed either as an independent storage unit or sitting together with D-cache/I-cache to effectively enhance performance and power. This trend has already been reflected on real designs, e.g., NVIDIA's latest Fermi GPU has software controlled scratchpad memories (SPM) called "shared memory" which can be partitioned into cache and SPM at configuration points 1:3 or 3:1, with SPM and L1 cache sitting on top of L2 cache. Similarly, the local store in IBM's Cell broadband can be managed as a combination of direct buffers to store access with regular patterns and software-controlled cache as a fall-back solution [73].

Comparing to single-level SCM, multi-level SCM designs provides better tradeoff the access speed difference between different memory levels, therefore has been widely explored. In typical embedded processors, the L1 SCM normally consists with fast SRAM memories (e.g. scratchpad memories) and last level (LL) SCM can be either SRAM or DRAM (e.g. FPGA's off-chip memory and GPU's global memory). The optimization target of SCMs sitting at different memory level also differs.

L1 SCM normally is a small piece of fast memory, which sits closest to the computing core and is responsible to feed data in time. Targeting low memory access latency, L1 SCM has been utilized as prefetch buffers in embedded systems and parallel architectures to hide memory access latency [1]. This is motivated by the fact that conventional cache prefetching suffers from the problem that the data evicted from cache by the newly prefetched data is still "alive," i.e., will be accessed frequently in the near future. An extreme case is that N prefetched elements are mapped to the same set in a direct-mapping cache. Therefore, only the last element will be kept in the cache after prefetching, while the previous N-1 data transfers are useless with additional energy

overhead. On the other hand, SCM-based prefetching can make a "smart" eviction decision, thereby avoiding such cache prefetch inefficiency.

On the other hand, shared last level SCM has been widely utilized in heterogeneous parallel architectures to tradeoff the low bandwidth from main memory. For example, the performance of PCIe bus connecting host memory is ~10GB/s, which turns out to be an important bottleneck of modern heterogeneous systems. Accordingly, how to efficiently reuse the data stored in LL-SCM becomes one of the major compiler challenges in a heterogeneous system where workloads distributed on different computing cores. Compared to hardware-controlled memories, the introduction of SCM as a last level buffer offers optimization potential on cross-core data transfers by taking the advantage of the knowledge of target applications.

To fully utilize the multi-level SCM memory space, we have investigated prefetching and reuse capability for L1 and LL SCM, respectively. We propose a reuse-aware SCM prefetching scheme, called RASP, to hide memory access latency and minimize the number of data transfers from lower-level memory; To efficiently manage LL-SCM, we propose a task-level-reuse-graph based LL-SCM data movement scheme to minimize the amount of data transfers between heterogeneous computing cores through the slow PCIe bus. An average 25% reduction of host-accelerator data transfers is observed from previous work.

# Chapter 2. Compiler Support for Customizable Vector Instruction Extension

Vectorization has been commonly employed in the high performance computing domain to exploit data-level parallelism in those applications. In this chapter we analyze the needs and opportunities to explore customized vector instructions and quantify their benefits. We build an automatic compilation flow in LLVM-2.7 compiler infrastructure to efficiently identify customized vector instructions from a given set of applications. The memory alignment overhead, which is known to be critical for vector processing efficiency, has been optimized in our customized vector ISA exploration flow. This flow is tested on the composable vector units, which can be used separately or in a chained mode to support a large number of (virtual) customized vector instruction units with minimal area overhead. The results show that our approach achieves an average 27% speedup over the state-of-art vector ISA. We also observe a large area (around 11.6X) gain over the dedicated ASIC-based design.

#### 2.1 Introduction

SIMD vector processors are very effective in executing programs with extensive data-level parallelism, such as multimedia processing, graphics and scientific computing. In recent years, vector extension has become one of the most common additions to both general purpose microprocessors and super computers, due to the growing demands on high-performance computing. There are several state-of-art vector ISAs in the market, such as Intel's AVX [40], Motorola/IBM's AltiVec [23].

It has been recognized that customization can achieve significant performance improvement [15] and this is also the case with the vector or SIMD applications.

Recently increasing attention has been paid to customized vector ISA support. The authors of [12] propose SystemC-based support for customized vector ISA. The work in [11] introduces a customized vector instruction set for multimedia applications. The work in [23] designs customized SIMD units with high-level synthesis techniques. The newly developed Convey system [26] provides supports for application-specific vector instruction sets, with which users are allowed to reconfigure the vector ISAs to match different application domains. This trend presents new challenges to both compiler and architecture design to provide efficient customized vector ISA support with small hardware cost.

At compiler side. the main challenge is how efficiently identify application/domain-specific vector instructions and perform automatic customized vectorization. A crucial step to achieve high performance in a customized vector design is the identification of frequently executed vector instructions. There already exist extensive work on customized scalar instruction exploration (e.g. [8][13]. However, a naïve employment of the existing techniques on the input program without considering the vector features will result in inefficient customized vector instruction generation. One important feature of vector processing is the existence of memory alignment problem raised by the vector architecture [18]. For example, AltiVec requires memory accesses to be aligned at a 16-byte boundary and it cannot handle unaligned vector loads and stores; In AVX mis-aligned memory accesses are supported with a large performance penalty.

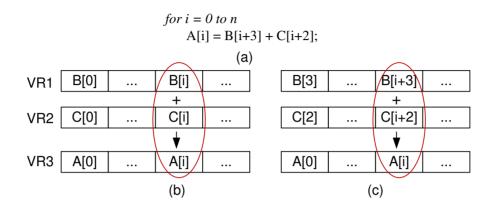

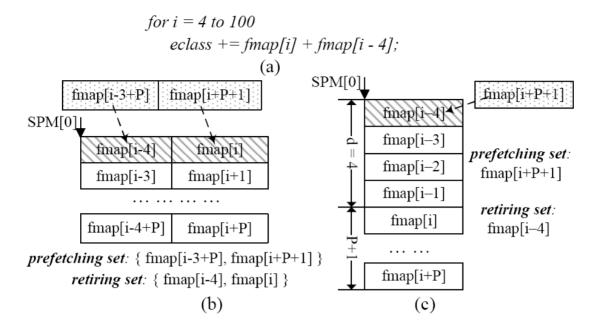

Here a mis-aligned memory reference means that the address of the data is not a multiple of the vector register size [26]. Let's look at the example in Figure 2-1 (without loss of generality, we assume for array reference  $A[i_1][i_2]...[i_N]$ , the starting address of each array dimension, namely A[0][0]...[0],  $A[i_1][0]...[0]$ ,  $A[i_1][i_2]..[i_{N-1}][0]$ , has been aligned to memory boundary).

As shown in Figure 2-1(b), arrays A, B and C are loaded into vector register VR1-3 in a mis-aligned manner. If we directly perform a vector add on the 3 vector registers, it will generate incorrect results, where A[i] = B[i] + C[i]; to resolve it, vector register VR1 and VR2 are shifted to left by 3 elements and 2 elements, respectively in Figure 2-1(c).

Therefore, in order to ensure the functionality correctness, the "shifted" alignment of the input nodes needs to match that of the output node. This alignment constraint imposes challenges on automatic vectorization process due to its sizable impact on the power-performance efficiency in vector processing.

Figure 2-1. (a) One example loop (b) Mis-aligned vector addition (c) Aligned vector addition.

In the customized vector ISA exploration phase, if the memory alignment issue has not been resolved properly, it may result in undesired overhead on performance. Let's consider a vectorizable loop shown below (without loss of generality. Here we assume A[0], B[0], etc. are aligned to memory boundary).

$$for i = 0 to n$$

$$A[i] += B[i+1]*C[i];$$

The scalar customized instruction candidates inside this loop only contain one multiply-add (MAC) operation. While for vector exploration, since additional alignment instructions are required to resolve the unaligned array reference B[i+1], both MAC and aligned MAC should be considered as customized vector instruction candidates, as shown in Figure 2-1(b). If we simply replace the sequential loop with unaligned vector MAC operations, it may result in either incorrect execution or pay considerable performance penalty.

Earlier implementations of vector processor [7] [18]re all based on non-customized vector instructions. The vector instructions in VIRAM are designed to vectorize

embedded system applications by adding support for narrower data-type and different styles of permutation. VESPA [26] is a flexible FPGA-based vector engine. However it only supports integer vector operations.

Figure 2-2. (a) Customized scalar instruction candidates (b) Customized vector instruction candidates.

In this chapter we introduce an automatic compilation flow to perform alignment-efficient customized vector instruction identification, and the architectural support for area-efficient customized vector operations.

- (1) We identify the existing opportunities to derive customized vector instructions. A boundary-extension technique and an operation-based vectorizability checking technique are developed to fully investigate customized vector instruction exploration space.

- (2) We propose an LLVM-based compilation flow to extract customized vector instructions from one or a set of applications. Pattern-based approaches have been used here to identify beneficial customized instruction candidate

- (3) We propose an optimal memory alignment scheme that minimizes the total *shifting distance* to generate alignment-efficient vector patterns.

This flow is tested on the composable vector processing units (CVUs), which can be chained together to create customized vector instructions. This design allows programmable customized vector extensions and can achieve up to 52% speedup over standard vector ISA and 14.6X area gain over the dedicated ASIC-based design.

### 2.2 Motivational Example

In this section, we illustrate the existence of application-specific or domain-specific customized vector patterns with real-life applications.

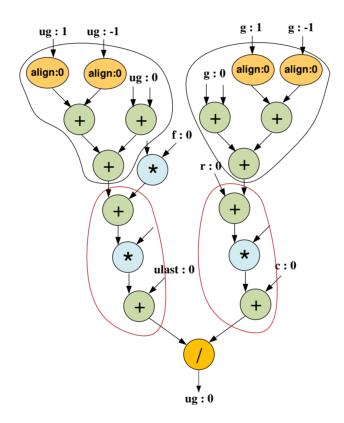

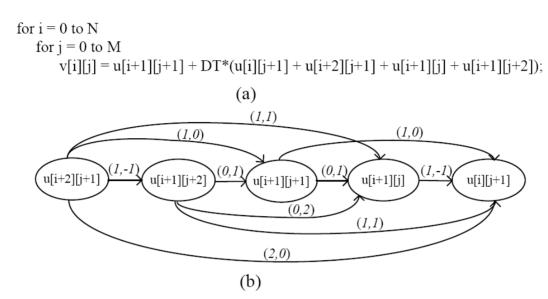

Let's first consider one computation kernel in *jacobi rician-denoise* [41] which is a double precision floating point application in the medical imaging domain. Figure 2-3 shows the kernel loop in this application, which performs five-point stencil computation on a 2D image. Seven arrays are involved in the computation kernel as inputs and the loop body can be vectorized without violating data dependencies. (here we only consider vectorization through the innermost loop)

```

for m = 1 to M - 1

for n = 1 to N - 1

u[m][n] = (ulast[m][n] + DT * (ug[m][n+1] + ug[m+1][n] + ug[m+1][n] + ug[m-1][n] + GM*f[m][n]))

/(c[m][n] + DT * (g[m][n+1] + g[m+1][n] + g[m+1][n] + g[m-1][n] + r[m][n]))

```

Figure 2-3. . One kernel loop in jacobi rician-denoise.

Figure 2-4 shows the corresponding data flow graph for the vectorizable loop, in which each node represents a vector instruction, such as vector-add or vector-multiply. Each vector input is denoted by the array name followed by alignment value normalized to output u[m][n]. For example, the relevant alignment offset between u[m][n] and

ug[m][n-1] is 1, therefore "ug:1" has been used to represent vector input ug[m][n-1].

From Figure 2-4, we can see the two branches of *div* operation are similar to each other in terms of both operation counts and data path. The left branch contains nine operation nodes and the right one contains eight nodes – only differ from each other by one *mul* operation, which exposes the opportunity to extract repeatedly executed customized vector instructions, sizing from one operation to eight operations. Two vector pattern candidates with occurrence equaling two have been highlighted in Figure 2-4.

Figure 2-4. Data flow graph of kernel loop in jacobi rician-denoise.

In this example, note that since ug[m][n+1] and ug[m][n-1] both serve as inputs to the same vector add operation and they are mis-aligned array references, two alignment nodes are inserted to match them to the alignment offset of ug[m][n], namely 0. The same scenario also applies to array reference g[m][n-1] and g[m][n+1]. Our optimization on

alignment node insertion will be discussed in Section 2.3.

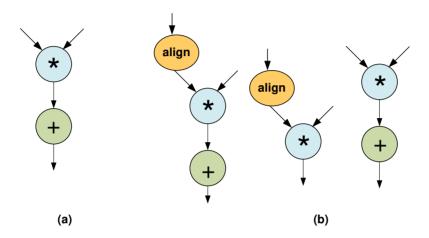

In addition to application-specific customized vector patterns, there also exist common vector patterns inside a specific application domain due to the similarity in computing models or algorithms, as shown in Figure 2-5. Figure 2-5(a) shows a double precision vectorizable accumulation of SQR operation, e.g., a[i]\*a[i]. The kernel code pieces in Figure 2-5(b) and (c) are extracted from *rician-denoise* and *level-set segmentation* [41] in the medical imaging domain. The vectorizable SQR-accumulation operation appears in both applications (4 times in *rician-denoise* and 3 times in *segmentation*), thus they can benefit from the same customized vector ISA extension.

Figure 2-5. (a) Data flow graph of SQR-accumulate (b) Kernel code piece in *jacobi* rician-denoise (c) Kernel code piece in *level-set segmentation*.

#### 2.3 Customized Vectorization Flow

Figure 2-6 shows the components of our customized vector instruction identification framework. This framework is implemented in LLVM-2.7 compiler infrastructure [42] with Omega Library [43] for dependency analysis. The flow is invoked as a back-end pass on the optimized LLVM intermediate representation (IR) code. As discussed in [9], automatic vectorization performed at source-level is usually decoupled from standard back-end optimization, comparing to lower-level IR, which is closer to the machine-level

code and can take the advantage of operating on optimized code. In our case, the optimized LLVM IR is used as top-level input in the customized vector instruction identification framework.

Figure 2-7 shows the kernel loop in *rician-denoise* application (to better illustrate each step in the framework, *gauss-seidel* implementation [41] is used here, which contains loop-carried true dependency).

Figure 2-6. Customized vector instruction identification flow.

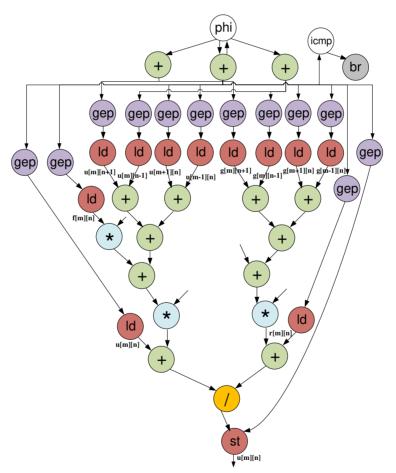

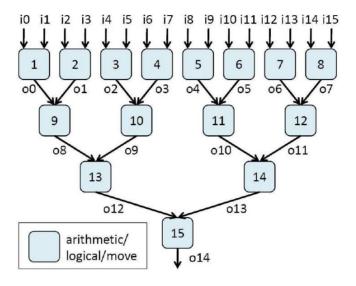

The data flow graph of the corresponding LLVM intermediate representation is shown in Figure 2-8. Each node in the data flow graph is labeled with the operation it performs and each edge represents the data flow dependency between two nodes.

```

for m = 1 to M - 1

for n = 1 to N - 1

u[m][n] = (u[m][n] + DT * (u[m][n+1] + u[m][n-1] + u[m+1][n] + u[m-1][n] + GM*f[m][n]))

/ (c[m][n] + DT * (g[m][n+1] + g[m][n-1] + g[m+1][n] + g[m-1][n] + r[m][n]))

```

Figure 2-7. Kernel code of gauss-seidel rician-denoise.

In this example, the node phi generates the value of loop induction variable n for the inner loop. If the value is obtained from the outer loop body, n equals 1; otherwise, n equals its current value plus one, namely the output of the add node under phi. To

calculate the address at the second array dimension for references u(g)[m][n-1] and u(g)[m][n+1], another two add nodes below phi accept the output of phi node, namely the value of n, and perform the corresponding array subscript calculation. The calculated array indices are sent to the getelementptr (gep) node to generate the address for the corresponding array element, which is followed by a load (ld) operation to access memory.

#### Algorithm 2-1. Vectorizable Code Region Extraction

- 1. G: LLVM-IR-based data flow graph of a given loop nest

- 2. BI: a set of boundary array / scalar input nodes in G

- 3. BO: a set of boundary output nodes in G

- 4.

- 5. for each node v in G,

- 6. if there exist a path from v to one node in BO and a path from one node in BI to v,

- 7. add v to V;

- 8. for each node v in V sorted in topological order,

- 9. if for any input t to v,  $t BI \cup V_{vec}$ ,

- 10. add v to V\_vec;

- 11. else

- 12. if there exists an edge t' $\rightarrow$ v such that t' BI  $\cup$  V\_vec,

- 13. add v to BI;

#### 2.3.1 Vectorizable Code Region Extraction

To extract the customized vector patterns which perform real computations, we need to remove the complementary nodes existing in the original LLVM IR, such as the loop invariant and branch instructions. Note that this cannot be achieved by simply removing operations in those classes and then performing customized vector instruction exploration on the reduced data flow graph. For example, in Figure 2-8 the three *add* operations below the *phi* node perform address calculation instead of real computation, thus should not be explored as customized vector instruction candidates. In our flow, we propose a *boundary-node-directed* vectorizable code region extraction approach.

Figure 2-8. Data flow graph of gauss-seidel rician-denoise.

Definition 2-1. The boundary nodes of the vectorizable code region in loop L are defined to be the legal inputs and outputs to a vector instruction, including memory load/store operations to continuous memory space (here we only consider array subscript as a linear combination of loop induction variable and constant), constants and scalar variables with value fixed inside L.

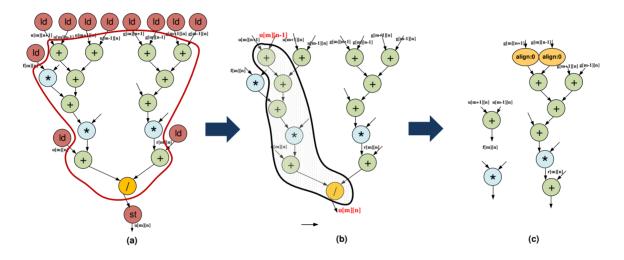

In <u>Algorithm 2-1</u>, any node that locates outside the subgraph enclosed by the boundary nodes will be removed, as shown in Figure 2-9(a).

Figure 2-9. Complementary code elimination, vectorizability checking and alignment node insertion in the kernel code of *gauss-seidel rician-denoise*.

The nodes in set V but not  $V\_vec$  are called "prohibited nodes", Those nodes cannot be vectorized due to illegal inputs. For example, the third addition in Figure 2-10(a) accepts random array access as input, which makes it in-vectorizable. However, we can introduce temporary arrays and apply loop distribution techniques to make it become a new "boundary node" (lines 11-12). In this case the operations following the in-vectorizable node will not be prohibited from vectorization, which helps to enlarge the customized vector pattern exploration space. As shown in Figure 2-10(b), L add operations in second inner loop can be performed in parallel. (Assume L equals the vector register length) This technique is referred as boundary extension in the remaining part of this chapter.

```

for \ i = 0 \ to \ n

A[i] = B[i] + *(ptr[i]) + C[i];

(a)

for \ i = 0 \ to \ n \ with \ step \ size \ L

for \ j = 0 \ to \ L

tmp[j] = *(ptr[i+j]);

for \ j = 0 \ to \ L

A[i+j] = B[i+j] + tmp[j] + C[i+j];

(b)

```

Figure 2-10. (a) Original code (b) Transformed code.

## 2.3.2 Operation-based Vectorizability Checking

Theorem 2-1. [29] A statement contained in at least one loop can be vectorized if the statement is not included in any cycle of dependences.

In the traditional loop vectorization techniques [29], one statement contains a set of operations and a corresponding memory store. For example, the statement in Figure 2-7 contains 13 operations. In those techniques, each statement is treated as the basic vectorization unit. However, this may lead to the loss of existing vectorization opportunities. For example, the loop body in Figure 2-7 contains one statement with self-dependency cycle. Based on Theorem 2-1, if the traditional approach is applied, all of the 13 operations inside that statement will be treated as in-vectorizable nodes. However, since the loop-carried true dependency only exists between u[m][n] and u[m][n-1], the nodes operated on the other array references can be executed in parallel without violating the existing dependency. Those vectorization opportunities will be missing in the statement-based approach.

To fully investigate the customized vector pattern space, we perform an *operation-based* dependency checking after applying the conventional statement-based approach. In the proposed operation-based dependency checking, each operation node in the vectorizable code region is treated as the basic vectorization unit to allow partial vectorization inside

one statement.

#### Algorithm 2-2. Vectorizability Checking

- 1. V\_vec : vectorizable nodes obtained from Algorithm 2-1.

- 2. S: a set of statements inside the given loop nest

3.

- 4. Perform statement-based vectorization algorithm [28] on *S*, add the nodes adjacent to the violated dependency edges to *N*;

- 5. **for** each node n in N,

- 6. remove n from  $V_{vec}$  and add it to N;

- 7. **for** each node v in  $V\_vec$  sorted in topological order,

- 8. **if** there exists an edge  $v \rightarrow n$  or  $n \rightarrow v$  such that  $n \in N$ ,

- 9. remove *v* from *V* vec and add it to *N*;

In Algorithm 2-2, the statement-based vectorization algorithm is first applied to differentiate vectorizable and in-vectorizable statements. For the in-vectorizable statements, further dependency checking is performed in an operation-based manner. Assume the statement is not vectorizable due to a set of violated dependency edges, lines 8-9 separate the operation nodes carrying the violated dependencies from those not. As shown in Figure 2-9(b), the violated dependency is between u[m][n-1] and u[m][n], the add operation associated with u[m][n-1] has been excluded from the vectorizable code region after dependency checking, as well as the downstream nodes reachable from u[m][n-1]. The statement can be partially vectorized by executing the unshaded nodes in parallel. By applying the operation-based vectorization check, the exploration space for customized vector pattern is further enlarged and exposes more opportunity to extract

beneficial instruction candidates. Comparing to statement-based approach, the extra complexity overhead of Algorithm 2-2 is  $O(|V\_vec|)$  where  $|V\_vec|$  is the number of nodes in the vectorizable code region.

## 2.3.3 Vectorizable Data Flow Graph Expansion

In this section we describe techniques to insert *alignment instructions* explicitly into the original data flow graph in presence of mis-alignment. The *alignment offset* of a memory access is defined as the byte-offset to the memory boundary of the array elements to be accessed at the first iteration in a normalized loop. For example, in the loop in Figure 2-1(a), the alignment offsets for accessing array *X* and *Y* are 3 and 2, respectively.

An alignment instruction is one that combines results of two neighboring vector load instructions and logically performs a shift on the vector registers. Note that there are different ways to insert alignment instructions. In [24] several heuristics are described, including zero-shift, eager-shift, lazy-shift and dominant-shift. A typical strategy is shown in Figure 2-11(a).

```

B'[i] = B[i+3]; \text{ //shift by 3} \\ C'[i] = C[i+2]; \text{ //shift by 2} \\ A[i] = B'[i] + C'[i]; \\ (a) \\ B'[i+2] = B[i+3]; \text{ //shift by 1} \\ A'[i+2] = B'[i+2] + C[i+2]; \\ A[i] = A'[i+2]; \text{ //shift by 2} \\ (b)

```

Figure 2-11. (a) Shifting scheme 1 (b) Shifting scheme 2.

Here the total shift distance is 3+2=5. Yet, when each alignment instruction shifts a vector register by only one, the solution is suboptimal. A better solution is in Figure 2-11(b), where the total shifting distance is 1+2=3.

In this chapter, we introduce an optimal shift scheme, with the goal of minimizing the total shifting distance; as in our architecture, we shift by one for each alignment instruction to reduce hardware cost. Our method is based on a mathematical

programming formulation, and is able to obtain the optimal solution efficiently by taking advantage of the total unimodularity of the constraint matrix.

Without loss of generality, we consider a data flow graph where each node is either a memory load/store or an arithmetic instruction that takes two inputs produces one output. For each arithmetic instruction I, a pair of integers  $(\beta_1, \beta_2)$  is introduced to model its alignment property, where  $\beta_1/\beta_2$  is the relative offset of the first/second input operand with regard to the output of I. In the previous example, the addition operation has an alignment vector (3, 2). For each arithmetic instruction I, we associate a label on each of its port  $o_I^1, o_I^2, o_I^3$  to indicate the actual alignment offset on its input operand  $o_I^1, o_I^2$  or its output  $o_I^3$ . To ensure correctness after alignment, we need to make sure

$$o_I^1 - o_I^3 = \beta_I^1 \tag{1}$$

$$o_I^2 - o_I^3 = \beta_I^2 (2)$$

This constraint means that the relative alignment offset between each input operand and the output value is fixed, and that they can be changed simultaneously when alignment instructions are inserted properly. In the above example, we have  $o_+^3 = o_+^1 - 3 = o_+^2 - 2$ .

For a memory access instruction m, its alignment offset is always zero, as we only do load/store in aligned fashion. We have constraint

$$o_m = 0 (3)$$

When the output of an instruction s is used by another instruction t as its first (or any other) operand, alignment instructions may be needed to shift the result of s. Let  $d_s$  denote the shifting distance, and we have

$$o_s^3 - o_t^1 \le d_s$$

(4)

$$o_t^1 - o_s^3 \le d_s$$

(5)

he above constraints means that we need to shift at least  $|o_s^3-o_t^1|$ .

When instruction s is used by multiple instructions  $\{t_1, t_2, ..., t_m\}$ , the total shifting distance is at least  $o_{ti}^{\ 1}$ - $o_{tj}^{\ 1}$ . This is because any alignment offset between  $o_{ti}^{\ 1}$  and  $o_{tj}^{\ 1}$  will be covered during the alignment. We have

$$o_{ti}^{1} - o_{tj}^{1} \le d_{s,}$$

for all i,j (6)

Combining the above constraints, we have the following formulation as an integer-linear programming.

minimize  $\sum d_s$

subject  $o_I^1 - o_I^3 = \beta_I^1$  for all instruction I

to

$o_I^2 - o_I^3 = \beta_I^2$  for all instruction I

$o_m = 0$  for all memory access

m

$o_s^3 - o_t^1 \le d_s$  for all s used by t

$o_t^1 - o_s^3 \le d_s$  for all s used by t

$o_{ti}^{1}$ -  $o_{tj}^{1} \le d_s$  for all s used by  $t_1$  and  $t_2$

All variables are integers (7)

The above formulation tries to minimize the total shifting distance for all values. For the aforementioned example, denote the instructions as  $1(\log x)$ ,  $2(\log y)$ , 3(the addition), 4(store to z), the formulation is

minimize  $d_1 + d_2 + d_3$

subject to  $o_1 = 0$

$$o_{2} = 0$$

$$o_{4} = 0$$

$$o_{3}^{1} - o_{3}^{3} = 3$$

$$o_{3}^{2} - o_{3}^{3} = 2$$

$$o_{1} - o_{3}^{1} \le d_{1}$$

$$o_{3}^{1} - o_{1} \le d_{1}$$

$$o_{2} - o_{3}^{2} \le d_{2}$$

$$o_{3}^{2} - o_{2} \le d_{2}$$

$$o_{3}^{3} - o_{4} \le d_{3}$$

$$o_{4} - o_{3}^{3} \le d_{3}$$

#### All variables are integers

Integer-linear programming formulations are known as a general-purpose tool for modeling combinational optimization problems, including those notoriously hard ones. An typical ILP solver, even if equipped with sophisticated algorithms (like cutting planes, dual decomposition), will still rely on enumerative approaches such as branch-and-bound, and thus still runs in exponential time in many practical cases. Therefore, the problems that can be solved by ILP are limited in practice. Fortunately, for the above formulation, we can show that the integrality constraints are unnecessary. That is, the problem formulation can be solved as a linear programming problem without the integrality constraints, while still guaranteeing integral solutions. This is because we can take advantage of the special structure in the constraint matrix for this specific problem. In the following, we show mathematically why the above formulation can be solved optimally in polynomial time.

Definition 2-2. (Total unimodularity). A matrix A is totally unimodular if every square submatrix of A has a determinant either 0, 1 or -1.

Clearly, a totally unimodular matrix can only have entries 0, 1, or -1. Total unimodularity plays an important role in combinatorial optimization, due to the result in Lemma 1.

Lemma 2-1 [28]. If A is totally unimodular and b is a vector of integers, every extreme point of polyhedron  $\{x: Ax \le b\}$  is integral.

Lemma 2-1 implies that an integer linear programming problem can be solved without the integrality constraints when its constraint matrix is totally unimodular and the right-hand side is integral.

Many previous work have taken advantage of the total unimodularity of the constraint matrix in a number of applications [28]. In fact, our formulation leads to a constraint matrix that has exactly the same structure as that of [19]. Thus the following theorem can be derived:

Theorem 2-2. The problem is tractable and can be solved in polynomial time with linear programming algorithm [19].

After the optimal alignment scheme is derived from the unimodularity of this formulation, the original data flow graph will be expanded to include the corresponding alignment nodes, as shown in Figure 2-9(c).

### 2.3.4 Pattern-Based Customized Vector Instruction

## **Identification**

This section presents the pattern-based approach to efficiently identify the vector pattern candidates from the data flow graph expanded by inserting optimized alignment nodes.

The pattern recognition approach we use is based on [18] work which is very scalable in benefit of subgraph enumeration and similarity checking technique. A breadth-first (HPR) search strategy is adopted in our flow to discover frequent pattern candidates in practice.

HPR, as suggested by its name, is a complete search algorithm which discovers patterns with a breath-first-search approach. At step k + 1, all the convex patterns with k nodes are

extended by one neighbor node using the proposed subgraph enumeration techniques. After a new subgraph is generated, it is compared to the existing patterns to perform graph isomorphism checking. If a subgraph is isomorphic to an existing pattern P, we call it a pattern instance of P. A characteristic-vector based filtering scheme is adopted to reduce the number of the graph isomorphism checking. The characteristic vector captures important properties of the original subgraph such that if the signature of a subgraph is significantly different than the signature of a given pattern, this subgraph is not needed for matching with the pattern, which avoids the graph isomorphism checking.

By applying the pattern-based approaches to the expanded data flow graph from Section 2.2, we can extract all the frequently executed vector pattern candidates with associated alignment information.

To measure the gain of a given customized vector pattern, we have used a model to estimate the energy-performance-product improvement in our flow. To simplify the model, we do not consider the boundary cases in a loop.

$$g \ a \ (pn) = \#i \ n \ s1t - (P_{c \ r \ i \ i})/c \gamma_{c} (1/L \#i \ n \ s \ t \ d \ i \ s_{i}t_{i})_{g}$$

Here #inst represents the estimated execution time with scalar instruction support; L is the length of vector register, namely the higher level of data parallelism supported by vector architecture. The length of critical path ( $|P_{critcal}|$ ) divided by the data parallelism factor L is used to estimate the vector execution time. Considering that with the complex customized vector patterns, the instruction counts can be reduced accordingly, which corresponds to less energy consumption on instruction decoding logic, as well as the potential reduction in the L1 instruction cache misses. Another benefit comes from the reduced number of branch prediction operation in the transformed vector code. The estimated instruction count ratio between customized vector instruction and scalar instruction equals  $1/L_{\#inst}$ , which is used to measure the difference in power consumption. Note that additional alignment instructions are introduced in the vectorized

code, which should also be taken into consideration in the energy-performance model. Here  $\alpha$  is the scaled energy cost by shifting one element and  $dist_{align}$  is the overall shifting distance introduced by the alignment instructions in the customized vector pattern.

# 2.4 Experiment Results

# 2.4.1 Evaluation Methodology

We have considered nine applications from widely known standard benchmarks suite like Parsec [10] (*streamcluster* and *swaptions*), Rodinia [13][14] (*cutcp*, *mri-q* and *mri-gridding*) and four applications from the medical imaging domain [41] (*denoise*, *deblur*, *registration* and *segmentation*).

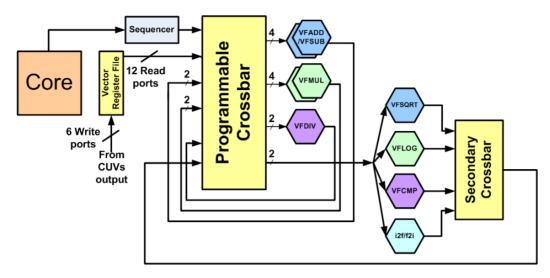

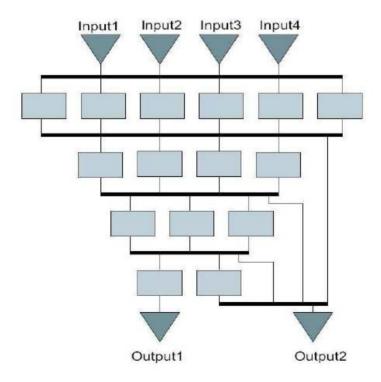

We evaluate the proposed customized vector instruction extraction flow by running full system simulations on each benchmark. The overall simulator framework is implemented upon Simics [31] and the GEMS toolset [32] in the single core configuration. Normal vector engine support has been added to this framework. Figure 2-12 shows our architectural support for composable vector units (CVUs). It consists of a series of CVUs, a programmable crossbar and a sequencer. They are all tightly-coupled connected to the core. The composable vector units are connected together through the programmable crossbar. The inputs to the programmable crossbar are from the outputs of CVUs and the core's register file. The outputs of the crossbar are connected to CVUs. The sequencer, which is programmed by the core, is responsible for reprograming the crossbar in every scheduling step. In this way different connection patterns between CVUs can be supported. Internally the crossbar is a series of multiplexers.

Figure 2-12. The CVU architecture.

# 2.4.2 Pattern Recognition Results

Table 3-1 shows the customized vector pattern recognition results for the nine benchmark kernels. At each row, columns 2-6 represents lines of kernel code, the number of pattern found, the number of pattern instances and runtime, respectively. For example, test bench *streamcluster*, the code in its kernel contains 96 lines of C code, and the 92 vector patterns are found with 240 pattern instances. The overall runtime is less than one second. From Table 3-1 we can see, the average number of instances for each pattern inside the kernel is around 4. The repeated occurrence of the same vector pattern in program kernels exposes the opportunity of program execution speedup by providing the customized vector support for the corresponding pattern.

The last column in Table 3-1 shows the area synthesis result for patterns in each benchmark, in total the area equals 5574062 um<sup>2</sup>.

Table 2-1. Pattern recognition results on 9 computation-intensive benchmarks and their synthesized area on ASIC.

|  | #line | #pattern | #inst | time (s) | Area (um²) |

|--|-------|----------|-------|----------|------------|

|--|-------|----------|-------|----------|------------|

| streamcluster | 96  | 92   | 240  | 0.13 | 117193  |

|---------------|-----|------|------|------|---------|

| swaptions     | 152 | 69   | 292  | 0.21 | 153371  |

| cutcp         | 67  | 78   | 285  | 0.19 | 471836  |

| mri-q         | 79  | 71   | 100  | 0.33 | 62424   |

| mri-gridding  | 119 | 119  | 385  | 0.49 | 904371  |

| denoise       | 274 | 187  | 650  | 0.52 | 1357131 |

| deblur        | 202 | 29   | 151  | 0.24 | 227410  |

| registration  | 222 | 1499 | 3122 | 1.42 | 506124  |

| segmentation  | 179 | 2211 | 4172 | 1.72 | 1774202 |

# 2.4.3 Alignment Optimization Results

To illustrate the of the proposed alignment insertion scheme, we have compared our solution to four alignment policies proposed in [24], in terms of the overall shifting distance and number of inserted alignment nodes (normalized to our solution). The four reference points in this evaluation include:

#### (i) Zero-shift policy (Z)

Shift each mis-aligned array reference to the alignment offset of 0 immediately after it is loaded from memory.

#### (ii) Eager-shift policy (E)

Shift each mis-aligned array reference directly to the alignment of the store.

#### (iii) Lazy-shift policy (L)

Based on the eager-shift policy, but delay shifting as long as the alignment offset matches between nodes with the same output node.

#### (iv) Dominant-shift policy (D)

Shift each mis-aligned array reference to the most dominant alignment offset in the graph.

Table 2-2. Comparison on overall shifting distance.

|                | Z   | E   | L | D   |

|----------------|-----|-----|---|-----|

| fft            | 3.4 | 2   | 2 | 1   |

| streamcluster  | 2.8 | 2.4 | 1 | 2.4 |

| rician-denoise | 1   | 1   | 1 | 1   |

| registration   | 1.5 | 1.5 | 1 | 1.5 |

| segmentation   | 1   | 2   | 1 | 1   |

We list the comparisons among the five alignment policies, as shown in Table 3-2. Here only the results of five applications with complicated mis-aligned patterns, such as stencil computations in the medical imaging domain and the mis-alignment introduced by sum reduction technique in *streamcluster*; The shifting distance in Table 3-2 has been normalized to the proposed solution, in which we can see our solution can generate the minimal shifting distance for all the five applications. Among the four schemes proposed in [24], for a few applications the lazy-shift or dominant-shift solution also equals the optimal one, and outperforms zero/eager solutions. While the intrinsic heuristic feature in the two policies lead to less efficient solutions in other cases. The overhead to calculate the optimal solution is less than 7% of the overall compilation time.

## 2.4.4 Performance Comparison Results

We consider three reference points in the experiments:

(i) Normal vector (NV): Execution of the program using standard state-of-art vector instructions (Intel AVX).

- (ii) **Dedicated custom vector (DCV)**: Execution of the program using dedicated ASIC-based customized vector instructions.

- (iii) Composable vector (CCV): Execution of the program using CVU-based customized vector instructions.

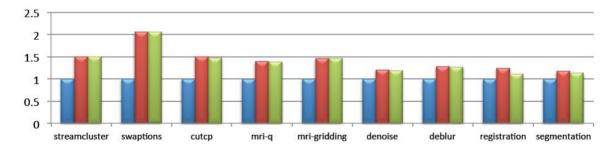

- Figure 2-13 shows the normalized speedup on each individual benchmark. Speedups have been normalized to the normal vector version. We make the following observations:

- (i) Benchmarks such as *mri-gridding*, *mri-q* and *deblur* achieve a very large speedup. This is because the kernels in these benchmarks i.e., the critical functions have a structured pattern which is suitable for our architecture. Our compilation flow successfully captured such vectorizable patterns.

- (ii) Benchmarks *denoise*, *registration* and *segmentation* achieve moderately good speedups. We find the patterns in those benchmarks contains two or three parallel *add* and *mul* operations. Due to the available CVU resource constraint we have, such parallelism cannot be fully supported in the CVU-based design.

- (iii) The execution time difference between CCV and DCV is very small. Though the latter design does not need to consider the resource constraint. On average CCV is 5% slower than the DCV design on all the benchmarks, which further illustrate the efficiency of our CVU configuration selection strategy.

Figure 2-13. Normalized speedup.

# 2.5 Conclusion and Future Work

Customized vector domain has attracted increasing attention from both academia and industry. To provide efficient customization support, in this chapter we introduce an

LLVM-based compilation flow to perform automatic customized vector ISA extension. A composable vector unit (CVU) is proposed to support a large number of customized vector instruction by allowing chaining among vector units. Our future direction is to extend the composable vector unit design to a multi-core environment such that the CVUs can be shared among multiple requesting cores.

# Chapter 3. Compilation for Programmable Accelerators

In recent days programmable accelerators (PA) are widely investigated in the design of domain-specific architectures to improve the system performance and power. Micro-architectures with a series of PA have been proposed to provide more general supports for customization. One important feature in the PA-rich systems is that the target computational kernels can be compiled with pre-defined PA templates and dynamically mapped onto real PAs at runtime. This imposes a demanding challenge on the compiler side regarding how to generate high-quality PA mapping code. In this chapter, we present an efficient PA compilation flow which is fairly scalable in mapping large computation kernels into PA-rich architectures. A concept called maximal PA candidate is proposed to drastically reduce the number of input PA candidates in the mapping phase without influencing the mapping optimality. Efficient pre-selection and pruning techniques are employed to further speedup the maximal PA mapping process. Our experimental results show that for 12 computation-intensive standard benchmarks, the proposed approach achieves a significant improvement on the compilation time comparing to the state-of-art PA compilation approaches. The average mapping quality is improved by 23.8% and 32.5% for connected PA candidates and disjoint ones, respectively.

# 3.1 Introduction

Customization is an appealing solution to increase performance power efficiency, which is one of the primary design concerns in the era of many-core systems. A recent industry trend to address it is introducing computation accelerators in many-core designs. The Convey system [51], Intel's Larrabee [52] and Nallatech [53] are example of this. The accelerators, which are normally designed as specialized hardware blocks in the general-purpose processors, can be implemented to support a wide variety of tasks, ranging from fairly simple ones (e.g., a multiply accumulate operation) to more complex

ones (e.g., FFT, encryption/decryption or video encoding/ decoding). However, very complicated accelerators will suffer from the same non-recurring hardware cost as most ASIP work does. On the other hand, a simple accelerator design, which may be general enough for most applications, cannot achieve significant power-performance gains with limited hardware specialization.