### Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Oct 2005

## Complex Power Distribution Network Investigation using SPICE **Based Extraction from First Principle Formulations**

Giuseppe Selli

James L. Drewniak Missouri University of Science and Technology, drewniak@mst.edu

Richard E. DuBroff Missouri University of Science and Technology, red@mst.edu

Jun Fan

Missouri University of Science and Technology, jfan@mst.edu

et. al. For a complete list of authors, see https://scholarsmine.mst.edu/ele\_comeng\_facwork/1510

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

G. Selli and J. L. Drewniak and R. E. DuBroff and J. Fan and J. L. Knighten and N. W. Smith and D. McCoy and B. Archambeault and S. Grivet-Talocia and F. G. Canavero, "Complex Power Distribution Network Investigation using SPICE Based Extraction from First Principle Formulations," Proceedings of the IEEE 14th Topical Meeting on Electrical Performance of Electronic Packaging (2005, Austin, TX), pp. 263-266, Institute of Electrical and Electronics Engineers (IEEE), Oct 2005.

The definitive version is available at https://doi.org/10.1109/EPEP.2005.1563754

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# Complex Power Distribution Network Investigation Using SPICE Based Extraction from First Principle Formulations

Giuseppe Selli\*

EMC Laboratory

University of

Missouri-Rolla

(currently at the IBM

T.J. Watson Research

Center for a coop)

James L. Drewniak Richard E. Dubroff EMC Laboratory University of Missouri-Rolla Jun Fan, James L. Knighten Norman W. Smith Dean McCoy NCR Corporation San Diego, CA Bruce Archambeault IBM Corporation Research Triangle Park NC Stefano Grivet-Talocia Flavio Canavero Electronics Dpt. Politecnico di Torino Torino, Italy

#### I. ABSTRACT

The modeling and the analysis of the power distribution networks (PDN) within multi-layer printed circuit board is crucial for the investigation of the performance of PCB systems. Carrying out such analyses in SPICE based tools has the advantage of being faster than the corresponding full-wave modeling and it allows obtaining both frequency and time domain results.

#### II. INTRODUCTION

The modeling and analysis of the power distribution networks (PDN) within multi-layer printed circuit boards (PCB) are usually carried out in full-wave electromagnetic simulation tools or SPICE based tools. The charge delivery task performed by the PDN allows the correct functioning of all the active devices located on a PCB. Therefore, the correct modeling is crucial along with the necessity of carrying out the analyses in an efficient, i.e., not time-consuming way.

Full wave modeling approaches encompass all of the interactions necessary for modeling the PDN. However, the computational efficiency may be low for complex geometry. In fact, these PDN's are usually characterized by multi-scale features, i.e., features from a few mil associated with the via barrels and plane separation to the tens of cm scale associated with the board dimensions.

As proposed in [1], breaking down the PDN geometry into smaller parts to be investigated separately and then recombining these by means of the segmentation method [1,2,4] is a viable and efficient way of analyzing each of the constituent elements with the most appropriate method, provided the proper boundary conditions are enforced. In [1], the aforementioned approach is carried out in the frequency domain by combining the analyses performed on the two constituent elements of the complex PDN shown in Fig.1 and Fig.2. The first element is a pair of planes, whose center part, corresponding to a BGA footprint with vias and antipads, is removed. The second part is the very same removed geometry corresponding to a BGA packaged IC footprint. The first part is analyzed with the cavity model formulation, whereas the second is simulated using an FEM method. The equivalent impedance networks obtained with the different formulation and analyses are finally recombined through the segmentation method [2].

Although this approach is very helpful for the correct modeling and the analysis of the PDN of interest, the ultimate need of a design engineer is a SPICE deck, which can be cascaded with other circuit representations in order to analyze the behavior of the entire link path and PDN. This goal can be achieved by employing the aforementioned concept [1] to the two equivalent circuit representations associated with the constituent parts of the geometry described in Fig.1 and Fig.2. The first one is extracted by means of the cavity model approach, while the second is obtained by employing of IdEM [5] on the FEM simulation results of the cut out geometry.

The results of the SPICE simulations are compared along with the results of the Hybrid Method, i.e., Cavity Model plus FEM and the results of an FEM simulation of the entire PDN geometry.

<sup>\*</sup>gs5xd@umr.edu or gselli@us.ibm.com . Tel.: (914) 945-1995 Fax: (914) 945-2141

#### II. GEOMETRIES INVESTIGATED

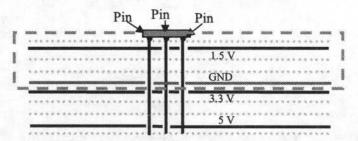

The geometry under investigation is obtained by extracting only the power delivery network associated with 1.5V and GND planes, as shown in Fig.1. The geometry consists of two solid planes, 10 cm by 8 cm, where many holes corresponding to a BGA package footprint are included. The hole patterns localized on the top and bottom planes correspond to the antipads of the BGA package pins connected to the 1.5 V plane, the GND plane or any other layer.

Fig.1. Board stack-up: the power distribution network considered is highlighted in the dashed box. The connections between the power layers and the IC are given just as an example.

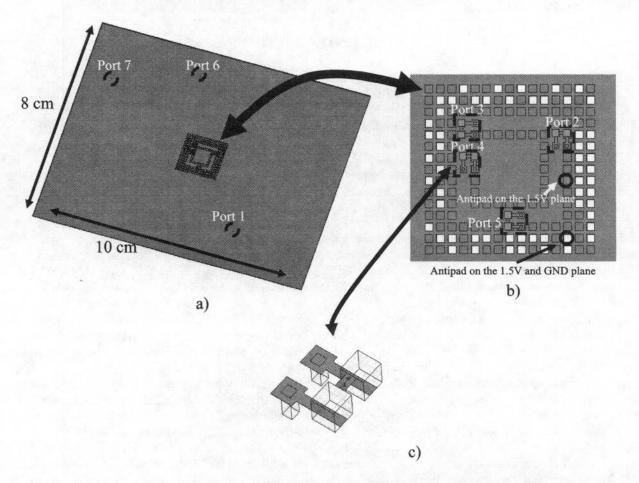

Fig.2. a) Top view of the of the power distribution network under investigation extracted from the stack-up of Fig.1. b) Close up of the hole pattern associated with the 1.5V plane of the PDN of interest. c) Close up of the interconnect associated with the ports located on the BGA footprint

Fig.2b shows the hole pattern on the top solid plane corresponding to the antipads associated with the pins of the BGA package connected to the bottom layer or any other of the layers. Seven excitation ports are employed in the geometry shown in Fig.2a. Four are located on the BGA footprint and three on the

reminder of the PDN. Each of the first four ports takes into account the entire interconnect from the bottom of the IC package down to the 1.5V or the GND plane and it consists of few elements, i.e., the balls - cubes in the current model - associated with the BGA package and the vias connecting the balls to the 1.5V or the GND planes. The spacing between the two planes is approximately 21 mils, the square balls have sides of 24 mils and the vias have sides of approximately 10 mils. Due to the complexity of the model, only the central 15 x 15 pins of an actual BGA package with all the pine assigned are represented in the 3D full wave model, as shown Fig.2b.

#### III. THE EQUIVALENT CIRCUIT MODELS AND THE RESULTS

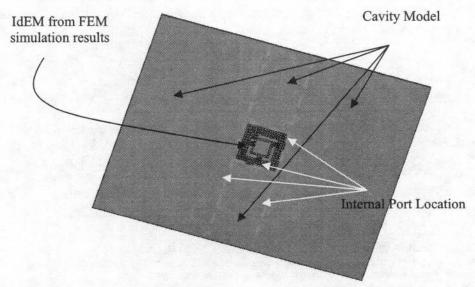

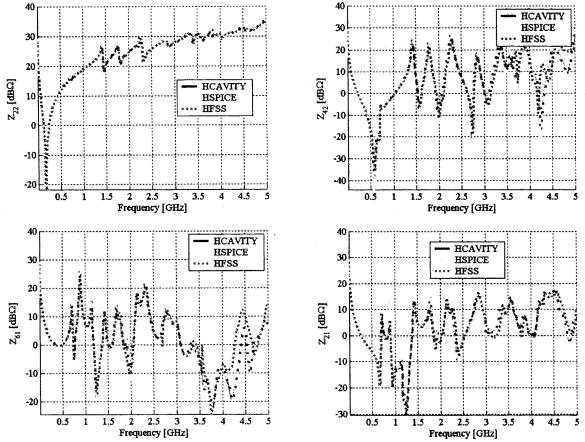

The well-known cavity model formulation allows the extraction of equivalent circuit models associated with 2D geometries [2-4]. However, the complex nature of the PDN shown in Fig.2 requires the employment of several methods in order to extract an overall equivalent circuit model to be simulated in a SPICE-based tool. In particular, the PDN of interest is partitioned into five elements as shown in Fig.3. The equivalent circuit models of four of the five elements are extracted by means of the cavity model approach [2-3], while the equivalent circuit model associated with the center element is extracted by means of IdEM [5] (Identification of Electrical Macromodel, circuit extraction tool developed at the EMC Laboratory of the Politechnic University of Torino) employed on the FEM simulation results of the BGA footprint geometry. The five equivalent models are then recombined together into one SPICE deck. The recombination is made possible by employing several internal ports along the sides of each pair of touching patches according to the segmentation method [2-4]. These ports are located along the dashed lines shown in Fig.3 and they are spaced apart a tenth of the wavelength associated to the highest frequency of interest, i.e., 5 GHz. The comparison of the self and transfer impedances between several ports shown in Fig.2 are given in Fig.4. The comparison is carried out by between FEM simulation results of the geometry under investigation in Fig.2, the Hybrid Cavity Model Method result presented in [1], and a SPICE simulation associated with the same geometry.

Fig.3. The PDN of interest is partitioned, an equivalent circuit model is extracted for each element and then all the elements are recombined

Fig.4. Self and transfer impedances comparison among different modeling approach of the same geometry of Fig.2. The Hybrid Cavity Model approach results and the SPICE simulation results overlap.

#### IV. CONCLUSIONS

The employment of different circuit extraction procedures and the segmentation method has been shown to give a good agreement up to several GHz, when the SPICE simulation results are compared with the results obtained by employing other methods.

In particular, a perfect match is obtained with the Hybrid Cavity Model approach, whereas no more than 10 dB difference is observed beyond 4GHz with respect to the FEM simulation results. On the other hand, a SPICE deck has the advantage of allowing time domain simulations of the PDN geometry of interest, it is faster than the corresponding full-simulation and it can be incorporated with other equivalent circuit model representations, allowing the possibility of investigating the entire full-link path within a SPICE based tool.

#### REFERENCES

- [1] G. Selli, J.L. Drewniak, R.E. Dubroff, J. Fan, J.L. Knighten, N.W. Smith, D. McCoy, B. Archambeault, "Power integrity investigation of BGA footprints by means of the segmentation method", submitted for publication in the Proc. of the 2005 IEEE Int. Symp. on Electromagnetic Compatibility, Chicago, August 8-12 2005.

- [2] T. Okoshi, Y. Uehara, and T. Takeuchi, "The segmantation method an approach to the analysis of microwave planar circuits," *IEEE Transactios on Microwave Theory and Techniques*, October 1976, pp. 662-668.

- [3] N. Na, J. Choi, S. Chun, M. Swaminatham, and J. Srinivasan, "Modeling and transient Simulation of planes in electronic packages," *IEEE Transaction on Advanced Packaging*, Vol. 23, No. 3, Aug. 2000, pp. 340-352.

- [4] C.Wang, J. Mao, G. Selli, S.Luan, L.Zhang, J.Fan, D.J.Pommerenke, R.E.Dubroff, and J.L.Drewniak, "An efficient approach for power delivery network design with closed-form expressions for parasitic interconnect inductance,", submitted for publication on IEEE Transactions on Advanced Packaging.

- [5] S. Grivet-Talocia, I.S.Stievano, F.G.Canavero, I.A.Maio, "A Systematic Procedure for the Macromodeling of Complex Interconnects and Packages," *EMC Europe 2004, International Symposium on Electromagnetic Compatibility, Eindhoven, The Netherlands, pp.414-419, September 6-10, 2004. See also http://www.emc.polito.it/*