# Concurrent Error Detection Using Watchdog Processors—A Survey

AAMER MAHMOOD, MEMBER, IEEE, AND E. J. MCCLUSKEY, FELLOW, IEEE

Abstract—This is a survey of concurrent system-level error detection techniques using a watchdog processor. A watchdog processor is a small and simple coprocessor that detects errors by monitoring the behavior of a system. Like replication it does not depend on any fault model for error detection. However, it requires less hardware as compared to replication. It is shown that a large number of errors can be detected by monitoring the control flow and memory access behavior. Two techniques of control flow checking are discussed and compared to the current error detection techniques. A scheme for memory access checking based on capability-based addressing is described. The design of a watchdog for performing reasonableness checks on the output of a main processor, by executing assertions, is also discussed.

Index Terms—Capability-based addressing, concurrent checking, control flow checking, coprocessor, distributed computing, executable assertions, microprogramming, parallel computing, signature analysis, system-level error detection, watchdog processor.

#### I. INTRODUCTION

**C**ONCURRENT (on-line or implicit) error detection techniques used in digital systems can be divided into two classes: circuit-level techniques and system-level techniques. The use of single error correcting and double error detecting codes for memories, parity bits for data buses, residue codes for ALU's, and self-checking circuits are all examples of circuit-level techniques [58]. Capability-based addressing [17], watchdog timers [47], fault-tolerant data structures [63], and use of replication (ESS-1A [60], FTMP [23], SIFT [66], C.vmp [57], and N-Version programming [9]) are some of the examples of the techniques used to detect errors at the system level.

#### A. Watchdog Processors

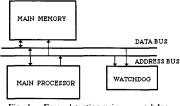

A watchdog processor [35], [42] is a small and simple coprocessor used to perform concurrent system-level error detection by monitoring the behavior of a main processor. The watchdog is an extension of the idea of a watchdog timer [10], [47], [48]. The organization of a system using a watchdog processor is shown in Fig. 1. Error detection by means of a watchdog is a two phase process. In the first phase (setup

Fig. 1. Error detection using a watchdog.

phase) the watchdog is provided with some information about the processor or process to be checked. During the second (checking) phase, it monitors the processor and collects the relevant information concurrently. Error detection is done by comparing the information collected concurrently with the information provided during the setup phase. The information provided to the watchdog to detect errors can be about the memory access behavior [43], the control flow [15], [26], [27], [36], [44], [46], [55], [59], [65], [67], the control signals [14], or the reasonableness of results [28], [37], [41], [49].

In terms of complexity, the watchdog lies between the current circuit-level and system-level techniques. Like other system-level techniques it does not require a simplistic fault model (single stuck-at, unidirectional, etc.), but it is cheaper than replication. Moreover, as the checking is done concurrently, the performance of the system does not suffer significantly. The use of watchdogs for concurrent (on-line) testing can be compared to functional (off-line) testing of microprocessors [64]. In both cases, the checking is done at a level higher than the circuit level. The watchdog can be added to any system without major changes to the system. If the system being monitored uses circuit-level error detection techniques, then the use of a watchdog can increase the reliability of the system by detecting errors which escape detection at the lower level. Another advantage of using a watchdog processor is that the checking circuitry is totally independent of the checked circuitry. This provides protection against common or related errors because of design diversity [6]. Other schemes use complementary logic [54] or processors from different manufacturers, as in Boeing 737-300 airplane [68], to overcome this problem. The very use of a watchdog processor provides protection against such errors. The use of a watchdog not only detects hardware errors but also software and design errors if reasonableness checks are performed on the output of the checked processor. Recently there has been a trend towards distributed computing using dedicated processors to perform specialized functions like floating-point calculations and input/output processing. [13] is

0018-9340/88/0200-0160\$01.00 © 1988 IEEE

Manuscript received December 12, 1985; revised July 31, 1986 and January 26, 1987. This work was supported in part by the National Science Foundation under Grant DCR-8200129 and by ROLM ML-SPEC Computer, San Jose. CA.

A. Mahmood was with the Center for Reliable Computing, Computing Systems Laboratory, Stanford University, Stanford, CA 94305. He is now with ROLM MIL-SPEC Computers, San Jose, CA 95134.

E. J. McCluskey is with the Center for Reliable Computing, Computing Systems Laboratory, Stanford University, Stanford, CA 94305.

IEEE Log Number 8716240.

#### MAHMOOD AND McCLUSKEY: ERROR DETECTION USING WATCHDOG PROCESSORS

| TABLE I           ERROR DETECTION MECHANISMS [52] |                          |                                                                          |  |  |

|---------------------------------------------------|--------------------------|--------------------------------------------------------------------------|--|--|

| IPF:                                              | Invalid Program Flow     | Improper sequence of instructions                                        |  |  |

| ioa:                                              | Incorrect Opcode Address | Fetching instruction from non-instruction address                        |  |  |

| UNM:                                              | Unused Memory            | Memory access to existent but<br>unused memory                           |  |  |

| IRA:                                              | Invalid Read Address     | Read access (for data) to<br>instruction area, or<br>non-existent memory |  |  |

| 10C:                                              | Invalid Opcode           | Illegal instruction                                                      |  |  |

| IWA:                                              | Invalid Write Address    | Attempt to write into non-alterable memory                               |  |  |

| NEM:                                              | Non-Existent Memory      | Access to a location with                                                |  |  |

|                                                   |                          | nó mémory                                                                |  |  |

TADLE

an example of design where a specialized processor is used for both I/O processing and error detection. Also, many systems are using special console processors for off-line diagnostics [5], [34]. The popularity of these techniques further supports the idea of using a watchdog coprocessor for concurrent error detection.

The paper is organized as follows: 1) Section II describes the experimental results about the error coverage of different system-level error detection techniques, 2) two kinds of control flow checking techniques are discussed in Section III, which also deals with detecting errors in hardwired and microprogrammed control units, 3) Section IV describes memory access checking, and 4) Section V discusses the use of a watchdog processor for performing reasonableness checks on the output of a main processor by executing assertions.

## II. EXPERIMENTAL EVALUATION OF DIFFERENT ERROR **DETECTION MECHANISMS**

A major decision in the design of a watchdog processor is the choice of a system characteristic to monitor. The chosen characteristic must satisfy the following requirements: 1) it should not make the watchdog complex, 2) it should provide good error coverage, 3) it should not require major changes to be made in the design of the checked processor, and 4) it should not result in high overhead to the monitored system. Many different mechanisms that can be used to detect errors at the system level were studied experimentally in [33] and [52].

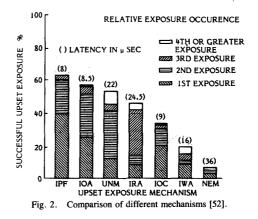

In [52] the seven mechanisms shown in Table I were studied by means of simulation. Faults (temporary and permanent) were injected on the external pins of the Z-80 microprocessor and the subsequent system response was recorded. For each mechanism, the relevant features of the response were extracted and compared to the response of the system with no faults. Any difference in the faulty and fault-free run was viewed as a successful detection of the fault by that particular mechanism. A total of 539 faults were injected. Of these 73 percent were detected by at least one of the mechanisms within 250  $\mu$ s (250  $\mu$ s being the maximum time for which the state of the system was observed). Fig. 2 describes the performance of

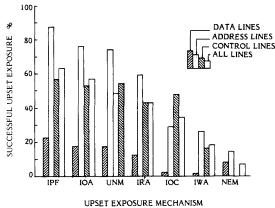

each individual mechanism. The highest point of the bar for each mechanism gives the total coverage, with different shaded portions indicating the time of detection relative to the other mechanisms. The first area indicates the percentage of time that the particular mechanism was the first to expose the fault, the second area indicates the percentage it was second, and so forth. The average latency from fault to detection is listed on the top of each bar. Fig. 3 shows the performance of each mechanism depending on where the fault was injected. It is clear from Figs. 2 and 3 that invalid program flow (IPF) was the best in detecting faults, both in terms of coverage (63 percent) and latency (8 µs). Moreover, most of the mechanisms did a good job of detection if the fault was on the address lines, but performed poorly if the injected fault was on the data line.

Similar results were obtained in an independent experimental study [33]. In this particular case, a software model of the processor (Texas Instrument SBR 9900) was used. This provided the opportunity to insert faults inside the processor and not just on the external pins.

#### III. CONTROL FLOW CHECKING

It is obvious from the results presented in Section II that control flow and memory access checking can be used very effectively for detecting errors at the system level. Control flow checking is discussed in this section and memory access checking is described in Section IV.

Any program can be represented graphically, with nodes representing some program unit and arcs representing the flow ' of control. A node can be a single statement, a block of statements with no jumps allowed from or into the block (branch-free interval), a loop-free interval, or a single procedure. All schemes of control flow checking are based on associating a signature or token with a node (called node signature). The watchdog is provided with the signatures and the relationship among signatures. This becomes the watchdog program. During execution of a program, the watchdog monitors the control flow of the program, computes the node signature concurrently (or accepts the signature explicitly transmitted by the main processor), and compares it to the signature provided earlier. Any discrepancy in the two signatures is taken as an indication of error. Many schemes for

checking control flow have been proposed [14], [27], [36], [44], [59], [67]. These schemes differ in their definition of a node and the node signature and in their derivation and representation of the watchdog program. In some schemes, the node is a high-level language construct [36] and in others it is a branch-free interval consisting of Assembly language instructions [44]. The signatures associated with the nodes can be either assigned arbitrarily (for example, using prime numbers) or they can be derived from the instructions in the node. Checking techniques in which the signatures are associated arbitrarily with the nodes will be called assigned-signature control flow checking and the techniques in which the signatures are derived from the nodes will be called *derived*signature control flow checking. In both cases, the watchdog program is homomorphic to the control flow structure of the main program. However, the method of computing the node signature has an important bearing on the error detection capability of different schemes.

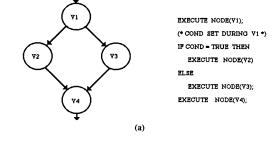

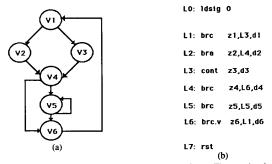

On the basis of their error detection capability, the schemes for checking control flow can be divided into three classes: 1) the schemes that check that the nodes are executed in an allowed sequence, 2) the schemes that verify the sequencing of the contents of a node, and 3) the schemes that do both. The schemes that use assigned-signature checking fall into the first category and the schemes that use derived-signature checking fall into the last two categories. As an example, consider the program and its graph shown in Fig. 4(a). Fig. 4(b) shows the watchdog program that only checks that the nodes are executed in an allowed sequence. (The allowed sequences are [V1 V2 V4] and [V1 V3 V4].) The node signatures are assigned arbitrarily in this case and explicitly transmitted to the watchdog. Most errors in the execution of the node itself, for example, change of an add instruction into a subtract instruction, are not detected. One advantage of such a scheme is that the watchdog program can be generated directly from a program written in a high-level language. Another advantage is that the two processors can operate asynchronously without making the watchdog complex. [36] is an example of such a technique.

Fig. 4(c) shows the watchdog program that only checks the sequencing of the contents of a node (with the node signature

#### IEEE TRANSACTIONS ON COMPUTERS, VOL. 37, NO. 2, FEBRUARY 1988

computed from the contents of the node). The watchdog has to be informed which node is being executed by the main processor. An example of such a scheme is [14]. Fig. 4(d) shows an example of a watchdog program whose execution by the watchdog results not only in checking the node transitions but it also detects errors in sequencing of the contents of the node itself. Signatures in both these cases [Fig. 4(c) and (d)] are not transmitted explicitly by the main processor but are computed concurrently by the watchdog. [15], [44], and [59] are examples of the technique shown in Fig. 4(d).

It should be pointed out that these schemes for control flow checking only verify that the nodes are executed in an allowed sequence and not necessarily the correct sequence (a sequence may be allowed but incorrect). Table II illustrates the main properties of different control flow checking schemes. These schemes are discussed later in Sections III-A, III-B, and III-C.

#### A. Assigned-Signature Control Flow Checking

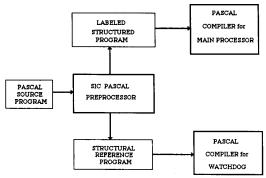

Examples of such techniques are [27], [36], and [67]. In [36] a technique called *structural integrity checking* (SIC), which is based on recognizing high-level control flow structures in computer programs, labeling these structures with signatures or labels, and checking the integrity of these structures at run time using a watchdog processor, is presented. The concept of SIC is based on the theory of formal languages and automata. It uses syntax-driven methods for encoding program structures and automatically generating two programs, one for the main processor and the other for the watchdog processor, from the original program. The schemes described in [27] and [67] also assign labels to program constructs. However, the method used for arriving at the labels in SIC results in much simpler implementation as compared to these two techniques.

A typical software configuration is shown in Fig. 5, using the language Pascal as an example. The SIC preprocessor reads in the Pascal source program and analyzes the program for four constructs: concatenation, selection, repetition, and abstraction (procedures). Table III shows examples of some of these constructs. Labels (signatures) are attached to these constructs and a program known as a Labeled Structured Program is generated for the main processor. The second output of the preprocessor is the Structural Reference Program for the watchdog. The structure of this program mimics the structure of the source program. In place of computations in the source program, the structural reference program contains statements to receive and check labels from the main processor. As the structural reference program does not contain code to execute the actions of the program being checked, the computational requirements for the watchdog are less than those for the main processor. As the main processor executes the labeled structured program, it transmits each label it encounters. The watchdog receives these labels and compares them to the labels generated within the watchdog by the structural reference program. In case of a mismatch, an error is signaled to the system component that manages error detection and recovery. The operations of SIC can be abstractly modeled as the activities of two automata. One automaton is the execution of the labeled structured program

| ACCEPT SIG(V1);   | CASE NODE OF             | ACCEPT SIG(V1), CHECK SIG(V1); |

|-------------------|--------------------------|--------------------------------|

| EITHER            | VI: CHECK SIG(VI);       | EITHER                         |

| ACCEPT SIG(V2)    | V2: CHECK SIG(V2);       | ACCEPT SIG(V2), CHECK SIG(V2)  |

| OR                | V3: CHECK SIG(V3);       | OR                             |

| ACCEPT SIG(V3);   | V4: CHECK SIG(V4);       | ACCEPT SIG(V3), CHECK SIG(V3); |

| ACCEPT SIG(Y4);   | END;                     | ACCEPT SIG(V4), CHECK SIG(V4); |

| (b)               | (c)                      | (d)                            |

| Fig. 4. Different | schemes for control flow | checking. (a) Main program.    |

Watchdog programs for (b) checking node transitions, (c) checking the node, and (d) checking both.

| TABLE II                          |                       |

|-----------------------------------|-----------------------|

| PROPERTIES OF DIFFERENT CONTROL F | FLOW CHECKING SCHEMES |

| SCHEME       | NODE                           | SIGNATURE | CHECKING<br>RESOLUTION | INTRA-NODE<br>CHECKING | INTER-NODE<br>CHECKING | SYNCH-<br>RONIZATION | MEM.<br>OVERHEAD | TIME<br>OVERHEAD |

|--------------|--------------------------------|-----------|------------------------|------------------------|------------------------|----------------------|------------------|------------------|

| SIC          | HIGH LEVEL<br>LANG. CONSTRUCT. | ASSIGNED  | VARIABLE               | NO                     | YES                    | ASYNC                | н                | н                |

| BASIC PSA    | BRANCH-FREE<br>INTERVAL        | DERIVED   | ONE NODE               | YES                    | YES                    | SYNC                 | н                | н                |

| GEN PSA      | BRANCH-FREE<br>INTERVAL        | DERIVED   | SEQUENCE OF<br>NODES   | YES                    | YES                    | SYNC                 | L                | н                |

| BAH          | BRANCH-FREE<br>INTERVAL        | DERIVED   | SEQUENCE OF<br>NODES   | YES                    | YES                    | SYNC                 | L                | н                |

| 8085 CHECKER | MACRO-<br>INSTRUCTION          | DERIVED   | ONE NODE               | YES                    | NO                     | SYNC                 | н                | Ŀ                |

| CERBERUS-16  | BRANCH-FREE<br>INTERVAL        | DERIVED   | SEQUENCE OF<br>NODES   | YES                    | YES                    | SYNC                 | L                | L                |

| RMP          | BRANCH-FREE<br>INTERVAL        | DERIVED   | SEQUENCE OF<br>NODES   | YES                    | YES                    | ASYNC                | L                | L                |

SIC:

STRUCTURAL INTEGRITY CHECKING

PATH SIGNATURE ANALYSIS

BAHH

BAHH

BRANCH ADDRESS HASHING

MPP

ROVING MONITORING PROCESSOR

ASYNC:

ASYNCHRONOUS

SYNC:

SYNCHRONOUS

SYNC:

IGH

L:

LOW

Fig. 5. Typical software configuration (SIC).

•

| CONCATENATION       begin     begin       send (x);     if token <> x then error;       a;     a;       b;     b;       end;     end;       if token <> y then error;       end;     end;       send (-x);     end;       b     b       b     b       end     else       else     begin       send (-y);     ccheck b >       c;     c;                  | begin     begin     begin       a;     a;     if token <> x then error;       a;     a;        b;     b;     if token <> y then error;       end;     end;        SELECTION       SELECTION       if token = -x then       b     b     b       b     b     check b >       end     end        else     else     else       b     b     b       send (-y);     if token = -x then                                                                                        | SOURCE    | MAIN          | WATCHDOG                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|---------------------------|

| send (x);     if token <> x then error;       a;     a; <check a="">       send (y);     if token &lt;&gt; y then error;       b;     b;     <check b="">       end;     end;     end;   SELECTION       if a then     begin       b     b       end     end (-x);       b     end       else     else       begin     send (-y);</check></check>        | send (x);         if token <> x then error;           a;         a;            a;         send (y);         if token <> y then error;           b;         b;         check a>           end;         end;         end;           SELECTION           if token <> y then error;           send (y);           b         send (-x);           b         end           else         else           b         send (-y);           c;         c;                           |           | CONCATENATION |                           |

| a;     a;     if token <> x then error;       a;     a;        send (x);     if token <> x then error;       b;     b;        end;     end;     if token <> y then error;       end;     end;     end;       if a then     begin       send (-x);     if token = -x then       b     b        end     end       else     else       begin     send (-y); | send (x);         if token <> x then error;           a;         a;            a;         send (y);         if token <> y then error;           b;         b;         check a>           end;         end;         end;           SELECTION           if token <> y then error;           send (y);           if a then         begin           begin           end         else           else         else           begin         send (-y);           c;         c; | beain     | begin         | begin                     |

| a;     a; <check a="">       send (y);     if token &lt;&gt; y then error;       b;     b;       end;     end;   SELECTION       if a then     if a then       b     b;       b     b;       end;     if token = -x then       else     else       b     b;       else     else       b     b;       else     if send (-y);</check>                      | a;       a; <check a="">         send (y);       if token &lt;&gt; y then error;         b;       b;       <check b="">         end;       end;       end;         SELECTION         if a then         b       b         b       b         end       end         else       else         b       b         c;       c;</check></check>                                                                                                                                  |           | -             | -                         |

| b; b; check b><br>end; end; end; end;<br>SELECTION                                                                                                                                                                                                                                                                                                       | b;<br>end;         b;<br>end;         < check b ><br>end;           send;         end;           if a then         if a then           b         b           b         end           else         else           b         else           c;         c;                                                                                                                                                                                                                 | a;        |               |                           |

| b; end; b; end; end; end; end; end; end; end; end                                                                                                                                                                                                                                                                                                        | b; end; b;<br>end; end; end; end; end; end; end;<br><br><br>SELECTION<br>if a then if a then begin send (-x); or c;                                                                                                                                                                                                                                                                                                                 |           | send (y);     | if token <> y then error; |

| SELECTION       if a then       begin       send (-x);       if token = -x then       ob       b       b       b       b       b       b       b       b       b       b       b       b       b       b       b       send       else       begin       send (-y);                                                                                      | SELECTION       if a then       begin       send (-x);       b       b       end       else       bigin       send (-y);       c;       c;                                                                                                                                                                                                                                                                                                                              | b;        | b;            |                           |

| if a then if a then begin send (-x); if token = -x then begin end else else begin send (-y);                                                                                                                                                                                                                                                             | if a then if a then begin send (-x); if token = -x then begin end else else begin send (-y); c;                                                                                                                                                                                                                                                                                                                                     | end;      | end;          | end;                      |

| begin         send (-x);         if token = -x then           b         b <check b="">           end         else         else           bsgin         send (-y);         send (-y);</check>                                                                                                                                                             | begin         if token = -x then           b         b <check b="">           end         else         else           begin         send (-x);         if token = -x then           c:         check b &gt;            c;         c;         <check c=""></check></check>                                                                                                                                                                                               |           | SELECTION     |                           |

| begin         send (-x);         if token = -x then           b         b <check b="">           end         else         else           begin         send (-y);         send (-y);</check>                                                                                                                                                             | begin         if token = -x then           b         b <check b="">           end         else         else           begin         send (-x);         if token = -x then           c:         check b &gt;            c;         c;         <check c=""></check></check>                                                                                                                                                                                               | if a then | if a then     |                           |

| send (-x);         if token = -x then           b         b <check b="">           end         else         else           begin         send (-y);</check>                                                                                                                                                                                              | send (-x);         if token = -x then           b         b         < check b >           end         end            else         else         else           b         send (-y);            c;         c;         c;         < check c >                                                                                                                                                                                                                              |           | 1             |                           |

| b         b         < check b >           end         else         else         else           begin         send (-y);         send (-y);         send (-y);                                                                                                                                                                                            | b         b         < check b >           end         end         else         else           else         else         begin         send (-y);           c;         c;         c;         < check c >                                                                                                                                                                                                                                                                 |           |               | if token = -x then        |

| else else else<br>begin<br>send (-y);                                                                                                                                                                                                                                                                                                                    | else else else<br>begin<br>c; c; c; < < check c >                                                                                                                                                                                                                                                                                                                                                                                                                       | Ь         |               |                           |

| begin<br>send (-y);                                                                                                                                                                                                                                                                                                                                      | begin           send (-y);           c;         c;           c;         c;                                                                                                                                                                                                                                                                                                                                                                                              |           | end           |                           |

| send (-y);                                                                                                                                                                                                                                                                                                                                               | c; c; c; <check c=""></check>                                                                                                                                                                                                                                                                                                                                                                                                                                           | else      | else          | else                      |

|                                                                                                                                                                                                                                                                                                                                                          | c; c; <check c=""></check>                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | begin         |                           |

| c; c; ccheck c>                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | send (-y);    |                           |

|                                                                                                                                                                                                                                                                                                                                                          | end;                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | c;        |               | < check c >               |

| end;                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | end;          |                           |

TABLE III

in the main processor and the second automaton is the execution of the structural reference program in the watchdog processor. The strings of labels produced by the execution of a labeled structured program can be described by a context-free grammar. The structural reference program is so constructed that the watchdog acting as a push-down automaton accepts exactly those strings described by the context-free grammar and rejects any other strings. As an example consider a part of a program shown in Table IV(a). From this program two programs shown in Table IV(b) and (c) are generated. The first one is executed by the main processor and the second one is executed by the watchdog processor.

### B. Derived-Signature Control Flow Checking

An example of derived-signature control flow checking is path signature analysis (PSA) [44] (only programs that do not modify themselves are considered). First, the basic scheme (called Basic PSA) will be discussed and then the modified scheme (called Generalized PSA) will be described.

In the Basic PSA Scheme, a deterministic signature is derived for each node of the graph (where each node is a branch-free interval); the signature of a node represents some characteristic of that node. For example, the result of mod-2 addition, a checksum, or linear feedback shift register (LFSR) signature of the instruction words in a node can be defined as the signature of that node. The signature is inserted at the beginning of each node. Two tag bits are used to differentiate signatures from the rest of instructions in the node. The watchdog monitors the data bus and captures the signatures as they appear, using tag bits to differentiate them from the rest

| STRUCTURAL INTEGRITY CHECKING.<br>PROCESSOR PROGRAM. (c) |                               |

|----------------------------------------------------------|-------------------------------|

| •                                                        |                               |

| •                                                        |                               |

| read(input, number);                                     |                               |

| repeat                                                   |                               |

| if number < 0 then begi                                  |                               |

| negsum := negsum +                                       | number;                       |

| number := number 🎙                                       | -1;                           |

| end;                                                     |                               |

| suma := suma + number;                                   |                               |

| read(input, number);                                     |                               |

| until (number = 0) or (ed                                | <pre>ln(input));</pre>        |

|                                                          |                               |

| •                                                        |                               |

| (a)                                                      |                               |

|                                                          |                               |

| send(50);                                                | if token <> 50 then error;    |

| <pre>read(input, number);</pre>                          |                               |

| send(187);                                               | if token <> 187 then error;   |

| begin                                                    | begin (# check repeat loop #) |

|                                                          | if token <> -82 then error;   |

| repeat                                                   | repeat                        |

| send(-82);                                               | (# loop terminated when       |

| (# -82 means loop executed #)                            | token not equal to -82 *)     |

| if number < 0 then begin                                 | if token = $-12$ then begin   |

| send (-12);                                              | (# -12 means 'if' executed #) |

| negsum := negsum + number;                               |                               |

| send(28);                                                | if token <> 28 then error:    |

| number := number 4 -1;                                   | ,                             |

| end else send(-13);                                      | end:                          |

| send(155):                                               | if token <> 155 then error;   |

| sum := sum + number;                                     |                               |

| send(48);                                                | if token <> 48 then error;    |

| read(input, number);                                     |                               |

| until (number = 0) or (eoln(input));                     | until token <> -82;           |

| send (-83); (# terminate loop #)                         |                               |

| end;                                                     | end;                          |

| (b)                                                      | (c)                           |

of instructions. The main processor executes a NOP instruction whenever a signature is fetched. For the rest of the instructions in the node, the watchdog computes the signature concurrently. At the end of the node, the watchdog compares the computed signature to the actual signature. Fig. 6 shows a typical structure of a node. Fig. 7(a) shows a sample program for the 68000 microprocessor with its corresponding graph. Fig. 7(b) shows the same program with signatures added. The signatures were computed using the Exclusive-or operation. The scheme described in [59] is very similar to the above mentioned technique. The main difference is that in [59] the signatures are added to the nodes such that the signature computed on-line at the end of node is all-one. This simplifies the checking circuitry because instead of a comparator, a simple gate is enough to generate an error signal.

1) Improvements: The insertion of explicit signatures in the instruction stream increases the memory overhead and reduces the performance. The schemes to be described next compute signature in such a way that each signature checks a greater number of instructions (compared to the Basic PSA), thereby reducing the total number of explicit signatures that need to be stored.

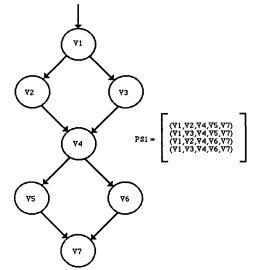

The first such scheme Generalized PSA, is described in [44]. In this scheme, the signatures are computed for sequences of nodes, that is, paths rather than single nodes. The program graph is broken into path sets and one signature is derived for each path set. Each path set contains one or more paths, with each path in the path set starting from the same node. As there is only one signature for each path set, each path in the path set must result in the same signature. In order to make this possible, sometimes pseudosignatures, called

TABLE IV

Fig. 6. Structure of a typical node (PSA).

| 001000<br>001006<br>001008<br>00100C<br>001010                     | V1                               | 207C00006002<br>4201<br>10386000<br>0C000009<br>6206         | LI: | MOVEA.L<br>CLR.B<br>MOVE.B<br>CMP.B<br>BHI.S          | #DATAI,AO<br>DI<br>DATA2,DO<br>#9,DO<br>L2 | (VI        |

|--------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------|-----|-------------------------------------------------------|--------------------------------------------|------------|

| 001012<br>001014                                                   | V2                               | 4880<br>12300000                                             |     | EXT.W<br>MOVE.B                                       | DO<br>0 (AO,DO),D1                         | (V2)<br>V3 |

| 001018<br>00101C                                                   | ٧3                               | 11C16001<br>4E75                                             | L2: | MOVE.B<br>RTS                                         | DI,DATA3                                   |            |

|                                                                    |                                  |                                                              |     | (a)                                                   |                                            |            |

| 001000<br>001002<br>001008<br>00100A<br>00100A<br>00100E<br>001012 | 01<br>00<br>00<br>00<br>00<br>11 | 1C46<br>207C00006002<br>4201<br>10386000<br>0C000009<br>6208 | LI: | (NOP)<br>MOVEA.L<br>CLR.B<br>MOVE.B<br>CMP.B<br>BHI.S | #DATA1,AO<br>DI<br>DATA2,DO<br>#9,DO<br>L2 |            |

| 001014<br>001016<br>001018<br>00101A                               | 01<br>00<br>00<br>11             | 5AB0<br>4880<br>1230<br>0000                                 |     | (NOP)<br>EXT.W<br>MOVE.B                              | DO<br>0 (AO,DO),01                         |            |

| 00101C<br>00101E<br>001022                                         | 01<br>00<br>11                   | 3FB5<br>11C16001<br>4E75                                     | L2: | (NOP)<br>MOVE.B<br>RTS                                | DI,DATA3                                   |            |

|                                                                    |                                  |                                                              |     | (b)                                                   |                                            |            |

Fig. 7. Basic path signature analysis. (a) A program for the 68000 processor. (b) The same program with signatures added.

Fig. 8. A program graph to illustrate Generalized PSA.

justifying signatures, are added to the paths in the path set (assuming that the inverse of the signature exists), so that no matter what path is executed in the path set, the same signature results.

As an example, consider the program graph shown in Fig. 8. It has one path set that consists of four different paths. In

order to make all these paths equisignature, the signatures of the nodes v3 and v6 are justified by assigning two justifying signatures to these nodes. (It is assumed that the Exclusive-or operation is being used for computing signatures.)

$h'(v3) = h(v3) \oplus h(v2)$  (justifying signature at node v3)

$h'(v6) = h(v6) \oplus h(v5)$  (justifying signature at node v6).

After this modification, the signatures of the paths would be

P1:

$$H1 = h(v1) \oplus h(v2) \oplus h(v4) \oplus h(v5) \oplus h(v7)$$

P2:  $H2 = h(v1) \oplus h(v3) \oplus h'(v3)$

$\oplus h(v4) \oplus h(v5) \oplus h(v7) = H1$

P3:  $H3 = h(v1) \oplus h(v2) \oplus h(v4)$

$\oplus h(v6) \oplus h'(v6) \oplus h(v7) = H1$

P4:  $H4 = h(v1) \oplus h(v3) \oplus h'(v3)$

$$\oplus$$

$h(v4)$   $\oplus$   $h(v6)$   $\oplus$   $h'(v6)$   $\oplus$   $h(v7) = H1$

where h(vi) is the signature of a single node.

The common signature of these paths (H1) is stored at the node v1. The total number of signatures for this example is three which is less than that in the Basic Scheme (seven). Fig. 9 shows the same program as in Fig. 7(a) with signatures added based on the Generalized method. The total number of signatures in this case is two, which is less than that in the basic method.

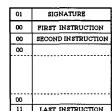

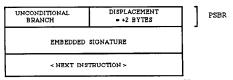

The second scheme, Branch Address Hashing (BAH) described in [55] improves the Basic PSA by combining some of the signatures with branch target addresses, thereby reducing the overhead for storing signatures by 50 percent. There are some notable differences between this scheme and the Basic PSA. The program graph is partitioned differently and the signatures are inserted at the end of nodes rather than at the beginning of nodes. Instead of embedding one signature immediately preceding every branch instruction, the branch address of the branch instruction is modified at assembly time such that during execution, the changed branch address combined with the concurrently computed signature gives the correct branch address. An explicit signature still needs to be embedded preceding every branch-in point (labeled instruction). In the case of an error, the concurrently computed signature and, hence, the computed branch address will be incorrect, resulting in the execution of a branch to an erroneous destination. The error will be detected when the next embedded signature is encountered. This is shown in Fig. 10. For the programs written in the Assembly language of the MC 68000 microprocessor, the signatures are embedded by using a pseudo-branch instruction (psbr). A psbr instruction is an unconditional branch to the location PC + 2. A 16-bit embedded signature as shown in Fig. 11, is stored immediately following the psbr instruction. The psbr instruction signals the monitoring hardware of the embedded signature. Use is made of the one-word prefetch of the MC 68000 microprocessor during the decode of psbr instruction. As the psbr instruction is being decoded, the embedded signature is

|     | 001000<br>001002<br>001008<br>00100A<br>00100E<br>001012 | 01<br>00<br>00<br>00<br>00<br>00 | 23F3<br>107C00006002<br>4201<br>10386000<br>0C000009<br>6208 | LI:  | (NOP)<br>MOVEA.L<br>CLR.B<br>MOVE.B<br>CMP.B<br>BHI.S | ;Path signature<br>#DATA1,AO<br>DI<br>DATA2,DO<br>#9,DO<br>L2 |

|-----|----------------------------------------------------------|----------------------------------|--------------------------------------------------------------|------|-------------------------------------------------------|---------------------------------------------------------------|

|     | 001014                                                   | 10                               | 5AB0                                                         |      | (NOP)                                                 | Justifying                                                    |

|     | 001016                                                   | 00                               | 4880                                                         |      | EXT.W                                                 | signature<br>DO                                               |

|     | 001018                                                   | 00                               | 1230                                                         |      | MOVE.B                                                | 0 (AO,DO),D1                                                  |

|     |                                                          |                                  |                                                              |      | MOVE.D                                                | 0 (10,00),01                                                  |

|     | 00101A                                                   | 00                               | 0000                                                         |      |                                                       |                                                               |

|     | 00101C                                                   | 00                               | 11C16001                                                     | L2:  | MOVE.B                                                | DI,DATA3                                                      |

|     | 001020                                                   | 11                               | 4E76                                                         |      | RTS                                                   | ;Terminal node                                                |

| Ci. | 0 The                                                    | como n                           | rogram as in Fig                                             | 7(2) | with signature                                        | es added using th                                             |

Fig. 9. The same program as in Fig. 7(a) with signatures added using the generalized method.

| CONCU | IRRENTLY<br>SIGNATU     | COMPUTED<br>RE                                                | SOURCE         | CODE      |

|-------|-------------------------|---------------------------------------------------------------|----------------|-----------|

|       | 0000                    |                                                               | jsbr           | input     |

|       | 3D08                    |                                                               | movi           | d0, tie   |

|       | F7A5                    |                                                               | cmpi           | #1, d0    |

| a:    | B863                    |                                                               | jit            | .L10000   |

|       | B0C5                    |                                                               | cmpl           | #384, d0  |

|       | 51B5                    |                                                               | jle            | .L81      |

| b:    | 0000                    |                                                               | psbr           | .L10000   |

|       | 7D22                    | .L10000:                                                      | movi           | #13, sp@- |

| a     | ddress given<br>ddress. | mputed signature<br>in the source code<br>for inserting an ex | to compute the | actual    |

Fig. 10. Branch address hashing [55].

Fig. 11. An embedded signature (BAH).

prefetched, detected, and compared to the running (concurrently computed) signature. In actual implementation, the inverse of the signature is stored so that the running signature is all-zeros, thereby making the comparison easier.

In order to understand how branch address hashing works, consider Fig. 10. Starting from the first instruction, the signature is computed concurrently as each instruction is fetched. At point marked "a" in the figure, in the Basic PSA, concurrently computed signature would have been compared to the signature inserted explicitly in the beginning of the node. However, in this case, comparison is only made when a pseudobranch instruction is encountered, which is before a branch-in point (labeled instruction). In case the jump is not taken at point "a," the signature is continued to be computed as instructions are fetched. If the jump is taken, then the jump address is computed by combining the signature computed up to that point with the address given in the jump instruction. This scheme has been actually implemented and experiments are being conducted to determine the error coverage.

2) Independent Watchdog Processors: All the techniques

for derived-signature control flow checking presented so far require that the signatures be inserted in the instruction stream. This increases the execution time of a program. However, by storing signatures in the local memory of a watchdog, this overhead can be removed. Two such schemes will be discussed. The first is a synchronous scheme for checking uniprocessor systems [46] and the second is an asynchronous scheme for monitoring multiprocessor systems [15], [65].

The watchdog processor which uses the first scheme is called **Cerberus-16**. The information about the program graph and path signatures is moved into (the environment of) the watchdog processor. The program executed by the watchdog has the same control flow structure as the program being executed in the main processor; that is, the graphs of both programs are identical. A node in the graph (G) of the program (P) being executed on the main processor represents a branch-free interval, whereas the node in the program (P') being executed in the watchdog consists of a single instruction that contains some information (such as signature or the size of node) about the corresponding node in graph G.

The architecture and organization of Cerberus-16 differs from most existing processors in two respects: 1) most instructions of this processor are control transfer instructions and 2) there is no ALU in this processor. The instructions for Cerberus-16 can be divided into two categories. The instructions in the first category are used for representing control flow in the program graphs. The general format of such instructions is

## OP Z, [L], [D]

where Z, L, and D represent the node size, the next node address (label), and the node signature, respectively. L and D fields are optional. The instructions in the second category are used for initialization and communication with the main processor. They have the following format.

#### OP or OP D.

Any program graph can be represented by a set of watchdog instructions. Depending on the type of a node, a suitable instruction is used to represent that node. As that node is executed by the main processor, the instruction corresponding to that node is executed by the watchdog. After z instructions have been executed by the main processor, the watchdog then expects a signal from the branch detecting circuitry to indicate whether a branch was taken by the main processor or not. If it detects a branch, then the watchdog also executes a branch using the L field to calculate the target address of the next instruction. The next watchdog instruction corresponds to the node which should be executed by the main processor after the branch. In case no branch is detected, the watchdog executes the next instruction in sequence. As each instruction is executed by the watchdog, the value in the D field (signature) is fed to the data compression unit whose output is saved in a register. As an example of how this architecture can be used for control flow checking, consider a program, with graph as shown in Fig. 12(a), being executed on the main processor. The corresponding program executed by the watchdog is

Fig. 12. Control flow checking with Cerberus-16. (a) The graph of the program executed by the main processor. (b) The corresponding program executed by Cerberus-16.

shown in Fig. 12(b). There are exactly six instructions corresponding to the six nodes of the main program. The Zi and di ( $i = 1 \cdots 6$ ) parameters in each instruction represent the size and the signature of the corresponding node in the main program, respectively. The instruction LDSIG initializes the signature register (S) to zero. At any given time, the register S contains the accumulated signature of the executed path. For example, if the main processor executes the node sequence (v1, v2, v4, v5, v5, v5, v6) and the compression function selected is xor, then the watchdog executes the instructions at addresses (L1, L2, L4, L5, L5, L5, L6) and the accumulated signature after the execution of this path would be

$$h=d1 \oplus d2 \oplus d4 \oplus d5 \oplus d5 \oplus d5 \oplus d6.$$

The instruction corresponding to the node v6 is BRC.V (branch conditional and verify) instruction. This instruction signals the end of the path. The signature computed by the watchdog at this point is compared to the actual signature of the path.

The same watchdog can be used for collecting statistical data about a system by changing the data [D] field of the watchdog instruction. An example of such data is the frequency of different instructions. It is interesting to note that the earliest design of a processor for monitoring another processor was for the purpose of collecting performance data [16]. However, the watchdog is much simpler compared to the earlier design.

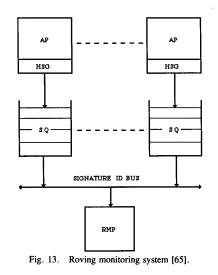

The above mentioned design of Cerberus-16 requires the watchdog to be tightly synchronized with the main processor. An asynchronous version of the above scheme is discussed in [15]. It is based on storing the control flow information of the program being executed on the monitored processor as the signature graph in the local memory of the monitoring processor. The graph is stored in the form of a linked list data structure. As each node is executed in the main processor, its signature use transmitted to the monitoring processor through a signature queue. The monitoring processor uses the signature graph to check that the next signature it receives belongs to a set of nodes which can be reached from the current node. This scheme can also be used for monitoring more than one processor if a different signature queue is used for each processor and signature graphs of all the programs being

executed on different processors are stored in the local memory of the monitoring processor.

[65] discusses the actual implementation of the processor (called Roving Monitoring Processor or RMP) described in [15]. Fig. 13 shows the general configuration of Roving Monitoring System. There is one hardware signature generator (HSG) for each application processor (AP). Each HSG generates a stream of signatures for its corresponding AP and stores it in the signature queue (SQ). The RMP samples the SO's according to some policy and checks that the signature stream generated by the AP corresponds with its signature graph, already stored in the local memory of RMP. Only eight instruction types, shown in Table V, are sufficient to represent the program graph. Signature words containing signature and processor ID arrive at the RMP from SQ via the common signature bus. The processor ID field is used by the RMP to access the appropriate program counter from the program counter register file. The prototype for RMP has been designed and implemented. It uses 90 MSI/SSI packages (excluding memory) and can monitor 16 processors. A series of fault insertion experiments, designed to determine the error coverage and error latency are being conducted.

3) Overhead: The memory overhead for storing signatures can be as high as 20 percent if the Basic PSA scheme described in Section III-B is used. However, if the improvements discussed in Section III-B-1 (Generalized PSA and branch-address hashing) are used, then the overhead can be reduced to 10 percent. The hardware required to implement the watchdog itself can be as little as 20 percent of the complexity of the MC 68000 microprocessor [40].

4) Error Coverage: Derived-signature control flow checking techniques discussed in Section III-B can detect both memory and control flow errors. Examples of control flow errors are incorrect sequence of instructions, branch to wrong address, branch from a wrong address, etc. These control flow errors can be the result of failures in the instruction register, the program counter, the address register, decoding circuitry, memory addressing circuitry, etc. It was shown in [40] that control flow errors can be modeled as memory errors for the

TABLE V INSTRUCTIONS FOR RMP [65]

| INSTRU      | CTIONS FOR RMP [65]                                                               |

|-------------|-----------------------------------------------------------------------------------|

| CMPS S, SRP | Compare signature with S, branch<br>relative to SRP if match                      |

| CMPSE S,SRP | Compare signature with S, branch<br>relative to SRP if match. Error if no match.  |

| CMPIE S     | Compare signature with S, go to the next instruction if match. Error if no match. |

| HASH        | Short relative branch, based on lower signature bits.                             |

| PUSH LPTR   | Push current address to stack, jump<br>long to location LPTR                      |

| POP         | Pop current address from stack.                                                   |

| POPSE       | Compare signature and pop the next address from stack. Error if no match.         |

| LJMP LPTR   | Unconditional jump to location LPTR                                               |

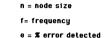

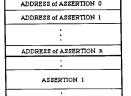

| ×           | 'w' Bits                                                                          |

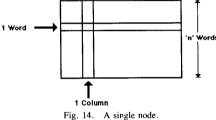

purpose of calculating error coverage. The problem is thus transformed to that of calculating coverage for errors in a block of data. The error coverage when parallel linear feedback shift register (PLFSR or MISR) is used to compute the signature is discussed in [40]. The results described in [40] are based on the properties of linear feedback shift registers [8], [20], [21] and on the observation that the number of instructions in a node is small [24], [56]. Suppose that the node has "n" words, each "w" bits wide (that is, each memory word is "w" bits wide), as shown in Fig. 14. Using a PLFSR to compute the signature of the node, it was shown in [40] that all single word errors are detected and most single column errors are detected. If n = 10 and w = 16, then the percentage of errors not detected due to aliasing (when the signature is same even in the presence of error), assuming all errors are independent and equally likely, is 0.0015 percent. Although the above results are for Basic PSA, they apply equally well to the other schemes (Generalized PSA, BAH). These results are true not only for memory errors but also for control flow errors. This is because control flow errors can be modeled as memory errors as described earlier.

In order to study the error coverage in more detail suppose that "w," the width of a node, is 32 bits. Further assume that

IEEE TRANSACTIONS ON COMPUTERS, VOL. 37, NO. 2, FEBRUARY 1988

the memory consists of 32 chips each with 1 bit/chip. If at most one memory module fails at one time, then at most one column (of the node) can be in error. If the size of a node, "n" (number of memory words in a node), is less than the width of the node, then all the errors will be detected [40]. If the size is greater than "w," then the ratio of undetected errors to the total possible errors is  $(2^{n-w} - 1)/(2^n - 1)$ . For large "n," this can be approximated by  $2^{-w}$ . Since at most one column can be in error, fault masking cannot occur. As an example, assume that the distribution of node sizes is as shown in Table VI. This distribution is based on the number of instructions executed between successful branches and is described in [24]. For each node size, the percentage of errors detected is shown in column "e" in Table VI. It can be seen that more than 99.9 percent of the errors are detected. If there is more than 1 bit/ chip, then single chip failure can result in multiple column error. However, even then the error coverage is greater than 90 percent as shown in [40].

Most of the memory errors will appear as column errors. Stuck faults on the data lines can also be modeled as column errors. Control flow errors can be represented as word errors. Such errors can be divided into two classes: one in which a node is mapped into an erroneous node of the same size and the other in which the size of erroneous node is different. If the checking scheme used by Cerberus-16 (Section III-B-2) is used, then any change in the node size is immediately detected. This is because the node size of each node is stored with the signature of that node. So only the errors which change a node into a different node of the same size can go undetected. For detection purposes, such errors can be modeled as some or all bits in a data block have been changed. As described earlier, for a node size of 10 words each 16 bits wide, the percentage of errors not detected due to aliasing is only 0.0015 percent. As an example of an error that changes the node size, consider a node of size "n." Suppose that as a result of a control flow error, words 0 to b - 1 of the node are not executed and the execution starts from the bth word. Then the signature computed after executing the words b to n - 1 in the node will be the same as if all the words in the node (0 to n 1) were executed with the words 0 to b - 1 replaced by all zero words. This means that jumping in the middle of node and starting the execution from the bth word is equivalent to the first b words being in error. This is shown in Fig. 15. If only the first word is missed, then this error (equivalent to a single word error) is guaranteed to be detected (assuming that the missed word was not all zero itself) [40]. Many other errors, like illegal opcode, illegal memory read/write, addition of a branch to a node, omission of a branch from a node, etc., can also be modeled as word errors. Hence, the results derived for memory errors also hold in the case of control flow errors.

The results described above are based on the assumption that all errors are equally likely. Although this assumption has been challenged for off-line (explicit) testing, there is as yet no reason to doubt its validity for concurrent testing. However, the best way to confirm the above results is by means of experimental studies. Such studies are being conducted at Carnegie-Mellon University [53] in which the schemes described in [55] and [65] are being evaluated experimentally.

TABLE VI

ERROR COVERAGE FOR 32-BIT WIDE MEMORY WITH 1 BIT/CIP

| Node Size<br>n | Freq.<br>f | # Error<br>Detected<br>e | f*e            |

|----------------|------------|--------------------------|----------------|

| 1              | .0192      | 100                      | 1.921%         |

| 2-3            | .0864      | 100                      | 8.645 <b>%</b> |

| 4-7            | .2381      | 100                      | 23.81%         |

| 8-15           | .3522      | 100                      | 35.22%         |

| 16-31          | .1499      | 100                      | 14.99%         |

| >31            | .1539      | 99.9                     | 15.38%         |

| OVERALL        | COVERA     | GE ∑ f*e                 | 99.9%          |

Fig. 15. An example of a control flow error.

# C. Checking the Control Section of a Processor

Some of the techniques used for control flow checking can also be used for checking the control section of a processor. A design for checking the sequence of control signals corresponding to each opcode, for hardwired control units, is discussed in [14]. It is based on assigning a unique signature to each opcode (some opcodes like branches require more than one signature). The signature is computed by compacting the sequence of control signals using a PLFSR. These signatures are stored in a ROM. When a particular opcode is executed by the processor, a signature is computed concurrently by using a PLFSR. The same opcode is used to fetch the stored signature from the ROM. A checker for the 8085 microprocessor was implemented using SSI/MSI chips. Seven control signals (visible at the pins) were monitored: ALE, S0, S1, IO/M, RD, WR, and INTA. The implementation required approximately 535 gates which is about 11 percent of the complexity of 8085.

The techniques used for checking the control flow of programs written in Assembly language, and discussed in Section III-B, can also be used for checking microprogrammed control units. However, this can result in high memory overhead and performance degradation. This is because the node size can be very small, especially if horizontal microinstructions are used. To overcome this difficulty, the schemes have been modified for checking microprogrammed control units. All the modifications are aimed at extending the microinstructions, thereby improving the performance. More details can be found in [40], [45], [59], and [26]. The schemes described in [40], [45], and [59] use derived signature checking, whereas [26] is based on assigned signature checking.

1) Comparison to the ESS-3A Processor: The ESS-3A (Electronic Switching Systems) is a microprogrammed processor [11], [61] and is designed to control the No. 3 ESS [25], a small electronic switching system, which can handle from 500 to 5000 telephone lines. ESS-3A was chosen for comparison for two reasons. First it has a very high availability requirement (down time of a few minutes per year), and second, it does not use duplication at the system level for error detection. Instead, it relies on the error detection circuitry built into the processor to detect faults. The techniques used in the control section for fault detection are as follows: 1) each of the two 8bit fields of a microinstruction is encoded in the 4-out-8 code. 2) two parity bits are used to check the sequencing of microinstructions, and 3) the instruction decoder is checked with a self-checking checker. The overhead of checking circuitry in the control section is about 30 percent. This does not include the memory overhead due to the 4-out-8 encoding and the two extra parity bits. The microprogram ROM contains 1024 words (extendable to 4096), each 32 bits wide. The memory overhead is about 14.28 percent. The redundancy in the control section provides protection against the following errors: 1) all unidirectional errors in the microprogram ROM, 2) some sequencing and addressing errors, and 3) decoding errors.

It was shown in [40], using the same results as described in Section III-B-4, that the watchdog processor provides better error coverage for comparable overhead cost. More than 90 percent of the memory errors are detected as was shown previously. All single word errors in the node are detected and very high error coverage is obtained for column errors (because of the small node size). This technique also provides much better protection against sequencing and addressing errors. If the signature is formed at the output of the decoder, instead of at the output of the microprogram ROM, then the decoding errors can also be detected.

The memory overhead can be as low as 7 percent (as compared to 14 percent in ESS-3A). The nonmemory overhead for the watchdog is comparable to the hardware dedicated to checking in ESS-3A.

#### **IV. MEMORY ACCESS CHECKING**

The watchdog can also detect errors in the main processor by monitoring the memory access behavior [43]. In fact, the watchdog discussed in Section III-B-2 (Cerberus-16) can be modified easily to check the memory access along with the control flow [46], thereby improving the error coverage. The design of a watchdog for memory access checking as described in [43] is based on the capability-based addressing [17] scheme in which each accessing object has to provide a capability (a protection key) for accessing another object. Each capability uniquely specifies an object. In the scheme described in [43], and shown in Fig. 16, explicit access to the physical memory segments is checked by an external watchdog processor. Basically, the set of all active objects (code or data) at any given time is represented by a directed graph (object graph). The object graph is stored in the watchdog processor in a table called segment access table (SAT). The SAT has one row for each code object; the entries in each row

IEEE TRANSACTIONS ON COMPUTERS, VOL. 37, NO. 2, FEBRUARY 1988

SMT Km Columns C: Code Object D: Data Object 0 SI **S1** Accessing 2 S2'RD 53'WI **S**3 Object 3 <u>S1</u> Accessed Object Parallel Match Expected Actual Memory Access Access ACCESS CHECK Access Error

Fig. 16. Memory access checking using a watchdog processor.

SAT

TABLE VII A PROGRAM SEGMENT WITH AN ASSERTION

are the capabilities (access rights) given to that object. The watchdog processor has another table called segment map table (SMT) that is used for mapping the physical page frame numbers (derived from the memory address bus) onto segment numbers representing objects. The SMT has one entry corresponding to each page frame in the processor's main memory. For each memory access, two segment numbers, Si and S<sub>i</sub>, are determined from the SMT, one for the accessing object and the other for the accessed object. These segment numbers are used to read the expected access right, SAT(Si,  $S_i$ ), from the SAT. The size of the SAT can be reduced significantly if it is assumed that at most Km objects can be accessed by any object. This makes it possible to organize the SAT as a parallel hash table that contains Km entries in each row. The segment number of the accessing object selects one row of this table. A parallel search is done to match the segment number of the accessed object with a segment number in the selected row and to read the corresponding access right (if a match occurs). This access right is compared to the actual CPU access. An access error is signaled if there is no match in the SAT or the access right is not correct.

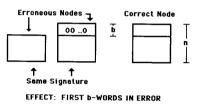

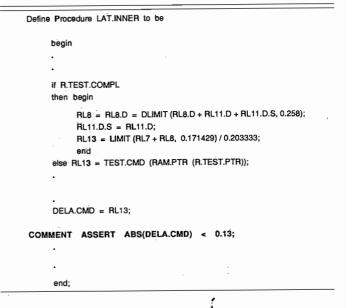

# V. REASONABLENESS CHECKS