## CONDITION MONITORING OF ELECTROLYTIC CAPACITORS FOR POWER ELECTRONICS APPLICATIONS

A Dissertation Presented to The Academic Faculty

by

Afroz M. Imam

In Partial Fulfillment

Of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology

May, 2007

## CONDITION MONITORING OF ELECTROLYTIC CAPACITORS FOR POWER ELECTRONICS APPLICATIONS

#### Approved by:

Prof. Ronald G. Harley, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Prof. Thomas G. Habetler School of Electrical and Computer Engineering Georgia Institute of Technology

Prof. Jerome Meisel School of Electrical and Computer Engineering Georgia Institute of Technology Prof. Deepak M. Divan, Co-advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Prof. Linda S. Milor School of Electrical and Computer Engineering Georgia Institute of Technology

Prof. J. Rhett Mayor School of Mechanical Engineering Georgia Institute of Technology

Date Approved: April 5, 2007

#### **ACKNOWLEDGEMENTS**

It has been four and a half years since I started my PhD in fall 2002 and I was fortunate to enjoy the guidance, assistance, support, and friendship of many without whom this work would not have taken shape. Here, I hope to express my gratitude to most of them.

First, I would like to thank my academic co-advisors, Prof. Ronald G. Harley and Prof. Deepak Divan for their continuous insight, enthusiasm, and encouragement. I am forever grateful to them for letting me pursue my research under their guidance. Their invaluable suggestions at difficult times have contributed a lot towards the success of this thesis. I would like to thank Prof. Thomas G. Habetler for helping me to choose the research topic and being a continuous source of inspiration. I have benefited immensely from his knowledge and experience. I would also like to thank Prof. Linda S. Milor, Prof. Jerome Meisel, and Prof. J. Rhett Mayor for taking some time of their busy schedule to serve on my PhD defense committee.

I would like to thank Mr. Paul Springer of NEETRAC for providing the financial support for my graduate studies. I must also thank the machinists, Lorand Csizar and Louis Boulanger, who were always available and willing to help with the laboratory experimental setup. I would also like to thank Deborah King for patiently putting up with my frequent purchase requests and room reservations.

I was fortunate to have many exceptional peers and colleagues in my research group. Among them, I wish thank Dr. Satish Rajagopalan, Lee Yungkook, Harjeet Johal,

Yi Yang, Zhi Gao, Jean-Carlos Hernandez, Dr. Salman Mohagheghi, Jyoti Sastry, and Anish Prasai for their invaluable input and countless enlightening conversations.

Finally, it is time to mention the people whom I care about the most: my mother, and loving memories of my father who is no longer with us. I am eternally grateful to my mother for the love, support, and encouragement that have helped to make everything I have accomplished possible. Sincerest thanks to my brothers and sisters for always believing in me and always supporting me.

# **TABLE OF CONTENTS**

| AC  | KNOWLEDGEMENTS                                  | iv   |

|-----|-------------------------------------------------|------|

| LIS | ST OF TABLES                                    | xiii |

| LIS | ST OF FIGURES                                   | xiv  |

| SUI | MMARY                                           | xix  |

| СН  | APTER 1: INTRODUCTION AND OBJECTIVE OF RESEARCH | 1    |

| 1.1 | Problem statement                               | 1    |

| 1.2 | Objective                                       | 2    |

| CH  | APTER 2: BACKGROUND MATERIAL AND PREVIOUS WORK  | 3    |

| 2.1 | Introduction                                    | 3    |

| 2.2 | Electrolytic capacitor                          | 3    |

| 2.3 | Electrolytic capacitor construction process     | 5    |

|     | 2.3.1 Etching                                   | 5    |

|     | 2.3.2 Formation                                 | 5    |

|     | 2.3.3 Slitting                                  | 6    |

|     | 2.3.4 Winding                                | 6  |

|-----|----------------------------------------------|----|

|     | 2.3.5 Impregnation                           | 7  |

|     | 2.3.6 Sealing and aging                      | 8  |

| 2.4 | Application guide                            | 8  |

|     | 2.4.1 Dielectric absorption                  | 8  |

|     | 2.4.2 Insulation and grounding               | 9  |

|     | 2.4.3 External pressure                      | 9  |

|     | 2.4.4 Mechanical vibration.                  | 10 |

|     | 2.4.5 Pressure relief vents                  | 10 |

|     | 2.4.6 Contact with electrolyte               | 11 |

|     | 2.4.7 Charge-discharge                       | 12 |

|     | 2.4.8 Polarity – reverse voltage             | 12 |

|     | 2.4.9 Flammability                           | 12 |

| 2.5 | Capacitor parameters and equivalent circuit. | 13 |

|     | 2.5.1 Capacitance                            | 13 |

|     | 2.5.2 Dielectric leakage resistance (DCR)    | 14 |

|     | 2.5.3 Equivalent series inductance (ESL)     | 15 |

|     | 2.5.4 Equivalent series resistance (ESR)     | 16 |

|     | 2.5.5 Operating temperature range            | 17 |

|     | 2.5.6 Storage temperature range              | 18 |

|     | 2.5.7 Rated DC voltage                       | 18 |

|     | 2.5.8 Rated surge voltage                    | 18 |

|     | 2.5.9 Transient over voltage                 | 19 |

|      | 2.5.10 Ripple current                                     | 19 |

|------|-----------------------------------------------------------|----|

| 2.6  | Capacitor bank configuration                              | 20 |

|      | 2.6.1 Parallel connection                                 | 20 |

|      | 2.6.2 Series connection                                   | 21 |

|      | 2.6.3 Parallel-series connection.                         | 22 |

|      | 2.6.4 Series-parallel connection                          | 23 |

|      | 2.6.5 Non-polarized connection                            | 23 |

| 2.7  | Cooling strategies.                                       | 24 |

| 2.8  | Shelf life                                                | 25 |

| 2.9  | Process consideration                                     | 25 |

|      | 2.9.1 Soldering                                           | 25 |

|      | 2.9.2 Mounting                                            | 25 |

| 2.10 | Disposal of electrolytic capacitors                       | 26 |

| 2.11 | Comparison to other types of capacitors                   | 26 |

|      | 2.11.1 Ceramic capacitors                                 | 26 |

|      | 2.11.2 Film capacitors                                    | 28 |

|      | 2.11.3 Solid tantalum capacitors                          | 29 |

| 2.12 | 2 Failure modes                                           | 30 |

|      | 2.12.1 Air-tightness failure of the vent (gas generation) | 31 |

|      | 2.12.2 Open failure                                       | 32 |

|      | 2.12.3 Short circuit                                      | 33 |

|      | 2.12.4 Degradation failure                                | 33 |

|      | 2.12.5 Failures of capacitor periphery                    | 33 |

| 2.13 | Need of condition monitoring for the electrolytic capacitor          | 34 |

|------|----------------------------------------------------------------------|----|

| 2.14 | 4 Reliability and fault detection                                    | 35 |

| 2.15 | 5 Previous work                                                      | 38 |

|      | 2.15.1 Diagnosis of electrolytic capacitor using the capacitor ESR   | 38 |

|      | 2.15.2 Diagnosis of electrolytic capacitor using voltage and current |    |

|      | signature                                                            | 43 |

| 2.16 | 5 Summary                                                            | 45 |

| СН   | APTER 3: FFT BASED FAULT PREDICTION OF AN ELECTROLYTIC               |    |

| CA   | PACITOR                                                              | 46 |

| 3.1  | Introduction                                                         | 46 |

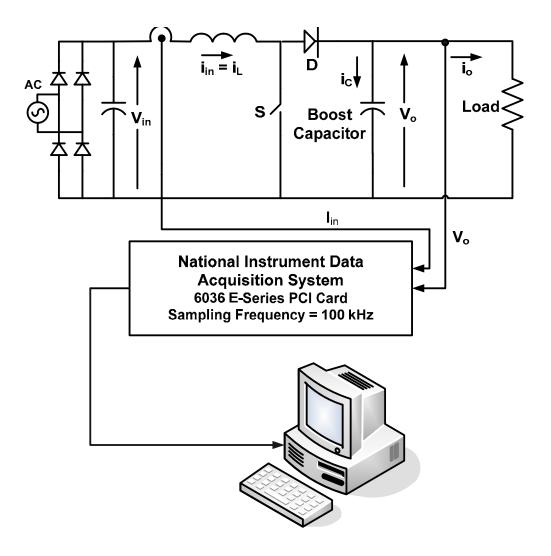

| 3.2  | Experimental setup.                                                  | 46 |

| 3.3  | Experimental results and discussion                                  | 50 |

| 3.4  | Summary                                                              | 57 |

| СН   | APTER 4: FAILURE PREDICTION OF ELECTROLYTIC CAPACITOR                |    |

| USI  | ING SYSTEM MODELING                                                  | 58 |

| 4.1  | Introduction                                                         | 58 |

| 4.2  | Experimental setup                                                   | 58 |

| 4.3  | Theory of system modeling                                            | 59 |

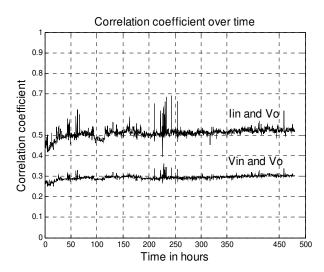

|      | 4.3.1 Correlation coefficient                                        | 60 |

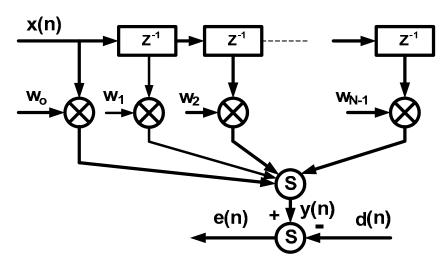

|      | 4.3.2 LMS based Wiener adaptive filter theory                        | 61 |

|      | 4.3.3 Derivation of LMS algorithm                                    | 62 |

| 4.4 | Results and discussion                                             | 64  |

|-----|--------------------------------------------------------------------|-----|

| 4.5 | Summary                                                            | 69  |

| СН  | APTER 5: CONDITION MONITORING OF ELECTROLYTIC                      |     |

| CA  | PACITORS BY PARAMETER ESTIMATION                                   | 70  |

| 5.1 | Introduction                                                       | 70  |

| 5.2 | Proposed method.                                                   | 72  |

|     | 5.2.1 Theory                                                       | 73  |

| 5.3 | Results and discussion                                             | 77  |

|     | 5.3.1 Simulation results                                           | 77  |

|     | 5.3.2 Experimental results                                         | 82  |

| 5.4 | Summary                                                            | 87  |

| СН  | APTER 6: CAPACITOR FAILURE DUE TO INRUSH CURRENT                   | 88  |

| 6.1 | Introduction                                                       | 88  |

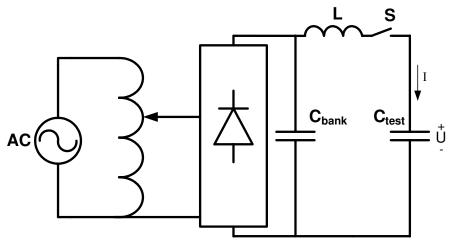

| 6.2 | Test setup and results by [42]                                     | 89  |

|     | 6.2.1 Discussion                                                   | 91  |

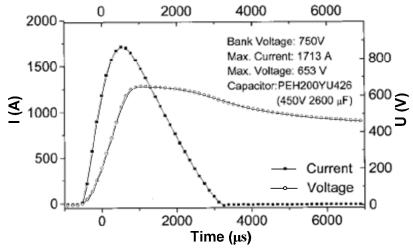

|     | 6.2.2 Analysis of successful pulse test results                    | 92  |

|     | 6.2.3 Analysis of unsuccessful pulse test results                  | 95  |

|     | 6.2.4 Conclusion of successful and unsuccessful pulse test results | 97  |

| 6.3 | Failure mechanism                                                  | 98  |

|     | 6.3.1 Construction                                                 | 98  |

|     | 6.3.2 Modeling and simulation results                              | 103 |

| 6.3.3 Experimental results            |                                                 |

|---------------------------------------|-------------------------------------------------|

| 6.3.3.1 Effect of curren              | nt pulses with short interval                   |

| 6.3.3.2 Effect of temper              | rature 114                                      |

| 6.3.3.3 Effect of curren              | nt pulses with long interval                    |

| 6.4 Summary                           | 116                                             |

|                                       |                                                 |

| CHAPTER 7: CONCLUSIONS, CO            | NTRIBUTIONS, AND                                |

| RECCOMENDATIONS                       | 117                                             |

| 7.1 Summary and conclusions           | 117                                             |

| 7.1.1 Conclusions of research         | n of phase 1: Electrolytic capacitor ripple     |

| voltage and current behavior          | with aging117                                   |

| 7.1.2 Conclusions of research         | n of phase 2: System modeling118                |

| 7.1.3 Conclusions of research         | n of phase 3: Real-time parameter estimation119 |

| 7.1.4 Conclusions of research         | n of phase 4: Capacitor failure due to inrush   |

| current                               | 120                                             |

| 7.2 Contributions                     | 120                                             |

| 7.3 Recommendations for future resear | rch122                                          |

| 7.3.1 Investigating different         | kinds of non-stationary operation122            |

| 7.3.2 Condition monitoring u          | using temperature                               |

| 7.3.3 Relaxation of pulse we          | akened capacitor with DC bias voltage123        |

| 7.3.4 Expansion to other faul         | ts in the system123                             |

|                                       |                                                 |

| APPENDIX A: NI 6036E FAMILY S         | PECIFICATIONS124                                |

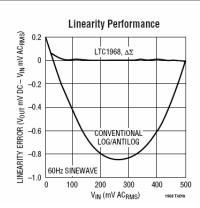

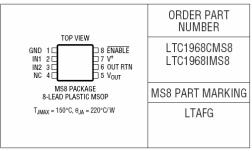

| APPENDIX B: LTC 1968: PRECISION WIDE BANDWIDTH RMS-TO-DC |     |

|----------------------------------------------------------|-----|

| CONVERTER                                                | 129 |

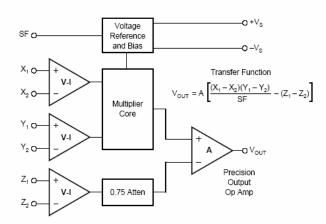

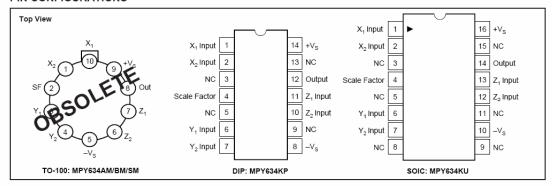

| APPENDIX C: WIDE BANDWIDTH PRECISION ANALOG MULTIPLIER   | 132 |

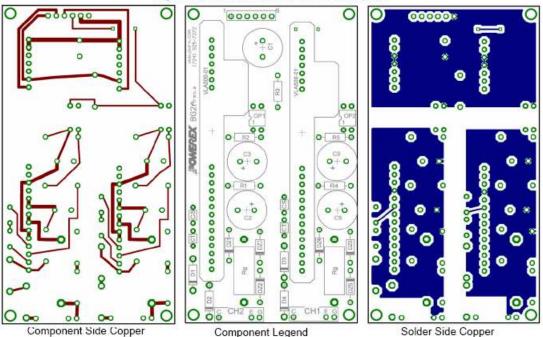

| APPENDIX D: BG2A: UNIVERSAL GATE DRIVE PROTOTYPE BOARD   | 135 |

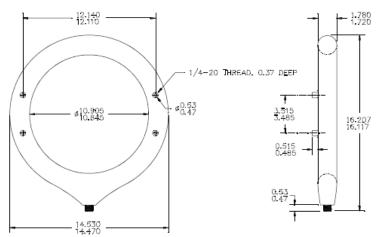

| APPENDIX E: PEARSON CURRENT MONITOR                      | 139 |

| REFERENCES                                               | 140 |

# LIST OF TABLES

| Table 3.1 | Electrolytic capacitor parameters of new and worn out capacitor      | 51  |

|-----------|----------------------------------------------------------------------|-----|

| Table 5.1 | Simulation results for estimated parameters                          | 87  |

| Table 5.2 | Experimental results for estimated parameters                        | 87  |

| Table 6.1 | Energy for successful and unsuccessful pulse                         | 98  |

| Table 6.2 | Thickness of different layers in the cylindrical capacitor           | 101 |

| Table 6.3 | Estimated values of parameters for equivalent cylindrical capacitors | 104 |

# LIST OF FIGURES

| Figure 2.1  | Cross section of an electrolytic capacitor            | ∠   |

|-------------|-------------------------------------------------------|-----|

| Figure 2.2  | Wound capacitor elements                              | 7   |

| Figure 2.3  | Cross section of wound capacitor element materials    | 7   |

| Figure 2.4  | Electrolytic capacitor equivalent circuit             | .13 |

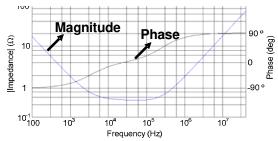

| Figure 2.5  | Bode-plots of the electrolytic capacitor              | .15 |

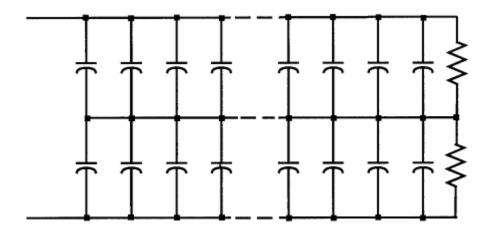

| Figure 2.6  | Parallel-series connection                            | .22 |

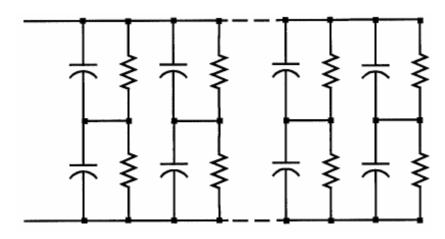

| Figure 2.7  | Series-parallel connection                            | .23 |

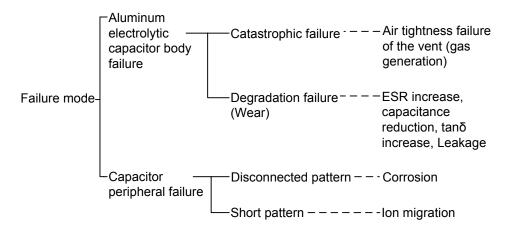

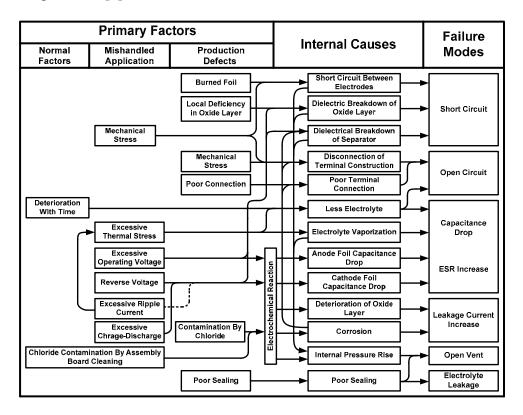

| Figure 2.8  | Failure mode chart                                    | .31 |

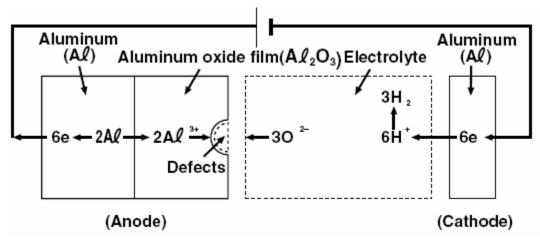

| Figure 2.9  | Chemical characteristics of an electrolytic capacitor | .32 |

| Figure 2.10 | Failure modes of an electrolytic capacitor            | .34 |

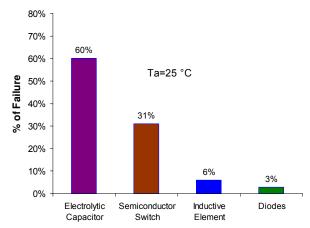

| Figure 2.11 | Distribution of failure for various power components  | .35 |

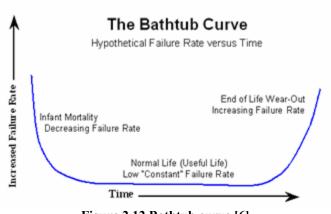

| Figure 2.12 | Bathtub curve                                         | .36 |

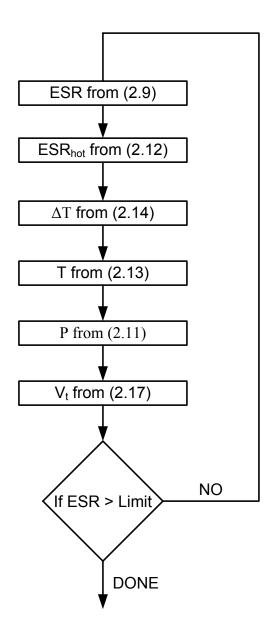

| Figure 2.13 | Flow-chart for the capacitor ESR estimation           | .42 |

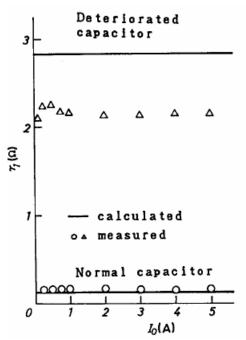

| Figure 2.14 | $\gamma_1$ versus load current, $I_o$                 | .44 |

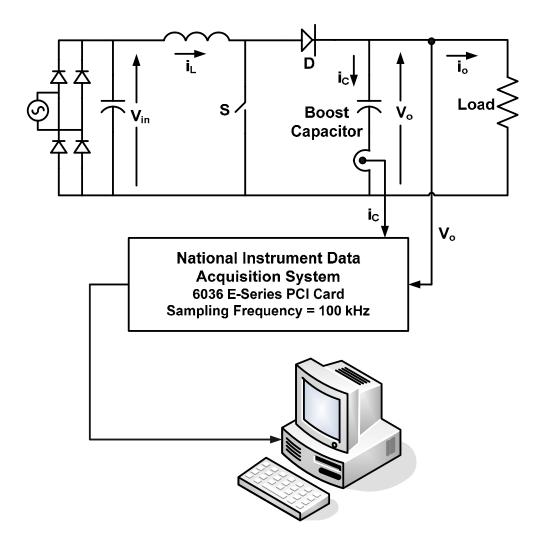

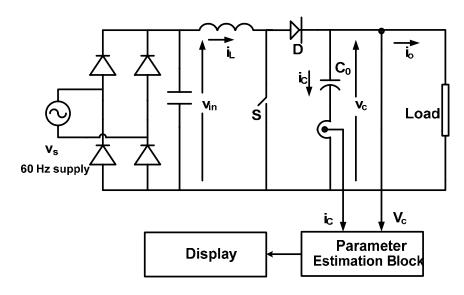

| Figure 3.1  | Boost-converter                                       | .47 |

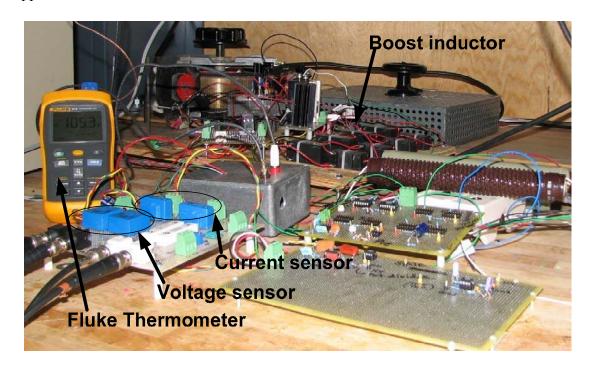

| Figure 3.2  | Boost converter experimental setup                    | .48 |

| Figure 3.3  | Interface with NI data acquisition system             | .48 |

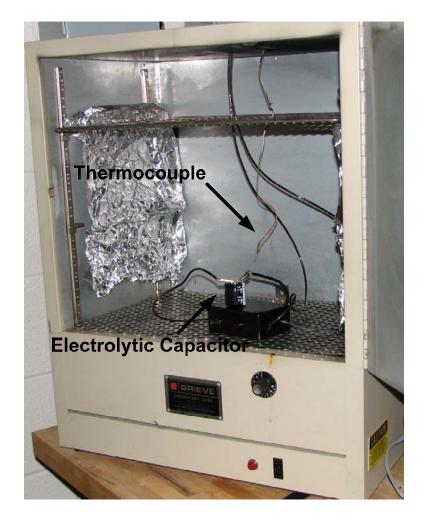

| Figure 3.4  | Temperature controlled oven                           | .49 |

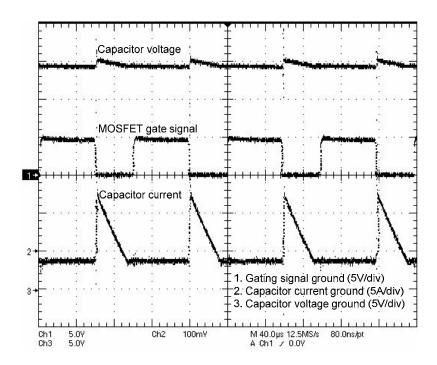

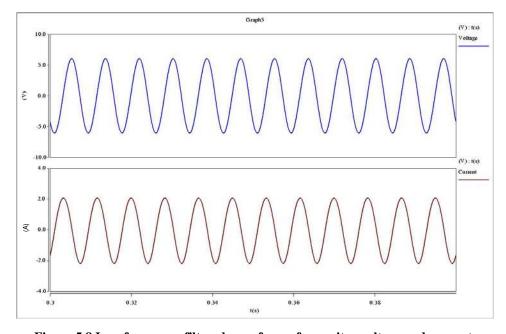

| Figure 3.5  | Waveforms for capacitor voltage and current           | .50 |

| Figure 3.6   | Bode plot of a new capacitor                                        | 51 |

|--------------|---------------------------------------------------------------------|----|

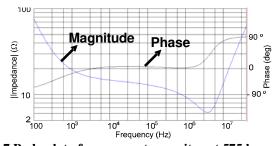

| Figure 3.7   | Bode plot of a worn-out capacitor                                   | 51 |

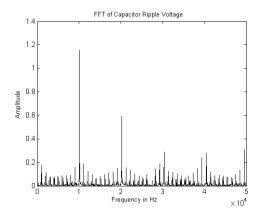

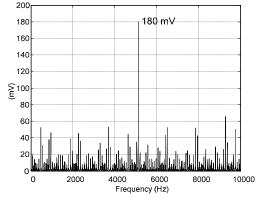

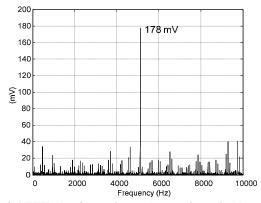

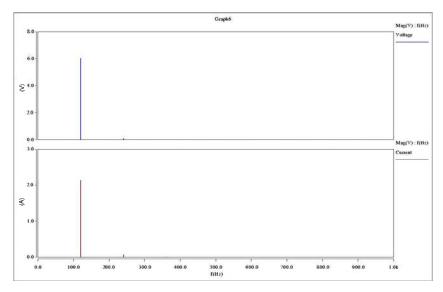

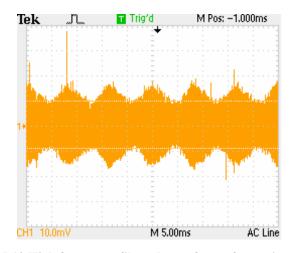

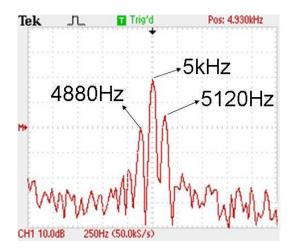

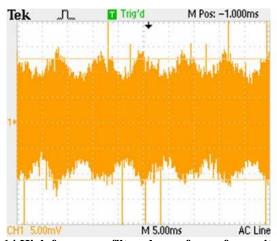

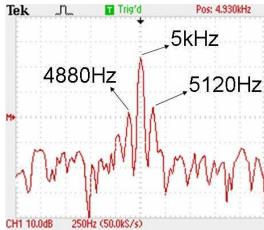

| Figure 3.8   | FFT plot for capacitor ripple voltage                               | 52 |

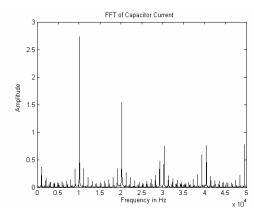

| Figure 3.9   | FFT plot for capacitor current                                      | 52 |

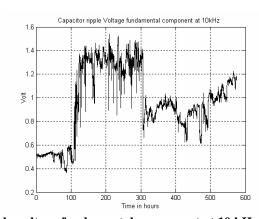

| Figure 3.10  | Capacitor ripple-voltage fundamental component                      | 52 |

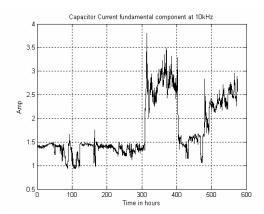

| Figure 3.11  | Capacitor current fundamental component                             | 53 |

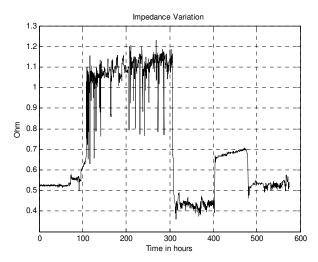

| Figure 3.12  | Capacitor impedance variation over time                             | 54 |

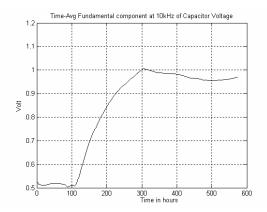

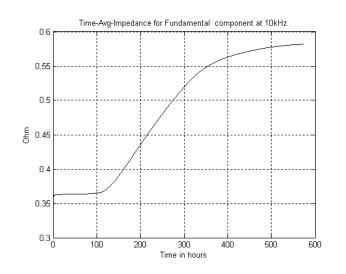

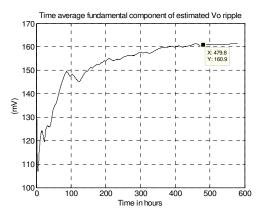

| Figure 3.13  | Time-average plot of fundamental component of the capacitor voltage | 55 |

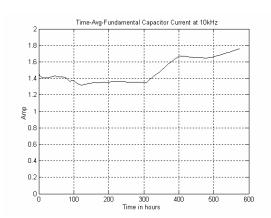

| Figure 3.14  | Time-average plot of fundamental component of the capacitor current | 55 |

| Figure 3.15  | Time-average plot of capacitor impedance                            | 56 |

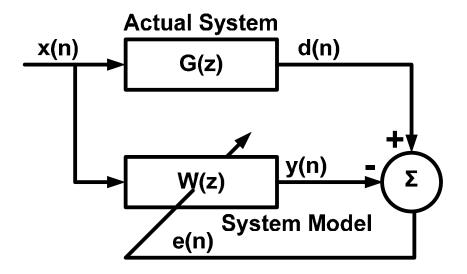

| Figure 4.1   | Structure of the adaptive filter model                              | 60 |

| Figure 4.2   | Correlation coefficient plots over time                             | 61 |

| Figure 4.3   | FIR based adaptive filter model                                     | 62 |

| Figure 4.4   | Boost-converter circuit                                             | 65 |

| Figure 4.5   | FFT plot for actual capacitor ripple voltage                        | 67 |

| Figure 4.6   | FFT plot for estimated capacitor ripple voltage                     | 67 |

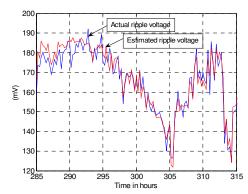

| Figure 4.7   | Portion of actual and estimated fundamental component of capacitor  |    |

| ripple volta | ge                                                                  | 68 |

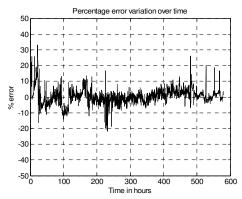

| Figure 4.8   | Percentage error variation over time                                | 68 |

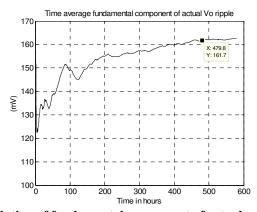

| Figure 4.9   | Time-average evolution of fundamental component of actual capacitor |    |

| ripple volta | ge                                                                  | 69 |

| Figure 4.10  | Time-average evolution of fundamental component of estimated        |    |

| capacitor ri | ople voltage                                                        | 69 |

| Figure 5.1   | Electrolytic capacitor equivalent circuit                               | 71 |

|--------------|-------------------------------------------------------------------------|----|

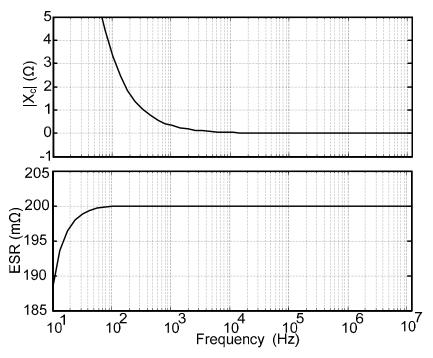

| Figure 5.2   | Bode-plot of electrolytic capacitor                                     | 74 |

| Figure 5.3   | Variation in X <sub>C</sub> and ESR with frequency                      | 75 |

| Figure 5.4   | Boost-converter                                                         | 75 |

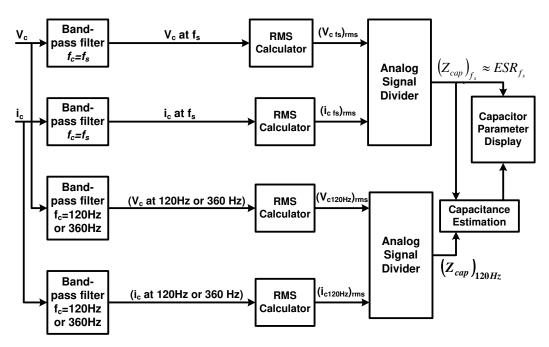

| Figure 5.5   | Parameter estimation scheme                                             | 76 |

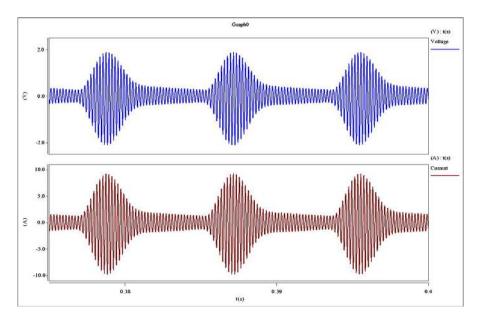

| Figure 5.6   | High frequency filtered waveform of capacitor voltage and current       | 78 |

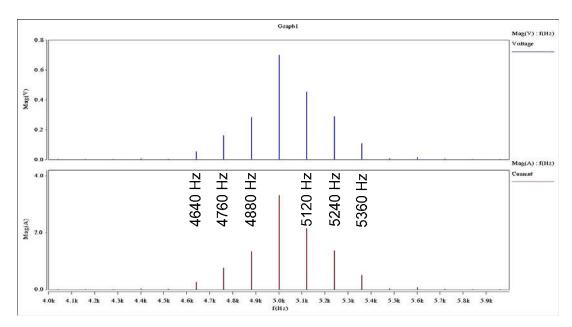

| Figure 5.7   | FFT plot of high frequency components for capacitor voltage and current | 79 |

| Figure 5.8   | Low frequency filtered waveform of capacitor voltage and current        | 81 |

| Figure 5.9   | FFT plot of low frequency filtered waveform of capacitor current        | 82 |

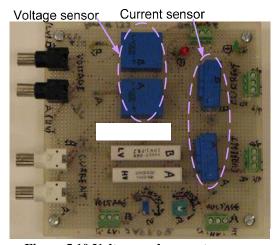

| Figure 5.10  | Voltage and current sensors.                                            | 82 |

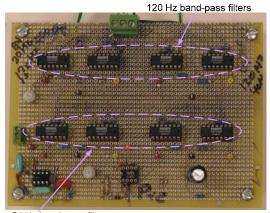

| Figure 5.11  | Analog band-pass filters                                                | 83 |

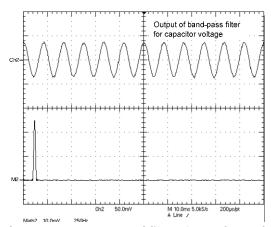

| Figure 5.12  | High frequency filtered waveform of capacitor voltage                   | 83 |

| Figure 5.13  | FFT plot of high frequency filtered waveform of capacitor voltage       | 84 |

| Figure 5.14  | High frequency filtered waveform of capacitor current                   | 84 |

| Figure 5.15  | FFT plot of high frequency filtered waveform of capacitor current       | 84 |

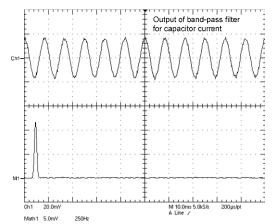

| Figure 5.16  | 120 Hz frequency component of filtered waveform of capacitor current    | 85 |

| Figure 5.17  | FFT plot of 120 Hz frequency component of filtered waveform of          |    |

| capacitor cu | nrrent                                                                  | 86 |

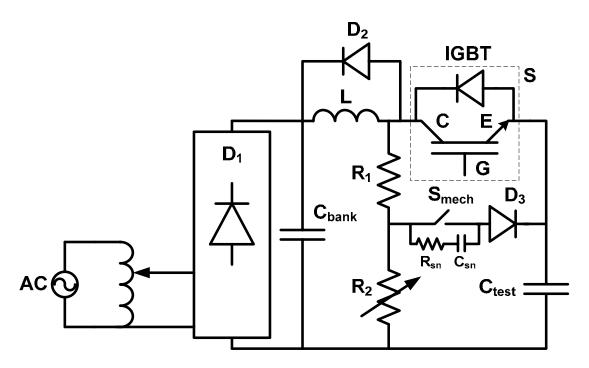

| Figure 6.1   | Experimental set up for transient over voltage effect                   | 90 |

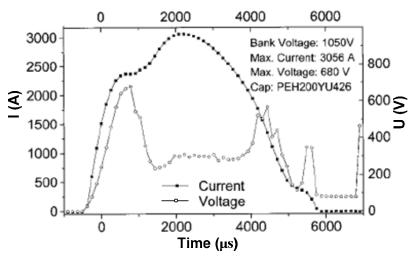

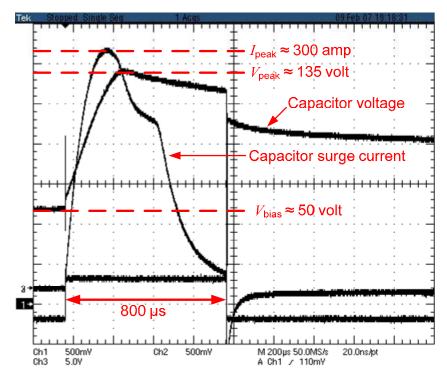

| Figure 6.2   | Successful pulse test result                                            | 90 |

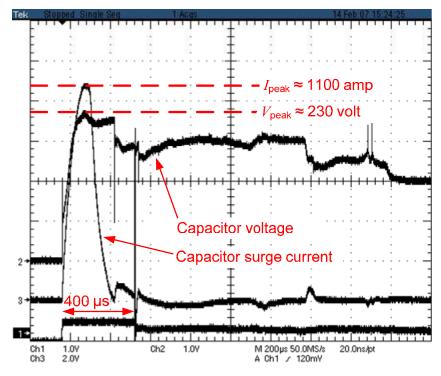

| Figure 6.3   | Unsuccessful pulse test result                                          | 91 |

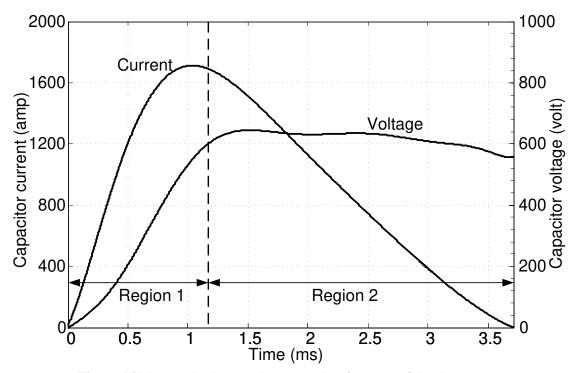

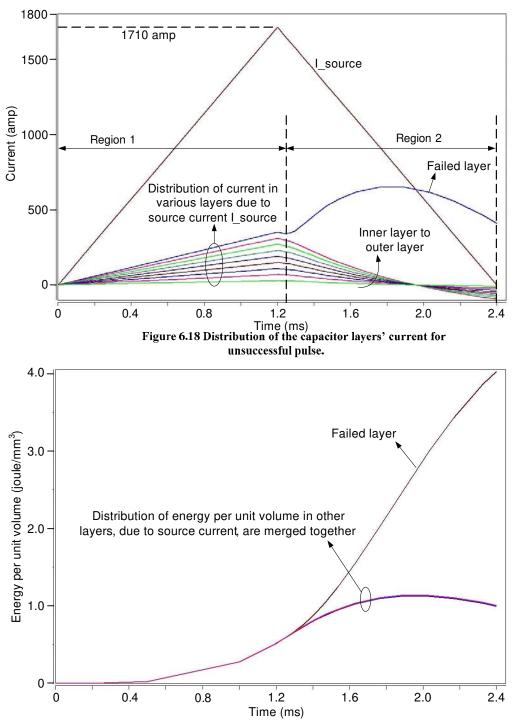

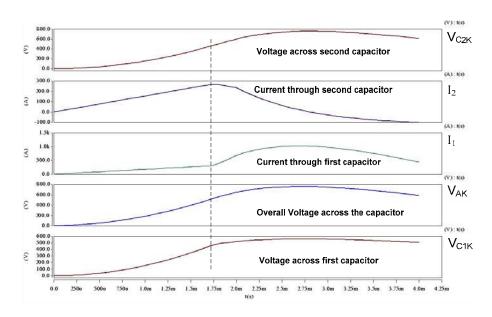

| Figure 6.4   | Measured voltage and current plots for successful pulse test            | 92 |

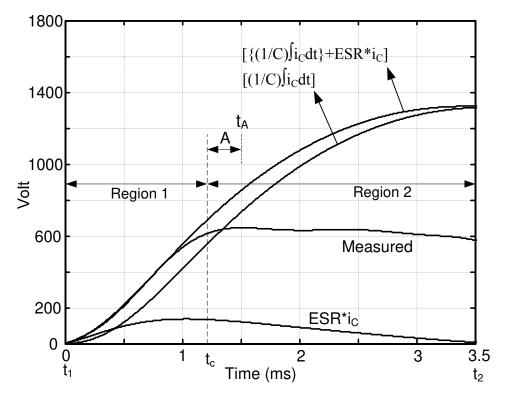

| Figure 6.5   | Voltage plots for successful pulse test                                 | 93 |

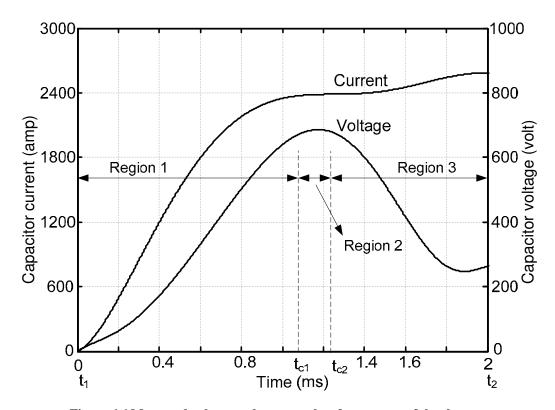

| Figure 6.6 Measured voltage and current plots for unsuccessful pulse test                | 95  |

|------------------------------------------------------------------------------------------|-----|

| Figure 6.7 Voltage plots for unsuccessful pulse                                          | 96  |

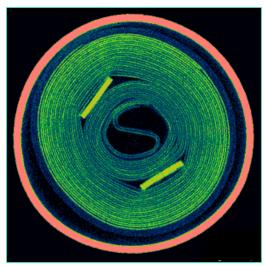

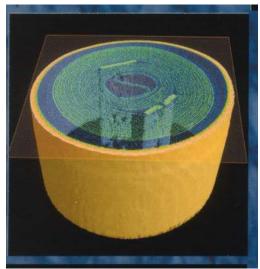

| Figure 6.8 X-ray view of the electrolytic capacitor                                      | 99  |

| Figure 6.9 3-D X-ray view of the electrolytic capacitor                                  | 99  |

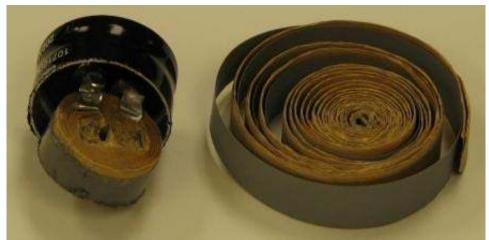

| Figure 6.10 Electrolytic capacitor                                                       | 100 |

| Figure 6.11 Electrolytic capacitor tab location                                          | 100 |

| Figure 6.12 Electrolytic capacitor single layer configurations                           | 101 |

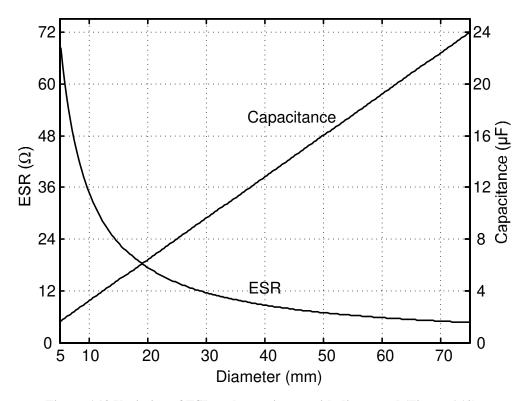

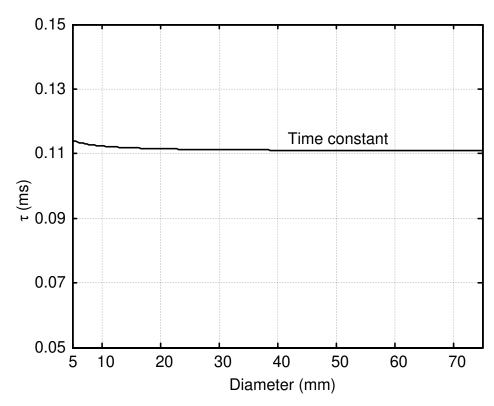

| Figure 6.13 Variation of ESR and capacitance with diameter                               | 102 |

| Figure 6.14 Variation of capacitor layer time-constant with diameter                     | 103 |

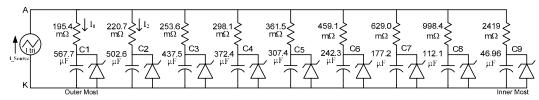

| Figure 6.15 Electrolytic capacitor model.                                                | 105 |

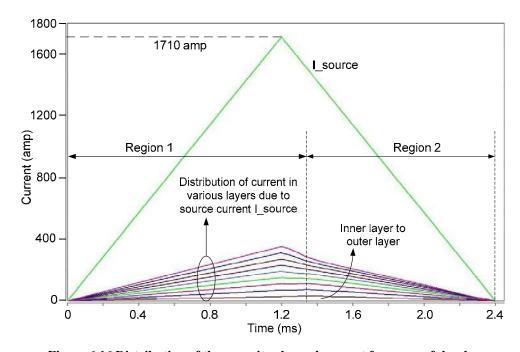

| Figure 6.16 Distribution of the capacitor layers' current for successful pulse           | 105 |

| Figure 6.17 Distribution of energy per unit volume for electrolytic capacitor layers for | or  |

| successful pulse                                                                         | 106 |

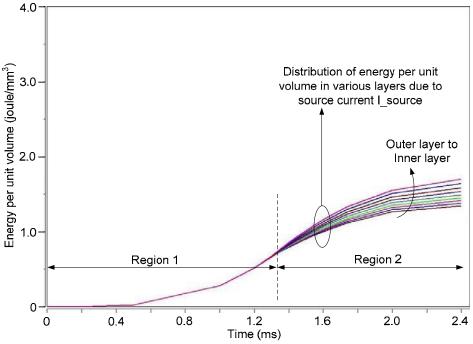

| Figure 6.18 Distribution of the capacitor layers' current for unsuccessful pulse         | 107 |

| Figure 6.19 Distribution of energy per unit volume for electrolytic capacitor layers for | or  |

| unsuccessful pulse.                                                                      | 107 |

| Figure 6.20 Effects of 'Zener diode' like breakdown                                      | 109 |

| Figure 6.21 Circuit diagram for effects of current-pulses testing                        | 110 |

| Figure 6.22 Voltage and current plots for a successful current pulse                     | 111 |

| Figure 6.23 Voltage and current plots for an unsuccessful current pulse                  | 111 |

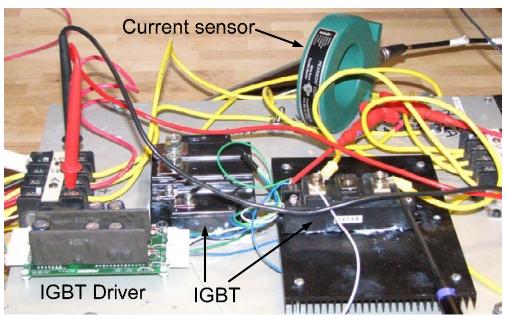

| Figure 6.24 Experimental setup for current surge effects                                 | 112 |

| Figure 6.25 Effect of current pulses on electrolytic capacitor leakage resistances       | 113 |

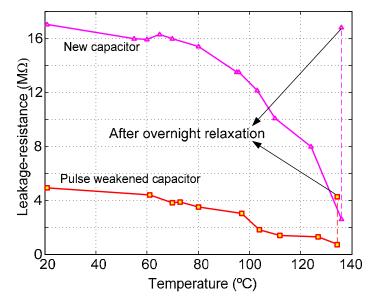

| Figure 6.26 Effect of temperature on new and current pulse weakened capacitors           | 114 |

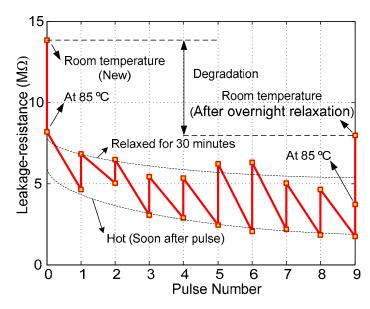

| Figure 6.27 Effect of current pulses with relaxation at 85 °C with first capacitor   | 115 |

|--------------------------------------------------------------------------------------|-----|

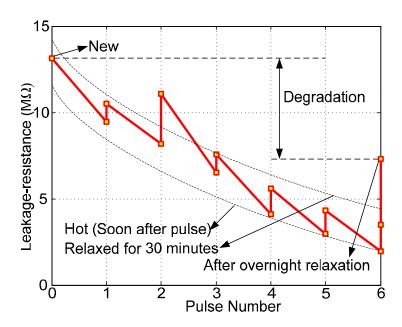

| Figure 6.28 Effect of current pulses with relaxation at room temperature with second | 1   |

| capacitor                                                                            | 116 |

## **SUMMARY**

The objective of this research is to advance the field of condition monitoring of electrolytic capacitors used in power electronics circuits.

The construction process of an electrolytic capacitor is presented. Descriptions of various kinds of faults that can occur in an electrolytic capacitor are discussed. The methods available to detect electrolytic capacitor faults are discussed. The effects of the capacitor faults on the capacitor voltage and current waveforms are investigated through experiments. It is also experimentally demonstrated that faults in the capacitor can be detected by monitoring the capacitor voltage and current.

Various ESR estimation based detection techniques available to detect capacitor failures in power electronics circuits are reviewed. Three algorithms are proposed to track and detect capacitor failures: an FFT based algorithm, a system modeling based detection scheme, and finally a parameter estimation based algorithm. The parameter estimation based algorithm is a low-cost real-time scheme, and it is inexpensive to implement.

Finally, a detailed study is carried out to understand the failure mechanism of an electrolytic capacitor due to inrush current.

## **CHAPTER 1**

## INTRODUCTION AND OBJECTIVE OF RESEARCH

#### 1.1 Problem statement

Aluminum electrolytic capacitors are used in most power electronic circuits because they can achieve high capacitance and voltage ratings in small, cost efficient case sizes. The high volumetric efficiency of an electrolytic capacitor is achievable because of its enhanced plate surface area and a very thin dielectric layer. This type of capacitor has traditionally been used for filtering, timing networks, by-pass, coupling, and other applications requiring a cost effective, volumetrically efficient, and highly reliable component. Unfortunately, electrolytic capacitors are considered to be a weak link in all of these applications [1].

Condition monitoring of the electrolytic capacitor is therefore assuming a new importance in critical high performance applications. Early detection of faults would allow preventive maintenance to be performed, and provide sufficient time for the controlled shutdown of the process, thereby reducing the costs of outage-time and repairs. The common faults in electrolytic capacitor include initial catastrophic failures because of misapplication or manufacturing defect, and wear-out faults. However, some research works have been reported in literature for the diagnosis of the electrolytic capacitor faults, most of these research focuses on the capacitor fault because of aging [18-31]. These reported research works are difficult to implement in a cost-effective way, which is

further explained in Chapter 2. A new low-cost online monitoring scheme for an electrolytic capacitor failure is presented in Chapter 5.

### 1.2 Objective

The objective of this research is to advance the field of fault monitoring of an electrolytic capacitor operating in a power electronic circuit in a cost-effective way. This objective is addressed as three parts in this thesis. The first part, Chapter 3, experimentally characterizes the effects of the capacitor wear-out faults on the capacitor ripple voltage, and the capacitor ripple current. The second part, Chapter 4, develops methods to detect the capacitor faults by system modeling using the converter input current. A cost-effective method, Chapter 5, for the condition monitoring of the electrolytic capacitor, is presented using parameter-estimation technique. The parameters of the capacitor change because of aging and misapplication. Therefore, the condition of an electrolytic capacitor can be monitored by monitoring the parameters of the capacitor in real-time.

Finally, electrolytic capacitor faults caused by inrush current due to line surgevoltage are studied in Chapter 6, and a model of the capacitor is developed to explain the failure of an electrolytic capacitor due to inrush current. A summary of contributions appear in Chapter 7.

#### **CHAPTER 2**

#### BACKGROUND MATERIAL AND PREVIOUS WORK

## 2.1 Introduction

To facilitate a clear understanding of the proposed condition monitoring schemes, the construction of an electrolytic capacitor is now considered in more detail. The various modes of the capacitor failures are discussed. In addition, this chapter reviews and summarizes the existing research for condition monitoring of an electrolytic capacitor.

## 2.2 Electrolytic capacitor

The aluminum electrolytic capacitor is a passive component that has kept pace with advancements in technology. Aluminum electrolytic capacitors are used in various applications because they can achieve high capacitance and high voltage ratings in small, cost-efficient case sizes. This type of capacitor has traditionally been used for filtering, timing networks, bypassing, coupling, and other applications requiring a cost-effective, volumetrically efficient, and highly reliable component. To understand how this is accomplished, it is important to examine some of the basic properties of capacitors [2, 3].

A capacitor is made up of two parallel plates, the electrodes, with a dielectric between them. The amount of capacitance is directly proportional to the surface area of the electrode, but inversely proportional to the dielectric thickness. If the thickness is

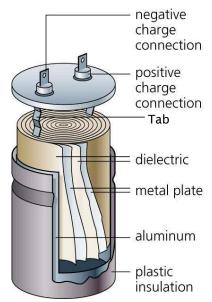

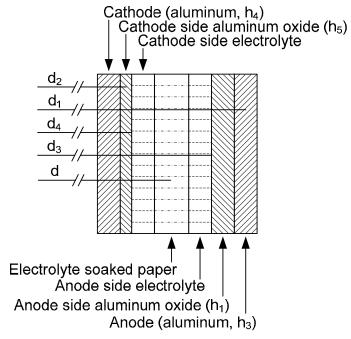

reduced by one-half, the capacitance is doubled. The high volumetric efficiency of an electrolytic capacitor is due to its enhanced plate surface area, which is enhanced by an etching process. A large internal surface can be created on the aluminum electrodes by electrochemical etching. The dielectric is typically an oxide with a high dielectric strength, which is electrochemically deposited in thin layers. This combination produces a high capacitance in a small volume [2-7]. The aluminum electrolytic capacitor consists of an anode foil, a cathode foil, and a separator paper that are wound together and impregnated with an electrolyte. The anode foil has an aluminum oxide layer acting as the dielectric. After the thin aluminum foil (65 to 100 microns) is electrochemically etched to increase the plate's surface area, the dielectric is produced by anodic oxidation on its surface. The cathode foil, in general, utilizes no oxidation process. An illustration of a typical aluminum electrolytic capacitor is shown in Figure 2.1.

Figure 2.1 Cross section of an electrolytic capacitor. (Source: Precision Graphics)

## 2.3 Electrolytic capacitor construction process

#### 2.3.1 Etching [3]

The plates, or electrodes, are made of high-purity thin aluminum foil (0.05 to 0.1 mm thick). To get the maximum capacitance for a given electrode surface area, an electrochemical process called "etching" is used to dissolve some of the surface material and increase the surface area of the foil in the form of a dense network of microscopic channels. The etching process consists of continuously subjecting the aluminum foil to a chloride solution with an AC, DC, or AC/DC voltage applied between the etch solution and aluminum foil. The increase in surface area is referred to as foil gain, and can be as much as 100 times for foil being used in low-voltage capacitor applications, and 20 to 25 times for higher-voltage applications [2].

## **2.3.2 Formation [3]**

The dielectric of the aluminum electrolytic capacitor is composed of a thin layer of aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), which develops or "forms" on the surface of the etched aluminum foil during a process called "formation." This process of forming the dielectric oxide on the aluminum foil (electrode) requires a continuous application of DC voltage at 140% to 200% of the rated voltage for the capacitor being manufactured. The dielectric thickness of this aluminum oxide film is approximately 15 Å/volt [2]. The insulation strength is approximately 10<sup>7</sup> V/cm. Since capacitance is inversely proportional to the dielectric thickness and the dielectric thickness is proportional to the forming voltage, the relationship between capacitance and forming voltage is given by [2]

$$C \times V = const$$

(2.1) where  $C = capacitance$ , and  $V = forming voltage$

This is true for high-voltage foil, which has a relatively coarse etch structure. However, for foils that have extremely fine etch structures, the conversion of aluminum to aluminum oxide has a significant smoothing effect on the etch structure, resulting in a non-linear relationship.

#### **2.3.3 Slitting [3]**

The etched and formed foil is then slit into various widths, depending on the specific size of the capacitor.

## 2.3.4 Winding [3]

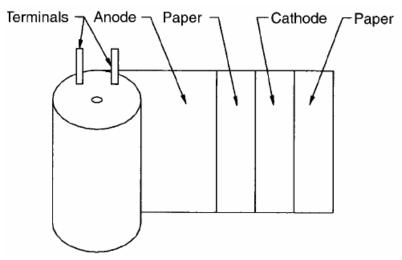

Each capacitor contains two foils, the positive foil is called the anode and the negative is called the cathode. The anode and cathode foils, along with a separator paper, called the "separator," are rolled into a cylindrical shape. The separator paper prevents the anode and cathode foils from coming into contact with each other, and shorting. As part of a highly automated winding process, aluminum tabs are attached to the anode and cathode foils. This completed assembly of etched and formed foil, separator paper, and attached tabs is called the capacitor "element" as shown in Figures 2.1, 2.2 and 2.3.

Figure 2.2 Wound capacitor elements.

Figure 2.3 Cross section of wound capacitor element materials.

## 2.3.5 Impregnation [3]

The electrolyte is now added to the assembly by a process called "impregnation." The method of impregnation requires the wound element to be immersed into the electrolyte by a vacuum/pressure cycle either with or without applied heat or simple

absorption. The electrolyte contains a solvent such as ethylene glycol and a solute such as ammonium borate. Should the dielectric film be damaged, the presence of the electrolyte will allow the capacitor to heal itself by forming more oxide. By selecting different electrolytes, capacitor characteristics such as operating temperature range, frequency response, shelf life, and load life, can be further improved.

#### 2.3.6 Sealing and aging [3]

The impregnated element is then sealed in an aluminum can. The sealing material may be rubber, rubber-backed phenolic, molded phenolic resin, or polyphylenesulfide (PPS). The final process is "aging," during which a voltage greater than the rated voltage of the capacitor is applied at elevated temperatures. The purpose is to reform (or repair) any oxide film that may have been damaged during the slitting, winding, and assembly processes.

# 2.4 Application guide

## 2.4.1 Dielectric absorption [2]

Dielectric absorption may be observed as the re-appearance of a voltage across a capacitor after the terminals have been shorted for a brief period, and the short removed. This characteristic is important in RC timing circuits, triggering systems, and phase shift networks. For aluminum electrolytic capacitors, dielectric absorption will allow up to 10% recovery of the charging voltage between 100 s and 1000 s at 25°C and it is more pronounced at higher temperatures. Maximum dielectric absorption can be obtained by charging capacitors for 1 hour at rated voltage and discharging through a dead short for 1 minute. Subsequent measurements over time can be made using a high impedance probe.

With high-voltage aluminum electrolytic capacitors, rebound voltages of 40 to 50 V are possible [2]. Rebound voltages are caused by internal chemical process in which there exists a small voltage across the capacitor terminals due to charge polarization in the capacitor dielectric-layer even in the absence of any external applied voltage. While such voltages are not a safety hazard, they can certainly create a frightening distraction if the terminals are shorted by a tool during installation. Conductive tape and wire shorting straps can be supplied to avoid this problem. The tradeoff is extra cost and the labor to remove them.

## 2.4.2 Insulation and grounding [2]

With non-solid electrolyte, aluminum electrolytic capacitor cans connect to the negative terminals through the electrolyte of the capacitor. The resulting isolation resistance may vary from a few ohms to a few thousand ohms. For axial-leaded capacitors and flat packs, the case is connected to the negative lead. If objects contacting the cases are to be at a potential other than the negative terminals, capacitors with insulating sleeves are used. The plastic insulation sleeve can withstand 3000 Vdc or 2500 Vac at 60 Hz [2].

#### 2.4.3 External pressure [2]

Aluminum electrolytic capacitors can operate at altitudes to 80,000 feet and at pressures as low as 3 kPa, and maximum air pressure depends on the size and style of the capacitor. Exceeding the maximum value can damage the capacitor by rupturing the case, opening the pressure-relief vent, or causing a short circuit.

#### 2.4.4 Mechanical vibration [2]

Aluminum electrolytic capacitors can generally withstand 10 g vibration forces. To test vibration resistance, a capacitor is clamped to a vibrating platform and subjected to a simple harmonic motion having maximum peak-to-peak amplitude of 0.06 inches and a maximum acceleration of 10 g or 15 g as specified. The frequency of vibration is varied linearly between 10 and 55 Hz. The entire frequency range is traversed in 1 minute. Unless specified otherwise, capacitors are vibrated for one and half hours with the direction of motion being parallel to the axis of the capacitor; then the capacitor is placed so that the direction of motion is perpendicular to the axis and vibration is continued for another one and half hours. During the last half hour of the test, the capacitor is connected to a bridge measuring circuit, and observations are made for any mechanical damage for a 3-minute period. In addition, there should not be any evidence of loosening of the capacitor element within the container when shaken by hand following the test. There should not be any indication of intermittent contact, open or shorting during the 3-minute observation period.

### 2.4.5 Pressure-relief vents [2]

During operation of an aluminum electrolytic capacitor with non-solid electrolyte, gas pressure normally increases. The gas is mostly hydrogen and excess pressure is avoided by permeation of the gas through the capacitor's seal. However, in some cases like the application of an overvoltage, reverse voltage, AC voltage or capacitor failure, excess pressure can cause the capacitor to explode. To avoid the risk of explosion, aluminum electrolytic capacitors are usually equipped with pressure-relief vent structures. These safety vents are intended to rupture and release the gas pressure. After

rupture, the capacitor has a limited life because it loses electrolyte and dries out. Care should be taken to avoid interfering with the operation of the vent, for instance by mounting elements, such as clamps, glue or potting compounds. In the case of large capacitors with the capacitor elements secured by thermoplastic potting, it should not be mounted with the safety vents down, as the potting may flow when the capacitors overheat, and block the vents. In rare cases, for capacitors mounted alone, and more often for capacitors in multiple-unit parallel capacitor banks, a fully functioning pressure relief device may not react in time. This could be from extreme overload or ignition of gas inside the capacitor through sparking caused by breakdown. Personnel should be protected from possible rupture of high-energy capacitors with substantial shielding. Examples of appropriate shielding for testing are quarter-inch thick steel or half-inch thick polycarbonate enclosures with one end open to redirect the explosion rather than contain it. The excess internal pressure will be relieved without violent expulsion of the capacitor element, or cover, or ignition of surrounding material.

## 2.4.6 Contact with electrolyte [2]

The electrolyte in non-solid electrolyte capacitors is a biodegradable liquid based on a stable solvent with a high boiling point as the main ingredient. Common solvents are ethylene glycol (EG), dimethylformamide (DMF), and gammabutyrolactone (GBL) [2]. The electrolyte includes an acid base system, and other chemicals. The electrolyte is chemically neutral and contains no lead compounds, or halogenated compounds. It has a low toxicity but contact with the skin or eyes should be avoided, and avoid prolonged inhalation. Contact with electrolyte can be treated by rinsing the exposed area with water. If the electrolyte contacts eyes, it should be flushed for 10 minutes with running water. If

vapors are present, the room should be ventilated. Smoke from burning electrolyte is irritating but does not contain dioxins or similar toxic substances.

#### 2.4.7 Charge-discharge [2]

Frequent, rapid charging and discharging of aluminum electrolytic capacitors which were not designed for such service, can damage the capacitors by overheating, and overpressure, or breakdown with consequent failure by open or short circuit.

## 2.4.8 Polarity – reverse voltage [2]

The polarity of each capacitor should be checked, both in circuit design and in mounting. While the capacitors can withstand continuous application of 1.5 V reverse voltage, exceeding that value can damage the capacitor by overheating, overpressure, and dielectric breakdown. This can result in associated open-circuit or short-circuit failures and rupture of the capacitor's pressure-relief vent.

### 2.4.9 Flammability [2]

Aluminum electrolytic capacitors contain materials, which can catch fire and support combustion when contacted by flames. Flammable parts include plastic parts, insulating sleeves, paper, and the electrolytes. Most capacitors will pass the needle-flame test requirements of UL 94V-O [48], and do not support combustion to the requirements of category B or C. In rare cases, the capacitor may self-ignite from heavy overload (high-ripple current) or capacitor defect. Hydrogen in the capacitor can ignite if sparking occurs during capacitor failure. In critical applications such as mining applications, fire-resistant shields should be provided.

## 2.5 Capacitor parameters and equivalent circuit [2]

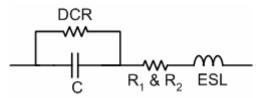

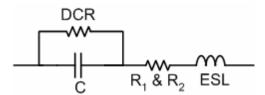

The equivalent circuit of an aluminum electrolytic capacitor is shown in Figure 2.2. Because of the physical design elements and construction, a capacitor not only has capacitance, but it also has a series resistance and an inductance as well as a parallel resistance allowing the flow of current.

Figure 2.4 Electrolytic capacitor equivalent circuit, where C = capacitance, ESL = equivalent-series-inductance, DCR = dielectric-leakage-resistance,  $R_1$  = electrolyte resistance,  $R_2$  = tab resistance.

#### 2.5.1 Capacitance

The capacitance of aluminum electrolytic capacitor as well as other capacitors, is expressed by

$$C = \frac{\mu_{\circ} \mu_{r} A}{d} \tag{2.2}$$

where  $\mu_0$  = Dielectric constant in free space (8.8542 x  $10^{-12}$  F/m)

$\mu_r$  = Relative dielectric constant of the material

A = Surface area of the dielectric ( $m^2$ )

d = Thickness of the dielectric (m)

A large capacitance can be obtained when

- The dielectric constant is high

- The surface area is large

- The dielectric is thin

In aluminum electrolytic capacitors, the relative dielectric constant is about 8 to 10, and the aluminum oxide dielectric layer is thin (about 15 Å per volt). However, high gain foil produced by the electrochemical etching, creates a surface magnification, or gain, as much as 100 times for the low voltage foil, and 20 to 25 times for the high voltage foil. Therefore, an aluminum electrolytic capacitor can provide a large capacitance compared to other types of capacitors of the same volume. In addition, capacitance tolerance is the permitted minimum and maximum capacitance values expressed as a percentage decrease and increase from the rated capacitance,  $\Delta C/C$ . Typical capacitance tolerances are  $\pm 10\%$ , and  $\pm 20\%$ , however, tighter tolerances are more readily available in high voltage capacitors, e.g., above 150 V, but tolerances tighter than  $\pm 10\%$  are generally not available [3-7]. However, tighter tolerance parts may meet other tolerance rating requirements, and are readily substitutable if available. Finally, the capacitance also varies with temperature and frequency, and the variation itself is dependent on the rated voltage and the capacitor size.

## 2.5.2 Dielectric leakage resistance (DCR)

The dielectric of a capacitor has a high resistance, which prevents the flow of DC current. However, some defect areas in the dielectric allow a small amount of current to pass, called leakage current [8]. The areas allowing current flow are due to small foil impurity sites that are not homogeneous, and the dielectric formed over these impurities does not create a strong bond. These bonds break down when the capacitor is exposed to high DC voltages, and hence the leakage current increases. Leakage current is also determined by the following factors:

#### • Capacitance value

- Applied voltage versus rated voltage

- Previous history

The leakage current is proportional to the capacitance and decreases as the applied voltage is reduced [2]. If the capacitor has been at elevated temperatures without voltage applied for an extended time, some degradation of the oxide dielectric may take place, which will result in a higher leakage current. Usually this damage will be repaired when voltage is reapplied.

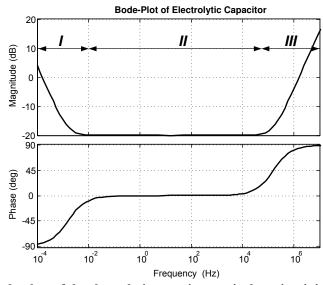

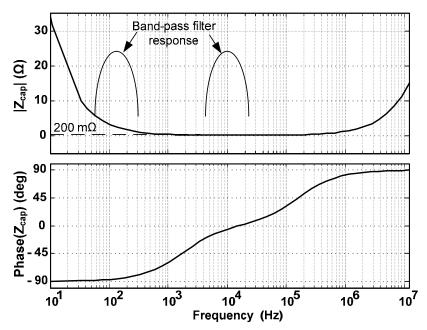

## 2.5.3 Equivalent series inductance (ESL)

The inductance of a capacitor is a constant, and is due primarily to the capacitor terminal connection. The inductance varies anywhere from 10 nH for miniature radial capacitors to as high as 100 nH for large can type capacitors. Generally, the inductance does not affect the overall impedance unless the capacitor is operating at high frequencies, as shown in the Bode-plot of the equivalent-circuit impedance of an electrolytic capacitor in Figure 2.5 for a 1 mF, 85 °C, 100 volt rated electrolytic capacitor.

Figure 2.5 Bode-plots of the electrolytic capacitor equivalent circuit impedance.

#### 2.5.4 Equivalent Series Resistance (ESR)

ESR leads to heat generation in the capacitor because of AC ripple current. The equivalent equation for ESR is shown in (2.3) [9].

$$ESR = R_1 + R_2 + R_3 (2.3)$$

where  $R_1$  = Frequency-sensitive resistance as a result of oxide thickness

$R_2$  = Temperature-sensitive resistance as a result of electrolyte

$R_3$  = Resistance because of the following components:

- Foil length

- Tabs

- Lead wires

- Ohmic contact resistance

The effect of the frequency-dependent part, R<sub>1</sub>, appears in the ripple current multipliers provided by manufactures [7]. This effect is caused by energy losses in the alignment of dipoles in the dielectric, and the time it takes for the dipoles to become oriented [8]. It becomes more significant for higher rated voltage capacitors because their oxide layer is thicker. For applications with a single frequency ripple current, the ESR can be simply adjusted by using a multiplier [2]. The amount of heat generated by the ripple current depends upon the ESR of the capacitor [13]. To have a low ESR, it is necessary to control the characteristics of the electrolyte, the separator paper, the winding alignment of the element, the position of the tabs, and the magnification and pit construction of the etched foil. All these factors contribute to the ESR of the capacitor [13-16]. The parallel combination of DCR and C models the dielectric oxide layer of the

capacitor, as shown in Figure 2.2. Equation (2.4) describes the complex impedance of the capacitor in Figure 2.4.

$$Z_{cap} = \frac{1}{\frac{1}{DCR} + j2\pi fC} + R_2 + R_3 + j2\pi fESL$$

(2.4)

where  $Z_{cap}$ = complex impedance of the capacitor, and f = frequency (Hz).

The value of ESR can be calculated as, ESR = Real part of  $(Z_{cap})$

Real part of

$$(Z_{cap}) = \frac{DCR}{1 + (2\pi f)^2 C^2 DCR^2} + R_2 + R_3$$

(2.5)

$$ESR = R_1 + R_2 + R_3 = \frac{DCR}{1 + (2\pi f)^2 C^2 DCR^2} + R_2 + R_3$$

(2.6)

Hence, the frequency-dependent part of ESR can be written as

$$R_{1} = \frac{DCR}{1 + (2\pi f)^{2} C^{2} DCR^{2}}$$

(2.7)

## 2.5.5 Operating temperature range [2]

The operating-temperature-range is the temperature-range over which the component will function, when energized, within the limits given in the specification. Capacitors are designed to operate over a range of ambient temperatures; moreover, the formation-voltage sets the high-temperature limit. Higher formation-voltages permit operation at higher operating temperatures but reduce the capacitance. The low-temperature limit is set largely by the cold resistivity of the electrolyte. A higher value of cold resistivity increases the capacitor's ESR 10 to 100 fold and reduces the available capacitance. Typical temperature ranges are: –20°C to +55°C, –25°C to 85°C, –40°C to 85°C, –40°C to 105°C, –55°C to 105°C, and –55°C to 125°C.

#### 2.5.6 Storage temperature range [2]

The storage temperature range is the temperature range to which the part can be subjected while un-energized while it retains conformance to specified electrical limits. It is the ambient temperature range over which the capacitors may be stored without damage for short periods. For longer period of storage, capacitors should be kept at cool room temperatures, and in an atmosphere free of halogen gases like chlorine and fluorine that can corrode the aluminum. Typical storage temperature ranges are from –55°C to the upper limit of the operating-temperature ranges.

#### 2.5.7 Rated DC voltage [2]

Rated DC voltage is the maximum peak voltage including ripple voltage that may be applied continuously between the terminals, and over the rated temperature range. Higher rated voltage capacitors may be substituted for lower rated voltage capacitors as long as case size, dispersion factor (DF), and ESR ratings are compatible [2].

### 2.5.8 Rated surge voltage [2]

Rated surge voltage is the maximum DC overvoltage to which the capacitor may be subjected at 25 °C for short periods not exceeding approximately 30 s at infrequent intervals of not less than 5 min. The surge voltage can be measured as follows: subject the capacitors to their rated surge voltage at normal room temperature and through a 1000  $\Omega$  ±10% resistor. Cycle the voltage 30 s on followed by 4.5 minutes off during which each capacitor is discharged through the charging resistor or equal resistor, and repeat the cycle for 120 h. Post-test requirements are for the DCL, ESR, and DF to meet the initial requirements, and for there to be no evidence of mechanical damage or electrolyte

leakage. In addition, the electrolyte residue with no droplets or visible flow is permitted [2].

#### 2.5.9 Transient over voltage [2]

Aluminum electrolytic capacitors can generally withstand extreme overvoltage transients of limited energy. An application of overvoltage more than about 50 V beyond the capacitor's surge voltage rating causes high leakage current, and a constant-voltage-operating mode similar to a zener diode operation. The capacitor may fail as a short-circuit if the electrolyte cannot take the voltage stress, but even if it can, this operating mode cannot be maintained for long because hydrogen gas is produced by the capacitor, and the pressure build up will cause the capacitor to rupture. However, special designs are available that use the overvoltage, zener-clamping-effect to successfully protect equipment from overvoltage transients such as lightning strikes.

#### **2.5.10 Ripple current [2]**

Ripple current is the AC current flowing in the capacitor. It is called ripple current because the associated AC voltage rides like ripple on water on the capacitor's DC bias voltage. The ripple current heats the capacitor, and the maximum permitted ripple current is set by the capacitor's load life specification. A significant temperature rise above the maximum permitted core temperature, will cause failure, even operation close to the maximum permitted core temperature dramatically shortens the expected life of the capacitor. The load life specifications for aluminum electrolytic capacitors operating at maximum permitted core temperature are typically 1000 to 10,000 hours. Ripple current ratings are specified for an expected temperature rise above the rated temperature.

Commonly, capacitor types rated at 85°C permit a temperature rise of 10°C, and have a maximum permitted core temperature of 95°C. However, types rated 105 °C permit a temperature rise of only 5°C, and have a maximum core temperature of 110 °C. Moreover, actual maximum permitted core temperatures may vary by type and manufacturer. Ripple current ratings usually assume that the capacitor is convection cooled and that the entire can is in contact with air. A convection coefficient of 0.006 W/°C/in<sup>2</sup> is used [2] to calculate the temperature rise from air to the case, and the core temperature is assumed to be same as the case temperature. The power dissipated is the ripple current squared times the ESR. Often the ESR value at 25°C, 120 Hz is used to calculate the power dissipated. With large-can capacitors, neglecting the temperature rise from the case to the core, can seriously overstate the ripple current capability. With some constructions, the core is 3 to 5°C per watt of ripple power hotter than the case. Therefore, the total temperature rise would be more than double the intended 10°C with rated ripple current and maximum ESR. However, generally it is safe to assume that the core temperature is the same as the case temperature for capacitors smaller than 25 mm in diameter [2].

# 2.6 Capacitor bank configuration [2]

#### 2.6.1 Parallel connection

Capacitors may be connected in parallel for increased capacitance and ripplecurrent capability. Parallel-connected capacitor banks have a minimum series inductance, and it requires a laminated bus or strip-line structure. Generally, one plane of the circuit board acts as the positive-connection and another plane as the negative-connection to all capacitors in the bus. The circuit resistance external to each capacitor should be equal to ensure equal current sharing. While the ripple-current divides among the capacitors in proportion to capacitance values for low-frequency ripple, and high frequency ripple-current divides in proportion to ESR values and the path resistance. In order to fuse the individual capacitors, a slow-start circuit should be included at equipment turn-on, and the fuse used for each capacitor should be rated at twice its expected, maximum ripple-current [10]. The slow start circuit can be a resistor in series with the capacitors that is shorted after initial charging.

#### 2.6.2 Series connection

Capacitors can be connected in series for increased voltage withstanding capability. During charging, the voltage across each of the capacitors connected in series is proportional to the inverse of the individual capacitance, but upon reaching the final voltage, the voltage across each capacitor is proportional to the inverse of the capacitor's leakage current. Of course, in a series-string, all leakage currents are the same, and the capacitors with a propensity for higher leakage current will get less voltage. Since leakage-current increases with applied voltage, a higher voltage results in higher leakage-resistance and the voltages tend to equalize. High voltage bus capacitors in series pairs connected to supply voltages 10% above twice the rated voltage have good voltage sharing over the full temperature range. Moreover, two capacitors in series will seldom require balancing resistors for voltage sharing. As an alternative, capacitors from the same manufacturing lot should be used to ensure equal leakage currents, or a higher rated voltage can be used to permit voltage imbalance with different manufacturers. In addition, capacitors in series should have the same thermal environment.

#### 2.6.3 Parallel-series connection

Capacitors connected as shown in Figure 2.6 with a common connection between multiple series combinations have the following considerations.

Figure 2.6 Parallel-series connection.

Advantages: As the number of capacitors in parallel increases, the total capacitance of the top group tends to equal the total capacitance of the bottom group even if individual capacitor values are not identical. This improves voltage balance during transients. In addition, the leakage current of the top group tends to equal the leakage current of the bottom group, so that voltage balance improves during steady-state conditions. Finally, only two balancing resistors are needed, and the top and bottom resistors are carefully matched so that it eliminates the need for any other balancing resistors.

Disadvantage: If one capacitor fails short, the other half of the bank gets the entire bus voltage, so other capacitors will fail as well. Therefore, one capacitor failure can cause failure of the entire bank unless the shorted capacitor is blown open.

#### 2.6.4 Series-parallel connection

Capacitors connected as shown in Figure 2.7 with multiple series combinations in parallel have the followings considerations. This configuration is the clear choice when balancing resistors are not used.

Figure 2.7 Series-parallel connection.

Advantages: If one capacitor fails short then the capacitor in series with it also fails, but other capacitors in the bank are unaffected. If balancing resistors are not used, then a high leakage current of one capacitor affects only a single pair of capacitors. The independent, series pairs permit fusing.

Disadvantages: With balancing resistors, the construction is more complex; many resistors need to be fitted, and the cost increases.

#### 2.6.5 Non-polarized connection

If two, same-value, aluminum electrolytic capacitors are connected in series, back-to-back with the positive terminals or the negative terminals connected, then the resulting combined equivalent single capacitor is a non-polarized capacitor with half the capacitance to either of the original pair. Each capacitor individually rectifies the applied

voltage, and act as if they had been bypassed by diodes. When voltage is applied, the correct-polarity capacitor gets the full voltage. In non-polarized aluminum electrolytic capacitors and motor start aluminum electrolytic capacitors, a second anode foil substitutes for the cathode foil to achieve a non-polarized capacitor in a single can. While non-polar aluminum electrolytic capacitors are available for momentary-duty AC applications like motor starting and voltage-reversing applications, the high dispersion factor (DF) of aluminum electrolytic capacitors, from 2% to 150%, causes excess heating and a short life in most AC applications.

## 2.7 Cooling strategies [2]

Capacitors conduct heat from the core to the bottom of the can more effectively than outwards to the sides. Advantage can be taken of this heat path can be taken by mounting the bottom of the capacitor cans directly to a metal chassis. In many can sizes, this method of mounting doubles the permitted ripple-current for the same temperature rise. Mounting can be done by using capacitors with special mounting studs and screwing the studs directly into the chassis plate, or it can be done by pressing the capacitors against a plate using the interconnecting bus structures. The seal pads create smooth bottoms by eliminating the steps at the sleeve rollovers [11]. The thermal resistance between the can and the chassis plate for capacitors merely sitting on the plate is about  $2.5^{\circ}$ C/W. This decreases to less than  $1^{\circ}$ C/W if the capacitors are pressed into place. In large-can capacitors, especially ones with potting, there is a significant temperature rise from the case to the core, and the center of the capacitor is the hottest spot. As an illustration, 20 amps of ripple-current at 120 Hz with a maximum ESR of 20 m $\Omega$ , dissipates 4 W of power. Consider, a total thermal resistance of  $3.07^{\circ}$ C/W for air on all

sides and 1.02°C/W for the capacitor can pressed against a large metal plate, or chassis. With 4 W, the 3.07°C/W thermal resistance results in a temperature rise of 12.3°C, and the 1.02°C/W results in a 4.1°C rise. The 1.02°C/W assumes that there is no temperature rise in the metal plate.

### **2.8 Shelf life [2]**

Aluminum electrolytic capacitors stored for more than 5 to 10 years may have increased levels of DC leakage current. Leakage current should be measured before use to check whether it meets application requirements before placing in the service. High leakage current units should be reconditioned by applying rated voltage through 1,000  $\Omega$  resistor for 30 minutes. Shelf life is a measure of how the capacitors will withstand storage for longer durations of time, especially at high temperature.

## 2.9 Process considerations [2]

## 2.9.1 Soldering

Strict soldering conditions such as temperature, duration, and minimum distance of solder from body should be considered for the protection of the capacitor. Contact with the insulating sleeve or other plastic parts with a soldering iron or molten solder should be avoided. In addition, any mechanical force like bending, straightening, twisting, or tilting of capacitors after soldering them into a printed circuit board, should be avoided.

#### 2.9.2 Mounting

At lower ambient temperatures aluminum electrolytic capacitors have longer operating lives, therefore, the capacitors should therefore be installed at the coolest place

on the circuit board. Aluminum electrolytic capacitors should be kept away from hot components like power resistors, power transistors, diodes, and transformers. Adequate space should be used to place the components for cooling air to circulate. This is especially important when high ripple current or charge/discharge loads are applied. In addition, aluminum electrolytic capacitors are normally polarized, and care should be taken to connect them with correct-polarity during installation in the circuitry. Adequate clearance should be provided for proper operation of the pressure-relief devise. The capacitors should be mounted such that the vent is at the top, or at least in the upper part of the capacitor. This assures that the least amount of the electrolyte will be expelled if the vent operates. Capacitors that include thermal-plastic potting should be mounted such that the potting cannot block the vent, should the potting melt during the capacitor failure.

## 2.10 Disposal of electrolytic capacitors [2]

Aluminum electrolytic capacitors with non-solid electrolyte principally include high-purity aluminum foils, capacitor paper, electrolyte, aluminum case, cover and sealing parts (phenolic, thermoplastic, rubber and phenolic board), insulating sleeve (polypropylene, polyester or polyvinylchloride) and, perhaps, safety-vent plugs made of synthetic rubber [12]. It should be incinerated above 1200 °C, and residue can be disposed in appropriate landfills.

# 2.11 Comparison to other types of capacitors [2]

### 2.11.1 Ceramic capacitors

Ceramic capacitors have become the preeminent, general-purpose non-polarized capacitor, especially in surface mount technology (SMT) chip devices where their low

cost makes them especially attractive [2]. With the emergence of thinner dielectric, multilayer units with rated voltages of less than 10 V, capacitance values in the hundreds of microfarads have become available. This intrudes on the traditional, high-capacitance province of aluminum electrolytic capacitors. Ceramic capacitors are available in three classes according to dielectric constant and temperature performance. Class 1 (NPO, COG) is suitable for low capacitance, tight tolerance applications in the range of 1 pF to a few mF. Class 2 (X7R) has 20 to 70 times as much capacitance per case size, but the capacitance typically varies about ±10 % over its –55 to 125°C temperature range, with a maximum change of +15 % to –25 %. Class 3 (Z5U) with about 5 times the capacitance of Class 2 has large variations of capacitance with voltage and temperature. The temperature range is –25°C to 85°C, and capacitance varies by about +20 % to –65 % over this range [2].

Ceramic capacitors are brittle and sensitive to thermal shock, so precautions need to be taken to avoid cracking during mounting, especially for high-capacitance large sizes. The typical temperature range for ceramic capacitors is –40°C to 85°C or 105°C, and their capacitance varies about +5 % to –40 % over this range, with a reduction in capacitance at cold temperatures. For example, capacitors rated at –55°C generally only have –10 % to –20 % capacitance losses at –40°C. Cold temperature performance for rated voltages of 300 V and higher is often worse, and temperature performance varies by manufacturer. Thus, Class 1 and 2 ceramic capacitors perform better than electrolytic capacitors at cold temperatures, and Class 3 ceramic capacitors perform worse at all temperatures [2].

Electrolytic capacitors give more capacitance and energy storage per unit volume than ceramic capacitors for all types except for low-voltage, Class 3 ceramic SMT chip type capacitors. While tolerances of  $\pm 5\%$  and  $\pm 10\%$  are routine for ceramic capacitors,  $\pm 20\%$ , and -10% to +50% are the norms for electrolytic capacitors. This makes electrolytic capacitors the choice for high capacitance applications like rectification filters and power hold up where more capacitance is a bonus and accuracy is not important. The low DF and high capacitance stability of Class 1 and 2 are ceramic capacitors especially suited to AC and RF applications. By comparison, electrolytic capacitors are polarized, and cannot withstand reverse voltages in excess of about 1.5 V. However, non-polar electrolytic capacitors are available for momentary duty AC applications like motor starting and voltage-reversing applications. High DF of electrolytic capacitors, from 2% to 150%, causes excess heating and short life in most AC applications. Ceramic capacitors are generally no more reliable than electrolytic capacitors because electrolytic capacitors have self-healing properties. Since high capacitance ceramic capacitors may develop micro-cracks, electrolytic capacitors are preferred for high capacitance values. However, small sizes of electrolytic capacitors may have limited life due to dry-out, and reliability becomes an issue when operating at high ambient temperatures, over 65 °C.

#### 2.11.2 Film capacitors [2]

Film capacitors offer tight capacitance tolerances, low leakage currents, and small capacitance changes with temperature. They are especially suited to AC applications through their combination of high capacitance, and low DF that permits high AC currents. However, they are relatively large in size and weight. The popular polymers used for plastic-film dielectric capacitors are polyester and polypropylene. The popular

polymer for SMT devices is polyphenylene sulfide (PPS). While film/foil construction is often used for small capacitance values less than 0.01 µF, and for high-current applications, the metallized-film types on the hand are usually preferred because they have smaller size, lower cost, and are self-healing. Film capacitors are general-purpose capacitors for through-hole applications and have special uses for tight-tolerance, AC voltage, high voltage, and snubbing. Polyester film capacitors operate from at -55°C to 85°C at rated voltage; in addition, +85°C to 125°C with linear voltage derating to 50 % of rated voltage. The typical capacitance change over the entire range is less than -5 % to +15%, and as low as  $\pm 1\%$  from 0°C to 50°C. Capacitance values are readily available up to 10 μF, and with special large sections up to 100 μF. Generally, available voltages are 50 to 1000 Vdc and 35 to 600 Vac. AC current handling is limited by polyester's high temperature DF of about 1%. Polypropylene film capacitors operate from -55°C to 85°C at rated voltage; in addition, 85°C to 105°C with linear voltage derating to 50 % of rated voltage. The typical capacitance change over the entire range is less than +2% to -4%with as low as  $\pm 1\%$  from -20°C to 60°C. Capacitance values are readily available up to 65 μF, and with special large sections up to 1000 μF. Generally, available voltages are 100 to 3000 Vdc and 70 to 500 Vac. AC current handling permits use in motor-run and other continuous duty AC applications. Compared to aluminum electrolytic capacitors, film capacitors take the lead in high voltage, AC voltage, and tight tolerance applications. However, aluminum electrolytic capacitors excel in capacitance and energy storage.

### 2.11.3 Solid tantalum capacitors [2]

Like aluminum electrolytic capacitors, solid tantalum capacitors are polarized devices (1 V maximum reverse voltage), having distinct positive and negative terminals,

and are offered in a variety of styles. Case styles include both molded and conformalcoated versions of radial, axial, and surface mount configurations. Typical capacitance values are from 0.1 μF to 1000 μF in voltage ratings from 2 V to 50 V. Typical maximum capacitance-voltage combinations are approximately 22 µF at 50 V for leaded styles, and 22 μF at 35 V for surface mount. Advantages of solid tantalum capacitors are temperature stability, volumetric efficiency, and compatibility with all automated assembly systems. However, weaknesses are the limited voltage and capacitance ranges, and a short-circuit failure mode accompanied by catching fire. The operating temperature range is -55°C to 85°C at rated voltage; in addition, +85°C to 125°C with linear voltage derating to 2/3 of rated voltage. The typical capacitance change over the entire range is less than  $\pm 5\%$ . Thus, electrolytic capacitors have a much broader voltage and capacitance ranges than solid tantalum capacitors but perform worse at cold temperatures. Solid tantalum capacitors are generally considered more reliable than electrolytic capacitors because solid tantalum capacitors do not wear out. Their failure rate decreases with time, while electrolytic capacitors wear out by drying-out of the electrolyte. As a practical matter, dry-out only affects the smallest capacitors operating in high-temperature environments. Larger electrolytic capacitors do not dry-out fast if operated in their specified conditions, and these are expected to last for 10 to 20 years for most applications. In addition, the open-circuit, dry-out failure in the electrolytic capacitors is benign compared to solidtantalum's short circuit failure mode.

# 2.12 Failure modes [2]

Failure modes of electrolytic capacitors can be classified as follows, Figure 2.8 [2].

Figure 2.8 Failure mode chart.

In catastrophic failure, the function of the capacitor is completely lost; therefore, it is easily detected as a failure. In degradation failure, the characteristics such as, ESR, capacitance,  $\tan\delta$ , and leakage resistance, gradually deteriorate to the stage at which it is judged as a failure. However, the point of failure will vary greatly with the performance required by the power electronics system in which it is used.

#### 2.12.1 Air-tightness failure of the vent (gas generation) [2]

Aluminum electrolytic capacitors have characteristics, which quickly repair film defects by the mechanism shown in Figure 2.9 and equation (2.8). Oxidation at the anode will cause reduction at the cathode, resulting in the generation of hydrogen gas (H<sub>2</sub>). However, when used under a condition within the guaranteed ranges noted in the manufacturers' catalog or delivery specifications, the generated hydrogen gas is extremely small, and any generated such gas is dissipated by the depolarization action of the electrolyte or through the sealing element, so there is no problem. However, if used under extreme conditions, such as high temperature, over voltage, reverse voltage, and excess ripple-current, exceeding the guaranteed ranges, damage to the dielectric film will increase, causing a sudden increase in hydrogen gas generated by the self-repairing

action. This will cause the internal pressure to rise rapidly, which leads to opening of the pressure-vent, or rupture of the capacitor can.

Figure 2.9 Chemical characteristics of an electrolytic capacitor.

$$2Al \to 2Al^{3+} + 6e^{-}$$

(2.8 a)

$$3H_2O \rightarrow 6H^+ + 3O^{2-}$$

(2.8 b)

$$2Al^{3+} + 3O^{2-} \rightarrow Al_2O_3$$

(2.8 c)

$$6H^+ + 6e^- \rightarrow 3H_2 \uparrow \tag{2.8 d}$$

#### 2.12.2 Open failure

Open failure can occur because of any of the following reasons [2]:

- mechanical damage to the lead connection,

- corrosion because of the infiltration of a corrosive material,

- evaporation of the electrolyte because of opening of the vent,

- final stage of gradual deterioration.

The first one occurs because of improper connection at the time of production or the lead being subjected to excessive stress, vibration, or impact. The second one occurs when halogenated ions (*Cl*) enter during production, or the capacitor is cleaned with a halogenated cleaner, or is reinforced with a resin containing halogenated compounds and halogenated substances enter the capacitor. These corrode the leads or electrode foils

until an open condition results. Third occurs when the internal electrolyte evaporates thereby causing the capacitor to dry-up. This reduces the capacitance and increases the  $\tan\delta$  of the capacitor. The fourth reason occurs at the end of the life of the capacitor through the process of deterioration, i.e. the final stages of degradation failure in which the electrolyte gradually penetrates through the seal causing the capacitance to drop, and  $\tan\delta$  to increase.

#### 2.12.3 Short circuit

A good electrolyte quickly repairs any defect in the oxide film damage at the electrodes [2]. However, a significant amount of damage in oxide film causes local concentrations of current, and this leads to catastrophic failure, such as short circuits of the capacitor electrodes. In addition, defects such as metal or other conductive particles on electrode foils during production can provide conducting paths for the current, resulting in a short circuit of the electrodes. Moreover, mechanical stress of the capacitor leads may also lead to short-circuiting of the capacitor electrodes.

#### 2.12.4 Degradation failure

The capacitor parameters change (capacitance decreases and ESR increases) because of emission of electrolyte from sealing surface. However, the assessment of degradation depends on the type of applications, which is further explained in detail in Chapter 3.

#### 2.12.5 Failures of capacitor periphery

Electrolyte leaking from aluminum electrolytic capacitors may influence areas around their periphery on a PCB (especially, wiring pattern), in the following two ways:

- Disconnected pattern: The electrolyte corrodes the metal traces on the PCB board,

and leads to a disconnected pattern of traces on the PCB.

- Shorted pattern: Emitted electrolyte ions from the capacitor seal may migrate between two traces under the influence of the electric field, and lead to a short circuit between traces.

A detailed chart of different failure modes of an aluminum electrolytic capacitor is shown in Figure 2.10 [7].

Figure 2.10 Failure modes of an electrolytic capacitor [7].

# 2.13 Need of condition monitoring for electrolytic capacitor

Condition monitoring is defined as the continuous evaluation of the health of the plant and equipment throughout its service life. It is important to be able to detect faults while they are still developing, called incipient failure detection. A timely warning that

can be followed by maintenance can avoid catastrophic failures and costly down times, and can provide a safe environment for human operators [18-31].

An aluminum electrolytic capacitor is often utilized to smooth the output of a switching regulator, DC bus filtering in motor drives, and in many other applications. These capacitors are generally thought to be the weak link in the life expectancy of the system, as shown in Figure 2.11 [1].

Figure 2.11 Distribution of failure for various power components [1].

Figure 2.11 displays the failure distribution of different components in a static converter. In 60% of the failures, electrolytic capacitors are responsible for the failure of the static converter. This shows that by monitoring the condition of the electrolytic capacitor can drastically improve the reliability of the static converter.

# 2.14 Reliability and fault detection

With the advancements in aluminum electrolytic capacitor technology, capacitors can be used in equipment that must have long life or must operate under severe conditions. For example, the capacitors used in telecommunication applications have an expected life of more than 20 years [6]. On the other side, aluminum electrolytic

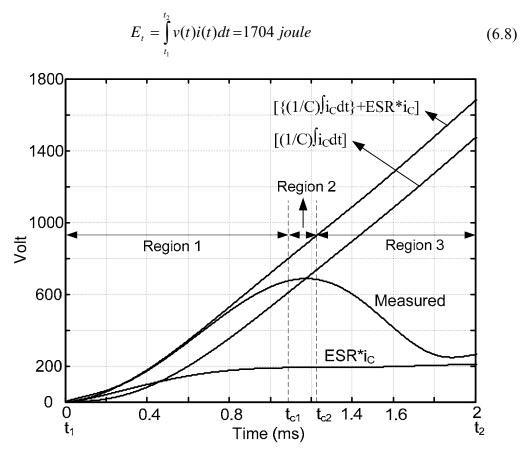

capacitors have run continuously at ~130 °C for more than one year. The careful selection of a capacitor for a particular application and proper installation in the circuit will assure good service life. All components will eventually fail. Usually this occurs by a slow, steady drift of parameters called wear-out. Sometimes there is a sharp change in capacitor properties, which is called a catastrophic failure. The failure rate of aluminum electrolytic capacitors follows a bathtub curve with time, as shown in Figure 2.12 [6].