TECHNISCHE UNIVERSITÄT MÜNCHEN

Lehrstuhl für Entwurfsautomatisierung

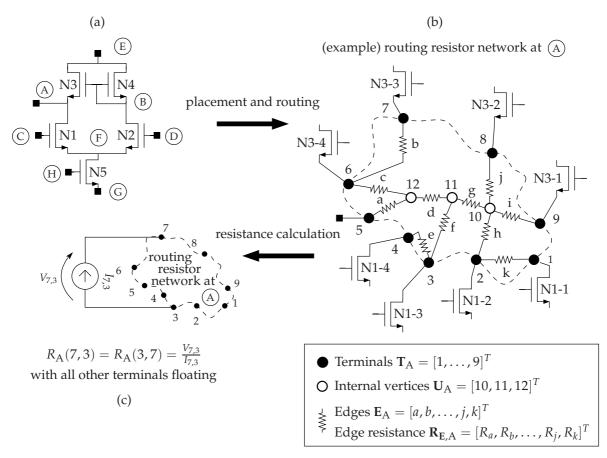

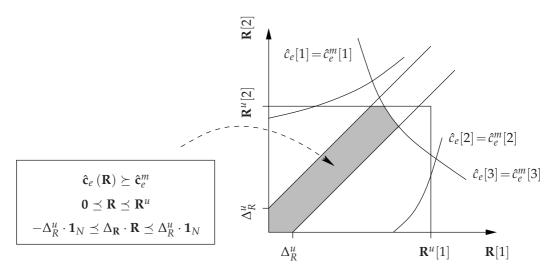

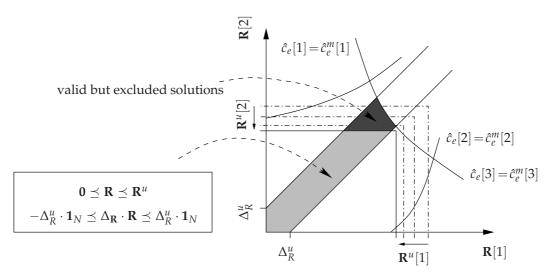

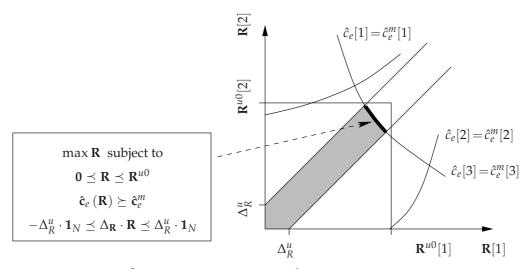

# Constraint-Based Layout-Driven Sizing of Analog Circuits

### Husni Habal

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

| UnivProf. DrIng. Martin Buss (Univ. Tokio)                      |

|-----------------------------------------------------------------|

| PrivDoz. DrIng. Helmut Gräb                                     |

| Prof. Dr. ir. Georges Gielen,<br>Katholieke Universiteit Leuven |

|                                                                 |

Heverlee/Belgien

Die Dissertation wurde am 04.04.2012 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 05.02.2013 angenommen.

"Compassion is the basis of morality." -Arthur Schopenhauer

#### Acknowledgments

This work is the culmination of four years of research activity at the Institute for Electronic Design Automation at TU München. Firstly, I want to acknowledge Dr. Helmut Gräb for his guidance and supervision without which this dissertation would not be possible. I thank Prof. Ulf Schlichtmann for his confidence and for giving me the opportunity to pursue research work at his institute. I thank my colleagues Dr. Daniel Müller-Gritschneder, Dr. Martin Strasser, Dr. Michael Pehl, Anja Boos, and Michael Eick with whom I worked closely. My friend Patrick Birrer receives special gratitude for his help and support. Ultimately, I would like to thank my parents for their love and support throughout my life.

# Contents

| 1 | Intro | oduction                                                        | 1  |

|---|-------|-----------------------------------------------------------------|----|

|   | 1.1   | Analog Integrated Circuit Design                                | 2  |

|   |       | 1.1.1 Basic Analog Design Flow                                  | 2  |

|   |       | 1.1.2 Circuit Performances, Specifications, and Constraints     | 2  |

|   |       | 1.1.3 Process Parameters, Operating Conditions, and Reliability | 4  |

|   |       | 1.1.4 Hierarchical Top-Down Design and Abstraction              | 4  |

|   |       | 1.1.5 Analog Circuit Design Automation                          | 5  |

|   | 1.2   | Motivation                                                      | 6  |

|   |       | 1.2.1 Backtracking in the Analog Design Flow                    | 6  |

|   |       | 1.2.2 Layout-Driven Circuit Sizing                              | 7  |

|   | 1.3   | State of the Art                                                | 9  |

|   | 1.4   | Contributions of this Thesis                                    | 11 |

|   | 1.5   | Related Publication                                             | 12 |

|   | 1.6   | Organization of this Thesis                                     | 12 |

| 2 | For   | mulation of the Circuit Sizing Problem                          | 13 |

|   | 2.1   | Basic Definitions                                               | 13 |

|   |       | 2.1.1 Electrical Circuit Topology                               | 13 |

|   |       | 2.1.2 Electrical Test Bench Topology                            | 14 |

|   |       | 2.1.3 Circuit Parameters                                        | 14 |

|   |       | 2.1.4 Circuit Performances                                      | 17 |

|   |       | 2.1.5 Circuit Sizing Rules                                      | 18 |

|   |       | 2.1.6 The Feasible Design Space and Performance Space           | 20 |

|   | 2.2   | Circuit Problem Formulation                                     | 21 |

|   |       | 2.2.1 Feasibility Analysis                                      | 21 |

|   |       | 2.2.2 Circuit Sizing to Meet Performance Specifications         | 21 |

| 3 | Ove   | erview of Layout Synthesis Steps                                | 23 |

|   | 3.1   | Introduction                                                    | 23 |

|   | 3.2   | Layout of Individual Physical Devices                           | 24 |

|   |       | 3.2.1 Device Layout Automation                                  | 24 |

|   | 3.3   | Device Placement                                                | 25 |

|   |       | 3.3.1 Circuit Placement Automation                              | 26 |

|   | 3.4   | Routing                                                         | 27 |

|   |       | 3.4.1 Circuit Routing Automation                                | 28 |

|   | 3.5   | Post-Layout Electrical Model Extraction                         | 28 |

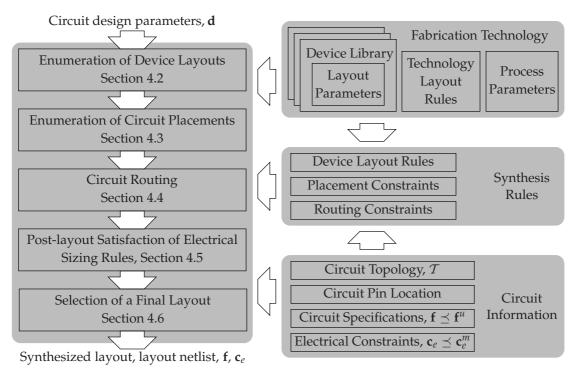

| 4 | New  | Autor   | matic Constraint-Based Layout Synthesis Flow                                          | 31  |

|---|------|---------|---------------------------------------------------------------------------------------|-----|

|   | 4.1  |         | luction                                                                               | 31  |

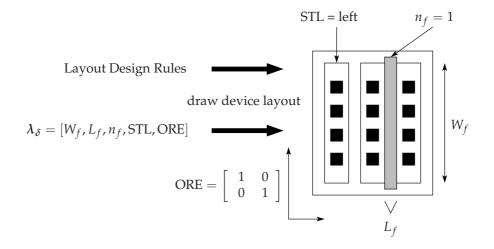

|   | 4.2  | Enum    | neration of Device Layouts                                                            | 32  |

|   |      | 4.2.1   | Constrained Enumeration of CMOS Device Layouts                                        | 36  |

|   |      | 4.2.2   | Constrained Enumeration of CMOS Devices in Common Cen-                                |     |

|   |      |         | troid Layout                                                                          | 40  |

|   | 4.3  | Enum    | neration of Circuit Placements                                                        | 45  |

|   |      | 4.3.1   | Placement Constraint Generation                                                       | 45  |

|   |      | 4.3.2   | Minimum Device Margins                                                                | 46  |

|   |      | 4.3.3   | Generation of Pareto-Optimal Placements                                               | 46  |

|   |      | 4.3.4   | Geometric Placement Specifications                                                    | 47  |

|   |      | 4.3.5   | Ordering and Curtailing of Circuit Placements                                         | 51  |

|   | 4.4  | Circui  | it Routing                                                                            | 52  |

|   |      | 4.4.1   | Pin Assignment                                                                        | 53  |

|   |      | 4.4.2   | Congestion Control                                                                    | 55  |

|   | 4.5  | Post-I  | Layout Satisfaction of Electrical Sizing Rules by Limiting Routing                    |     |

|   |      | Resist  | tance                                                                                 | 57  |

|   |      | 4.5.1   | Post-Layout Electrical Sizing Rules                                                   | 57  |

|   |      | 4.5.2   | Routing Limits to Satisfy Post-Layout Electrical Constraints                          | 60  |

|   |      | 4.5.3   | Maximization of $\mathbf{R}^{u}$ in the Feasible Effective Resistance Space $\cdot$ . | 70  |

|   |      | 4.5.4   | Acyclic Routing Network Graphs of Maximum Edge Number .                               | 72  |

|   |      | 4.5.5   | Numerical Solution to (4.86) by Successive Linear Programming                         | 76  |

|   | 4.6  | Select  | ion of a Final Layout                                                                 | 77  |

|   |      | 4.6.1   | Post-Layout Circuit Extraction                                                        | 78  |

|   |      | 4.6.2   | Scalar Cost Metric Of Performance Specifications                                      | 78  |

|   | 4.7  | Sumn    | nary                                                                                  | 80  |

| 5 | Lavo | out-Dri | iven Circuit Sizing                                                                   | 81  |

| • | 5.1  |         | luction                                                                               | 81  |

|   | 5.2  |         | w of the Search Algorithm Employed in Circuit Sizing                                  | 81  |

|   | 5.3  |         | ical Description of the Layout-Driven Circuit Sizing Problem                          | 85  |

|   | 5.4  |         | s in Numerical Function Evaluation                                                    | 89  |

|   | 5.5  |         | netric Inequality Constraint Functions                                                | 91  |

|   | 5.6  |         | ical Performances and Constraints Without Layout Synthesis                            | 91  |

|   |      | 5.6.1   | Truncation Error                                                                      | 91  |

|   |      | 5.6.2   | Computational Error                                                                   | 92  |

|   |      | 5.6.3   | Adjustments to Palliate Truncation and Computational Error .                          | 93  |

|   | 5.7  |         | rmances with Layout-Driven Circuit Sizing                                             | 95  |

|   |      | 5.7.1   | Discretization Error                                                                  | 95  |

|   |      | 5.7.2   | Placement Dependency                                                                  | 97  |

|   |      | 5.7.3   | Solution Selection in the Design Space Under Consideration of                         |     |

|   |      |         | Discretization and Placement Error                                                    | 99  |

|   |      | 5.7.4   | Partial Derivative Calculation Under Consideration of Dis-                            |     |

|   |      |         | cretization and Placement Error                                                       | 102 |

|    | 5.8<br>5.9                                                                                   | On the Cost of Circuit Sizing                                                                                                                                                                                                                          |                          |  |  |

|----|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|

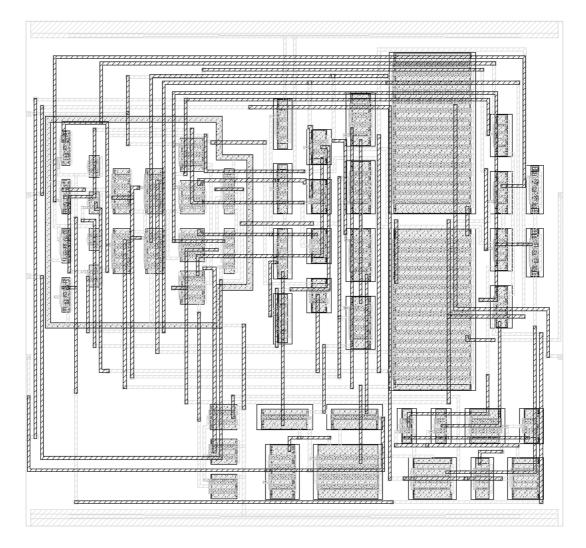

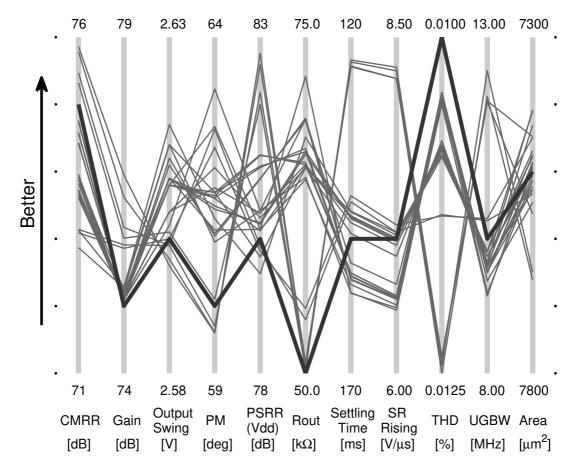

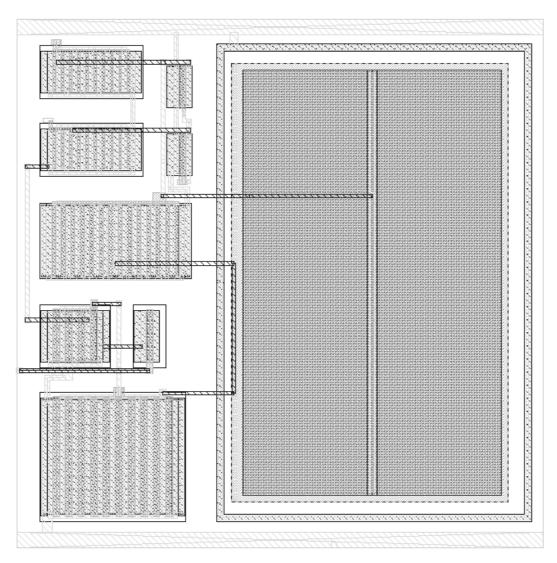

| 6  | <b>Circ</b><br>6.1                                                                           | Examples         Description of the Example Circuits         6.1.1       Folded Cascode Operational Amplifier (FC-OA)         6.1.2       Tunable Operational Transconductance Amplifier (TOTA)         6.1.3       Miller Operational Amplifier (MOA) | 111<br>114               |  |  |

|    | 6.2                                                                                          | <ul> <li>Experimental Setup</li></ul>                                                                                                                                                                                                                  | 123<br>124               |  |  |

|    | 6.3                                                                                          | <ul> <li>Circuit Sizing Results and Comparison</li></ul>                                                                                                                                                                                               | 125<br>125<br>130<br>134 |  |  |

| 7  | 6.4<br><b>Con</b>                                                                            | Summary                                                                                                                                                                                                                                                | 139<br><b>141</b>        |  |  |

| Α  | Area                                                                                         | a Estimation Without Layout Synthesis                                                                                                                                                                                                                  | 143                      |  |  |

| В  | Арр                                                                                          | proximation to the Gradient of the Area Estimate                                                                                                                                                                                                       | 147                      |  |  |

| Bi | bliog                                                                                        | raphy                                                                                                                                                                                                                                                  | 149                      |  |  |

| No | omen                                                                                         | clature                                                                                                                                                                                                                                                | 163                      |  |  |

| Li | Lists         165           List of Figures         165           List of Tables         167 |                                                                                                                                                                                                                                                        |                          |  |  |

| Ak | ostra                                                                                        | ct in German                                                                                                                                                                                                                                           | 169                      |  |  |

# **Chapter 1**

# Introduction

The market for commodity integrated circuit (IC) solutions is dominated by complementary metal-oxide-semiconductor (CMOS) fabrication technology. This is due to the low static power, high device density, and cheap manufacturing cost of CMOS chips. Analog circuits, such as analog-to-digital (A/D) converters, radio frequency (RF) front end interfaces, and frequency synthesizers are often implemented as components of a mixed-signal CMOS IC that is dominated by a large digital core, such as a microcontroller or digital signal processor (DSP) [KCJ<sup>+</sup>00]. The evolution of CMOS mixed-signal fabrication technology is focused on improving the specifications of the digital core, including higher gate and memory densities, lower power consumption, and a longer mean time to failure (MTTF). In order to improve the latter specifications, CMOS devices have been scaled down to deep sub-micron dimensions and are designed to operate at a low supply voltage [ANvLT05].

This course of technology progression has imposed many challenges on the analog designer. The designer must account for complex nonlinear device models, low threshold voltages, large process parameter variations, channel length modulation caused by short device length, and gate leakage when designing a circuit to meet a set of performance specifications, such as minimum gain and maximum power.

To aid the analog designer, research in analog electrical design automation (EDA) has focused on two tasks. The first task is to add more layers of hierarchy and abstraction in the design flow, while the second is to find means of automation in each design step, such as the dimensioning of components and layout synthesis.

High level programming languages and modeling tools are often used at the first stage of analog design, as they are fast and easy to set up [Mata]. Commercial toolboxes are available for some applications [Matb]. At a lower level, a hardware description language (HDL), such as Verilog-A [VLR] or VHDL-AMS [DV03], is used to create behavioral models of analog circuits. Tools for the automatic dimensioning of circuit components are available [AEG<sup>+</sup>00a, Cad03b], as are tools for automatic analog placement and routing [SEG<sup>+</sup>08, Cad03a]. These tools, however, still lag behind their digital counterparts – offering many opportunities for original research.

# **1.1 Analog Integrated Circuit Design**

## 1.1.1 Basic Analog Design Flow

The design flow of an analog circuit at the device (transistor) level of detail consists of four standard and consecutive steps:

- 1. *Circuit topology selection*: A circuit topology, also referred to as a circuit structure, is a network of electrical devices; each device has at least two terminals and a behavioral model for analytical or numerical simulation. A circuit structure is selected that has the potential to fulfill the specified functional purpose of the circuit.

- 2. *Circuit sizing*: Constituent in each behavioral device model is one or more device design parameters, for example, in the CMOS device model, the drain to source current is a function of channel width and length. During circuit sizing values are assigned to the design parameters of each device in the circuit topology. Design parameter values are selected so that the circuit operates with the desired functionality.

- 3. *Circuit layout synthesis*: A circuit layout is the blueprint of planar geometric shapes used to create photo masks for the physical realization of the circuit in a specific fabrication technology using the technique of photo lithography. During layout synthesis, the geometric shapes representing sized topology devices are drawn on an IC floor plan. The network connections between devices are also drawn according to the circuit topology.

- 4. *Post-layout circuit extraction and electrical verification*: A new network of electrical devices is generated based on the circuit layout. This new network is a closer approximation to the physical circuit than the sized circuit topology. It is used to verify that the circuit still has the desired functionality after layout synthesis.

### 1.1.2 Circuit Performances, Specifications, and Constraints

A circuit performance is a descriptive quantity of circuit behavior deemed of value by the analog designer. It is useful to divide circuit performances into geometric and electrical categories. Electrical performances are selected based on the intended function of the analog circuit, for example, operational amplifier, low noise amplifier, or mixer. Geometric performances describe the spacial properties of the circuit, such as the area and aspect ratio of the circuit after layout.

A circuit specification is a functional equation or inequality of circuit performances. When the circuit specification is true, the circuit is said to exhibit the proper behavior. In practice most specifications take the form of an upper or lower bound on the value of a circuit performance. Circuit specifications alone may not be sufficient to describe the behavior of an analog circuit [MCR00, MGS08]. Additional designer knowledge about the circuit topology can be translated into functional equations or inequalities of the circuit topology node voltages and branch currents, hereafter called electrical constraints, and functional equations or inequalities of the design parameters, hereafter called geometric constraints.

The circuit topology is electrically controllable through a subset of its network nodes, which are defined as *external nodes*. In order to calculate the electrical performances, specifications, and constraints, one or more test bench circuits are constructed by the analog designer and connected to the external circuit nodes. Test bench circuits are electrical networks that establish the electrical operating conditions under which the circuit is expected to operate. These include the voltage and current stimulus, the correct loading at each external node, and the correct external feedback paths between the external nodes.

Electrical performances and specifications are typically calculated as an expression or sequence of expressions from the voltages at and currents through the external topology nodes. The test bench setup for the measurement of electrical performances and specifications is normally independent of the circuit topology and depends only on the electrical signals at the external circuit nodes. In contrast, electrical constraints are often calculated from internal topology node voltages and branch currents. They are topology dependent and must be redefined for a change in the topology.

The circuit and test bench form a mathematical model of a closed electrical system. A numerical circuit simulator is used to study the behavior of this system, such as SPICE [Nag75], Spectre [Kun95a], or Titan [Inf08]. Numerical simulation requires detailed mathematical device models such as BSIM [SSKJ87] and EKV [EKV95].

The type of analysis method that is used in simulation is dependent on the type of stimulus sources present in the test bench network and the type of response that is to observed. The analysis methods typically used for analog circuits include the following:

- DC analysis, or circuit quiescent (bias) point calculation.

- AC analysis, or linear small signal frequency domain circuit analysis.

- Transient simulation, or the time domain large-signal solution of differential algebraic circuit equations.

- Harmonic balance to calculate the steady-state response of an electrical circuit without the need for a transient simulation.

- Periodic steady state (PSS) simulation and Periodic small-signal analysis [YP02]. PSS directly computes the periodic steady-state response of a circuit without transient analysis.

## 1.1.3 Process Parameters, Operating Conditions, and Reliability

In addition to design parameters, several process parameters constitute terms in a device model. As the name implies, the value of the process parameters depends on the semiconductor fabrication technology used to realize the IC [LJX<sup>+</sup>]. Due to the imperfections of sub-wavelength lithography, random dopant fluctuations, and line edge roughness during the IC fabrication procedure, process parameters are often not constant in value after manufacturing the IC. Process parameters values may change systematically or stochastically between silicon wafers, between dies on the same wafer, or between devices on a single die [AN07, BMR07, LBSG07, LDH<sup>+</sup>08]. The general trend in CMOS semiconductor fabrication technology is that the coefficient of variation of the process parameters increases with every new technology generation and reduction in device scale [tec09]. Variable process parameters increase the complexity of analog circuit design, as appropriate layout techniques, production yield levels, and margins of error in specifications and constraints must be considered in the design flow [Has01, AEG<sup>+</sup>00a, CLW10, GMGS09, YL08].

Circuit behavior is also dependent upon the operational conditions external to the circuit topology. Circuit stimulus, loading, and feedback conditions, as imposed by the test bench circuit, influence the circuit through electrical signals at the external circuit nodes. For example, the value of the DC supply voltage and the load impedance are set in the test bench circuit. In addition, environmental parameters, such as temperature, are normally considered within device models. These operating conditions are typically represented by a set of operational parameters; their value is typically not constant, but fluctuates over a range that needs to be taken into account during circuit design.

Reliability is defined as the ability of a circuit to conform to its specifications over a specified period of time under specific conditions [GDWM<sup>+</sup>08]. The effects of electromigration (EM), time-dependent-dielectric-breakdown (TDDB) and hot carrier degradation (HCI and NBTI) significantly affect circuit reliability in deep sub-micron CMOS fabrication technologies and must be taken into consideration during analog circuit design [WVN<sup>+</sup>06].

### 1.1.4 Hierarchical Top-Down Design and Abstraction

A large analog system, such as a frequency synthesizer or RF front end, may be comprised of many thousands of devices. For complete architectures, such as a WLAN physical layer, there may be digital and software components that are integral to the system and that must be designed in tandem with the analog sections. Constructing test benches, selecting appropriate constraints and specifications, then synthesizing and verifying such systems is intractable using only the basic analog design flow.

Large systems are therefore partitioned into sub-blocks by identifying the sub-tasks performed by the system. If the design of a sub-block is still infeasible, then further

partitions may be necessary until the basic analog design flow can be applied. The result of system partitioning is a hierarchy tree of circuit blocks. At each level in the hierarchy, constraints, performances, and specifications need to be identified according to the function of each block and its relation to the block above it in hierarchy. Abstraction of functionality can be employed to create a simplified behavioral model of a block in the hierarchy tree before it is designed at the detailed device level and to reduce the time needed to simulate large blocks [RGR07].

## 1.1.5 Analog Circuit Design Automation

Complete or partial automation techniques are available for each step of the basic analog design flow.

Two broad approaches are used to automate topology selection. In the first approach, designer knowledge or an iterative search algorithm is used to create a circuit of small functional blocks. Each functional block performs an elementary analog operation, for example a current mirror. Multiple structures for each functional block are predefined and saved in a library along with the constraints necessary to ensure correct behavior. The structure with the greatest potential to fulfill the purpose of the complete circuit is then chosen for each functional block. circuit sizing is often combined with topology selection in this approach [HRC89, ETP89, DCR05]. The second widely used method of topology selection is topology generation from basic devices, for example CMOS transistors, using graph grammar rewriting [DV09], or signal flow graphs [GE95].

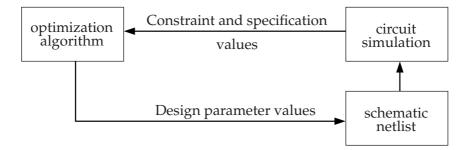

For circuit sizing automation, a set of design parameters that satisfy the circuit constraints and specifications is sought out using a numerical optimization algorithm. Design parameter values are systematically selected by the optimization algorithm and the corresponding value of the constraints and performances are evaluated by numerical circuit simulation. The optimization algorithm terminates when a set of design parameters is found that evaluates all constraints and specifications to true. In this case the circuit is designated as feasible. Circuit sizing automation using a numerical optimization algorithm is illustrated in Figure 1.1.

Many optimization algorithms have been used in analog circuit sizing, the most popular categorization of algorithms is to divide them into deterministic [LD81, NRSVT88, AEG<sup>+</sup>00a, GH10, Soo08, EDGS03, AEG<sup>+</sup>00b, LGXP04] and stochastic algorithms [Kes95, GWS90, SCP07, ORC96, MFDCRV94, ABD03, PKR<sup>+</sup>00]. Since the numerical simulation of analog circuit incurs a high computational cost, the number of constraint and performance evaluations needed to terminate the algorithm is an important measure of algorithm fitness.

Circuit layout synthesis is comprised of the device placement and routing operations. There are many design heuristics and constraints that must be fulfilled during the placement and routing of devices, such as device orientation, proximity, and symmetry conditions [Has01]. Several algorithms to automate placement and routing are available in literature [ESGS10, XY09, WCC03, PCLX01, RM08, HRM08, Cad03a].

Geometric and electrical verification ensure that the post-layout circuit fulfills the technology layout rules and that the circuit will operate correctly after layout synthesis. Mature commercial tools to extract a circuit model from a layout and to perform verification are readily available [Cad05].

# 1.2 Motivation

## 1.2.1 Backtracking in the Analog Design Flow

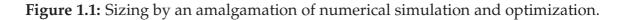

As stated in Section 1.1.1, the basic analog design flow consists of four steps that are completed consecutively. It may be necessary to backtrack one or more steps up the design flow if progress cannot be made towards completion, as shown in Figure 1.2.

Backtracking is costly, the problem blocking progress must be identified and a remedy determined; multiple iterations through the design flow may be necessary before successful completion.

If no combination of circuit topology and design parameter values exists to fulfill the specifications, then a redesign of the system at a higher level must be performed. This is illustrated by backtracking paths (1) and (2) in Figure 1.2. One remedy is to pursue a bottom-up design approach whereby all attainable performance values are ascertained before high system level design is begun.

A failure detected during the layout synthesis or electrical verification steps typically means circuit sizing and layout creation must be repeated. This is illustrated by backtracking paths (3) and (4) in Figure 1.2. A remedy is to consider or estimate the effects of layout synthesis during circuit sizing. This is the principle objective of this dissertation, and is expanded upon in Section 1.2.2.

Figure 1.2: Backtracking and reiteration through the design flow may be necessary.

### 1.2.2 Layout-Driven Circuit Sizing

Layout synthesis may have a critical effect on circuit behavior:

- Layout-induced parasitic components, such as routing resistance and coupling capacitance, affect electrical performance.

- Systematic and intra-die random process parameters that depend on device placement, such as the distance between symmetric devices in Pelgrom's law [LBSG07], process gradients, and anisotropic effects, affect electrical performance and yield numbers.

Circuit performance values may change significantly after layout synthesis due to these two items, consequently a specification may become unsatisfied.

In top-down design, geometric specifications, such as the maximum area and aspect ratio of a circuit block, may be set at the system level. The location of pin connections on the boundary of the layout silhouette might also be fixed during chip floorplanning prior to circuit block design [KWY96]. If the geometric specifications cannot be satisfied during the layout synthesis step, then device dimensions, such as CMOS transistor widths, must be reduced and circuit sizing repeated.

Several remedies can be applied to mitigate these flaws:

• Design heuristics are applied during layout synthesis to help match the electrical performance of the circuit before and after layout synthesis [Has01]; for example, the use of common centroid device placement and symmetric signal path routing to improve matching and increase common mode signal rejection in differential signal paths.

- Circuit area is estimated from device dimensions, such as CMOS transistor width and length, before layout synthesis; maximum area is then set as a specification during circuit sizing.

- Performance specifications are tightened by an extra margin to account for the effects of layout synthesis.

It may not be feasible to negate the complete effects of layout synthesis or to estimate area with enough accuracy before actual layout.

For example, Table 1.1 states the specifications and lists the simulated performance values of a CMOS operational amplifier after both circuit sizing and layout synthesis. The value of some performances, such as common mode rejection ratio (CMRR), power supply rejection ratio (PSRR), and total harmonic distortion (THD), change significantly. The PSRR and THD specifications are unsatisfied after layout synthesis. Area estimation is too pessimistic – a more favorable tradeoff can probably be found between performances in the feasible performance space, and the result of circuit sizing is sub-par after layout synthesis.

| Table 1.1: Performances and | l specifications of a | CMOS operational | amplifier |

|-----------------------------|-----------------------|------------------|-----------|

|-----------------------------|-----------------------|------------------|-----------|

| Specification           | Unit      | After          | After            |  |

|-------------------------|-----------|----------------|------------------|--|

| Specification           | OIIIt     | Circuit Sizing | Layout Synthesis |  |

| $Gain \ge 80$           | dB        | 83             | 83               |  |

| $\text{CMRR} \ge 100$   | dB        | 114            | 111              |  |

| $\text{PSRR} \geq 90$   | dB        | 90             | 86               |  |

| Power $\leq 0.50$       | mW        | 0.41           | 0.42             |  |

| $\text{THD} \leq 0.100$ | %         | 0.091          | 0.104            |  |

| Area $\leq 3500$        | $\mu m^2$ | 3495*          | 3229             |  |

\*Estimated layout area used during circuit sizing.

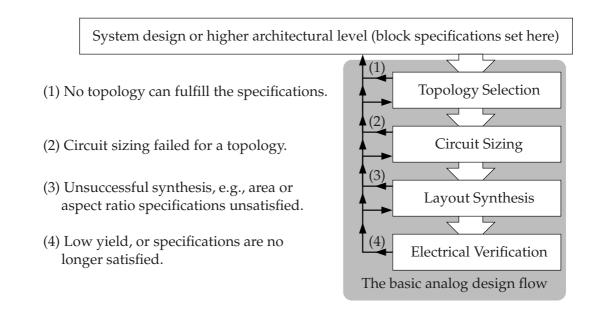

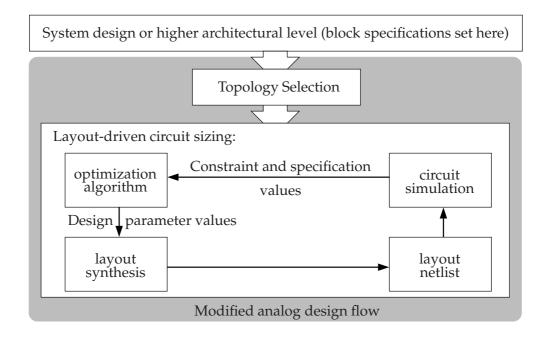

For problematic circuit problems where mitigation methods are unsatisfactory, layout synthesis can be integrated into the circuit sizing step to create a so-called layout-driven solution to the circuit sizing problem as illustrated in Figure 1.3. The result of layout-driven sizing is a layout that meets the circuit specifications and constraints.

Several layout-driven circuit sizing methods, as well as placement and routing algorithms, can be found in literature; they are reviewed in the state of the art section.

Figure 1.3: Analog design flow with layout-driven circuit sizing.

# 1.3 State of the Art

The state of the art in layout-driven (or layout-aware) circuit sizing can be divided into template-based and non-template-based methods.

As the name implies, template based methods rely on the use of layout templates [CLGRF08, BJS05, JZB<sup>+</sup>06]. A template specifies the spatial relation between circuit devices, such as transistors and capacitors, as well as fixed interconnect paths for routing. The template is created for each circuit topology prior to circuit sizing.

Template methods can be roughly categorized according to the data structure used to store the spacial relation between devices and the algorithm used for automatic circuit sizing. Used data structures include the slicing tree, O-tree, and B\*-tree. Global optimization algorithms were used in the state of the art methods, including evolutionary algorithms and simulated annealing.

In [CLGRF08] a template defined by a slicing tree is used to estimate circuit area and layout parasitics. Interconnect parasitic estimates are stored in a lookup table associated with the template, while analytical-geometric techniques are used to extract the parasitics of placed devices. A simulated annealing algorithm is used for circuit sizing, requiring several thousand iterations for convergence in the given circuit examples.

Other methods, such as [HJBRS05, LZ10], are aimed at process migration or performance retargeting. An existing circuit layout is used as a template, device dimensions are modified, after which interconnects are shrunk or extended to meet the layout and electrical design rules of the process technology.

For process migration, the technology layout rules may change prohibiting a direct downscaling of a template. As an example, in some 65 and 45nm technologies, transistor gates must be aligned on a grid while all gates must share the same orientation. It may also be difficult to avoid new routing conflicts or an increase in routing congestion when downscaling.

For performance retargeting, the aspect ratio of circuit devices may become extreme if the device parameters, such as CMOS width, change by a significant amount. This was solved in the references by the addition of geometric constraints on template devices. However, due to the fixed spatial relation between template devices, these geometric constraints must be severe, this will decrease the size of the optimization search space.

The non-template-based layout-driven sizing methods rely on simplifying approximations for performance evaluation, layout construction, and the modeling of layout parasitic devices in order to perform expeditious circuit sizing.

In [PV09] a linear regression model of the performances is used. The design space is sampled and a layout netlist is generated for each sample to define model parameters. The Pareto tradeoff [Par06] between performances is then explored using a multi-objective simulated annealing algorithm. Only layout parasitic devices are roughly approximated, while geometric constraints and matching are not considered.

In [YD09] performance sensitivity to node capacitance and device mismatch is used to direct placement using an algorithm based on slicing trees. Different shapes are considered for each device. A custom fast circuit simulator is used, however only DC and AC performance sensitivities can be calculated.

Several constraint-driven placement and routing algorithms can be found in [XY09, WCC03, PCLX01, SEG<sup>+</sup>08] and [RM08, HRM08] respectively. In [ESGS10], the circuit graph is subdivided into hierarchical proximity and symmetry groups and placement constraints are automatically generated. The tool of [SEG<sup>+</sup>08] was then used for the placement generation of several example circuits. Although not complete layout-driven circuit sizing solutions, these algorithms automate key layout synthesis steps.

# **1.4 Contributions of this Thesis**

A design flow is presented for automatic layout synthesis starting with a topology and a set of circuit design parameter values. The flow is driven by geometric design, placement, and routing constraints and is not a template-based method. The new flow is integrated with the deterministic nonlinear optimization algorithm in [SSGA00] to perform layout-driven circuit sizing.

The novelty, in comparison to the state of the art, is summarized in six items:

- A deterministic optimization algorithm is used. In contrast to stochastic global search algorithms, such as evolutionary algorithms and simulated annealing, the deterministic algorithm has local scope, but converges to a solution within a small number of iterations, moreover, it requires a small number of performance evaluations. Less than 250 performance evaluations were needed for the most complicated circuit example. Theoretically, Q-superlinear convergence is possible with a smooth objective function.

- In the state of the art, simplifications are made to expedite performance evaluation. Knowledge-based equations, regression models, or a custom numerical simulator is used that is limited to DC and AC analysis. This is necessary as the used stochastic search algorithms demand thousands of performance evaluations. No simplifications are made in the proposed method; any numerical simulator can be used.

- The closest competitor in literature pursuing a method that is not template-based generates layout placements using a slicing tree algorithm. In the new method, a placement algorithm based on B\*-trees is used [SEG<sup>+</sup>08]. It is known that a wider range of placement arrangements can be explored using B\*-trees than slicing or O-tree algorithms [WCC03].

- Layout parasitics are extracted by an integral equation field solver with an permissible error of 3%. No analytical-geometric models are used to expedite parasitic estimation.

- DC electrical constraints are employed during layout synthesis to ensure correct circuit function and robustness. It has been shown in [MCR00, MGS08] that geometric and electrical circuit sizing rules are important for circuit function and robustness. Whilst almost all layout-driven methods in the state of the art implement the geometric constraints during layout synthesis, none check that the electrical constraints also remain satisfied. Parasitic resistance, however, can have an effect on the DC bias point of the circuit. In this thesis, the DC electrical constraints are ensured during routing by dynamically setting the upper bound on the allowed resistance of each routing path, by solving an optimization subproblem.

- The effect of routing congestion is considered in the new method. Layouts are adjusted to eliminate congestion.

The bulk of the state of the art methods and the ones that consider the most details in layout synthesis are template-based methods. In addition to the six items above, the presented method is distinguished from template-based methods in some categories:

- For each device in the circuit, a multi-valued mapping between device design parameters (such as CMOS transistor width and length) and possible device layouts is performed. Only layouts that satisfy certain geometric constraints and minimize discretization error due to manufacturing grid alignment are considered as possibilities for placement.

- For devices in a common centroid placement configuration, the number of divisions and the interleave pattern is selected during layout synthesis for an optimal layout. Traditionally, the number of divisions is fixed at the schematic level.

- In template-based methods, devices have a set location in the layout template that is fixed by a single slicing tree, O-tree, or B\*-tree. During synthesis, only placements that conform to the fixed tree can be considered. In contrast, every possible B\*-tree is considered by the new method.

## **1.5 Related Publication**

Parts of the research work completed in this dissertation have been published in [HG11]. The principle steps of automatic constraint-based layout synthesis were described, as was the integration with a deterministic circuit sizing algorithm. The new layout-driven circuit sizing algorithm was demonstrated on two circuit examples, an operational amplifier and a tunable operational transconductance amplifier.

## 1.6 Organization of this Thesis

The reminder of this dissertation is organized as follows. In Chapter 2, mathematical definitions are given for circuit parameters, performances, and sizing rules. This is followed by a formulation of the circuit sizing problem. In Chapter 3, the basic steps of layout synthesis are detailed. Techniques to extract an electrical model from a geometric layout are also reviewed. In Chapter 4, the new automatic constraint-driven layout synthesis flow is presented. In Chapter 5, the new layout-driven circuit sizing procedure is presented. The issues resulting from numerical function evaluation and layout synthesis are described, as are techniques to handle these issues for successful sizing. Chapter 6 details the circuit sizing process for three circuit examples. The results of layout-driven sizing are compared to those of traditional circuit sizing without integrated layout synthesis. Chapter 7 concludes this dissertation.

# **Chapter 2**

# Formulation of the Circuit Sizing Problem

This chapter starts with mathematical definitions for circuit parameters, performances, and sizing rules. This is followed by a description of the circuit sizing problem for feasibility and for the fulfillment of performance specifications.

## 2.1 Basic Definitions

#### 2.1.1 Electrical Circuit Topology

An electrical circuit topology, T, is an interconnection of electrical devices, in which each device has two or more terminals. The topology can be represented by a hypergraph  $HG(V, \mathcal{E})$ , were the vertices, V, are the interconnects (circuit nodes) and the hyperedges,  $\mathcal{E}$ , are the devices [EGB06]:

$$\mathcal{T} \longrightarrow HG(\mathcal{V}, \mathcal{E}) \tag{2.1}$$

Each device  $\delta \in \mathcal{E}$  is associated with a 3-tuple consisting of the device name, device type, and a list of device-terminal to vertex connections:

$\boldsymbol{\delta} = \begin{bmatrix} \text{"name"} \\ \text{"type"} \\ \text{"connections"} \end{bmatrix} \quad \begin{array}{l} \text{e.g., MN1, MN2, MP1, C1, R1, ...} \\ \text{e.g., NMOS, PMOS, polysilicon-capacitor, ...} \\ \text{e.g., } [\nu_3, \nu_1, \nu_9] \text{ with } \{\nu_1, \nu_3, \nu_9\} \in \mathcal{V} \end{array}$ (2.2)

The possible device types depend on the used technology. Each device type is associated with an electrical model for simulation and geometric rules for layout synthesis.

The circuit is electrically controllable through a subset of its vertices,  $V_e \subseteq V$ , defined as external circuit nodes.

### 2.1.2 Electrical Test Bench Topology

A test bench topology, TB, is an interconnection of electrical devices. It is designed to be connected to the external nodes,  $V_e$ , of a circuit topology, T, and establish the operating conditions under which electrical behavior is studied. This includes bias, stimulus, and external load and feedback conditions. Open paths in the hypergraph of T must also be closed by connecting to a test bench.

As with the circuit topology, the test bench can be represented by a second hypergraph with vertices VB and devices (edges) EB:

$$\mathcal{TB} \longrightarrow HG(\mathcal{VB}, \mathcal{EB}); \ \mathcal{V}_e = \mathcal{V} \cap \mathcal{VB}$$

(2.3)

#### 2.1.3 Circuit Parameters

The circuit and test bench depend on a number of parameters that control how device models will behave during numerical simulation. These parameters can be classified into three separate categories:

#### **Design Parameters**

These are the parameters that can be freely adjusted by the circuit designer. A further distinction can be made between design parameters attached to circuit devices,  $\mathcal{E}$ , such as the width and length of a CMOS transistor, and the capacitance of a polysilicon capacitor; and design parameters attached to test bench devices,  $\mathcal{EB}$ , typically the DC voltage or current of power source used to bias the circuit.

As well as electrical behavior, design parameters attached to circuit devices will affect the geometric attributes of the circuit, such as layout area.

Let  $\mathbf{d}_{\delta}$  denote the design parameters of a device  $\delta \in \mathcal{E} \cup \mathcal{EB}$ ,  $\mathcal{D}_{\delta}$  denote the associated domain. For example, if  $\delta$  is CMOS device, then  $\mathbf{d}_{\delta} = \mathbf{d}_{\text{CMOS}}$  and  $\mathcal{D}_{\delta} = \mathcal{D}_{\text{CMOS}}$  as given in Table 2.1.

| $\mathbf{d}_{\mathrm{CMOS}} \! \in \! \mathcal{D}_{\mathrm{CMOS}}, \ \mathcal{D}_{\mathrm{CMOS}} = \mathcal{D}_{W} \times \mathcal{D}_{L}$ |              |                                 |                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|----------------------------------------|--|

| i                                                                                                                                          | description  | $\mathbf{d}_{\mathrm{CMOS}}[i]$ | Domain                                 |  |

| 1                                                                                                                                          | total width  | W                               | $\mathcal{D}_W = [W_{\min}, W_{\max}]$ |  |

| 2                                                                                                                                          | total length | L                               | $\mathcal{D}_L = [L_{\min}, L_{\max}]$ |  |

Table 2.1: CMOS device design parameters

The CMOS design parameters are the transistor width and length. The domain of each parameter is a bounded interval of real numbers. A bound may denote a technology constraint or a designer preference.

The *circuit design parameters* are ordered as vector  $\mathbf{d}_{\mathcal{E}}$ , with  $n_{d\mathcal{E}} = |\mathbf{d}_{\mathcal{E}}|$ :

$$\mathcal{E} = \{\delta_1, \delta_2, \ldots\} \Rightarrow \begin{cases} \mathbf{d}_{\mathcal{E}} = [\mathbf{d}_{\delta_1}^T; \mathbf{d}_{\delta_2}^T; \ldots]^T & \text{(circuit design parameters)} \\ \mathcal{D}_{\mathcal{E}} = \mathcal{D}_{\delta_1} \times \mathcal{D}_{\delta_2} \times \cdots & \text{(associated design space)} \end{cases}$$

(2.4)

The test bench design parameters are ordered as vector  $\mathbf{d}_{\mathcal{EB}}$ , with  $n_{d\mathcal{EB}} = |\mathbf{d}_{\mathcal{EB}}|$ :

$$\mathcal{EB} = \{\delta_1, \delta_2, \ldots\} \Rightarrow \begin{cases} \mathbf{d}_{\mathcal{EB}} = [\mathbf{d}_{\delta_1}^T; \mathbf{d}_{\delta_2}^T; \ldots]^T & \text{(test bench design parameters)} \\ \mathcal{D}_{\mathcal{EB}} = \mathcal{D}_{\delta_1} \times \mathcal{D}_{\delta_2} \times \cdots & \text{(associated design space)} \end{cases}$$

(2.5)

The *design parameters* are combined in vector **d**, with  $n_d = |\mathbf{d}|$ ; the complete design space is denoted by  $\mathcal{D}$  and is assumed to be a bounded subset of an Euclidean space:

$$\mathbf{d} \in \mathcal{D}$$

such that  $\mathbf{d} = \begin{bmatrix} \mathbf{d}_{\mathcal{E}} \\ \mathbf{d}_{\mathcal{EB}} \end{bmatrix}$ ,  $\mathcal{D} = \mathcal{D}_{\mathcal{E}} \times \mathcal{D}_{\mathcal{EB}}$ ,  $\mathcal{D} \subset \mathbb{R}^{n\mathbf{d}}$  (2.6)

It is necessary to normalize the design parameters, so that design parameters with different units and with widely different design space bounds are comparable. Normalization is also necessary to avoid ill-conditioned transformations during numerical analysis [TB97]. In general, normalization can be accomplished by a bijective linear transformation, and is represented here by a normalization matrix **N**:

$$\mathbf{d}_{\text{normalized}} = \mathbf{N} \cdot \mathbf{d}_{\text{original}}; \quad \mathcal{D}_{\text{original}} \longmapsto \mathcal{D}_{\text{normalized}}$$

(2.7)

$$\mathbf{d}_{\text{original}} = \mathbf{N}^{-1} \cdot \mathbf{d}_{\text{normalized}}; \quad \mathcal{D}_{\text{normalized}} \stackrel{\mathbf{N}^{-1}}{\longmapsto} \mathcal{D}_{\text{original}}$$

(2.8)

Unless explicitly mentioned, it will be assumed in subsequent analysis and discussion that the design parameters are suitably normalized.

#### **Process Parameters**

Process parameters denote properties of the semiconductor fabrication technology as represented in device electrical models. For example, the BSIM3 model for CMOS devices [LJX<sup>+</sup>] has 16 important process parameters [PDML94, MI92]. It is worth noting that the effect of the fabrication process on geometric properties, such as the effective channel width and length of CMOS devices, is normally considered in the electrical models with suitable relations and process parameters.

Due to manufacturing imperfections, the value of some process parameters may vary between fabricated circuits. If variability is large enough to have a measurable effect on electrical circuit behavior, then it must be accounted for during circuit design.

Process parameters can have components that vary systematically, such as acrossfield and layout dependent variation terms [AN07], as well as statistical components that are values of a random variable. A statistical component is global if it has the same value of random variable for all devices on the same die. A statistical component is local if the value can be different for each device on the same die. Global components can be represented by a single random variable, while local component values must be picked individually for each device. In [PDML94], global variance and correlation is estimated for 16 CMOS process parameters in the BSIM model, while in [LHC86, PDW89] the mismatch in CMOS threshold voltage, current factor, and drain current due to the local variation of process parameters is studied. In [MI92], a stochastic model for the value of process parameters is developed that includes local variation components. Local variance and correlation was estimated for 16 CMOS process parameters in the BSIM model. Another model of local variation that takes into account the distance between the barycenter of devices according to Pelgrom's law is given in [LBSG07].

Examples of process parameters with a global statistical component in the BSIM3 model are gate oxide thickness (Tox), channel doping concentration (Nch), and drainsource sheet resistance (Rsh). Process parameters with a large enough local variation component to cause a mismatch in electrical properties, such as drain current, include mobility at nominal temperature ( $\mu$ 0) and the nominal threshold voltage (Vth0).

It is possible to transform the random variables of an arbitrary probability density function (PDF) into random variables of a Gaussian distribution [Esh92]. This allows the global and local statistical component values to be selected from a Gaussian distribution.

Let **s**, be the vector of transformed statistical component values of the complete circuit with  $n_{xs} = |\mathbf{s}|$ . The joint Gaussian PDF of **s** is pdf<sub>N</sub>(**s**):

$$\mathbf{s} \in \mathbb{R}^{n\mathbf{xs}}; \ \mathbf{s} \sim \mathrm{pdf}_{N}(\mathbf{s}); \ \mathrm{pdf}_{N}(\mathbf{s}) = \frac{1}{\sqrt{2\pi}^{n\mathbf{xs}}\sqrt{\mathrm{det}(\mathbf{C})}} \cdot exp(-\frac{\beta^{2}(\mathbf{s})}{2})$$

(2.9)

$$\beta^{2}(\mathbf{s}) = (\mathbf{s} - \mathbf{s}^{0})^{T} \cdot \mathbf{C}^{-1} \cdot (\mathbf{s} - \mathbf{s}^{0})$$

(2.10)

where  $s^0$  is the mean value of the Gaussian PDF and **C** is the covariance matrix.

When modeling nominal circuit behavior only, the value of  $\mathbf{s}$  is fixed to  $\mathbf{s}^0$ .

#### **Operating Parameters**

These are test bench and environment parameters that depend on the operating conditions and cannot be adjusted freely.

Environmental operating parameters, such as temperature, are set in the simulation environment – to be used directly in device models. Test bench operating parameters, such as the supply voltage or a load capacitance, are attached to test bench devices.

The test bench and environment operating parameters are combined and ordered in a vector of operating parameters,  $\theta$ , with  $n_{\theta} = |\theta|$ . Operating conditions may vary; this must be taken into account during circuit design. For this purpose it will be assumed that each operating parameter varies within a bounded interval of real numbers. The lower and upper bounds are denoted by the vectors  $\theta^l$  and  $\theta^u$  respectively:

$$\boldsymbol{\theta} \in \mathbb{R}^{n^{\star}} \land \quad \boldsymbol{\theta}^{l} \preceq \boldsymbol{\theta} \preceq \boldsymbol{\theta}^{u} \tag{2.11}$$

The relation  $\leq$  is defined for arbitrary vectors **x** and **y** with  $|\mathbf{x}| = |\mathbf{y}|$  as follows:

$$\mathbf{x} \preceq \mathbf{y} \iff \underset{1 \leq i \leq |\mathbf{x}|}{\forall} x_i \leq y_i \tag{2.12}$$

The nominal value of the operating parameters is denoted by  $\theta^0$  and is used when simulating nominal circuit behavior.

#### 2.1.4 Circuit Performances

A circuit performance is an indicator of circuit behavior that is important to the circuit designer or is useful in hierarchical design and function abstraction.

Electrical performances, such as gain and power consumption, depend on the electrical behavior of the circuit. Each is obtained by electrical simulation of the circuit using a suitable test bench, simulator, and analysis method.

Let  $\mathbf{f}_e$  denote the vector of electrical performances, such that  $n_{\mathbf{f}e} = |\mathbf{f}_e|$ , and  $\boldsymbol{\phi}_{\mathbf{f}e}$  denote the mapping of circuit parameters to electrical performances:

$$\boldsymbol{\phi}_{\mathbf{f}e}: \mathbb{R}^{n\mathbf{d}} \times \mathbb{R}^{n\mathbf{s}} \times \mathbb{R}^{n\theta} \longrightarrow \mathbb{R}^{n\mathbf{f}e}: \begin{bmatrix} \mathbf{d} \\ \mathbf{s} \\ \mathbf{\theta} \end{bmatrix} \longmapsto \mathbf{f}_e \tag{2.13}$$

When only the nominal electrical behavior of the circuit as a function of the design parameters is of interest, the statistical and operational parameters are fixed to their nominal values:

$$\boldsymbol{\phi}_{\mathrm{f}e,0}: \mathbb{R}^{n\mathbf{d}} \longrightarrow \mathbb{R}^{n\mathbf{f}e}: \begin{bmatrix} \mathbf{d} \\ \mathbf{s}^{0} \\ \mathbf{\theta}^{0} \end{bmatrix} \longmapsto \mathbf{f}_{e}$$

(2.14)

Geometrical performances represent the geometrical properties of the circuit, such as area, width, length, and aspect ratio. Layout synthesis must be completed to get accurate values of geometric performances, as the graph representation of a topology has insufficient geometrical information for accurate calculation. Nevertheless, a model to estimate the geometrical performances from the circuit design parameters could be used, as is done for area in [Has01].

Let  $\mathbf{f}_g$  denote the vector of geometric performances, such that  $n_{\mathbf{f}g} = |\mathbf{f}_g|$ , and  $\boldsymbol{\phi}_{\mathbf{f}g}$  denote the mapping of circuit design parameters to geometric performances.

$$\boldsymbol{\phi}_{\mathbf{f}g}: \mathbb{R}^{n\mathbf{d}\mathcal{E}} \longrightarrow \mathbb{R}^{n\mathbf{f}g}: \mathbf{d}_{\mathcal{E}} \longmapsto \mathbf{f}_g \tag{2.15}$$

The nominal electrical and the geometric performances are combined in one vector:

$$\boldsymbol{\phi}_{\mathbf{f}}: \mathbb{R}^{n\mathbf{d}} \longrightarrow \mathbb{R}^{n\mathbf{f}}: \mathbf{d} \longmapsto \mathbf{f}$$

(2.16)

With

$$\mathbf{f} = \begin{bmatrix} \mathbf{f}_e \\ \mathbf{f}_g \end{bmatrix}; \quad n_{\mathbf{f}} = n_{\mathbf{f}e} + n_{\mathbf{f}g}$$

(2.17)

The image of the design space,  $\mathcal{D}$ , by the mapping  $\phi_f$  is denoted by  $\mathcal{F}$ :

$$\mathcal{D} \stackrel{\phi_{\mathbf{f}}}{\longmapsto} \mathcal{F} \tag{2.18}$$

#### 2.1.5 Circuit Sizing Rules

An analog circuit topology, T, is normally composed of smaller functional subblocks, each of which performs a recognized analog operation. For example, two CMOS devices can be connected as a simple current mirror or as a differential pair [GZEA01].

Each sub-block is associated with a set of sizing rules to ensure that it functions as intended and to reduce the mismatch due to statistical variation in parameters. These rules can be derived algebraically, often from simple analytical models, such as the Schichman-Hodges model for CMOS devices [SH68], and from mismatch models, such as the mismatch model of drain current [LHC86, PDW89].

At the circuit level, identification of all sub-blocks and the application of the associated sizing rules should improve overall circuit functionality and ensure that the circuit continues to operate when considering process and operating parameter variation. Identification of sub-blocks and the application of sizing rules may also be necessary for correct layout synthesis.

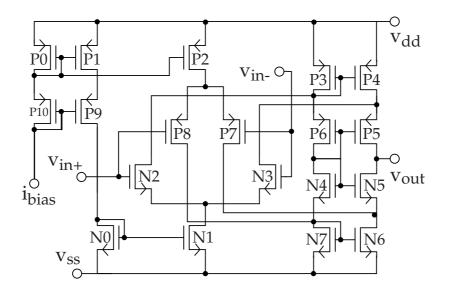

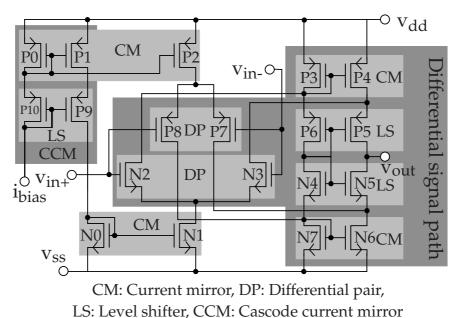

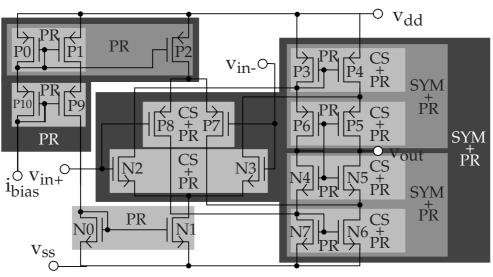

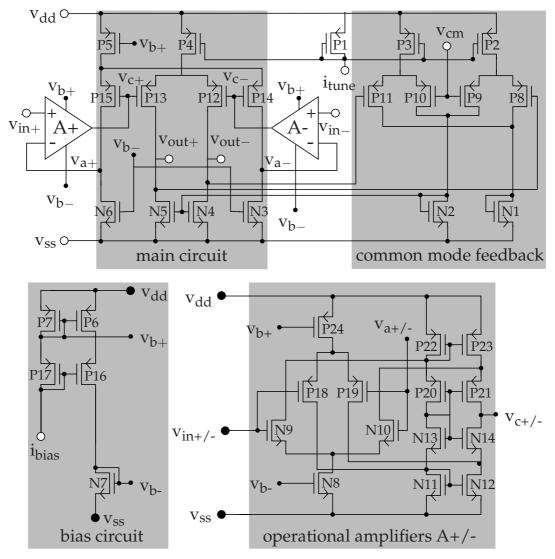

Functional blocks and sizing rules have been described under various names in a series of publications [HRC89, VLv<sup>+</sup>95, dMHBL01, DNAV99, dMHBL98, MV01, DGS03, BSV04, LHC86, GZEA01, SPS<sup>+</sup>03, MGS08]. In [MGS08], a library of more than 26 CMOS and Bipolar functional blocks is presented, along with a structure recognition algorithm to automatically identify them in a circuit topology. For example, the sizing rules of the NMOS differential pair in Figure 2.1.5 are listed in Table 2.2.

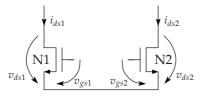

Figure 2.1: NMOS differential pair.

Sizing rules can be separated into two categories:

| Geometric rules |                            | Electrical rules |                                           |  |

|-----------------|----------------------------|------------------|-------------------------------------------|--|

| /1/             | $L_{1} = L_{2}$            | /9/              | $ V_{ds2} - V_{ds1}  \le V^{(1)}$         |  |

| /2/             | $W_1 = W_2$                | /10/             | $ V_{gs2} - V_{gs1}  \le V^{(2)}$         |  |

| /3/             | $W_1 \cdot L_1 \ge Area_m$ | /11/             | $V_{ds1} - V_{gs1} + V_{th1} \ge V^{(3)}$ |  |

| /4/             | $L_1 \ge L_m$              | /12/             | $V_{ds1} \ge V^{(4)}$                     |  |

| /5/             | $W_1 \ge W_m$              | /13/             | $V_{gs1} - V_{th1} \geq V^{(5)}$          |  |

| /6/             | $W_2 \cdot L_2 \ge Area_m$ | /14/             | $V_{ds2} - V_{gs2} + V_{th2} \ge V^{(3)}$ |  |

| /7/             | $L_2 \ge L_m$              | /15/             | $V_{ds2} \ge V^{(4)}$                     |  |

| /8/             | $W_2 \ge W_m$              | /16/             | $V_{gs2} - V_{th2} \ge V^{(5)}$           |  |

Table 2.2: Sizing rules of an NMOS differential pair based on [MGS08]

$V^{(1)}$  to  $V^{(5)} \in \mathbb{R}^+$  are electrical margins,

Area<sub>*m*</sub>,  $L_m$ ,  $W_m \in \mathbb{R}^+$  are geometric margins.

#### **Electrical rules**

These are inequality constraints that depend on the circuit DC bias point under nominal conditions. They can be formulated in terms of the design parameters:

$$\mathbf{d} \stackrel{\text{DC analysis}}{\longmapsto} \mathbf{V}(\mathbf{d}), \mathbf{I}(\mathbf{d}); \ \mathbf{h}_{e}(\mathbf{V}(\mathbf{d}); \mathbf{I}(\mathbf{d})) \succeq \mathbf{c}_{e}^{m}$$

(2.19)

where  $\mathbf{h}_e$  denotes the vector of all the electrical constraint functions, the elements of **V** are the DC voltages of the topology vertices in  $\mathcal{V}$ , and the elements of **I** are the DC terminal currents of the topology devices in  $\mathcal{E}$ . The constant  $\mathbf{c}_e^m$  is a vector of margins.

For abstract analysis, the formulation can be simplified:

$$\boldsymbol{\phi}_{ce}(\mathbf{d}) = \mathbf{h}_{e}(\mathbf{V}(\mathbf{d}); \mathbf{I}(\mathbf{d})); \qquad (2.20)$$

$$\boldsymbol{\phi}_{\mathbf{c}e}: \mathbb{R}^{n\mathbf{d}} \longrightarrow \mathbb{R}^{n\mathbf{c}e}: \mathbf{d} \longmapsto \mathbf{c}_{e}; \ \mathbf{c}_{e} \succeq \mathbf{c}_{e}^{m}$$

(2.21)

where  $\mathbf{c}_e$  denotes the vector of electrical constraints, such that  $n_{\mathbf{c}e} = |\mathbf{c}_e|$ .

#### **Geometric rules**

These are algebraic equalities and inequalities involving the geometric properties of topology devices, such as the width, length, and area.

The geometric equalities are used to reduce the dimensions of the design space by identifying and eliminating dependent design parameters. For instance, for the set of linear equalities, the dependent parameters can be identified by the application of the Gaussian elimination algorithm.

Let  $\mathbf{c}_g$  denote the vector of geometric inequality constraints, such that  $n_{\mathbf{c}g} = |\mathbf{c}_g|$ , and let  $\boldsymbol{\phi}_{\mathbf{c}g}$  denote the mapping of topology design parameters to geometric inequality constraints:

$$\boldsymbol{\phi}_{\mathbf{c}g}: \mathbb{R}^{n\mathbf{d}\mathcal{E}} \longrightarrow \mathbb{R}^{n\mathbf{c}g}: \mathbf{d}_{\mathcal{E}} \longmapsto \mathbf{c}_g; \ \mathbf{c}_g \succeq \mathbf{c}_g^m \tag{2.22}$$

Variable elimination methods can also be applied to the system of inequality constraints to create a reduced system of same kind, but with fewer variables:

$$\underbrace{\begin{bmatrix} \mathcal{D}_{\mathcal{E},\text{original}} \\ \mathbf{c}_{g,\text{original}} \succeq \mathbf{c}_{g,\text{original}}^{m} \end{bmatrix}}_{\text{original problem}} \underbrace{\begin{bmatrix} \mathcal{D}_{\mathcal{E},\text{reduced}} \\ \mathbf{c}_{g,\text{reduced}} \succeq \mathbf{c}_{g,\text{reduced}}^{m} \end{bmatrix}}_{\text{reduced problem}} (2.23)$$

$$\mathbf{d}_{\mathcal{E},\text{original}} = [\mathbf{d}_{\delta 1}^{T}; \mathbf{d}_{\delta 2}^{T}; \ldots]^{T} \xrightarrow{\text{methods}} \mathbf{d}_{\mathcal{E},\text{reduced}}; |\mathbf{d}_{\mathcal{E},\text{reduced}}| \leq |\mathbf{d}_{\mathcal{E},\text{original}}|$$

(2.24)

For example, the Fourier-Motzkin elimination algorithm [DE73, SGA07] can be applied to the set of linear inequalities to reduce the number of parameters.

A necessary condition of variable elimination is that the original and reduced systems have the same solutions over the remaining variables. This is necessary so that the individual device design parameters can be calculated and the circuit sized:

$$\mathbf{d}_{\mathcal{E}, \text{reduced}} \stackrel{\text{inverse of}}{\longmapsto} \mathbf{d}_{\mathcal{E}, \text{original}} = [\mathbf{d}_{\delta 1}^{T}; \mathbf{d}_{\delta 2}^{T}; \ldots]^{T}$$

(2.25)

Unless explicitly mentioned, it will be assumed in subsequent analysis and discussion that the mapping of (2.24) has been performed implicitly for the design parameters and inequality constraints and that  $\mathbf{d} = [\mathbf{d}_{\mathcal{E}, \text{reduced}}; \mathbf{d}_{\mathcal{E}\mathcal{B}}]$ .

The electrical and the geometric constraints are combined in one vector:

$$\boldsymbol{\phi}_{\mathbf{c}}: \mathbb{R}^{n\mathbf{d}} \longrightarrow \mathbb{R}^{n\mathbf{c}}: \mathbf{d} \longmapsto \mathbf{c}; \ \mathbf{c} \succeq \mathbf{c}^{m}$$

(2.26)

With

$$\mathbf{c} = \begin{bmatrix} \mathbf{c}_e \\ \mathbf{c}_g \end{bmatrix}; \ \mathbf{c}^m = \begin{bmatrix} \mathbf{c}_e^m \\ \mathbf{c}_g^m \end{bmatrix}; \ n_{\mathbf{c}} = n_{\mathbf{c}e} + n_{\mathbf{c}g}$$

(2.27)

#### 2.1.6 The Feasible Design Space and Performance Space

The feasible design space,  $\hat{D}$ , is defined as the subset of the design space, D, that fulfills the electrical and geometric circuit constraints (the circuit sizing rules):

$$\hat{\mathcal{D}} = \{ \mathbf{d} \in \mathcal{D} \mid \boldsymbol{\phi}_{\mathbf{c}}(\mathbf{d}) = \mathbf{c} \land \mathbf{c} \succeq \mathbf{c}^{m} \}$$

(2.28)

The feasible performance space,  $\hat{\mathcal{F}}$ , consists of all elements in the performance space corresponding to elements of the feasible design space,  $\hat{\mathcal{D}}$ , according to mapping  $\phi_{\mathbf{f}}$ :

$$\hat{\mathcal{F}} = \left\{ \mathbf{f} \in \mathbb{R}^{n\mathbf{f}} \mid \exists_{\mathbf{d} \in \hat{\mathcal{D}}} \boldsymbol{\phi}_{\mathbf{f}}(\mathbf{d}) = \mathbf{f} \right\}$$

(2.29)

The mapping of the feasible design space to the feasible performance space can be written as:

Vectors  $f^+$  and  $f^-$  denote the upper and lower bounds of the feasible design space and are defined below:

$$\mathbf{f}^{+} = \inf \hat{\mathcal{F}} \quad (\inf \inf \inf \, \mathbf{R}^{n\mathbf{f}}) \tag{2.31}$$

$$\mathbf{f}^- = \sup \hat{\mathcal{F}}$$

(supremum of  $\hat{\mathcal{F}}$  in  $\mathbb{R}^{n\mathbf{f}}$ ) (2.32)

It is assumed that these bounds always exist for analog circuit design problems.

### 2.2 Circuit Problem Formulation

In this section, a series of related circuit problems will be defined based on the mapping of the feasible design space to the performance space.

#### 2.2.1 Feasibility Analysis

Feasibility Analysis is the problem of finding any element of the feasible design space:

Find any

$$\mathbf{d} \in \hat{\mathcal{D}}$$

(2.33)

Conversely, the sizing rules are feasible if they are satisfied by at least one design parameter vector.

#### 2.2.2 Circuit Sizing to Meet Performance Specifications

A general specification is an inequality involving a function of circuit performances. Specifications are set at the system design level for each sub-block circuit. The correct operation of a system depends on specification satisfaction in each sub-block. Let  $\mathbf{s}(\mathbf{f})$  denote a general vector of specification functions, and let  $\mathbf{f}^l$  and  $\mathbf{f}^u$  denote lower and upper specifications respectively:

$$\mathbf{f}^{l} \preceq \mathbf{s}(\mathbf{f}) \preceq \mathbf{f}^{u} \tag{2.34}$$

Without loss of generality, it is assumed that the specifications take the form of an upper bound,  $f^u$ , on the value of the performances:

$$\mathbf{f} \leq \mathbf{f}^{u} \tag{2.35}$$

If necessary, a performance space can be transformed so that the specifications take the form of (2.35):

$$\begin{array}{ccc} \mathbf{f}^{l} \preceq \mathbf{s}(\mathbf{f}) \preceq \mathbf{f}^{u} \implies & \mathbf{f}_{\text{new}} \preceq \mathbf{f}_{\text{new}}^{u} \\ \text{specifications in original} & \text{specifications in a new} \\ \text{performance space} & \text{performance space} \end{array}$$

(2.36)

For example, general specifications  $\mathbf{f}^l \preceq \mathbf{s}(\mathbf{f}) \preceq \mathbf{f}^u$  can be transformed as follows:

$$\mathbf{f}^{l} \leq \mathbf{s}(\mathbf{f}) \leq \mathbf{f}^{u} \implies \underbrace{\begin{bmatrix} \mathbf{s}(\mathbf{f}) \\ -\mathbf{s}(\mathbf{f}) \end{bmatrix}}_{\mathbf{f}_{\text{new}}} \leq \underbrace{\begin{bmatrix} \mathbf{f}^{u} \\ -\mathbf{f}^{l} \end{bmatrix}}_{\mathbf{f}_{\text{new}}}$$

(2.37)

This transformation preserves the differentiability class of  $\mathbf{s}(\mathbf{f})$ , but has twice as many dimensions after transformation, such that  $|\mathbf{f}_{new}| = 2|\mathbf{s}(\mathbf{f})|$ .

The circuit sizing problem is formulated as follows in the performance space:

Find any

$$\mathbf{f} \in \hat{\mathcal{F}}$$

subject to  $\mathbf{f} \preceq \mathbf{f}^u$  (2.38)

The solution to the circuit sizing problem in the design space is usually of interest, since it can be readily used to synthesize a circuit:

Find any

$$\mathbf{d} \in \hat{\mathcal{D}}$$

subject to  $\mathbf{f} \leq \mathbf{f}^{u}$  where  $\boldsymbol{\phi}_{\mathbf{f}}(\mathbf{d}) = \mathbf{f}$  (2.39)

# **Chapter 3**

# **Overview of Layout Synthesis Steps**

## 3.1 Introduction

A layout is blueprint of planar geometric shapes used to create photo masks for the physical realization of an IC in a specific fabrication technology using the technique of photo lithography.

The layout of a circuit block can be separated into three steps:

- Layout of individual physical devices, such as MOS transistors, and polysilicon capacitors.

- Compact placement of device layout polygons relative to each other on a plane.

- Routing of connections between device terminals, as well as the circuit pins.

Layout synthesis is followed by electrical and geometric verification to ensure the correctness of the synthesis process.

Electrical behavior may change in ways that may not be accounted for during circuit sizing at the topology level. Electrical verification aims to check if the electrical constraints and the specifications set on electrical performances are satisfied by the circuit post-layout synthesis. In order to complete electrical verification, an electrical model must be extracted from the layout geometry and the technology information.

Geometric verification checks if the layout geometry fulfills the technology layout rules (design rule checking or DRC), as well as the specifications set on geometric performances, such as width, length, area, and aspect ratio. Layout design rules specify geometric and connectivity restrictions at the layout level. They are particular to a semiconductor manufacturing process and ensure the correctness of a mask set. They also ensure sufficient margins to account for variability in semiconductor manufacturing processes.

The remainder of this chapter is organized in four sections. Sections 3.2 through 3.4 describe the three steps of layout synthesis in detail. The conditions necessary to

ensure circuit functionality and robustness after layout are explained. Algorithms and techniques found in literature to automate each step are also listed. Section 3.5 reviews the techniques used to extract an electrical model from a geometric layout.

## 3.2 Layout of Individual Physical Devices

For each device in the circuit topology, the planar geometric layers needed to create the physical realization using the process of photolithography are drawn.

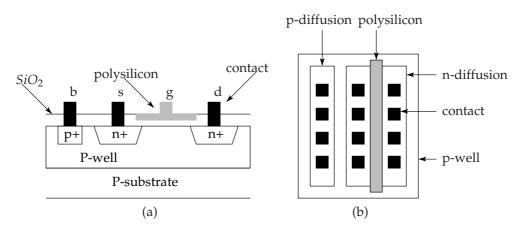

For example, Figure 3.1(a) shows a simplified cross section of a fabricated NMOS transistor, while Figure 3.1(b) shows the geometric layout information needed to correctly fabricate the NMOS device. The NMOS device layout, as pictured, is formed of 16 rectangles in five different layers.

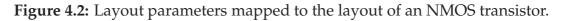

Figure 3.1: Physical cross section and layout of an NMOS transistor.

In order to systematically create device layouts, each device in the circuit topology is attached to a list of layout parameters that depend on the device type, such as NMOS, PMOS, polysilicon capacitor, etc. For example, the number of folds and gate orientation are two layout parameters of a CMOS device. The layout parameters are used to draw the geometric layout of the device according to the layout rules of the used fabrication technology.

### 3.2.1 Device Layout Automation

A procedure can be used to map a list of layout parameters to a device layout in a systematic manner that meets all technology layout rules. For example, in the commercial Cadence analog design framework, parametric cells (PCELLS) are created for each type of device, and used to map layout parameters to a device layout [Cad08].

# 3.3 Device Placement

The individual device layouts are placed relative to each other on a plane. There may be innumerable possible arrangements to place the devices, however certain considerations must be taken into account during placement; these considerations are listed below:

- Circuit geometric constraints must be satisfied by the layout; these constraints include the technology layout rules and the circuit dimension, area, and aspect ratio specifications.

- The placement should be compact maximizing area utilization.

- The parasitic devices on both halves of a differential circuit must be balanced. At the placement level, this is ensured by placing devices symmetrically along differential signal paths.

- In order to be successful, circuit routing should be taken into account during the placement step. Connected devices should be placed in proximity, thereby reducing total wire length and parasitic routing resistance. Noise sensitive signal paths should be kept away from noise sources to avoid coupling through layout parasitic coupling capacitors. Margins of space must be left between devices to insure that device terminal are unblocked and reachable by routing layers. These margins must also be wide enough to avoid routing congestion [Sax07]. Symmetric device placement is also necessary to create symmetric routing.

- The variation in the electrical behavior between matched devices is dependent on device placement, as will be described here: Process anisotropic effects are caused by certain manufacturing steps, such as plasma etching, ion implant angle, or from lattice orientation. Adjacent structures to matched devices may have a systematic influence on the value of the process parameters. Die stress from packaging or thermal gradients may cause considerable systematic drift in process parameter values. Finally, the variance in the value of some process parameters, such as CMOS nominal threshold voltage Vth0, depends on the distance between devices; this is modeled by the distance term in Pelgrom's law [LBSG07]. It is difficult to numerically model the effect of placement-dependent variation at the device level, since information about the spacial variation in the value of the process parameters is typically not supplied by the fabrication technology foundry. However, the effect of placement on electrical performance can be minimized by using appropriate layout techniques [Has01].

For example, the appropriate techniques for matched CMOS devices are tabulated in Table 3.1, along with the source of mismatch that is minimized by each technique. The techniques are adjacent parallel placement, matching drain-tosource orientation, splitting and interleaving of devices fingers, splitting and common centroid layout, and the use of dummy elements to surround matched devices.

| Layout techniques                 | Local process | Systematic | Adjacent   | Anisotropic |

|-----------------------------------|---------------|------------|------------|-------------|

|                                   | parameters    | gradients  | structures | effects     |

| Adjacent parallel placement       | Х             | Х          |            |             |

| Surround by dummy elements        |               |            | Х          |             |

| Common centroid                   | Х             | Х          |            |             |

| Split and interleave              | Х             | Х          |            |             |

| Match drain-to-source orientation |               |            |            | Х           |

Table 3.1: Layout techniques for matched CMOS devices

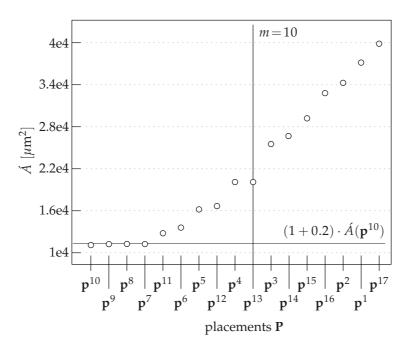

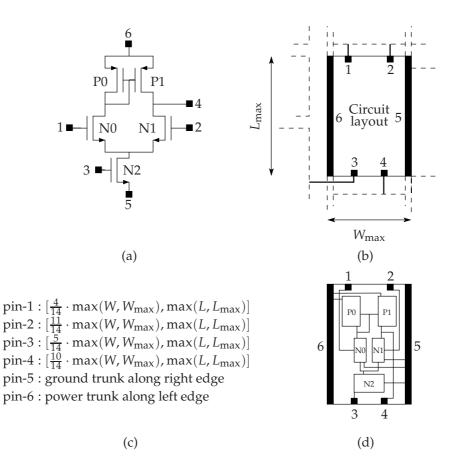

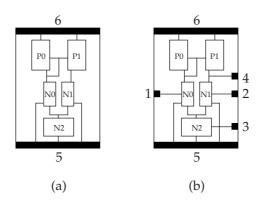

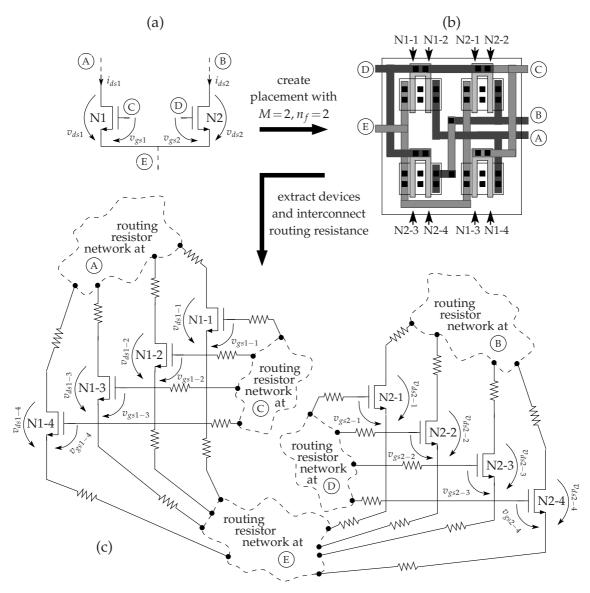

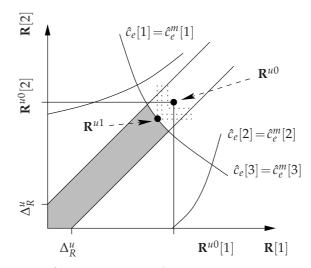

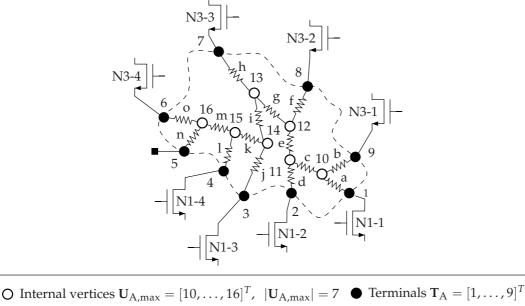

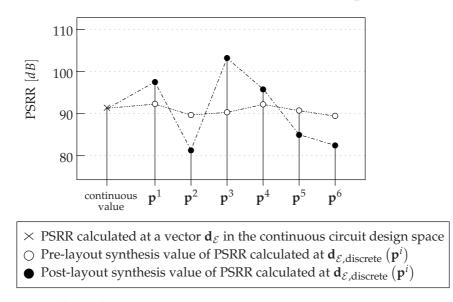

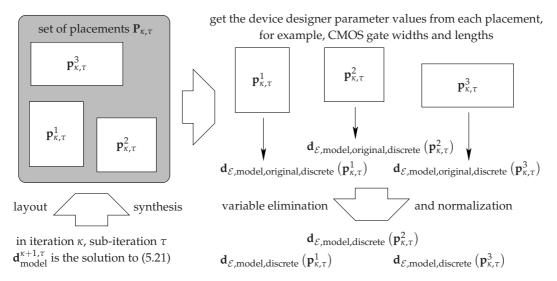

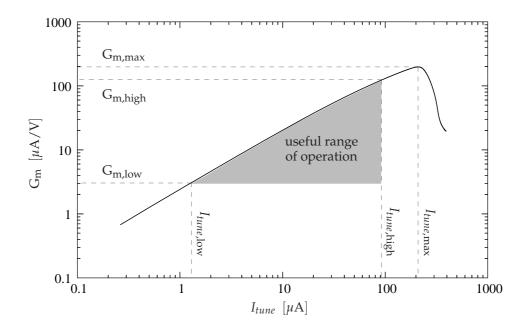

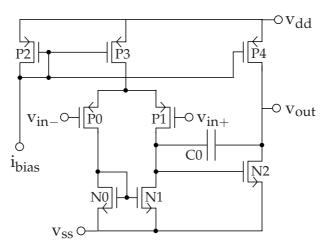

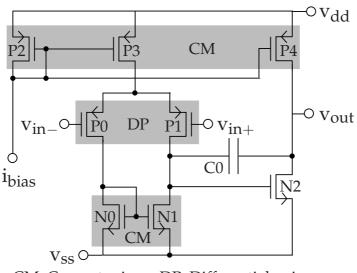

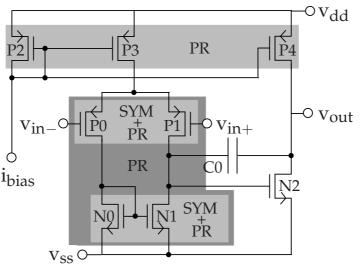

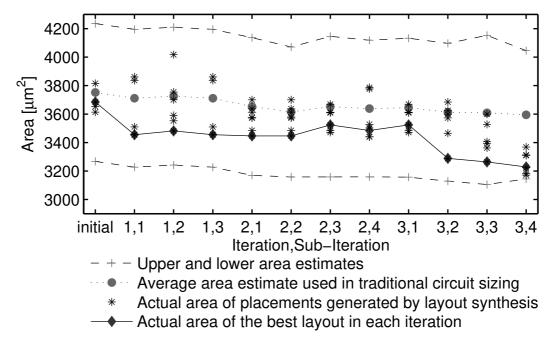

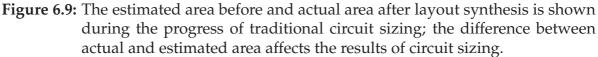

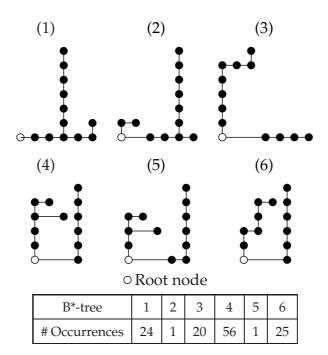

In the state of the art, placement considerations have been formulated as geometric constraints to limit the space of possible placement arrangements. In [EK96], the proposed constraints are maximum area, the deviation from a specified circuit aspect ratio, and a maximum path delay for each routing path. Common centroid and symmetry constraints are formulated in [XY09], while in [SEG<sup>+</sup>08], device proximity, symmetry, common centroid, and minimum distance constraints are used.