## Construction and Performance of the ATLAS SCT Barrels and Cosmic Tests

by

Bilge Melahat Demirköz Balliol College

B.S., Massachusetts Institute of Technology (2001) S.M., Massachusetts Institute of Technology (2004)

Submitted to the Department of Physics for the degree of

Doctor of Philosophy

$\operatorname{at}$

Balliol College OXFORD UNIVERSITY

April 2007

© Bilge Melahat Demirköz, MMVII. All rights reserved.

The author hereby grants to Oxford University permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part.

## Construction and Performance of the ATLAS SCT Barrels and Cosmic Tests

by

Bilge Melahat Demirköz

Submitted to the Department of Physics on April 17, 2007, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

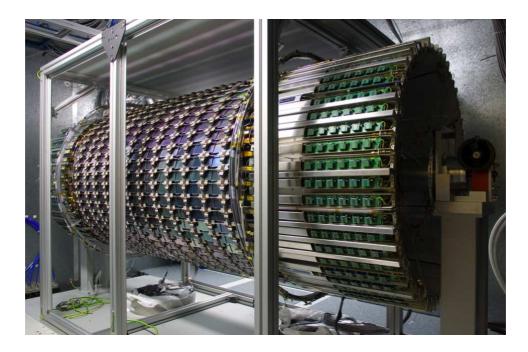

ATLAS is a multi-purpose detector for the LHC and will detect proton-proton collisions with center of mass energy of 14TeV. Part of the central inner detector, the Semi-Conductor Tracker (SCT) barrels, were assembled and tested at Oxford University and later integrated at CERN with the TRT (Transition Radiation Tracker) barrel. The barrel SCT is composed of 4 layers of silicon strip modules with two sensor layers with  $80\mu$ m channel width. The design of the modules and the barrels has been optimized for low radiation length while maintaining mechanical stability, bringing services to the detector, and ensuring a cold and dry environment. The high granularity, high detector efficiency and low noise occupancy ( $< 5 \times 10^{-4}$ ) of the SCT will enable ATLAS to have an efficient pattern recognition capability.

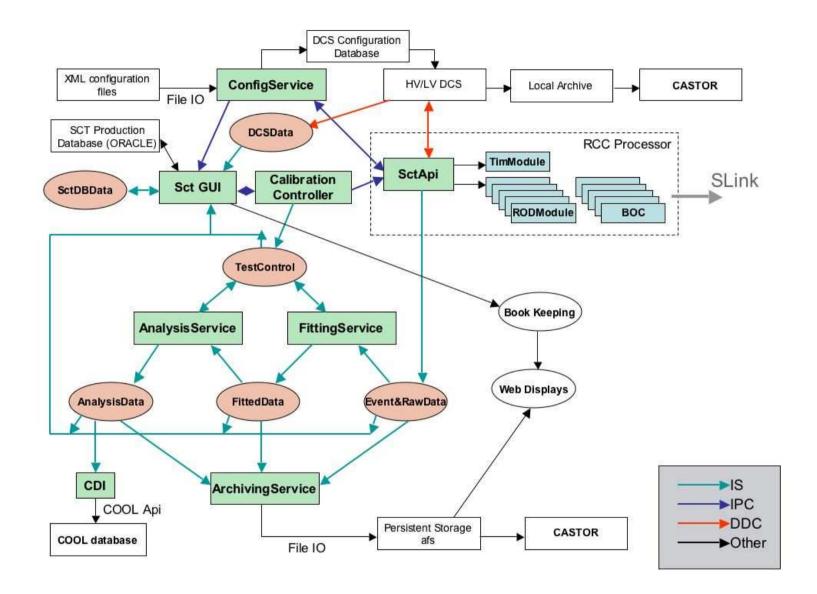

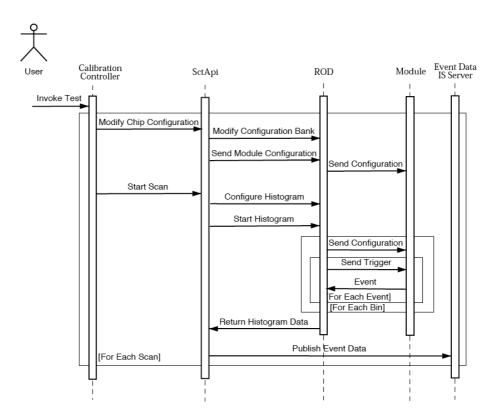

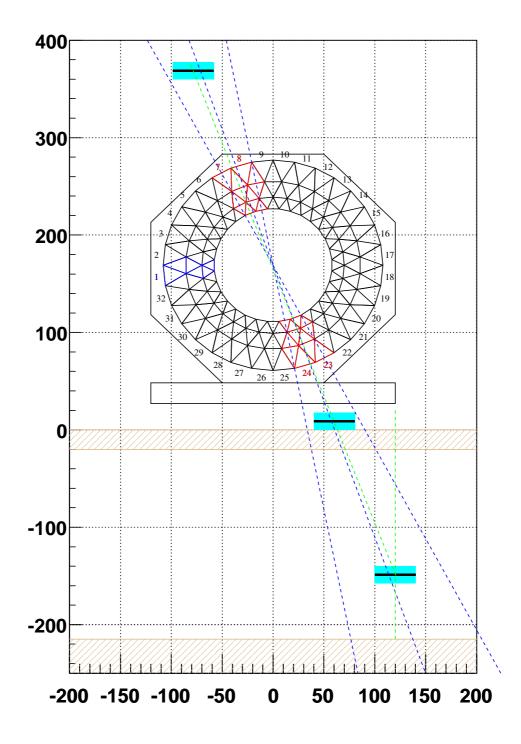

Due to the binary nature of the SCT read-out, a stable read-out system and the calibration system is of critical importance. SctRodDaq is the online software framework for the calibration and also the physics running of the SCT and has been developed and tested during construction and commissioning of the detector with cosmics. It reliably measures the SCT performance parameters for each of the  $6.3 \times 10^6$ channels in the SCT, identifies defects and problematic modules and writes them to an offline database for access from Athena, the ATLAS offline software framework. This dataflow chain has been exercised during the cosmics run at CERN, where a  $5 \times 10^5$  cosmics sample for the combined SCT and TRT detectors was collected with a scintillator based trigger. It is now being commissioned in the ATLAS pit.

## Acknowledgments

I would like to thank the Particle Physics and Astronomy Council (PPARC) and Scottish Power for awarding me the Dorothy Hodgkin Award which funded me for the duration of my graduate studies and again to PPARC for awarding me a Long Term Attachment (LTA) position at CERN. I would like to thank the Oxford Physics department and Balliol College for providing funding which enabled me to go to conferences. I would like to thank Profs. Ulrich Becker and Susan Cooper for inspiring me and helping me start my studies at Oxford University.

In a collaboration like ATLAS, it is simply impossible to thank each and everyone for their ideas. Here simply, I would like to thank everyone who took the time to discuss things with me. Irregardless, there will be unspoken heroes.

I would like to thank the team that I am part of, for it has been an honor to work with them: all members of the SctRodDaq and readout hardware development team and everyone involved in barrel macro-assembly and integration. Especially, Drs. Alan Barr, Chris Lester, Bruce Gallop, Dave Robinson, Matt Warren and John Hill have provided insight into the inner workings of the SCT and have made a creative and constructive group to work with. I would especially like to thank Peter Phillips whose help and strong support made this thesis possible. I would also like to thank *Bugs Bunny*, now a necessary figure in daily SCT operations, for surviving all attempts on his life.

I would like to thank Drs. Tony Weidberg and Georg Viehhauser who have given me wise advice and helped me navigate through a few rough seas. I would also like to thank Drs. Heinz Pernegger, Janet Carter, Mike Tyndel and Pippa Wells for their enthusiam and leadership has been an inspiration. Drs. Nigel Hessey and Todd Huffman have both been wonderful as thesis committee members. I thank them both very much for their efforts in finalizing this thesis.

Last but not least, I would like to thank my friends and my family.

This thesis is dedicated to the memory of Prof. Gian-Carlo Rota, friend and mentor.

## Author's Contribution

The work presented in this thesis is necessarily the work of a large number collaborations. Here I will try to briefly describe my specific contributions.

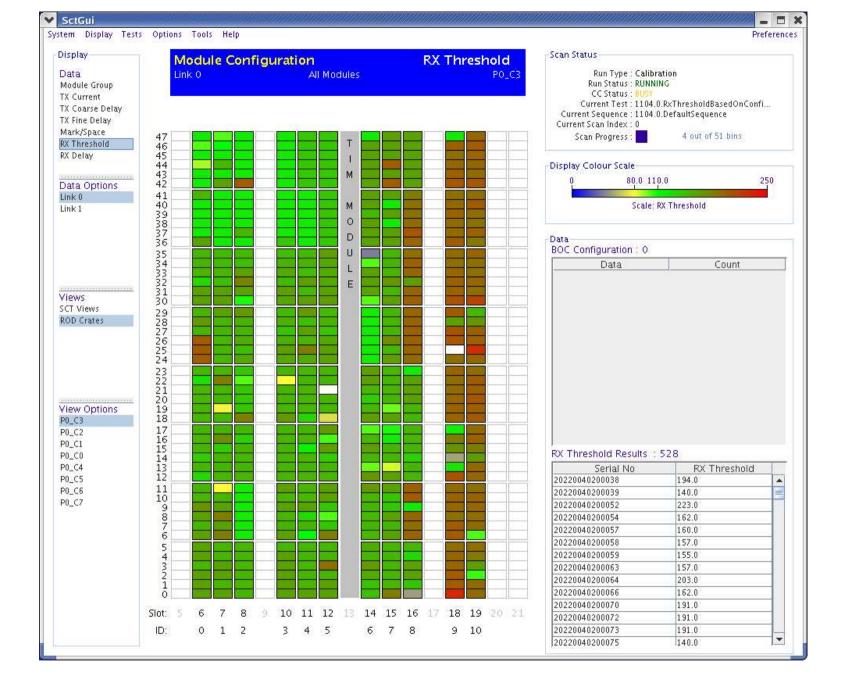

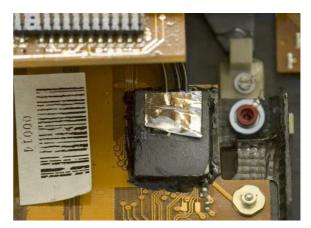

My work began with the start of macro-assembly of modules onto barrels at Oxford in October 2004. Since I was exempted from taking classes, I started immediately running cabling, fibring and testing shifts on the barrels on a daily basis, until September 2005. Testing involved learning how to operate the DCS (Detector Control System), monitor the cooling system and interlocks as well as using the testing software, called SctRodDaq. Initially, I wrote the XML-configurations for the barrels and all MURs (Minimum Unit of Readout) on the barrels. Daily testing required new configurations everyday. I also wrote the testing guidelines and updated them regularly, documenting software and hardware problems and solutions on the SctWiki. After becoming an "expert" user of SctRodDag, I helped improve the testing software. I wrote several tests and analyses for pick-up, common-mode noise diagnosis, such as CounterErrorTest, DoubleTriggerNoiseTest and OccupancyPerEvent. I found that there were a few cases of lightleaks from opto-packages onto some modules on Barrel 3 which increased the noise. A fix was found for other barrels that were assembled later. I refined the analysis of some tests such as NMaskTest, RxThresholdTest and NPtGainTest. I improved some tools to define defects and modified the software so that pipeline defects can be updated after a PipelineTest. I identified a few modules which were swapped during the macro-assembly process from their trimming "fingerprints."

As I moved to CERN in September 2005, with the last assembled barrel, I worked on the reception testing of barrels at CERN and started working on preparing the barrels for a combined cosmics test with the TRT, while the barrels were being integrated. I wrote a new package (ISSummaryWriter) to put NPtGain and Noise Occupancy test results into a form that can be easily inserted into a database and for the database, wrote a translation method in the configuration service to be able to code the offline identifier for a given module. I worked on modifying CDI (Conditions Database Interface) for SCT requirements and used CDI later to put two data sets into COOL during cosmics commissioning.

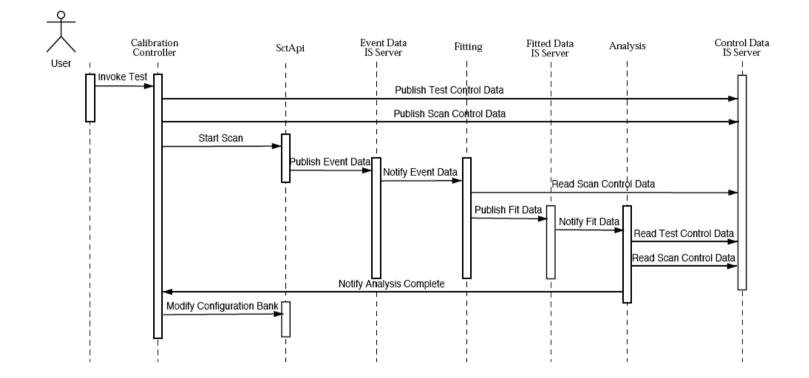

In view of improving SctRodDaq for the final system, I ran the test system, H8Testbox, to debug several versions of DSP code, for faster and on-ROD histogramming. I wrote a new package (ISTestResult) which makes all the test summaries available in IS (InformationService) under the general ATLAS software framework. The SctGui now reads this information instead of text summaries and this improved the speed of the calibration procedure significantly.

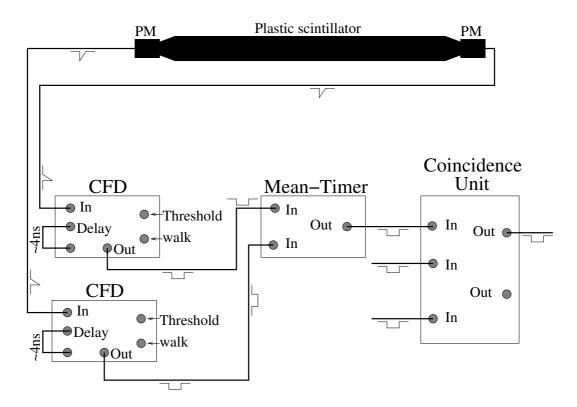

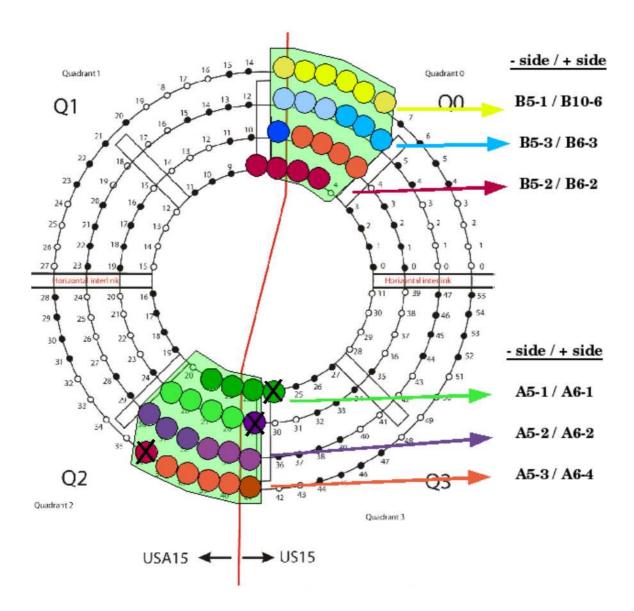

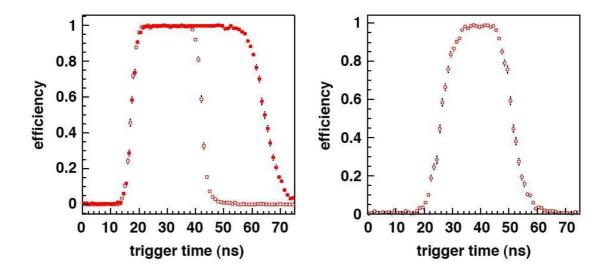

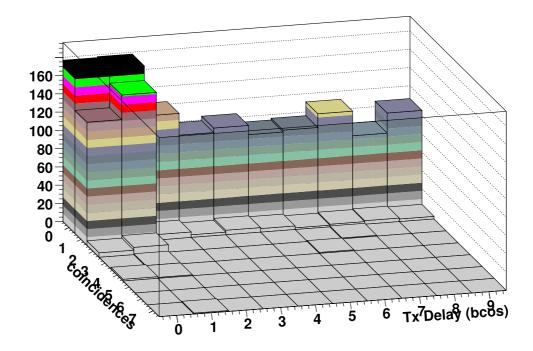

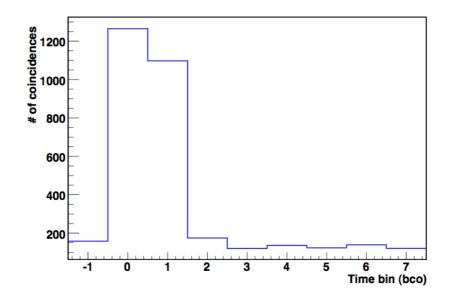

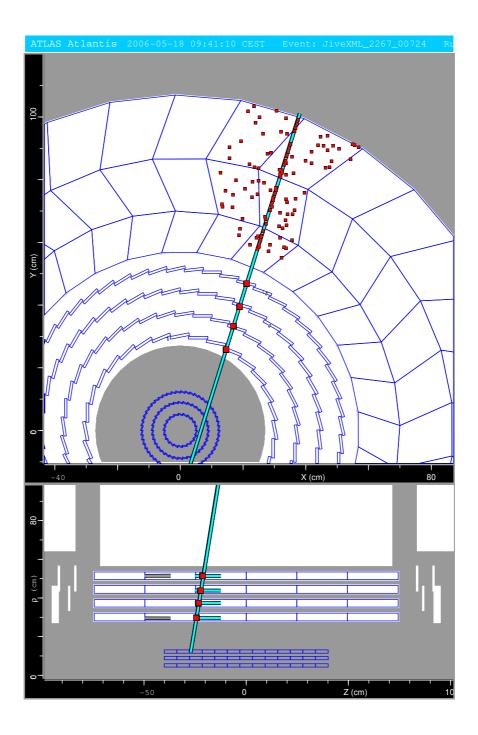

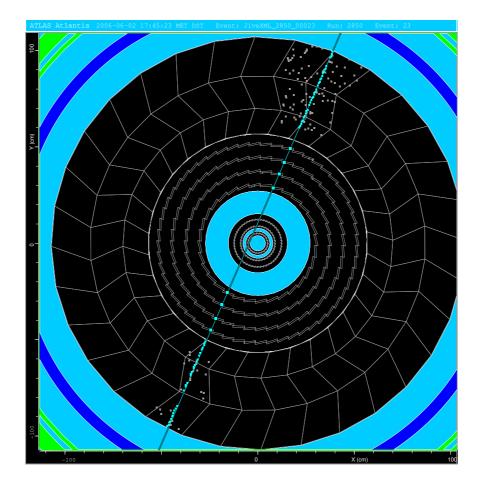

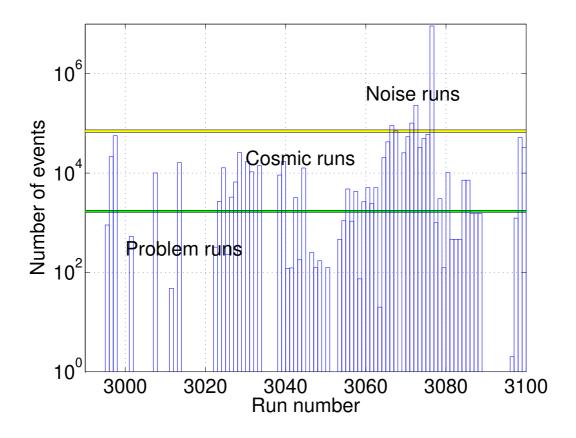

Towards the test with the TRT, I worked on combining the readout of the SCT with the general ATLAS-wide software framework and I helped setup the scintillator system for the trigger of this combined test. I wrote a dedicated DAQ to read out TDC/ADC information from the scintillators (over VME) and insert this information into the ATLAS bytestream during physics datataking, also in the same readout cycle with the SCT and the TRT. Then I setup the timing and trigger chain for the combined run, paying special attention to the distribution of the signals for the relative and absolute timing of the detectors. After working on understanding the trigger latency, I had the idea to count coincidences while scanning through trigger delay to time-in the SCT to within 5nsec. For diagnosing problems quickly during the cosmics running, I improved a light-weight bytestream converter for the online system, which decodes the information from the ATLAS readout chain so that it can highlight problematic modules, or desynchronisation problems. This new version of the bytestream converter also could plug in to the TRTviewer, which is a light-weight online event displayer for the InnerDetector, originally intended for the TRT, but was expanded later to cover the SCT. After running commissioning shifts of the SCT sectors and running cosmics, I helped debug problems experienced during the cosmics running, such as ROS (ReadOut Sub-system) memory-limitations, which is part of the ATLAS event-building hardware.

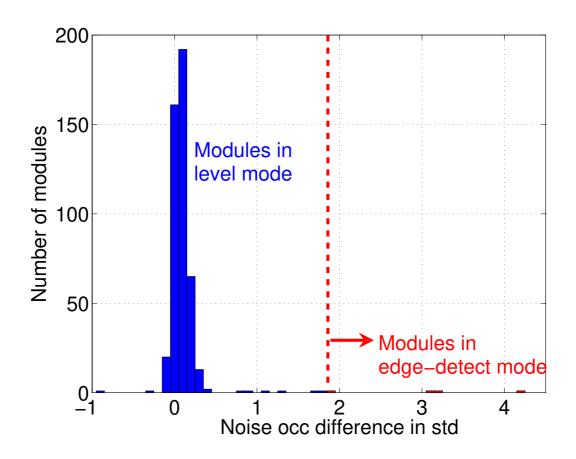

In addition to my duties with the SCT barrel commissioning, I helped debug problems during the reception testing of both of the SCT endcaps at CERN and during the cosmics running of a sector of Endcap-C. I discovered that Endcap-C had been running in the edge-mode while taking cosmics data instead of level-mode which increased the noise occupancy by ten-fold.

After the barrel cosmics, I have been working on moving my online expertise to the offline by helping the monitoring experts implement the coincidence timing histograms offline. With this method, Endcap-C was timed in. I have worked on decoding the configuration information from the online databases in the offline software to use it in the module efficiency calculations.

# Contents

| Intr | oducti                  | ion                                                                                                                                                                                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1  | LHC:                    | The Large Hadron Collider                                                                                                                                                                                                                                                                        | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2  | ATLA                    | S: A Toroidal LHC Apparatus                                                                                                                                                                                                                                                                      | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.1                   | ATLAS Coordinate Systems                                                                                                                                                                                                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.2                   | Physics Goals                                                                                                                                                                                                                                                                                    | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.3                   | Energy loss and particle identification                                                                                                                                                                                                                                                          | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.4                   | Magnet System                                                                                                                                                                                                                                                                                    | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.5                   | Inner Detector                                                                                                                                                                                                                                                                                   | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.6                   | Calorimeter System                                                                                                                                                                                                                                                                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.7                   | Muon System                                                                                                                                                                                                                                                                                      | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.8                   | Trigger and Data Acquisition System                                                                                                                                                                                                                                                              | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.2.9                   | Offline Processing                                                                                                                                                                                                                                                                               | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCI  | Г: Sem                  | i-Conductor Tracker                                                                                                                                                                                                                                                                              | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1  | Silicor                 | Detectors                                                                                                                                                                                                                                                                                        | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.1.1                   | Silicon Detectors in a radiation environment                                                                                                                                                                                                                                                     | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.1.2                   | Design requirements of the SCT module                                                                                                                                                                                                                                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.2  | SCT b                   | oarrel modules                                                                                                                                                                                                                                                                                   | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.1                   | SCT wafers                                                                                                                                                                                                                                                                                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.2                   | Radiation damage to an SCT module                                                                                                                                                                                                                                                                | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 2.2.3                   | Principle of binary read-out                                                                                                                                                                                                                                                                     | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                         |                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | 2.2.4                   | Front-end electronics                                                                                                                                                                                                                                                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 1.1<br>1.2<br>SC<br>2.1 | <ol> <li>1.1 LHC:</li> <li>1.2 ATLA</li> <li>1.2.1</li> <li>1.2.2</li> <li>1.2.3</li> <li>1.2.4</li> <li>1.2.5</li> <li>1.2.6</li> <li>1.2.7</li> <li>1.2.8</li> <li>1.2.9</li> <li>SCT: Sem</li> <li>2.1</li> <li>Silicon</li> <li>2.1.1</li> <li>2.1.2</li> <li>2.2</li> <li>SCT is</li> </ol> | 1.2       ATLAS: A Toroidal LHC Apparatus         1.2.1       ATLAS Coordinate Systems         1.2.2       Physics Goals         1.2.3       Energy loss and particle identification         1.2.4       Magnet System         1.2.5       Inner Detector         1.2.6       Calorimeter System         1.2.7       Muon System         1.2.8       Trigger and Data Acquisition System         1.2.9       Offline Processing         1.2.1       Silicon Detectors         2.1       Silicon Detectors in a radiation environment         2.1.2       Design requirements of the SCT module         2.2.1       SCT wafers         2.2.2       Radiation damage to an SCT module |

|   | 2.3 | Detect | or control and readout                     | 65  |

|---|-----|--------|--------------------------------------------|-----|

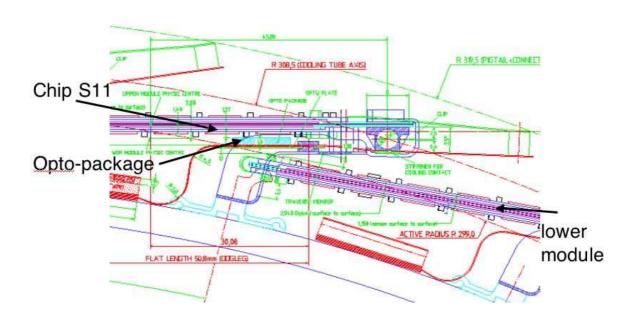

|   |     | 2.3.1  | Optical Communication with Modules         | 65  |

|   |     | 2.3.2  | Detector Control System                    | 67  |

|   |     | 2.3.3  | Off-detector readout                       | 70  |

|   |     | 2.3.4  | Configuration of the SCT system            | 78  |

| 3 | SCI | Г Barr | els: Production to Commissioning           | 85  |

|   | 3.1 | Calibr | ation of binary readout                    | 85  |

|   | 3.2 | Modul  | e Production                               | 87  |

|   | 3.3 | Macro  | -Assembly and testing at Oxford University | 90  |

|   |     | 3.3.1  | SCT Hardware                               | 92  |

|   | 3.4 | SCT (  | Online Software                            | 93  |

|   |     | 3.4.1  | TDAQ                                       | 94  |

|   |     | 3.4.2  | SctRodDaq                                  | 98  |

|   | 3.5 | Data A | Acquisition Runs                           | 105 |

|   |     | 3.5.1  | Calibration Runs                           | 105 |

|   |     | 3.5.2  | Physics Mode Runs                          | 106 |

|   |     | 3.5.3  | ATLAS Event Building and Event Format      | 107 |

|   | 3.6 | SCT C  | Calibration                                | 108 |

|   |     | 3.6.1  | SCT Scans and Tests                        | 110 |

|   |     | 3.6.2  | ModuleProbe                                | 111 |

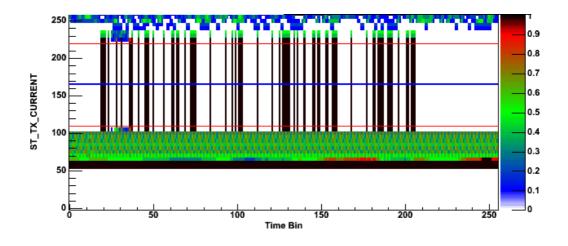

|   |     | 3.6.3  | TxCurrentTest                              | 114 |

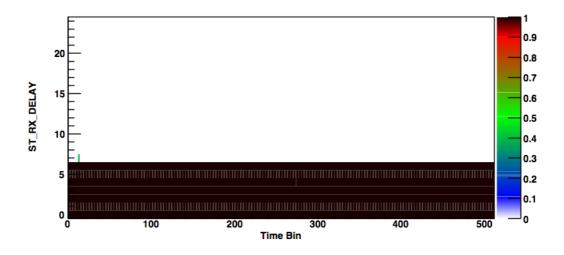

|   |     | 3.6.4  | RxDelayTest                                | 115 |

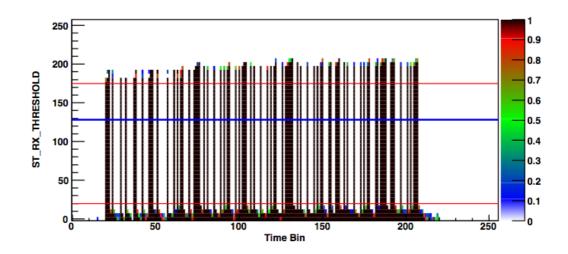

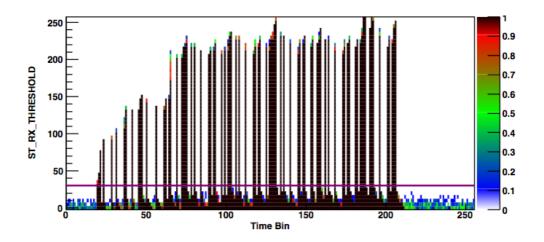

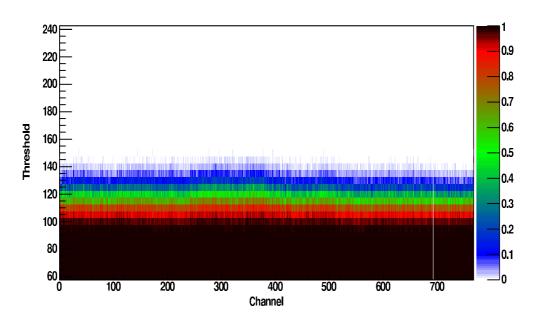

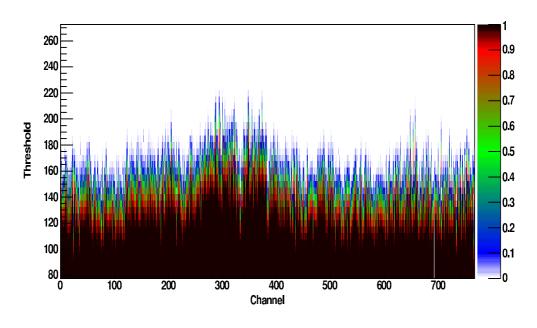

|   |     | 3.6.5  | RxThresholdTest                            | 116 |

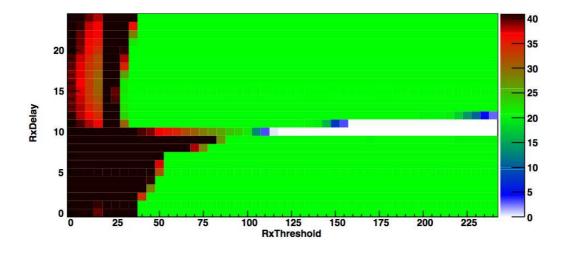

|   |     | 3.6.6  | 2D BOC Scan                                | 119 |

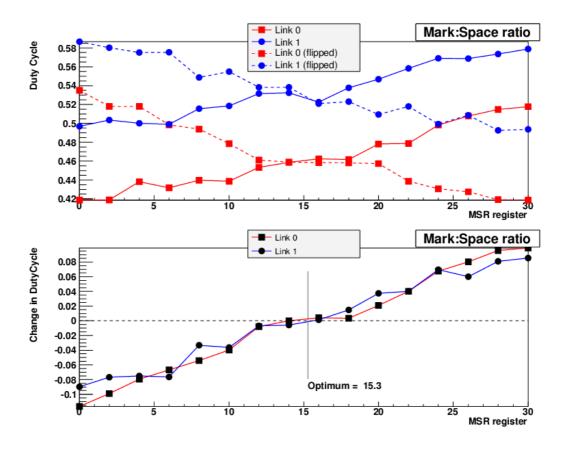

|   |     | 3.6.7  | MarkSpaceRatioTest                         | 120 |

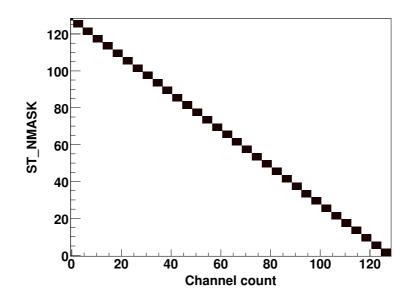

|   |     | 3.6.8  | NMaskTest                                  | 121 |

|   |     | 3.6.9  | PipelineTest                               | 122 |

|   |     | 3.6.10 | FullByPassTest                             | 123 |

|   |     | 3.6.11 | Counter Error Test                         | 124 |

|             | oendix         |                                                                                              | 213                      |

|-------------|----------------|----------------------------------------------------------------------------------------------|--------------------------|

| Cor         | clusio         | ns                                                                                           | 211                      |

| 5.4         | Resul          | ts $\ldots$ | 201                      |

| 5.3         | Physi          | cs Data Taking                                                                               | 192                      |

| 5.2         | Trigge         | r Distribution and Timing                                                                    | 184                      |

|             | 5.1.2          | Timing Results                                                                               | 181                      |

|             |                | system                                                                                       | 178                      |

|             | 5.1.1          | Measurement of the phase of the trigger with respect to the                                  |                          |

| 5.1         | Descr          | iption of the Cosmic Setup                                                                   | 171                      |

| $\cos$      | mic Te         | ests of the ATLAS Inner Detector Barrels                                                     | 171                      |

|             | 4.1.3          | The SCT IS servers for the conditions database                                               | 166                      |

|             | 4.1.2          | SCT DAQ Conditions Database                                                                  | 165                      |

|             | 4.1.1          | SCT Conditions Databases                                                                     | 164                      |

| 4.1         | Imple          | ementation of a realistic detector                                                           | 163                      |

| SC          | Г Cond         | litions Database                                                                             | 163                      |

| <b>J</b> .0 | Darrer         |                                                                                              | 107                      |

| 3.8         |                | Synchronous Triggers Noise Test      Test Results                                            | $151 \\ 157$             |

|             | 3.7.7<br>3.7.8 | Double Trigger Noise Test         Symphronous Triggers Noise Test                            | $149 \\ 151$             |

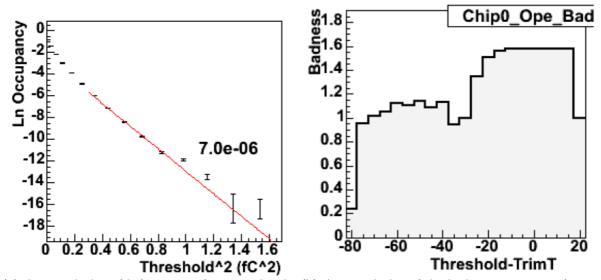

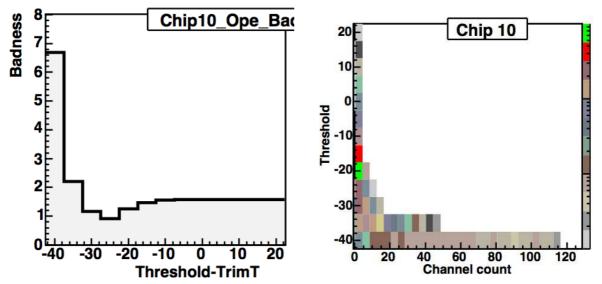

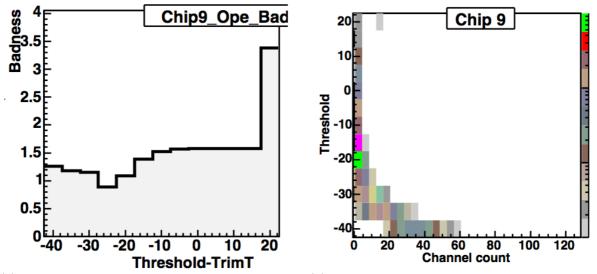

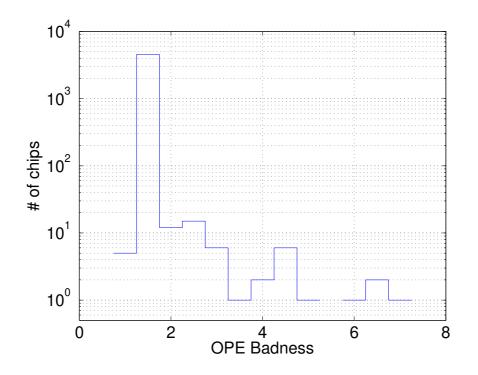

|             | 3.7.6          | Noise Occupancy Test and Occupancy Per Event (OPE)                                           | 146                      |

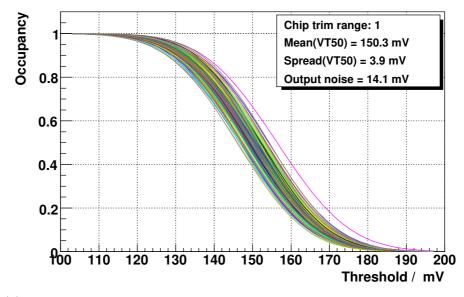

|             | 3.7.5          | TrimRange                                                                                    | 142                      |

|             | 3.7.4          | Response Curve                                                                               | 135                      |

|             | 3.7.3          | Three Point Gain Test                                                                        | 131                      |

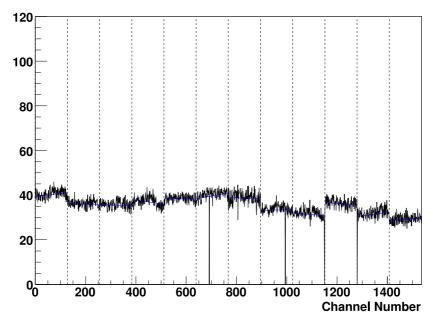

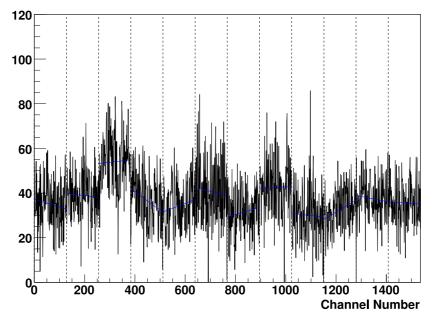

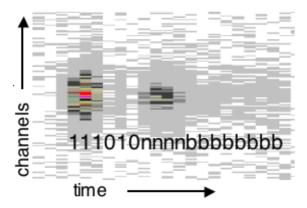

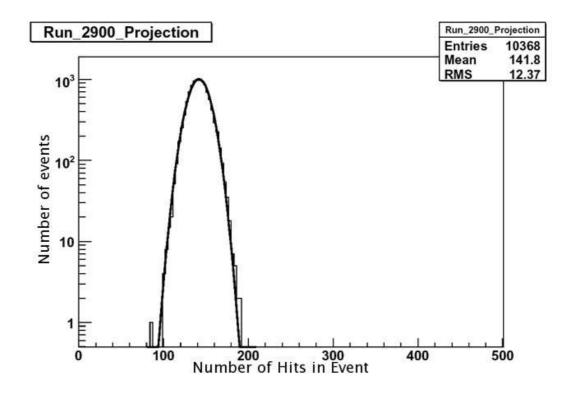

|             | 3.7.2          | Occupancy per Event                                                                          | 128                      |

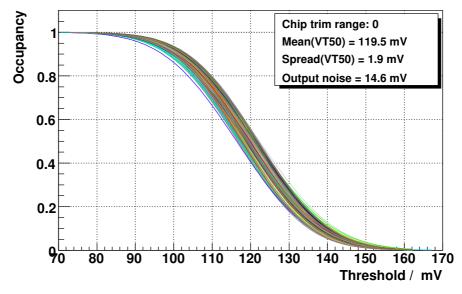

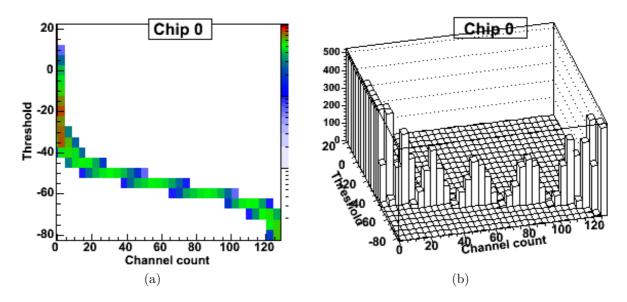

|             | 3.7.1          | Threshold scans                                                                              | 127                      |

| 3.7         |                | g Tests                                                                                      |                          |

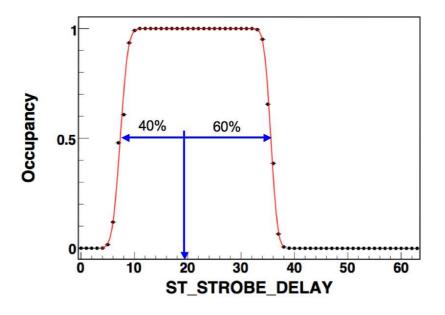

|             | 3.6.12         | Strobe Delay Test                                                                            | 124                      |

| 37          | 7              |                                                                                              | 3.6.12 Strobe Delay Test |

# List of Figures

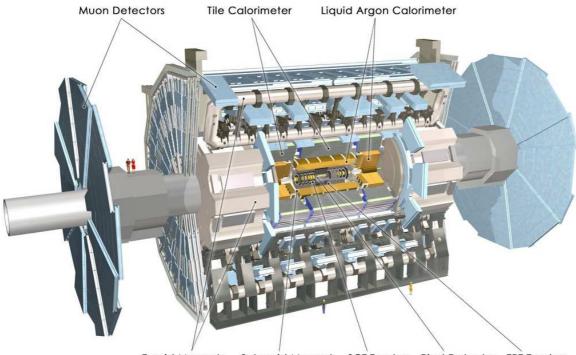

| 1-1 | A schematic drawing of the ATLAS detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

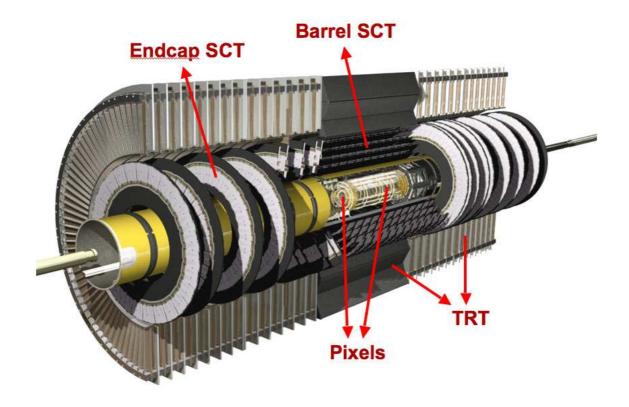

| 1-2 | A 3-dimensional cut-away view of the ATLAS inner detector. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34 |

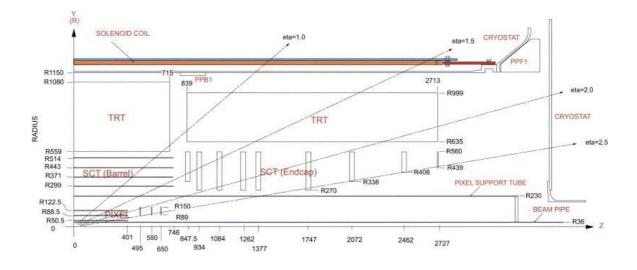

| 1-3 | Position and $\eta$ -coverage of the inner detector components, [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

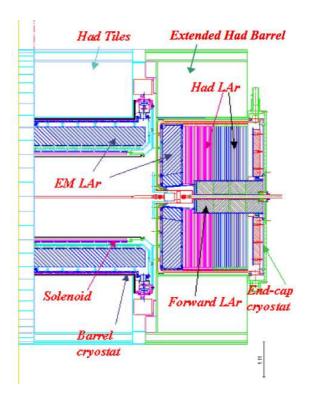

| 1-4 | A cutaway of one half of the calorimeter system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 42 |

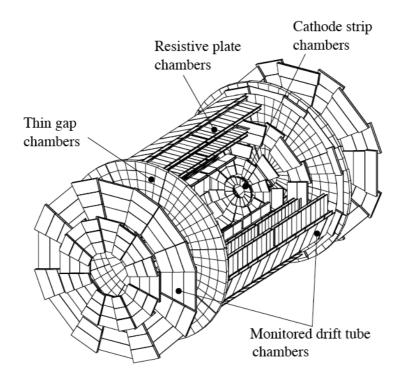

| 1-5 | A cutaway view of the 3 barrel layers and 3 wheels of each end-cap. $% \left( {{{\rm{A}}_{{\rm{A}}}}_{{\rm{A}}}} \right)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44 |

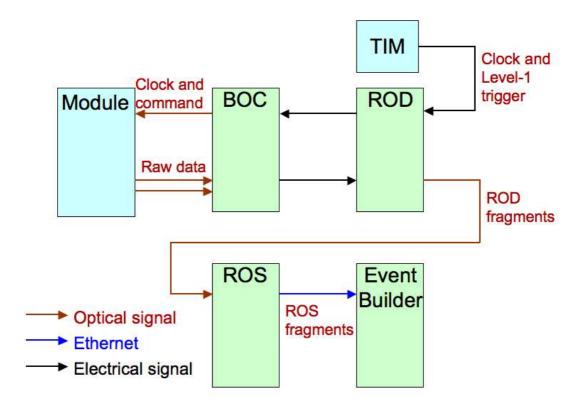

| 1-6 | Timing and trigger distribution to the SCT modules and ATLAS read-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|     | out schema.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47 |

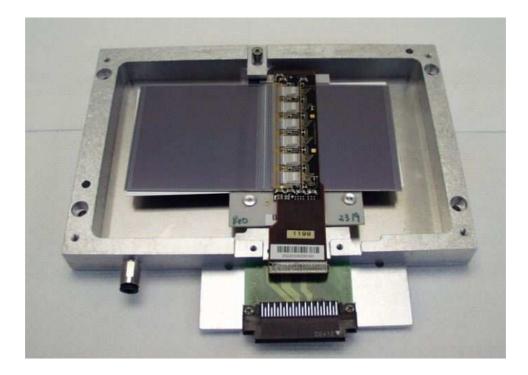

| 2-1 | A barrel module shown in a test-box with a test connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53 |

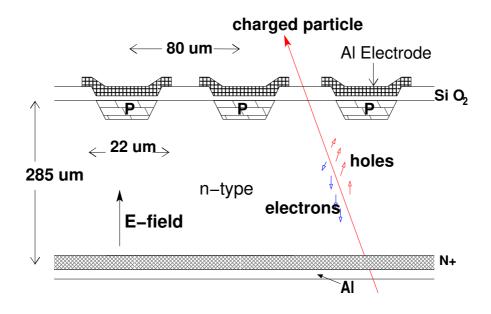

| 2-2 | A schematic cross-section of an SCT sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55 |

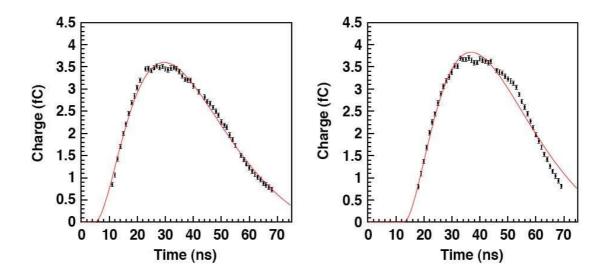

| 2-3 | The reconstructed pulse shape due to beam particles from the test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|     | beam for a non-irradiated and an irradiated module. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57 |

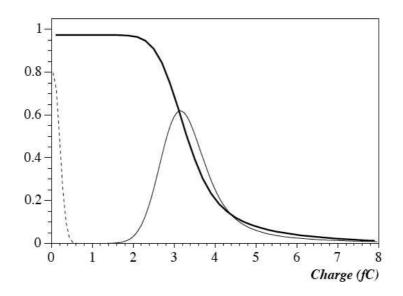

| 2-4 | Noise distribution and Landau charge deposit distribution for a MIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|     | at normal incidence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

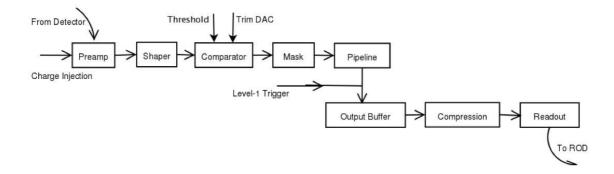

| 2-5 | Signal processing chain within the ABCD chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62 |

| 2-6 | Different chip by-passing schemes for normal and modified modules $% \left( {{{\left( {{{{{{}}}} \right)}}}} \right)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66 |

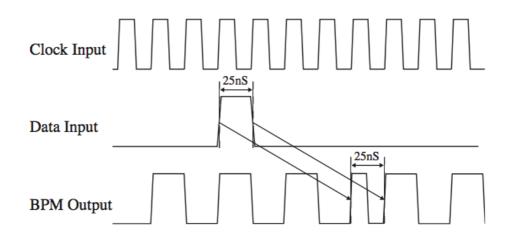

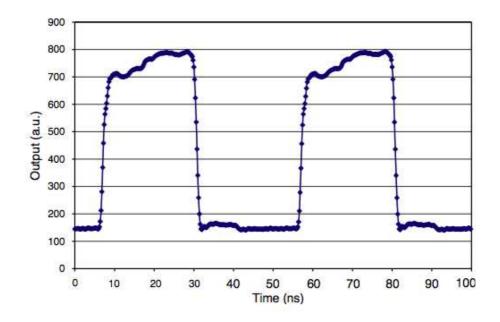

| 2-7 | The principle of bi-phase mark<br>(BPM) encoding. $\hfill \hfill \ldots \hfill $ | 67 |

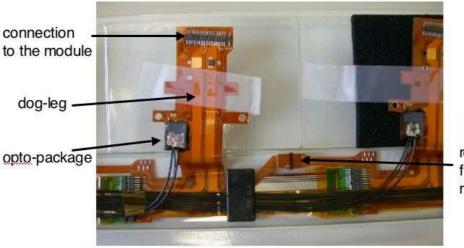

| 2-8 | A photo of two Low Mass Tapes and doglegs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

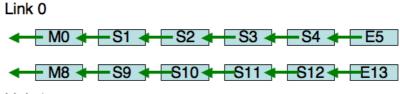

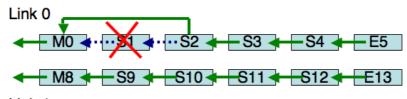

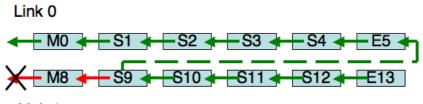

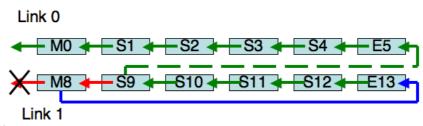

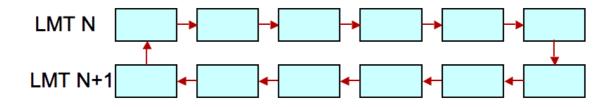

| 2-9 | Schematic drawing of a clockwise TX redundancy loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80 |

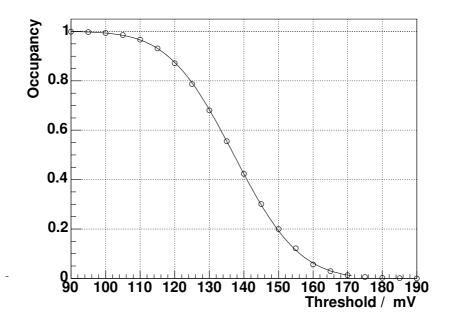

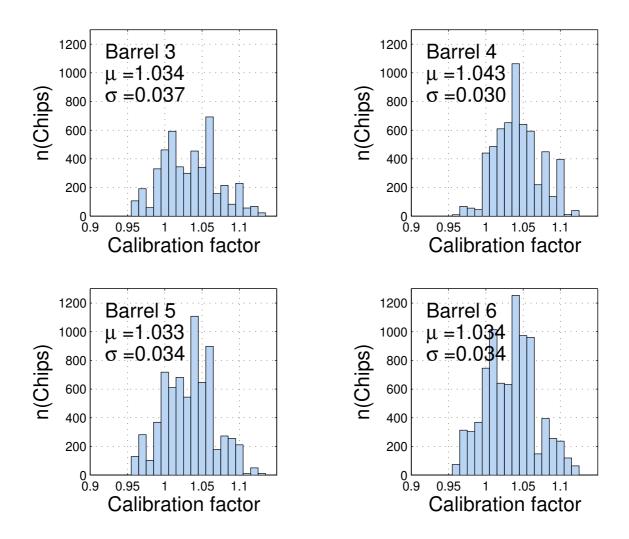

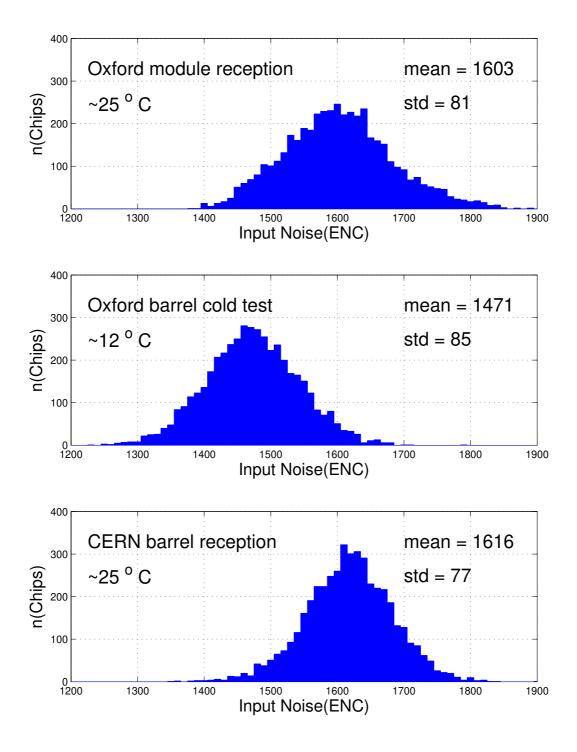

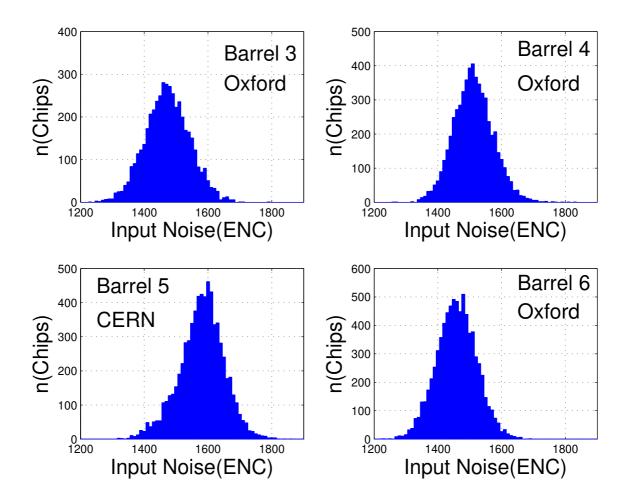

| 3-1 | Occupancy as a function of front-end discriminator threshold. $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 86 |