## Continuous-Time Delta-Sigma A/D Converters for High Speed Applications

by

### **Omid Shoaei**

A thesis submitted to the Faculty of Graduate Studies and Research in partial fulfilment of the requirements for the degree of Doctor of Philosophy

> Carleton University © Omid Shoaei 1995

The undersigned hereby recommend to the Faculty of Graduate Studies and Research acceptance of the thesis,

### "Continuous-Time Delta-Sigma A/D Converters for High Speed Applications"

submitted by

**Omid Shoaei**

in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Chair, Department of Electronics

Thesis Supervisor

External Examiner

Carleton University November, 29, 1995

### Abstract

This is a thesis about implementation of a  $\Delta\Sigma$  modulator with continuous-time techniques. A methodology to obtain proper continuous-time (*s*-domain) transfer functions for a continuous-time  $\Delta\Sigma$  modulator has been presented. Different classes of continuous-time modulators based on the DAC waveform in the  $\Delta\Sigma$  loop and the number of digital delays in the feedback loop have been recognized and analyzed. A new structure for the LC-based  $\Delta\Sigma$  modulators has been proposed. A fourth-order transconductor-*C* modulator has been implemented in a 0.8µm BiCMOS technology. Advantages and drawbacks of continuous-time modulators particularly with transconductor-*C* technique have been investigated. A new transconductor-*C* filter and further work are recommended to improve the performance of the current modulator.

### Acknowledgments

I would like to take this opportunity to thank those who have made the last four years of my life a memorable and unforgettable experience.

To Martin Snelgrove, my supervisor: Thanks for your support, for your intelligent guidance, for your valuable comments when I needed them most. Above of all, for giving me the opportunity to go to BNR and Northern Telecom and have a good taste of what a high-tech company is about. A few words can not express the extent to which I am indebted to your positive influence.

To Calvin Plett: Thanks for discussions during the period of designing the circuit for my  $\Delta\Sigma$  loop filter.

To high-speed lab folks: Thanks to Theo Varelas for assistance during the process of laying out my chips, thanks to Seyfollah Bazarjani for comments during design and layout of my circuit and thanks to Luc Lussier and Philip Lauzon for laying out test boards for me.

To Ayal Shoval: Thanks for discussion on your chip for making up a prototype  $\Delta\Sigma$  modulator.

To Northern Telecom and BNR: Thanks for providing me facilities over a period of one year for layout and simulations and for the fabrication of various test chips.

For Financial supports: Thanks to OCRI/NSERC chair held by Martin Snelgrove, window grant from BNR, Micronet and Ministry of Culture and Higher Education of Iran.

To my parents: Thanks for your love, support and motivation.

Finally and especially to my wife, Zahra Morovat: Thanks for your love, care and understanding. Thanks for being a good mother and sometimes even a father for my daughters Fatemeh and Neda when I couldn't perform my responsibilities as a father during last four years.

# **Table of Contents**

| Table of Contents                                                                                   | v             |

|-----------------------------------------------------------------------------------------------------|---------------|

| List of Figures                                                                                     | ix            |

| List of Tables                                                                                      | xiv           |

| List of Symbols                                                                                     | XV            |

| 1 Introduction                                                                                      | 1             |

| 1.1 Analog-to-Digital Conversion                                                                    | 1             |

| 1.2 Contributions                                                                                   | 3             |

| 1.3 Organization of the Thesis                                                                      | 4             |

| 2 Overview of Delta-Sigma Modulator                                                                 | 6             |

| 2.1 Continuous-time Delta-Sigma Modulator                                                           | 7             |

| 2.2 Bandpass Delta-Sigma Modulator                                                                  | 9             |

| 2.3 Stability in a Delta-Sigma Modulator                                                            | 12            |

| 2.3.1 Quasi-linear Loop Gain                                                                        | 12            |

| 2.3.2 BIBO or One-norm Criterion                                                                    | 14            |

| 2.3.3 Two-norm Criterion                                                                            | 15            |

| 2.4 Summary                                                                                         | 20            |

| 3 Continuous-Time Delta-Sigma Modulator Transfer Funct sign                                         | ion De-<br>21 |

| 3.1 Transformation of a Discrete-Time Delta-Sigma Modulator to a Cont<br>Time Delta-Sigma Modulator |               |

| 3.1.1 NRZ Transformation                                                                            | 25            |

| 3.1.2 RZ and HZ Transformation                                                                      | 34            |

| 3.1.3 NRZ and RZ Transformations in State Space Form                                                | 37            |

| 3.1.4 Zero-Delay Scheme                                                                             |               |

| 3.1.5 The Sensitivity of a Continuous-time $\Delta\Sigma$ Modulator to U Loop Delays |                |

|--------------------------------------------------------------------------------------|----------------|

| 3.1.6 Simulation of $\Delta\Sigma$ Extra Loop Delay                                  | 51             |

| 3.1.7 The Signal Transfer Function                                                   | 53             |

| 3.2 Implicit Anti-alias (Image) Filtering                                            | 58             |

| 3.3 Simulation Results                                                               | 67             |

| 3.3.1 Signal-to-Noise Ratio                                                          | 67             |

| 3.3.2 Anti-alias Filtering Simulation                                                | 68             |

| 3.4 Summary                                                                          | 71             |

| Multi-Feedback (Pulse Shaping) Design for LC Bandpa                                  | ass Delta-Sig- |

#### 4 ma Modulator 72

| 4.1 An LC Delta-Sigma Modulator | 72 |

|---------------------------------|----|

| 4.2 Multi-Feedback Design       | 75 |

| 4.2.1 DAC Pulse Shaping         | 77 |

| 4.2.2 Signal Transfer Function  | 82 |

| 4.3 Simulation Results          | 83 |

| 4.4 Summary                     | 84 |

#### 5 Transconductor-C Filter Design for Continuous-Time Delta-Sigma 86 **Modulator**

| 5.1 Transconductor-C Filters                                             | 86  |

|--------------------------------------------------------------------------|-----|

| 5.1.1 A Generic Transconductor-C Biquad (second-order) Filter            | 87  |

| 5.1.2 Resonator with Infinite Q                                          | 89  |

| 5.2 Filter Architecture                                                  | 90  |

| 5.3 Sensitivity to the Loop Filter Parameters (Q and Resonant Frequency) | 93  |

| 5.4 Transconductor-C-Amplifier Devices                                   | 96  |

| 5.4.1 Transconductor-C-Amplifier Biquad                                  | 98  |

| 5.4.2 A BiCMOS Differential Transconductor                               | 100 |

| 5.4.3 The Second-Stage Amplifier                                         | 102 |

| 5.4.4 Excess Phase Cancellation                                          | 103 |

| 5.4.5 Small Signal Analysis                             | 109 |

|---------------------------------------------------------|-----|

| 5.4.6 Non-linearity Analysis                            | 113 |

| 5.4.6.1 Input-stage BiCMOS Transconductor Non-linearity | 114 |

| 5.4.6.2 Open-Loop Transconductor Simulations            | 118 |

| 5.4.6.3 The Second-stage Amplifier Non-linearity        | 119 |

| 5.4.6.4 Closed-loop Transconductor Simulations          | 125 |

| 5.4.6.5 Two-tone Intermodulation Simulation             | 126 |

| 5.5 A Practical Fourth-order $\Delta\Sigma$ Modulator   | 126 |

| 5.5.1 Loop Filter Center Frequency Control              | 127 |

| 5.5.2 $\Delta\Sigma$ Modulator Loop Components          | 129 |

| 5.5.2.1 Multi-input Transconductors                     | 129 |

| 5.5.2.2 Two-level DAC                                   | 130 |

| 5.5.2.3 Latched Comparator and D-flip flop              | 130 |

| 5.5.3 The TC-amp $\Delta\Sigma$ Modulator Simulated SNR | 131 |

| 5.6 Summary                                             | 133 |

|                                                         |     |

### 6 Testing of a Prototype Second-Order Bandpass Delta-Sigma Modulator 134

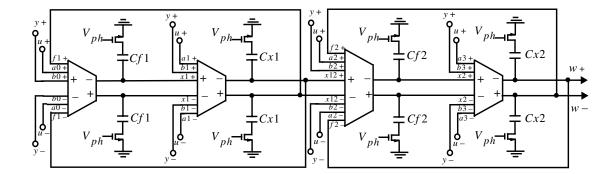

| 6.1 Modulator Implementation         | 134 |

|--------------------------------------|-----|

| 6.2 Automatic Tuning                 | 136 |

| 6.3 Experimental Results             | 138 |

| 6.3.1 Signal-to-Noise Ratio (SNR)    | 138 |

| 6.3.2 Linearity                      | 139 |

| 6.3.3 Anti-alias (Image) Performance | 141 |

| 6.3.4 ΔΣ NTF Notch Frequency Control | 142 |

| 6.4 Summary                          | 143 |

|                                      |     |

# 7 Circuit Noise and Power Considerations 145

| 7.1 Noise Analysis for the Transconductor-amp-C Integr | rator145 |

|--------------------------------------------------------|----------|

| 7.1.1 Cascode Active Load                              | 146      |

| Appendix D: Discrete-time to continuous-time state space transition              |                |

|----------------------------------------------------------------------------------|----------------|

| Appendix C: The TC-amp circuit small signal analysis                             | 200            |

| Appendix B: Signal transfer function                                             | 197            |

| Appendix A: Multiple-pole transformation                                         | 193            |

| References                                                                       | 187            |

| 8.5 Future Work                                                                  | 184            |

| 8.4 Clock Jitter Effects                                                         | 180            |

| 8.3.3 Common-Mode Problem in the First Stage Transconductors                     | 176            |

| 8.3.2 High Loop Propagation Delay Time                                           | 174            |

| 8.3.1 Low-Q at Working Speed                                                     | 174            |

| 8.3 Problems in ZA09 and ZA14 Parts                                              | 174            |

| 8.2.2 $\Delta\Sigma$ Modulator Results                                           | 171            |

| 8.2.1 Biquad Filter Results                                                      | 171            |

| 8.2 ZA14 Results                                                                 |                |

| 8.1.3 $\Delta\Sigma$ Modulator Results                                           |                |

| 8.1.2 Biquad Filter Results                                                      |                |

| 8.1.1 Layout Plot                                                                |                |

| 8.1 ZA09 Results                                                                 |                |

| 8 Testing Results of the Monolithic Modulators and Filters w<br>ture Suggestions | ith Fu-<br>162 |

| 7.5 Summary                                                                      | 161            |

| 7.4 Regular Transconductor-C Design                                              |                |

| 7.3 Comparison of Different Designs                                              | 153            |

| 7.2 Power Minimization and CM feedback                                           | 150            |

| 7.1.3 Input NMOS Triode-Mode Devices                                             | 148            |

| 7.1.2 Bipolar Cascode Transistor                                                 | 148            |

# **List of Figures**

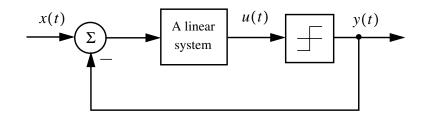

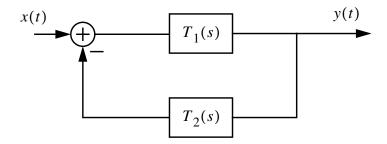

| Figure 2.1: A general $\Delta\Sigma$ modulator                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

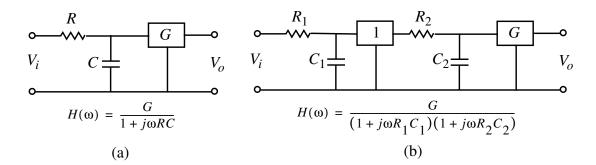

| Figure 2.2: The modulator loop filters used in [Ino63] with their transfer functions, (a) single-integrator, and (b) double-integrator                                                                                                                                     |

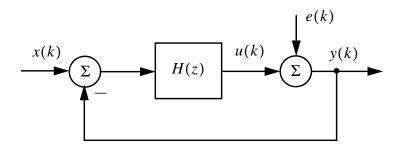

| Figure 2.3: The general linear model for a $\Delta\Sigma$ modulator                                                                                                                                                                                                        |

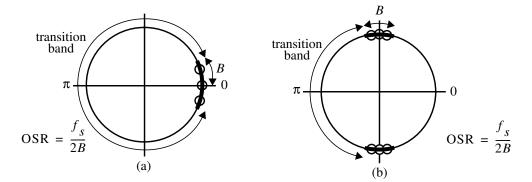

| Figure 2.4: The frequency mapping produced by the $z^{-1} \rightarrow -z^{-2}$ transformation, the <i>NTF</i> zeros and the band of interest <i>B</i> in (a) lowpass and (b) bandpass modulators                                                                           |

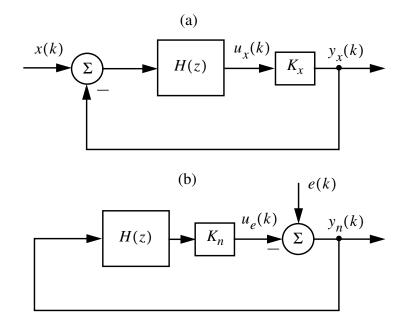

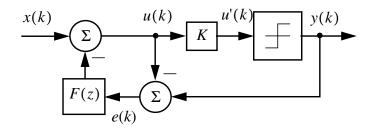

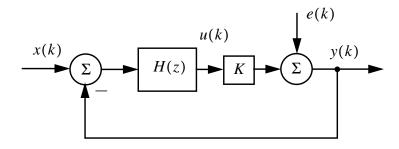

| Figure 2.5: (a) Linearized system for the input signal to modulator, (b) equivalent system for quantization noise                                                                                                                                                          |

| Figure 2.6: A $\Delta\Sigma$ modulator with a positive gain element in front of the quantizer14                                                                                                                                                                            |

| Figure 2.7: A general $\Delta\Sigma$ modulator with linearized quantizer model16                                                                                                                                                                                           |

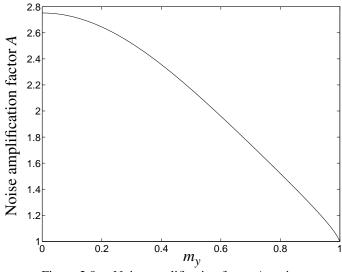

| Figure 2.8: Noise amplification factor A against $m_y$                                                                                                                                                                                                                     |

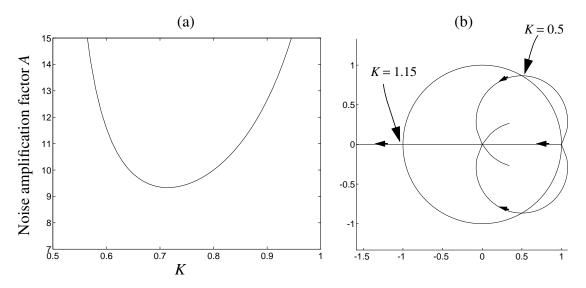

| Figure 2.9: (a) Noise amplification factor A versus K for a third-order multiple-pole lowpass modulator, (b) $NTF_K(z)$ root locus versus K                                                                                                                                |

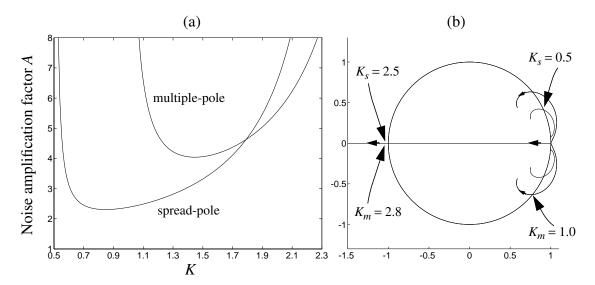

| Figure 2.10: (a) Noise amplification factor A versus K for a modified third-order multiple-pole lowpass modulator and a spread-pole design, (b) $NTF_K(z)$ root locus versus K, where $K_m$ stands for multiple-pole (outer curve) and $K_s$ for spread-pole (inner curve) |

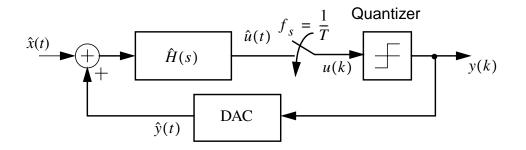

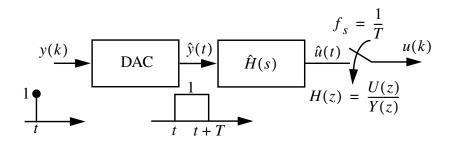

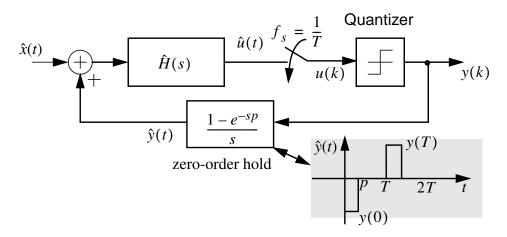

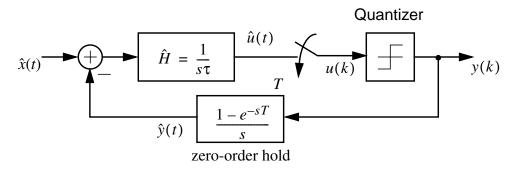

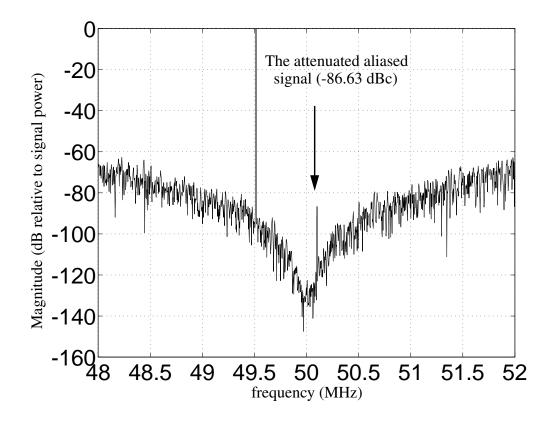

| Figure 3.1: A continuous-time $\Delta\Sigma$ modulator                                                                                                                                                                                                                     |

| Figure 3.2: $\Delta\Sigma$ open loop block diagram                                                                                                                                                                                                                         |

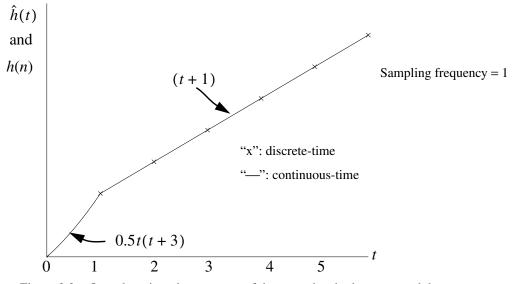

| Figure 3.3: Open-loop impulse response of the second-order lowpass modulator23                                                                                                                                                                                             |

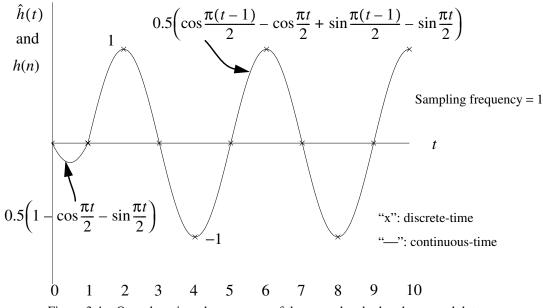

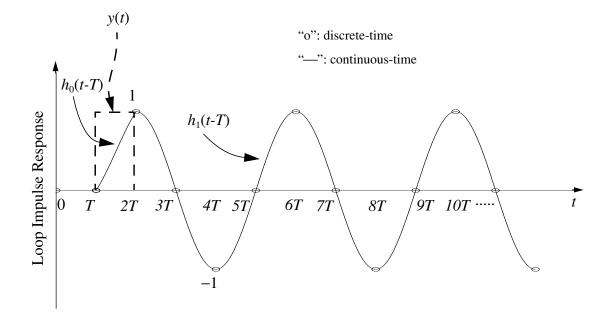

| Figure 3.4: Open-loop impulse response of the second-order bandpass modulator23                                                                                                                                                                                            |

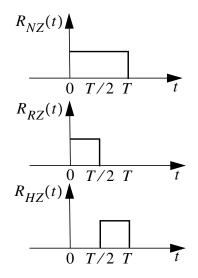

| Figure 3.5: NRZ, RZ, and HZ DAC feedback impulse responses24                                                                                                                                                                                                               |

| Figure 3.6: A continuous-time $\Delta\Sigma$ modulator                                                                                                                                                                                                                     |

| Figure 3.7: A first-order continuous-time $\Delta\Sigma$ modulator                                                                                                                                                                                                         |

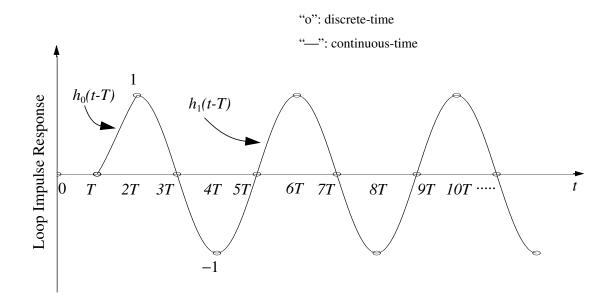

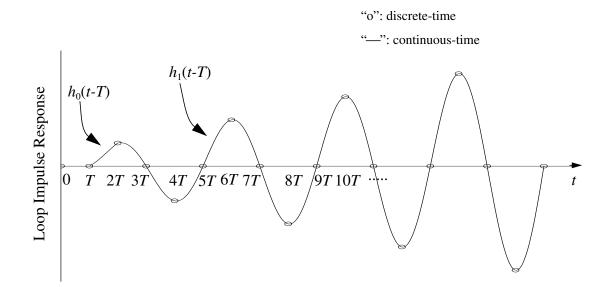

| Figure 3.8: Open-loop impulse response of the one-delay scheme second-order bandpass modulator                                                                                                                                                                             |

| Figure 3.9: Open-loop impulse response of the one-delay scheme fourth-order bandpass modulator                                                                                                                                                                             |

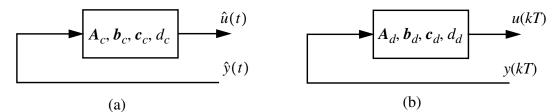

| Figure 3.10: (a) A continuous-time loop filter and (b) a discrete-time loop filter equivalent shown by their state-space parameters                                                                                                                                        |

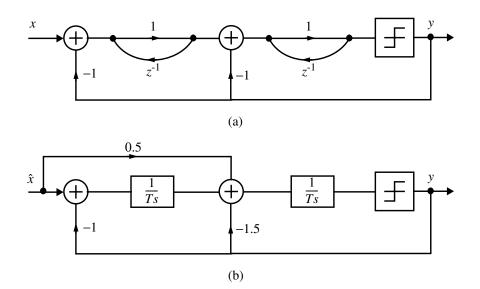

| Figure 3.11: State-space diagram of (a) a discrete-time and (b) a continuous-time second-order lowpass modulators                                                                                                                                                          |

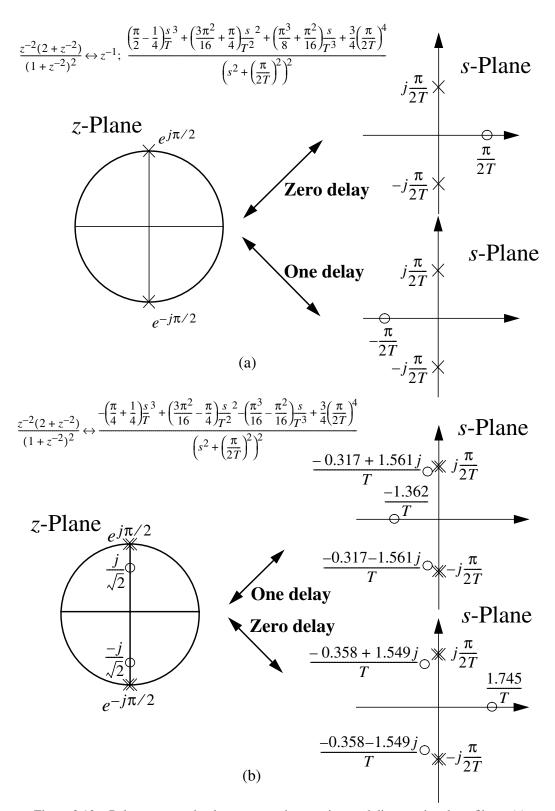

| Figure 3.12: Pole-zero mapping between continuous-time and discrete-time loop filters, (a) second-order loop, (b) multiple-pole fourth-order loop41                                                                                                                        |

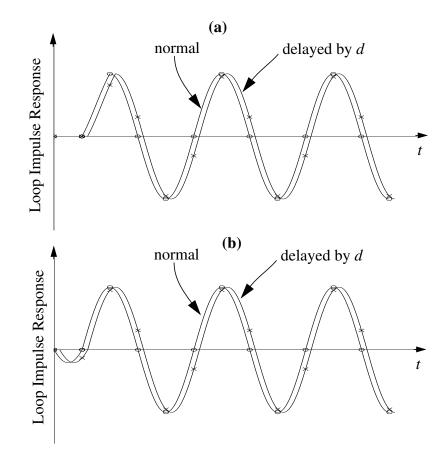

| Figure 3.13: The effect of an extra loop delay on the loop samples in the a) one-delay b) zero-delay schemes of the second-order bandpass modulators42                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

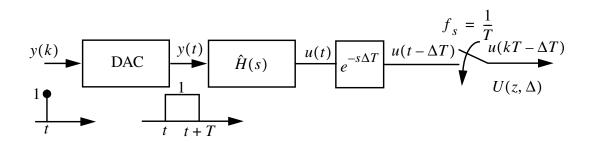

| Figure 3.14: A continuous-time $\Delta\Sigma$ open loop block diagram with an extra loop delay                                                                                                                         |

| Figure 3.15: Open-loop impulse response of the one-delay scheme second-order bandpass modulator                                                                                                                        |

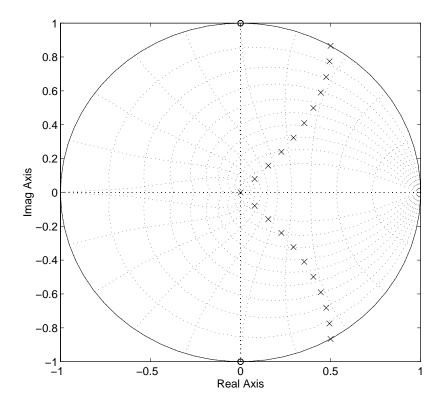

| Figure 3.16: The root-locus of the continuous-time second-order bandpass modulator with loop delay respect to <i>m</i>                                                                                                 |

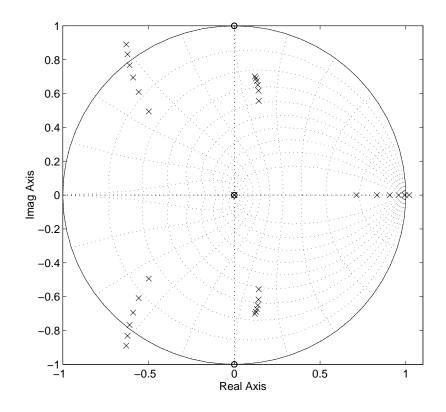

| Figure 3.17: The root-locus of the continuous-time fourth-order multiple-pole bandpass modulator with loop delay respect to <i>m</i>                                                                                   |

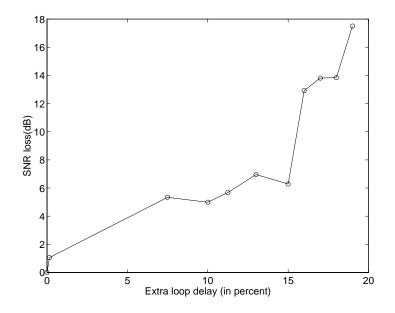

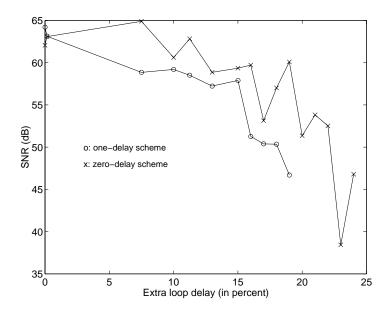

| Figure 3.18: <i>SNR</i> loss in a 2MHz bandwidth respect with extra loop delay percentage $(d/T)$ , where <i>T</i> is a clock period                                                                                   |

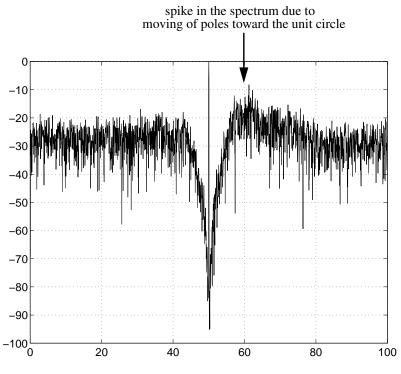

| Figure 3.19: The noise-shaping spectrum for a 19% extra loop delay52                                                                                                                                                   |

| Figure 3.20: SNR in both one-delay and zero-delay schemes for a 2MHz bandwidth respect with extra loop delay percentage $(d / T)$ , where T is a clock period                                                          |

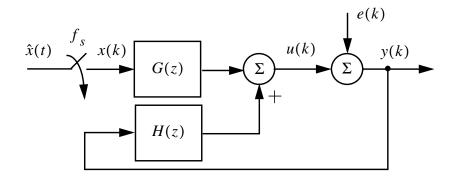

| Figure 3.21: Discrete-time delta-sigma modulator with linearized quantizer model ( <i>G</i> and <i>H</i> transfer functions share poles)                                                                               |

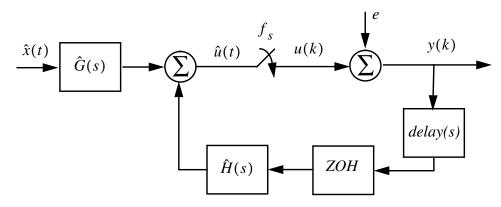

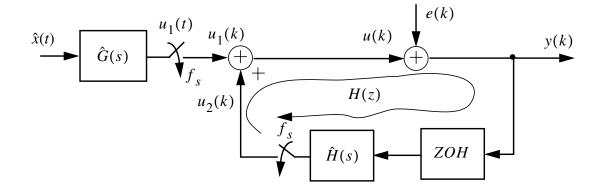

| Figure 3.22: Continuous-time $\Delta\Sigma$ modulator, equivalent to the discrete-time modulator shown in Fig. 3.21                                                                                                    |

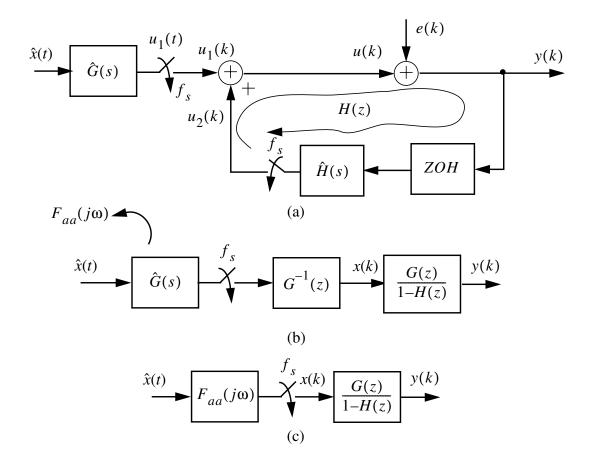

| Figure 3.23: (a) One representation of a continuous-time modulator (b) another arrangement of Fig. 3.23a, and (c) the equivalent discrete-time modulator with an extra input filter shown by $F_{aa}(j\omega)$         |

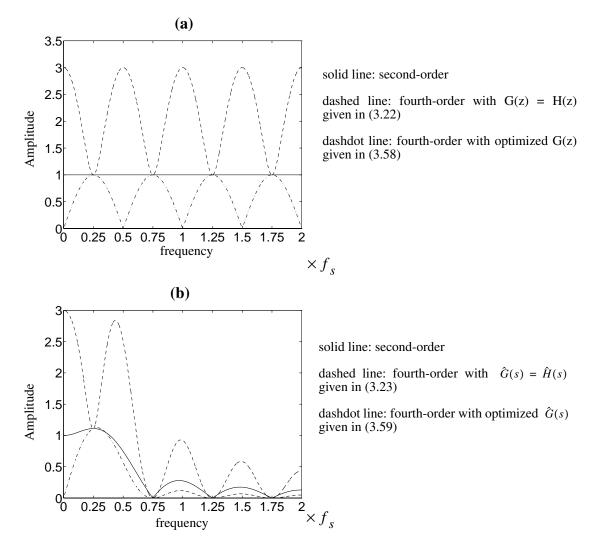

| Figure 3.24: (a) Discrete-time and (b) continuous-time <i>STFs</i> for the three examples61                                                                                                                            |

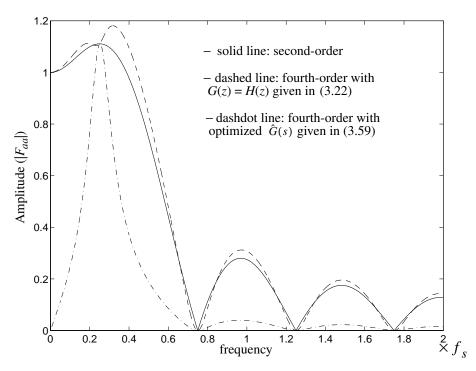

| Figure 3.25: The implicit anti-alias filter frequency response in the three continuous-<br>time examples                                                                                                               |

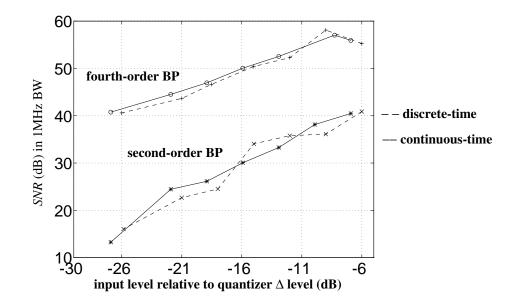

| Figure 3.26: (a) Simulation results of discrete-time and continuous-time modulators derived by the NRZ pulse invariant transformation for a fourth and a second order modulators ( $f_{in} = 20$ MHz and BW = 1 MHz)67 |

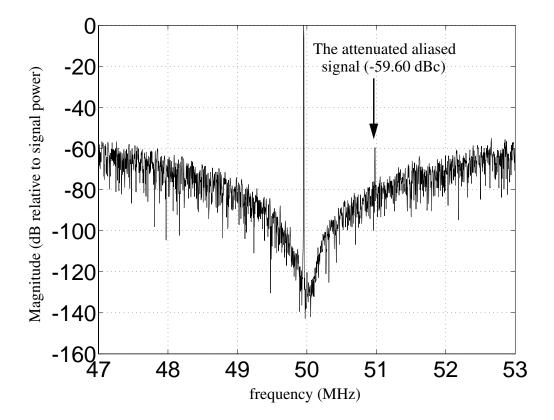

| Figure 3.27: Anti-alias filtering simulation of the multiple-pole fourth-order system (3.23). $f_{in} = 49.95$ MHz and a single tone aliasing signal at $f = 149.02$ MHz                                               |

| Figure 3.28: Anti-alias filtering simulation of the multiple-pole fourth-order system (3.23). $f_{in} = 49.51$ MHz and a single tone aliasing signal at $f = 149.90$ MHz70                                             |

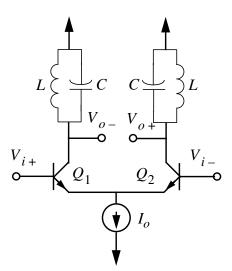

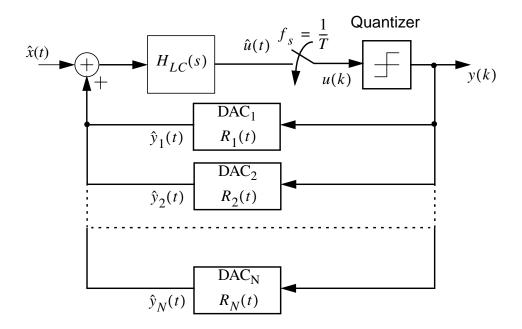

| Figure 4.1: A generic bandpass continuous-time $\Delta\Sigma$ modulator                                                                                                                                                |

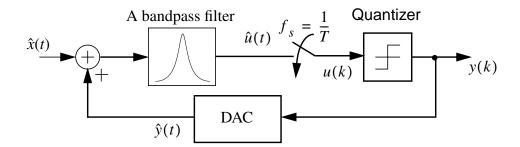

| Figure 4.2: A differential LC resonator                                                                                                                                                                                |

| Figure 4.3: A multi-feedback representation of a LC modulator                                                                                                                                                          |

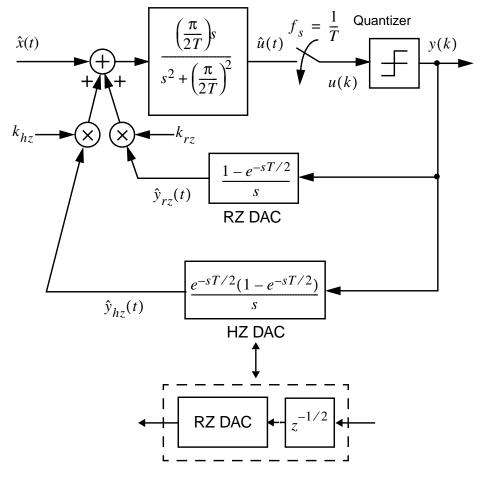

| Figure 4.4: A second-order multi-feedback (RZ and HZ) $\Delta\Sigma$ modulator with a LC resonator loop filter                                                                                                         |

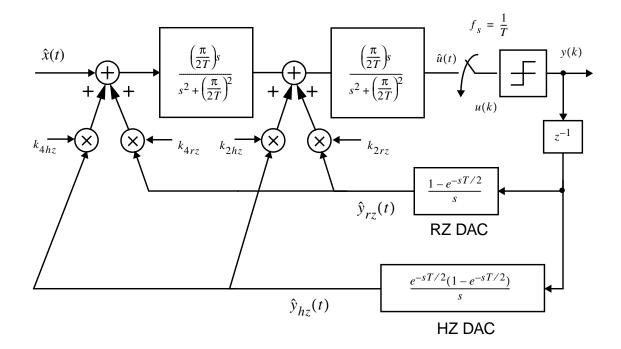

| Figure 4.5: A fourth-order multi-feedback (RZ and HZ) $\Delta\Sigma$ modulator with cascade of two LC resonator loop filters                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

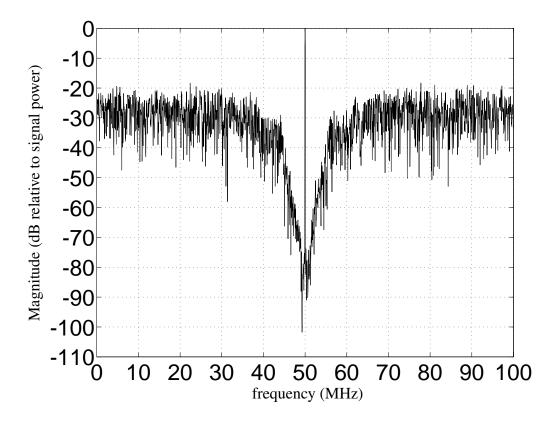

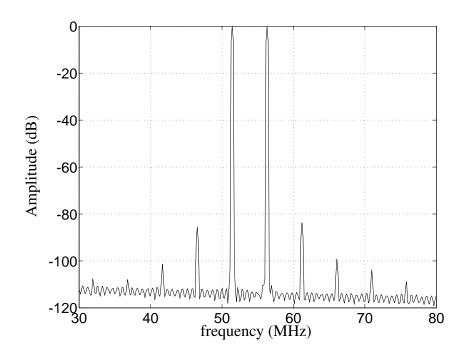

| Figure 4.6: The bit stream spectrum of simulated 4th-order LC modulator (input frequency is at 50MHz)                                                                                                                                    |

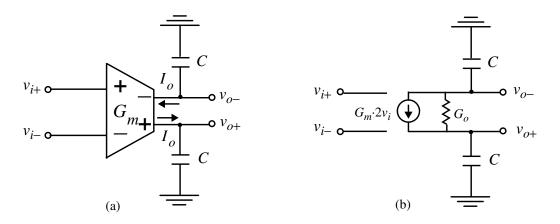

| Figure 5.1: (a) A simple Transconductor-C Integrator, (b) a model for the TC integrator in (a)                                                                                                                                           |

| Figure 5.2: A transconductor-C resonator (a) single-ended (b) differential                                                                                                                                                               |

| Figure 5.3: A transconductor-C resonator with Q enhancement                                                                                                                                                                              |

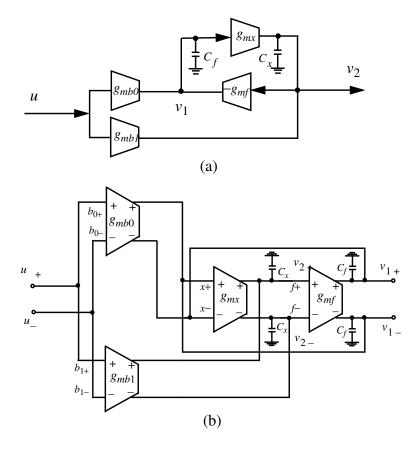

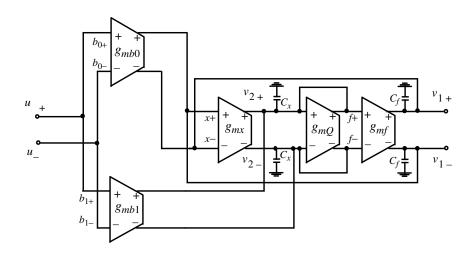

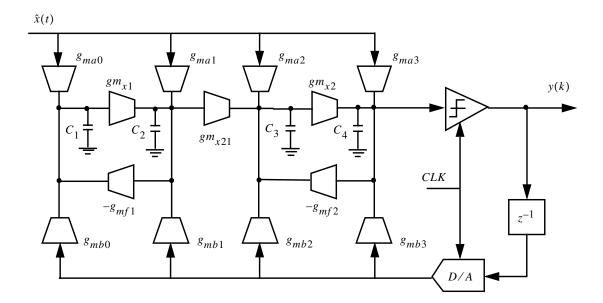

| Figure 5.4: A 4th-order $\Delta\Sigma$ TC modulator single-ended schematic (including cascade of two resonators)                                                                                                                         |

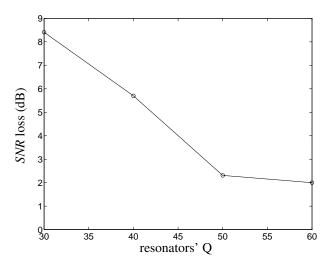

| Figure 5.5: SNR loss versus Q of resonators for a modulator with 12% excess loop delay                                                                                                                                                   |

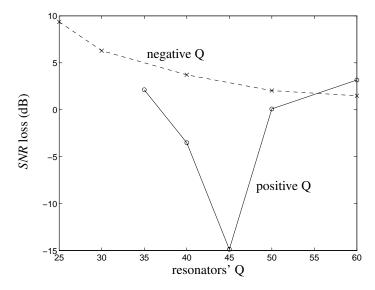

| Figure 5.6: SNR loss versus negative and positive Q of resonators for a modulator with zero excess loop delay                                                                                                                            |

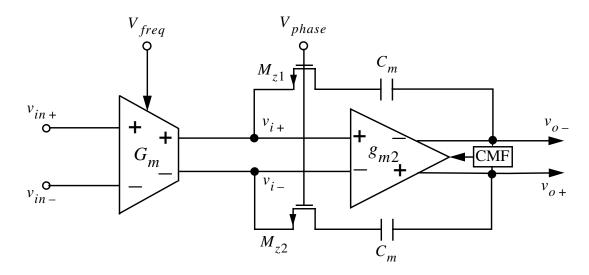

| Figure 5.7: Simplified schematic of a differential TC-amp integrator where $M_{z1}$ and $M_{z2}$ perform excess phase compensation                                                                                                       |

| Figure 5.8: A simplified second-order TC-amp based biquad loop99                                                                                                                                                                         |

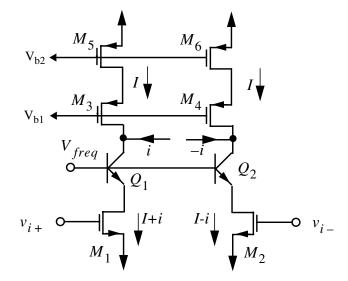

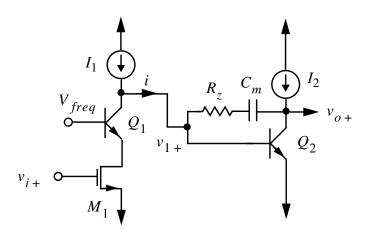

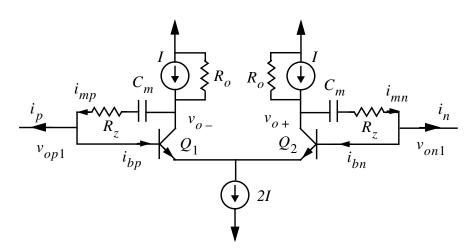

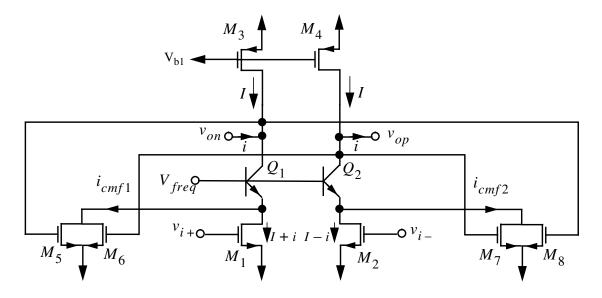

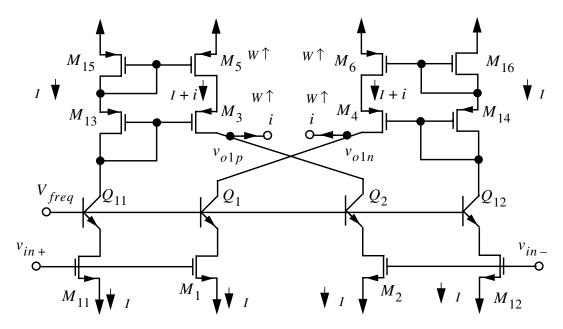

| Figure 5.9: A differential BiCMOS transconductor                                                                                                                                                                                         |

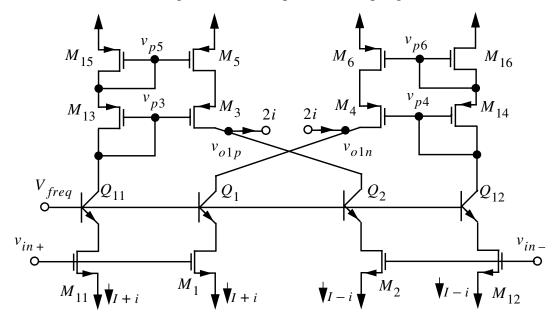

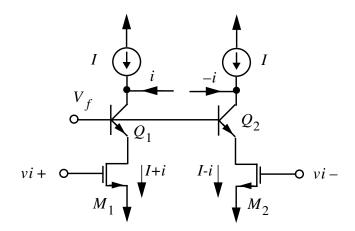

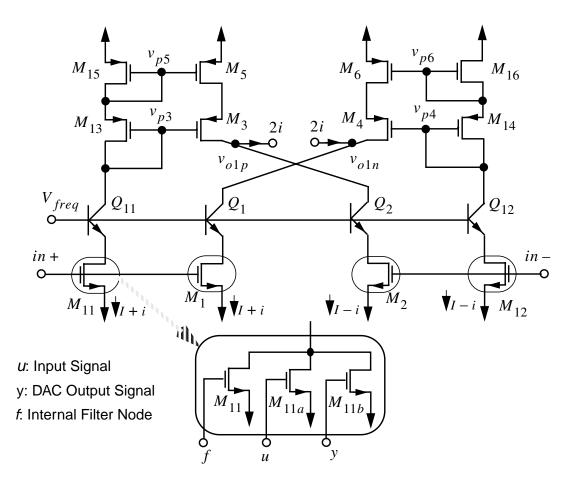

| Figure 5.10: A practical differential cross-coupled BiCMOS transconductor101                                                                                                                                                             |

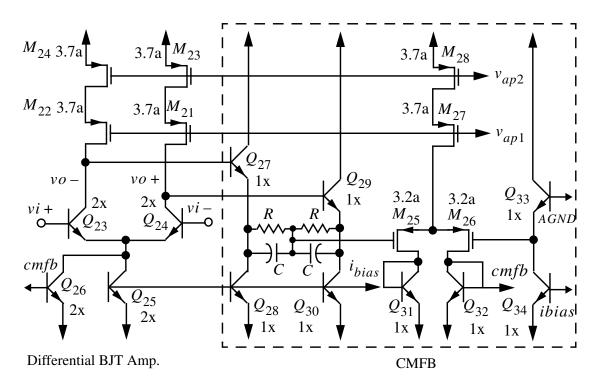

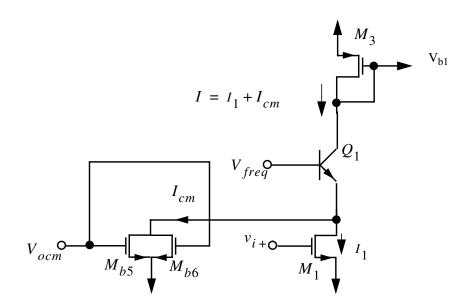

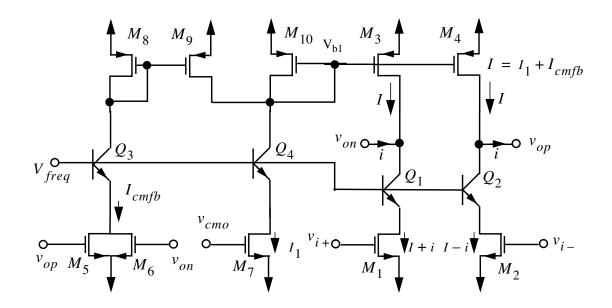

| Figure 5.11: Schematic diagram of the practical differential amplifier with continuous-<br>time CMFB used for the TC-amp integrator102                                                                                                   |

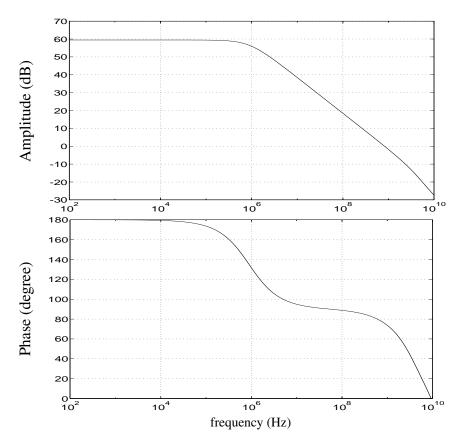

| Figure 5.12: Frequency response of the second-stage amplifier (with 2.5 pF capacitive load)                                                                                                                                              |

| Figure 5.13: A resonator implemented by two integrators in a closed loop system. 104                                                                                                                                                     |

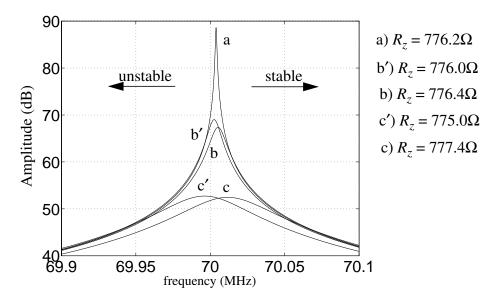

| Figure 5.14: Tuning of the Q of the filter by adjusting the loop integrators' phases. (a) shows -180° loop phase, (b) and (c) leading, and (b') and (c') lagging phase conditions. The expanded frequency axis exaggerates Q sensitivity |

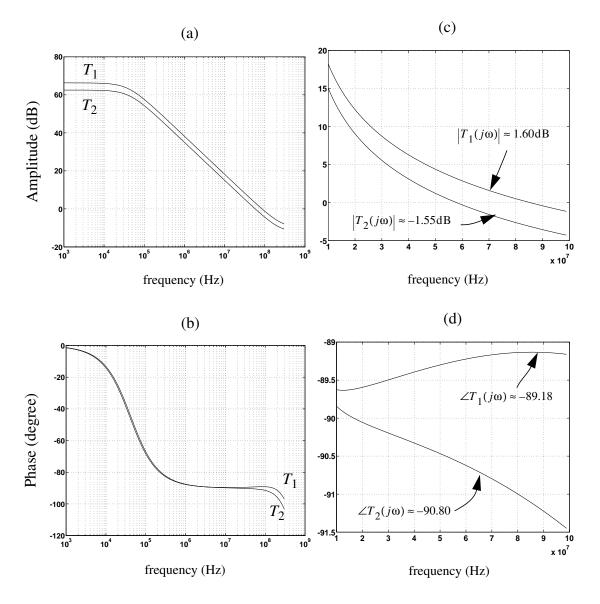

| Figure 5.15: (a) Amplitude and (b) phase frequency response of loop integrators, (c) and (d) same as (a) and (b) plotted in the band of interest107                                                                                      |

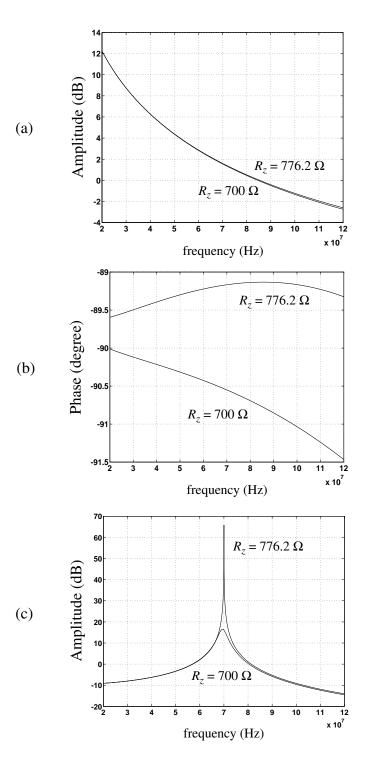

| Figure 5.16: The effect of an $R_z$ change on (a) gain (b) phase of integrator $T_1$ and (c) on resonator Q108                                                                                                                           |

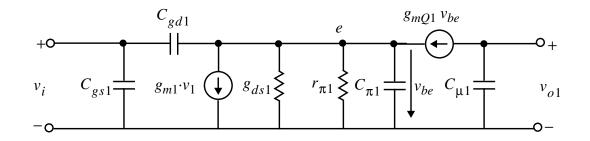

| Figure 5.17: A simplified half circuit schematic of TC-amp109                                                                                                                                                                            |

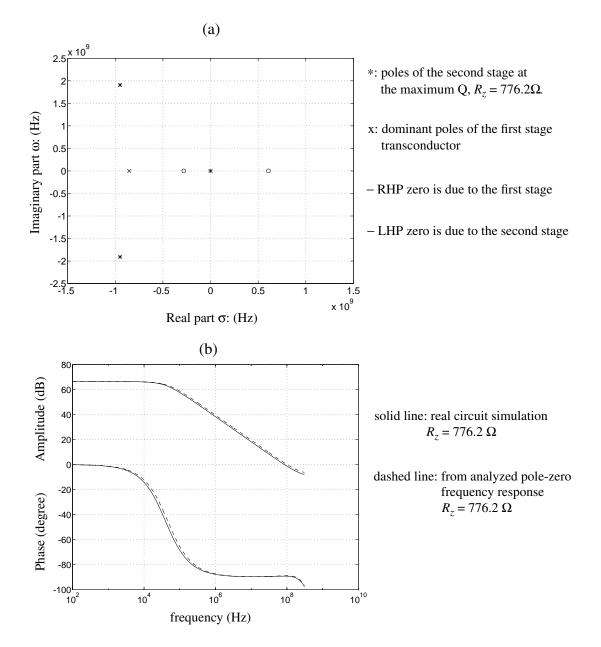

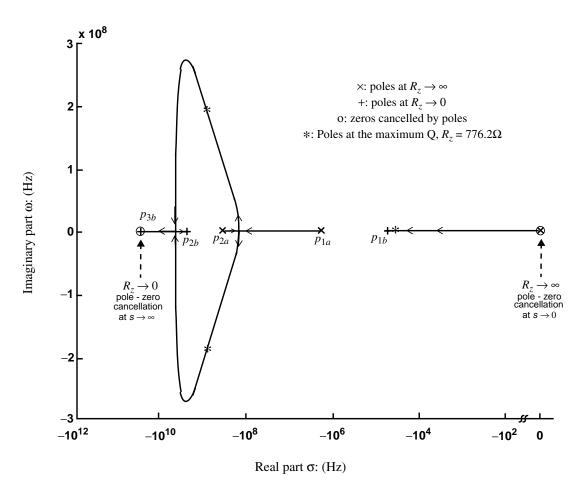

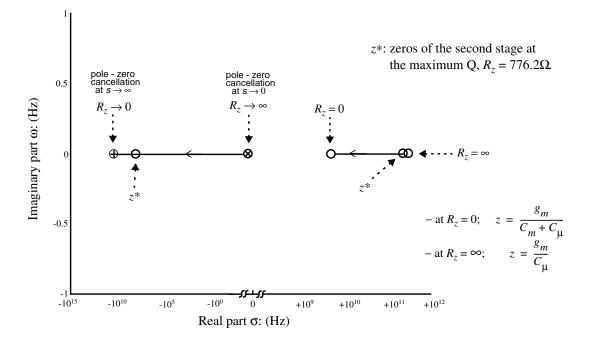

| Figure 5.18: (a) Poles and zeros of the whole TC-amp integrator, (b) frequency response of a system with the given poles and zeros along with that of the practical circuit simulation                                                   |

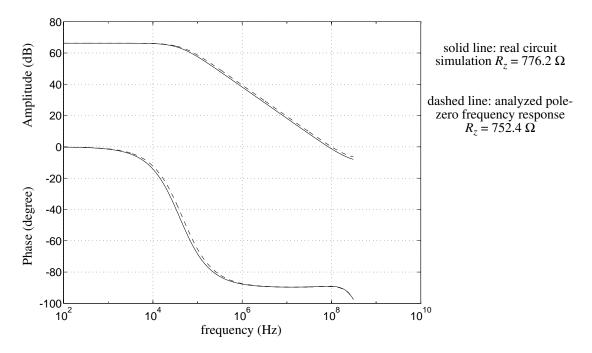

| Figure 5.19: The model matches to simulation at different $R_z$ value ( $R_z = 752.4$ $\Omega$ )                                                                                                                                         |

| Figure 5.20: A simplified differential circuit schematic of the BiCMOS transconductor shown in Fig. 5.10                                                                                                                                 |

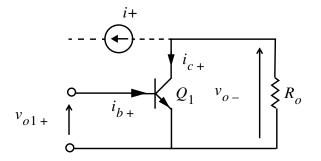

| Figure 5.21: A simplified model for the second stage amplifier119                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.22: A simplified half circuit schematic of second stage amplifier122                                                                                                                                            |

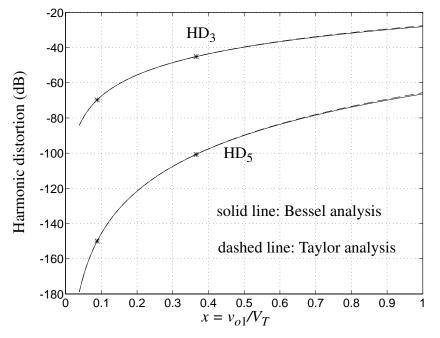

| Figure 5.23: The third and fifth harmonic distortion of a differential BJT amplifier vs. the normalized input amplitude                                                                                                  |

| Figure 5.24: The TC-amp integrator configured as a simple single-pole lowpass filter                                                                                                                                     |

| Figure 5.25: The simulated spectrum of the output signal of Fig. 5.24 when supplied by two tones with 0.1 V amplitude levels and frequencies at 51.27 MHz and 56.15 MHz                                                  |

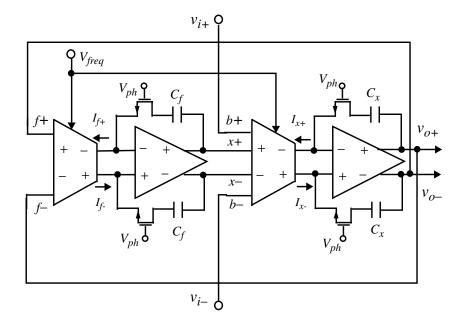

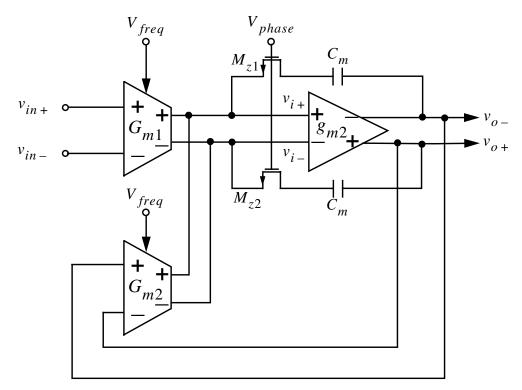

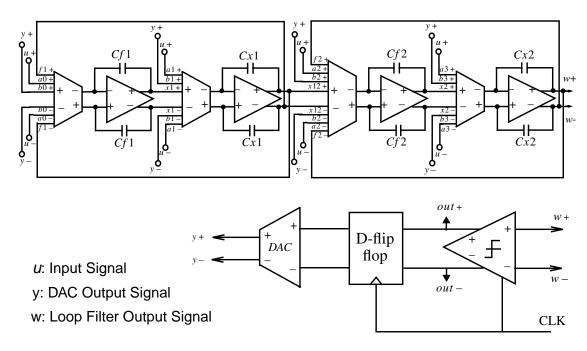

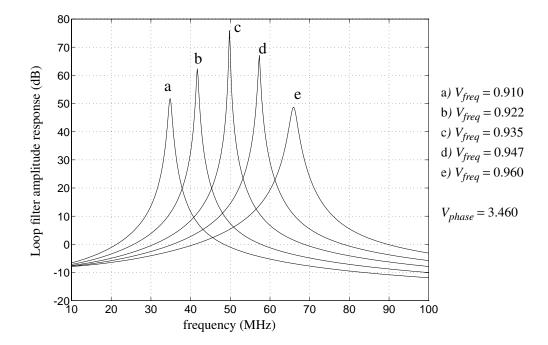

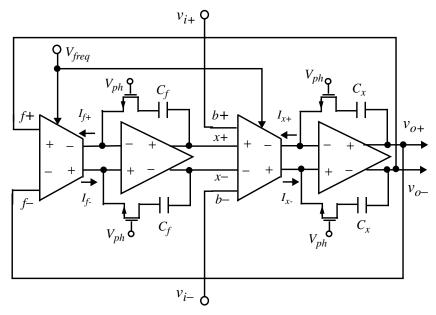

| Figure 5.26: A 4th-order TC-amp $\Delta\Sigma$ modulator128                                                                                                                                                              |

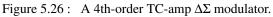

| Figure 5.27: The fourth-order $\Delta\Sigma$ modulator center frequency control by changing Vfreq, in every simulation $V_{phase} = 3.460$                                                                               |

| Figure 5.28: A three-input transconductor                                                                                                                                                                                |

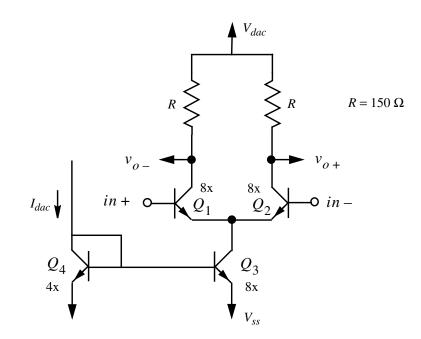

| Figure 5.29: A schematic of two-level current steering DAC                                                                                                                                                               |

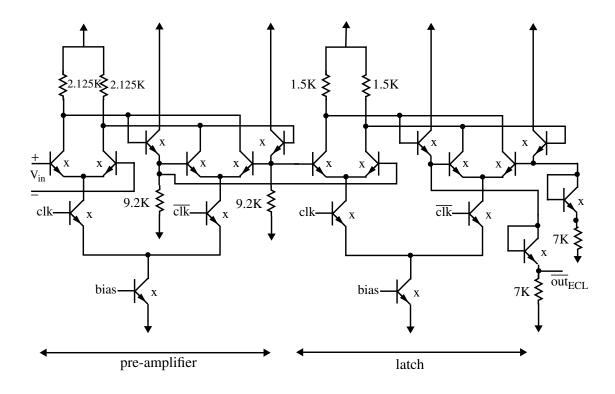

| Figure 5.30: A pseudo-ECL latched comparator                                                                                                                                                                             |

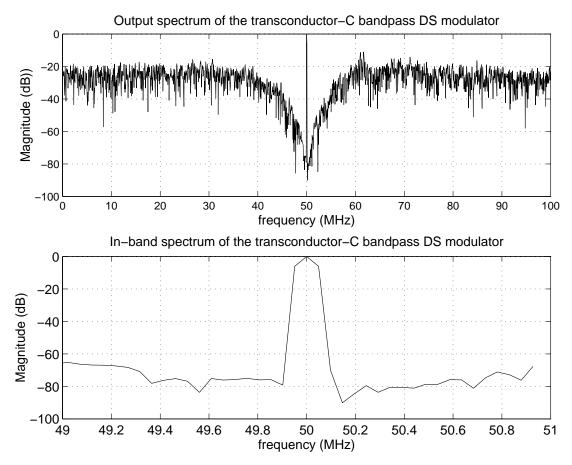

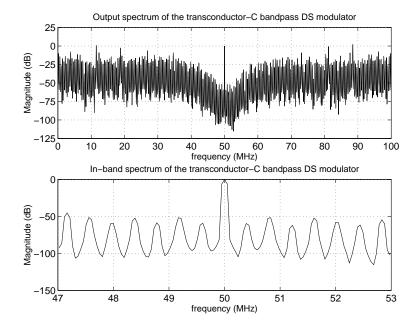

| Figure 5.31: A bandpass noise-shaping spectrum of the fourth-order modulator obtained from simulation of real circuits                                                                                                   |

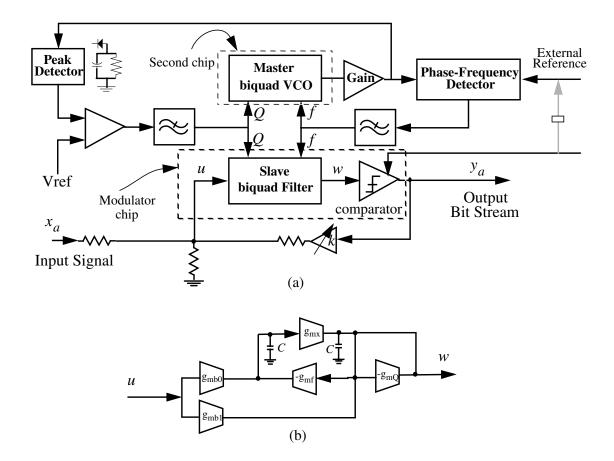

| Figure 6.1: Single ended diagram of (a) the second-order Sigma-Delta modulator with tuning circuitry, (b) $G_m$ -C biquad filter                                                                                         |

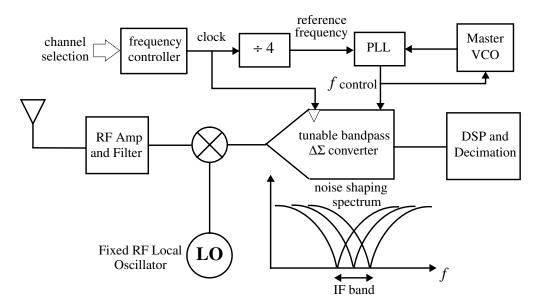

| Figure 6.2: Block diagram showing the possible channel selection at the IF stage by a tunable bandpass $\Delta\Sigma$ modulator                                                                                          |

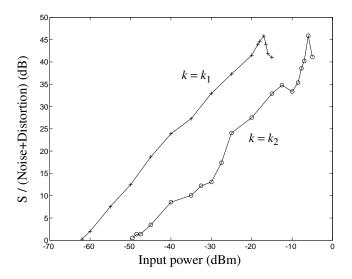

| Figure 6.3: Measured SNR versus input signal level for different gain values ( $k1 = k2$ -10 dB), for BW = 200 KHz                                                                                                       |

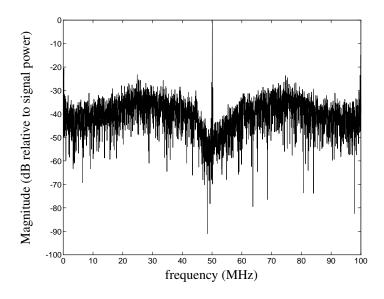

| Figure 6.4: Experimental output spectrum of the second-order modulator                                                                                                                                                   |

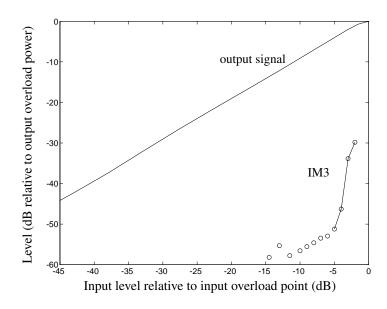

| Figure 6.5: Measured output signal and IM <sub>3</sub> level v.s. the input signal level140                                                                                                                              |

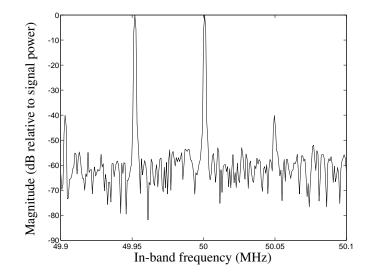

| Figure 6.6: Intermodulation (linearity) performance of $\Delta\Sigma$ modulator with two in-band input tones having -5 dB power relative to overload point141                                                            |

| Figure 6.7: Experimental result for tuning of the $\Delta\Sigma$ modulator noise-shaping center frequency. The three different tuned $\Delta\Sigma NTF$ notch frequencies are at 45 MHz, 55 MHz and 65 MHz, respectively |

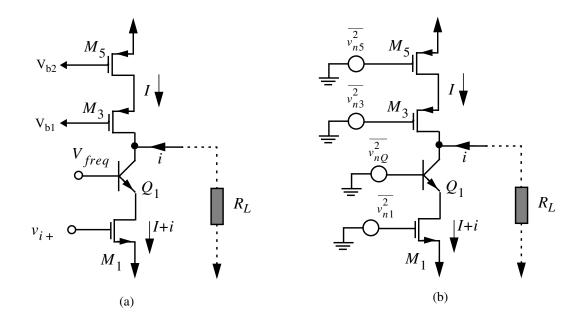

| Figure 7.1: (a) A half circuit schematic of the differential BiCMOS transconductor shown in Fig. 5.28, (b) device equivalent noise sources are added146                                                                  |

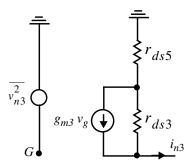

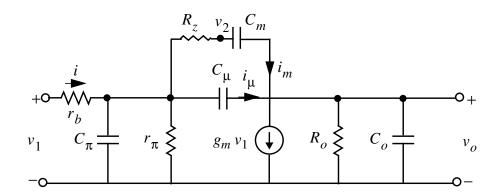

| Figure 7.2: A small signal model of the PMOS devices of Fig. 7.1148                                                                                                                                                      |

| Figure 7.3: A low-voltage design for the first stage transconductor                                                                                                                                                      |

| Figure 7.4: Bias circuitry for the transconductor shown in Fig. 7.3                                                                                                                                                      |

| Figure 7.5: Another approach for CM feedback                                                                                                                                                                             |

| Figure 7.6: The regular TC version of the loop filter shown in Fig. 5.26160                                                                                                                                              |

| Figure 8.1: A simplified second-order TC-amp based biquad loop163                                                                                                                                                        |

| Figure 8.2: Layout plot of the fourth-order modulator and the biquad bandpass filter                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 8.3: The center frequency of the bandpass filter is tuned at three different frequencies: 30MHz, 70MHz and 100MHz                                            |

| Figure 8.4: Three different Q adjustments for the bandpass filter centered at 50.5MHz:<br>Q=8, Q=18, Q=170                                                          |

| Figure 8.5: Two-tone intermodulation spurious-free output level                                                                                                     |

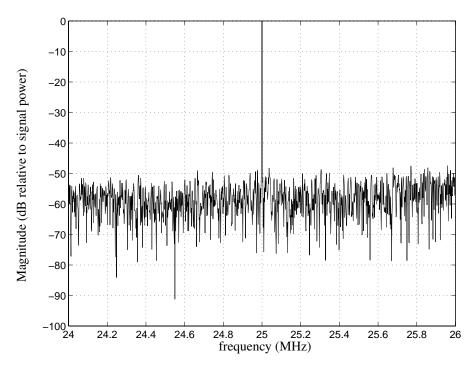

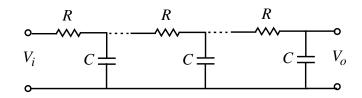

| Figure 8.6: A bandpass noise-shaping spectrum of the fourth-order ZA09 chip at 25MHz                                                                                |

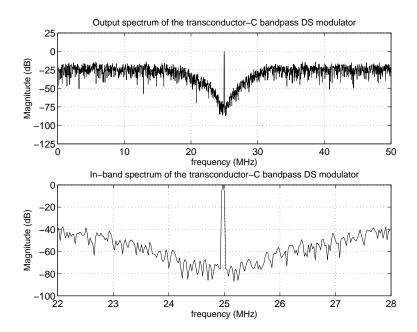

| Figure 8.7: In-band spectrum of the fourth-order ZA09 chip at 25MHz170                                                                                              |

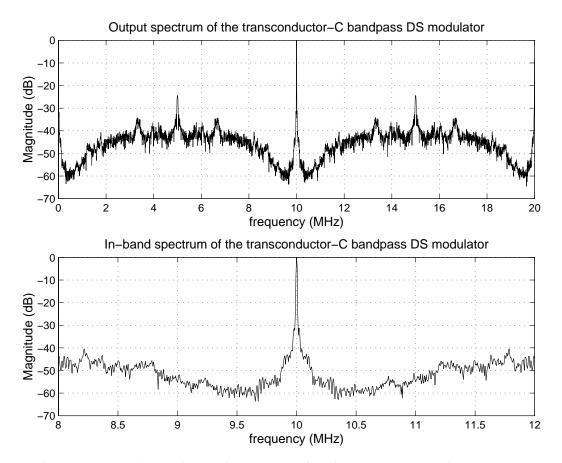

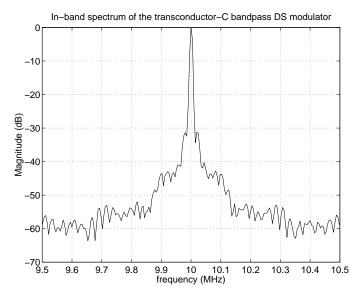

| Figure 8.8: A bandpass noise-shaping spectrum of the fourth-order ZA14 chip at 10MHz                                                                                |

| Figure 8.9: In-band region of the spectrum shown in Fig. 8.8                                                                                                        |

| Figure 8.10: A simple lumped RC model for interconnect parasitic elements inside the loop filter                                                                    |

| Figure 8.11: Simulating a CM voltage drift by changing of load device widths178                                                                                     |

| Figure 8.12: The simulated spectrum of the ZA09 / ZA14 fourth-order modulators with 0.2% mismatching between PMOS current mirror and active load devices            |

| Figure 8.13: The simulated spectrum of the new 3V fourth-order modulator with 5% mismatching between PMOS bias and active load devices                              |

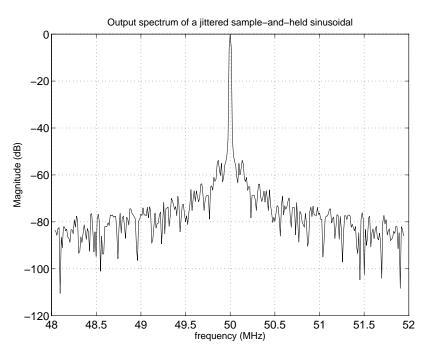

| Figure 8.14: Spectrum of a sinusoidal signal after passing through a sample-and-hold which is clocked with a random Gaussian clock; jitter standard deviation = 1ps |

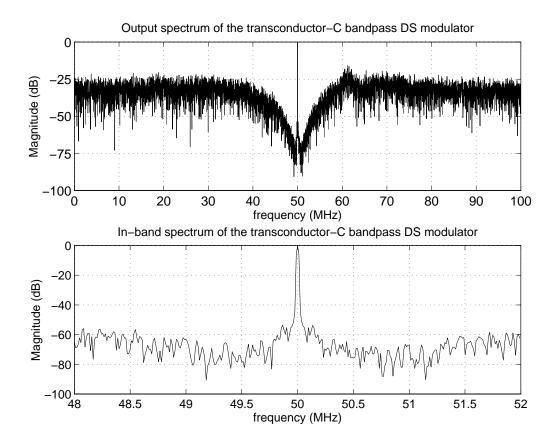

| Figure 8.15: The simulated spectrum of the ZA09 / ZA14 fourth-order modulators clocked with a 200MHz clock having a 1ps standard deviation jitter                   |

| Figure B.1: Another representation of a continuous-time modulator shown back in Fig. 3.22                                                                           |

| Figure C.1: Simplified small signal model of the Miller stage in Fig. 5.17201                                                                                       |

| Figure C.2: Root locus of the second stage amplifier with respect to Rz variation205                                                                                |

| Figure C.3: Zero locus of the second stage amplifier with respect to Rz variation207                                                                                |

| Figure C.4: Simplified small signal model of the first stage transconductor208                                                                                      |

## **List of Tables**

| Table 3.1: Examples of <i>s</i> - and <i>z</i> -domain $\Delta\Sigma$ modulator loop transfer functions 36          |

|---------------------------------------------------------------------------------------------------------------------|

| Table 3.2: Some transform examples    46                                                                            |

| Table 3.3: Gains of the third example modulators given in Fig. 3.24.                                                |

| Table 4.1: Second-order LC modulator parameters.    80                                                              |

| Table 4.2: Multiple-pole fourth-order LC modulator parameters.    83                                                |

| Table 5.1: The SNR simulation results for fourth-order modulators       132                                         |

| Table 6.1: The measured implicit anti-alias filter frequency response.       142                                    |

| Table 7.1: Noise and power comparison among different designs    153                                                |

| Table 7.2: MSA, DR and <i>SNR</i> of the $\Delta\Sigma$ modulators with some of the loop filters given in Table 7.1 |

| Table 8.1: Experimental results obtained from the filter at Q=3 and 50MHz 165                                       |

| Table 8.2: Experimental results obtained from the filter at Q=3 and 50MHz 171                                       |

| Table 8.3: Clock jitter simulation result summary.    183                                                           |

| Table 8.4: Clock jitter simulation result summary.    183                                                           |

# List of Symbols

A list of the major symbols, notations and abbreviations with their definitions are as follows:

|                  | Absolute value                                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------|

| $\  \ _1$        | One-norm                                                                                            |

| $\  \ _{\infty}$ | Infinity-norm                                                                                       |

| $A_c$            | An $N \times N$ state space matrix for a continuous-time modulator                                  |

| $A_d$            | An $N \times N$ state space matrix for a discrete-time modulator                                    |

| $A_{dc}$         | The DC gain of an amplifier                                                                         |

| A(K)             | Noise amplification factor which demonstrates a stability check for a $\Delta\Sigma$ modulator      |

| A/D              | Analog-to-digital                                                                                   |

| ADC              | Analog-to-digital converter                                                                         |

| $a_k$            | A residue of a discrete-time $\Delta\Sigma$ loop transfer function                                  |

| $\hat{a}_k$      | A residue in a continuous-time $\Delta\Sigma$ loop filter                                           |

| В                | Bandwidths in Hz                                                                                    |

| b <sub>c</sub>   | An $N \times 1$ vector defining the state space parameter of a continuous-time modulator            |

| b <sub>d</sub>   | An $N \times 1$ vector defining the state space parameter of a discrete-time modulator              |

| С                | Capacitor                                                                                           |

| CMRR             | Common-mode rejection ratio                                                                         |

| C <sub>ox</sub>  | Oxide capacitance of the gate-to-body per unit area                                                 |

| c <sub>c</sub>   | An $N \times 1$ vector defining the state space parameter of a continuous-time modulator            |

| c <sub>d</sub>   | An $N \times 1$ vector defining the state space parameter of a discrete-time modulator              |

| $\Delta T$       | A fraction of one clock period in a continuous-time $\Delta\Sigma$ modulator as an extra loop delay |

| D/A              | Digital-to-analog                                                                                   |

| DAC              | Digital-to-analog converter                                                                         |

|                  |                                                                                                     |

| $d_c$               | a scaler defining the state space parameter of a continuous-time modulator                                                                                      |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $d_d$               | a scaler defining the state space parameter of a discrete-time modulator                                                                                        |

| $\Delta\Sigma$      | Delta-Sigma                                                                                                                                                     |

| e(k)                | Additive White noise modeling the $\Delta\Sigma$ quantization noise                                                                                             |

| F <sub>i</sub>      | Noise figure of the ith stage amplifier                                                                                                                         |

| $F_{aa}(\omega)$    | Implicit anti-alias filtering frequency response in a continuous-time modulator                                                                                 |

| $\varphi_i(\omega)$ | Phase frequency response of a transconductor circuit                                                                                                            |

| f                   | Frequency in Hz                                                                                                                                                 |

| $f_{bp}$            | A frequency in a bandpass region (like $f_s/4$ ) in Hz                                                                                                          |

| $f_{lp}$            | A frequency in a low pass region around DC in Hz                                                                                                                |

| $f_s$               | Sampling frequency in Hz                                                                                                                                        |

| G                   | Gain                                                                                                                                                            |

| $G_i$               | Gain of the <i>i</i> th stage amplifier                                                                                                                         |

| G(z)                | Transfer function of the feedforward filter in a discrete-time modulator                                                                                        |

| $\hat{G}(j\omega)$  | Frequency response of the feedforward filter in a continuous-time $\Delta\Sigma$ modulator                                                                      |

| $G_i(\omega)$       | Amplitude frequency response of a transconductor circuit                                                                                                        |

| $G_m$               | Transconductance representation of an OTA in its model                                                                                                          |

| $G_m$ - $C$         | Transconductor-capacitor circuit                                                                                                                                |

| $G_o$               | Output conductance representation of an OTA in its model                                                                                                        |

| g <sub>ds</sub>     | Drain-source conductance                                                                                                                                        |

| $g_m$               | Transconductor element                                                                                                                                          |

| 8 <sub>mb</sub>     | Body-effect transconductance                                                                                                                                    |

| g <sub>mbi</sub>    | <i>i</i> th transconductance element in the feedforward path of a transconductor-<br><i>C</i> filter used in the feedback loop of a $\Delta\Sigma$ modulator    |

| g <sub>mai</sub>    | <i>i</i> th transconductance element in the feedforward path of a transconductor-<br><i>C</i> filter used in the feedforward path of a $\Delta\Sigma$ modulator |

| $g_{mf}$            | One of two transconductance elements in a resonator configuration                                                                                               |

| $g_{mx}$            | One of two transconductance elements in a resonator configuration                                                                                               |

| $g_{oX}$            | The output conductance of the transconductor called $X$                                                                                                         |

| H(z)                | Open-loop transfer function of a $\Delta\Sigma$ modulator                                                                                                       |

|                     |                                                                                                                                                                 |

| HD <sub>i</sub>                | <i>i</i> th harmonic distortion in dB                                                      |

|--------------------------------|--------------------------------------------------------------------------------------------|

| $H_{LC}(s)$                    | A simple transfer function of an LC resonator                                              |

| H(z,m)                         | Open-loop modified z-transfer function of a $\Delta\Sigma$ modulator with extra loop delay |

| $H(e^{j\omega T})$             | Loop frequency response of a discrete-time modulator                                       |

| $\hat{H}(s)$                   | Open-loop transfer function of a continuous-time $\Delta\Sigma$ loop filter                |

| h(n)                           | The entire $\Delta\Sigma$ open-loop impulse response                                       |

| $\hat{h}(t)$                   | The $\Delta\Sigma$ loop filter impulse response                                            |

| Ι                              | DC current in a transistor                                                                 |

| $I_D$                          | Drain current in a MOSFET                                                                  |

| $I_E$                          | Emitter current in a bipolar transistor                                                    |

| IIP <sub>3</sub>               | Third-order intermodulation intercept point in dBm                                         |

| IM <sub>3</sub>                | Third-order intermodulation product referred to the fundamental tone level in dBc          |

| <i>I<sub>m</sub></i>           | Peak current swing in a transistor                                                         |

| $I_n(x)$                       | Modified Bessel function of the first kind, of order <i>n</i>                              |

| $I_{\underline{S}}$            | Constant saturation current in a bipolar transistor                                        |

| $I_{\underline{S}}$<br>$i_n^2$ | Current noise spectral density in A <sup>2</sup> /Hz                                       |

| i                              | Small signal current in a transistor                                                       |

| $\overline{i(t)}$              | Average DC value of $i(t)$                                                                 |

| k                              | Boltzmann's constant                                                                       |

| K                              | Loop gain a $\Delta\Sigma$ modulator                                                       |

| $K_{\chi}$                     | A quasi linear gain defined for a $\Delta\Sigma$ modulator related to the input signal     |

| K <sub>n</sub>                 | A quasi linear gain defined for a $\Delta\Sigma$ modulator related to quantization noise   |

| k <sub>hz</sub>                | Half delayed return to zero coefficient in an LC modulator                                 |

| k <sub>nz</sub>                | Non return to zero coefficient in an LC modulator                                          |

| $k_{rz}$                       | Return to zero coefficient in an LC modulator                                              |

| L                              | Length of A CMOS channel                                                                   |

| LC                             | Inductance-capacitance tank circuit                                                        |

| LHP                            | Left half plane in the S-plane                                                             |

| MSA                            | Maximum amplitude signal at which the modulator results in the maximum SNR                 |

| $\mu_n$        | Electron mobility in the induced <i>n</i> channel                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------|

| NEF            | noise excess factor                                                                                                |

| NF             | Noise figure of entire circuit                                                                                     |

| Nq             | In-band quantization noise                                                                                         |

| NRZ            | Non-return-to-zero pulse waveform                                                                                  |

| N <sub>t</sub> | Input referred thermal noise voltage integrated over a certain bandwidth                                           |

| NTF(z)         | Noise transfer function of a $\Delta\Sigma$ modulator                                                              |

| $NTF_{K}(z)$   | ) Noise transfer function of a modulator as a function of loop gain $K$                                            |

| $NTF_m(z)$     | ) Noise transfer function obtained from the modified <i>z</i> -transform of the modulator loop                     |

| OSR            | Oversampling ratio                                                                                                 |

| pdf            | probability density function                                                                                       |

| $p_i$          | <i>i</i> th pole of a circuit                                                                                      |

| Q              | Quality factor of a filter                                                                                         |

| R              | Resistor                                                                                                           |

| R              | Sampling rate to the twice of the maximum input signal frequency ratio in a bandpass modulator                     |

| RHP            | Right half plane in the S-plane                                                                                    |

| $R_{HZ}(t)$    | A RZ pulse waveform with a half delay                                                                              |

| $R_i(t)$       | An arbitrary DAC pulse waveform                                                                                    |

| $R_{NZ}(t)$    | NRZ pulse waveform                                                                                                 |

| $R_p(t)$       | A pulse waveform with p sec aperture                                                                               |

| $R_{ph}$       | The resistive model for the NMOS transistor in series with Miller capacitor                                        |

| $R_{RZ}(t)$    | RZ pulse waveform                                                                                                  |

| $R_{z}$        | The resistor in series with Miller integrating capacitor                                                           |

| RZ             | Return-to-zero pulse waveform                                                                                      |

| r <sub>b</sub> | Base region resistance in a bipolar transistor                                                                     |

| $r_{kls}$      | MOS drain-to-source small signal output resistance                                                                 |

| Σ              | Sum over all parts from <i>i</i> to <i>k</i>                                                                       |

| S(K)           | One-norm of a $\Delta\Sigma$ modulator's noise transfer function as a function of loop gain <i>i.e.</i> $NTF_K(z)$ |

| SFDR           | Spurious free dynamic range                                                                                        |

| $S_i / N_i$        | Signal-to-noise ratio at the input of an amplifier                           |

|--------------------|------------------------------------------------------------------------------|

| $S_o/N_o$          | Signal-to-noise ratio at the output of an amplifier                          |

| STF(z)             | Signal transfer function of a $\Delta\Sigma$ modulator                       |

| $STF_c(\omega)$    | Signal frequency response in a continuous-time $\Delta\Sigma$ modulator      |

| S                  | Complex frequency in S-plane                                                 |

| $\hat{s}_k$        | A pole in a continuous-time $\Delta\Sigma$ loop filter                       |

| sgn(x)             | Sign function                                                                |

| Т                  | Absolute temperature                                                         |

| Т                  | A clock period                                                               |

| TC-amp             | Transconductor-capacitor-amplifier circuit                                   |

| TIMD               | Total intermodulation distortion in dB                                       |

| T(s)               | Voltage transfer function of a transconductor circuit                        |

| V <sub>BE</sub>    | Base-Emitter junction voltage drop in a bipolar transistor                   |

| $V_{DS}$           | MOS drain-to-source voltage                                                  |

| $V_{GS}$           | MOS gate-to-source voltage                                                   |

| V <sub>freq</sub>  | Control voltage to tune the center frequency of a filter                     |

| $V_{f}$            | Shorter form used for $V_{freq}$                                             |

| V <sub>on</sub>    | The so-called on voltage in a MOSFET                                         |

| V <sub>phase</sub> | Control voltage to cancel the excess phase and so the Q of a filter          |

| $V_{ph}$           | Shorter form used for V <sub>phase</sub>                                     |

| $V_{th}$ or $V_t$  | MOS threshold voltage                                                        |

| $\frac{V_T}{2}$    | Thermal voltage in a bipolar transistor                                      |

| $v_n^2$            | Voltage noise spectral density in V <sup>2</sup> /Hz                         |

| W                  | Width of a CMOS channel                                                      |

| ω                  | Frequency in rad/s                                                           |

| ω                  | Center frequency of a bandpass filter in rad/s                               |

| ω                  | Unity bandwidth of an op-amp in rad/s                                        |

| ω <sub>s</sub>     | Sampling frequency in rad/s                                                  |

| $\hat{X}(j\omega)$ | Spectrum of an input signal to a continuous-time modulator                   |

| $\hat{x}(t)$       | Input signal to a continuous-time modulator                                  |

| $Y(e^{j\omega T})$ | Spectrum of an output signal in a continuous-time or discrete-time modulator |

|                    |                                                                              |

| Ordinary z-transform                                            |

|-----------------------------------------------------------------|

| Modified z-transform                                            |

| Zero order hold                                                 |

| Complex frequency in Z-plane                                    |

| A pole of a discrete-time $\Delta\Sigma$ loop transfer function |

| <i>i</i> th zero of a circuit                                   |

|                                                                 |

### Chapter 1

### Introduction

### **1.1 Analog-to-Digital Conversion**

It is not exaggerating to say that data converters are key components of almost any electronic system. Since the real world is inherently analog and the trend in telecommunication, voice, video, instrument, computer and many other applications is to get a digital form of the analog signal to make use of robust, flexible and reliable signal processing, the analog-digital interfaces become critical paths. In terms of complexity data converters are composed of many analog building blocks such as opamps, sample (track)-and-holds and comparators which makes their design very challenging especially when a system is put on a chip. In a data converter designers often have to mix analog and digital techniques and acquire a very good knowledge in both analog and signal processing areas. Sometimes even dealing with some abstract theories such as nonlinear phenomena and stability becomes unavoidable. In this sense, perhaps the most interesting class of data converters is Delta-Sigma ( $\Delta\Sigma$ ) analog-todigital (A/D) converters which are sometimes referred to as oversampling, interpolative or noise-shaping converters. A  $\Delta\Sigma$  A/D converter usually consists of an analog part called a  $\Delta\Sigma$  modulator producing an oversampled bit stream followed by a digital part implementing decimation and digital filtering to complete the A/D conversion.

Depending on the application of an A/D converter the trade-off among speed, resolution and power is made given the specifications and the process. In [Snel92] a comparison among several analog-to-digital converters (ADC) has been made and the resultant plots demonstrate very useful relations. Regarding speed and accuracy it was found that the best converters had  $2^N f_s = 100$ GHz, where N is the converter's resolution in bits and  $f_s$  the sampling frequency. For eight-bit converters a wide range of 1mW–10 mW/MHz has been found as a relationship between power and sampling rate while the best 8-bit part was consuming 2.5 mW/MHz. This means that in a state-of-the art converter one can expect to get an 8-bit ADC with 100 MHz sampling frequency consuming 250 mW. A survey among some of the most recent ADCs in the literature verified the preceding information. For example, an 8-bit 150 MHz sampling ADC with 350 mW power consumption was reported in 1995 [Mor95]. However, most ADCs were consuming higher power in the order of 1W at high sampling rates [Kim93] or higher resolution (10 bits) [Col93].

As mentioned, Delta-Sigma ( $\Delta\Sigma$ ) converters form a popular class of analog-to-digital converters. However, they have been mostly developed for high precision voice applications using switched-*C* techniques. For video applications such as digital-TV, HDTV or direct satellite broadcast systems usually a moderate dynamic range between 7 to 10 bits is enough but a fairly high clock rate in order of 100 MHz is required. So far, flash [Rey94] or half-flash [Lon93], pipeline and/or sub-ranging [Con93], [Lin90], [Nis95] A/D converters have been developed for the video applications.

This thesis studies the feasibility of a  $\Delta\Sigma$  modulator for high-speed high-bandwidth applications such as video. Since it is well known that continuous-time techniques such as transconductor-*C* filters can be faster than their switched-*C* counterparts in the same process, the motivation for this thesis was the development of a method for implementing continuous-time  $\Delta\Sigma$  modulators with special stress on transconductor-*C* realization. Although one can not expect to achieve a very high dynamic range performance from transconductor-*C* circuits due to their known non-linearity problems, it seems that for the medium dynamic range applications such as video, these circuits are suitable.

Another motivation for studying the transconductor-*C* approach for  $\Delta\Sigma$  modulation was the new trend for moving analog/digital interface closer to the signal source which necessitates higher ADC sampling rates. Perhaps, talking about analog-to-digital conversion for radio frequencies (RF) in GHz range seems to be a bit unrealistic today. However, conversion of analog signals at an intermediate frequency (IF) is quite achievable. A  $\Delta\Sigma$  modulator for converting an IF signal at up to 10.7 MHz [Sing94] has been already reported using switched-*C* techniques. This thesis investigates the possibility of analog-to-digital conversion of an analog signal at higher IF frequencies. This thesis demonstrates a fourth-order  $\Delta\Sigma$  transconductor-*C* circuit implementation. It also shows some practical advantages and drawbacks of a continuous-time  $\Delta\Sigma$ implementation which have been supported by analysis and simulations and practically verified by experiments. It studies the problems associated with the LC realizations [Gail89], [Thu91], [Tro93] and introduces a new structure for an LC  $\Delta\Sigma$  modulator.

### **1.2 Contributions**

The contributions made in this thesis to the study and implementation of a continuoustime  $\Delta\Sigma$  modulator are as follows:

- It gives a methodology to obtain a continuous-time loop filter transfer function from a switched-*C* counterpart given the waveform(s) of the digital-to-analog converter(s) (DAC) in the ΔΣ feedback loop. The loop filter transfer functions for some important modulators have been explicitly presented.

- 2) It develops two different classes of equivalent continuous-time modulators for every switched-*C* modulator which has at least two loop delays: *i*) a zero-delay modulator and *ii*) a modulator with one or more digital loop delays.

- 3) It analyzes the effects of the extra loop delays or propagation delay times of the components in a continuous-time  $\Delta\Sigma$  modulator such as those in the comparator, latch or D-flip flop, DAC and parasitic interconnects by the modified *z*-transform method. It explicitly derives the modified noise transfer functions  $NTF_m(z)$  for two popular bandpass modulators as well.

- 4) It analytically proves the anti-alias filtering property of continuous-time modulators which is then verified by simulations and real circuit experiments.

- 5) It introduces a novel architecture for LC type  $\Delta\Sigma$  modulators which provides enough degrees of freedom to produce an arbitrary  $\Delta\Sigma$  loop impulse response.

- 6) It employes a master-slave tuning algorithm to control the notch center frequency and the Q of noise-shaping in a second-order transconductor- $C \Delta \Sigma$  modulator. Such a method has been already used for tuning of the transconductor-C filters but to the author's knowledge not for tuning of  $\Delta \Sigma$  modulator parameters.

- 7) It demonstrates the design and implementation of a fully monolithic fourth-order transconductor- $C \Delta \Sigma$  modulator along with a master biquadratic (biquad) filter in a 0.8µm BiCMOS process. It gives the experimental results of the realized chips. It clearly explains the causes of the discrepancies between simulations and experiments and suggests a new design for a future implementation.

### **1.3 Organization of the Thesis**

**Chapter 2** introduces the concepts of a continuous-time  $\Delta\Sigma$  as well as a bandpass  $\Delta\Sigma$  modulator. Stability criteria in a  $\Delta\Sigma$  modulator are critically reviewed and a mixture of one-, two- and infinity-norm constraints given in [Risb94] are compared to some previous stability criteria.

**Chapter 3** proposes a systematic method to obtain a proper *s*-domain transfer function for a continuous-time modulator from an original discrete-time (switched-*C*) equivalent. It shows how different DACs in a modulator loop such as non-return-to-zero (NRZ), return-to-zero (RZ) and so on would lead to different continuous-time loop filters. It discusses the sensitivity of continuous-time modulators to the extra loop delays. It culminates by proving the anti-alias filtering property of continuous-time modulators.

**Chapter 4** introduces a new pulse-shaping architecture for LC continuous-time modulators. It shows how the overall loop impulse response of an LC modulator can be fixed to coincide with that of an ideal discrete-time equivalent by providing two degrees

#### **Chapter 1–Introduction**

of freedom at the input of each LC resonator in DAC feedback paths.

**Chapter 5** develops a BiCMOS transconductor-*C*-amplifier (TC-amp) filter for a fourthorder  $\Delta\Sigma$  modulator. It studies the sensitivity of a general transconductor-*C* modulator to its loop filter parameters (Q and center frequency). It gives an analysis with simulation support to show how the Q of a TC-amp filter can be adjusted using cancellation of excess phase in each resonator (integrator) by tuning resistors in series with the Miller integrating capacitors. It demonstrates a small-signal and non-linearity analysis for the proposed TC-amp integrator. It concludes with the simulation results of the entire transconductor-*C*-amplifier  $\Delta\Sigma$  modulator circuit.

**Chapter 6** shows the implementation of a second-order transconductor- $C \Delta \Sigma$  modulator with a master-slave automatic tuning scheme. It discusses the linearity of the modulator and the matching between the master and the slave parts. It proves the anti-alias filtering property of transconductor-C modulators experimentally.

**Chapter 7** investigates the speed, tunablity, noise and power trade-offs in the proposed class of triode-mode BiCMOS transconductor-C modulators. It shows how the dynamic range of a transconductor-C modulator can be improved by optimizing the transconductor-C circuits with respect to their input-referred noise. It shows that this improvement sacrifices the modulator's speed and tunablity while the power consumption is slightly lowered. It concludes with the introduction of a regular transconductor-C modulator architecture as opposed to the designed TC-amp modulators.

**Chapter 8** demonstrates the experimental results of two fourth-order bandpass TC-amp  $\Delta\Sigma$  modulators along with their master biquad filters implemented in a 0.8µm BiCMOS process. It shows the experimental noise-shaping spectrums of both chips. It investigates disagreements between the chips' noise-shaping spectra and simulation results. It diagnoses some important causes and proposes a complete new design for a future implementation.

Chapter 2

## Overview of Delta-Sigma Modulator

Delta-Sigma ( $\Delta\Sigma$ ) modulation refers to a class of noise-shaping linear encoders (typically one-bit) which transforms an analog (continuous-time) signal to an oversampled bit stream. A general diagram of a  $\Delta\Sigma$  modulator is shown in Fig. 2.1. Oversampling of the continuous-time signal before quantization reduces the quantization noise density by the factor of the oversampling ratio OSR which is defined as the ratio of the sampling rate to twice the signal bandwidth (Nyquist rate). The inband quantization noise is reduced by 3 dB (0.5 bit) for every doubling of the oversampling ratio. The linear system in the modulator loop shapes the quantization noise by placing nulls in the quantization noise spectrum at the band of interest which in turn enhances the output bit stream signal-to-quantization noise ratio further. Delta-Sigma modulators have been of outstanding interest at low-speed high-resolution applications. However, they have not been very successful in high-speed high-bandwidth applications. The explanation is that the high performance of  $\Delta\Sigma$  modulators can typically be exploited at high oversampling ratios. For high bandwidth applications this requires a very high sampling rate which makes the real implementation very difficult. Switched-C techniques have been the dominant approach for implementing the  $\Delta\Sigma$  loop filters. One can achieve very good matching and linearity with a switched-C technique; however, the clock speed is a limiting factor. The reasons are the opamp speed (bandwidth) and non-ideal effects in the switches like nonzero "on"-resistance and clock feedthrough. It is shown [Greg86] that in order to have a negligible error at a switched-C integrator with a two-phase clock scheme, the unity-gain bandwidth of the opamp  $\omega_{0}$ should be (at least) five times as large as the clock frequency  $f_s$  *i.e.*  $f_o \approx 5 f_s$ . Recently, a

continuous-time technique [Gail89], [Thu91], [Tro93] for bandpass LC-based modulators has been introduced as an alternative for the switched-*C* (discrete-time) approach. The continuous-time modulators can also make use of some other continuous-time techniques such as the transconductor-*C* ( $G_m$ -*C*) approach. Since a transconductor-*C* integrator operates at its unity-gain frequency  $\omega_0$ , so one can estimate that within the same technology a typical continuous-time filter can be five times faster than a typical switched-*C* one.

Figure 2.1 : A general  $\Delta\Sigma$  modulator.

The higher-order  $\Delta\Sigma$  modulators can alleviate the high-speed clock requirement somewhat. That's why many researchers have developed some higher-order  $\Delta\Sigma$ topologies [Lee87b], [Ada91], [Cha90]. Unfortunately, modulator structures (order > 2) are prone to instability. So, the stability analysis continue to be a central research issue for these modulators [Risb94].

In this chapter an overview on continuous-time modulators will be given. Then, bandpass  $\Delta\Sigma$  modulators are reviewed. A survey of  $\Delta\Sigma$  stability analyses will conclude the chapter.

### 2.1 Continuous-time Delta-Sigma Modulator

Delta-Sigma modulation was proposed in 1962 [Ino62] by Inose *et. al.* as a modification of Delta modulation, which couldn't fulfill the requirements of digital transmission of analog signals. The same authors in 1963 [Ino63] presented an analysis for signal-tonoise characteristics of a  $\Delta\Sigma$  modulator along with a real circuit implementation. Their modulator loop filter was an integrator composed of the discrete-component continuoustime circuits. Fig. 2.2 shows a block diagram of the lowpass filters used in [Ino63], where *G* represents the loop DC-gain implemented by a transistor. Later on in [Bra69] it was shown that since the modulator feedback signals are sampled, the loop behavior including the continuous-time feedback loop filter can be described by a *z*-domain transfer function. The general analysis given in [Bra69] was correct, however, the *z*-domain transfer functions proposed for a simple integrator  $1/(s + \alpha)$  and a double integrator  $(s + \beta)/s^2$  were wrong. Candy [Can74] used the same idea to make an 8-bit A/D converter intended for 1-MHz signal bandwidths. He used a continuous-time single-stage integrator for the modulator loop similar to that in [Ino62]. His analysis showed again despite the fact that the loop filter is continuous-time, because of the presence of a sampler (quantizer) inside the modulator loop, the loop function can be expressed by a *z*-domain transfer function. Ignoring aliasing effects he gave representation for the baseband spectrum of the output signal for the first-order modulator. In [Can85] an extended analysis of [Can74] was given which related a

Figure 2.2 : The modulator loop filters used in [Ino63] with their transfer functions, (a) singleintegrator, and (b) double-integrator.

modulator with a second-order continuous-time filter to its discrete-time equivalent. This was a correct *z*-domain loop transfer function representing a loop including a continuous-time double integrator and a D/A with a non-return to zero (NRZ) feedback pulse:

$$\frac{2z-1}{\left(z-1\right)^2} \leftrightarrow \frac{1+1.5sT}{\left(sT\right)^2} \tag{2.1}$$

where *T* is the sampling period.

With the advent of switched-C filters most integrated-circuit  $\Delta\Sigma$  A/D converters became