# Control of Three-Phase, Four-Wire PWM Rectifier

Rajesh Ghosh and G. Narayanan, Member, IEEE

Abstract—This paper presents the analysis, design, and control of a four-wire rectifier system using split-capacitor topology. The proposed controller does not require any complex transformation or input voltage sensing. A detailed analysis of the distortions in the line and the neutral currents is presented. It is shown that the single-carrier-based, conventional sine-triangle PWM (CSPWM) scheme results in a peak-to-peak neutral current ripple, which is greater than the peak-to-peak ripple of any of the line currents. Also, for the same operating condition, the distortions in the line and the neutral currents increase considerably, when a three-limb boost inductor is used instead of three single-phase inductors. A three-carrier-based SPWM scheme is proposed in this paper. Compared to CSPWM, the proposed scheme significantly reduces the neutral current ripple when three single-phase inductors are used, and reduces both line and neutral current ripples when a three-limb inductor is used. The control scheme is verified through Matlab simulation. It is implemented on an field-programmable gate-array (FPGA)-based digital controller and tested on a prototype. Simulation and experimental results are presented.

*Index Terms*—AC-DC power conversion, boost rectifier, current control, digital control, four-wire converter, harmonic analysis, harmonic distortion, neutral current, sine-triangle PWM.

## I. INTRODUCTION

I N an electrical power distribution system, electrical power is typically distributed through three-phase, four-wire networks. Because of the ever-increasing computer loads, the loads supplied by the utility are increasingly of single-phase and nonlinear nature. While critical loads such as computers require well-regulated and sinusoidal voltages to be applied, these draw distorted currents from the mains at a poor power factor. Consequently, the line currents in the distribution system contain considerable lower order harmonics, the neutral wire carries excessive current, and the system operates at low input power factor. These cause considerable overheating in the neutral wire and in the distribution transformer supplying the load [1]–[3].

The computer loads could be fed from the mains through a three-phase ac–dc–ac converter [4]–[7], drawing sinusoidal currents from the mains at a high power factor and maintaining regulated and sinusoidal voltages at the output.

The above three-phase line conditioner comprises two back-to-back connected three-phase converters. The conditioner must have a four-wire output to feed several single-phase loads connected at its output. The output neutral must be connected to the mains neutral to facilitate earth fault protection

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2007.911783

for the loads and to stabilize the potential of the output neutral with respect to the potential of the source neutral [6]–[8]. The latter is absolutely essential as the load enclosures are grounded at the source neutral [8].

Both the front-end converter and the inverter could be a three-leg converter. The source and the load neutrals could be connected to the star-point of the secondary windings of an isolation transformer, whose primary is fed from the inverter [4].

Alternatively, to avoid the requirement of an isolation transformer, three-leg converters with split dc bus capacitors could be considered [5], [6]. The mains and the load neutrals could be connected to the midpoint of the dc bus. Another option is to have an additional leg in one of the two converters and to connect the two neutrals to the midpoint of this additional leg [7]. The relative merits and demerits of the two topologies have been discussed in [9], [10]. This paper deals with the analysis, design, and control of a three-leg converter with split dc bus [11], [12], which can be used as a four-wire front-end converter in three-phase transformerless line conditioner and UPS applications [5], [6].

A number of control techniques have been reported for threephase ac–dc converters [6], [10]–[19]. Most of them require complex transformations, PLL [20], and a number of voltage and current sensors. As a result, the associated control scheme becomes complex and its implementation requires large computational power.

Addressing the above issues, the indirect current control scheme has been reported for three-wire rectifier [21] and single-phase, half-bridge rectifier [22], which do not require input voltage sensing. This paper extends the above concept to four-wire PWM rectifier with the split-capacitor topology [11]. Various issues such as balancing the two halves of the dc bus and maintaining low neutral current are addressed.

The control schemes presented in [5] and [6] use a conventional sine-triangle PWM (CSPWM) scheme to generate the gating pulses for the converter switches. The three sinusoidal voltage references are compared with a common high-frequency triangular carrier. In this paper, it is shown that the above PWM scheme results in a peak-to-peak neutral current ripple greater than the peak-to-peak ripple in the line currents. A three-carrierbased SPWM scheme is proposed, which considerably reduces the rms ripple in the neutral current compared to the CSPWM scheme.

In three-phase application, a three-limb inductor is more widely used than three single-phase inductors due to cost, size and weight considerations [23], [24]. A recent publication [24] shows that the zero-sequence circulating current characteristics of parallel three-phase inverters change drastically, when a three-limb inductor replaces three single-phase inductors. In the

Manuscript received September 29, 2006; revised March 22, 2007. Recommended for publication by Associate Editor S. Choi.

The authors are with the Department of Electrical Engineering, Indian Institute of Science, Bangalore, India, 560012 (e-mail: rajesiisc@yahoo.co.in; gnar@ee.iisc.ernet.in; gnar@ieee.org).

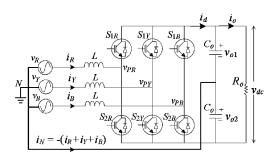

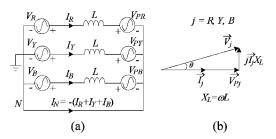

Fig. 1. Three-phase, four-wire PWM rectifier.

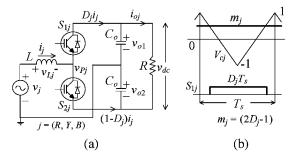

Fig. 2. (a) Single-phase half-bridge rectifier and (b) sine-triangle modulation scheme.

present work, it is shown that the switching-frequency ripples in the line and neutral currents of a four-wire converter, with the CSPWM scheme, increase considerably with the above change. It is also shown that, in addition to reducing the neutral current distortion, the proposed SPWM scheme effectively reduces the line current distortion when a three-limb boost inductor is used.

The proposed control scheme and the SPWM scheme are simulated in Matlab/Simulink. These are implemented on an field-programmable gate-array (FPGA)-based digital controller [25] and validated experimentally on a laboratory scale prototype. Simulation and experimental results are presented.

#### II. ANALYSIS AND CONTROL

This section presents the proposed control scheme for the four-wire rectifier. The analysis of the four-wire rectifier with the proposed method of control is also presented.

## A. Proposed Control Scheme

A four-wire PWM rectifier is shown in Fig. 1. For the purpose of analysis, it can be regarded as three independent single-phase half-bridge rectifiers [22], sharing a common dc bus. Fig. 2(a) shows the *j*th phase half-bridge rectifier.

The four-wire rectifier is controlled such a way that its *j*th phase averaged input current  $I_j$  is proportional to the *j*th phase input voltage  $v_j$  as shown in (1), where j = R, Y, B, and  $R_e$  is the emulated resistance of the converter [22]. Consequently, the rectifier draws balanced and sinusoidal currents from the supply mains, when the input voltages are balanced and sinusoidal

$$I_i = v_i / R_e. \tag{1}$$

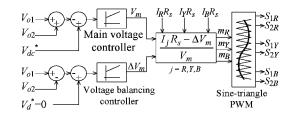

Fig. 3. Block diagram of the proposed control scheme.

In each switching cycle  $T_s$ , the switches  $S_{1j}$  and  $S_{2j}$  are operated with complementary gating pulses of duty ratios  $D_j$ and  $(1 - D_j)$ , respectively. The switching-cycle averaged pole voltage  $V_{Pj}$  is as shown in (2), where the averaged voltage drops across the inductors L are neglected and  $V_d = V_{o1} - V_{o2}$ . Equations (1) and (2) yield (3), where  $R_s$  is the current sensing gain [22]

$$V_{Pj} = V_{dc}(2D_j - 1)/2 + V_d/2 \approx v_j$$

(2)

$$I_j R_s = \frac{v_{\rm dc} R_s}{2R_e} (2D_j - 1) + \frac{v_d R_s}{2R_e}.$$

(3)

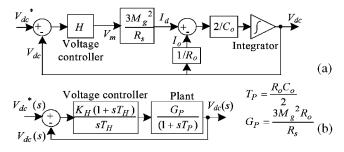

A voltage controller is used to control the output voltage  $V_{dc}$  and another to maintain balance between  $V_{o1}$  and  $V_{o2}$  (see Fig. 3). The two controller outputs are defined in (4) and (5), respectively [22]. Equations (3)–(5) yield (6)

$$V_m = V_{\rm dc} R_s / (2R_e) \tag{4}$$

$$\Delta V_m = V_d R_s / (2R_e) \tag{5}$$

$$D_j = \frac{1}{2} \left( 1 + \frac{I_j R_s - \Delta V_m}{V_m} \right). \tag{6}$$

A sine-triangle PWM scheme may be used to generate the gating pulses for the switch  $S_{1j}$  as shown in Fig. 2(b), where  $V_{cj}$  is the *j*th phase triangular carrier and  $m_j$  is the *j*th phase pole voltage reference as shown in (7). Using (2), (6), and (7), the voltage  $V_{Pj}$  is expressed as shown in (8)

$$m_j = 2D_j - 1 = \frac{I_j R_s - \Delta V_m}{V_m} \tag{7}$$

$$V_{Pj} = m_j \left(\frac{V_{\rm dc}}{2}\right) + \frac{V_d}{2} = \left(\frac{I_j R_s - \Delta V_m}{V_m}\right) \frac{V_{\rm dc}}{2} + \frac{V_d}{2}.$$

(8)

The block diagram of the proposed control scheme is shown in Fig. 3. It should be noted that due to neutral connection, the use of conventional space vector PWM for better utilization of the dc bus must be avoided [11].

Since the proposed controller does not use any input voltage sensor/estimator, PLL, current controller and complex transformation, it is much simpler than the conventional controllers presented in [6] and [13]–[18]. Consequently, its implementation would require less computational power than the above schemes.

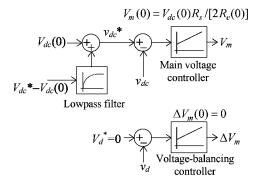

Fig. 4. Proposed soft startup algorithm.

#### B. Soft Startup Scheme

A boost rectifier draws abnormal line currents from the supply mains during startup, when its dc bus is uncharged and the initial average pole voltage is substantially different from the mains voltage. In order to prevent this, the dc bus is precharged up to a voltage  $V_{\rm dc}(0)$  (usually the peak line voltage) and the initial average pole voltage is decided based on the measured input voltage before the control pulses to the devices are released.

Unlike the conventional controller [6], the input voltage is not measured in the proposed control scheme. Let us assume that the initial conditions for  $V_{dc}$ ,  $V_d$ ,  $V_m$ , and  $\Delta V_m$  at the instant of releasing the gating pulses are  $V_{dc}(0)$ , zero,  $V_m(0)$ , and zero, respectively. With this, the *j*th phase input side of the four-wire rectifier may be represented by (9) for the first few switching cycles, where  $R_e(0)$  is the initial emulated resistance as shown in (10) [see (8)]

$$L\frac{dI_j}{dt} + R_e(0)I_j = v_j \tag{9}$$

$$R_e(0) = \frac{V_{\rm dc}(0)R_s}{2V_m(0)}.$$

(10)

It can be seen from (9) that irrespective of the power rating of the converter, the starting current can be limited by choosing a high-valued  $R_e(0)$ . Since the initial condition for  $V_m$  cannot be set at zero [see (7)], it must be selected to be small to keep  $R_e(0)$  high.

Further, the charging rate of the dc bus can be controlled to charge the dc bus capacitor slowly from  $V_{dc}(0)$  to  $V_{dc}^*$  over a period of few seconds after releasing the gating pulses. This can be achieved by varying the reference voltage  $v_{dc}^*$  gradually from  $V_{dc}(0)$  to  $V_{dc}^*$  using a lowpass filter as shown in Fig. 4. The desired initial conditions for  $V_m$  and  $\Delta V_m$  are shown in Fig. 4. Further details are given in Section VI, where an experimental verification of the soft startup scheme is presented.

#### C. Averaged Input Characteristics

Fig. 5(a) shows the averaged input side model of the rectifier. At steady state, both  $\Delta V_m$  and  $V_d$  corresponding to the *j*th phase are close to zero, and  $V_m$  is a constant [see Section II-D]. As a result, the pole voltage  $V_{Pj}$  is in phase with its respective line current  $I_j$  as shown in Fig. 5(b). If the average voltage drop

Fig. 5. (a) Averaged model of the input side of the rectifier and (b) its phasor representation.

across L is considered, unlike in (2), then the source voltage  $v_j$  is as shown in Fig. 5(b).

The corresponding input power factor is given in (11), where  $V_R$  and  $V_{P1}$  are the rms values of  $v_j$  and  $V_{Pj}$ , respectively, and  $P_o$  is the output power. The power factor is load dependent but close to unity as seen from

$$\cos\theta = \frac{V_{P1}}{V_R} = \cos\left(\frac{1}{2}\sin^{-1}\left(\frac{2P_o X_L}{3V_R^2}\right)\right).$$

(11)

## D. DC Bus Voltage-Imbalance

The dc side of the rectifier shown in Fig. 2(a) may be represented by (12) and (13), where  $R_c$  is the equivalent shunt resistance of the capacitors  $C_o$ . Equations (12) and (13) yield (14), where  $\tau = R_C C_o$  and  $v_d = v_{o1} - v_{o2}$

$$C_o \dot{v}_{o1} = D_j I_j - \frac{v_{o1}}{R_c} - \frac{v_{o1} + v_{o2}}{R}$$

(12)

$$C_o \dot{v}_{o2} = -(1 - D_j)I_j - \frac{v_{o2}}{R_c} - \frac{v_{o1} + v_{o2}}{R}$$

(13)

$$\dot{v_d} + \frac{1}{\tau} v_d = \frac{I_j}{C_o}.$$

(14)

The actual averaged input current might contain a small dc offset  $I_{o1(ss)}$  at steady state as shown in (15) due to various asymmetries in the system as pointed out in [26]–[28]

$$I_j = I_m \sin \omega t - I_{o1(ss)}.$$

(15)

The effect of the above offset current on the output voltage imbalance is shown in (16), where  $V_d(0)$  is the initial voltage imbalance at t = 0,  $\phi = \tan^{-1}(\omega\tau)$  and  $\omega\tau \gg 1$  [27]. At steady state, the first term in the RHS of (16) does not decay, when  $R_c$  is neglected (i.e.,  $R_c = \infty$ ) [27]. However, it decays to zero, when  $R_c$  is considered to be finite. The second term in the RHS of (16) causes a sinusoidal ripple in  $v_d$ , while the last term causes a steady-state dc voltage imbalance  $V_{d(dc,ss)} = -I_{o1(ss)}R_c$

$$v_d(t) = \left[ V_d(0) + \frac{I_m}{\omega C_o} \right] e^{\frac{-t}{\tau}} + \frac{I_m}{\omega C_o} \sin(\omega t - \phi) - I_{o1(ss)} R_c \left[ 1 - e^{\frac{-t}{\tau}} \right]. \quad (16)$$

Fig. 6. (a) Dc equivalent model of the *R*-phase of the rectifier system and (b) simulated dc bus voltage imbalance.

TABLE I PARAMETERS AND COMPONENTS OF THE SYSTEM

| Po                    | 1600W                         | Co                     | 2200µF                                     |

|-----------------------|-------------------------------|------------------------|--------------------------------------------|

| $V_R$                 | 110V                          | R <sub>s</sub>         | 1/10Ω                                      |

| $V_{o1}, V_{o2}$      | 200V                          | f <sub>sw</sub>        | 10kHz                                      |

| f                     | 50Hz                          | $R_c$                  | 10000Ω                                     |

| Single-phase inductor | $L_d = L_c = 8.6 \mathrm{mH}$ | Three-limb<br>inductor | $L_d = 8.2 \text{mH}$<br>$L_c = 0.132 L_d$ |

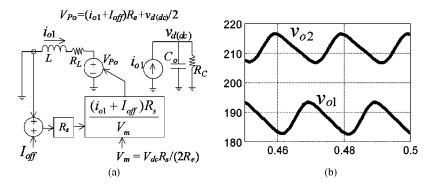

The steady offset current  $I_{o1(ss)}$  may be due to error in current measurement among the possible causes [26]–[28]. A small offset  $I_{off}$  due to the current sensor causes a corresponding offset in  $V_{Pj}$  as per (8). The effect of  $I_{off}$  on voltage imbalance can be studied using the dc equivalent model of the *R*-phase of the rectifier (without any voltage balancing mechanism) shown in Fig. 6(a). Here  $V_{Po}$  is the averaged pole voltage due to offset  $(i_{o1} + I_{off})$  as shown in Fig. 6(a). Further,  $v_{d(dc)}$  is the line-cycle average of  $v_d$  and  $R_L$  is the resistance of L. The above system may be represented by (17). The steady state values of  $i_{o1}$  and  $v_{d(dc)}$  are shown in (18) and (19), respectively, where  $R_c \gg R_e$  and  $R_e \gg R_L$

$$\begin{bmatrix} \dot{i}_{o1} \\ \dot{v}_{d(\mathrm{dc})} \end{bmatrix} = \begin{bmatrix} \frac{-(R_L + R_c)}{L} & \frac{-1}{2L} \\ \frac{1}{C_o} & \frac{-1}{R_c C_o} \end{bmatrix} \begin{bmatrix} i_{o1} \\ v_{d(\mathrm{dc})} \end{bmatrix}$$

$$+ \begin{bmatrix} D \\ 0 \end{bmatrix} I_{\text{off}} \tag{17}$$

$$I_{o1(ss)} \approx -(2R_e/R_c)I_{off}$$

(18)

$$V_{d(dc,ss)} \approx -(2R_e)I_{off}.$$

(19)

The above analysis is also verified through simulation. The R-phase of the rectifier system, without closing the voltage-balancing loop, is simulated in Matlab with the following parameters:  $P_o = 500 \text{ W}$ ,  $R_c = 10 \text{ k}\Omega$ ,  $I_{\text{off}} = 0.5 \text{ A}$ , L = 8.6 mH,  $R_L = 0.5 \Omega$  and  $V_{\text{dc}}^* = 400 \text{ V}$  (other parameters are shown in Table I). The corresponding emulated resistance  $R_e$  is 24  $\Omega$ . Fig. 6(b) shows the steady-state output voltage waveforms, where the dc voltage imbalance  $V_{d(\text{dc},\text{ss})}$  is found to be -24 V. This may also be obtained using (19).

In the proposed scheme, the dc bus voltage imbalance is corrected by adding a dc component  $\Delta V_m$  in the averaged pole voltages  $V_{Pj}$  [see (8)]. This circulates suitable dc currents through the lines, and hence through the neutral, to compensate

Fig. 7. Main voltage loop: (a) averaged model and (b) frequency domain model.

for the voltage imbalance due to various system asymmetries. The steady-state value of  $\Delta V_m \approx I_{o1(ss)}R_s$  is close to zero.

## E. Voltage Loops

Using (4) and the input-output power balance, the averaged dc bus current  $I_d$  corresponding to a given  $V_m$  is obtained as shown in (20), where  $M_g = \sqrt{2}V_R/V_{dc}$

$$I_d = \left(\frac{3M_g^2}{R_s}\right) V_m.$$

(20)

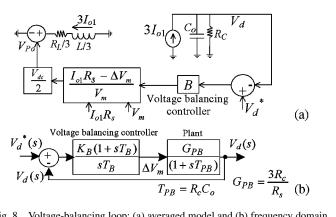

Using (20), and Figs. 1 and 3, the averaged and the frequency domain models of the main voltage loop, which controls  $V_{dc}$ , are derived. These are shown in Fig. 7(a) and (b), respectively. Fig. 6(a) may be used to obtain the averaged voltage-balancing loop and its frequency domain model shown in Fig. 8(a) and (b), respectively. The above models are useful in selection of controller parameters for the voltage loops.

## **III. PWM WITH PHASE-SHIFTED CARRIERS**

The rms ripple in the neutral current must be maintained low to reduce EMI and overall system losses [1]–[3]. The instan-

Fig. 8. Voltage-balancing loop: (a) averaged model and (b) frequency domain model.

Fig. 9. (a) Conventional sine-triangle PWM scheme and (b) proposed sine-triangle PWM scheme.

taneous neutral current  $i_N$  is as shown in Fig. 1. Though the averaged neutral current in a balanced system is zero, the instantaneous neutral current contains switching-frequency ripple as follows:

$$i_N = \tilde{i}_N = -(\tilde{i}_R + \tilde{i}_Y + \tilde{i}_B).$$

<sup>(21)</sup>

Fig. 9(a) shows the CSPWM scheme, where the pole voltage references  $m_R$ ,  $m_Y$  and  $m_B$  are compared with a common triangular carrier  $V_c$  to generate the gating pulses for the converter switches [6]. The ripples in the three line currents over a switching cycle  $T_s$  are as shown in Fig. 9(a). The current ripples in the three phases are of the same sign in a given half carrier cycle. Hence, the three get added up, resulting in a high neutral current ripple as seen from Fig. 9(a).

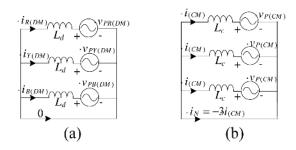

Fig. 10. (a) Differential mode ripple equivalent circuit and (b) common mode ripple equivalent circuit.

To reduce the neutral current ripple, it must be ensured that not all three line current ripples are of the same sign at a given instant. This is easily achieved by using three carriers, shifted in phase by  $120^{\circ}$  at the carrier frequency, as shown in Fig. 9(b). Compared to Fig. 9(a), there is significant reduction in the neutral current ripple as can be seen in Fig. 9(b). The effect of using phase-shifted carriers on the individual line current ripple is negligible.

It should be noted that in three-phase application, the study of single-carrier PWM versus phase-shifted, three-carrier PWM has been reported by numerous researchers [29], [30]. Since the main focus has been on minimizing the line current distortion in three-wire applications in these works, the single-carrier PWM has been found to be better than three-carrier PWM. However, in case of four-wire application, the three-carrier PWM is seen to be more effective than the single-carrier PWM in terms of neutral current distortion as seen qualitatively from Fig. 9.

Further analysis could be done considering the ripple in the instantaneous pole voltage  $v_{Pj}$ , which causes the ripples in the line and neutral currents. The voltage  $v_{Pj}$  is as shown in (22), where the switching function  $S_{1j}$  equals one, if the top device of *j*th phase is on or equals zero, if the bottom device is on. Also, in (22),  $\tilde{v}_{Pj}$  is the ripple in the pole voltage  $v_{Pj}$ , respectively

$$v_{Pj} = (2S_{1j} - 1)V_{dc}/2 = V_{Pj} + \widetilde{v}_{Pj}.$$

(22)

Similar to the line current ripples, the instantaneous sum of the ripples of the three pole voltages is nonzero. For the purpose of analysis, the *j*th phase ripple quantities  $\tilde{v}_{Pj}$  and  $\tilde{i}_j$  can be divided into a common mode and a differential mode components,  $[\tilde{v}_{P(CM)}, \tilde{v}_{Pj(DM)}]$  and  $[\tilde{i}_{(CM)}, \tilde{i}_{j(DM)}]$  as shown in (23) and (24), respectively [31]

1

$$\widetilde{v}_{P(CM)} = (\widetilde{v}_{PR} + \widetilde{v}_{PY} + \widetilde{v}_{PB})/3$$

$$\widetilde{v}_{Pj(DM)} = \widetilde{v}_{Pj} - \widetilde{v}_{P(CM)}$$

$$\widetilde{i}_{(CM)} = (\widetilde{i}_R + \widetilde{i}_Y + \widetilde{i}_B)/3$$

$$\widetilde{i}_{(CM)} = \widetilde{i}_{V} - \widetilde{i}_{VCM}$$

(24)

$$\dot{i}_{j(\mathrm{DM})} = \dot{i}_j - \dot{i}_{(\mathrm{CM})}.$$

(24)

The ripples  $\tilde{v}_{Pj(DM)}$  and  $\tilde{v}_{P(CM)}$  cause the ripple currents  $\tilde{i}_{j(DM)}$  and  $\tilde{i}_{(CM)}$  as shown in Fig. 10(a) and (b), respectively, where  $L_d$  and  $L_c$  are the differential mode and the common mode inductances offered by the inductors L (see Fig. 1) to

Fig. 11. Simulated waveforms of differential mode and common mode ripple voltages for M = 0.75 and  $f_{sw} = 2.5$  kHz.

$\tilde{i}_{j(\text{DM})}$  and  $\tilde{i}_{(\text{CM})}$ , respectively. The ripple  $\tilde{i}_{(\text{CM})}$  determines the neutral current as shown in

$$i_N = -3i_{(\rm CM)}.$$

(25)

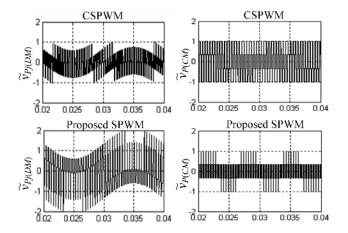

The ripple voltages  $\tilde{v}_{Pj(DM)}$  and  $\tilde{v}_{P(CM)}$  depend on the carrier frequency  $f_{sw}$ , peak-to-peak carrier,  $V_{dc}$  and  $m_j$ . A threephase, two-level voltage source inverter using both CSPWM and the proposed SPWM schemes is simulated in Matlab. The parameters are as follows:  $V_{\rm dc}=2$  p.u., peak-to-peak carrier =  $V_{\rm dc}/2$  p.u., f = 50 Hz,  $m_j = M \sin(\omega t - \phi_j)$ p.u.,  $\phi_R = 0^{\circ}$ ,  $\phi_Y = 120^\circ, \phi_B = 240^\circ$  and  $V_{P1} = M/\sqrt{2}$ . Fig. 11 shows the waveforms of  $\widetilde{v}_{Pi(DM)}$  and  $\widetilde{v}_{P(CM)}$  over a line cycle for M=0.75 and  $f_{sw}=2.5~{\rm kHz}.$  The corresponding harmonic spectra are shown in Fig. 12. As seen from the left column of Fig. 12, the dominant differential mode component due to the proposed SPWM is much higher than the corresponding component due to CSPWM. On the other hand, as seen from the right column of the figure, the dominant common mode component due to CSPWM is much higher than the corresponding component due to the proposed SPWM. Thus, the proposed SPWM leads to higher differential mode distortion, but lower common mode distortion, compared to CSPWM. Further, it is seen from Fig. 12 that both  $\tilde{v}_{Pi(DM)}$  and  $\tilde{v}_{P(CM)}$  have components around  $f_{sw}$  and its multiples. However, the two do not contain harmonics of the same order. The ripple currents  $i_{j(DM)}$  and  $i_{(CM)}$ have components at the same frequencies as those of  $\widetilde{v}_{Pj(\mathrm{DM})}$ and  $\widetilde{v}_{P(CM)}$ , respectively.

The input current total harmonic distortion factor (THD)  $I_{\text{THD}}$  is as shown in (26), where  $I_{\text{THD}(\text{DM})}$  and  $I_{\text{THD}(\text{CM})}$  are the THD components contributed by  $\tilde{i}_{j(\text{DM})}$  and  $\tilde{i}_{(\text{CM})}$ , respectively, as shown in (27). Further, in (27),  $I_{R1}$  is the rms value of the fundamental component of the line currents,  $\tilde{I}_{j(\text{DM})k}, \tilde{I}_{(\text{CM})k}, \tilde{V}_{Pj(\text{DM})k}$  and  $\tilde{V}_{P(\text{CM})k}$  are the rms values of the kth harmonic components of  $\tilde{i}_{j(\text{DM})}, \tilde{i}_{(\text{CM})}, \tilde{v}_{Pj(\text{DM})}$  and  $\tilde{v}_{P(\text{CM})}$ , respectively,  $X_d = \omega L_d, X_c = \omega L_c, \omega = 2\pi f$  rad/s, and  $V_{\text{WTHD}(\text{DM})}$ , and  $V_{\text{WTHD}(\text{CM})}$  are the weighted THD (WTHD) components of  $v_{Pj}$  as shown in (28). The rms neutral

Fig. 12. Simulated spectra of differential mode and common mode ripple voltages for M=0.75 and  $f_{sw}=2.5$  kHz.

current  $I_N$  may be normalized with respect to  $I_{R1}$  as shown in (29)

$$I_{\text{THD}} = \sqrt{I_{\text{THD}(\text{DM})}^{2} + I_{\text{THD}(\text{CM})}^{2}}$$

(26)

$$I_{\text{THD}(\text{DM})} = \sqrt{\sum_{k=2}^{\infty} \left(\frac{\tilde{I}_{j(\text{DM})k}}{I_{R1}}\right)^{2}}$$

$$= \left(\frac{V_{P1}}{X_{d}I_{R1}}\right) V_{\text{WTHD}(\text{DM})}$$

(27)

$$I_{\text{THD}(\text{CM})} = \sqrt{\sum_{k=2}^{\infty} \left(\frac{\tilde{I}_{(\text{CM})k}}{I_{R1}}\right)^{2}}$$

$$= \left(\frac{V_{P1}}{X_{c}I_{R1}}\right) V_{\text{WTHD}(\text{CM})}$$

(27)

$$V_{\text{WTHD}(\text{DM})} = \sqrt{\sum_{k=2}^{\infty} \left(\frac{\tilde{V}_{Pj(\text{DM})k}}{kV_{P1}}\right)^{2}}$$

(28)

$$I_{\text{WTHD}(\text{CM})} = \sqrt{\sum_{k=2}^{\infty} \left(\frac{\tilde{V}_{P(\text{CM})k}}{kV_{P1}}\right)^{2}}$$

(28)

$$I_N/I_{R1} = 3I_{\text{THD(CM)}}.$$

(29)

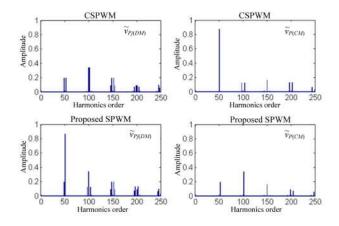

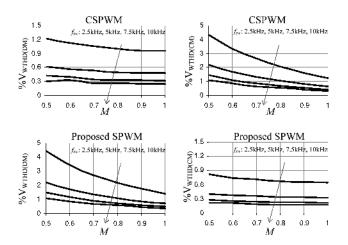

Equations (26)–(29) show that for a particular set of  $I_{R1}$ ,  $V_{P1}$ ,  $X_d$  and  $X_c$ , the line and neutral current distortions can be estimated from the weighted THD's  $V_{WTHD(DM)}$  and  $V_{WTHD(CM)}$ . Fig. 13 shows the  $V_{WTHD(DM)}$  and  $V_{WTHD(CM)}$  as obtained through simulation for different values of M and  $f_{sw}$ . Compared to CSPWM, the proposed SPWM increases the differential mode voltage distortion, while decreasing the common mode voltage distortion. The overall WTHD of the pole voltages, however, remains practically the same.

Let us consider an example, where  $V_{P1} \approx V_R$  [see Fig. 5(b)],  $L_d = L_c = 8.6$  mH and the other parameters are as shown in Table I. The estimated line and neutral current distortions are tabulated in Table II. It can be seen that the differential mode current distortion is higher under proposed SPWM scheme, while the common mode current distortion is higher in CSPWM

Fig. 13. The weighted THD's  $V_{WTHD(DM)}$  and  $V_{WTHD(CM)}$  under CSPWM and proposed PWM schemes.

TABLE II ESTIMATED LINE AND NEUTRAL CURRENT DISTORTIONS

|                                 | $L_d = L_c = 8.6 \mathrm{mH}$ |               | $L_d = 8.2 \text{mH and}$ $L_c = 0.132 L_d$ |               |

|---------------------------------|-------------------------------|---------------|---------------------------------------------|---------------|

|                                 | CSPWM                         | Proposed SPWM | CSPWM                                       | Proposed SPWM |

| I_THD(DM)                       | 2.2%                          | 4.56%         | 2.3%                                        | 4.76%         |

| I_THD(CM)                       | 4.24%                         | 1.4%          | 33.6%                                       | 11%           |

| I_THD                           | 4.77%                         | 4.77%         | 33.76%                                      | 11.9%         |

| I <sub>N</sub> /I <sub>R1</sub> | 12.7%                         | 4.2%          | 101%                                        | 33%           |

scheme. Since, the overall line current distortions under both the SPWM schemes are practically the same, the increased differential mode current distortion should not be seen as a drawback of the proposed SPWM scheme. On the other hand, the decreased common mode current ripple associated with the proposed SPWM scheme considerably reduces the neutral current distortion as seen from Table II.

It should be noted that both the common mode ripple  $i_{(CM)}$ and the distortion factor  $I_{THD(CM)}$  are zero, when the midpoint of the dc bus is disconnected from the supply neutral (see Fig. 1). This is similar to the case of a three-wire PWM rectifier [21]. As the differential mode distortion factor  $I_{THD(DM)}$  alone decides the line current THD, it is not preferred to use the proposed SPWM scheme in such application.

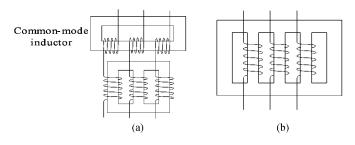

## IV. INDUCTORS FOR THREE-PHASE APPLICATION

The boost inductors L can be either three single-phase inductors or a three-limb inductor as shown in Fig. 14(a) and (b), respectively. However, a three-limb inductor is more widely used due to economic considerations as discussed in section I and in [23], [24].

Unlike single-phase inductors, a three-limb inductor does not have independent magnetic circuits for the three-phase fluxes. Compared to differential mode fluxes, the magnetic core of such an inductor offers high reluctance to the common mode fluxes. Therefore, compared to differential mode currents, the above inductor offers very low-valued inductance to the common mode currents [24]. The decreased common mode

Fig. 14. (a) Single-phase inductor and (b) three-limb inductor.

Fig. 15. Simulated line and neutral current waveforms using three single-phase boost inductors (each of 8.6 mH).

inductance has an effect of increasing the common mode ripple in line current and the neutral current. The differential mode line current ripple, however, remains same as that of using three equivalent single-phase inductors. Since, the proposed SPWM scheme considerably reduces the common mode voltage ripple (see Figs. 11 to 13), the ripples in the line and neutral currents are expected to be less under proposed SPWM scheme than under CSPWM scheme.

In order to verify the above predictions, a practical three-limb inductor is considered. The ratio of  $L_c$  to  $L_d$  for this inductor is experimentally found to be 0.132. The parameters are as shown in Table I. Using (26), (27), and (29) and Fig. 13, the estimated line and neutral current distortions under both the CSPWM and the proposed SPWM schemes are tabulated in Table II (for  $L_d =$ 8.2 mH and  $L_c = 0.132L_d$ ). These may be compared with the corresponding results as obtained using three single-phase inductors (for  $L_d = L_c = 8.6$  mH).

Fig. 16. Simulated line and neutral current waveforms using a three-limb boost inductor ( $L_d = 8.2 \text{ mH}$  and  $L_c = 0.132 L_d$ ).

Fig. 17. (a) A three-limb inductor connected in series with a common mode inductor and (b) a five-limb inductor.

### V. SIMULATION RESULTS

The four-wire rectifier system (Figs. 1 and 3) using both the CSPWM and the proposed SPWM schemes is simulated in Matlab/Simulink. The parameters used are as shown in Table I. The inductor model used in the simulation is as shown in (30), where  $v_{Lj}$  is the voltage across the *j*th phase inductor [see Fig. 2(a)],  $x = L_c/L_d$ , and  $i_{j(DM)}$  and  $i_{(CM)}$  are the instantaneous differential mode and common mode components of the line current  $i_j$ . The simulation results are shown in Figs. 15 and 16. These results agree well with the estimated results presented in Table II

$$v_{Lj} = L_d \frac{di_{j(\text{DM})}}{dt} + xL_d \frac{di_{(\text{CM})}}{dt} + R_L i_j$$

$$= L_d \frac{di_j}{dt} - (1-x)L_d \frac{di_{(\text{CM})}}{dt} + R_L i_j.$$

(30)

In order to reduce the common mode ripple current, a common mode inductor can be used in series with a three-limb inductor as shown in Fig. 17(a). Another choice is to use a five-limb inductor as shown in Fig. 17(b), which is a combination of a common mode inductor and a three-limb inductor in a single frame.

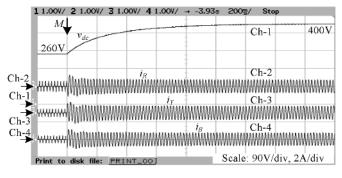

Fig. 18. Measured startup transients.

#### VI. EXPERIMENTAL VERIFICATION

This section presents the experimental setup and the various experimental results.

#### A. Experimental Prototype

The power circuit of the four-wire rectifier prototype is shown in Fig. 1. The parameters are shown in Table I. The proposed control scheme (Fig. 3) is implemented on an Altera EP1C12Q240C8 FPGA platform [25]. The total number of logic elements used is 2860.

In order to have a one-to-one comparison of the number of logic elements consumed, the synchronous reference frame control scheme discussed in [6] is implemented. This control scheme is found to consume 8496 logic elements. The requirement of additional 5636 logic elements may be attributed to the additional functional blocks, namely the PI current controllers, three-phase to dq transformation, dq to three-phase transformation and unit vector generation, which are not required in the proposed control scheme.

The main voltage loop and the voltage-balancing loop (Figs. 7 and 8) are designed for a closed loop bandwidth of 40 Hz and a phase margin of 65°. In each switching cycle  $T_s$ , the measured line currents  $i_R$ ,  $i_Y$ , and  $i_B$  are sampled at the peaks of their respective carriers  $V_{CR}$ ,  $V_{CY}$  and  $V_{CB}$  [see Fig. 9(b)]. This sampling strategy helps avoid sampling the switching noises and obtain samples closer to the averaged currents  $I_R$ ,  $I_Y$ , and  $I_B$ [32]. The output voltages  $v_{o1}$  and  $v_{o2}$  are sampled at the peak of the carrier  $V_{CR}$ .

#### B. Steady State and Dynamic Performances

During these tests, three single-phase boost inductors (see Table I) are used. To start the converter, the dc bus is precharged up to  $V_{\rm dc}(0) = 260$  V before the control pulses to the devices are released. The lowpass filter (Fig. 4) time constant is set at 400 ms. The initial condition for  $\Delta V_m$  is set at zero, while the same for  $V_m$  is set corresponding to an initial emulated resistance  $R_e(0)$  of 200  $\Omega$ . An 800  $\Omega$  load-resistor is connected across the dc bus. The measured starting transient is shown in Fig. 18, where the gating pulses are applied at an instant M. It can be seen that the proposed soft-start algorithm helps the output voltage build gradually, keeping the starting current low.

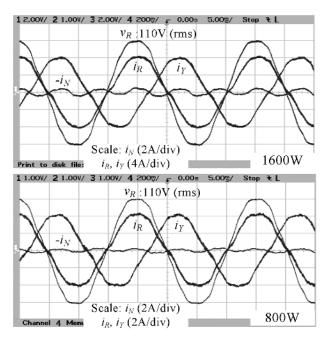

The measured input voltage, input current and neutral current at output powers of 1600 and 800 W are shown in Fig. 19. The

Fig. 19. Steady state input voltage, input current and neutral current waveforms for the output powers at 1600 and 800 W.

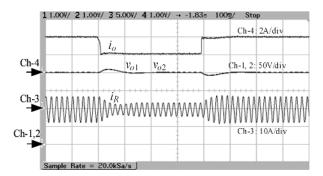

Fig. 20. Dynamic response of the four-wire rectifier system.

corresponding input current THD's are 4.3% and 4.6%, respectively, which satisfy the harmonic standard [33]. In both cases, the input power factor is close to unity and the neutral current is low.

It should be noted that during the above tests, the input phase voltages contain significant lower order harmonic distortion (see Fig. 19). Since the proposed control scheme forces the input currents to replicate their respective input voltages (1), similar lower order harmonic distortions are seen in the line currents. The triplen harmonic components of the input phase voltages result in corresponding neutral currents as seen in Fig. 19.

Fig. 20 shows the dynamic response of the rectifier system, when the output power is suddenly changed between 1600 and 800 W. The dynamic response can be further improved by using load current feedforward [34]. Fig. 20 also shows that the proposed controller maintains balance between the voltages of the two halves of the dc bus successfully during steady state as well as during transients.

Fig. 21. Steady state sampled input voltage, input current and neutral current waveforms under unbalanced input voltage condition.

## C. Effect of Input Voltage Unbalances

The control scheme presented in this paper is derived based on the assumption that the input phase voltages are balanced. In order to check its performance against input voltage unbalances, an unbalance is created by supplying the Y-phase of the rectifier through an additional series impedance of  $(5 + j6.3)\Omega$ . The corresponding experimental results for an output power of 1600 W are shown in Fig. 21. It can be seen that due to resistance emulation action [see (1)], the phase currents are roughly proportional to their respective input phase voltages. The unbalanced line currents return to the source through the neutral as shown.

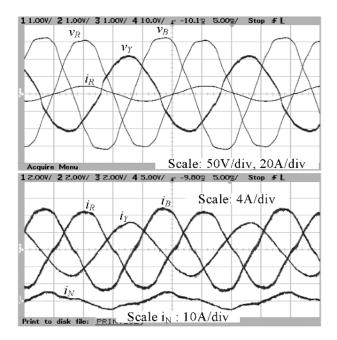

## D. The Line and Neutral Current Distortions

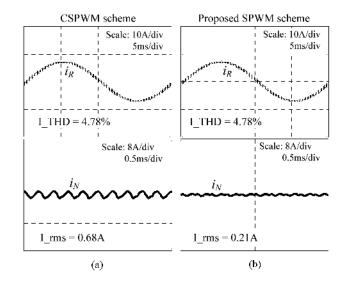

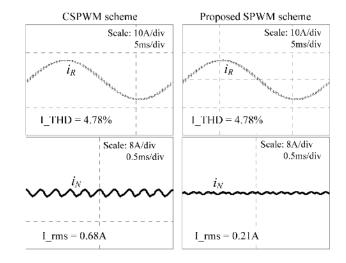

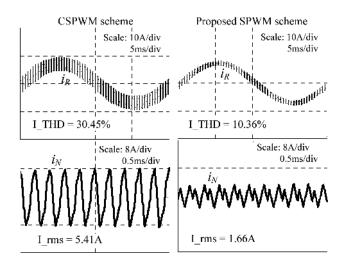

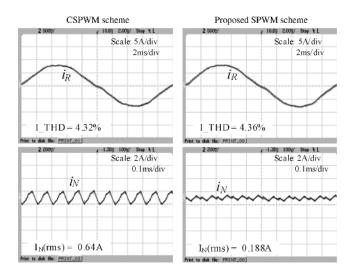

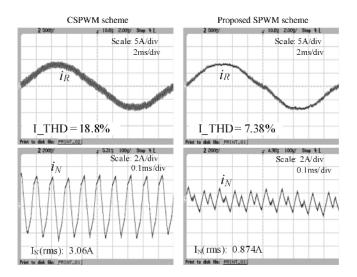

The rectifier system is tested at 1600 W output power using both CSPWM and proposed SPWM schemes. In each case, both single-phase inductors and three-limb inductor are considered (see Table I). The various experimental results are shown in Figs. 22 and 23. The measured input current THD's and the rms values of the neutral current are shown in Figs. 22 and 23.

The above experimental results agree well with the corresponding simulation results shown in Figs. 15 and 16. It can be seen that the measured line and neutral current distortions are better than the corresponding distortions as obtained through simulation. This can be attributed to the source inductances adding up to the boost inductances in the experimental setup, while the source inductances have been neglected in the simulation.

## VII. CONCLUSION

A control method is presented for a three-phase, four-wire PWM rectifier. The necessary control operations are performed by processing the measured three line currents and two output voltages measured without using input voltage information

Fig. 22. Experimental line and neutral current waveforms using three singlephase boost inductors (each of 86 mH).

Fig. 23. Experimental line and neutral current waveforms using a three-limb boost inductor ( $L_d = 8.2 \text{ mH}$  and  $L_c = 0.132 L_d$ ).

and/or any complex transformation. Two voltage controllers are used to hold the output voltage at the reference and to maintain balance between the two halves of the dc bus, respectively. A soft-startup algorithm is presented to start the converter smoothly without causing any appreciable transients. The analysis of the averaged input characteristics, dc bus voltage-imbalance, the main voltage loop and the voltage balancing loop is presented.

A three-carrier-based sine-triangle PWM (SPWM) scheme is proposed for the four-wire PWM rectifier, which considerably reduces the rms ripple in the neutral current compared to the conventional SPWM scheme, when three single-phase inductors are used as the boost inductors. Further, compared to CSPWM scheme, the proposed PWM scheme considerably reduces both the line and the neutral current distortions, when a three-limb inductor is used as the boost inductors. A complete analysis of the line and neutral current distortions is presented.

Finally, the proposed control and the PWM scheme are simulated in Matlab. These are implemented on an FPGA based digital platform and validated experimentally on a laboratory scale prototype. The simulation and experimental results are presented.

#### REFERENCES

- C. A. Quinn, N. Mohan, and H. Mehta, "A four-wire, current-controlled converter provides harmonic neutralization in three-phase, fourwire systems," in *Proc. IEEE Applied Power Electronics Conf. Expo.* (APEC), 1993, pp. 841–846.

- [2] H. L. Jou, "Performance comparison of the three-phase active-powerfilter algorithms," *Proc. Inst. Elect. Eng.—Gener. Trans. Distrib.*, vol. 142, no. 6, pp. 646–652, Nov. 1995.

- [3] H. L. Jou, J. C. Wu, K. D. Wu, W. J. Chiang, and Y. H. Chen, "Analysis of zig-zag transformer applying in the three-phase four-wire distribution power system," *IEEE Trans. Power Del.*, vol. 20, no. 2, pp. 1168–1173, Apr. 2005.

- [4] M. Dai, M. N. Marwali, J.-W. Jung, and A. Keyhani, "A PWM rectifier control technique for three-phase double conversion ups under unbalanced load," in *Proc. IEEE Applied Power Electronics Conf. Expo.* (APEC), Mar. 2005, vol. 1, pp. 548–552.

- [5] Y. K. Lo and C. L. Chen, "Three-phase four wire voltage controlled AC line conditioner with unity input power factor and minimized output voltage harmonics," in *Proc. Inst. Elect. Eng.*—*Electr. Power Appl.*, Jan. 1995, vol. 142, no. 1, pp. 43–49.

- [6] M. E. Fraser, C. D. Manning, and B. M. Wells, "Transformerless fourwire PWM rectifier and its application in AC-DC-AC converters," in *Proc. Inst. Elect. Eng—Electr. Power Appl.*, Nov. 1995, vol. 142, no. 6, pp. 410–416.

- [7] J. G. Tracy and H. E. Pfitzer, "Achieving high efficiency in a double conversion transformerless UPS," in *Proc. Annu. Conf. of Industrial Electronics Soc. (IECON)*, Nov. 2005, pp. 942–945.

- [8] IEEE Recommended Practice for Grounding of Industrial and Commercial power Systems, IEEE Std. 142-1991.

- [9] X.-B. Yang, W.-Y. Wu, and H. Shen, "Adaptive three dimensional space vector modulation in abc coordinates for three phase four wire split capacitor converter," in *Proc. 5th Int. IEEE Power Electronics Motion Control Conf. (IPEMC)*, Aug. 2006, vol. 3, pp. 1–5.

- [10] R. Zhang, F. C. Lee, and D. Boroyevich, "Four-legged three-phase PFC rectifier with fault tolerant capability," in *Proc. IEEE Power Electronics Specialist Conf. (PESC)*, Jun. 2000, vol. 1, pp. 359–364.

- [11] M. E. Fraser and C. D. Manning, "A proposed predictive average current controller for four-wire boost rectifiers," in *Proc. Inst. Elect. Eng.* —*Power Electron. Variable Speed Drives*, Sep. 1996, pp. 144–149.

- [12] M. I. M. Montero, E. R. Cadaval, and F. B. González, "Comparison of control strategies for shunt active power filters in three-phase four-wire systems," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 229–236, Jan. 2007.

- [13] Z. Chen, "Three-phase four-wire system power distribution using a power electronic converter," *IEEE Power Eng. Rev.*, pp. 47–49, Oct. 2000.

- [14] P. Verdelho and G. D. Marques, "Four-wire current-regulated PWM voltage converter," *IEEE Trans. Ind. Electron.*, vol. 45, no. 5, pp. 761–770, Oct. 1998.

- [15] M. Aredes, J. Hafner, and K. Heumann, "Three-phase four-wire shunt active filter control strategies," *IEEE Trans. Power Electron.*, vol. 12, no. 2, pp. 311–318, Mar. 1997.

- [16] F. Liccardo, P. Marino, C. Schiano, and N. Visciano, "Three-phase four-wire active front-end feeding a three-level voltage source inverter," in *Proc. IEEE Int. Symp. Industrial Electronics (ISIE)*, May 2004, vol. 2, pp. 1153–1158.

- [17] T. Noguchi, H. Tomiki, S. Kondo, and I. Takahasi, "Direct power control of PWM converter without power-source voltage sensors," *IEEE Trans. Ind. Appl.*, vol. 34, no. 3, pp. 473–479, May–Jun. 1998.

- [18] M. Malinowski, M. Kazmierkowski, S. Hansen, F. Blaabjerg, and G. D. Marques, "Virtual-flux-based direct power control of three-phase PWM rectifiers," *IEEE Trans. Ind. Appl.*, vol. 37, no. 4, pp. 1019–1027, Jul.–Aug. 2001.

- [19] A. G. Cerrada, O. P. Ardila, V. F. Batlle, P. R. Sánchez, and P. G. González, "Application of a repetitive controller for a three-phase active power filter," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 237–246, Jan. 2007.

- [20] P. Rodríguez, J. Pou, J. Bergas, J. I. Candela, R. P. Burgos, and D. Boroyevich, "Decoupled double synchronous reference frame PLL for power converters control," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 584–592, Mar. 2007.

- [21] S. Chattopadhyay and V. Ramanarayanan, "Digital implementation of a line current shaping algorithm for three phase high power factor boost rectifier without input voltage sensing," *IEEE Trans. Power Electron.*, vol. 19, no. 3, pp. 709–721, May 2004.

- [22] R. Ghosh and G. Narayanan, "A simple analog controller for singlephase half-bridge rectifier," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 186–198, Jan. 2007.

- [23] C. Y. Jeong, J. G. Cho, Y. Kang, G. H. Rim, and E. H. Song, "A 100 kVA power conditioner for three-phase four-wire emergency generators," in *Proc. IEEE Power Electronics Specialist Conf. (PESC)*, 1998, vol. 2, pp. 1906–1911.

- [24] Y. Zhang, Y. Kang, and J. Chen, "The zero-sequence circulating currents between parallel three-phase inverters with three-pole transformers and reactors," in *Proc. 21st Annu. IEEE Applied Power Electronics Conf. Expo. (APEC)*, Mar. 2006.

- [25] S. Venugopal and G. Narayanan, "Design of FPGA based digital platform for control of power electronics systems," presented at the Nat. Power Electronics Conf. (NPEC), IIT Kharagpur, India, 2005.

- [26] J. T. Boys and A. W. Green, "Current-forced single phase reversible rectifier," *Proc. Inst. Elect. Eng.*, vol. 136, no. 5, pt. B, pp. 205–211, 1989.

- [27] R. Srinivasan and R. Oruganti, "A unity power factor converter using half-bridge topology," *IEEE Trans. Power Electron.*, vol. 13, no. 3, pp. 487–500, May 1998.

- [28] Y. K. Lo, T. H. Song, and H. J. Chiu, "Analysis and elimination of voltage imbalance between the split capacitor in half-bridge boost rectifiers," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 1175–1177, Oct. 2002.

- [29] O. A. Sadaba, P. S. Girpide, J. L. Taberna, I. M. Morales, and L. M. Palomo, "Voltage harmonics generated by 3-level converters using PWM natural sampling," in *Proc. IEEE Power Electronics Specialist Conf. (PESC)*, Jun. 2001, vol. 2, pp. 1561–1565.

- [30] J. Hamman and F. S. Van Der Merwe, "Voltage harmonics generated by voltage-fed inverters using PWM natural sampling," *IEEE Trans. Power Electron.*, vol. 3, no. 3, pp. 297–302, Jul. 1988.

- [31] G. Grandi, D. Casadei, and U. Reggiani, "Common- and differentialmode HF current components in AC motors supplied by voltage source inverters," *IEEE Trans. Power Electron.*, vol. 19, no. 1, pp. 16–24, Jan. 2004.

- [32] P. Mattavelli, G. Spiazzi, and P. Tenti, "Predictive digital control of power factor preregulators with input voltage estimation using disturbance observers," *IEEE Trans. Power Electron.*, vol. 20, no. 1, pp. 140–147, Jan. 2005.

- [33] IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems, IEEE Std. 519-1992.

- [34] R. Ghosh and G. Narayanan, "Generalized feedforward control of single-phase PWM rectifiers using disturbance observers," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 984–993, Apr. 2007.

**Rajesh Ghosh** received the Diploma degree from Coochbehar Polytechnic, Coochbehar, India, in 1994, the B.E. degree from Jadavpur University, Kolkata, India, in 2000, and the M.Tech. degree from the Indian Institute of Technology, Kanpur, India, in 2001, and the Ph.D. degree from the Indian Institute of Science, Bangalore, India, in 2007, all in electrical engineering.

From 1994 to 2000, he was with the Substations Department of Calcutta Electric Supply Corporation (CESC), Ltd., Kolkata, India, where he was involved

in the maintenance and erection and commissioning of LT/HT switchgears, power, and distribution transformers. Between 2002 and 2003, he was an Electrical Engineer with GE Global research Center (JFWTC), Bangalore, India, working in the field of ac–dc power conversion and motor drives. Currently, he is working as a Design Engineer with American Power Conversion (APC), R&D Division, Bangalore, India, where he is working in the field of ac–dc–ac power conversion. His research interests are the design, analysis, and control of switched-mode power converters, UPS, and active power filters.

**G. Narayanan** (S'99–M'01) received the B.E. degree from Anna University, Chennai, in 1992, the M.Tech. degree from the Indian Institute of Technology, Kharagpur, in 1994, and the Ph.D. degree from the Indian Institute of Science, Bangalore, in 2000.

He is currently an Assistant Professor in the Department of Electrical Engineering at the Indian Institute of Science, Bangalore. His research interests include ac drives, pulsewidth modulation, multilevel inverters, and protection of power devices.

Dr. Narayanan received the Innovative Student Project Award for his Ph.D. work from the Indian National Academy of Engineering in 2000, and the Young Scientist Award from the Indian National Science Academy in 2003.