Received July 13, 2020, accepted July 30, 2020, date of publication August 10, 2020, date of current version August 21, 2020.

Digital Object Identifier 10.1109/ACCESS.2020.3015315

# Control Strategies and Power Decoupling Topologies to Mitigate $2\omega$ -Ripple in Single-Phase Inverters: A Review and Open Challenges

ADITYA R. GAUTAM<sup>10</sup>, (Member, IEEE), DEEPAK M. FULWANI<sup>10</sup>, (Member, IEEE), RAMMOHAN R. MAKINENI<sup>2</sup>, AKSHAY KUMAR RATHORE<sup>3</sup>, (Senior Member, IEEE), AND DHEERENDRA SINGH<sup>1</sup>, (Senior Member, IEEE)

<sup>1</sup>Department of Electrical and Electronics Engineering, Birla Institute of Technology and Science, Pilani, Pilani 333031, India

Corresponding author: Deepak M. Fulwani (df@iitj.ac.in)

This work was supported in part by the DST-SERB-Core Research Grant, and in part by the Ministry of Electronics and Information Technology, Government of India.

**ABSTRACT** This paper provides a comprehensive review of the control approaches and the power-decoupling topologies to mitigate  $2\omega$ -ripple problem in the single-phase inverters, its solutions, and discusses open challenges yet to be addressed. The cause and effects of  $2\omega$ -ripple problem and its solution based on the passive and active power-decoupling techniques are discussed. A subcategory of the active power-decoupling technique nominated as the control-oriented compensation technique is reviewed in detail, this technique can achieve the ripple-mitigation at the source through the control but not necessarily adds extra circuit or active filter to the system. The control-oriented compensation techniques can be applied in the two-stage DC-DC-AC converters and the single-stage inverters having a front-end control capability with the H-bridge such as in the quasi-switched-boost inverters. The merits and associated challenges of these techniques are listed and summarized in a tabular form. Finally, a conclusive discussion with open challenges is presented.

**INDEX TERMS**  $2\omega$ -ripple, single-phase inverter, control strategies, power-decoupling schemes.

# I. INTRODUCTION

Power converters are one of the important entity in the power applications such as renewable/hybrid energy applications, and the power inverters are generally used to supply AC loads in such applications. In the low power applications ( $< 5\,kVA$ ), the single-phase power converter are generally used [1]. In the literature, several topologies of the single-phase DC-AC power converters, for example, Z source inverter (ZSI), quasi-ZSI, quasi-switched boost inverter (quasi-SBI), differential inverters, and two-stage converters are extensively explored for different power applications.

The DC-AC power converters supply to AC loads with the unwanted reflection of Second-order Harmonic Current SHC) ripple ( $2\omega$ -ripple or two-time-line frequency ripple) at the DC input. In the single-stage DC-AC converter, this ripple at the DC link propagates towards the DC source and injects into the DC source if the DC link capacitance is not sufficient or no compensation technique is

The associate editor coordinating the review of this manuscript and approving it for publication was Shihong Ding.

used. The  $2\omega$ -ripple poses same problem to the three-phase DC-AC converter with the unbalanced load condition [2]. The ripple also reflects in AC-DC power conversion [3]. A general practice to avoid the injection of ripple into the DC source is to use a large size aluminum electrolytic capacitor (E-cap) at the DC-link. However, the E-caps are vulnerable to low-frequency ripple due to low ripple handling capability and high parasitic resistance [4]. The ripple causes  $i^2r$ -heating loss inside the electrolytic capacitors [5], [6]. The life-span of an E-cap is 10% - 90% of a year at  $105^{\circ}$  C [4]; quite smaller than the life of a solar PV panel ( $\approx 20$  years) in a PV system [7]. This raises an important question on the reliability of complete system. A study conducted using data of 213 failure cases from 103 grid-tied solar PV systems at the Florida solar energy suggests that 139 failures are due to the inverter failure [8]. As per a study conducted in [9], in the power converters, 51% instances of inverter's failure are due to solid-state devices and aluminum capacitors. Moreover, 21% failure instances out of 51% are due to the aluminum capacitor failures only. The film capacitor is a reliable alternative to replace the electrolytic capacitor. The low ESR

<sup>&</sup>lt;sup>2</sup>Department of Electrical Engineering, IIT Jodhpur, Jodhpur 342037, India

<sup>&</sup>lt;sup>3</sup>Department of Electrical and Computer Engineering, Concordia University, Montreal, QC 55104, Canada

value and large ripple handling capability of film capacitor makes it a suitable choice. However, an equivalent size of film capacitor is required in lieu of the electrolytic capacitor. The relative high cost of the film capacitor poses challenges to its viability [10]. However, the use of film capacitor is suitable and preferred in the active power decoupling circuits or control-oriented power decoupling techniques; a comparatively small size film capacitor is required in the active filter [11].

This paper reviews several power-decoupling techniques majorly classified as passive power-decoupling techniques (PPTs) and active power-decoupling techniques (APTs). Generally, APT adds additional power electronics circuit with an energy storage element such as film capacitor to the H-bridge. A subcategory of APTs, nominated here as the control-oriented compensation techniques (CCTs) for the two-stage DC-DC-AC power converters and single-stage inverters having front-end control-circuits with H-bridge such as in the quasi-switched boost inverters is discussed in detail. The CCTs eliminate the necessity of additional active filter. It is to be noted that the available review work in the literature [12]-[14] documents several active filter topologies to mitigate  $2\omega$ -ripple problem, however, this paper complements the available review work by providing a comprehensive review on the control-oriented techniques based on the different control strategies. The power decoupling-techniques are further categorized based on the topographical arrangement of active filter and control strategies i.e. application of power decoupling technique at (i) DC side of inverter and (ii) AC side of inverter (mixed-type). Beginning with the introduction of  $2\omega$ -ripple problem, the effect of SHC ripple on the system will be discussed. A detailed review of different  $2\omega$ -ripple mitigation techniques will be discussed. Eventually, the gaps and future scope are extracted and discussed. Section I begins with the introduction, followed by a discussion on the background of  $2\omega$ -ripple and its effect on the system in Section II. The Section III reviews several  $2\omega$ -ripple control schemes from the existing literature. In the Section IV, conclusive discussion and open problems are presented.

# II. 2ω-RIPPLE: ITS BACKGROUND AND CONSEQUENCE

For an ideal inverter, the instantaneous values of input power and output power must be equal. However, in actual scenario, there is the power mismatch between the instantaneous values of DC power and AC power; the pulsating nature of AC power causes the pulsation in the DC input power.

# A. BACKGROUND OF 2ω-RIPPLE

Suppose an inverter supplies AC load at  $\omega$  rad/s. The mathematical representation of such systems is [15],

$$v_{ac} = V_m cos(\omega t), \quad i_{ac} = I_m cos(\omega t - \theta)$$

(1a)

$$v_{ac}i_{ac} = 0.5V_mI_mcos\theta + 0.5V_mI_mcos(2\omega t - \theta)$$

(1b)

$$p_{ac} = P_o + p_r \tag{1c}$$

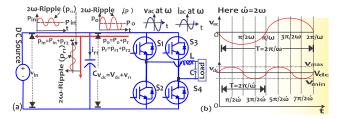

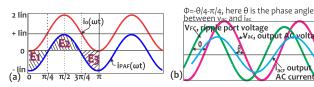

Here  $v_{ac}$  and  $i_{ac}$  are the instantaneous output AC voltage and output AC current of inverter.  $\theta$  is displacement angle. The subscript m stands for the maximum value of  $v_{ac}/i_{ac}$ . The underline part of (1c) is  $2\omega$ -power ripple pulsating over the average DC offset. The Fig. 1(a) depicts this phenomenon.

FIGURE 1. (a) Background of  $2\omega$ -ripple in single-phase inverter. (b) Waveform of AC output voltage and DC-link voltage.

In Fig. 1(a), suppose  $v_{dc}$  is the instantaneous voltage at DC-link and  $i_r$  is the current through DC-link capacitor (C) and assume  $2\omega$ -ripple passes through the capacitor only i.e.  $p_r = p_{r1}$  and therefore no ripple propagates to the input i.e.  $p_{r2} = 0$  then the instantaneous power of capacitor is,

$$p_r = v_{dc}i_r \tag{2a}$$

$$p_r = (V_{dc} + v_r)i_r = V_{dc}i_r + v_ri_r$$

(2b)

Here  $V_{dc}$  is the average voltage of DC-link and  $v_r$  is  $2\omega$ -ripple voltage. For large value of C, the value of  $v_r$  in (2b) is negligible, this implies that  $v_r i_r \ll V_{dc} i_r$ . This gives,

$$p_r = V_{dc}i_r \tag{3}$$

Using the value of  $p_r$  from (1c) in (3) gives,

$$i_r = \frac{0.5V_m I_m cos(2\omega t - \theta)}{V_{dc}} = \frac{P_{rms} cos(2\omega t - \theta)}{V_{dc}}$$

(4)

Here rms stands for root-mean-square. Also,

$$i_r = C \frac{dv_r}{dt} \tag{5}$$

Using (4) and (5) gives,

$$dv_r = \frac{P_{rms}}{CV_{dc}}cos(2\omega t - \theta)dt \tag{6}$$

Integrating (6) from both sides and using upper and lower limits in it from Fig. 1(b) gives,

$$\int_{v_l}^{v_u} dv_r = \int_{\frac{\pi}{4\omega}}^{\frac{3\pi}{4\omega}} \frac{P_{rms}}{CV_{dc}} cos(2\omega t - \theta) dt$$

(7a)

$$\Delta v = v_u - v_l = \frac{P_{rms}}{2\omega C V_{dc}} \left[ sin(2\omega t - \theta) \right]_{\frac{\pi}{4\omega}}^{\frac{3\pi}{4\omega}}$$

(7b)

$$\Delta v = \frac{P_{rms}}{\omega C V_{dc}} cos\theta \tag{7c}$$

Here  $\Delta v$  is the peak to peak voltage ripple and subscripts u and subscript l stand for upper limit and lower limit respectively. For the given value of  $\Delta v$ ,  $P_{rms}$ ,  $\theta$  and  $V_{dc}$ , the size of capacitor required at the DC-link is,

$$C \ge \frac{P_{rms}}{\omega \Delta v V_{dc}} cos\theta = \frac{P_{rms}}{\omega \Delta v V_{dc}} p.f.$$

(8)

Here p.f. stands for power-factor.

# B. CONSEQUENCES OF 2ω-RIPPLE ON SYSTEM

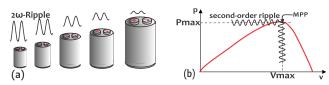

The  $2\omega$ -ripple poses several issues related to cost, size, efficiency, reliability and stability on the system [16], [17]. This ripple forces an over-rated design of components and increases the peak-rating of system. Consequently,  $i^2r$  in the system increases. The  $i^2r$ -loss inside the E-cap causes heating of electrolyte [4], [18]. To restrict the DC-link voltage ripple to  $\pm 1\%$ , an E-cap of  $\approx 6$  mF is required for a 100 W-inverter operating at 60 Hz with 48 V-DC-link voltage [19], the Fig. 2(a) depicts this issue. An injection of  $2\omega$ -ripple into the fuel cell causes fuel-starvation and stress on the membrane [20]. The low frequency ripples (<400 Hz) should be kept < 10% for the long life expectancy [21], [22]. In [21], it is established that for a solid-oxide fuel-cell, a 17%-reduction in the peak-value of current ripple (from 22% to 5%) improves its efficiency by 5% that can go upto 9% for the ripple compensation by 31%. In PFC based LED lighting, the low frequency causes the flickering effect [19], [23], [24]. In the MPPT operation of the solar-PV or fuel cell, a pulsation of the  $2\omega$ -ripple about the maximum power points (MPPs) of the power/current/voltage may shift the actual MPPs. According to [25], a decrease of 5% in the efficiency and power of the solar-PV with MPPT operation is observed for an 8% ripple in the rms value of MPPs. In the Fig. 2(b), the effect of the  $2\omega$ -ripple on the MPPs is shown using P-V diagram [26]. Table 1 summarizes the Section II(B). The injection of  $2\omega$ -ripple into the battery

FIGURE 2. (a) For the same voltage rating, a large size E-cap decouples more  $2\omega$ -ripple. (b) Effect of  $2\omega$ -ripple on MPPT operation [27].

causes heating effect. According to [28], a current ripple more than 8% may badly affect the electrodes and electrolyte of the battery and reduces the performance and efficiency of the

system. Moreover, ripple increases the voltage/current stress on the system components [34], [35].

#### **III. CLASSIFICATION OF RIPPLE MITIGATION METHODS**

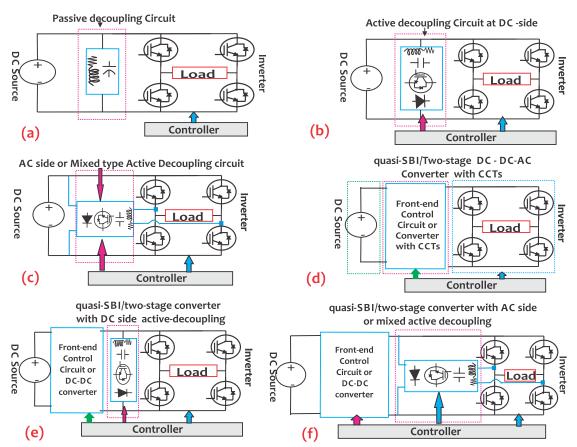

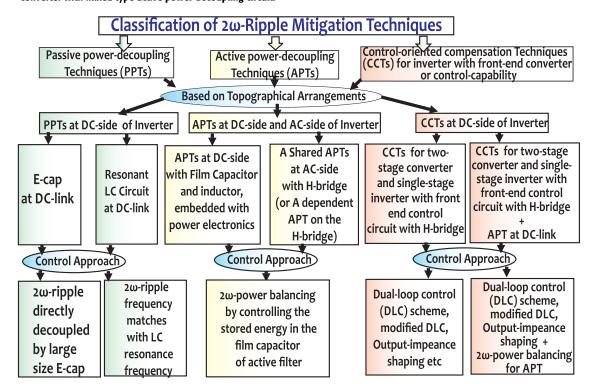

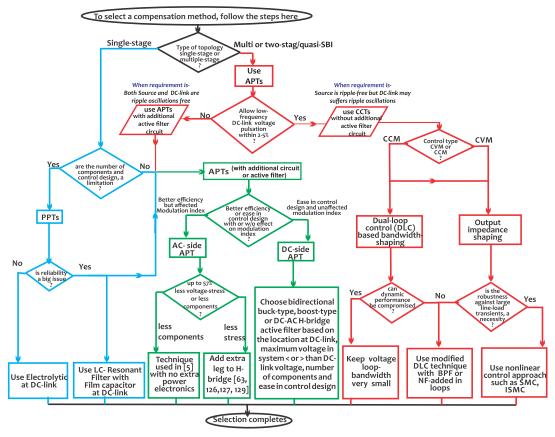

The propagation of  $2\omega$ -ripple towards the DC source can be avoided by storing the  $2\omega$ -power ripple in a large E-cap at the DC-link (at the input of inverter) or forcing the voltage to swing at  $2\omega$  directly at the DC-link itself or allowing the indirect voltage-swing across the film capacitor (other than at DC-link) through a power electronics based control. Besides this, the control-oriented techniques can directly be used in the two-stage DC-DC-AC converters and single-stage inverters with the front-end control-capability; this eliminates the necessity of additional active filter. Some control-oriented techniques are the output-impedance shaping, loop-bandwidth shaping in dual-loop control, generation of the ripple-free reference of the input current and forcing the ripple flow in the direction other than the DC source. In general, these different techniques can be classified as (i) passive power-decoupling techniques (PPTs) (ii) active power-decoupling techniques (APTs), and its sub-category (iii) control-oriented compensation techniques (CCTs) for inverter with front-end converter or in-built front-end control circuit. These techniques can be implemented (a) at DC side of the inverter and (b) at AC side of the inverter; a mixed-type arrangement. The Fig. 3 and Fig. 4 depict basic methodologies and control techniques of  $2\omega$ -ripple mitigation.

#### A. PASSIVE POWER-DECOUPLING TECHNIQUES

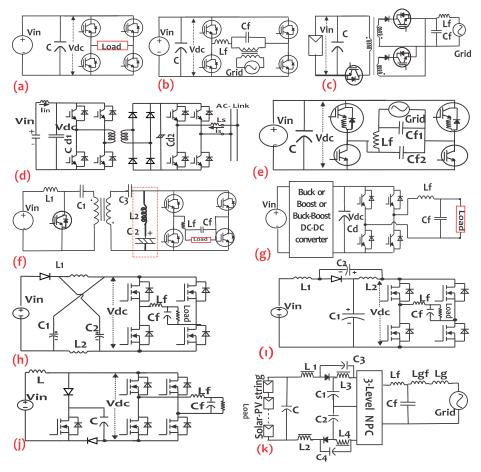

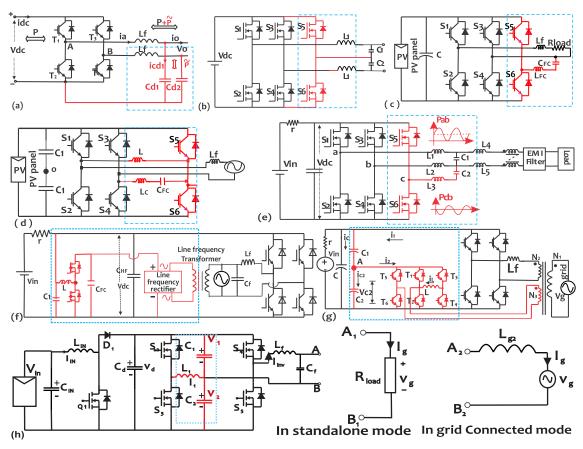

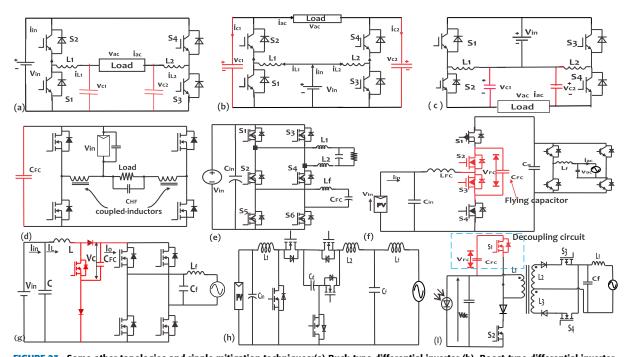

PPTs are conventional and easy to implement without using control schemes. The topologies shown in the Fig. 5(a-b) are the conventional stand-alone voltage source converter (VSC) [36]–[38] and grid-connected (VSC) [39]–[41] respectively.

Some of the isolated topologies are shown in the Fig. 5(c)-(d)-(f). A flyback-type center-tapped inverter (see Fig. 5(c)) is proposed in [42] for the isolated operation. The Fig. 5(d) shows a high frequency-link two-stage DC-DC converter for the high power applications [43], [50]–[52]. The converter shown in Fig. 5(e) can step-up/down voltage

TABLE 1. Summary of cause, effect and design constraint of  $2\omega$ -ripple.

| Affected system/algorithm | Effect on system                       | Cause and constraint                                           | Reference        |

|---------------------------|----------------------------------------|----------------------------------------------------------------|------------------|

| Capacitor at DC-link      | Heating effect; Reduction in life of   | Large ESR causes $i^2r$ -losses and                            | [19], [28], [29] |

|                           | aluminum capacitor by $10\% - 90\%$    | high temperature: a $10^{\circ}$ C rise in temperature,        |                  |

|                           | a year at $105^o$ $C$                  | reduces life of E-cap by half; To limit voltage                |                  |

|                           |                                        | pulsation within $\pm 1\%$ , a $\approx 6 \ mF$ E-cap required |                  |

|                           |                                        | for $100 W, 60 Hz$ —inverter                                   |                  |

| Fuel cell stack           | Poor efficiency and affect life        | $2\omega$ -ripple > $10\% - 15\%$                              | [21], [22], [30] |

| Fuel cell MPPT            | Excessive use of $H_2/O_2$ or reactant | $2\omega$ -ripple > 8%                                         | [28]             |

| Solar PV MPPT             | Poor efficiency; Nuisance tripping     | $2\omega$ -ripple > 10%; Oscillation about MPP                 | [25]             |

| Battery                   | Affect the electrodes and electrolyte, | $2\omega$ -ripple > 8%; Heating due to hysteresis              | [28]             |

| LED lights                | Flickering effect; Visual fatigue      | No time delay or latency effect                                | [19], [24], [31] |

|                           |                                        | in LED lights against $2\omega$ -ripple flicker                | [23], [32]       |

|                           |                                        | should be restricted within 10%                                |                  |

| System components         | Over-rated design; High stress         | low frequency and increase in peak values                      | [33]             |

|                           |                                        |                                                                |                  |

FIGURE 3. Topographical arrangements of power decoupling techniques: (a) PPTs at DC link (b) APTs at DC link (c) APTs at AC side; a mixed type arrangement (d) ZSI, quasi-SBI or two-stage DC-DC-AC converter with CCT only (e) ZSI, quasi-SBI or two-stage DC-DC-AC converter with active power decoupling circuit at DC side (f) ZSI, quasi-SBI or two-stage DC-DC-AC converter with mixed type active power decoupling circuit.

**FIGURE 4.** Flow chart of classification of  $2\omega$ -ripple mitigation techniques.

FIGURE 5. Passive power decoupling techniques. (a) Isolated Voltage source inverter [36]. (b) Grid-tied-Voltage source converter [39]. (c) Flyback-type center-tapped inverter [42]. (d) Inverter with front-end dual-bridge converter with high-frequency DC-link [43]. (e) Transformer-less buck and boost inverter topology [44]. (f) Pulse-link DC-AC converter [45]. (g) Two-stage DC-DC-AC converter (having a front-end buck or boost or buck-boost DC-DC converter) [46]. (h) Z-source inverter. (i) Quasi-Z source inverter. (j) Quasi-switched boost inverter. (k) Three-level single-phase impedance source inverter(Fig. 5(h-k) [47]-[49]).

without using a front-end DC-DC converter or a transformer [44]. All these topologies use a large electrolytic capacitor at the DC link [53]–[55]. The large size inductors used in the current-fed inverter can minimize the ripple at the input [56], and also by employing a tuned-resonant filter at the DC-link, the  $2\omega$ -ripple can be decoupled [57]. In [45], authors have proposed a pulse-link DC-AC converter (see Fig. 5(f)). In this topology  $L_2C_2$  makes the resonating tank. This resonant-filter is tuned at  $2\omega$  such that the most of  $2\omega$ -ripple passes through the low impedance  $L_2C_2$ branch when the resonance frequency  $(\omega_0)$  matches with 2ω. The two-stage DC-DC-AC converter are popular in the RE energy applications [46], [58]–[60] (see Fig.5(g)). Conventionally, a large size E-cap is used at the DC link in these topologies. These topologies still have a challenge of accidental short-circuiting of the switches in the same leg(s) of the inverter [61]. The impedance-source inverters (ISIs) [47]-[49] are the good choice in such limitations and operating conditions. However, these topologies require large size impedance-source network to filter low-frequency  $2\omega$ -ripple [62]-[64]. In Fig.5(h-k), Z-source inverter, quasi-Z source inverter and quasi-switched boost inverter are shown.

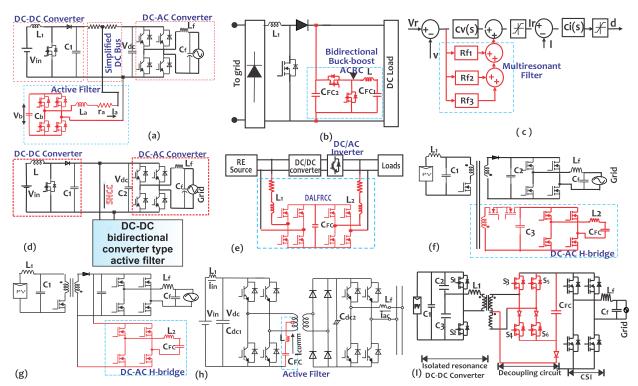

#### **B. ACTIVE POWER-DECOUPLING TECHNIQUES**

Generally, APTs use additional power electronic devices and energy buffer especially a thin film capacitor. An inductor is also required to transfer  $2\omega$ -power ripple between the coupling point of active filter at the DC or AC side of the main circuit and the buffer capacitor connection point. The ripple control scheme is combined with the main control. In general, the control aims to balance the required  $2\omega$ -ripple power in the system by exchanging the reserved power of buffer capacitor in the active filter. Nevertheless, a proper selection of the film capacitor is a priori to keep the design optimum. The minimum size of the filter capacitor required in the different APTs is tabulated in the Table 2.

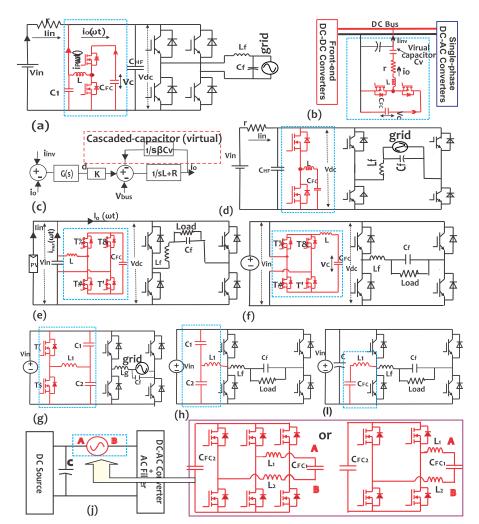

FIGURE 6. Active power-decoupling circuits at DC-link. (a) CPS-PAF-Boost type [65]. (b) ALFRCD with cascaded capacitor [66]. (c) Current control loop of ALFRCD with virtual cascaded capacitor [66]. (d) Bidirectional-buck type APT [67], [68]. (e) FB-RCR circuit [68], [69]. (f) Ripple-port circuit [19]. (g) Dual-voltage control decoupling strategy using a symmetric half-bridge circuit with H-bridge [70], [71]. (h) Dependent power decoupling with two-phase legs [1], [72], [73] and (i) [73], [74]. (j) Series power decoupling technique with two legs [75] and three legs [76].

#### 1) APTs AT DC SIDE/LINK

In the DC side arrangement, the active power decoupling circuit is directly shunted at the DC-link by replacing the large size E-cap (see Fig. 6(a) to Fig.6(g).

These topologies are independent of the H-Bridge of the DC-AC power converter. The circuits in the Fig. 6(h) and Fig. 6(i) are the dependent decoupling circuits and utilize a part of the H-Bridge. Recently, some series power decoupling technique as shown in Fig. 6(j) are proposed [75]–[77]. This type of decoupling techniques add a series active decoupling circuit between the source and H-Bridge. In general, the active filter topologies are buck-type, boost-type, buck-boost type [65]–[67], [69], [78]–[81] and H-bridge type [19], [69], [82], [83], and the basic principle of ripple decoupling in the APTs using active filter (especially H-bridge type) at the DC-side is as follows [19]. Suppose  $C_{FC}$  is the film capacitor for power decoupling in active filter.

The voltage across the film capacitor is  $v_c$  is given by,

$$v_c = V_{c_m} cos(\omega t + \varphi) \tag{9}$$

Here  $V_{c_m}$  is maximum value of the capacitor voltage and  $\varphi$  is an arbitrary phase-angle. The current through the capacitor is,

$$i_{c} = C_{FC} \frac{d}{dt} V_{c_{m}} cos(\omega t + \varphi)$$

(10)

The decoupling power ripple is given by,

$$p_{FC} = v_c(t)i_c(t) \tag{11a}$$

$$= v_c(t)C_{FC}\frac{d}{dt}V_{c_m}cos(\omega t + \varphi)$$

(11b)

$$= -0.5C_{FC}V_{c_m}^2\omega sin(2\omega t + 2\varphi) \qquad (11c)$$

The  $2\omega$ -power ripple at DC-link is equal to  $p_{FC}$ . Applying power ripple balance at the DC-link and using (1cc)

FIGURE 7. Working principle of (a) CPS-PAF [65], [69] (b) ripple port control [19].

and (11c),

$$0.5V_m I_m cos(2\omega t - \theta) = -0.5C_{FC} V_{c_m}^2 \omega sin(2\omega t + 2\varphi)$$

(12a)

$$P_o cos(2\omega t - \theta) = -0.5C_{FC} V_{c_m}^2 \omega sin(2\omega t + 2\varphi)$$

(12b)

In (12bb), the amplitude of  $V_{c_m}$  is adjusted by control such that  $P_o = 0.5 C_{FC} V_{c_m}^2 \omega$  which follows,

$$sin(2\omega t + 2\varphi) = cos(2\omega t - \theta) \tag{13}$$

Solving (13) gives,

$$\varphi = -\frac{\pi}{4} - \frac{\theta}{2} \tag{14}$$

The active filter decouples  $2\omega$  power ripple if (14) holds and  $P_o = 0.5 C_{FC} V_{c_m}^2 \omega$  is satisfied by some value of  $V_{c_m}$ . The control adjusts  $\varphi$  and  $V_{c_m}$  to buffer  $2\omega$ -power ripple.

In [65], a current pulsation smoothing-parallel active filter (CPS-PAF) is proposed. The CPS-PAF consists of a small film capacitor and a conventional non-isolated buck/boost circuit (see Fig. 6(a)). This circuit behaves like a currentsource. The working principle of power decoupling is shown in the Fig. 7(a) [65], [69]. In Fig. 6(a), the controller continuously compares the input current  $(I_{in})$  with instantaneous value of the DC-link current  $(i_o(\omega t))$ . For  $I_{in} > i_o(\omega t)$  in interval  $0 - \pi/4$  and  $3\pi/4 - \pi$ , the capacitor  $C_{FC}$  stores energy (boost-mode) and for  $I_{in} < i_o(\omega t)$  in interval  $\pi/4$  –  $3\pi/4$  releases the energy (buck-mode). For energy stored (say  $E_1 + E_3$ ) equals to energy released (say  $E_2$ ) by  $C_{FC}$ , the low frequency pulsation at the DC-link is zero.  $C_{HF}$ takes care of high frequency ripples. However, the active power imbalance between input and output of PAF and the power loss of PAF cause a decrease in the voltage of  $C_{FC}$  resulting in a lower value of  $V_c$  than the DC-link voltage. In such case the PAF gets short-circuit the input and output and ripple elimination is affected [69]. To resolve this problem, a mixed type APT version of CPS-PAF is proposed in [65] (see Fig. 9(f)). The grid feeds the rectified power to  $C_{FC}$  through the line transformer to compensate the losses. However, the system becomes bulky and complex. In Fig. 6(b), a buck-boost type active low-frequency ripple control device (ALFRCD) is shown that is proposed in [66] for the building-integrated photo-voltaic (BIPV) systems. The concept of ripple mitigation using ALFRCD is same as presented in [65]. However, in [66], a virtual capacitor is added in series with the inductor of the active filter through the control (see Fig. 6(b)). The virtual capacitor is realized by adding an integrator in the current control-loop (see Fig. 6(c)).

The control scheme forces the output current of the active filter  $(i_o)$  to track the DC-link current  $(i_{inv})$ .

The important requirement of this scheme is to keep the voltage of the film capacitor  $(C_{FC})$  higher than the bus voltage. Wang et al. proposed a similar bidirectional buck type-APT (see Fig. 6(d)) in [67]. The working principle of the power ripple decoupling control scheme is same as in [65] (see Fig. 7(a)). In [67], a DCM control scheme is used such that the  $C_{FC}$  stores all the  $2\omega$ -ripple and L functions like a power transfer element. Therefore, L does not store decoupling power that is good in terms of the power-density. Also, unlike CPS-PAF, the voltage of  $C_{FC}$  is less than the DC bus or DC-link voltage or any other voltage in the system. It is to be noted that the discontinuous current mode (DCM) operation of the front-end DC-DC converter of two-stage converter minimizes the input  $2\omega$ -ripple inherently due to the less interaction of DC source and DC-link during discontinuous operation [84]. The buck-derived and boost-derived two-stage converter has minimum  $2\omega$ -ripple at the input in the DCM operation. A four-switch based bidirectional fullbridge-ripple current reduction (FB-RCR) circuit is shown in the Fig. 6(e) [69], [75]. The working principle of the FB-RCR is same as of CPS-PAF of [65]. However, unlike [65], there is no requirement of the line-frequency transformer with the rectifier. The internal energy losses which are the cause of constant voltage decrease of  $C_{FC}$  in the FB-RCR circuit are compensated by sourcing power from the input source itself. However, the FB-RCR circuit contains four switches which operate at the high frequency. Therefore, the system becomes bulky and the switching loss increases. A similar APT based on the ripple-port concept is presented in [19] (see Fig. 6(f)). The control design is based on (9)-(14). The working principle of this technique is depicted in the Fig. 7(b). In the Fig. 6(f) and Fig. 7(b),  $\phi$  is the phase difference between the instantaneous voltage of the film capacitor  $(v_{FC})$  across  $C_{FC}$  and output voltage of inverter  $(v_{ac})$ , and  $\theta$  is the displacement angle between instantaneous value of  $v_{ac}$  and  $i_{ac}$ .

In [70], Tang et al. have proposed a dual voltage control strategy for the symmetric half-bridge circuit with H-bridge. The circuit diagram is shown in the Fig. 6(g). The two capacitors  $(C_1, C_2)$  are used to decouple the power ripple. The control scheme aims to modulate the switches of half bridge such that the voltages across the two capacitors are equal and  $2\omega$ -pulsating voltage component over the offsets of voltages are out of phase by 180°. Following the power balancing condition, the required power decoupling condition

$$\varphi = 0.5 tan^{-1} \left( \frac{-V_{rms}}{\omega L_f I_{rms}} \right) \tag{15a}$$

$$\varphi = 0.5 tan^{-1} (\frac{-V_{rms}}{\omega L_f I_{rms}})$$

(15a)

$$V_c = \sqrt{\frac{\sqrt{(V_{rms} I_{rms})^2 + (\omega L_f I^2 m)^2}}{\omega (2C_f - L_f (2\omega C_f)^2)}}$$

(15b)

Here  $I_{rms}$  and  $V_{rms}$  are rms values of AC current and voltage.  $I_m$  is maximum current of AC current.  $C_f = C_1 = C_2$ .  $V_c$  is rms offset-voltage of capacitors.  $\varphi$  is phase difference between the grid voltage and pulsing voltage in the capacitor.

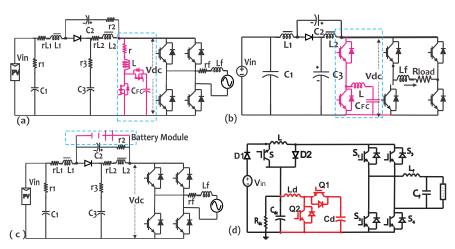

FIGURE 8. quasi-ZSI with DC-side (a) boost-type active filter [85] (b) bidirectional buck-boost type active filter [86] (c) battery module [87] and (d) boost-type APT [66] for single-phase switched boost inverter [88].

The active power decoupling techniques shown in the Fig. 6(h) and Fig. 6(i) share at least one of the phase of H-bridge and active filter. Therefore, such APTs are dependent on the H-bridge. This affects the modulation signal of inverter. In the two-phase legs topologies (see Fig. 6(h-i)), the DC voltage utilization is always kept  $\leq 0.5$  to avoid the over-modulation and to keep the size of film capacitor minimum.

In the impedance source inverters, the minimization of size of impedance network in the presence of  $2\omega$ -ripple is a challenge. In [85], a hysteresis current controlled active filter is proposed to confine  $2\omega$ -ripple within the active filter (see Fig. 8(a)). The control logic is same as shown in the Fig. 7(a). However, the ripple control design for the quasi-ZSI is somewhat more challenging than the H-bridge converter. A bidirectional buck-boost type active filter for quasi-ZSI is shown in the Fig. 8(b) [86]. The design of active filter is similar as shown in the Fig. 6(d). In [87], a comprehensive design of asymmetric ZS-network in the perspective of high frequency and low frequency ripple minimization is discussed the first time. The optimum design of ZS network is presented for a battery energy-stored quasi-Z source inverter (see Fig. 8(c)). A study on  $2\omega$ -power decoupling in switched boost inverter is carried out in [88] (see Fig. 8(d)). The boost-type APT proposed in [66] is used in this work. As discussed before, the E-cap is most vulnerable component, a pre-analysis of the effect of impedance network of quasi-ZSI and shoot-through duty on the remaining useful life of E-cap may help designers to predict the overall life of system [89].

### 2) APTs AT AC SIDE; A MIXED TYPE ARRANGEMENT

This arrangement of APT utilizes a part of DC side and a part of AC side of the main circuit, and the active filter generally shares atleast one leg of the inverter. The AC-side power decoupling techniques improve the power conversion efficiency in comparison to the DC-side power as the low frequency power pulsations are forced to confine at the AC-side [90], [91]. Some of recent AC side APTs are shown in the Fig. 9. In [1], Serban has proposed an APT using two decoupling capacitors at the AC-side (see Fig. 9(a)). The technique does not add extra power electronics to main circuit. However, the DC-link voltage and current loading of the inverter set a trade-off for the values of decoupling capacitors. Consequently, the efficiency of system is affected. The utilization factor of storage elements is < 50%. The circuits of Fig. 9(b-g) add extra switches to the system. The inclusion of third leg with the H-Bridge reduces the stress on the switches by 57% in comparison to H-Bridge [93], [96]. Zhu et al. in [91] proposed a ripple confinement control technique for the circuit shown in Fig. 9(b). This technique implements a voltage waveform control [90] to confine the pulsating power within the capacitors at AC-side. A brief explanation of the waveform control is presented in the subsection III(D). A 100% utilization of the storage elements can be achieved using this method. However, this technique adds an extra pair of switches (see Fig. 9(b)) and increases the voltage-stress on the capacitors. In [92], Chen et al. have proposed a  $2\omega$ -power pulsation mitigation at the DC-link using the SVPWM method for the circuit proposed in [97] (see Fig. 9(c)). This technique eliminates capacitance and minimizes voltage and current stress on the switches for a range of the power factor. However, two extra switches are required and the total device power rating is increased by 50%. An APT for grid connected AC-DC power converter as shown in the Fig. 9(d) is proposed in [93]. This APT significantly reduces the size of DC-link capacitor. The stress on switches is reduced up to 70% for all the power factor. The study analyzes the effect of grid-side inductance as well and provides design guidelines for different system parameter for the practical implementation. Another APT is proposed in [94] for microinverter applications; a problem

FIGURE 9. Mixed type of APTs without adding extra power electronics (a) proposed in [1] and adding extra pair of switches (b) proposed in [91] (c) proposed in [92] (d) proposed in [93] (e) proposed in [94] (f) Modified version of CPS-PAF scheme based circuit in Fig. 6(a) [65] (g) Hybrid filter [57] (h) proposed in [95].

from the Google little box challenge. The proposed technique is implemented on the GaN-based  $3\phi$ -inverter topology as shown in the Fig. 9(e). In the circuit of Fig. 9(e), the load is fed between the phase a and b and the decoupling circuit is placed between phase b and c. The basic principle of ripple cancellation is that the control keeps the sum of instantaneous powers  $p_{a-b}$  and  $p_{b-c}$  a constant value. Therefore, the ripple is confined within the AC side decoupling circuit and DC side becomes ripple-free. The GaN switches have comparatively better figure of merits such as low on-state conduction loss, wide-band gap, switching frequency and efficiency. A similar topology is presented in [97]. In [57], a hybrid filter is proposed as shown in Fig. 9(g). In the hybrid filter, there are three legs. The ripple energy is stored in both, capacitor C<sub>1</sub> and inductor, L. Using Kirchhoff's current Law at A in Fig. 9(g),

$$i_C = i_1 - (i_2 + i_{C2}) \tag{16}$$

In Fig. 9(g), for  $C_2 \ll C_1$  the  $i_{C2}$  can be neglected in (16),

$$i_C \approx i_1 - i_2 \tag{17}$$

The hybrid filter generates  $i_2$  such that  $i_1 = i_2$ . For this the inductor current is controlled to keep the voltage across  $C_2$ constant. However, the voltage  $v_{c2}$  keeps on decreasing due to

internal loss of filter. The hybrid filter alone is not sufficient. Therefore, an additional leg (switches  $T_5$ ,  $T_6$ ) is added to import the energy from the grid as shown in Fig. 9(g). This is a mixed type APT. Nevertheless, a small capacitor can be used for the power decoupling. However, the extra switches in third leg make the circuit bulky. In [95], authors presented a single-phase inverter topology that is a combination of front-end boost stage, a half-bridge inverter stage, and a buck-boost type power decoupling stage (see Fig, 9(h)). The size of decoupling capacitor used in this work is optimized based on efficiency of converter, average dc-link voltage, and dc voltage utilization factor of the capacitors.

An AC side active filter is proposed for the quasi-ZSI in [63]. The control confines  $2\omega$  ripple within the LC of filter using a third leg besides the H-bridge (see Fig. 10). The control aims to switch the third leg such that  $2\omega$ -ripple energy stored in L and  $C_{FC}$  of filter is exchanged; the power decoupling principle is same as presented in [19]. However, the energy stored in inductor is also considered. In Fig. 10, the decoupling ripple power between B and C is given by,

$$p_{FC} = v_c i_{FC} + L \frac{di_{FC}}{dt} i_c$$

$$= \frac{V_{c_m}^2 C_{FC} (1 - \omega^2 L C_{FC}) sin2(\omega t + \varphi)}{2}$$

(18a)

$$= \frac{V_{c_m}^2 C_{FC} (1 - \omega^2 L C_{FC}) sin2(\omega t + \varphi)}{2}$$

(18b)

TABLE 2. Design of minimum value of filter capacitor.

| Topology or Filter type            | Filter location                                            | Minimum design value                                                                                                                                                                                                                                                                                                         | Reference  |

|------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1) E-Cap                           | DC-link at DC side                                         | $C_{dc} = \frac{P_o}{\omega V_{dc} \Delta v}$ $C_{FC} = \frac{P_{in}(P_{in} - V_{in}I_{trans})}{\omega V_c V_{in}(2P_{in} - V_{in}I_{trans})}$                                                                                                                                                                               | [19]       |

| 2) LC series filter                | Embedded with centre taping                                | $C_{FC} = \frac{\frac{dC_{in}(P_{in} - V_{in}I_{trans})}{dV_{in}(P_{in} - V_{in}I_{trans})}$                                                                                                                                                                                                                                 | [98]       |

| (See Fig. 22(h))                   | of transformer in half-active bridge in DC-DC-AC converter | $w_{cvin}(z_{lin} - v_{in} t_{trans})$                                                                                                                                                                                                                                                                                       |            |

| 3) LC filter in H-Bridge type      | Embedded with active                                       | $C_{FC} = \frac{2P_{in}}{\omega V_c^2 (1 - \omega^2 L)}$                                                                                                                                                                                                                                                                     | [83]       |

| active filter (See Fig. 22(f-g))   | filter at DC side                                          | $c_m$ (- $c_m$ )                                                                                                                                                                                                                                                                                                             |            |

| 4) Flying capacitor                | Flying capacitor in modified                               | $C_{FC} = \frac{2W}{\omega(v_v^2 - v_t^2)}$                                                                                                                                                                                                                                                                                  | [81]       |

| (See Fig. 23(f))                   | boost- derived DC-DC-AC converter                          | $\omega(c_u \cup c_l)$                                                                                                                                                                                                                                                                                                       |            |

| 5) Extra third leg and LC filter   | Embedded with active                                       | $C_{FC} = \frac{4V_m I_m}{4V_m I_m \omega^2 L + V_{1}^2 M_{32} \omega}$                                                                                                                                                                                                                                                      | [63], [99] |

| with H-Bridge(See Fig. 10)         | filter at AC side                                          | $4 v_m r_m \omega = B + v_{dc} m_{32} \omega$                                                                                                                                                                                                                                                                                |            |

| 6) E-cap at DC-link                | At DC-link of two-                                         | $C_{dc} = \frac{1.359S}{\omega \Delta v V_{do}}$                                                                                                                                                                                                                                                                             | [59]       |

| 7) Capacitors and Inductors        | stage converter<br>quasi-Z Source                          |                                                                                                                                                                                                                                                                                                                              | [62]       |

| (See Fig. 5(i))                    | network                                                    | $C_{1} = C_{2} = \frac{(1-2D_{sh})^{2} + \sqrt{(1-2D_{sh})^{2} (\frac{V_{m}I_{m}}{2V_{dc}i_{Lr}})^{2} - (\frac{4\omega LI_{dc}(D_{sh}-1)}{V_{dc}})^{2}}}{L_{1} = L_{2} = \frac{v_{cr}(1-2D_{sh})}{2\omega i_{Lr}} \frac{4\omega^{2}L}{2U_{cr}}$ $C_{1} = \frac{v_{cr}(1-2D_{sh})^{2}}{2U_{cr}} \frac{4\omega^{2}L}{2U_{cr}}$ |            |

| 8) E-cap at DC-link with           | E-cap at DC-link                                           | $L_1 = L_2 = \frac{2}{2\omega i_{Lr}}$ $C_{dc} = \frac{2T_{ac}\Delta P}{\Delta v(2V_c + \Delta v)}$                                                                                                                                                                                                                          | [100]      |

| control strategy proposed in [100] | of two-stage converter                                     | $\Delta v (2V_{dc} + \Delta v)$                                                                                                                                                                                                                                                                                              |            |

| 9) Capacitors                      | High gain q-SBI                                            | $C_1 = \frac{D_{sh}(1 - D_{sh})(1 - 2D_{sh})}{2v_1\%(1 - 4D_{sh} + 2D_{sh}^2)fR_L}$                                                                                                                                                                                                                                          | [101]      |

| (See Fig. 20(d))                   | Network                                                    | $C_1 = \frac{D_{sh}(1 - D_{sh})(1 - 2D_{sh})}{2v_1\%(1 - 4D_{sh} + 2D_{sh}^2)fR_L}$ $C_2 = \frac{(1 - D_{sh})^2}{2v_2\%(1 - 4D_{sh} + 2D_{sh}^2)fR_L}$                                                                                                                                                                       |            |

| 10) CPS-PAF                        | Embedded with active                                       | $C_{FC} = \frac{0.422\pi P_{in}}{\omega(V_s^2 - V_i^2)}$                                                                                                                                                                                                                                                                     | [65]       |

| (See Fig. 6(a))                    | filter at DC side                                          | $\omega(v_u-v_l)$                                                                                                                                                                                                                                                                                                            |            |

| 11) LC filter                      | Embedded with the                                          | $C_{FC} = rac{V_m I_m}{\omega V^2}$                                                                                                                                                                                                                                                                                         | [79]       |

| (See Fig. 23(e))                   | main circuit at AC side                                    | $^{\omega_{\gamma_c}}$                                                                                                                                                                                                                                                                                                       |            |

In Table 2, Input power,  $P_{in}$ ; input voltage,  $V_{in}$ ; Peak to peak ripple voltage across  $C_{FC}$ , v; Upper voltage limit of v,  $V_u$ ; Lower voltage limit of v,  $V_l$ ; Average voltage across filter capacitor ( $C_{FC}$ ),  $V_c$ ; Maximum voltage across filter capacitor,  $V_{cm}$ ; Transformer current,  $I_{trans}$ ; maximum voltage/current at inverter output,  $V_m / I_m$ ; DC-link voltage,  $V_{dc}$ ; DC-link current,  $I_{dc}$ ; Modulation index,  $M_{32}$ , series inductance with  $C_{FC}$ , L; Apparent output power of inverter, S; Peak-peak DC-link voltage ripple,  $\Delta v$ ; Shoot-through duty,  $D_{sh}$ ; Desired amplitude of  $2\omega$ -ripple in through inductor,  $i_{Lr}$ ; Desired amplitude of  $2\omega$ -ripple across  $C_{transformer}$ ; Time period of AC output,  $T_{ac}$ , Power mismatch during  $T_{ac}$ ,  $\Delta P$ ; Capacitors used in [101],  $C_1$ ,  $C_2$ ; Peak-to-peak voltage ripple (of  $C_1$ ,  $C_2$ ),  $v_1$ ,  $v_2$ ; Simplified equivalent DC load,  $R_L$ ; switching frequency, f; angular supply frequency of inverter,  $\omega$ , Buffer energy, W.

FIGURE 10. Mixed type active decoupling circuit for the quasi-ZSI [63].

To decouple the  $2\omega$ -power ripple, the addition of the  $2\omega$ -ripple power component of (1cc) and  $p_{FC}$  in (18bb) should equate to zero i.e.  $p_r + p_{FC} = 0$ . This implies,

$$P_o cos(2\omega t - \theta) = 0.5V_{c_m}^2 C_{FC} (1 - \omega^2 L C_{FC}) sin(2\omega t + 2\varphi)$$

$$\tag{19}$$

Here  $V_{c_m}$  is the maximum value of the voltage across the  $C_{FC}$  and  $i_{FC}$  is the current through L.  $P_o = 0.5V_{rms}I_{rms}$ . To decouple the power ripple the control follows  $P_o = 0.5V_{c_m}^2C_{FC}(1-\omega^2LC_{FC})$  and  $\theta = -0.5\varphi + \frac{\pi}{4}$ .

Recently, a research has been conducted on high frequency ripple at source in the impedance source inverters [102], [103]. However, the focus of this review work is low-frequency ripple ( $2\omega$ -ripple) hence effect of high frequency is not covered here.

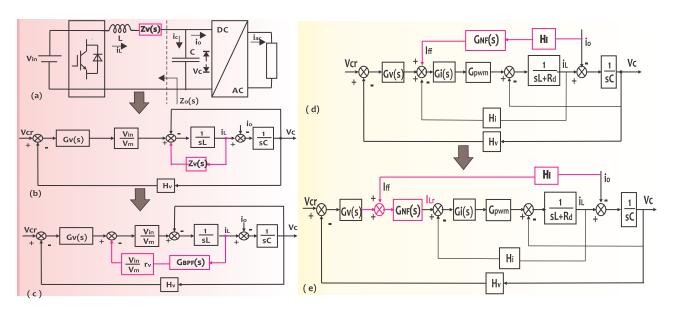

# C. CONTROL-ORIENTED COMPENSATION TECHNIQUES (CCTs)

Two-stage DC-DC-AC converters and single-stage DC-AC converters with front-end control capability can mitigate the ripple at input using the suitable control, this eliminates the necessity of active filter. The main concept is to design a control scheme that restricts the propagation of  $2\omega$ -ripple towards the DC source(s) while forcing the ripple to confine at the DC link. However, this causes a deliberated increase in  $2\omega$ -pulsation at the DC-link. This may affect the THD level of output of the inverter. According to European standards (EN50160) for the public distribution systems, the low frequency voltage pulsation of the DC bus-voltage should be kept within 2% range and the THD level of output of the inverter should be kept within 5% [104]. Therefore, an optimum design of the DC-link capacitor is involved. The ripple can be eliminated completely by using an active filter at the DC bus. The Fig. 11 shows block diagrams of the stand-alone and grid-connected DC-DC-AC converter with active-filter and without active-filter at the DC-link.

# 1) CCTs WITHOUT ADDITIONAL ACTIVE FILTER

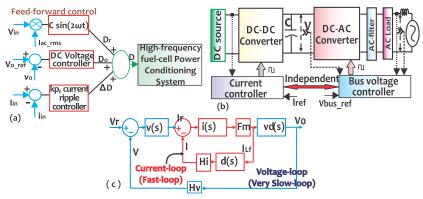

Kwon *et al.* have proposed a current-fed resonant push-pull converter and DC-AC converter based power conditioning system (PCS) for the fuel-cell application

FIGURE 11. Two-stage DC-DC-AC converter. (a) Stand-alone/Grid-tied without active-filter. (b) Stand-alone/Grid-connected with active-filter.

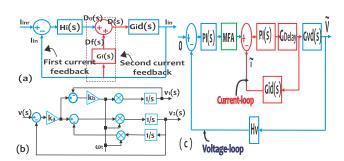

with a ripple-mitigation compensator [34]. The control block-diagram is shown in the Fig. 12(a). The control generates a duty  $(D_0)$  for the DC voltage regulation in the closed-loop. A feed-forward controller takes care of the  $2\omega$ -ripple by adding ripple-cancellation duty  $(D_r)$  to  $D_o$ . To reduce the ripple further, a perturbed duty  $(\Delta D)$ is generated using the current control-loop and added to give overall duty  $(D = D_o + D_r + \Delta D)$ . However, the performance of the feed-forward controllers are poor in terms of disturbance rejection and robustness against parametric uncertainty [105]. Feedback control approaches are widely used in the different applications such as tracking, regulation, disturbance rejection, robust control. In literature, the concept of the ripple-mitigation using the feed-back control in the two-stage converters is put forward in the two perspective. First one is based on the adopting a modified dual-loop control method. The method utilizes a current mode control (CMC) scheme. Second method is based on the output-impedance shaping. The method of output-impedance shaping can be implemented in a voltage mode control (VMC) i.e. using a single control loop also.

The CMC-based dual-loop control method has an inner current-loop and an outer voltage-loop. To ensure the ripple-reduction at the input of the two-stage converter, the interaction between the inner-loop and outer-loop is avoided such that disturbances in the voltage-loop do not pass to the current-loop [17], [105], [106]. One way to achieve this is to make a separate current-loop control and voltage-loop control as shown in the Fig. 12(b) [105]. However, in such schemes, the current-loop of the first-stage should be designed to get a very high gain at  $2\omega$ . This makes

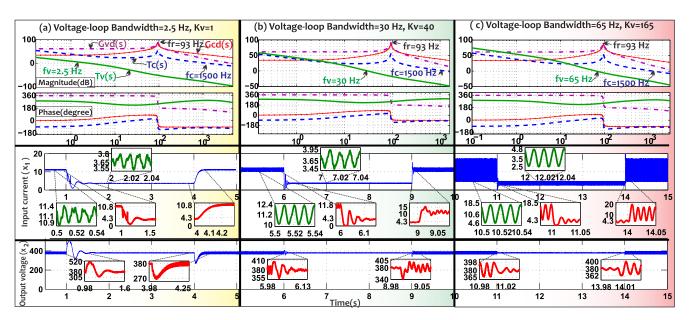

the real-time implementation challenging due to hardware limitations [105]. Liu and Lai have proposed a dual-loop control method for the front-end converter of a fuel-cell sourced DC-DC-AC converter [106]. The Fig. 12(c) depicts the dual-loop control method. The basic concept of the ripple reduction proposed in [106] is based on the bandwidthshaping. Instead of making the independent current-loop and voltage-loop, the bandwidth (BW) of voltage-loop is reduced significantly. According to [106], a reduction in the  $2\omega$ -ripple at the input can be achieved provided that the BWs of inner-loop and the outer-loop have a separation of half-decade (at least) from  $2\omega$  frequency. The basic idea is the minimization of  $2\omega$ -ripple component in the reference current of the inner-loop controller. However, the very low BW of the voltage-loop causes the sluggish or poor system response at the load transients. Therefore, this method has a trade-off between the  $2\omega$ -ripple-reduction and dynamic performance. In Fig. 14, the effect of bandwidth of voltage-loop on the ripple-reduction and dynamic performance is depicted using simulation results. These results are presented for an 1 - kW boost-derived DC-DC-AC converter having input voltage, 120 V; DC-link voltage, 380 V; L = 1 mH; C = $360 \mu F$  and AC voltage 230 V, 50 Hz. In Fig. 14, the  $f_v$  and  $f_c$ are cut-off frequencies/BWs of voltage-loop and current-loop respectively.  $G_{vd}$  and  $G_{cd}$  are control to voltage and control to current transfer functions. Tv and  $T_c$  are closed-loop-gains of voltage-loop and current-loop respectively. The results of Fig. 14 are summarized in Table 3.

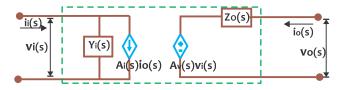

Recently,  $2\omega$ -ripple problem is addressed in conjunction with the hybrid parameters of DC-DC converter. These parameters relate the input-output behavior of DC-DC converter. A general input-output relation using the hybrid parameters of two-port network (see Fig. 13) is given by [108],

$$\begin{bmatrix} \tilde{v}_o(s) \\ \tilde{i}_i(s) \end{bmatrix} = \begin{bmatrix} A_v(s) & Z_o(s) \\ Y_i(s) & A_i(s) \end{bmatrix} \begin{bmatrix} \tilde{v}_i(s) \\ \tilde{i}_o(s) \end{bmatrix}$$

(20)

$Z_o(s)$  and  $Y_i(s)$  are output impedance and input admittance respectively, generally used for the stability analysis of the cascaded system.  $A_o(s)$  is audio-susceptibility parameter used for the estimation of input-output noise-transmission and

FIGURE 12. (a) Feed-forward scheme [34]. (b) Independent current & voltage loops [105]. (c) Dual loop control with very low voltage loop bandwidth [106].

TABLE 3. Comparison of simulation results for different voltage-loop bandwidths or  $f_V$  [107](see Fig. 14).

| Parameters                   | $f_v = 2.4Hz$ | $f_v = 30Hz$ | $f_v = 65Hz$ |

|------------------------------|---------------|--------------|--------------|

| 1) $\%$ $2\omega$ -ripple in | 4.5           | 21           | 125          |

| input current                |               |              |              |

| 2) %Overshoot/               | +37/-29       | +7.9/-10.5   | +4.5/-4.7    |

| Undershoot in                |               |              |              |

| DC link voltage              |               |              |              |

| 3) Settling time (ms)        | 600/250       | 130/50       | 20/10        |

| of voltage at load           |               |              |              |

| application/removal          |               |              |              |

FIGURE 13. Two-port network of DC-DC converter: Hybrid parameters.

$A_i(s)$  is the back-current gain parameter. The parameters  $Z_o(s)$  and  $A_i(s)$  are used for the  $2\omega$ -ripple mitigation in the two-stage converters. However,  $Z_o(s)$  parameter is widely explored in the output impedance shaping methods and a few methods have used  $A_i(s)$  parameter (see Fig. 18) [108].

In the output-impedance shaping method, the control modifies the output-impedance of the front-end DC-DC converter such that the  $2\omega$ -ripple see more impedance in the direction of DC source. This method achieves the ripple-suppression at the input, however the control causes poor dynamic performance of system; the high output-impedance of system leads to poor system dynamics [109], [110]. In both the methods (i.e. dual-loop control method and output-impedance-shaping), there is a need to maintain the sufficient bandwidth of the voltage-loop throughout the desired frequency band of the operation.

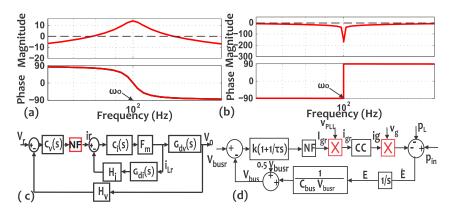

Recently, some modified and improved control techniques have been proposed using the above mentioned concepts to minimize the  $2\omega$ -ripple at the DC input and to improve the system response simultaneously [17], [33], [58], [105], [108], [111]–[118]. These control schemes use resonant filters, for instance, notch-filter (NF) or band-pass filter (BPF) in the current or voltage loop. The basic principle is to minimize the  $2\omega$ -ripple in the reference of input current or to sufficiently reduce the bandwidth of the voltage-loop at  $2\omega$  only while maintaining high bandwidth of the voltage-loop at the other frequencies. The similar methods have been presented in the context of the power-factor correction (PFC) AC-DC converter [13], [14], [74], [119], [120]. However, the focus of this work is limited to review the existing literature in the context of the DC-AC power converter or inverter. The band-pass filter (BPF) and notch filter (NF) are generally used to mitigate the  $2\omega$ -ripple without affecting the dynamic performance of the system. The characteristics of BPF and NF are shown in the Fig. 15(a) and Fig. 15(b) using the Bodeplot. The BPF allows to pass a certain range of the frequencies of the input signal. The output signal leads the input signal by  $\pi/2$  rad in 0 to  $\omega_o$  range and lags by  $\pi/2$  rad beyond the  $\omega_o$ . Therefore, a total of  $\pi$  rad phase-shift occurs. The NF filter has inverse characteristics of the BPF. The NF allows all the frequencies except the frequencies located in a very narrow range of the resonance frequency  $(\omega_o)$ . A notch-filter also gives a phase-change of  $\pi$  rad for a transform of the input signal to the output signal, the phase is negative for the frequencies below  $\omega_o$ .

In [16], the authors have proposed NF-added to the voltage-loop in the dual-loop control for a standalone DC-DC-AC converter. The reference inductor current is generated by passing the output of voltage controller through NF. Therefore, the method is named as notch-filter inserted current reference (NF-CR) scheme. The control block-diagram is shown in the Fig. 15(c). The NF attenuates  $2\omega$ -signal in reference of the inductor current. This minimizes the  $2\omega$ -ripple in input current. In [105], a control scheme is proposed for a grid-connected two-stage converter. A current controller is used with the first-stage and DC bus control is achieved by the grid-connected DC-AC converter. The method adopts a grid-side based  $2\omega$ -ripple compensation. A quasi-notch filter (quasi-NF) is added in the voltage-loop of the second-stage of the converter. The transfer function of quasi-NF is,

$$G_{NF}(s) = \frac{s^2 + \frac{\omega_o}{Q_z}s + \omega_o^2}{s^2 + \frac{\omega_o}{Q_p}s + \omega_o^2}$$

(21)

Here, Quality factor, Q is related as  $|Q|_{dB} = |Q_p|_{dB} |Q_z|_{dB}$ .  $|Q_z|_{dB}$  and  $|Q_p|_{dB}$  are the quality factors of zero and pole respectively. The quasi-NF provides a much smaller voltage-loop gain than the current-loop gain at  $2\omega$ . This minimizes the  $2\omega$ -ripple at the input. This method retains the good dynamic performance of the system at all other frequency except the frequencies about and at  $2\omega$ . However, Q of the quasi-NF should be designed properly. Similar to [105], an another grid-side based  $2\omega$ -ripple compensation is adopted in [17]. The control scheme is shown in the Fig. 15(d). The control avoids the interaction of current-loop and voltage-loop at  $2\omega$ . However, the control design is involved to develop an LTI model from the time varying system model (see Fig. 15(d)); the two multiplications just before and after the current controller (CC) make model time varying. All three methods discussed above use notch filter. The use of the notch-filter may introduce a significant negative phase-shift to the frequencies lower than the characteristic frequency of notch filter [115]. This may introduce instability to the system.

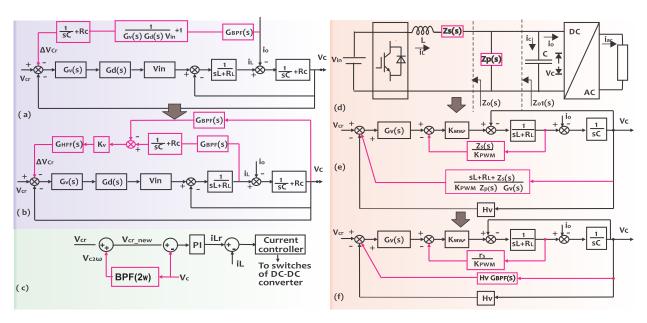

In [115], Zhang *et al*. have proposed a voltage mode control (VMC) based band-pass filter incorporated into the inductor feedback path for a buck-derived two-stage converter (see Fig. 16(a-c)). The method is based on the output-impedance shaping. In Fig. 16(a), a virtual impedance  $(Z_{\nu}(s))$  is added in series with the inductor. The concept is, to increase the impedance of inductor branch at  $2\omega$  frequency

FIGURE 14. Effect of bandwidth of voltage-loop in dual-loop control: trade-off between ripple-reduction and dynamic performance of DC-DC-AC converter [107].

**FIGURE 15.** (a) Bode plot of BPF. (b) Bode plot of NF. (c) NF-CR control scheme [16]. (d) Control scheme based on NF proposed in [17].

such that the impedance of DC-link capacitor branch is less than the impedance of inductor branch. This compels the  $2\omega$ -ripple to pass through the capacitor instead of the inductor branch. Using Fig. 16(b), the impedance of the inductor branch is,

$$Z_o(s) = -\frac{v_c(s)}{i_L(s)} = \frac{sL + Z_v(s)}{1 + G_v(s)\frac{V_{in}}{V_{oo}}H_v}$$

(22)

Here,  $G_v$  is voltage-loop controller,  $H_v$  is voltage sensor gain,  $V_m$  is PWM gain.  $Z_v(s)$  is the virtual impedance added in the current feedback path. Suppose  $Z_v(s)$  is a virtual resistance,  $say r_v$ . Therefore, the method can be named as virtual resistance scheme (VRS) [115]. In (22), an increase in  $Z_o(s)$  is achieved by increasing the value of  $r_v$ . However, this decreases the magnitude of the loop-gain in the low frequency range [122]. To balance this, the gain of Gv(s) can be decreased. However, this reduces the bandwidth of voltage-loop and hence degrades the dynamic performance

of the system. Therefore, there is a trade-off between the design of  $r_v$  and bandwidth of the voltage-loop. Eventually, the results are the same as of the dual-loop control of [106]. This problem is solved by adding a BPF in the current feedback path instead of using a constant  $r_v$  only (see Fig. 16(c)). The BPF is tuned at  $2\omega$  and hence provides a high gain at  $2\omega$  only. This adds a high virtual impedance in series of inductor branch at  $2\omega$ . This reduces  $2\omega$ -ripple at the DC input without affecting the dynamic performance. However, adding a BPF leads a  $-\pi/2$  to  $\pi/2$  phase-rotation about the characteristic frequency of the BPF. Therefore, in [58], Zhang et al. further extended their work to resolve the challenges of [115] by adopting the current mode control (CMC) approach for the buck-derived two-stage converter. The work has presented different improved control strategies. The first control strategy, namely notch filter-inserted load current feed-forward scheme (NF-LCFFS), is realized by adding an NF in the load current in a feed-forward way

FIGURE 16. (a)-(b)-(c) A BPF based control scheme proposed in [115]. (d) NF-LCFFS and (e) NF-CR-LCFFS proposed in [58].

FIGURE 17. (a)-(b) VMC-LCFFS proposed in [121], (c) CMC-based control scheme proposed in [111], and (d)-(e)-(f) BPF-CVFS proposed in [33].

(see Fig. 16(d)). It is worth noting that the load current feed-forward control schemes improve the dynamic performance at the load-transients [123]. Therefore, the dynamic performance of the system is better. The NF attenuates the  $2\omega$ -ripple in the current-loop, therefore the  $2\omega$ -ripple reduces at the input of the two-stage converter. However, the voltage-loop in the Fig. 16(d) may contaminate the reference current of the inner-loop. Therefore, a further improvement is proposed by merging NF-CR scheme of [16] with the NF-LCFFS, and hence called NF-CR+LCFFS. It is worth to note that the NF-CR scheme has an NF already to minimize  $2\omega$ -ripple from the current reference of the inner-loop. A simplified block diagram is shown in

the Fig. 16(e) where the two NFs are transformed to one. A single NF added at the output of the summing point after the voltage controller eliminates the requirement of the two NFs. This scheme almost eliminates the  $2\omega$ -ripple and also improves the dynamic performance of the system. However, the feed-forward schemes are susceptible to the disturbances and lack of the robustness as mentioned before. Moreover, NF may induce instability to the system as it affects the bandwidth of the voltage-loop. A detailed analysis and comparison of the control schemes of [115] and [58] are presented in [33]. A voltage control mode based load-current feed-forward scheme (VMC-LCFFS) is proposed in [121]. The control block-diagram of the VMC-LCFFS is shown in

the Fig. 17(a). The  $2\omega$ -ripple reduction utilizes the concept of modification in the reference value of DC-bus voltage in agreement with the desired pulsation in the DC bus voltage at  $2\omega$ . This makes DC-bus capacitor to have nearly all the  $2\omega$ -ripple. It is to be noted that the bus voltage is no longer constant but pulsates at  $2\omega$  (due to the addition of  $\Delta V_{cr}$  term with  $V_r$ ). A BPF is required with the load current feed-forward path to take-out the  $2\omega$ -ripple from the load current  $(i_o)$  which then generates a desired  $\Delta V_{cr}$ that is to be added in  $V_r$ . The presence of integrator in the LCFFS path result into continuous integration action. This results into the rapid growth of the DC-bias in the LCFFS controller that leads to incorrect voltage tracking. Therefore, a high-pass filter (HPF) is also added at the end of LCFF path (see Fig. 17(b)). The scheme minimizes the  $2\omega$ -ripple while retaining the good dynamic performance. However, the control design is involved and the control of the VMC-LCFFS depends on the accuracy of the system parameters. A simple CMC-based control method for the said problem is proposed in [111]. This control scheme is similar to the control scheme proposed in [121]. The control block diagram is shown in the Fig. 17(c). The DC-link voltage reference is modified by adding  $V_{c_{2\omega}}.$  The  $V_{c_{2\omega}}$  is extracted by passing the DC-link voltage through a BPF. The modified reference voltage  $V_{cr_{new}}$  having  $2\omega$  voltage ripple cancels  $2\omega$ -voltage ripple of the actual DC-link voltage  $(v_c)$ . This results in a ripple-free current reference in the current controlloop. A comparison of these control schemes is given in the [33] in the perspective of the output-impedance shaping. A similar control scheme i.e. BPF-incorporated capacitor voltage feedback scheme (BPF-CVFS) as presented in [111] is discussed in [33]. However, this control scheme is based on VMC method unlike the CMC method of [111]. The block-diagram of BPF-CVFS is shown in the Fig. 17(d-f). These all control schemes of [58], [115] are discussed for a buck-derived DC-DC-AC converter. These schemes are further explored for the boost converter in [117].

An effective use of the NF and BPF is proposed in [108] with the back-current gain based approach (using  $A_i(s)$ ). The control block-diagrams are shown in the Fig. 18(a-b).

FIGURE 18. Back-current gain based scheme with (a) NF (b) BPF.

$A_i(s)$  relates input current  $(i_{in}(s))$  with the output current  $(i_o(s))$  of a system (e.g. DC-DC converter). In [108], it is established that for a VMC based control, the voltage-loop has a little effect on the  $2\omega$ -ripple attenuation. However, the  $2\omega$ ripple reduction can be achieved for  $\omega_o < 2\omega$ .  $\omega_o$

is the resonance frequency of LC circuit of the DC-DC converter. This is achieved by using average CMC scheme. However, this scheme also trade-off between ripple-reduction and dynamic performance. Therefore, further improvements in the back-current gain control scheme are made using (i) NF embedded in the voltage feedback branch and (ii) BPF embedded in the current feedback branch.

An  $2\omega$ -ripple mitigation technique is proposed in [124] for a fuel-cell sourced current-fed dual half bridge (CF-DHB) converter. A phase-shift control scheme is adopted that regulates the DC voltage and minimize the  $2\omega$ -ripple. The optimized duty is set to 0.5. The PI controls the DC-link voltage and a proportional resonant (PR) controller (tuned at  $2\omega$ ) suppresses  $2\omega$ -ripple at the source. The PR controller modifies the main phase-shift angle to eliminates the input current ripple. The PR controller is similar to an integrator having infinite DC gain at characteristic frequency. Tuning PR to very low  $\omega_0$  forces a difficult implementation of it on the low cost controller board (such as 16-bit DSP) [125]. In [126], authors have proposed a sinusoidal charging scheme for the dual-active-bridge based Si-charger and GaN-charger with the reduction in size of the capacitor at the DC-link using resonant controller and rotating frame control approach. The objective is achieved by injecting  $2\omega$ -ripple into the battery for the charging purpose. The size of DC-link capacitor decreases to 84% for Si-charger and 90% for GaN charger. However, this advantage comes after the ripple injection to the battery. The recent studies have addressed several detrimental effects of  $2\omega$ -ripple on the battery life [28]. Therefore, a long-term testing is needed for such schemes. In [118], Liu et al. have proposed a novel ripple compensator for a boost-derived-PV grid-connected inverter with batterystorage. The control scheme utilizes a double channel current feedback control to minimize the  $2\omega$ -ripple in the input current. The basic idea is to regulate the  $2\omega$ -voltage ripple in the DC-link voltage by adding a small disturbance of  $2\omega$  $(say D_f)$  in the average duty  $(D_o)$ . The Fig. 19(a) shows the control block-diagram. In the Fig. 19(a),  $G_f$  is a third-order general integrator (ToGI) filter (see Fig. 19(b)) to extract  $2\omega$ -component. A grid-side based bus voltage control is adopted. The voltage error of voltage-loop is passed through an NF. This eliminates the  $2\omega$ -component from the grid-side

FIGURE 19. (a) Double input feedback and (b) third-order general integrator proposed in [118] (c) MAF based dual-loop control proposed in [127].

FIGURE 20. (a) Conventional shoot-through duty based-unipolar SPWM proposed (b) Modified shoot-through duty based-unipolar SPWM proposed in [64] (c) The low-pass filter based control scheme proposed in [62] (d) control scheme proposed in [101].

current reference. The current-error in the current-loop of the bus-voltage control is passed through proportional-resonant controller, this control the sinusoidal waveform of the grid current. A gain is multiplied with the output of  $G_f$  to regulate the value of  $2\omega$ -ripple. A large value of the gain minimizes the  $2\omega$ -ripple. However, this may induce instability to the system. Therefore, there is a trade-off between the stability and the ripple-reduction using a current feedback in the double-channel current feedback control. Use of multiple integrator in the  $2\omega$ -ripple-filter design may slow down the system dynamics. In [127], authors have proposed a dual-loop control for the boost-derived two-stage converter. The control scheme uses a moving average filter (MAF) in the voltage-loop to make the voltage-loop gain very low at  $2\omega$ . The control block diagram is shown in the Fig. 19(c). This scheme is similar to NF-CR of [16]. However, unlike NF-CR, this scheme can attenuates multiple of  $2\omega$  as well. In [112], another control scheme based on the MAF is proposed to control the swinging bus. The MAF has several advantages such as fastest step response, easy to implement using low-cost control-board, reduces random noise and notches the multiple of  $2\omega$ . However, the performance of MAF based on time-domain is better than the frequency-domain.

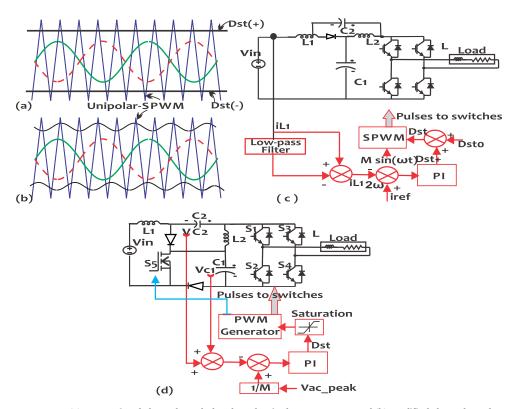

ZSI, quasi-ZSI, quasi-SBI eliminates the requirement of multiple stages. They can boost the input voltage and are capable of the shoot-through operation. In [64], authors have proposed a modified shoot-through duty based

unipolar-SPWM technique as shown in the Fig. 20(b). The conventional technique is shown in the Fig. 20(a). The control forces the voltage across the capacitors of quasi-ZSI network to swing at  $2\omega$  or to store the all  $2\omega$ -decoupling power. This reduces the ripple at the DC input. However, in comparison to conventional method, the modified scheme introduces more voltage stress on the switches i.e. 53% more than conventional scheme. An optimum design of the quasi-ZSI network parameters is given in [62]. However, a part of the  $2\omega$ -ripple still flows through the quasi-ZSI network. The inductors store the decoupling power temporarily. It is better to transfer the stored decoupling power to capacitors; the power density of the capacitor is higher than inductor. Therefore, a PI regulator based control scheme is proposed in [62]; the control scheme is shown in the Fig. 20(c). The input current is passed through a low pass filter. This gives the DC current component which then subtracted from the actual input current to give  $2\omega$ -ripple. A PI controller generates the required pulsation in the equivalent shoot-through duty. The control scheme confines the ripple in capacitors and minimizes in the inductor current and input current. However, this method has a trade-off between stability and speed of response. In [101], a new quasi-SBI topology for the high voltage gain with a benefit of  $2\omega$ -ripple reduction is proposed. A thorough study is carried out to design the impedance network. A control scheme is added to keep the input ripple-free. The control method is shown in the

Fig. 20(d). The voltages of capacitors are added and then subtracted from the reference voltage. The DC-link voltage reference is generated based on the output voltage and modulation index. The voltage error is regulated to generate desired shoot-through duty. The application of this topology is limited to the low-power applications.

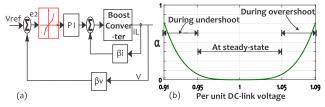

The non-linear control approaches are robust and suitable for system having large line-load transients. In [59], authors have proposed a dual-loop control method for the boost-derived-DC-DC-AC converter (see Fig. 21(a)). The ripple-reduction is achieved by adopting the output-impedance shaping. The control utilizes a sampled series feedback as the inner-loop. The series-feedback increases the output-impedance of front-end converter. A parallel feedback is added as outer-loop to regulate the DC-link voltage. However, the two feedback channels impose trade-off between the system dynamics and the ripplereduction. Therefore, a non-linear compensator is added in between the voltage-error generation point and current controller. The non-linear compensator gives high gain at the load-transients to compensate the undershoot/overshoot in the DC-link voltage. However, an abrupt change in the gain may induce instability to the system. Therefore, a fine design of the non-linear compensator is required. A swing bus-voltage control is proposed in [128] for a stand-alone fuel-cell buck-derived two-stage converter. A nonlinear natural switching surface (NSS) based boundary control takes care of the very large input voltage-swing at  $2\omega$ . The controller minimizes the DC-link voltage swing and hence distortion in the output AC voltage. However, the practical implementation of such discontinuous variable frequency schemes based on the sliding mode control may introduce chattering effect in the switching [129]. In [130], [131], authors have proposed an adaptive switching function to minimize the  $2\omega$ -ripple at the input of the boost-derived two-stage converter using the fixed-frequency based-SMC. The switching function is a combination of the inductor current error  $(e_1)$  and  $\alpha$  times voltage error  $(e_2)$ .  $\alpha$  is power function of the  $e_2$  i.e.  $\alpha = \psi e_2^{\beta}$ .  $\beta$  and  $\psi$  are design parameters. The profile of  $\alpha$  is shown in the Fig. 21(b). For a very small value of  $\alpha$ , the output-impedance is high, hence the ripple reduces at the input. At the line-load transients,  $\alpha$ changes monotonically to converge the system dynamics at a faster rate. In [132], authors have proposed a SMC based

FIGURE 21. (a) Non-linear compensator technique proposed in [59] (b) Adaptive-SMC based ripple-mitigation technique proposed in [130].

phase cancellation technique for an  $1-\phi$  grid-connected Quasi-Z-Source NPC Inverter. To cancel  $2\omega$ -ripple the

existing phase difference of  $\pi$  rad/s between capacitor voltage and inductor voltage at DC side is used.

It is to be noted that the control schemes presented in this Section still require a large size capacitor or an optimized value of the capacitance at the DC-link at the input-end of DC-AC converter [133]. The pulsation at DC-link are kept within the desired limit by choosing an optimum size of DC-link capacitor. Though the system performance at line-load transients is better despite the optimum size of DC-link capacitor which is achieved by different linear or nonlinear control approaches. To further minimize or eliminate  $2\omega$ -pulsation in the voltage at DC-link, an auxiliary circuit/active filter is added. In the next subsection, two-stage DC-DC-AC converter with the additional active filter are discussed.

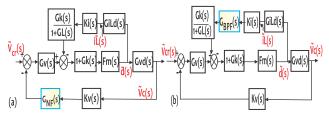

# 2) CONTROL-ORIENTED COMPENSATION TECHNIQUES WITH ADDITIONAL ACTIVE FILTER