### University of Arkansas, Fayetteville

# ScholarWorks@UARK

**Graduate Theses and Dissertations**

5-2016

# Correcting Current Imbalances in Three-Phase Four-Wire **Distribution Systems**

Vinson Joseph Jones University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

#### Citation

Jones, V. J. (2016). Correcting Current Imbalances in Three-Phase Four-Wire Distribution Systems. Graduate Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/1576

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

# Correcting Current Imbalances in Three-Phase Four-Wire Distribution Systems

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Vinson Jones University of Arkansas Bachelor of Science in Electrical Engineering, 2014

# May 2016 University of Arkansas

| This thesis is approved for recommo      | endation to the Graduate Council.  |

|------------------------------------------|------------------------------------|

| Dr. Juan Carlos Balda<br>Thesis Director |                                    |

| Dr. Alan Mantooth<br>Committee Member    | Dr. Roy McCann<br>Committee Member |

#### **ABSTRACT**

The objective of this thesis is to present the theory, design, construction, and testing of a proposed solution to unbalanced current loading on three-phase four-wire systems. The Unbalanced Current Static Compensator is the name of the prototype; herein referred to as the UCSC. The purpose of this prototype is to redistribute current between the three phases of a distribution system. Through this redistribution, negative- and zero-sequence currents are eliminated and a balanced system is seen upstream from the point of installation.

The UCSC consists of three separate single-phase H-bridge inverters that all share the same dc-link capacitor. Each of these inverters performs independently using a single-phase rotating reference frame controller. Each either draws or injects current onto the distribution system lines to balance the active currents and performs power factor correction for voltage compensation. A 34.5 kV, 6 MVA system was built and simulated in Matlab/Simulink™ to test the validity of this solution. A scaled-down UCSC prototype was then designed and constructed to compensate for a 208 V, 10 kVA system. Results from both the simulations and testing of this UCSC prototype are presented and analyzed.

# **ACKNOWLEDGEMENTS**

Thank you to Dr. Balda for the opportunity to further my knowledge in Electrical Engineering and the support and advice on this project.

# TABLE OF CONTENTS

# CHAPTER 1

| INTRODUCT | ΓΙΟΝ                                                       | 1  |

|-----------|------------------------------------------------------------|----|

| 1.1       | Motivations for this Research Work                         | 1  |

| 1.2       | Existing Solutions                                         | 1  |

| 1.2.1     | Zig-Zag Transformers                                       | 2  |

| 1.2.2     | Neutral-Wire Series Compensators                           | 3  |

| 1.2.3     | Neutral Wire Series Compensator/Zig-Zag Transformer Hybrid | 4  |

| 1.2.4     | Three-Level Inverter with Neutral Point Clamp (NPC)        | 5  |

| 1.2.5     | α-β Instantaneous Power Controller                         | 7  |

| 1.3       | Proposed UCSC Solution                                     | 9  |

| 1.4       | Objectives of Thesis                                       | 10 |

| 1.5       | Organization of Thesis                                     | 11 |

| 1.6       | References                                                 | 12 |

| CHAPTER 2 |                                                            |    |

| THEORY OF | FUCSC OPERATION                                            | 14 |

| 2.1       | Control of the UCSC                                        | 14 |

| 2.1.1     | Reference Current Generator Stage                          | 15 |

| 2.1.2     | Voltage Controller Stage                                   | 16 |

| 2.1.3     | Current Controller                                             | 17 |

|-----------|----------------------------------------------------------------|----|

| 2.2       | ABC to D-Q Transformation                                      | 18 |

| 2.3       | Second-Order Generalized Integrator (SOGI)                     | 20 |

| 2.4       | Design of LCL Filters                                          | 22 |

| 2.5       | Pulse-Width Modulation Algorithm                               | 25 |

| 2.6       | Discretization of the UCSC control system functions            | 26 |

| 2.7       | Concluding Remarks                                             | 27 |

| 2.8       | References                                                     | 28 |

| CHAPTER 3 |                                                                |    |

| SIMULATIO | ON PROCESS AND RESULTS                                         | 29 |

| 3.1       | Introduction                                                   | 29 |

| 3.2       | Realized Changes to Previously Suggested Simulation Model      | 29 |

| 3.2.1     | PWM Control Signal Normalization                               | 30 |

| 3.2.2     | Current Reference Generator                                    | 30 |

| 3.3       | Modifying the Time-Domain Simulations to Reflect the Prototype |    |

| Implement | ation                                                          | 32 |

| 3.3.1     | Sensing Circuitry                                              | 33 |

| 3.3.2     | Inverter Devices and Filter Components                         | 35 |

| 3.3.3     | Pre-Filtering of d-q Signals                                   | 36 |

| 3.3.4     | Coupling Transformers                                          | 37 |

| 3.3.5     | Discrete Phase-Lock Loop Algorithm                      | 38 |

|-----------|---------------------------------------------------------|----|

| 3.3.6     | Discrete d-q Transformation                             | 39 |

| 3.4       | Simulation Results of the New Model                     | 40 |

| 3.5       | Conclusions                                             | 42 |

| 3.6       | References                                              | 43 |

| CHAPTER 4 | 4                                                       |    |

| DESIGN OF | THE SCALED-DOWN UCSC PROTOTYPE                          | 44 |

| 4.1       | Introduction                                            | 44 |

| 4.2       | Design of the Prototype Power Stage                     | 44 |

| 4.2.1     | Scaling-Down the Case Study                             | 44 |

| 4.2.2     | Calculations for the dc Link Capacitor Sizing           | 45 |

| 4.2.3     | Design of the Gate Driving Circuit                      | 46 |

| 4.2.4     | The Effect of Parasitics on System Performance          | 47 |

| 4.2.5     | Design of the Printed Circuit Board for the Power Stage | 49 |

| 4.3       | Design of the Filter Inductors                          | 51 |

| 4.4       | Calculations for the IGBT Heat Sink                     | 63 |

| 4.5       | Sensors and Measurement Conditioning                    | 65 |

| 4.6       | Concluding Remarks                                      | 66 |

| 4.7       | References                                              | 67 |

# CHAPTER 5

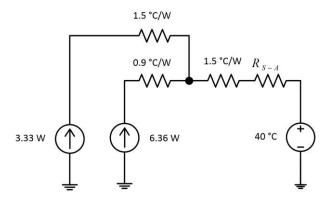

| Ι | IMPLEMENTATION OF THE CONTROL ALGORITHM IN A MICROCONTROLLER 68 |                                                                      |    |

|---|-----------------------------------------------------------------|----------------------------------------------------------------------|----|

|   | 5.1                                                             | Introduction                                                         | 68 |

|   | 5.2                                                             | Developing a Single-DSP System                                       | 68 |

|   | 5.3                                                             | Controller Implementation in the DSP                                 | 69 |

|   | 5.4                                                             | Start-Up and Shutdown Procedure                                      | 70 |

|   | 5.5                                                             | Initializing the DSP Modules                                         | 72 |

|   | 5.5.1                                                           | Analog-to-Digital Converter                                          | 72 |

|   | 5.5.2                                                           | Pulse-Width Modulator                                                | 73 |

|   | 5.5.3                                                           | CPU Timer                                                            | 74 |

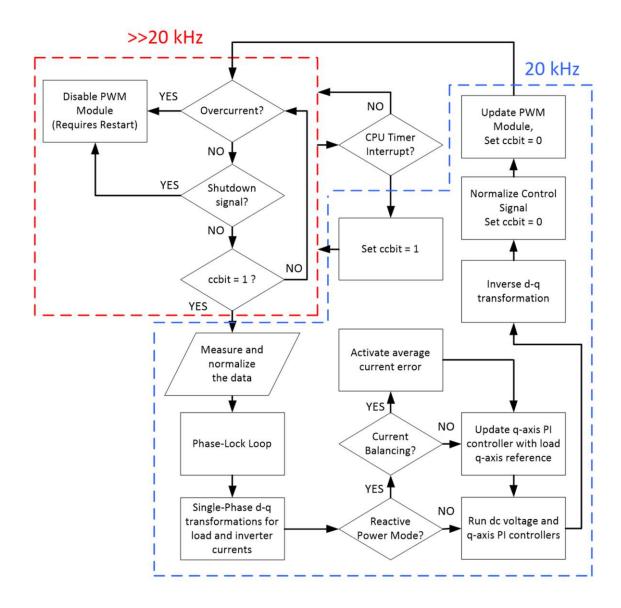

|   | 5.6                                                             | Calculating the Dead Time for the Inverter-Leg Semiconductor Devices | 74 |

|   | 5.7                                                             | Modifications for EMI Reduction                                      | 76 |

|   | 5.8                                                             | Concluding Remarks                                                   | 77 |

|   | 5.9                                                             | References                                                           | 77 |

| C | HAPTER 6                                                        |                                                                      |    |

| Т | ESTING OF                                                       | F THE UCSC PROTOTYPE                                                 | 78 |

|   | 6.1                                                             | Experimental Setup                                                   | 78 |

|   | 6.2                                                             | Testing of the UCSC Prototype                                        | 79 |

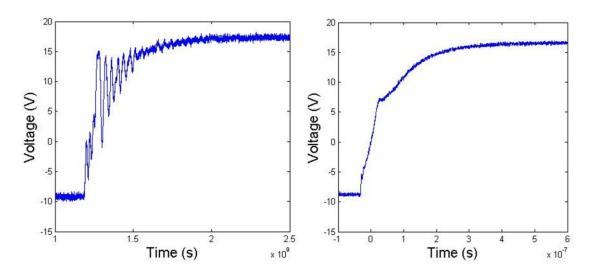

|   | 6.2.1                                                           | Effect of Increasing the dc-bus Voltage                              | 81 |

|   | 622                                                             | Effect of a Decrease in the Dead Time                                | ۷1 |

| 6.2.3      | Effect of Increased Inverter Loading                                | . 83 |

|------------|---------------------------------------------------------------------|------|

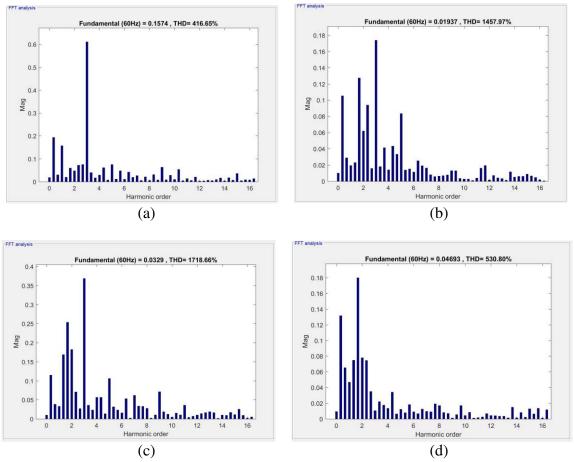

| 6.3        | Causes of Output Voltage Distortion in a Single-Phase Inverter      | . 83 |

| 6.4        | Effect of Harmonic Voltage Components                               | . 88 |

| 6.5        | Effect of Improper Measurements                                     | . 89 |

| 6.6        | Conclusions                                                         | . 89 |

| 6.7        | References                                                          | . 90 |

| CHAPTER 7  |                                                                     |      |

| CONCLUSIO  | NS AND FUTURE WORK                                                  | . 92 |

| 7.1        | Conclusions                                                         | . 92 |

| 7.2        | Recommendations for Future Work                                     | . 93 |

| 7.2.1      | Implement a method for compensating the distortion due to dead time | . 93 |

| 7.2.2      | Include of a mechanism for compensating for grid voltage distortion | . 94 |

| 7.2.3      | Develop applications for the UCSC in mesh networks                  | . 94 |

| 7.2.4      | Apply the UCSC control to different three-phase inverter topologies | . 94 |

| 7.2.5      | Augment the UCSC controller to compensate for harmonic currents     | . 94 |

| 7.2.6      | Add the ability to partially compensate for reactive power          | . 95 |

| 7.3        | References                                                          | . 96 |

| APPENDIX A | $\mathbf{A}$                                                        |      |

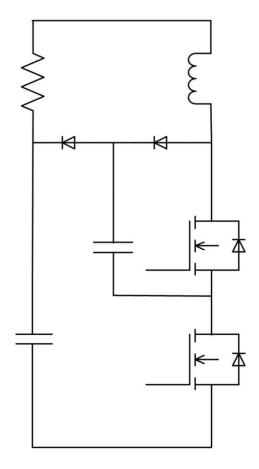

| SNUBBERS 1 | FOR SEMICONDUCTOR DEVICES                                           | . 97 |

| A.1        | RCD Snubber                                                         | . 97 |

| A.2     | Overvoltage Snubber   | 98  |

|---------|-----------------------|-----|

| A.3     | Turn-On Snubber       | 98  |

| A.4     | Undeland Snubber      | 99  |

| A.5     | References            | 100 |

| APPENDI | IX B                  |     |

| DIGITAL | SIGNAL PROCESSOR CODE | 101 |

| B.1     | The Main.c File       | 101 |

# LIST OF FIGURES

| Figure 1-1. Zig-zag transformer compensation system                                               | 2 |

|---------------------------------------------------------------------------------------------------|---|

| Figure 1-2. Neutral-wire series compensator system                                                | 3 |

| Figure 1-3. Zig-zag and series compensator hybrid system                                          | 1 |

| Figure 1-4. NPC three-phase three-level voltage source inverter                                   | 5 |

| Figure 1-5. Three-level four-leg voltage source inverter                                          | 5 |

| Figure 1-6. Indirect current control block diagram                                                | 3 |

| Figure 1-7. Proposed shoot-through current immune topology                                        | ) |

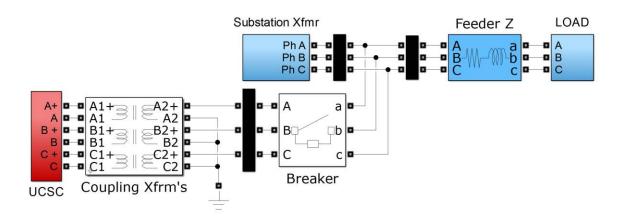

| Figure 1-8. Connection of the UCSC to the distribution system                                     | l |

| Figure 2-1. The UCSC power topology                                                               | 1 |

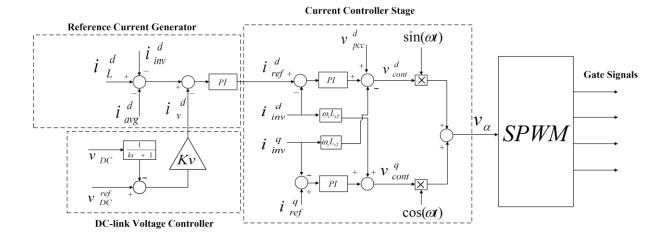

| Figure 2-2. UCSC simplified block schematic                                                       | 5 |

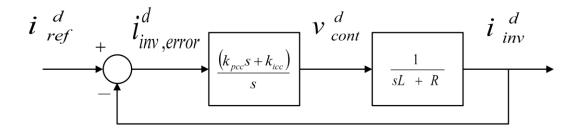

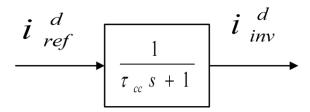

| Figure 2-3. Simplified current controller block diagram                                           | 3 |

| Figure 2-4. Equivalent current controller block diagram                                           | 3 |

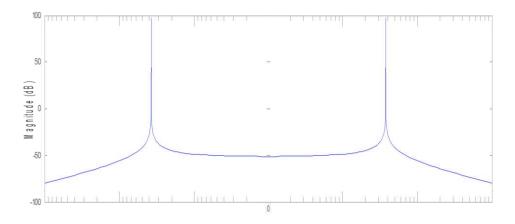

| Figure 2-5. Frequency response of the SOGI                                                        | l |

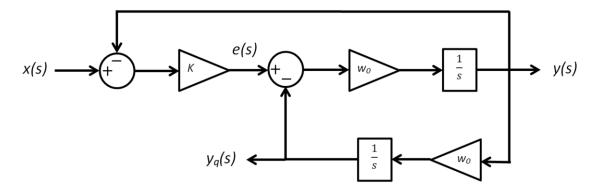

| Figure 2-6. Block diagram for the SOGI-QSG                                                        | 2 |

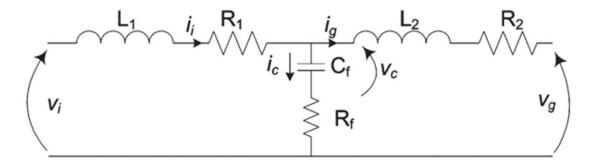

| Figure 2-7. Schematic for an LCL filter                                                           | 3 |

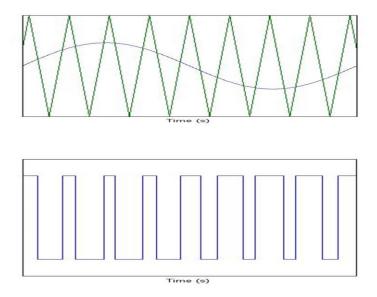

| Figure 2-8. SPWM waveforms (top) and the resulting pulses (bottom)                                | 5 |

| Figure 3-1. Matlab/SIMULINK <sup>TM</sup> UCSC system                                             | ) |

| Figure 3-2. Substation currents from the previous model in different UCSC operating modes 30      | ) |

| Figure 3-3. PWM control signal normalization                                                      | l |

| Figure 3-4. Previously suggested controller                                                       | 2 |

| Figure 3-5. Outputs of the current reference and voltage PI controllers in the previous system 33 | 3 |

| Figure 3-6. Current reference PI controller output for new system                                 | 33         |

|---------------------------------------------------------------------------------------------------|------------|

| Figure 3-7. Reference generator for the current controller                                        | 34         |

| Figure 3-8. Effect of the notch filter before (left) and after (right)                            | 34         |

| Figure 3-9. Measurement filtering and conditioning used in the simulations                        | 35         |

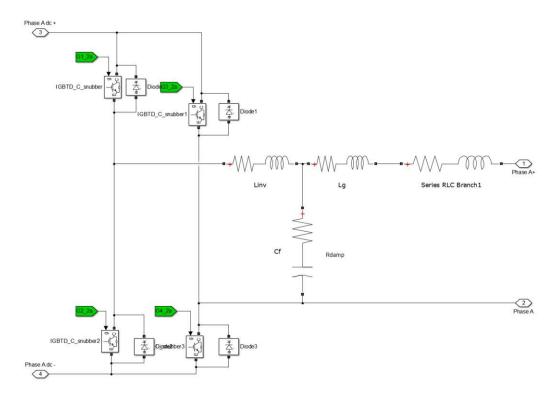

| Figure 3-10. Inverter implemented in SIMULINK <sup>TM</sup>                                       | 36         |

| Figure 3-11. Dialog box for the IGBTs and diodes used in the SIMULINK <sup>TM</sup> simulations 3 | 37         |

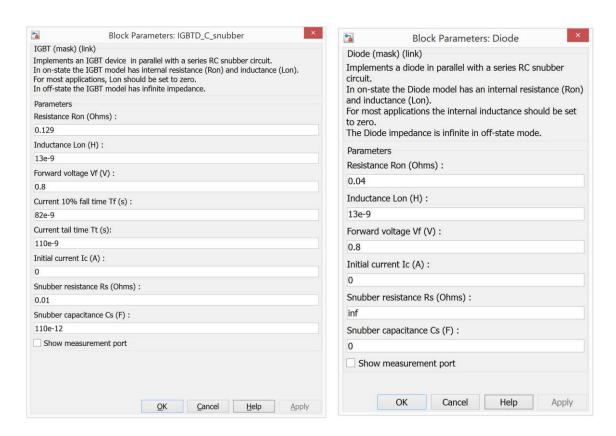

| Figure 3-12. Discrete phase-lock loop block diagram                                               | 38         |

| Figure 3-13. D-Q Transformation                                                                   | 39         |

| Figure 3-14. Substation currents from new continuous model in different UCSC operating mode       | es         |

| 4                                                                                                 | <b>‡</b> 1 |

| Figure 3-15. Substation currents from the discrete-domain prototype simulation                    | 12         |

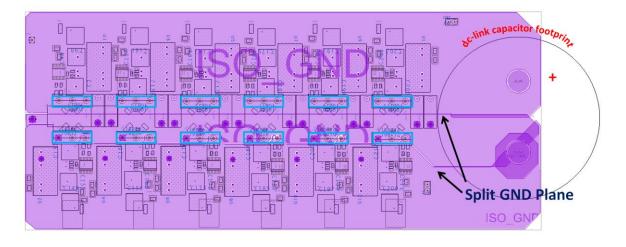

| Figure 4-1. Bottom layer photoplot for the power stage PCB used in the UCSC prototype 5           | 50         |

| Figure 4-2. Bottom-middle layer photoplot for the power stage PCB used in the UCSC prototyp       | e          |

|                                                                                                   | 50         |

| Figure 4-3. Top-middle layer photoplot for the power stage PCB used in the UCSC prototype . 5     | 51         |

| Figure 4-4. Top layer photoplot for the power stage PCB used in the UCSC prototype 5              | 51         |

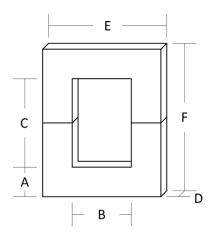

| Figure 4-5. Dimensions of a C core pair                                                           | 55         |

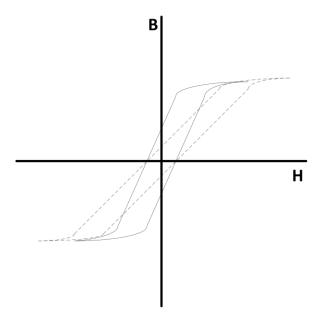

| Figure 4-6. B-H Curve without airgap (solid line) and with airgap (dotted line)                   | 56         |

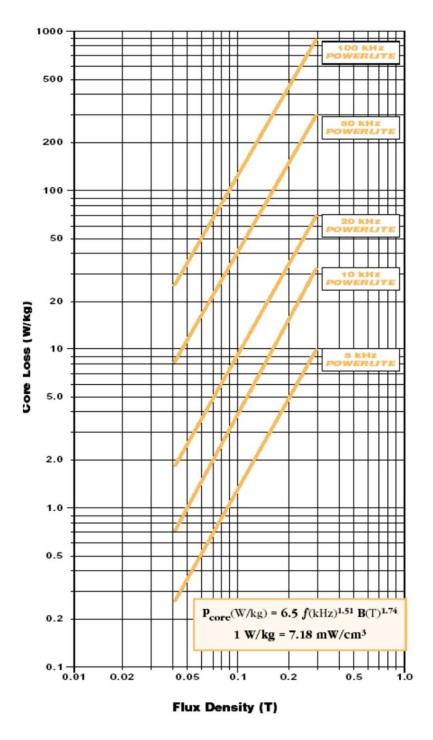

| Figure 4-7. Core loss curves for the Hitachi POWERLITE amorphous cores                            | 50         |

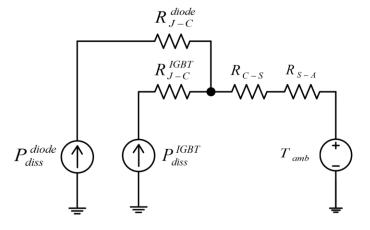

| Figure 4-8. Equivalent thermal circuit for IGBT and antiparallel diode                            | 54         |

| Figure 4-9. Thermal circuits for the IGBT and antiparallel diode                                  | 55         |

| Figure 5-1. Flowchart for the DSP processes                                                       | 70         |

| Figure 5-2. Turn-off current waveform for an IGBT                                                 | 15         |

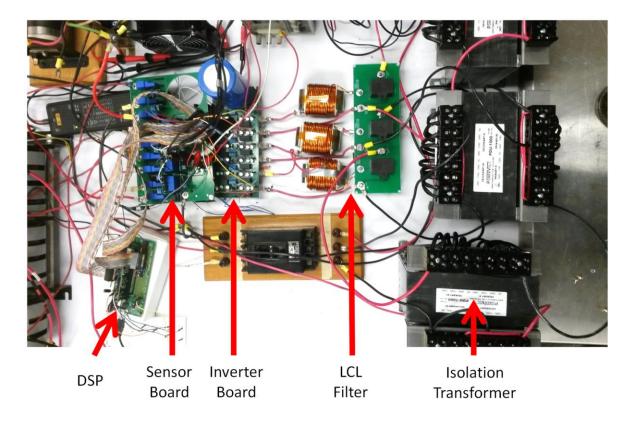

| Figure 6-1. Experimental setup for testing of the UCSC prototype                                     |

|------------------------------------------------------------------------------------------------------|

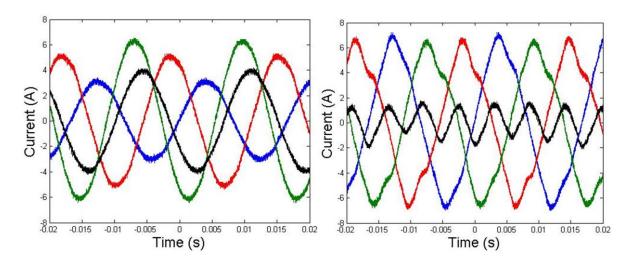

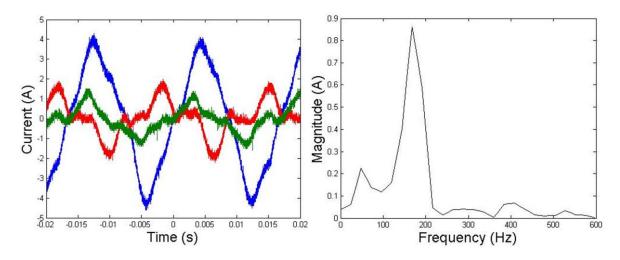

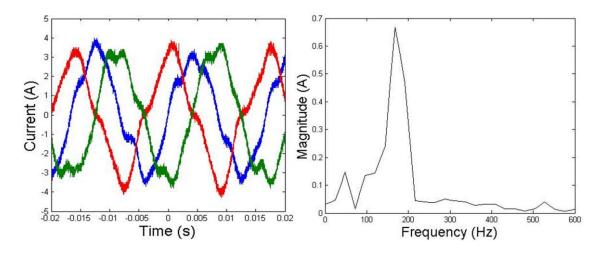

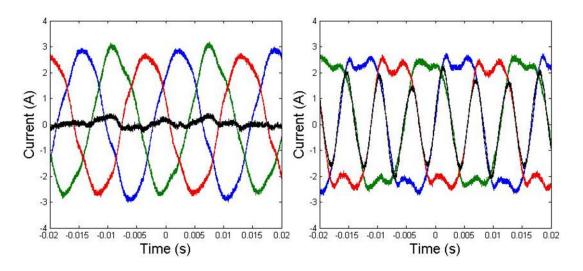

| Figure 6-2. Unbalanced load currents (left) and substation current (right) during testing 79         |

| Figure 6-3. Phase Voltage and Current before (left) and during (right) UCSC full operation 80        |

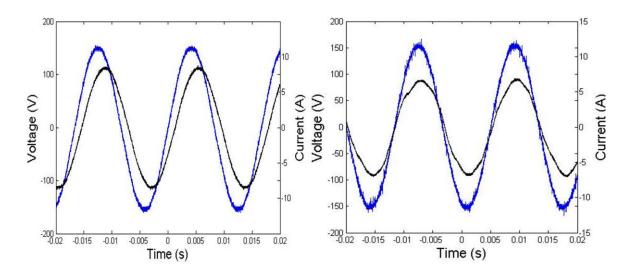

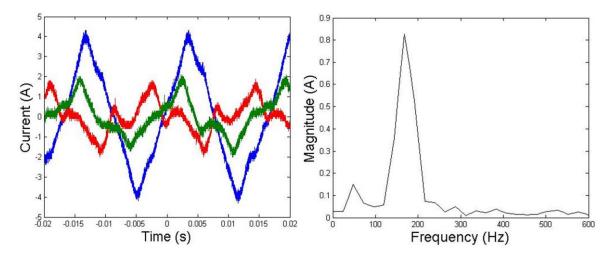

| Figure 6-4. UCSC inverter currents (left) and FFT of the substation neutral current (right) during   |

| full UCSC operation                                                                                  |

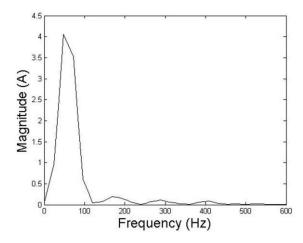

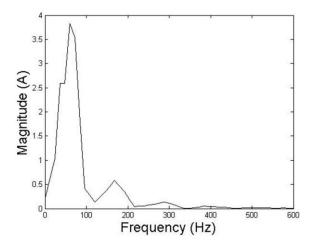

| Figure 6-5. FFT of the substation current                                                            |

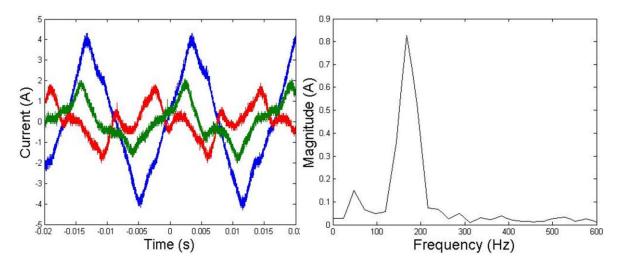

| Figure 6-6. Inverter Currents (left) and FFT of substation neutral current (right) with 300 V dc     |

| bus                                                                                                  |

| Figure 6-7. Inverter Current (left) and FFT of substation neutral current (right) with 0.833 $\mu s$ |

| dead time                                                                                            |

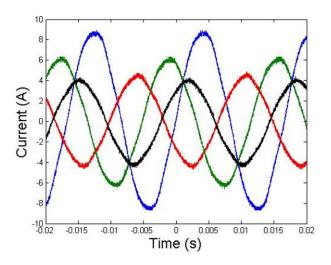

| Figure 6-8. Unbalanced load currents during increased load testing                                   |

| Figure 6-9. Inverter currents (left) and FFT of the substation neutral current (right) with          |

| increased inverter loading                                                                           |

| Figure 6-10. FFT of substation current with increased inverter loading                               |

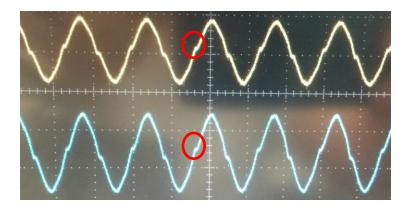

| Figure 6-11. Unipolar inverter output distortion due to dead time                                    |

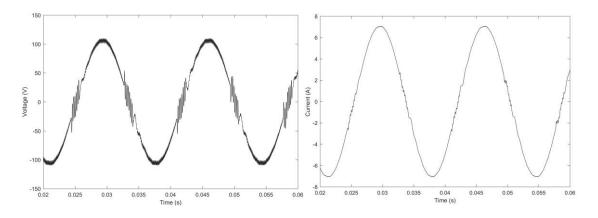

| Figure 6-12. Voltage (left) and current (right) waveforms produced from the hybrid modulation        |

| scheme                                                                                               |

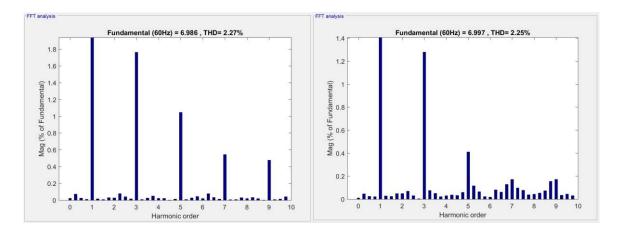

| Figure 6-13. FFT of inverter output current with unipolar (left) and hybrid (right) modulation       |

| scheme                                                                                               |

| Figure 6-14. Substation currents during UCSC operation without (left) and with (right) grid          |

| voltage distortion                                                                                   |

| Figure 6-15. IGBT Turn on without (left) and with (right) appropriate voltage probes                 |

| Figure 6-16. IGBT Turn-on Vce without (left) and with (right) appropriate voltage probes 90          |

| Figure 7-1. Shoot-through current immune topology | . 95 |

|---------------------------------------------------|------|

| Figure A-1. RCD Snubber Circuit                   | . 97 |

| Figure A-2. Overvoltage Snubber                   | . 99 |

| Figure A-3. Undeland Snubber Circuit              | 100  |

# LIST OF TABLES

| Table 3-1. Parameters of the prototype IGBTs                                                  | 36 |

|-----------------------------------------------------------------------------------------------|----|

| Table 4-1. Load power ratings for the case study and scaled-down prototype                    | 45 |

| Table 4-2. DC Link Capacitor Parameters                                                       | 46 |

| Table 4-3. 2.2 mH and 0.5 mH Inductor Design Parameters                                       | 52 |

| Table 4-4. Amorphous Core Data                                                                | 54 |

| Table 4-5. Variables for switching and conduction losses in controlled semiconductor devices. | 64 |

| Table 5-1. Gate Driver Circuit IC Datasheet Parameters                                        | 75 |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Motivations for this Research Work

In an ideal three-phase four-wire distribution system, each of the phases would be connected to identical customers and the same amount of current would be drawn from each phase. In practical systems, this is not the case as there is much variation in the type and connection timing of customers. This situation leads to an unbalance in the currents that run through each phase. As a result, the currents do no sum to zero at the neutral conductor, which causes several issues in the power transmission system:

- Extra current in the neutral wire of four-wire systems which can result in unsafe conditions, and in some cases, an incorrectly sized conductor [1].

- Electric machine overheating due to negative-sequence currents [2].

- Magneto-motive force (MMF) generated by negative-sequence currents interferes with the positive-sequence MMF. This along with the machine overheating causes a drop in the efficiency of the system [3].

- Zero-sequence fluxes produced in wye-connected ungrounded transformers can cause overheating [4].

Several different attempts have been made to mitigate the effects of the negativesequence and zero-sequence currents. These are described in the next section.

### 1.2 Existing Solutions

The presented solutions can be classified into two different types of compensators: passive and active compensators. The passive solutions do not react to changes in the system like

the active compensators and, as a result, are often not as effective. However, passive systems are usually cheaper and do not require complex control techniques and sensing that active systems do.

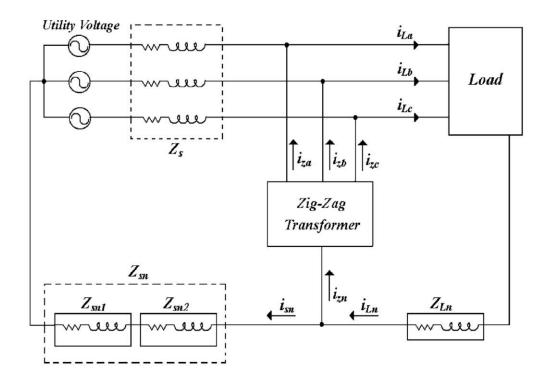

### 1.2.1 Zig-Zag Transformers

To eliminate the zero-sequence current components that would flow through the neutral in three-phase four-wire systems one proposed method is the introduction of a zig-zag transformer in parallel with the load [5]. Zig-zag transformers are wound in such a way that they have very low impedance to zero-sequence currents and very large impedance to positive- and negative- sequence currents. The system setup is shown in Fig. 1-1 where  $Z_s$  is the impedance of the phase conductor between the source and transformer,  $Z_{sn}$  is the impedance of the neutral conductor between the transformer and the source, and  $Z_{Ln}$  is the neutral conductor impedance

Figure 1-1. Zig-zag transformer compensation system [1]

between the load and the transformer. Ideally, this would remove the zero-sequence current injected into the utility system and thus reduce the stress on the system; however, the impedance  $Z_{sn}$  plays a large part in the performance of this solution. If  $Z_{sn}$  is large then the attenuation is better, though this requires that the transformer is either further away from the utility, thus compensating less load, or that an inductor be placed in series with the neutral, which adds a significant cost to the system and can cause abnormal operation of load-side equipment.

Moreover, this solution loses its advantage in unbalanced utility voltage conditions due to the fundamental-component zero-sequence currents which may cause the transformer to overheat. These disadvantages suggest the need for another solution, particularly based on power electronics.

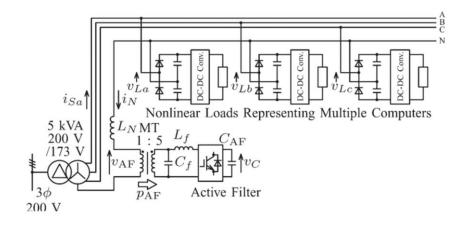

### 1.2.2 Neutral-Wire Series Compensators

A voltage-source inverter in series with the neutral conductor is applied to reduce the harmonic currents reaching the utility system [6]. Fig. 1-2 demonstrates a test case. By inducing a series voltage in the neutral conductor the inverter creates a high impedance path for harmonic currents in the form of a virtual inductor. The performance of the system improves as

Figure 1-2. Neutral-wire series compensator system [2]

the reactance of the inverter increases, but a balance must be achieved between the desired attenuation of neutral current and the level of voltage distortion that is caused as a result.

#### 1.2.3 Neutral Wire Series Compensator/Zig-Zag Transformer Hybrid

This method combines the two previous solutions. In this system there is a zig-zag transformer connected in parallel with the load and in addition there is a voltage-source inverter connected in series with the utility-side neutral conductor [7]. Fig. 1-3 demonstrates the described system.

The series inverter helps to force the harmonic zero-sequence currents through the transformer and back to the load by producing a voltage waveform in the neutral that mimics high impedance. The hybrid systems require less knowledge of the system impedance for them to be effective and allow for smaller and cheaper zig-zag transformers. This solution is effective, and reduces current imbalances, but only through mitigating the harmonic currents contribution to this problem. The fundamental zero-sequence currents still flow back to the utility.

Figure 1-3. Zig-zag and series compensator hybrid system [3]

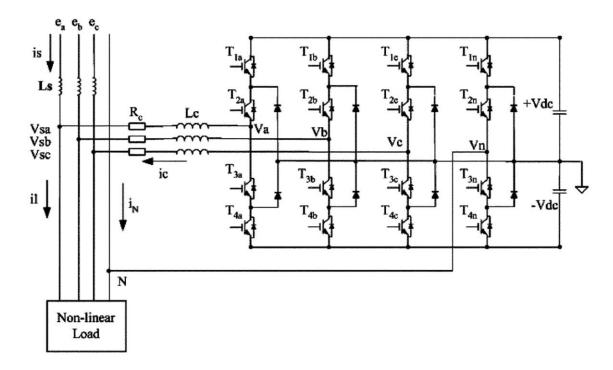

### 1.2.4 Three-Level Inverter with Neutral Point Clamp (NPC)

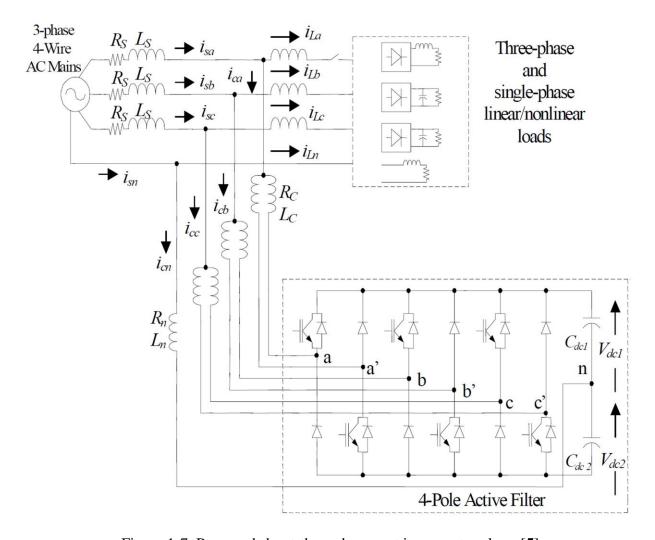

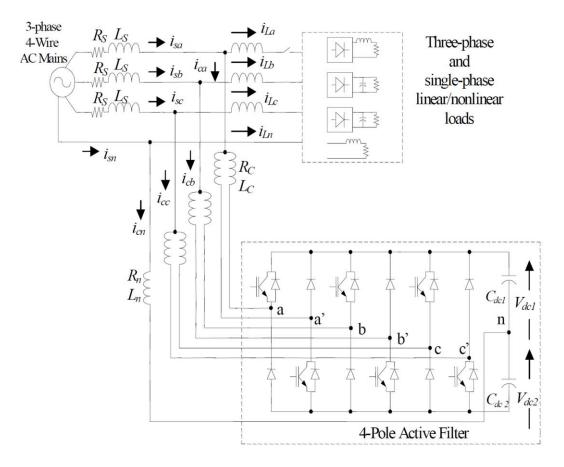

This solution uses a NPC three-leg voltage source inverter as shown in Fig. 1-4 where  $L_s$  is the inductance of the conductor from the source to the point of common coupling (PCC),  $R_c$  is the resistance between the output of the inverter and the PCC, and  $L_c$  is the inductance between the output of the inverter and the PCC [8]. This setup allows for better compensation of neutral currents due to the added control of the output voltage relative to the neutral. To control this inverter, a switch commutation strategy called space vector modulation is implemented where a map of all possible switching combinations is constructed [8]. A different set of output voltage or output vectors is obtained for each of these combinations. Through control in the  $\alpha$ - $\beta$ -0 or other domain, the amount of time spent at each of these vectors is calculated as well as the order. Using this technique an averaged output vector can be produced to allow for precise control over the output voltage.

Figure 1-4. NPC three-phase three-level voltage source inverter [4]

Figure 1-5. Three-level four-leg voltage source inverter [4]

This method can be generalized for any number of switching positions and can also be used to control the four-leg converter in Fig. 1-5Figure 1-5. The fourth leg of this inverter gives the user better control over neutral currents as there are now more neutral point switching vectors to choose from; however, it is not only more expensive to add this fourth leg, but the SVM becomes more complex.

The complexity of using SVM, compared to SPWM (sinusoidal pulse width modulation), can be a problem due to the extra computation resources required to implement the modulation technique. Larger computational load can lead to reduction in the frequency at which the controller can be run when implementing these techniques on digital signal processors [9]. This disadvantage could be mitigated by delegating the control signal modulation to an FPGA with parallel computing ability, but integration of an FPGA into the design adds more complexity to the final solution.

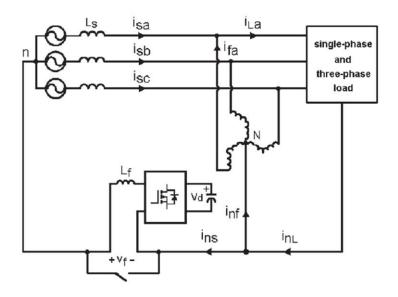

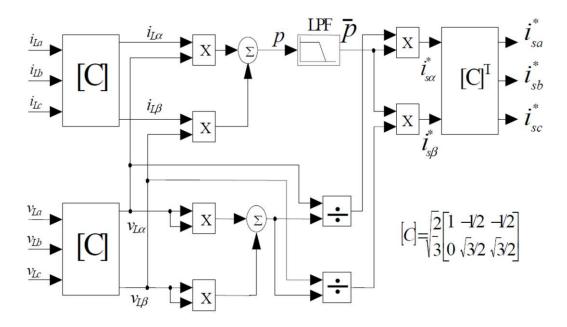

#### 1.2.5 α-β Instantaneous Power Controller

This solution keeps the controller in the stationary  $\alpha$ - $\beta$  reference frame. Given that the filtering and computational delays are properly dealt with, this type of control allows for the elimination of a phase-lock loop as well as a second transformation into the dq rotating reference frame. The control in [6] works by calculating the instantaneous power required by the load and, by normalizing the  $\alpha$  and  $\beta$  voltage terms, and a current reference for the inverters is then set which is proportional to the power needed on each phase. This controller achieves full compensation of reactive currents required by the load and current balancing. Also, it can compensate for low-order harmonics present within the distribution system with the use of a low-pass filter on the instantaneous power calculations.

Two different versions of this controller are used. The direct current controller method generates the control signal for an active filter directly by calculating the harmonic and reactive current components that need to be delivered to the load by the filter. The indirect current controller calculates the fundamental-component current that should be the only one supplied by the source. The difference between this fundamental component reference and the actual source current becomes the control signal for the active filter. As a result it provides all current components but the fundamental one. Fig. 1-6Figure 1-6 contains the block diagram for the indirect current controller. The  $i_L$  components are the measured load currents, the  $v_L$  components are the voltages of each phase at the PCC, and the  $i_{sb}^*$  components are the generated current references for the inverters.

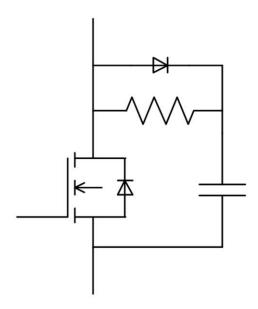

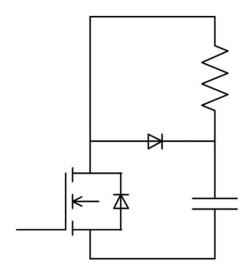

Fig. 1-7Figure 1-7 indicates the topology of the inverter used in the testing of the  $\alpha$ - $\beta$  controller. This topology is convenient because it is not susceptible to the shoot-through current that

Figure 1-6. Indirect current control block diagram [5]

normally is a problem in inverters with cascade devices, and thus reduces the need for the dead time in the switching pulses. This topology has the same number of active switches as a standard three-phase inverter, but has twice the number of diodes and twice the PCC connecting reactors.

A NPC configuration is also required for proper functionality, which adds to the cost.

The  $\alpha$ - $\beta$  stationary reference frame controllers are generally easier to implement than d-q synchronous reference frame controllers. This is because they do not require as many reference frame transformations or the phase-lock loops required for the transformations. They may also have better transient behavior as experienced in [7] However, their performance can be severely diminished by any magnitude or phase error in the measurements or calculations because these control strategies directly use ac waveforms to construct the current references in the inverter controller [12].

Figure 1-7. Proposed shoot-through current immune topology [5]

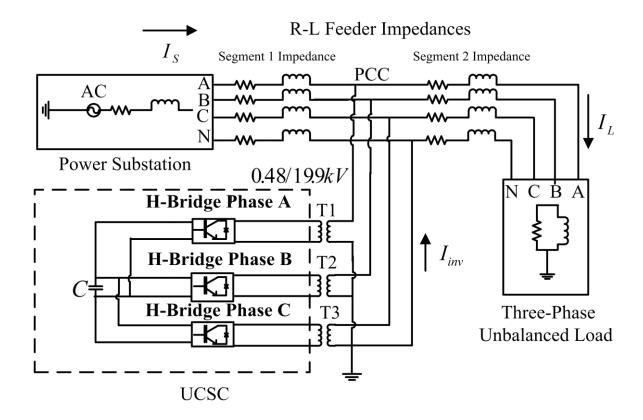

## 1.3 Proposed UCSC Solution

A case study is developed to test any possible solutions based on data from a 34.5 kV distribution feeder. At peak power, the three phase loads were 877 kW + 500 kVAR, 707 kW + 300 kVAR, and 753 kW + 300 kVAR, so these load ratings were chosen for the case study [13].

The topology selected for the UCSC has three single-phase full-bridge inverters. This is useful for several reasons:

- Each of the inverters can control their respective phases current completely independent of the other phases.

- There is full utilization of the dc bus voltage which is not the case for neutralpoint-clamped inverters.

- Control of an H-bridge is relatively simple and does not require more complex modulation schema as required by four-leg inverter topologies.

The largest flaw with the use of this topology is that 12 switching position are required and thus 12 IGBTs and 12 diodes are required.

A diagram showing the connection of the UCSC to the distribution system is displayed in Fig. 1-8Figure 1-8. Each of the inverters shares a single dc-bus capacitor. All three are coupled to the 34.5 kV distribution system using 480V/19.9kV single-phase distribution transformers that boost the voltage to the required value as well as provide the necessary isolation required by industry standards. Not shown in the figure is the line-to-neutral LCL filter at the output of each of the inverters. The UCSC is to be installed just downstream from the distribution substation to compensate for as many downstream loads as possible.

### 1.4 Objectives of Thesis

The main objectives of this thesis are to improve upon the UCSC solution developed in [9] and then, to validate its performance using a constructed prototype. This will be done in three main steps:

- First, the theoretical background behind the operation of the UCSC will be developed.

- 2) Second, simulation results will be analyzed for potential improvements.

Figure 1-8. Connection of the UCSC to the distribution system [6]

3) Third, the scaled down prototype will be built, tested, and the experimental results analyzed.

### 1.5 Organization of Thesis

The theory behind the operation of the UCSC will be presented in Chapter 2. The simulations of the system will be addressed in Chapter 3. This will include the construction of the simulation models and any changes from previous model in [13] and the results from those simulations. The assembly and design of the scaled down prototype is documented in Chapter 4 and the controller implementation is presented in Chapter 5. The measurements and analysis of the results that come from testing of the prototype are found in Chapter 6. Conclusions and recommendations for future work are given in Chapter 7.

#### 1.6 References

- [1] J. Kennedy, C. A. Nucci, A. Borghetti, G. Contaxis A. P. S. Meliopoulos, "Power distribution practices in USA and Europe: impact on power quality," in *Proceedings of the 8th International Conference on Harmonics and Quality of Power*, Athens, 1998, pp. 24-29.

- [2] R. G. Harley, E.B. Makram, and E.G. Duran, "The effects of unbalanced networks on synchronous and asynchronous machine transient stability," *Electric Power System Research*, vol. 13, no. 2, pp. 119-127, October 1987.

- [3] R.H. Salim, R.A. Ramos, and N.G. Bretas, "Analysis of the small signal dynamic performance of synchronous generators under unbalanced operating conditions," in *IEEE Power and Energy Society General Meeting*, 2010, pp. 1-6.

- [4] T.A. Short, *Electrical Power Distribution Handbook*. Boca Raton, FL: CRC Press Taylor & Taylor Croup, 2004.

- [5] Jou Hurng-Liahng, Wu Jinn-Chang, Wu Kuen-Der, Chiang Wen-Jung, and Chen Yi-Hsun, "Analysis of zig-zag transformer applying tin the three-phase four-wire ditribution power system," *IEEE Transactions on Power Delivery*, vol. 20, no. 2, pp. 1168-1173, April 2005.

- [6] S Inoue, T. Shimizu, and K. Wada, "Control Methods and Compensation Characteristics of a Series Active Filter for a Neutral Conductor," *Industrial Electronics, IEEE Transactions on*, vol. 54, no. 1, pp. 433-440, February 2007.

- [7] Sewan Choi and Minsoo Jang, "Analysis and Control of a Single-Phase-Inverter-Zigzag-Transformer Hybrid Neutral-Current Suppressor in Three-Phase Four-Wire Systems," *Industrial Electronics, IEEE Tansactions on*, vol. 54, no. 4, pp. 2201-2208, August 2007.

- [8] Ning-Yi Dai, Man-Chung Wong, and Ying-Duo Han, "Application of a three-level NPC inverter as a three-phase four-wire power quality compensator by generalized 3DSVM," *Power Electronics, IEEE Transactions on*, vol. 21, no. 2, pp. 440-449, March 2006.

- [9] D. Dujic, M. Jones, and Levi E., "Contrinuous Carrier-Based vs. Space Vector PWM for Five-Phase VSI," in *EUROCON*, 2007. The International Conference on Computer as a Tool, Warsaw, 2007, pp. 1772-1779.

- [10] Singh G.N and P Rastgoufard, "A new topology of active filter to correct power-factor, compensate harmonics, reactive power and unbalance of three-phase four-wire loads," in *Applied Power Electronics Conference and Exposition*, Miami Beach, 2003, pp. 141-147.

- [11] Matias Diaz and Roberto Cardenas, "Analysis of Synchronous and Stationary Reference Frame Control Strategies to Fulfill LVRT Requirements in Wind Energy Conversion Systems," in *Ecological Vehicles and Renewable Energies (EVER)*, 2014 Ninth

International Conference on, Monte-Carlo, 2014, pp. 1 - 8.

- [12] D. N. Zmood and D. G. Holmes, "Stationary frame current regulation of PWM inverters with zero steady state error," in *Power Electronics Specialists Conference*, Charleston, 1999, pp. 1185-1190.

- [13] Manuel A. S. Tejada, "Unbalanced Current Static Compensator," Dept. of Elect. Eng., Univ. of Arkansas, Fayetteville, MS Thesis 2014.

### **CHAPTER 2**

### THEORY OF UCSC OPERATION

### 2.1 Control of the UCSC

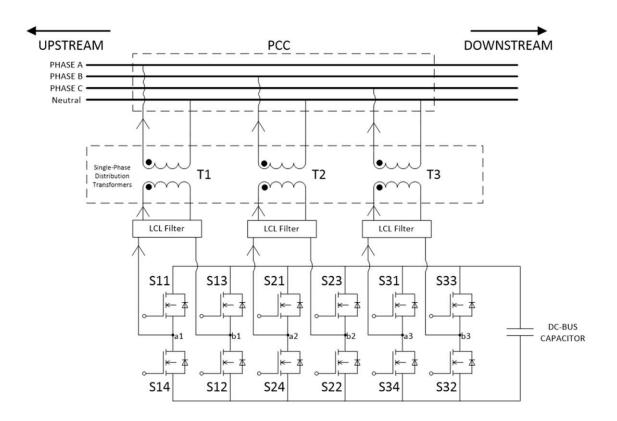

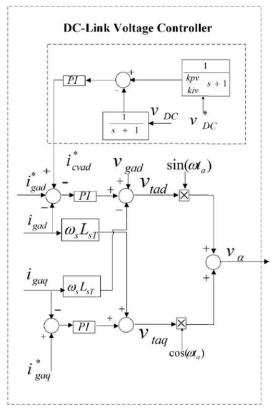

The power topology of the UCSC is displayed in Fig. 2-1 and the control block schematic for each inverter is shown in Fig. 2-2Figure 2-2. The UCSC's three single-phase inverters inject or draw current at the point of common coupling (PCC) to compensate for the load currents in such a way that the substation currents are balanced. The various subsystems of the controller will be explained next. The controller first transforms the inverter and load currents along with phase voltages at the PCC into the d-q synchronously-rotating reference frame using a

Figure 2-1. The UCSC power topology

Figure 2-2. UCSC simplified block schematic

single-phase  $\alpha$ - $\beta$  to d-q transformation [1].

#### 2.1.1 Reference Current Generator Stage

This section of the block schematic is responsible for generating the reference signal for the current controller. Using the d-axis component of the load current from each phase an average load current is calculated  $i_{avg}^d$ . The substation currents  $i_{sa}^d$ ,  $i_{sb}^d$ , and  $i_{sc}^d$  are then compared to the average load current through current summation at the PCC  $(i_s^d = -i_{inv}^d - i_L^d)$  to develop the respective d-axis current references. The resulting error signal for each phase is summed with  $i_v^d$  and routed into a PI controller whose output is the d-axis reference current  $i_{ref}^d$  for the current controller.

Because the three single-phase inverters circulate the currents between the phases, there is no net current drawn from the grid into the capacitor except the current used to maintain the dc bus voltage. The PI controller gains  $(k_{pref}, k_{iref})$  are specified by using the following method from [2]:

$$i_{cap} = C_{DC} \frac{dv_{DC}}{dt} = \left[ k_{pref} \left( v_{DC}^{ref} - v_{DC} \right) + k_{iref} \int \left( v_{DC}^{ref} - v_{DC} \right) \right] \tag{1}$$

In (1) the capacitor equation relating its current and voltage is used to develop a relationship between the error signal  $(v_{DC}^{ref} - v_{DC})$  and the capacitor voltage. Using the Laplace transform and solving for  $\frac{v_{DC}}{v_{DC}^{ref}} = T_{ref}(s)$  in (1) results in:

$$T_{ref}(s) = \frac{v_{DC}}{v_{DC}^{ref}} = \frac{k_{pref}}{C_{DC}} \frac{\left(s + \frac{k_{iref}}{k_{pref}}\right)}{\left(s^2 + \frac{k_{pref}}{C_{DC}}s + \frac{k_{iref}}{C_{DC}}\right)} \tag{2}$$

this takes a similar form to the general form of a two-pole transfer function given by:

$$T(s) = \frac{\omega_{cc}^2}{(s^2 + 2\zeta\omega_{cc}s + \omega_{cc}^2)}$$

(3)

Using the theory behind this general form, the response of the reference PI controller can be determined through the following relationships:

$$2\zeta\omega_{cc} = \frac{k_{pref}}{(C_{DC})} \longrightarrow k_{pref} = 2\zeta\omega_{cr}(C_{DC})$$

(4)

$$\omega_{cc}^2 = \frac{k_{iref}}{(C_{DC})} \longrightarrow k_{iref} = (C_{DC})\omega_{cr}^2$$

(5)

A damping factor  $\zeta = \frac{\sqrt{2}}{2}$  is used and corresponds to a 5% overshoot given a step change in set point.

### 2.1.2 Voltage Controller Stage

The voltage controller regulates the voltage for the dc-link capacitor, common to all three phases of the UCSC, within a certain band; the specified voltage ripple is 1% of the rated voltage The controller senses and filters the bus voltage  $v_{DC}$  and compares this instantaneous value to a set reference value  $v_{DC}^{ref}$ . The difference in these values is then processed through a gain to

regulate the effect of an error in the dc bus voltage versus an error in the currents. The error signal  $i_{v}^{d}$ , after being modified, is added to the reference current generators error signal.

#### 2.1.3 Current Controller

The d-axis current reference  $i_{ref}^d$  is compared to the inverter d-axis current  $i_{inv}^d$ . The error between these two signals is then routed to a PI controller to establish the response characteristics of the current controller [1]. The d-axis component of the grid voltage  $v_{pcc}^d$  is added to the signal as a feed-forward element to bias the voltage output of the inverter. Also, a decoupling term is added to take into account the coupling between the q-axis currents and the inductances of the filter and transformer. The same process is done for the q-axis current controller; however, the current reference becomes the q-axis component of the load current (this fully compensates for the reactive power). The feed-forward q-axis grid voltage is assumed to be 0. The decoupling term comes from the interaction between the d-axis current component and the inductances present. To produce a control signal for the PWM generator the signals are converted back to the  $\alpha$ - $\beta$  reference frame, where the  $\alpha$  component is the output voltage waveform.

The simplified block diagram for the current controller is shown in Fig. 2-3Figure 2-3. The first block represents the transfer function for the PI controller and the second one the plant model for the output filter. The PI controller gains for the current controller  $(k_{pcc}, k_{icc})$  are specified by using the following method [1]. The transfer function L(s) for the open-loop system is given by:

$$L(s) = \frac{(k_{pcc}s + K_{icc})}{Ls^2 + Rs} = \left(\frac{K_{pcc}}{Ls}\right) \frac{\left(s + \frac{K_{icc}}{K_{pcc}}\right)}{\left(s + \frac{R}{L}\right)}$$

(6)

Figure 2-3. Simplified current controller block diagram

By choosing the relationship between  $K_{icc}$  and  $K_{pcc}$  appropriately  $\left(\frac{K_{icc}}{K_{pcc}} = \frac{R}{L}\right)$ , the pole and zero cancel out. This is useful because this leads to a much simpler closed-loop transfer function given by:

$$G(s) = \frac{L(s)}{1 + L(s)} = \frac{1}{\left(\frac{L}{K_{pcc}}\right)s + 1}$$

(7)

The closed-loop system is drawn in Fig. 2-4Figure 2-4. Using the chosen proportional and integral gain ratio as given above the PI gains can be selected from:

$$\frac{L}{K_{PCC}} = \tau_{cc} \tag{8}$$

### 2.2 ABC to D-Q Transformation

The control diagram described above requires dc values in order to be stable. This requires the ac voltages and currents that are sensed by the UCSC to be transformed into dc

Figure 2-4. Equivalent current controller block diagram

value equivalents in order to be used [3]. This is accomplished through the use of the Park's transformation, otherwise known as the d-q-0 transformation, which takes an input vector of the 3 voltage (or current) functions and outputs a vector that consists of dc values in steady state corresponding to the magnitude of the input ac functions.

The d-q-0 transformation is derived from another vector manipulation method known as the Clarke's transformation or the  $\alpha$ - $\beta$ -0 transformation that changes the reference axis that is used to measure the phasor values in a three-phase system [4]. The new reference axes are called the  $\alpha$ ,  $\beta$ , and 0 axis that are rotated such that the zero axis is equidistant from the original a, b, and c axes. The new values for the three phasors are their reflections upon the new reference axes. Thus, all the original phasors in a balanced three-phase system cancel out to zero on the zero axis. This is useful for the control of balanced three-phase systems because it effectively eliminates a variable. A system defined in the abc reference frame can be fully described by the variables  $\alpha$  and  $\beta$ . The  $\alpha$ - $\beta$ -0 transformation is given by [3]:

$$\begin{bmatrix} \alpha \\ \beta \\ 0 \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(9)

With the system in the  $\alpha\beta0$  reference frame, the transformation to the dq0 reference frame is given by:

$$\begin{bmatrix} d \\ q \\ 0 \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos(\omega t) & \sin(\omega t) & 0 \\ -\sin(\omega t) & \cos(\omega t) & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \\ 0 \end{bmatrix}$$

(10)

This rotates the  $\alpha$  and  $\beta$  reference axes around the 0 axis at the same frequency as the sinusoids that define the phasors. The effect of this rotation is that the periodic signals become DC values. The full d-q-0 transformation and its inverse are shown below:

$$\begin{bmatrix} d \\ q \\ 0 \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos \theta & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ \sin \theta & \sin(\theta - \frac{2\pi}{3}) & \sin(\theta + \frac{2\pi}{3}) \\ \frac{\sqrt{2}}{2} & \frac{\sqrt{2}}{2} & \frac{\sqrt{2}}{2} \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

(11)

$$\begin{bmatrix} a \\ b \\ c \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} \cos \theta & -\sin \theta & \frac{\sqrt{2}}{2} \\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) & \frac{\sqrt{2}}{2} \\ \cos(\theta + \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) & \frac{\sqrt{2}}{2} \end{bmatrix} \begin{bmatrix} d \\ q \\ 0 \end{bmatrix}$$

(12)

In the case of unbalanced three-phase systems, the three-phase transformations shown above are not as effective because they do not help to eliminate the number of variables used to define the system. This is because the 0 axis contains a non-zero value. One approach to deal with this problem is the use of single-phase d-q transformations [3]. The  $\alpha$ - $\beta$  to d-q transform in this case is a straightforward modification of the above equation and is given by:

$$\begin{bmatrix} d \\ q \end{bmatrix} = \begin{bmatrix} \cos(\omega t) & \sin(\omega t) \\ -\sin(\omega t) & \cos(\omega t) \end{bmatrix} \begin{bmatrix} \alpha \\ \beta \end{bmatrix}$$

(13)

The initial transformation process is different from (9). In order to establish the  $\alpha$ - and  $\beta$ axis values for a single-phase system the value used for the  $\alpha$  axis is the present value of the

function that defines the ac waveform, such as  $sin(\omega t)$ , and the  $\beta$  axis value is the value of that

same function but lagged for a quarter cycle; that is,  $sin(\omega t - \frac{\pi}{2})$ . This gives the magnitude and

phase information for the ac waveform [3].

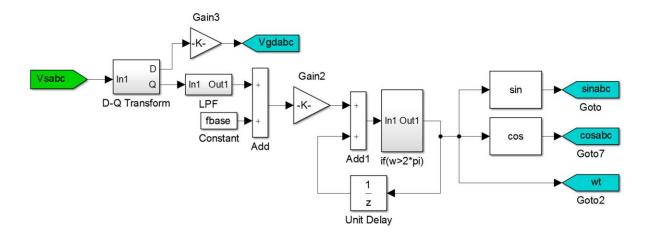

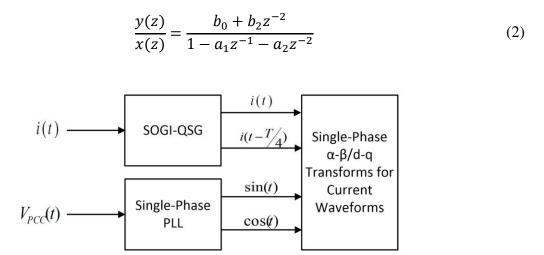

### 2.3 Second-Order Generalized Integrator (SOGI)

A SOGI is actually the transformation of an integrator in the dq reference frame into its corresponding operation in the stationary  $\alpha\beta$  reference frame. This is done by transforming

$$y^{dq} = y^{+dq} + y^{-dq} = \left(\frac{1}{s}\right)(x^{+dq} + x^{-dq}) \tag{14}$$

into the stationary reference frame [5]. The results of the transformation are:

$$\frac{y^{\alpha\beta}}{x^{\alpha\beta}} = \frac{1}{(s - j\omega_0)} + \frac{1}{(s + j\omega_0)} = \frac{2s}{(s^2 + \omega_0)}$$

(15)

where  $y^{+dq}$  and  $y^{-dq}$  represent the output in the positive and negative sequence rotating reference frames. The frequency response of this system is illustrated in Fig. 2-5Figure 2-5. This shows that the SOGI has infinite gain at 60 Hz and -60 Hz. By using negative feedback the SOGI can be used to track an input signal and as outputs, reproduces the input signal along with a signal of identical amplitude but lagging 90 degrees.

In Matlab/Simulink<sup>TM</sup>, the creation of an orthogonal signal for use in a single-phase d-q transformation is as simple as using a delay block with a step of a quarter cycle. The same operation in the DSP would take up a large amount of space. For a sampling rate of 10 kHz, a quarter-cycle delay would require the saving of 2500 numbers, which takes up a lot of memory especially with a word length of 32 bits, so it is not very efficient.

Figure 2-5. Frequency response of the SOGI

Figure 2-6. Block diagram for the SOGI-QSG

This is where a second-order generalized integrator quadrature signal generator (SOGI-QSG) can be used. This configuration of the SOGI takes in a sinusoidal input signal and then outputs two other sinusoidal signals. One of them is the fundamental frequency sinusoid component of the input and the other output is fundamental frequency sinusoid component of the input but delayed by a quarter cycle. The transfer functions for each of these outputs are:

$$\frac{y(s)}{x(s)} = \frac{K\omega_0 s}{s^2 + K\omega_0 s + \omega_0^2} \tag{16}$$

$$\frac{y_q(s)}{x(s)} = \frac{K\omega_0^2}{s^2 + K\omega_0 s + \omega_0^2}$$

(17)

Where  $\omega_0$  is the frequency to which the SOGI is tuned. Fig. 2-6Figure 2-6 contains the block diagram of the SOGI-QSG [5].

## 2.4 Design of LCL Filters

An LCL filter has become more commonly used in grid interfacing systems due to its superior current ripple attenuation when compared to the conventional L or LC filters. An L filter is simple, but only has a -20 dB/dec frequency response for the entire frequency spectrum. The LCL filter matches the performance of an L filter for lower frequencies, but can achieve a 60 dB/dec attenuation at higher frequencies, allowing for smaller magnetic components.

The basic structure of the LCL filter is shown in Fig. 2-7Figure 2-7. Because the design of this filter is based on the attenuation of harmonics that arise from active grid-connected devices the value of  $v_g$  is considered to be zero as the grid voltage is considered to be a pure 60 Hz voltage source. The output of the inverter is a PWM voltage and the filter is used to eliminate high-frequency current components. This leads to following transfer function [6]:

$$T_{LCL}(s) = \frac{i_g}{v_{inv}} = \frac{1}{L_{inv}C_f L_g s^3 + (L_{inv} + L_g)s}$$

(18)

The problem with this response characteristic is that a resonance occurs that might make the LCL filter actually produce worse current ripple in the output of the inverter. A solution for eliminating this resonance is the use of the resistor,  $R_f$  in series with the shunt capacitor to lessen the effects of the resonance, but unfortunately results in higher system losses. As a tradeoff for using a passive damping resistor, the 60 dB/dec attenuation after the resonant frequency reduces to 40 dB/dec. The transfer function that takes into account the effect of the damping resistor is given by:

$$T_{LCL}(s) = \frac{i_g}{v_{inv}} = \frac{C_f R_f s + 1}{L_{inv} C_f L_g s^3 + C_f (L_{inv} + L_g) R_f s^2 + (L_{inv} + L_g) s}$$

(19)

In order to avoid significant change in the power factor of the filter, the parallel capacitor is

Figure 2-7. Schematic for an LCL filter [6]

limited to a percentage of the base capacitance of the system [6]. This requires knowledge of the power and voltage ratings of the inverter as follows:

$$C_f = (0.02) \frac{1}{\omega X_{base}} = (0.02) C_b = (0.02) \frac{P_{inv}}{\omega V_{la}^2}$$

(20)

If this capacitor is to be connected in a delta configuration then line-to-line voltage  $V_{LL}$  would be used instead of line-to-ground voltage  $V_{LG}$ . This derivation of the LCL, instead of being designed based on a cutoff frequency to eliminate specified harmonics, is designed to attenuate the overall ripple current amplitude. The inverter-side inductor is determined from an initial ripple attenuation, which is a reduction to 20% as follows [6]:

$$\Delta i = \frac{V_{DC}}{8L_{inv}f_{sw}} \le (0.20)I_{max} \tag{21}$$

The value of the grid side inductor is determined once again by using required ripple current reduction, which is 10%, so resulting attenuation is (20%)(10%) = 2%. Relevant equations are:

$$L_{q} = rL_{inv} \tag{22}$$

$$\frac{i_o(h_s)}{i_{inv}(h_s)} = \frac{1}{|1 + r(1 - L_{inv}C_h(0.02)(\omega_{sw})^2)|}$$

(23)

Due to the effect of the additional inductor the filter actually has a resonant frequency of its own at:

$$\omega_{res} = \sqrt{\frac{L_{inv} + L_g}{L_{inv} \times L_g \times C_f}}$$

(24)

This resonant frequency should be chosen at most to be half of the switching frequency of the inverter and at least ten times greater than the fundamental frequency [6]. This keeps the filter from amplifying switching noise as well as the lower order harmonics that are potentially

produced in a single-phase inverter. In addition to choosing the appropriate resonant frequency a resistor is added in series with the parallel capacitor in order to attenuate the resonance. The value of this resistance is given by:

$$R_{damp} = \frac{1}{3 \times \omega_{res} \times C_f}$$

(25)

The factor of 3 in the denominator would be eliminated if the resistor is placed in delta configuration.

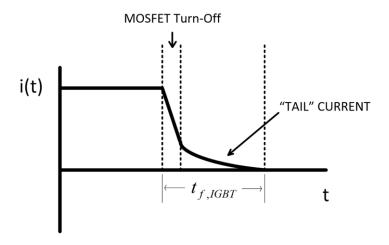

## 2.5 Pulse-Width Modulation Algorithm

A sinusoidal pulse width modulation (SPWM) is employed in order to produce the sinusoidal output voltage with an inverter [7]. This technique compares a sinusoidal control signal which under normal operating conditions has an amplitude of less than 1. This control signal is compared to a triangular waveform with an amplitude of 1. When the triangular waveform has a lower value than the control signal then the output of the PWM generator is 1 and when it is higher the output of the PWM generator is 0. When this output of the inverter is filtered appropriately the resulting output is a sinusoidal voltage with the same frequency magnitude as the control signal sent to the PWM generator. The frequency of the triangular waveform corresponds to the switching frequency of the inverter. These signals can be applied to the full-bridge inverter in many different ways. An example of this is drawn in Fig. 2-8Figure 2-8.

In bipolar PWM switching one set of signals is sent to the top and bottom switches of the first leg of the inverter and the second leg receives the same signals but inverted. Thus, the output of the inverter can either be  $-V_{dc}$  or  $V_{dc}$ , where  $V_{dc}$  is the voltage of the dc bus. Unipolar PWM switching uses a PWM generator for each leg of the inverter; one generator receives the

control signal unmodified and the other receives the same control signal but negated. This type of modulation means that the top two or bottom two switches in the inverter can be on at the same time, which means that the voltage across the load can be 0 V,  $V_{DC}$ , or  $-V_{DC}$ . Unipolar switching doubles the effective switching frequency of the inverter resulting in less harmonic currents.

## 2.6 Discretization of the UCSC control system functions

Once the UCSC control system has been verified using continuous-domain techniques, the system must be transferred to the discrete domain in order to apply it to a real-world prototype by transforming all control operations into their Z-domain equivalents. The general method for this application would be the unilateral z-transformation [8]:

$$X(z) = Z\{x(t)\} = \sum_{n=0}^{\infty} x(nT_s)z^{-n}$$

(26)

The continuous function x(t) is broken into discrete parts based on the sampling rate of the system  $T_s$  and  $z^{-n}$  is an operator that when applied to a variable refers to its value "n"

Figure 2-8. SPWM waveforms (top) and the resulting pulses (bottom)

sampling periods earlier. As computing an infinite series can be cumbersome and many control operations are done in the Laplace domain, it is much simpler to make use of s-to-z approximations. Five examples of Laplace-to-discrete transformations are given below [9]:

Euler Forward:

$$s = \frac{1-z^{-1}}{T_S z^{-1}}$$

Euler Backward:

$$s = \frac{1-z^{-1}}{T_s}$$

Tustin (Trapezoidal):

$$s = \frac{2}{T_s} \frac{1-z^{-1}}{1+z^{-1}}$$

Zero-Order Hold:

$$s = (1 - z^{-1})Z\left\{\frac{H(s)}{s}\right\}$$

Matched Pole-Zero:

$$z = e^{sT_s}$$

### 2.7 Concluding Remarks

This chapter presented the underlying theory behind the operation and control of the UCSC. This included the reference frames that the controller relies upon, how the controller operates, and the process of developing a controller that works in a real-world implementation. The next chapter will focus on building simulations and resulting results that were used to verify the performance of the UCSC.

#### 2.8 References

- [1] Manuel A. S. Tejada, "Unbalanced Current Static Compensator," Department of Electrical Engineering, University of Arkansas, Fayetteville, MS Thesis 2014.

- [2] M. S. Huertas, "The use of power electonics for emulating power distribution feeders," Department of Electrical Engineering, University of Arkansas, Fayetteville, Masters Thesis 2008.

- [3] U. A. Miranda, L. G. B. Rolim, and M Aredes, "A DQ synchronous reference frame current control for signle-phase converters," in *IEEE 36th Power Electronics Specialists Conference PESC'05*, Recife, 2005, pp. 1377-1381.

- [4] P.C. Krause, O. Wasynczuk, and S.D. Sudhoff, *Analysis of Electric Machinery and Drive Systems*, 3rd ed. Somerset, United States of America: Wiley, 2013.

- [5] C. A. Busada, S. Gomez Jorge, A. E. Leon, and J. A. Solsona, "Current controller based on reduced order generalized integrators for distributed generation systems," *IEEE Transactions Industrial Electronics*, vol. 59, no. 7, pp. 2898-2909, 2012.

- [6] A. Reznik, M.G. Simoes, A. Al-Durra, and S.M. Muyeen, "Filter Design and Performance Analysis for Grid-Interconnected Systems," *Industry Applications, IEEE Transactions on*, vol. 50, no. 2, pp. 1225-1232, March-April 2014.

- [7] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics: Converters Applications and Design*, 3rd ed. New Jersey, United States of America: JW&S Inc, 2003.

- [8] H. A. Helm, "The Z transformation," *The Bell System Technical Journal*, vol. 38, no. 1, pp. 177-196, January 1959.

- [9] F. J. Rodriguez et al., "Discrete-time implementation of second order generalized integrators for grid converters," in *Proceedings 34th Annual Conference IEEE Industrial Electronics*, 2008, pp. 176-181.

#### **CHAPTER 3**

## SIMULATION PROCESS AND RESULTS

### 3.1 Introduction

The system shown in Fig. 3-1 was implemented and tested in Matlab/SIMULINK<sup>TM</sup> in order to establish the plausibility of the proposed solution. This system is based upon the 6 MVA, 34.5 kV radial feeder case study described in Chapter 1 [1]. The inverters are rated 480 V<sub>L-N</sub>, and have a current rating of 2048 A, giving each a 1 MVA rating.

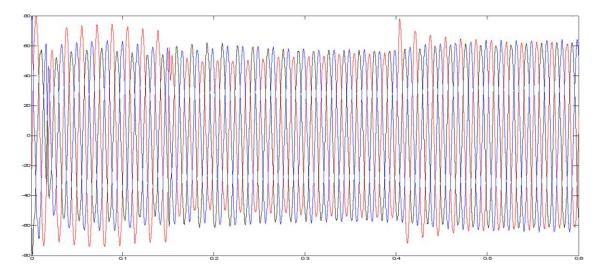

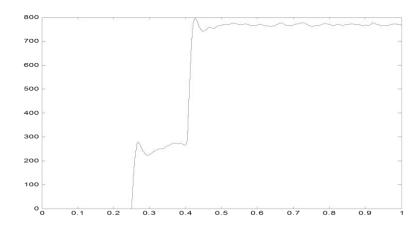

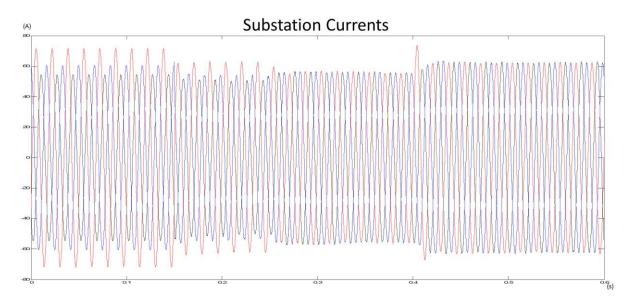

Fig. 3-2 shows the simulation results of the case study from the model proposed in [1]. The UCSC is in 3 different modes of operation. In the first mode from t = 0.03 s to t = 0.15 s, the UCSC is compensating for the unbalanced loads. From t = 0.15 s to t = 0.60 s, the UCSC is fully operational. At t = 0.40 s, there is a step increase of 30% in one of the phase loads.

## 3.2 Realized Changes to Previously Suggested Simulation Model

Several changes were made to the original model proposed in [1] either to improve its performance or to reduce its computational load. These changes are addressed below.

Figure 3-1. Matlab/SIMULINK<sup>TM</sup> UCSC system

Figure 3-2. Substation currents from the previous model in different UCSC operating modes

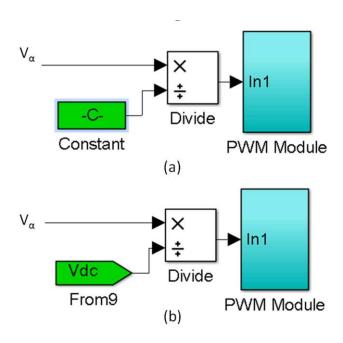

### 3.2.1 PWM Control Signal Normalization

The previous model in [1] and the change made to it are shown in Fig. 3-3. If the control signal is normalized as in Fig. 3-3 (a), then the resulting control signal will contain the same 2<sup>nd</sup> harmonic component that is present in the dc bus voltage. This will result in a 3<sup>rd</sup> harmonic voltage component being produced in the output of the inverter because of the rotating reference frame. The control signal is now normalized using the instantaneous dc bus voltage to avoid this harmonic as in Fig. 3-3 (b).

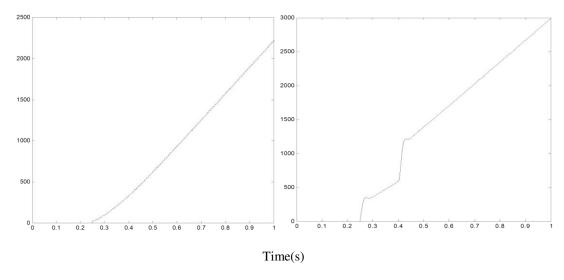

### 3.2.2 Current Reference Generator

In the original model, displayed in Fig. 3-3, a reference current from the dc-bus voltage controller was added to the error between the d-axis inverter current,  $i_{gad}$ , and the d-axis current reference,  $i_{gad}^*$ . The result of this scheme was a "wind-up" of the PI controllers for the reference current and the voltage controller. An example of this is shown in Fig. 3-5 where the output of PI controllers continues to rise even when the UCSC is in steady-state operation.

Figure 3-3. PWM control signal normalization

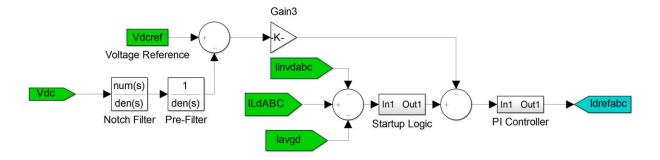

By adding now directly the dc-bus voltage error to the reference current error; this "wind-up" and extra DSP calculations were avoided. The PI controller for the voltage error was eliminated. The resulting output from the current reference PI controller now has the form illustrated in Fig. 3-6. The new system is shown in Fig. 3-7.

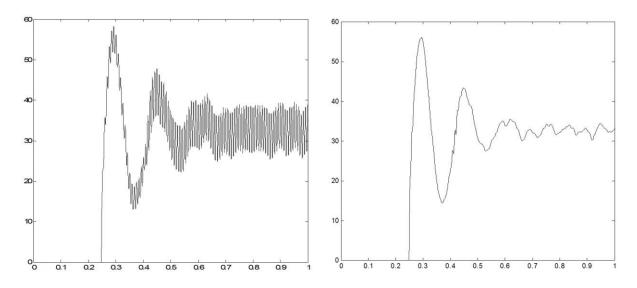

In addition to moving the voltage error, a notch filter at 120 Hz was added to the Vdc measurement used to compare to the reference. The elimination of the 2<sup>nd</sup> harmonic voltage ripple in the control system is desirable because (a) PI controllers are meant to work upon dc values and because (b) 2<sup>nd</sup> harmonics in the d-q reference frame become 3<sup>rd</sup> harmonic components in the control waveforms sent to the PWM generator. This results in a 3<sup>rd</sup> harmonic component in the output voltage of the single-phase inverters used in the UCSC. The voltage measurement before and after the notch filter is shown in Fig. 3-8.

Another change within the reference current generator refers to the sourcing of the

Figure 3-4. Previously suggested controller [1]

current measurements. Instead of measuring all the substation, load and inverter currents, as done previously, the model now just computes the inverter and loads current and uses KCL at the PCC to determine the substation currents. This saves computational time for the DSP to perform the SOGI and d-q transforms (associated with sampling these currents) that make up most of the DSP's calculations.

## 3.3 Modifying the Time-Domain Simulations to Reflect the Prototype Implementation

To better emulate the behavior of the prototype, the controller was modeled as it is implemented in the DSP and the start-up procedure is modified to be indicative of the laboratory testing. The sections below describe the realized changes.

Figure 3-5. Outputs of the current reference and voltage PI controllers in the previous system

Figure 3-6. Current reference PI controller output for new system

### 3.3.1 Sensing Circuitry

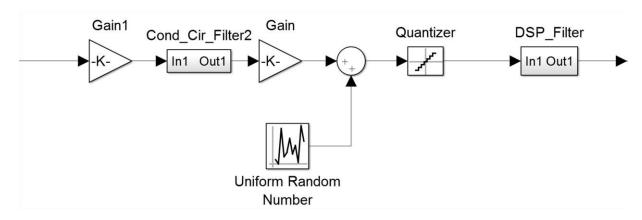

Fig. 3-9 is the block diagram that emulates the current and voltage measurements as implemented in the actual system. The first gain is the conversion ratio between the actual current or voltage being measured by the sensors and its output, followed by the voltage output of the conditioning circuits that are connected to the sensor's output. The filter after this first gain is analog filtering as a result of the feedback capacitor in the operational amplifier based conditioning circuit. The second gain is the compensation due to any loss in gain from the effects

Figure 3-7. Reference generator for the current controller

of the analog filtering.

The uniform random number block generates noise to mimic the noise experienced in the actual ADC measurements. The quantizer block mimics the ADC characteristics of the DSP where the ADC module can only detect 4096 different discrete voltage values between the digital ground and supply voltage (3.0 V). The last block is the digital filter used to eliminate high-frequency noises from the ADC measurements. This digital filter averages the last two samples. This is the discrete domain equivalent to a single-pole continuous transfer function with a cutoff frequency at half of the sampling frequency.

Figure 3-8. Effect of the notch filter before (left) and after (right)

Figure 3-9. Measurement filtering and conditioning used in the simulations

#### 3.3.2 Inverter Devices and Filter Components

When validating the control of the system, semiconductor devices near to ideal are used in the simulations. But to get the appropriate behavior of the inverters, IGBT and diode models that better describe the behavior of the actual IGBT and antiparallel diode co-package found in the prototype are used as shown in Fig. 3-10. The most important parameters are the minimum voltage drop across the IGBT  $V_{CE}$ , the on-state resistance of the IGBT  $r_{on}$ , the minimum voltage drop across the antiparallel diode  $V_d$ , and the on-state resistance of the antiparallel diode  $r_{don}$ . Though the models used also allow for package inductances, turn-off and tail current times, and parasitic snubber, these are not as important for a full system simulation as the time step required to witness the phenomenon that these parameters cause is too small to efficiently test the model. These are important when looking at the effects of parasitics, which will be described later.

The prototype IGBTs are the FGH20N60SFDTU from Fairchild Semiconductor whose main parameters are listed in Table 3-1. Fig. 3-11 shows the dialog box for the IGBT and antiparallel diodes used in the simulations. It is also important to use accurate values for the inductances and resistances in the filter because of the decoupling terms required in the current controller for each phase. This includes finding the actual inductances and winding

Figure 3-10. Inverter implemented in SIMULINK<sup>TM</sup>

resistances of the filter inductors. There is a slight variation in the inductance between each of the inductors because the inductors were handmade; an impedance meter was used to test the inductance of each of the inductors.

# 3.3.3 Pre-Filtering of d-q Signals

In [1], the output of the d-q transformations were first filtered through single-pole transfer functions such as  $\frac{1}{\tau s+1}$ . This introduced an additional measurement delay on the signals used in

Table 3-1. Parameters of the prototype IGBTs

| Property                       | Value           |

|--------------------------------|-----------------|

| $V_{CE}$ Breakdown Voltage     | 600 V           |

| Rated Collector Current @ 25°C | 40 A            |

| Maximum Power @ 25°C           | 165 W           |

| Operating Temperature          | -55°C to +150°C |

Figure 3-11. Dialog box for the IGBTs and diodes used in the SIMULINK™ simulations the control algorithm. These filters that can slow down the settling and the response times for any changes in the load currents were removed to avoid these affects.

#### 3.3.4 Coupling Transformers

The transformers in the simulations were characterized using the short-circuit and dc resistance test on the transformers used in the lab testing. The short-circuit test consisted of shorting the low-voltage side of transformer and then increasing the high-side voltage until the rated current. Then, the leakage reactance can be calculated using the current and voltage on the high side. The winding resistance is found by applying a dc voltage to both sides of the transformer and calculating the dc resistance based on the current that flows. The resistance of

the windings for a 60 Hz waveform can be approximated by the dc resistance because the skin effect is negligible at low frequencies unless the conductors used have a very large cross-sectional area.

### 3.3.5 Discrete Phase-Lock Loop Algorithm

The phase-lock loop algorithm implemented in the DSP is summarized in Fig. 3-12, where a normalized grid voltage is the input. Then, a single-phase d-q transformation is performed based on the previously estimated grid angle. If the grid angle estimation is correct, then the d-q transformation will result in a null q component and the d component is the peak magnitude of the grid voltage. Assuming that the estimated grid angle is wrong, the q component has a non-zero value and becomes an error signal. This error signal is processed through a PI controller that acts as a low-pass filter (LPF) to eliminate any measurement noise [2]. The transfer function for the LPF is given by:

$$Y_{LPF}(z) = \frac{\left(\frac{2K_P + K_i t_{samp}}{2}\right) - \left(\frac{2K_P + K_i t_{samp}}{2}\right)z^{-1}}{1 - z^{-1}}$$

(1)

Figure 3-12. Discrete phase-lock loop block diagram

where  $K_P$  is the proportional gain,  $K_i$  is the integral gain, and  $t_{samp}$  is the sampling period.

This filtered error signal is added to the nominal grid value to either increase or decrease the rate of change of the estimated phase angle. This causes the derivative of the phase angle to increase or decrease in order to eliminate the q component. The most recently calculated sine and cosine values are used in the next cycle of the algorithm [2]. The sine and cosine functions in the DSP are actually computed using a lookup table (LUT) that includes 512 values to define each quarter of the sine and cosine functions; so, it is assumed that there is a negligible amount of error between the actual function and the values used by the DSP.

### 3.3.6 Discrete d-q Transformation

The d-q transformation as performed in the DSP is illustrated in Fig. 3-13. A SOGI-QSG is used to produce a quadrature signal for the single-phase transformation [2]. The outputs of the SOGI-QSG are used along with the sine and cosine of the grid voltage angle to produce the d-and q-axis outputs. The discrete transfer functions from the Tustin approximation for both outputs of the SOGI-QSG are:

Figure 3-13. D-Q Transformation

$$\frac{y_q(z)}{x(z)} = \frac{qb_0 + qb_1z^{-1} + qb_2z^{-2}}{1 - qa_1z^{-1} - qa_2z^{-2}}$$

(3)

where,  $b_2$ ,  $a_1$ ,  $a_2$ ,  $qb_0$ ,  $qb_1$ ,  $qb_2$ ,  $qa_1$ , and  $qa_2$  are constant that are specified in:

$$b_0 = \frac{x}{(x+y+4)}$$

,  $b_2 = \frac{-x}{(x+y+4)}$  (4)

$$a_1 = \frac{2(4-y)}{(x+y+4)}$$

,  $a_2 = \frac{x-y-4}{(x+y+4)}$  (5)

$$qb_0 = \frac{1}{2}qb_1 = qb_2 = \frac{ky}{(x+y+4)},\tag{6}$$

$$x = 2k\omega_n T_s, y = (\omega_n T_s)^2 \tag{7}$$

using the fundamental frequency  $\omega_n$ , sampling period  $T_s$ , and the forward gain k.

#### 3.4 Simulation Results of the New Model

The substations currents from the new model in the continuous domain are shown in Fig. 3-14. This includes most of the changes mentioned above; however, it excludes all discretization modifications. As in Fig. 3-2 the waveforms encompass three different operating modes of the UCSC. From t = 0.00 s to t = 0.15 s, the UCSC is not operational. From t = 0.15 s to t = 0.25 s, the UCSC is compensating for the reactive power of the load. From t = 0.25 s to t = 0.60 s ,the UCSC is fully operational. At t = 0.40 s there is a step increase of 30% in one of the phase loads. The substation currents in steady state are brought to a *UBF* of 0.497%, where *UBF* is calculated using:

$$UBF = \frac{|negative\ sequence|}{|positive\ sequence|} x100\% \tag{8}$$

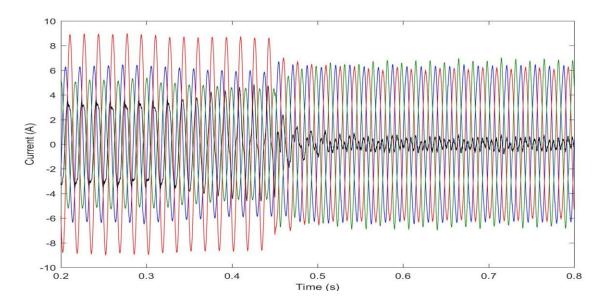

Using the rated currents and voltages for which the UCSC prototype was designed, discrete-domain simulations were run to predict the system performance. Demonstrating

Figure 3-14. Substation currents from new continuous model in different UCSC operating modes

the predicted prototype performance in the same operating modes as the case-study simulations, the substation currents are shown in Fig. 3-15. From  $t=0.20\,\mathrm{s}$  to  $t=0.30\,\mathrm{s}$ , the UCSC is not operational. From  $t=0.30\,\mathrm{s}$  to  $t=0.45\,\mathrm{s}$ , the UCSC is compensating for the reactive power of the load. And from  $t=0.45\,\mathrm{s}$  to  $t=0.80\,\mathrm{s}$ , the UCSC is fully operational. Some neutral current

Figure 3-15. Substation currents from the discrete-domain prototype simulation

exists due to the non-idealities that were introduced into the model. The most significant component of this neutral current is the third harmonic produced from dead time effect in the output of the UCSC inverters. In steady state, these simulations yielded an average *UBF* of 0.37%, down from an *UBF* of 18.2% when the UCSC is not operational.

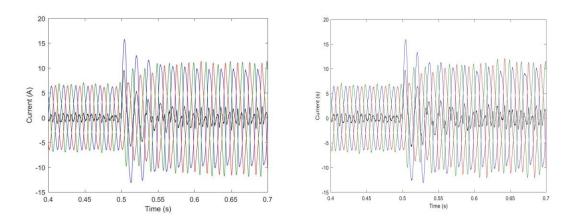

## 3.4.1 Effect of Incorrect Decoupling Terms

Within the current controller as described in Chapter 2 there are decoupling terms that allow for separate control of the d-axis and q-axis currents. Fig. 3-16(a) and Fig. 3-16(b) show the substation currents from the laboratory prototype simulations with and without the decoupling terms, respectively, during a large load change on one phase. Though they both perform as expected in steady-state, the simulation with the decoupling terms shows better transient response. The absence of the decoupling terms is an extreme case, but a diminished transient performance can also be caused by incorrect assumption about filter inductance values.

#### 3.5 Conclusions

Improvements made upon the UCSC controller improved its dynamic response and made it more stable. Through several other modifications, such as the discretization of the controller

Figure 3-16. Transient reponse of UCSC with (a) and without (b) decoupling terms

and the inclusion of dead time, a model that was more indicative of a real implementation of the UCSC was created. This model showed the compensator was still effective at reducing the negative- and zero-sequence fundamental current components as seen by the substation.

With the viability of the proposed solution confirmed by simulations the next step is the construction of a prototype that can be tested in a laboratory setting. Determining the effect of different component choices on the performance of the UCSC becomes easier with a simulation that emulates the non-ideal behavior of an actual prototype. The simulation can help to validate component choices before they are installed on the prototype.

#### 3.6 References

- [1] Manuel A. S. Tejada, "Unbalanced Current Static Compensator," Department of Electrical Engineering, University of Arkansas, Fayetteville, Masters Thesis 2014.

- [2] Texas Instruments, C28x Solar Library Module User's Guide, 2014.

#### **CHAPTER 4**

## DESIGN OF THE SCALED-DOWN UCSC PROTOTYPE

#### 4.1 Introduction

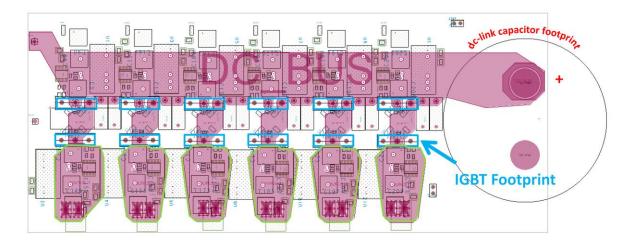

The objective of this chapter is to explain the process for designing and constructing the UCSC scaled-down prototype based on the 34.5 kV, 6 MVA case study. Thus, this chapter begins with the procedure used for scaling down the case study introduced in Chapter 1, and includes component selections as well as the printed circuit board layout. A comprehensive design process for AC inductors is also included because the required inductors are not commercially available.

### 4.2 Design of the Prototype Power Stage

#### 4.2.1 Scaling-Down the Case Study

A per-unit scaling is used to reduce the power rating of the case study in Chapter 1 to a level that can be produced in a laboratory environment. A base power  $S_{base} = 6$  MVA along with a base voltage  $V_{base} = 34.5$  kV are used to convert the case study parameters to their per unit equivalents. A base power  $S_{base,lab} = 10$  kVA and a base voltage  $V_{base,lab} = 208$  V were chosen based on the power delivery and voltage capabilities in the lab. These base values are then used to convert the per unit values from the case study into the real laboratory system values. The power rating for each of the UCSC prototype inverters is chosen based on the active and reactive power demand of the calculated loads. A summary of the results from these calculations is presented in Table 4-1. From these power ratings, each inverter was designed for 1 kVA at a voltage of 120  $V_{L-N}$ .

Table 4-1. Load power ratings for the case study and scaled-down prototype

| Parameter                 | Cast Study | Laboratory |  |  |

|---------------------------|------------|------------|--|--|

| P <sub>Load1</sub> (kW)   | 877        | 1.461      |  |  |

| Q <sub>Load1</sub> (kVAR) | 500        | 0.833      |  |  |

| P <sub>Load2</sub> (kW)   | 707        | 1.178      |  |  |