### This document is downloaded from DR-NTU (https://dr.ntu.edu.sg) Nanyang Technological University, Singapore.

# Current crowding effect on copper dual damascene via bottom failure for ULSI applications

Vairagar, A. V.; Tan, Cher Ming; Arijit, Roy; Krishnamoorthy, Ahila; Mhaisalkar, Subodh Gautam

2005

Tan, C. M., Arijit, R., Vairagar, A. V., Krishnamoorthy, A., & Mhaisalkar, S. G. (2005). Current crowding effect on copper dual damascene via bottom failure for ULSI applications. IEEE Transactions on Device and Materials Reliability, 5(2), 198-205.

https://hdl.handle.net/10356/100916

https://doi.org/10.1109/TDMR.2005.846830

© 2005 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted without the explicit permission of the copyright holder. http://www.ieee.org/portal/site.

Downloaded on 23 Aug 2022 03:02:14 SGT

## Current Crowding Effect on Copper Dual Damascene Via Bottom Failure for ULSI Applications

Cher Ming Tan, Senior Member, IEEE, Arijit Roy, A. V. Vairagar, Ahila Krishnamoorthy, and Subodh G. Mhaisalkar

Abstract—Reliability of interconnect via is increasing an important issue in submicron technology. Electromigration experiments are performed on line/via structures in two level Cu dual damascene interconnection system and it is found that wide line/via fails earlier than the narrow line/via. Atomic flux divergence based finite element analyses is performed and stress-migration is found to be important in the failure rate behavior observed. Semi-classical width dependence Black's equation together with the finite element analysis revealed that the difference in the time to failure is due to the much larger average current density along the interface between the line and via for the wide line/via structure, and good agreement is obtained between the simulation and experimental results.

Index Terms—Atomic flux divergence, copper, current crowding, via electromigration.

### I. INTRODUCTION

LECTROMIGRATION (EM) induced failure continues to be a major reliability issue as the feature size of ULSI technology is reducing. The ever increasing complexity of interconnect system requires more demanding reliability on the various components in the system. Today, the limiting factor in interconnect reliability is increasingly dominated by the EM performance of vias with the performance of lines playing a substantially lesser role in submicron technology [1]–[3]. The transition from Al to Cu interconnects leads to new via structure fabricated by dual damascene process, and the EM reliability of Cu interconnects has not been found to be as good as anticipated over Al interconnects [4]. A recent critical review can be found in [5] in this aspect.

In a via structure, current density, temperature, and stress distributions are not uniform as in an interconnect line. The peak current density appears at the inner corners of via-top and via-bottom, resulting in high local current density at the corners. This high local current density produces strong electron wind driving force and hence affects the median time to failure (MTF) as MTF is directly related to the current density by the semi-classical Black's formula. Furthermore, the atomic flux divergences due to nonuniform distributions of temperature and stress could be comparable to that due to electron-wind force.

Manuscript received September 5, 2004; revised November 5, 2004. This work was supported in part by A\*STAR/IME.

- C. M. Tan and A. Roy are with the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore 639798, Singapore (e-mail: ecmtan@ntu.edu.sg; PB2917949@ntu.edu.sg).

- A. V. Vairagar and S. G. Mhaisalkar are with the School of Materials Engineering, Nanyang Technological University, Singapore (e-mail: PB1750142@ntu.edu.sg; Subodh@ntu.edu.sg).

- A. Krishnamoorthy is with Semiconductor Process Technologies, Institute of Microelectronics, Singapore 117685 (e-mail: ahila@ime.a-star.edu.sg).

Digital Object Identifier 10.1109/TDMR.2005.846830

Moreover, Cu EM performance is strongly depends on the interface/surface available for mass transport [6], [7]. Unfortunately, chemical-mechanical polishing (CMP), an integral part of the Cu interconnect fabrication process, does not allow the top surface of metallization line to be covered by the barrier layer unlike its side walls and bottom surface. Therefore, at the inner corner of the via-bottom, two kinds of diffusion interface paths are available: one with Cu and barrier layer at the cylindrical via bottom; and the other with Cu and cap layer at the top surface of metallization near the cylindrical via. These are the locations at which the current is crowded. Hence, current crowding in via should be a dominant factor for via EM performance. Though the effect of current crowding has been reported for Al based interconnects, similar work has not been explored for Cu based interconnects. In this work, the effect of such current crowding on Cu via EM performance will be investigated.

In this work, we will focus on the via bottom failure of a two-level Cu dual damascene line/via structures with line widths of 0.28 and 0.7  $\mu$ m, respectively. They will be termed as narrow and wide line/via, respectively, in the subsequent discussion. Both structures have the same cylindrical via diameter of 0.26  $\mu$ m and line thickness of 0.35  $\mu$ m. EM experiments and three-dimensional (3-D) static finite element analysis (FEA) will be employed to explain the various physical failure mechanisms at the EM test condition.

### II. EXPERIMENTAL DETAILS

EM test structures with line widths of 0.28 and 0.7  $\mu$ m have been fabricated using 0.18  $\mu$ m Cu/oxide dual damascene technology. The first inter-metal dielectric (IMD) stack consisted of plasma enhanced chemical vapor deposited (PECVD) layer of 50 nm SiN and 800 nm undoped silicate glass (USG) on top of p-Si substrate using Novellus concept two Sequel Express PECVD system. M1 trench was patterned using 248 nm lithography, and the USG layer was etched using a fluorine-based dry-etch chemistry in TFL 85 DRM oxide etcher. Photoresist stripping and wet clean were performed to ensure polymer residue-free trenches.

Formation of Cu metallization in these trenches involved depositing a stack of 25 nm Ta barrier and 150 nm Cu seed by physical vapor deposition (PVD) in Applied materials PVD/CVD Endura HP 5500 followed by 0.6  $\mu$ m electrochemically plated (ECP) Cu layer using Novellus SABRE system. A 50 nm thick SiN layer was deposited after CMP process to serve as Cu cap layer. Then layers of 800 nm USG, 50 nm SiN and 500 nm USG were deposited as IMD-2 in which 50 nm SiN serve as trench-2 stop layer. Via and M2 trench were then formed by a via-first dual damascene process. In the M1 test structures, M2 (lines

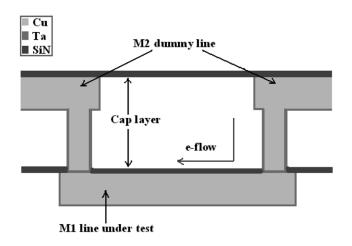

Fig. 1. Cross sectional schematic diagram of the test structure.

connected to pads) were short so that voids would be expected to form in M1 and is *vice versa* for the M2 test structures. The lines are  $0.35~\mu m$  thick and the via diameter is  $0.26~\mu m$  for all the test structures. Both the M1 and M2 test structures were fabricated on the same wafers while only EM characterization of M1 test structure will be discussed for the present work. Schematic diagram of the test structure employed in this study is shown in Fig. 1.

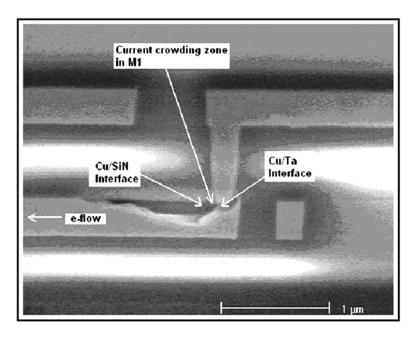

EM test was performed using *Qualitau* package level electromigration test system. Resistance increase with time was monitored until failure. Failure criterion of 10% increase in resistance was used in this study. Both the narrow and wide line/via M1 test structures were tested with 0.8 MA/cm² current density at three different temperatures of 300°C, 325°C, and 350°C, with their MTFs computed. The cumulative failure distributions for the narrow and wide line/via structure are shown in Figs. 2 and 3, respectively. The EM results are summarized in Table I. The narrow and wide line/via M2 test structures are also tested with the same EM test conditions as that of M1 test structures but their results will not be discussed in this work. The physical failure analysis has been performed using focused ion beam (FIB), and Fig. 4 shows a FIB image of a failed line/via structure.

### III. SIMULATION

In order to understand the various physical mechanisms in the via EM failure in this work, 3-D FEA was performed where the atomic flux divergences (AFD) due to various driving forces were computed. In contrast to a pure diffusion process in which the concentration gradient of the moving species is the only driving force, EM phenomenon is a completed diffusion process controlled by multiple physical mechanisms, including electron-wind force induced migration (EWM), stress induced migration (SM) as well as thermal induced migration or thermo-migration (TM). The mathematical implementation for the atomic flux divergences due to theses physical mechanisms has been described by Dalleau *et al.* [8] with common activation energy for the three migration processes. However, this is not true from microscope point of view. A detail discussion on this fact can be found in a line EM work presented by Zhang *et al.*

Fig. 2. Cumulative failure distribution for the narrow line/via.

Fig. 3. Cumulative failure distribution for the wide line/via.

[9] and Tan *et al.* [10]. In this work, we follow the later work and applied to a via/line structure.

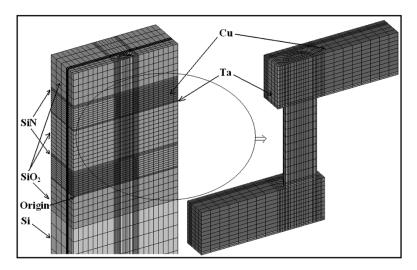

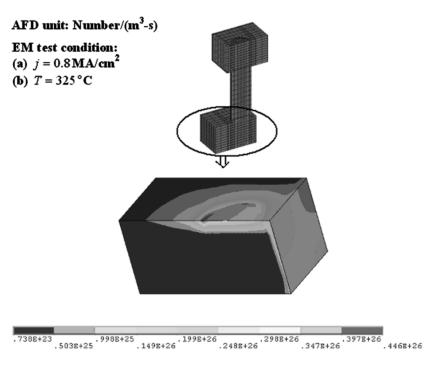

The basic structure after discritization for FEA is shown in Fig. 5. The length, width, and thickness of the structure are taken along the X, Y, and Z (vertical direction) axes, respectively. The location of the global origin of the coordinate system is shown in Fig. 5, and all the computational results are calculated with

Fig. 4. FIB image of a via bottom failure.

Fig. 5. Typical meshing of the line/via structure for FEA.

TABLE I EM TEST DATA

| Stressing<br>Temp.<br>(in °C) | t narrow ( in hrs) for narrow line/via | $t_{50}^{wide}$ (in hrs) for wide line/via | Ratio of $\frac{t_{50}^{narrow}}{t_{50}^{wide}}$ from experiment | Ratio of $\frac{t_{50}^{narrow}}{t_{50}^{wide}}$ using equation (2) with n=1.9 |

|-------------------------------|----------------------------------------|--------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 300                           | 418.8                                  | 315.4                                      | 1.33                                                             | 1.33                                                                           |

| 325                           | 280.2                                  | 203.3                                      | 1.38                                                             | 1.38                                                                           |

| 350                           | 189.4                                  | 132.9                                      | 1.43                                                             | 1.42                                                                           |

respect to this origin. For realistic, the full substrate thickness of 300  $\mu$ m is considered in the model.

The multiphysics finite element analysis software ANSYS is used here. As the element aspect ratio is limited to 20 in the software, it is difficult to discritize all the sub-domains in the structure by using the "Mesh Tool" or "Map Mesh" to mesh the entire structure. Therefore, direct generation technique is used for discritization [11].

In addition, complexity arises due to the fact that the circular via-end surfaces are connected to the rectangular metallization surfaces. Such connection requires both the cylindrical and rectangular coordinate systems to be considered in the model, and proper connection between the two coordinate systems is necessary. Hence, every node in the meshing is created by defining its coordinates and "brick" element is formed that connect the adjacent 8 nodes with defined material properties. With this way of building the FE model, though it is tedious, the user can have a full control and flexibility on the model.

It is a common practice to take the stress-free temperature (SFT) of the damascene interconnects in between 350 °C to

TABLE II

EM PARAMETERS FOR FE SIMULATION

| Parameter                    | Material | Value                               | Reference |

|------------------------------|----------|-------------------------------------|-----------|

| Electronic charge (e)        | -        | 1.6021 × 10 <sup>-19</sup>          | -         |

|                              |          | Coulomb                             |           |

| Boltzmann's constant         | -        | $1.3867 \times 10^{-23}$            | -         |

| $(k_B)$                      |          | Joule/°K                            |           |

| Atom concentration           | Cu       | $8.44 \times 10^{-28} / \text{m}^3$ | -         |

| Activation energy for        | Cu       | 0.6 eV                              | -         |

| EWM                          |          |                                     |           |

| Activation energy SM         | Cu       | 0.74 eV                             | [14]      |

| Effective charge             | Cu       | 4                                   | [10]      |

| number $(Z^*)$               |          |                                     |           |

| Diffusion constant           | Cu       | $7.8 \times 10^{-5}$                | [16]      |

| $(D_{\theta})$               |          | $m^2/s$                             |           |

| Atomic volume $(\Omega)$     | Cu       | $1.18 \times 10^{-29} \mathrm{m}^3$ | -         |

| Resistivity @ 20°C           | Cu       | $1.69 \times 10^{-8}$               | [17]      |

| $(\boldsymbol{ ho}_{	heta})$ |          | $\Omega$ -m                         |           |

| Temperature                  | Cu       | $4.3 \times 10^{-3}$                | [18]      |

| coefficient of               |          | Ω-m/°K                              |           |

| resistivity ( <b>α)</b>      |          |                                     |           |

| Resistivity @ 300 °C         | Ta       | $70 \times 10^{-8}$                 | [19]      |

| (ρ)                          |          | Ω-m                                 |           |

$400\,^{\circ}\text{C}$  [12]–[14], depending on annealing temperature of the sample. In this work,  $300\,^{\circ}\text{C}$  is taken as SFT in the simulation.

The FEA model developed here consists of two steady state analyses, namely a direct coupled analysis with the current and temperature fields, and an analysis with indirect coupling between temperature and stress fields. In the first stage of analysis, the substrate bottom surface is kept at constant EM test temperature, and a constant line current density of 0.8 MA/cm<sup>2</sup> is applied as boundary conditions. The nodal temperatures are then retrieved from this stage for use in the second stage of simulation. In the second stage of simulation, structural analysis is performed with the following three boundary conditions: 1) nodal temperatures obtained in the first stage of analysis are used as the body force temperature; 2) the substrate bottom surface is kept fixed i.e., no displacement is allowed to the bottom surface of Si substrate; and 3) the vertical symmetric plane is constrained to remain vertical as arise from the mirror symmetrical nature of the structure under consideration.

With this model, the atomic flux divergences due to EWM, SM, and TM are computed for the wide line/via test structure considering the three different test temperatures of 300 °C, 325 °C, and 350 °C with the same line current density of 0.8 MA/cm² at time zero of EM test for all the cases. All the dimensional parameters in the simulation are exactly same as the experimental test structure. The EM parameters and materials properties used in the simulation are listed in Tables II and III.

### IV. RESULTS AND DISCUSSION

### A. EM Test Data Analysis

From the CDF plots in Fig. 2 and 3, one can see that there is significant variation of the  $log\text{-}normal\ \sigma$  with stressing temperature. As significant difference in  $\sigma$  implies different failure mechanisms, one should expect the activation energy  $(E_a)$  of EM is different at different test temperatures.

TABLE III

MATERIAL PROPERTIES FOR FE SIMULATION

| Material | Young's<br>Modulus<br>(GPa) | Poisson<br>ratio | Thermal<br>conducti<br>vity<br>(W/mK) | Coefficient<br>of thermal<br>expansion<br>(/°K) | Reference  |

|----------|-----------------------------|------------------|---------------------------------------|-------------------------------------------------|------------|

| Cu       | 129.8                       | 0.339            | 379                                   | $16.5 \times 10^{-6}$                           | [17], [19] |

| Ta       | 186.2                       | 0.35             | 53.65                                 | $6.48 \times 10^{-6}$                           | [20]-[21]  |

| SiN      | 265                         | 0.27             | 0.8                                   | $1.5 \times 10^{-6}$                            | [22]-[25]  |

| $SiO_2$  | 71.4                        | 0.16             | 1.75                                  | $0.68 \times 10^{-6}$                           | [12], [17] |

| Si       | 130                         | 0.28             | 61.9                                  | $4.4 \times 10^{-6}$                            | [12], [17] |

However, it is interesting to note that, the  $\sigma$ 's are very close for the two line widths at a given test temperature. Since it is reported that  $E_a$  vary with line width [26], and with the close  $\sigma$  values observed between the two line widths, we should expect that their  $E_a$  difference should be small.

In order to determine the difference in  $E_a$ , we estimated the  $E_a$  using the data from the two test temperatures of 300 and 325 °C. This  $E_a$  can be viewed as the mean  $E_a$  in the temperature range of 300–325 °C. The  $E_a$  values obtained are 0.48 and 0.52 eV for the narrow and wide line/via structures, respectively. Hence, the difference in  $E_a$  is only 0.04 eV, which is indeed small as expected. From the  $E_a$  values calculated, one can see that the failure is interfacial diffusion dominated [4], [5].

Note here that the test data from 350 °C is not used for the above-mentioned calculation of  $E_a$  because its  $\sigma$  value is too much difference from that at 300 °C. Hence, its inclusion in the average  $E_a$  computation could render a large error.

The  $E_a$  of around 0.5 eV might indicate poor copper process. However, for the M2 test structures fabricated together with the M 1 test structures studied in this work, the EM failure data of the M2 test structures show an activation energy of 0.85 and 0.88 eV for the narrow and wide line/via, respectively. Thus the activation energy in this case is within 0.8–1.0 eV, characteristic of a robust copper processes [4], [5]. Hence the low value of  $E_a$  in the M1 test failure should not be taken as an indication of the poor copper process, instead it represents a different physical mechanism underlying the electromigration processes.

### B. Atomic Flux Divergence (AFD) Distribution

As AFD is the basic element for void mechanic in EM, we studied the AFD distribution in detail. To study the AFDs due to various driving forces under consideration, we compute the distribution of the AFD over the portion of the structure from the via zone to M1 line 0.5  $\mu$ m away from the via zone. The AFD will be expected to be maximum around the via zone, and minimum along the M1 line far away from the zone. It is found that the distribution is the same if it is beyond 0.5  $\mu$ m from the via zone in M1 line.

From the simulation, the contribution of AFD due to TM was found to be negligible (5 order less) as compared to the AFD contributions due to EWM and SM. This is consistent with the report made recently by Nguyen *et al.* [27].

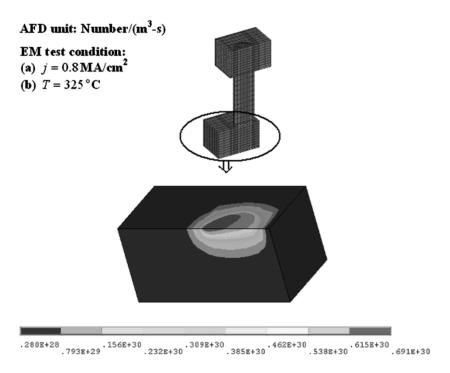

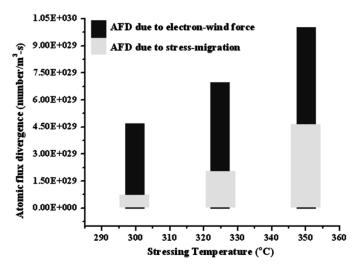

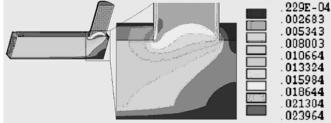

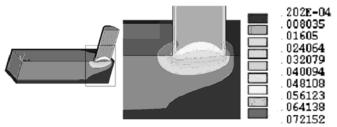

As an example, the AFD distribution due to EWM and SM at test temperature of 325 °C for the case of wide line/via are shown in Figs. 6 and 7, respectively. One can note that the maximum (positive) AFD zones for both the EWM and SM are the

Fig. 6. AFD distribution due to the EWM.

Fig. 7. AFD distribution due to the SM.

same, and they coincide with the failure zone as found in the experiments. The AFD distributions due to EWM and SM are shown in Fig. 8. From this figure, it is clear that the contribution due to SM increases with increasing test temperature. This probably explain the difference in the log-normal  $\sigma$  observed at different test temperatures.

It can also be noted that the SM contribution to the total AFD is much higher in case of wide line/via compared to that in the narrow line/via. This is because at the same current density,

more heat will be generated which will increase the temperature in the case of wide line/via compared to narrow line/via, causing larger degree of nonuniformity in the stress distribution in the structure in the case of wide line/via.

It is also to be noted here that only qualitative information can be drawn from this static AFD calculation [28]. In reality, during the void growth, AFD will vary, and hence quantitative conclusion can be made only with dynamic model, and this is beyond the scope of the present work.

Fig. 8. AFD distributions at three EM test temperatures.

### C. Via Bottom Current Density Dependency

From the above discussion, one concludes that the EM process was mainly governed by EWM up to the test temperature of 325 °C for the EM test structures under investigation. Therefore, the "current crowing effect" in the line/via structure must be taken into account to understand the MTF behavior of the structures since MTF is inversely proportional to AFD [8], [29].

To ensure the same electron-wind driving force, which is proportional to applied current density rather than the current, both the structures were tested with the same line current density, though the total current in the wide line/via will be 2.5 times of that in the narrow line/via at the same current density level. The EM reliability of the two interconnect structures at service condition with same current can be estimated by extrapolating the EM test data using reliability statistics [30]. Such extrapolation is however beyond the scope of this work.

The via bottom has been identified experimentally as the failure location for both narrow and wide line/via structures at the Cu/Ta or Cu/SiN interfaces in the M1 line. As can be seen in Figs. 9 and 10, the magnitudes of the average current densities along the interfaces of Cu/Ta and Cu/SiN near the via bottom for both structures depend on the line width. It can be computed that the average current density for the narrow line/via (Fig. 9) is 1.7 times the current density in the M1 line, and it is 4.9 times the M1 current density in case of wide line/via (Fig. 10).

The higher ratio of the average current density along the interfaces mentioned above for the wide line/via structure can be understood as follows. As the line current density is the same for both cases, the total current is higher in the wide line/via structure. However, the via diameter is the same for all the test structures, and thus the current is much crowded in the wide line/via structure. This renders the average current density having a higher ratio over the current density in M1 line, and making the current crowed zone more vulnerable to failure.

Under such a high current density, it is reasonable to assume that Cu/Ta or Cu/SiN interfaces are the dominant diffusion path. The average activation energies found earlier do suggest that the Cu interface/surface is indeed the dominant diffusion path.

Fig. 9. Current density contour plots for the narrow line/via.

Fig. 10. Current density contour plots for the wide line/via.

On the other hand, since the thickness of Ta barrier is 25 nm in our experiments, it is adequate to act as a perfect blocking boundary to the Cu atom flow [31]. Thus, the interface diffusion can only occur at the interface between M1 line and the cap layer near the via zone or at the interface between M1 line and Ta via bottom barrier, and the failure is in essence a line electromigration failure.

The  $t_{50}$  of line EM is given by the width dependence Black's equation [32] as follows:

$$t_{50} = BWj^{-n} \exp\left(\frac{E_a}{kT}\right) \tag{1}$$

where B is a constant depending on the material, failure criteria etc., W is the line width, j is the current density,  $E_a$  is the activation energy and n is the current density exponent. It is generally agreed that electromigration failure that is controlled by the nucleation of void should yield n=2 [33], and for the case of "downstream" stressing (i.e., the direction of electron flow is same with the present case) in Cu damascene line/via structure, it was reported that the value of n is between 1.87 to 2.01 [26].

Therefore, the ratio of  $t_{50}$  for narrow to wide line/via structure is given by

$$\frac{t_{50}^{\text{narrow}}}{t_{50}^{\text{wide}}} = \left(\frac{W^{\text{narrow}}}{W^{\text{wide}}}\right) \left(\frac{j_{\text{int}}^{\text{narrow}}}{j_{\text{int}}^{\text{wide}}}\right)^{-n} \exp\left(\frac{\Delta E_a}{kT}\right)$$

(2)

where the superscripts narrow and wide correspond to the narrow and wide line/via, respectively. The subscript int refers to the interface current density at the line/via bottom interface, and  $\Delta E_a$  is the difference in activation energies of the narrow and wide line/via structures which is found to be -0.04 eV as computed previously.

In order to estimate n, (2) was evaluated using the simulated current density at test temperature at  $300\,^{\circ}\text{C}$  with n varying from 1.8 to 2.0. It is found that n=1.9 for the  $t_{50}$  ratio in (2) to agrees well with our experimental data, and this value of n is well within the reported value [26]. With this value of n, we computed the  $t_{50}$  ratio at other test temperatures, and the results

are summarized in Table I. One can see an excellent agreement between the simulation and experimental results.

On the other hand, if the  $t_{50}$  ratio using (2) is computed without considering the current crowding, we will have the factor  $(j_{\rm int}^{\rm narrow}/j_{\rm int}^{\rm wide})^{-n}$  equal to 1 as line current densities are the same for both the structures. For the case where the test temperature is 325 °C, the MTF ratio will be 0.18 which is far from the experimental observation. Hence, this study implies that the uniform line current density cannot be used to estimate the MTF of via EM, and indeed the current crowding effect affect the MTF significantly. The average current density along the interface at line/via bottom should be used to compute the MTF of the via bottom EM failure for the line/via structure.

### V. CONCLUSION

Current crowding is found to be a dominant factor in via bottom failure for deep submicron Cu interconnects via structure. The failure time for wide line/via has been found to be shorter as compared to narrow line/via at identical EM test condition due to the effect of current crowding. From our 3-D finite element analyses, it is shown that the stress induced migration cannot be ignored at high test temperature, which is  $350\,^{\circ}$ C in this work. The increasing contribution of stress induced migration in the EM process probably explains the decrease in log-normal  $\sigma$  with increasing test temperature.

The uniform line current density is found to be inappropriate for the estimation of MTF of EM in the line/via structure, but the width dependence Black's equation with average current density along the line/via interface provides an excellent approximation for the MTF.

### REFERENCES

- J. S. Huang, T. L. Shofner, and J. Zaho, "Direct observation of void morphology in step-like electromigartion resistance behavior and its correlation with critical current density," *J. Appl. Phys.*, vol. 89, pp. 2130–2133, Feb. 2001.

- [2] J. A. Walls, "The influence of TiN ARC thickness on stress-induced void formation in tungsten-plug vias," *IEEE Trans. Electron Devices*, vol. 44, no. 12, pp. 2213–2219, Dec. 1997.

- [3] J. S. Huang, C. C. Y. Everett, Z. B. Zhang, and K. N. Tu, "The effect of contact resistance on current crowding and electromigration in ULSI multilevel interconnects," *Mat. Chem. Phys.*, vol. 77, pp. 377–383, Jan. 2003.

- [4] J. R. Lloyd, J. Clemens, and R. Snede, "Copper metallization reliability," *Microelectron. Rel.*, vol. 39, pp. 1595–1602, Nov. 1999.

- [5] E. T. Ogawa, K. D. Lee, V. A. Blascheke, and P. S. Ho, "Electromigration reliability issues in dual-damascene Cu interconnects," *IEEE Trans. Reliabil.*, vol. 51, no. 12, pp. 403–419, Dec. 2002.

- [6] M. W. Lane, E. G. Liniger, and J. R. Lloyd, "Relationship between interfacial adhesion and electromigration in Cu metallization," *J. Appl. Phys.*, vol. 93, pp. 1417–1421, Feb. 2003.

- [7] E. Glickman and M. Nathan, "On the unusual electromigration behavior of copper interconnects," *J. Appl. Phys.*, vol. 80, pp. 3782–3791, Oct. 1996.

- [8] D. Dalleau and K. Weide-Zaage, "Three-dimensional voids simulation in chip metallization structure: A contribution to reliability evaluation," *Microelectron. Rel.*, vol. 41, pp. 1625–1630, Oct. 2001.

- [9] G. Zhang, C. M. Tan, Z. H. Gan, K. Prasad, and D. H. Zhang, "Comparison of the time-dependent physical processes in the electromigration of deep submicron copper and aluminum interconnects," in 2003 Proc. Mat. Res. Soc. Symp., vol. 766, pp. 139–144.

- [10] C. M. Tan, G. Zhang, and Z. Gan, "Dynamic study of the physical processes in the intrinsic line electromigration of deep submicron copper and aluminum interconnects," *IEEE Trans. Device Mater. Reliab.*, vol. 4, no. 3, pp. 450–456, Sep. 2004.

- [11] ANSYS User's Manual, ANSYS Inc., Canonsburg, PA.

- [12] Y.-L. Shen and U. Ramamurty, "Temperature-dependent inelastic response of passivated copper films: Experiments, analyses, and implications," *J. Vacuum Sci. Technol. B*, vol. 21, no. 4, pp. 1258–1264, Jul. 2003

- [13] S.-H. Rhee, Y. Du, and P. S. Ho, "Thermal stress characteristics of Cu/oxide and Cu/low-k submicron interconnect structure," *J. Appl. Phys.*, vol. 93, no. 7, pp. 3926–3933, Apr. 2003.

- [14] S. P. Hau-Riege and C. V. Thompson, "The effects of the mechanical properties of the confinement material on electromigration in metallic interconnects," *J. Mater. Res.*, vol. 15, no. 8, pp. 1797–1802, Aug. 2000.

- [15] E. T. Ogawa, J. W. McPherson, J. A. Rosal, K. J. Dickerson, T. C. Chiu, L. Y. Tsung, M. K. Jain, T. D. Bonifield, J. C. Ondrusek, and W. R. McKee, "Stress-induced voiding under vias connected to wide Cu metal leads," in *Proc. IEEE Reliability Physics Symp.*, 2002, pp. 312–321.

- [16] K. L. Lee, C. K. Hu, and K. N. Tu, "In situ scanning electron microscope comparison studies on electromigration of Cu and Cu(Sn) alloys for advanced chip interconnects," *J. Appl. Phys.*, vol. 78, pp. 4428–4437, Oct. 1995

- [17] Y.-L. Shen, "Analysis of Joule heating in multilevel interconnects," *J. Vacuum Sci. Technol. B*, vol. 17, no. 5, pp. 2115–2121, Sep. 1999.

- [18] C.-C. Chang, J. S. Jeng, and J. S. Chen, "Microstructural and electrical characteristics of reactively sputtered Ta-N thin films," *Thin Solid Films*, vol. 413, pp. 46–51, Jun. 2002.

- [19] Y.-L. Chin and B.-S. Chiou, "Effects of underlayer dielectric on the thermal characteristics and electromigration resistance of copper interconnect," *Jpn. J. Appl. Phys.*, vol. 42, no. 12, pp. 7502–7509, Dec. 2003.

- [20] Engineering Material Properties [Online]. Available: http://apo.nmsu.edu

- [21] R. K. Williams, R. S. Graves, T. L. Hebble, D. L. McElroy, and J. P. Moore, "Phonon and electron components of the thermal conductivity of tantalum at intermediate temperatures," *Phys. Rev. B*, vol. 26, no. 6, pp. 2932–2942, Sep. 1982.

- [22] D. Schneider and M. D. Tucker, "Non-destructive characterization and evaluation of thin films by laser-induced ultrasonic surface waves," *Thin Solid Films*, vol. 290–291, pp. 305–311, Dec. 1996.

- [23] J.-H. Zhao, W.-J. Qi, and P. S. Ho, "Thermomechanical property of diffusion barrier layer and its effect on the stress characteristics of copper submicron interconnect structures," *Microelectron. Rel.*, vol. 42, pp. 27–34, Jan. 2002.

- [24] S.-M. Lee and D. G. Cahill, "Heat transport in thin dielectric films," J. Appl. Phys., vol. 81, no. 6, pp. 2590–2595, Mar. 1997.

- [25] T. F. Retajczyk Jr. and A. K. Sinha, "Elastic stiffness and thermal expansion coefficients of various refractory silicides and silicon nitride films," Thin Solid Films, vol. 70, no. 2, pp. 241–247, Aug. 1980.

- [26] D. Padhi and G. Dixit, "Effect of electron flow on model parameters of electromigration-induced failure of copper interconnects," *J. Appl. Phys.*, vol. 94, pp. 6463–6467, Nov. 2003.

- [27] H. V. Nguyen, C. Salm, B. Krabbenborg, K. Weide-Zaage, J. Bisschop, A. J. Mouthaan, and F. G. Kuper, "Effect of thermal gradients on the electromigration lifetime in power electronics," in *Proc. IEEE Relia-bility Physics Symp.*, 2004, pp. 619–620.

- [28] C. Q. Ru, "Intrinsic instability of electromigration induced mass transport in a two-dimensional conductor," *Acta Mater.*, vol. 47, pp. 3571–3578, Oct. 1999.

- [29] G. Weiling, L. Jhiguo, J. Tianyi, C. Yaohai, C. Changhua, and S. Guangdi, "The electromigration and reliability of VLSI metallization under temperature gradient conditions," in *Proc. IEEE Solid-State and Integrated Circuit Technology*, 1998, pp. 226–229.

- [30] L. M. Gignac, C.-K. Hu, and E. G. Liniger, "Correlation of electromigration lifetime distribution to failure mode in dual damascene Cu/SiLK interconnects," *Microelectron. Eng.*, vol. 70, pp. 398–405, Nov. 2003.

- [31] E. G. Liniger, C.-K. Hu, and L. M. Gignac, "Effect of liner thickness on electromigration lifetime," J. Appl. Phys., vol. 93, pp. 9576–9582, Jun. 2002

- [32] J. R. Black, "Electromigration—A brief survey and some recent results," IEEE Trans. Electron Devices, vol. ED-16, no. 4, pp. 338–347, Apr. 1969.

- [33] M. Shatzkes and J. R. Lloyd, "A model for conductor failure considering diffusion concurrently with electromigration resulting in a current density exponent of 2," J. Appl. Phys., vol. 59, pp. 3890–3893, Jun. 1986.

Cher Ming Tan (M'84–SM'00) was born in Singapore in 1959. He received the B.Eng. degree (Hons.) in electrical engineering from the National University of Singapore in 1984, and the M.A.Sc. and Ph.D. degrees in electrical engineering from the University of Toronto, Toronto, ON, Canada, in 1988 and 1992, respectively.

He joined Nanyang Technological University (NTU) as an academic staff in 1997, and he is now an Associate Professor in the School of Electrical and Electronic Engineering. His current research

areas are reliability data analysis, electromigration reliability physics and test methodology, and quality engineering such as QFD. He also works on silicon-on-insulator structure fabrication technology and power semiconductor device physics.

Dr. Tan is currently an Executive Committee member of the IEEE Singapore Section, Chairman of the Certified Reliability Engineer Board of Singapore Quality Institute, and Committee member of the Strategy and Planning Committee of the Singapore Quality Institute. He has also been elected to the Research Board of Advisors of the American Biographical Institute and was elected International Educator of the Year 2003 by the International Biographical Center, Cambridge, U.K. He is now appointed as a Fellow of the Singapore Quality Institute and a Fellow of the Singapore Institute of Manufacturing Technology. He is currently listed in *Who's Who in Science and Engineering* as well as *Who's Who in the World* due to his achievements in science and engineering.

connects.

Arijit Roy received the B.Sc. degree in physics (Hons.) from North Bengal University, India, in 1996, the M.Sc. degree in physics from the Indian Institute of Technology, Kharagpur, in 1999, and the M.Tech. degree in instrument technology from the Indian Institute of Technology, Delhi, in 2000. He is presently pursuing the Ph.D. degree in the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore.

His research interests are electromigration, stress migration reliability physics of copper ULSI interA. V. Vairagar, photograph and biography not available at the time of publication

Ahila Krishnamoorthy has been a Senior Research Scientist with the Institute of Microelectronics, Singapore, since April 2001. Her interests are in the process integration and reliability improvement of Cu-low k and Cu-ultra low-k back end of the line interconnects. Prior to this, she developed self-passivating Cu metallization and self-assembled monolayer diffusion barriers at Rensselaer Polytechnic Institute, Troy, NY, from 1997 to 2000. She holds two patents on methods to develop a Cu-alloy diffusion barrier.

Subodh G. Mhaisalkar has over 10 years of experience in Senior R&D and Process Engineering positions in the field of microelectronics. He has held positions of Director of Engineering in ST Assembly and Test Services and Senior Managerial positions in National Semiconductor and Gintic Institute of Manufacturing Technology Singapore (now renamed to SIMTech). His area of expertise has been reliability, process engineering, packaging design, and development of advanced electronic materials. In his career in the industry, he has pioneered

design, process, thermal management, and design elements for packaging of microprocessors, flip chip assemblies, plastic packages, and advanced ball grid arrays. His current research interests include polymer electronics (thin film transistor, photovoltaics, and memory devices), nanoelectronics materials (processes and reliability) and microelectronics and optoelectronics materials, processes, and packaging.