# Current mismatch reduction in charge pumps using regulated current stealing-injecting transistors for PLLs

# Mohd Khairi Zulkalnain, Yan Chiew Wong

Faculty of Electronic and Computer Engineering, Universiti Teknikal Malaysia Melaka, Malaysia

| Article Info                                                           | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Article history:                                                       | A charge pump for phase locked loops (PLL) with a novel current mismatch com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Received May 16, 2021<br>Revised Jul 16, 2021<br>Accepted Jul 28, 2021 | pensation technique is proposed. The proposed circuit uses a simple yet effective<br>current stealing-injecting (CSI) technique and feedback to reduce mismatch between<br>the negative-channel-metal-oxide (NMOS) and positive-channel-metal-oxide (PMOS)<br>transistors. The current stealing transistor steals the current from a replica branch and                                                                                                                                                                                                                                                               |  |  |  |  |

| Keywords:                                                              | mirrors it to the output where it is added to the output branch by the injecting tran-<br>sistor. A feedback mechanism is used to set the drain voltages of both branches to                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Charge pump<br>Current mismatch<br>Phase locked loop                   | be equal and mitigate channel length modulation and ensure high accuracy. The pro-<br>posed circuit was designed on Silterra 130nm technology and simulated using Cadence<br>Spectre. The simulation results show that the proposed circuit yields a maximum of<br>0.107% and minimum of 0.00465% current mismatch while operating at a low supply<br>voltage of 800mV for a range of 100mV to 700mV. The proposed design uses only<br>one rail-to-rail op amp for compensating the mismatch and an addition of 4 transistors<br>and utilizing 75% of the supply voltage for high voltage controlled oscillator (VCO) |  |  |  |  |

This is an open access article under the CC BY-SA license.

## **Corresponding Author:**

Yan Chiew Wong Faculty of Electronic and Computer Engineering Universiti Teknikal Malaysia Melaka Jalan Hang Tuah Jaya, Durian Tunggal, 76100, Melaka, Malaysia Email: ycwong@utem.edu.my

tuning range.

## 1. INTRODUCTION

Recently, there has been an increasing demand for continuous supply of integrated circuits or better known as chips, for various purposes, the most recent and prevalent applications being 5G wireless chips and processors. One common block in these chips is the phase locked loops (PLL). The motivation of this work is to build one of the most important building blocks in a PLL system, namely, the charge pump. As mentioned earlier, the PLL has seen usage in chips, specifically serializes and deserializes (SERDES) protocols and radio frequency (RF) transceiver systems. In SERDES protocols, the PLL in the transmitter chain is responsible for the timing functionality [1]-[3]. Meanwhile, in RF transceivers, the PLL is used for the up-conversion and down-conversion of the signal through the mixer [4]-[6]. Apart from that, PLLs can also be used as frequency multipliers in microcontrollers, autonomous batteryless circuits [7] and as a clock generator in wireless sensor nodes (WSN) for health monitoring systems [8].

This work highlights the research problem with the charge pump in the PLL that can disrupt the PLL operation due to the current mismatch of the up current carried by the positive-channel-metal-oxide (PMOS) and down current carried by the negative-channel-metal-oxide (NMOS). Specifically, the current mismatch

causes reference spur and static phase offset in the PLL leading to PLL spectral impurity [9]-[12]. The implication of the spectral impurity in the PLL caused by current mismatch in the SERDES system is that the reference spur causes jitter in the PLL and degrades the timing capabilities on the transmitter side. Meanwhile, in the RF transceiver the implication of an impure spectral performance in the PLL manifests itself in the form of an overlap in the desired signal and the nearby adjacent signal when the mixer up-converts an RF signal. Therefore, it is imperative that the current mismatch problem be minimized in the PLL.

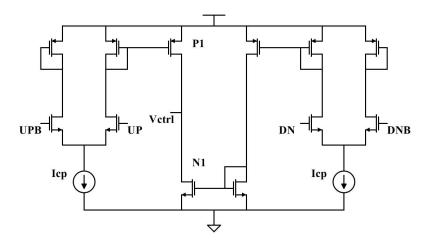

Consider a conventional current steering charge pump depicted in Figure 1. The current mismatch between the PMOS and NMOS exists due to the difference in the transistor electron mobility ( $\mu C_{ox}$ ) and threshold voltage ( $V_{th}$ ) values of the different transistors, leading to different current values carried by the NMOS and PMOS transistors at the output branch namely N1 and P1 respectively. On top of that, the channel length modulation causes the current through these transistors to vary largely due to variation in Vctrl. Since the Vctrl is supplied at the drain of both NMOS and PMOS transistors, the current will vary largely, hence degrading the accuracy. The problem is made even worse at lower voltage, since the current mirrors have limited headroom to operate in saturation, especially when the Vctrl is close to the upper and lower rails, these PMOS and NMOS, will be pushed to the triode region and hence degrade the current mirror performance. This translates to limited Vctrl range in which the charge pump can operate optimally and consequently affect the tuning range of the voltage controlled oscillator (VCO). Ideally, a VCO should have a wide tuning range to achieve a wide frequency range, which translates to high VCO gain and ease of PLL locking.

Figure 1. Conventional current-steering charge pump

This work attempts to minimize the current mismatch by using negative feedback technique to ensure the down current in the NMOS tracks the up current in the PMOS. The novelty of this work compared to other works in literature is the technique in which the feedback configuration is carried out, which is using a simple yet effective current stealing-injecting (CSI) technique and feedback to reduce mismatch between the NMOS and PMOS transistors. Other than that, this work is capable of operating down to a low supply voltage of 0.8V. Lastly, the amount of components used in the proposed charge pump design are far less compared to those reported in literature. Specifically, the proposed charge pump only uses one rail to rail op amp and an addition of 4 transistors.

## 2. RELATED WORKS IN CHARGE PUMP DESIGN

## 2.1. Advanced mismatch calibration techniques

Lin *et al.* [13] proposed two techniques to overcome the charge pump mismatch, namely by using a dynamic charge pump with current-matching capabilities. Other than that, they proposed introducing a DC offset to the output of the charge pump in order to increase linearity and decrease spur in the PLL. A PLL employing the random pulsewidth matching (RPWM) and sub-sampling charge pump (SSCP) technique was demonstrated in [14]. This work attempts improve the spur performance using the mentioned techniques by averaging, randomizing and lastly reducing the ripples at the output of the charge pump which is fed into the

63

VCO. The works by [15]-[17] employ digital calibration techniques to calibrate the charge pump mismatch. The typical blocks involved include a lock detector (LD), some form of phase detector, a digitally-controlled charge pump and calibration circuitry. The calibration circuitry can be in the form of digital-to-analog converter (DAC), filter and digital logics, as is the case in [15] or even successive-approximate register (SAR) based logic [16]-[17] and controls the digitally-controlled charge pump calibration process. The idea is basically the same, that is, the LD functions to detect whether the PLL has been locked and signals the start of calibration. The phase detector, either bang bang phase detector (BBPD) [15]-[16] or high resolution phase detector (HRPD) [17], functions to detect the difference of phase between the reference frequency and the feedback frequency. HRPD is an improvement of the BBPD proposed by [17] and is superior in terms of accuracy.

## 2.2. Analog-centric techniques

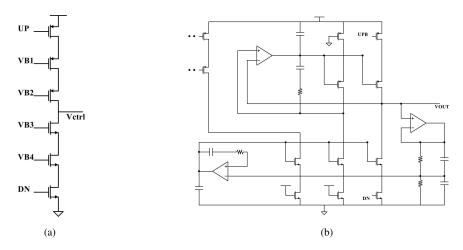

Other more traditional approaches are more analog centric in the way that they employ negative feedback loops and replica bias techniques to handle the current mismatch [19]-[24]. Some of these techniques are viable only due to the abundance of voltage headroom while others are inherently complex in terms of design implementation, that is they require additional circuitry for current compensation. For example, Figure 2(a) shows the charge pump architecture by [18] in which a cascode structure was used. Since the transistors need to be in saturation region, the  $V_{DS}$  of each stacked transistor must be high, hence the output voltage, Vctrl is limited to a range of roughly  $2V_{DSn}$  to  $V_{DD} - 2V_{SDp}$ . On top of that, this technique is only viable when there is ample headroom for the transistors to saturate and is not suitable for low voltage design.

With regards to complexity, while the mentioned works use the concept of negative feedback, the key here is to use as fewer components as possible for implementing the compensation schemes. As an example, Figure 2(b) shows the charge pump design proposed by [19] in which a lot of extra circuitry was added in order to compensate the current mismatch such as 3 op amps, capacitors and resistors. Other than that, the work by [20] uses 1 rail to rail op amp while also adding extra circuitry for current compensation and mismatch cancellation. Hwang *et al.* [21] use 2 op amps in a dual feedback loop to compensate the current mismatch. On the other hand, Lozada and Espinosa [23] designed a fully differential charge pump which requires double the normal circuitry to operate. A bulk-driven charge pump in triple well technology was proposed by [24] which uses 1 op amp with the addition of several transistors and also resistors.

Figure 2. Examples of charge pump architectures; (a) A cascode charge pump design by [18], (b) A charge pump design by [19] utilizing 3 op amps as the compensation scheme

#### 2.3. Low voltage techniques

The recent trend of CP design is moving towards low supply voltage architectures. Some of the recent CP circuit design techniques that have been employed for low voltage operation include gate switching CP [25]-[26], DTMOS transistors for leakage control [27], diode-connected MOS CP [28], non-cascode source-switch CP [29], clock-gated CP with tunable low pass filter (LPF) [30] and dual feedback loop CP [31].

From the literature survey, it can be concluded that there is room for improvement in terms of the complexity of the architecture used in order to compensate the current mismatch. It can be seen that previous

Current mismatch reduction in charge pumps using regulated current stealing ... (Mohd Khairi Zulkalnain)

works, especially the advanced techniques use a lot of components or blocks in implementing the compensation such as SAR and DAC. This could potentially increase power consumption and area of the PLL. The analogcentric approach also has the advantage of simplicity and can be further exploited to operate at lower voltage. Similar to the advanced techniques, existing analog-centric architecture uses bulky compensation circuitry that can be further reduced to save area and power consumption. This work will focus on employing a current mismatch reduction technique that minimzes number of components used so as to reduce complexity while operating at low supply voltage. At the same time, the employed technique maximizes the utilization of the limited headroom at low supply voltage for high VCO tuning range.

## 3. RESEARCH METHOD

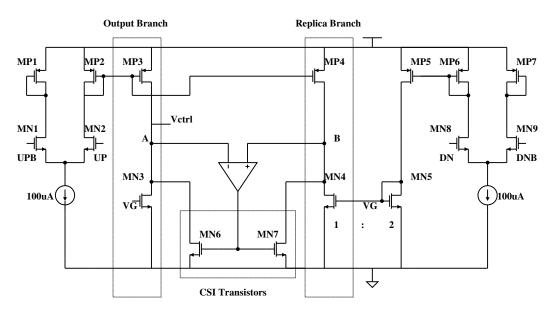

The proposed charge pump is shown in Figure 3. It consists of the current steering charge pump, a replica branch to replicate the output branch and a pair of current stealing-injecting transistors. The replica branch is added to the current steering charge pump to extract the current mismatch via a current stealing transistor and inject the current back to the output branch. The current stealing transistor MN7 steals some current from the replica branch and mirrors it to the transistor MN6 which then injects the current to the output branch. The op amp is used in negative feedback configuration to set nodes A and B to be equal and ensure that the transistors in both branches have the same  $V_{DS}$  and hence have the same residue current flowing into MN7 and out of MN6. This scheme reduces the mismatch as the current injected into output branch through MN6 is forced to track the residue current from the replica branch via MN7 using negative feedback. In order to ensure the feedback is functioning, the ratio of the current flowing through MN4 and MN3 to MN5 should not be equal to 1. This work, the ratio of MN5 to MN4 is 2:1, that is the current flowing through MN4 and MN3 is half of that in MN5. Table 1 shows the device sizing of the proposed charge pump circuit.

Figure 3. The proposed current-steering charge pump with current stealing-injecting (CSI) technique and feedback

The sourcing and sinking of current of the charge pump will be controlled by a block called the phase frequency detector (PFD) in the PLL. The PFD will output a high or low signal to the switches, namely transistors MN1, MN2, MN8 and MN9. For example, if the UP signal is high, while DN signal is low, the branch with MN2 will hog the current and MP2 will mirror the current to the output stage. Meanwhile, the branch containing MP7 and MN9 will hog all the current since the DN signal is low, leaving no current to flow from MP6 to MP5.

|        | $\mathcal{O}$ | 1 1    |             |

|--------|---------------|--------|-------------|

| Device | Size          | Device | Size        |

| MP1    | 30u/1u, m=2   | MN2    | 4u/130n     |

| MP2    | 30u/1u, m=2   | MN3    | 20u/1u, m=4 |

| MP3    | 30u/1u, m=2   | MN4    | 20u/1u, m=4 |

| MP4    | 30u/1u, m=2   | MN5    | 20u/1u, m=8 |

| MP5    | 30u/1u, m=2   | MN6    | 10u/1u, m=4 |

| MP6    | 30u/1u, m=2   | MN7    | 10u/1u, m=4 |

| MP7    | 30u/1u, m=2   | MN8    | 4u/130n     |

| MN1    | 4u/130n       | MN9    | 4u/130n     |

Table 1. Device sizing for the proposed charge pump design

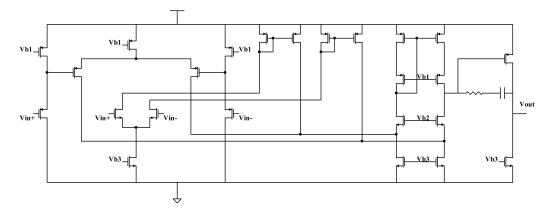

The opposite happens when the UP signal is low and DN is high. In order to ensure wide compliance range of the charge pump, a rail to rail input op amp must be used. This work uses a rail-to-rail amp by [32] for constant-gm operation. The op amp used in this design uses a common drain input stage as a DC level shifter to shift the input voltages down and ensure constant-gm operation, followed by a common source stage. The input stage is followed by a current summing stage and a folded cascode load. A push-pull configuration was used for the output stage with miller compensation. The op amp design is depicted in Figure 4.

Figure 4. The rail-to-rail input op amp with common drain input stage as DC level shifter for constant-gm operation [32]

# 4. RESULT AND DISCUSSION

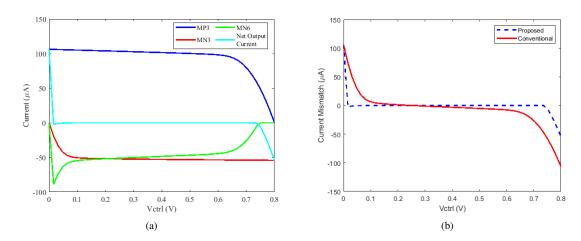

A pre-layout SPICE simulation was done using Cadence Spectre EDA tool to verify the effectiveness of the proposed technique in reducing the current mismatch in the charge pump. The simulation environment is under typical transistor conditions at a temperature of  $27^{\circ}$ . Figure 5(a) shows the drain current that is drawn by transistors at the output branch, namely MP3, MN3, MN6 and the net current. As explained previously, the drain current of MP3 carries  $100\mu$ A, while MN3 carries  $50\mu$ A. The drain current of MN6 is mirrored from MN7 and it tracks the difference of current between the MP4 and MN4, which ideally is  $50\mu$ A. The drain current of MN6 is injected to the output node A to compensate for the mismatch. The net output current is given by the sum of the drain currents of MP3, MN3 and MN6. As depicted, it can be seen that the net output current is relatively constant in the  $0\mu$  regime, signifying that the output current mismatch is minimized.

Figure 5(b) shows the comparison of current mismatch with and without the current stealing-injecting and feedback technique. For the conventional charge pump, it can be seen that the current mismatch varies greatly when the Vctrl is varied from 0V to 0.8V, achieving up to an absolute current mismatch of  $26\mu$ A or 26%across the range of 100mV to 700mV. In contrast, the proposed charge pump circuit is relatively constant with an absolute maximum and minimum current mismatch of only 107 nA or 0.107% and 4.65 nA or 0.00465% respectively for the same range with 75% utilization of the headroom. The stark contrast between the current mismatch of the proposed and the conventional charge pump is a testament to the effectiveness in reducing the current mismatch in charge pumps. On top of that, the proposed circuit guarantees a mismatch of less than 1% from 31mV to 737mV which is 87.5% of the available headroom. From the Figure 5, it can also be noticed that when Vctrl approaches the upper and lower supply rails, the current mismatch deteriorates as the transistors MP3, MP4 and MN3 and MN4 will go into the linear region.

Current mismatch reduction in charge pumps using regulated current stealing ... (Mohd Khairi Zulkalnain)

Figure 5. The current mismatch simulation results; (a) Drain current of transistors at the output branch, (b) Current mismatch when Vctrl is varied from 0 to 0.8V

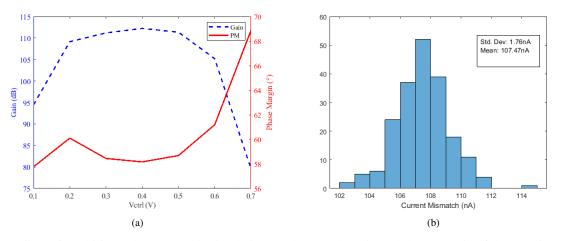

In order to ensure the proposed circuit is not oscillating, the stability of the negative feedback loop in the charge pump design is analyzed. Figure 5(a) shows the gain and phase margin of the proposed charge pump over the input Vctrl range of 100mV to 700mV. As can be seen, the achieved gain is from 79.58 dB to 112.23 dB. The phase margin range is from 57.8° to 68.9° indicating that the design is stable since it is within the vicinity of 60°. A Monte Carlo statistical simulation is carried out to verify under process variation, namely the ( $\mu C_{ox}$ ) and ( $V_{th}$ ). By running the Monte Carlo simulation, the extent of process variation on the current mismatch can be gauged. The Monte Carlo was run using Cadence Spectre tool with the confidential model files as the input given by the foundry, which cannot be disclosed. Figure 6(b) shows the Monte Carlo simulation of the proposed charge pump.

Figure 6. Stability and Monte Carlo simulation results; (a) The gain and phase margin of the negative feedback loop in the proposed charge pump design, (b) Statistical Monte Carlo simulation for current mismatch with 200 runs

The design achieved an absolute maximum current mismatch with a mean of 107.4nA and standard deviation of 1.76nA, proving that it is a robust design over global and local variations. It can be seen that although subjected to process variation, the Monte Carlo simulation shows that the mismatch closely agrees with the pre-layout simulation under typical conditions. Table 2 summarizes the performance of the proposed CSI relative to previous works in charge pump design. From the table, it can be seen that the proposed design has the lowest current mismatch among all other works reported in literature. The calculation of the percentage of utilization is (High boundary - Low boundary)/VDD \* 100% In the proposed design, the high boundary

is 700mV while the low boundary of the 100mV. The boundaries are taken at 100mV from the supply voltage (800mV) and ground (0V) to ensure the transistors at the output and replica branch have sufficient  $V_{DS}$  to operate in saturation. With a supply voltage (VDD) of 800mV, the proposed charge pump yields a percentage of utilization of 75%. On top of that, the design operates at a supply voltage of 800mV, which is the lowest among all the other works and still manage to achieve 75% utilization, on par with or better than other works. This superior current mismatch performance will enable it to minimize the effects of spur on the PLL and ensure spectral purity.

|                               | 1         | 1       |             | 01    | 1 0      |         |       |

|-------------------------------|-----------|---------|-------------|-------|----------|---------|-------|

|                               | This Work | [20]    | [21]        | [22]  | [23]     | [24]    | [25]  |

| Technology (nm)               | 130       | 180     | 65          | 130   | 65       | 180     | 180   |

| Supply Voltage (V)            | 0.8       | 3       | 1.0         | 1.2   | 1.1      | 1.8     | 1.2   |

| Vctrl Range (V)               | 0.1-0.7   | 0.2-2.7 | 0.1-0.85    | 0.2-1 | 0.1-0.92 | 0.3-1.5 | 0.2-1 |

| Absolute Current Mismatch (%) | 0.005-0.1 | 2.1     | 0.023-0.432 | 3.2   | 0.05     | 0.32    | 0.9   |

| Up/Down Current ( $\mu A$ )   | 100       | 600     | 150         | 100   | 1000     | 100     | 140   |

| Percentage of Utilization (%) | 75        | 83.33   | 75          | 66.67 | 74.5     | 66.67   | 66.67 |

| Standard Deviation (%)        | < 0.02    | NA      | < 0.03      | 1.7   | <2       | <3.5    | NA    |

Table 2. Comparison of previous works in charge pump design

#### 5. CONCLUSION

A novel charge pump utilizing the CSI technique and feedback was designed to minimize the current mismatch which is important to reduce spur which will deteriorate the spectral purity of the PLL. The proposed charge pump uses only 1 rail to rail op amp in addition to 4 more transistors for the compensation scheme, which is low in complexity, resulting in high accuracy and minimal mismatch. Pre-layout SPICE simulation results using Cadence Spectre EDA tool show significant improvement over existing architectures in literature in terms of current mismatch, achieving a maximum and minimum mismatch of 0.107% and 0.00465% respectively at 800 mV supply voltage from a range of 100mV to 700mV. The design is also robust across process variations and is suitable for low voltage applications. In the future, the layout for the charge pump will be design for silicon fabrication. On top of that, the proposed charge pump design will be integrated at the top level with other blocks such as PFD, VCO, frequency divider and low pass filter for the system level PLL design. The practical applications of this includes RF wireless transceivers targeting applications such as WiFi, Bluetooth or 5G can have better PLL performance. Other than that, SERDES protocol chips that employ a PLL for timing purposes such as MIPI, SONET, USB, HDMI, PCI Express, Ethernet protocols can have accurate timing circuitry.

#### REFERENCES

- J. Lee, P. Chiang, P. Peng, L. Chen and C. Weng, "Design of 56 Gb/s NRZ and PAM4 SerDes Transceivers in CMOS Technologies," *IEEE Journal of Solid-State Circuits*, vol. 50, pp. 2061-2073, 2015, doi: 10.1109/JSSC.2015.2433269.

- [2] Z. Zhang, G. Zhu, C. Wang, L. Wang and C. P. Yue, "A 32-Gb/s 0.46-pJ/bit PAM4 CDR Using a Quarter-Rate Linear Phase Detector and a Self-Biased PLL-Based Multiphase Clock Generator," *IEEE Journal of Solid-State Circuits*, vol. 55, no. 10, pp. 2734-2746, Oct. 2020, doi: 10.1109/JSSC.2020.3005780.

- [3] A. Roshan-Zamir et al., "A 56-Gb/s PAM4 Receiver With Low-Overhead Techniques for Threshold and Edge-Based DFE FIR- and IIR-Tap Adaptation in 65-nm CMOS," *IEEE Journal of Solid-State Circuits*, vol. 54, no. 3, pp. 672-684, March 2019, doi: 10.1109/JSSC.2018.2881278.

- [4] S. Ek, et al., "A 28-nm FD-SOI 115-fs Jitter PLL-Based LO System for 24–30-GHz Sliding-IF 5G Transceivers," IEEE Journal of Solid-State Circuits, vol. 53, no. 7, pp. 1988-2000, July 2018, doi: 10.1109/JSSC.2018.2820149.

- [5] W. El-Halwagy, A. Nag, P. Hisayasu, F. Aryanfar, P. Mousavi and M. Hossain, "A 28-GHz Quadrature Fractional-N Frequency Synthesizer for 5G Transceivers With Less Than 100-fs Jitter Based on Cascaded PLL Architecture," *IEEE Trans. on Microwave Theory and Techniques*, vol. 65, no. 2, pp. 396-413, Feb. 2017, doi: 10.1109/TMTT.2016.2647698.

- [6] D. Liao, H. Wang, F. F. Dai, Y. Xu and R. Berenguer, "An 802.11a/b/g/n Digital Fractional- N PLL With Automatic TDC Linearity Calibration for Spur Cancellation," 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2016, pp. 134-137, doi: 10.1109/RFIC.2016.7508269.

- [7] C. C. Boon, M. V. Krishna, M. A. Do, K. S. Yeo, A. V. Do and T. S. Wong, "A 1.2 V 2.4 GHz low spur CMOS PLL synthesizer with a gain boosted charge pump for a batteryless transceiver," in 2012 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 2012, pp. 222-224, doi: 10.1109/RFIT.2012.6401667.

Current mismatch reduction in charge pumps using regulated current stealing ... (Mohd Khairi Zulkalnain)

- [8] C. Y. Saw, Y. C. Wong, S. L. Loh, and H. Zhang, "On-chip ultra low power optical wake-up receiver for wireless sensor nodes targeting structural health monitoring," *TELKOMNIKA (Telecommunication, Computing, Electronics* and Control), vol. 18, no. 5, pp. 2257-2264, 2020, doi: 10.12928/TELKOMNIKA.v18i5.13378.

- [9] P. Su and S. Pamarti, "Mismatch Shaping Techniques to Linearize Charge Pump Errors in Fractional-N PLLs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 6, pp. 1221-1230, June 2010, doi: 10.1109/TCSI.2009.2031746.

- [10] S. Kim, J. Rhim, D. Kwon, M. Kim and W. Choi, "A low-voltage PLL with a current mismatch compensated charge pump," in 2015 International Soc Design Conference (ISOCC), 2015, pp. 15-16, doi: 10.1109/ISOCC.2015.7401629.

- [11] H. M. S. Fazeel, L. Raghavan, C. Srinivasaraman and M. Jain, "Reduction of Current Mismatch in PLL Charge Pump," in 2009 IEEE Computer Society Annual Symposium on VLSI, 2009, pp. 7-12, doi: 10.1109/ISVLSI.2009.45.

- [12] Vaishali and R. K. Sharma, "Low Power Charge Pump with reduced Glitch for PLL Applications," in Second International Conference on Intelligent Computing and Control Systems, 2018. ICICCS 2018 Second International Conference on Intelligent Computing and Control Systems (ICICCS), 2018, pp. 1-4, doi: 10.1109/ICCONS.2018.8662928.

- [13] T. Lin, C. Ti and Y. Liu, "Dynamic Current-Matching Charge Pump and Gated-Offset Linearization Technique for Delta-Sigma Fractional- N PLLs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 56, no. 5, pp. 877-885, May 2009, doi: 10.1109/TCSI.2009.2016180.

- [14] T. Liao, C. Chen, J. Su and C. Hung, "Random Pulsewidth Matching Frequency Synthesizer With Sub-Sampling Charge Pump," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 59, no. 12, pp. 2815-2824, Dec. 2012, doi: 10.1109/TCSI.2012.2206462.

- [15] P. Yang, Y. Guo, H. Jiang and Z. Wang, "A 360–456 MHz PLL frequency synthesizer with digitally controlled charge pump leakage calibration," in 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2019, pp. 285-286, doi: 10.1109/A-SSCC47793.2019.9056900.

- [16] Y. Chen, Y. Yu and Y. E. Chen, "A 0.18-μ m CMOS Dual-Band Frequency Synthesizer With Spur Reduction Calibration," *IEEE Microwave and Wireless Components Letters*, vol. 23, no. 10, pp. 551-553, Oct. 2013, doi: 10.1109/LMWC.2013.2279113.

- [17] C. Liang, S. Chen and S. Liu, "A Digital Calibration Technique for Charge Pumps in Phase-Locked Systems," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 2, pp. 390-398, Feb. 2008, doi: 10.1109/JSSC.2007.914283.

- [18] N. T. Hieu, T. Lee and H. Park, "A Perfectly Current Matched Charge Pump of CP-PLL for Chip-to-Chip Optical Link," in 2007 Conference on Lasers and Electro-Optics - Pacific Rim, 2007, pp. 1-2, doi: 10.1109/CLEOPR.2007.4391088.

- [19] N. Joram, R. Wolf, and F. Ellinger, "High swing PLL charge pump with current mismatch reduction," *Electronics Letters*, vol. 50, no. 9, pp. 661-663, 2014, doi: 10.1049/el.2014.0804.

- [20] A. G. Amer, S. A. Ibrahim and H. F. Ragai, "A novel current steering charge pump with low current mismatch and variation," in 2016 IEEE International Symposium on Circuits and Systems (ISCAS), 2016, pp. 1666-1669, doi: 10.1109/ISCAS.2016.7538887.

- [21] M. S. Hwang, J. Kim, and D.-K. Jeong, "Reduction of pump current mismatch in charge-pump PLL," *Electronics Letters*, vol. 45, no. 3, pp. 135-136, 2009, doi: 10.1049/el:20092727.

- [22] K. Moustakas and S. Siskos, "Low voltage CMOS charge pump with excellent current matching based on a rail-torail current conveyor," in 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), 2015, pp. 1-4, doi: 10.1109/NEWCAS.2015.7182077.

- [23] O. Lozada and G. Espinosa, "A charge pump with a 0.32% of current mismatch for a high speed PLL," Analog Integr. Circuits Signal Process, vol. 86, pp. 321-326, 2016, doi: 10.1007/s10470-015-0676-y.

- [24] P. Liu, P. Sun, J. Jung, and D. Heo, "PLL charge pump with adaptive body-bias compensation for minimum current variation," *Electronics Letters*, vol. 48, no. 1, pp. 16-18, 2012, doi: 10.1049/el.2011.2835.

- [25] D. Zhong, Y. Han, J. Sun, Q. Zhou, R. C. C. Cheung, and W. Sui, "A perfectly current matched charge pump with wide dynamic range for ultra-low voltage applications," *IEICE Electron. Express*, vol. 11, no. 23, 2014, doi: 10.1587/elex.11.20140993.

- [26] K. Cheng, Y. Tsai, Y. Lo and J. Huang, "A 0.5-V 0.4–2.24-GHz Inductorless Phase-Locked Loop in a System-on-Chip," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 58, no. 5, pp. 849-859, May 2011, doi: 10.1109/TCSI.2010.2089559.

- [27] S. Ikeda, S. Lee, H. Ito, N. Ishihara and K. Masu, "A 0.52-V 5.7-GHz low noise sub-sampling PLL with dynamic threshold MOSFET," in 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2014, pp. 365-368, doi: 10.1109/ASSCC.2014.7008936.

- [28] A. Paidimarri, N. Ickes and A. P. Chandrakasan, "A 0.68V 0.68mW 2.4GHz PLL for ultra-low power RF systems," in 2015 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2015, pp. 397-400, doi: 10.1109/RFIC.2015.7337789.

- [29] S. Yu and P. Kinget, "A 0.65-V 2.5-GHz Fractional-N Synthesizer With Two-Point 2-Mb/s GFSK Data Modulation," IEEE Journal of Solid-State Circuits, vol. 44, no. 9, pp. 2411-2425, Sept. 2009, doi: 10.1109/JSSC.2009.2023156.

Indonesian J Elec Eng & Comp Sci, Vol. 24, No. 1, October 2021 : 61 – 69

68

69

- [30] B. Xiang, Y. Fan, J. Ayers, J. Shen and D. Zhang, "A 0.5V-to-0.9V 0.2GHz-to-5GHz Ultra-Low-Power Digitally-Assisted Analog Ring PLL with Less Than 200ns Lock Time in 22nm FinFET CMOS Technology," in 2020 IEEE Custom Integrated Circuits Conference (CICC), 2020, pp. 1-4, doi: 10.1109/CICC48029.2020.9075897.

- [31] M. Jalalifar and G.S. Byun, "Near-threshold charge pump circuit using dual feedback loop," *Electronics Letters*, vol. 49, no. 23, pp. 1436-1438, 2013, doi: 10.1049/el.2013.1304.

- [32] M. Wang, T. L. Mayhugh, S. H. K. Embabi and E. Sanchez-Sinencio, "Constant-gm rail-to-rail CMOS op-amp input stage with overlapped transition region," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 2, pp. 148-156, Feb. 1999, doi: 10.1109/4.743758.

#### **BIOGRAPHIES OF AUTHORS**

**Mohd Khairi Zulkalnain** is a Master's student at Universiti Teknikal Malaysia Melaka (UTeM), Malaysia. He obtained his Bachelor's degree at Iowa State University in 2014. His research interests include designing analog blocks, data converters and RF circuits. He is currently working as an Analog IC Design Engineer at a local company in Malaysia.

**Yan Chiew Wong** Associate Professor Dr. Wong Yan Chiew has completed her doctorate from The University of Edinburgh, United Kingdom on 2014. She has more than 5 years industry experience in semiconductor process design. Has previously worked at Infineon Technologies and Intel. Yan Chiew has involved intensively in the research of RF and mixed signal circuitries, adaptive impedance matching and power management control system. She has authored a number of research papers in the field of adaptive algorithm, RF reconfigurable design, EDA and etc. She has been able to successfully design and develop high voltage CMOS control chips and RF circuitries. She is equipped with both design and implementation skills.